# Selective Harmonic Mitigation Technique for High Power Converters

J. Napoles, J. I. Leon, *Member, IEEE*, R. Portillo, *Member, IEEE*, L. G. Franquelo, *Fellow Member, IEEE*, and M. A. Aguirre, *Member, IEEE*

Abstract—In high power applications the maximum switching frequency is limited due to thermal losses. This leads to highly distorted output waveforms. In such applications, it is necessary to filter the output waveforms using bulky passive filtering systems. The recently presented selective harmonic mitigation technique (SHMPWM) produces output waveforms where the harmonic distortion is limited fulfilling specific grid codes when the number of switching angles is high enough. The related technique has been previously presented using a switching frequency equal to 750Hz. In this paper, a special implementation of the SHMPWM technique optimized for very low switching frequency is studied. Experimental results obtained applying SHMPWM to a three-level neutral point clamped converter using a switching frequency equal to 350Hz are presented. The obtained results show that the SHMPWM technique improves the results of previous selective harmonic elimination (SHEPWM) techniques for very low switching frequencies. This fact highlights that the SHMPWM technique is very useful in high power applications leading its use an important reduction of the bulky and expensive filtering elements.

Index Terms-Multilevel systems, Harmonic distortion, Filters.

## I. INTRODUCTION

**I** N HIGH power applications, the harmonic content of the output waveforms has to be reduced as much as possible in order to avoid distortion in the grid and to reach the maximum energy efficiency. On such applications, the thermal losses in the power semiconductors limit the maximum switching frequency to a few hundreds of Hertz and multilevel converters are the most suitable power systems to be used. Many recent works with different multilevel converter topologies have been recently presented showing their good performance for high power applications [1]–[3].

In addition, it is necessary to use special modulation techniques and filtering systems in order to fulfil the grid codes in the point of common coupling. Usually grid codes establish specific limits for harmonics up to  $50^{th}$  and for the total harmonic distortion (THD). The passive filters used to reduce harmonic distortion into the grid are very bulky and expensive.

On the other hand, the use of an efficient modulation method is very convenient to obtain output waveforms with acceptable harmonic content. One of the most interesting modulation techniques for high power applications is the well known selective harmonic elimination pulse width modulation (SHEPWM) technique originally presented in [4]. This technique is able to obtain output signals with lower harmonic content than other techniques because makes zero a limited number of low order harmonics. On the other hand, the recently presented selective harmonic mitigation pulse width modulation (SHMPWM) technique [5] is able to relax the constraints used in the SHEPWM technique to obtain output waveforms with better harmonic performance taking into account actual grid regulations. In [5] it was shown that using the SHMPWM technique with the switching frequency equal to 750Hz, it is possible to fulfil both the CIGRE WG 36-05 and EN 50160 grid code requirements without using any additional filtering system. In this paper, a very low switching frequency equal to 350 Hz is considered using only 7 switching angles which leads to new designs of the objective function (OF) of the SHMPWM technique. This is a big difference with reference [5] where the high number of switching angles achieved the fulfillment of the grid code without using filtering systems. In this paper it is shown that using 7 switching angles, some harmonics are above the maximum limits of the grid code even using the SHMPWM technique. An analytical way to define the OF has been introduced in this paper defining factors such as the safety margin  $\rho$  and the penalty factor  $\lambda_p$ . Depending on the specific application of the high power converter, two possible solutions to define the OF have been introduced. The different solutions (strategies S1 and S2) are focused on the improvement of different harmonics as is explained in section IV. A comparison with the SHEPWM technique in the same low switching frequency conditions is included. A three-phase three-level diode clamped converter is used as experimental setup to illustrate the benefits obtained by the SHMPWM technique.

Using SHEPWM it is possible to make zero a limited number of harmonics but the non canceled harmonics are not considered in the algorithm and could reach very high amplitudes. This leads to the fact that it is not possible to keep them below a desired value having a great impact in the size and cost of the filtering system. However, the flexibility of SHMPWM can be used to apply different criteria for low and high order harmonics considered in the grid code. Low order harmonics can be reduced to values below the limits specified in the grid code. High order harmonics, where there is not any control using SHEPWM, can be reduced using SHMPWM. In this paper, the computing effort of the SHMPWM technique is

Manuscript received February 5, 2009. Accepted for publication June 11, 2009. Copyright © 2009 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org. J. Napoles, J. I. Leon, L. G. Franquelo, R. Portillo and M. A. Aguirre are with the Electronic Engineering Department, University of Seville (Spain), (e-mail: jnl@gte.esi.us.es).

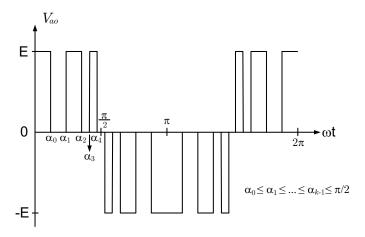

Fig. 1. Three-level pre-programmed PWM switching pattern with five switching angles  $(\alpha_0, \alpha_1, \alpha_2, \alpha_3, \alpha_4)$ .

focused on reducing as much as possible the harmonic content which has to be filtered to fulfil the grid code. The main goal is to reduce the filtering requirements in order to decrease the size, weight and cost of the filtering elements.

This paper is organized as follows; in section II the SHM-PWM principle is briefly summarized. Next section describes the filter design problem and the most commonly used solution. In section IV, the differences between SHEPWM and SHMPWM techniques are detailed and a comparison using the obtained simulation results is carried out in section V. Experimental results validating the improvements obtained using the SHMPWM method are presented in section VI. Finally, the conclusions of the paper are detailed in the last section.

## **II. SHMPWM PRINCIPLE**

The Fourier analysis of the typical three-level preprogrammed PWM switching pattern (Fig. 1) considering k switching angles  $\alpha_i$  (*i*=0,...,*k*-1) generates the following equations where  $H_j$  is the harmonic amplitude of  $j^{th}$  order:

$$H_{j} = \frac{4}{j\pi} \sum_{i=0}^{k-1} \left[ (-1)^{i} \sin(j\alpha_{i}) \right],$$

where  $j = 1, 2, \dots, n.$  (1)

These equations can be solved in order to obtain the harmonic amplitudes  $H_1$ ,  $H_2$ ,...,  $H_n$  desired values. Classic SHEPWM technique fixes the value of  $H_1$  (which is normally called modulation index  $(M_a)$ ) to a certain value and also eliminates k-1 harmonics. Usually, the most interesting harmonic orders to be eliminated are the odd non-triplen ones because using three-phase topologies without neutral connection the triplen harmonics do not appear in the line-to-line voltages. Therefore, the application of the SHEPWM technique leads to solve the following expressions:

$$H_{1} = \frac{4}{\pi} \sum_{i=0}^{k-1} \left[ (-1)^{i} \sin(\alpha_{i}) \right]$$

$$0 = \frac{4}{j\pi} \sum_{i=0}^{k-1} \left[ (-1)^{i} \sin(j\alpha_{i}) \right],$$

where  $j = 5, 7, 11, \dots, q.$  (2)

The SHMPWM technique is based on the idea that it is not necessary to reduce to zero the harmonics while they are kept below acceptable levels. Those levels are defined by the grid codes which establish maximum allowed limits for each harmonic order and THD in order to maintain the quality of the grid. The SHMPWM technique is based on solving the following inequalities system where  $L_i$  is the maximum allowed level imposed by the applied grid code.

$$|M_a - H_1| \le L_1$$

$$\frac{1}{|H_1|} \frac{4}{j\pi} \sum_{i=0}^{k-1} \left[ (-1)^i \sin(j\alpha_i) \right] \le L_j,$$

where  $j = 5, 7, 11, \dots, 49.$  (3)

The SHMPWM method relaxes the restrictions of (2) and is able to generate output signals with low harmonic content applying (3). This fact allows to consider more harmonic orders than the SHEPWM technique as can be observed from (2) and (3). This flexibility is very useful in high power systems due to the filtering system requirements will be relaxed which leads an important reduction in the cost, volume and weight of the filtering components. Hence, it is possible to choose the most appropriate filtering shape for each application previously to the computing process.

The inequalities system (3) can be synthesized in an objective function (OF) which has to be minimized:

$$OF(\alpha_0, \dots, \alpha_{k-1}) = \sum_{i=1, 5, \dots, 49} c_i E_i^2 + c_{THD} THD.$$

(4)

The  $c_i$  coefficients of the OF are modeled as non linear functions and, in general, have been implemented as follows:

$$if (E_i < \rho L_i) c_i = 1;$$

else  $c_i = \lambda_p;$  (5)

Where  $\rho \epsilon(0, 1]$  is the safety margin of the maximum allowed level  $L_i$  and  $\lambda_p$  is defined as the penalty factor ( $\lambda_p \gg 1$ ).

The  $L_i$  values correspond to the maximum allowed levels shown in (3). As can be observed from expression (5), if the obtained harmonic distortion of order  $i^{th}$  ( $E_i$ ) is below the 80% (assuming that  $\rho$ =0.8) of its corresponding  $L_i$  value, the associated  $c_i$  is equal to 1. In other case, as the distortion is close to the maximum allowed value  $L_i$ , a penalty is imposed in the  $c_i$  coefficient in order to focus the optimization search reducing the distortion in this specific harmonic order. This penalty is defined as the weight factor  $\lambda_p$ . In [5], where the SHMPWM technique was introduced using 15 switching angles, a safety margin  $\rho$  equal to 0.8 and a constant ratio penalty factor  $\lambda_p$  equal to 1000 was used. The  $L_i$  values were equal to the maximum values defined by the applied grid code. As was shown in [5], using 15 switching angles per quarter of period gives enough flexibility to completely fulfill the grid code. However, for very high power applications, a low number of switching angles has to be used. In this paper, 7 switching angles have been applied (this corresponds to switching frequency equal to 350Hz) and this does not allow enough margin to meet the grid codes without any additional filtering system. In this way, as examples of the flexibility of the SHMPWM technique, different particularizations of the expression (5) have been applied in order to achieve several optimization criteria.

It must be noticed that the definition of the  $c_i$  functions is the base of the SHMPWM technique because they must be adapted to the concrete conditions of the application. In this paper two different strategies have been studied and the details of each implementation will be discussed in section IV.

The whole system described by (3) and (4) can be solved using an optimization method. Different algorithms have been tested but the well known simulated annealing optimization method [6], [9] has been finally used in the present paper because it easily allows new formulations of the problem. Other methods such as particle swarm, tabu search, genetic algorithms, ant colony systems, stochastic evolution, etcetera would obtain similar results [7], [8], [10].

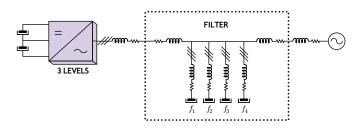

# III. FILTER DESIGN

High power converters have to work at very low switching frequency leading to output signals with undesired harmonic distortion. These harmonics have to be filtered in order to maintain the quality in the power supply. The obtained experimental results presented in this paper show that the SHMPWM technique is a powerful tool to be applied in order to relax the final filtering requirements. Any other element which reduces the harmonic content as the coupling transformer can also be considered in order to relax the requirements of the filter. There are different possible filtering strategies to reduce the harmonic content generated by power converters. The most commonly used are passive filters, active filters and hybrid filters mixing both passive and active modules [11]-[13]. In high power applications, passive filters are normally the most suitable solution. The filter topology most commonly used in high power applications is the LCL filter with harmonic traps (Fig. 2). The filter design is a very important topic because in high power applications the reactive elements are very bulky and expensive. Some important design guides can be found in [14] and [15]. The most important problem related to passive filters is the existence of possible resonances with the grid [16]. Different techniques have been reported in order to avoid this phenomenon when passive filters are used [17].

# IV. SHMPWM vs SHEPWM

As it has been commented above, the SHEPWM technique has been widely used for high power applications [18]–[21].

Fig. 2. Typical passive filter topology for high power applications. This structure is known as LCL filter with harmonic traps.

With this technique it is possible to directly eliminate a limited number of harmonics (being this limitation related to the used switching frequency) reducing the tuned filters needed to meet the grid codes. The main drawback of the SHEPWM technique is that the value of the non-zeroed harmonics can not be managed to get any optimization objective. The SHMPWM technique improves the SHEPWM results because it is able to reduce the filtering requirements generating output signals with a higher number of harmonics under the values specified in the grid codes using the same switching frequency. This fact makes the SHMPWM technique specially useful for high power applications. In addition, SHMPWM technique can be used in a larger range of  $M_a$  improving other previous techniques [22]-[24]. In this work, grid codes EN 50160 [25] and CIGRE WG 36-05 [26] have been considered in the computing process but any other grid code could be chosen. These grid codes detail specific limits up to harmonic order  $50^{th}$ . The THD is also limited by these specific grid codes to 8% but considering only the harmonics up to  $40^{th}$ . Table I summarizes the limits specified by the applied grid codes.

In order to compare SHEPWM and SHMPWM techniques, it is assumed that the control strategy of the converter avoids any possible resonance. The number of switching angles  $\alpha_i$  is equal to 7 per quarter of a 50Hz cycle which corresponds to a switching frequency of 350Hz using a three-level converter. With 7 switching angles the SHEPWM can fix the  $M_a$  and eliminate six non-desired harmonics, usually the non-triplen lower order harmonics, i.e.  $5^{th}$ ,  $7^{th}$ ,  $11^{th}$ ,  $13^{th}$ ,  $17^{th}$  and  $19^{th}$ . A  $M_a$  range from 0.60 to 1.16 in steps of 0.01 is applied considering both the SHEPWM and the SHMPWM techniques.

The flexibility of the SHMPWM can be used in the computing process in order to determine the switching angles  $\alpha_i$  which generate the most appropriate harmonic spectrum depending on the application. In this work two different strategies have been studied:

1) Strategy I (S1): A limited number of low order harmonics must meet the grid code without any filtering system. The number of these harmonics must be at least the same than using SHEPWM. The rest of harmonics specified in the grid code, which exceed the maximum limits, are reduced as much as possible independently whether they are low or high order harmonics. This idea can be translated to the OF using a particularized version of the expression (5). In this case, the penalty factor  $\lambda_p$  is equal to 1000. Besides, the  $L_i$  levels have been divided in two groups. For harmonics up to  $19^t h$ , the  $L_i$  values

| Odd non-triplen harmonics |                 | Odd triple | n harmonics               | Even Harmonics |                 |  |

|---------------------------|-----------------|------------|---------------------------|----------------|-----------------|--|

| Harmonic                  | Relative        | Harmonic   | Relative                  | Harmonic       | Relative        |  |

| order (n)                 | Voltage $(L_i)$ | order (n)  | order (n) Voltage $(L_i)$ |                | Voltage $(L_i)$ |  |

| 5                         | 6%              | 3          | 5%                        | 2              | 2%              |  |

| 7                         | 5%              | 9          | 1.5%                      | 4              | 1%              |  |

| 11                        | 3.5%            | 15         | 0.5%                      | 610            | 0.5%            |  |

| 13                        | 3%              | 21         | 0.5%                      | >10            | 0.2%            |  |

| 17                        | 2%              | >21        | 0.2%                      |                |                 |  |

| 19                        | 1.5%            |            |                           |                |                 |  |

| 23                        | 1.5%            |            |                           |                |                 |  |

| 25                        | 1.5%            |            |                           |                |                 |  |

| >25                       | 0.2+32.5/n      |            |                           |                |                 |  |

TABLE I

GRID CODE EN 50160 REQUIREMENTS + QUALITY GRID CODE CIGRE WG 36-05

are the limits specified by the grid code as in [5]. For higher harmonics up to  $49^{th}$ , the maximum harmonic distortion obtained using the SHEPWM technique in the whole range of  $M_a$  has been used as the  $L_i$  values. In this case  $\rho$ =0.9.

2) Strategy II (S2): A limited number of low order harmonics must meet the grid code without any filtering system. The number of these harmonics must be at least the same than using SHEPWM as in S1. For the rest of harmonics considered in the grid code, S2 is focused on reducing as much as possible the harmonic content from order  $23^{rd}$  to  $29^{th}$ . In addition, S2 is designed to keep, if possible, the higher order harmonics up to 49<sup>th</sup> below the maximum values obtained using the SHEPWM modulation technique. In this case, the particularized version of expression (5) is defined using a penalty factor  $\lambda_p$  equal to 5000 for all the harmonics up to  $29^{th}$  and equal to 1000 for higher harmonics. The  $L_i$  levels those defined for strategy S1 except for the harmonics  $23^{rd}$ ,  $25^{th}$  and  $29^{th}$  where a constant value equal to 15% has been used. Again has been chosen  $\rho = 0.9.$

S1 represents the most immediate way to apply SHMPWM with a reduced number of switching angles. On the other hand, S2 is focused on reducing the grid connection filter taking into account that the reactive elements to filter low order harmonics are specially bulky and expensive. S2 pays special attention on lower order harmonics at the expense of relaxing the allowed distortion of the high order harmonics.

It must be noticed that both S1 and S2 strategies are obtained defining the  $c_i$  cost functions mentioned in section II in a suitable way. The working conditions are completely different compared with [5] and an heuristic search is needed to translate the descriptions of the strategies presented above to the group of  $c_i$  functions. This search is an important novelty presented in this paper.

# V. SIMULATION RESULTS

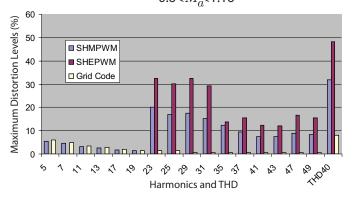

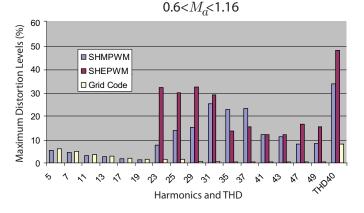

SHEPWM technique and SHMPWM technique applying S1 and S2 have been tested firstly by simulations. A three-level converter has been considered to compare the techniques. Fig.

3 and Fig. 4 show a comparison between the obtained simulation results using the SHEPWM and SHMPWM techniques considering the strategies S1 and S2 respectively. In both figures are represented the worst THD and the worst value

Strategy S1 0.6<*M*<sub>a</sub><1.16

Fig. 3. Simulation results comparing SHEPWM and SHMPWM techniques considering the strategy S1 with switching frequency equal to 350Hz. Worst case in the interval  $0.6 < M_a < 1.16$ .

Strategy S2

Fig. 4. Simulation results comparing SHEPWM and SHMPWM techniques considering the strategy S2 with switching frequency equal to 350Hz. Worst case in the interval  $0.6 < M_a < 1.16$ .

of distortion of each harmonic obtained for a specific range of the modulation index  $M_a$  (from 0.60 to 1.16). In Fig. 3, it is clear that using the SHMPWM technique with strategy S1, the maximum distortion levels for the non-eliminated harmonics are under the maximum values obtained using the SHEPWM technique. This fact is especially relevant for harmonics  $23^{rd}$  to  $31^{st}$  where the results obtained using the SHEPWM technique nearly double those obtained using the SHEPWM technique nearly double those obtained using the SHMPWM method.

Fig. 4 shows a comparison between the simulation results obtained using the SHEPWM technique and SHMPWM method with strategy S2. In this case, the maximum distortion levels in the range  $23^{rd}$  to  $29^{th}$  have been reduced as much as possible compared with the SHEPWM results and with SHMPWM using S1. This is very interesting because the filtering elements needed in the tuned filters are more bulky, heavy and expensive in low order harmonics. This advantage is achieved at the expense of the fact that harmonics  $35^{th}$ and  $37^{th}$  are higher than the maximum values obtained using SHEPWM. S2 could be a very interesting strategy in those cases where is better to reduce the maximum power supported by the reactive elements of low order harmonics than in high order harmonics because the cost, weight and size grow more than linearly. These results demonstrate that the flexibility of the SHMPWM method can be very useful and lets the designer to choose the most appropriate filtering shape according to each application. In S2, the main goal is to reduce as much as possible harmonics  $23^{rd}$  to  $29^{th}$  but any other strategy could be chosen.

Using SHMPWM technique with S1 or S2, it can be noticed that the very low order harmonics (up to harmonic  $19^{th}$ ) the distortion levels are under the limits specified by the grid codes. Using SHEPWM and SHMPWM techniques it is not necessary any tuned filter in the low order harmonics. In the higher order harmonics, if S1 is applied, the obtained distortion is much higher using SHEPWM method than using the SHMPWM technique. This means that the tuned filters have to support higher powers which deal with more bulky and expensive filtering elements. On the other hand, if S2 is applied, the most important advantage of SHMPWM compared with SHEPWM is focused on the reduction of the tuned filters dedicated to the lower order harmonics. It must be noticed that this is a very important advantage because the cost in both, inductors and capacitors, grow more than linearly when the maximum current (or voltage) is increased keeping the inductance or reactance value.

# VI. EXPERIMENTAL RESULTS

All the results presented in the previous sections have been experimentally tested using the 150kVA IGBT-based back-toback three-level three-phase diode-clamped converter shown in Fig. 5. This prototype is a scale down model of high power converters and both the modulation techniques and experimental results obtained with it can be extended to any three-level higher power converter. The chosen semiconductors are the IGBT modules SKM 300 GB 123 D of 300A and 1200V from Semikron. A hardware platform based on a TMS320VC33 DSP is used to control the rectifier and the inverter sides of the converter. The rectifier side is controlled to establish a DC-link voltage equal to 800V. The inverter side is used to feed a passive RL load with R=120 $\Omega$  and L=15mH. Both SHMPWM and SHEPWM techniques have been applied to the inverter in order to compare their performances. In the computing process real power semiconductors have been considered to keep a safety margin of  $32\mu s$  between two consecutives switching angles as in [22].

The SHMPWM technique in a closed loop control scheme was presented in [27] where the switching frequency was equal to 750Hz. However, in this case, the reference waveforms to be generated by the inverter side are determined in open loop corresponding to a 50Hz purely sinusoidal signal. In addition, in this paper, the same grid codes are applied but only seven

Fig. 5. 150 kVA IGBT-based back-to-back three-level diode-clamped inverter. The DC-Link voltage is 800V.

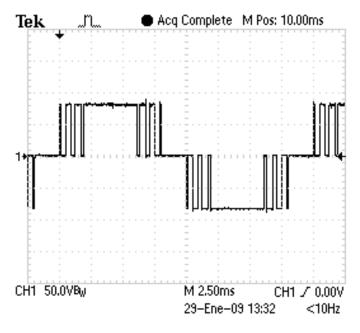

Fig. 6. Experimental phase to middle point voltage using 7 switching angles for a three-level converter obtained using a 1:5 voltage ratio oscilloscope probe.

| TABLE II                                                                                                      |

|---------------------------------------------------------------------------------------------------------------|

| Simulation and experimental results using SHEPWM and SHMPWM techniques considering strategies $\$1$ and $\$2$ |

| Harmonic          | Maximum SHEPWM(%) |             | SHMPWM-S1(%) |             | SHMPWM-S2(%) |             |             |

|-------------------|-------------------|-------------|--------------|-------------|--------------|-------------|-------------|

| order (n)         | Limit $(L_i)$     | simulations | experiments  | simulations | experiments  | simulations | experiments |

| 5                 | 6                 | 0.00        | 0.26         | 5.40        | 5.54         | 5.40        | 5.50        |

| 7                 | 5                 | 0.00        | 0.26         | 4.50        | 4.48         | 4.50        | 4.47        |

| 11                | 3.5               | 0.00        | 0.22         | 3.15        | 3.21         | 3.15        | 3.19        |

| 13                | 3                 | 0.00        | 0.18         | 2.70        | 2.74         | 2.68        | 2.73        |

| 17                | 2                 | 0.00        | 0.20         | 1.80        | 1.93         | 1.80        | 1.82        |

| 19                | 1.5               | 0.00        | 0.33         | 1.35        | 1.45         | 1.35        | 1.37        |

| 23                | 1.5               | 34.52       | 32.03        | 20.16       | 20.48        | 7.60        | 7.75        |

| 25                | 1.5               | 30.08       | 28.07        | 16.80       | 16.71        | 13.93       | 12.02       |

| 29                | 1.32              | 32.49       | 33.05        | 17.64       | 17.93        | 15.20       | 15.06       |

| 31                | 1.25              | 29.30       | 27.02        | 15.12       | 15.05        | 25.32       | 25.14       |

| 35                | 1.13              | 13.76       | 13.09        | 12.45       | 12.57        | 22.82       | 22.40       |

| 37                | 1.08              | 15.45       | 15.15        | 9.45        | 9.95         | 23.26       | 22.85       |

| 41                | 0.99              | 12.22       | 12.09        | 7.56        | 7.68         | 12.06       | 12.21       |

| 43                | 0.96              | 12.12       | 12.07        | 7.56        | 7.32         | 11.14       | 10.97       |

| 47                | 0.89              | 16.72       | 17.02        | 8.82        | 8.88         | 8.18        | 8.02        |

| 49                | 0.86              | 15.77       | 15.23        | 8.32        | 8.03         | 8.24        | 7.84        |

| THD <sub>40</sub> | 8                 | 48.21       | 49.84        | 32.31       | 34.03        | 34.87       | 34.12       |

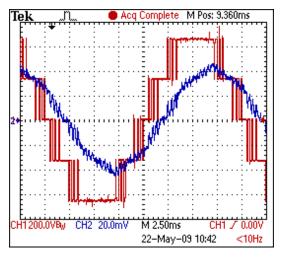

switching angles are considered leading to a low switching frequency equal to 350Hz as can be observed in Fig. 6. Fig. 7 shows the current of one phase in the load and the line voltage for  $M_a$ =1.20 using the SHMPWM technique with strategy S2. An oscilloscope voltage probe with an attenuation ratio of 1:5 and a 10mV/A current probe were used to obtain both captures. The SHMPWM technique allows to obtain solutions with good performance with  $M_a$  up to 1.20. However, a modulation index range from 0.6 to 1.16 is chosen in order to make a fair comparison with the well-known SHEPWM technique.

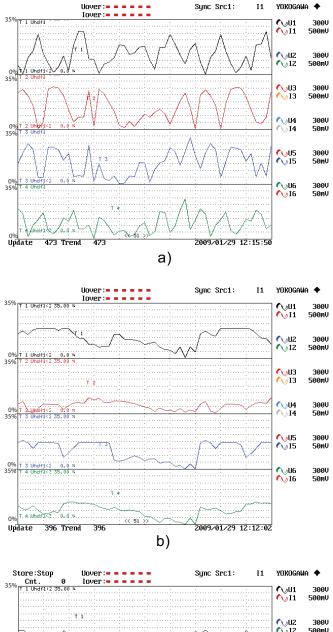

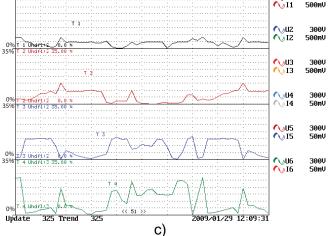

In Fig. 8, the trends of the magnitudes of the harmonics  $(23^{rd}, 25^{th}, 29^{th}, and 31^{st})$  using the different techniques studied in this paper have been represented. Fig. 8a, Fig. 8b and Fig. 8c correspond to the results obtained using the

Fig. 7. Experimental current and line voltage for  $M_a$ =1.20 obtained using a 1:5 voltage ratio oscilloscope probe and 10mV/A for the current probe

SHEPWM technique, using the SHMPWM with strategy S1 and using the SHMPWM with strategy S2 respectively. In all the cases, the vertical scale has been adjusted from 0% to 35% of the fundamental harmonic amplitude. The horizontal scale is the simulation time. In the experiment, the modulation index  $M_a$  is changing continuously from 0.60 to 1.16 using steps equal to 0.01. Each specific modulation index value is applied during 1 second and the experimental results have been taken during 1 minute in order to show the results for all the modulation index range.

All the experimental results are summarized in Table II for experiments E1 and E2. From left to right are shown the harmonic order, the maximum levels specified by the grid codes and the results obtained with SHEPWM and SHMPWM techniques. The shown results correspond with the maximum harmonic distortion obtained in the whole range of  $M_a$ . All the harmonic distortion values are specified as a percentage respect to the fundamental harmonic value. From top to bottom are studied all the harmonics of interest (odd non-triplen) and in the final row is detailed the THD obtained considering up to harmonic  $40^{th}$ .

The results from Table II show the advantages obtained using the SHMPWM technique in comparison with SHEPWM due to the flexibility of the method. As can be observed from Table II, the simulation results are in accordance with the obtained experimental results. From the experimental results, for harmonics up to  $19^{th}$ , using SHEPWM and SHMPWM it is not necessary any filtering system because the maximum output values are always under the limit specified in the grid codes. For the rest of harmonics considered by the grid code, from  $23^{rd}$  to  $49^{th}$ , the results obtained using the SHMPWM technique depend on the selected strategy during the computation process (S1 or S2).

Considering E1, the maximum values obtained using SHM-PWM are always below the maximum values obtained using

Fig. 8. Experimental values in the whole  $M_a$  range obtained using: a) SHEPWM, b) SHMPWM-S1 and c) SHMPWM-S2. From top to bottom, harmonics  $23^{rd}$ ,  $25^{th}$ ,  $29^{th}$  and  $31^{st}$ . The scales have been adjusted from 0 to 35% of the fundamental harmonic amplitude.

SHEPWM in the whole  $M_a$  range. This result represent a great advantage of SHMPWM respect to the SHEPWM because the grid connection filter requirements will be clearly reduced. For instance, harmonic distortions from  $23^{rd}$  to  $31^{st}$  are improved reducing the maximum level nearly to the half value.

Considering E2, for harmonics from  $23^{rd}$  to  $49^{th}$ , from data of Table II it can be noticed that harmonics  $23^{rd}$  to  $29^{th}$  are greatly reduced compared with those obtained using SHEPWM. This was the primary objective of strategy S2 to determine the switching angles to be applied to the SHMPWM technique. In fact, the distortion of harmonics from  $23^{rd}$  to  $29^{th}$  using S2 is also lower than that achieved by strategy S1. This improvement is achieved at the expense of the fact that harmonics  $35^{th}$  and  $37^{th}$  have distortion above the level obtained using the SHEPWM technique. S2 was defined in this way because the filtering elements needed to meet the grid codes are bigger and more expensive whilst the harmonics considered have lower orders.

#### VII. CONCLUSIONS

In this paper, a comparison between the SHEPWM and SHMPWM for very low switching frequency (350Hz) for a three-level converter is presented. In high power applications, the thermal losses limit the maximum switching frequency to a few hundreds of Hertz ( $f_s <$ 500Hz). In this context, it is necessary to eliminate the undesired harmonics using filtering systems. The SHEPWM has been traditionally used in high power applications because it is able to generate output waveforms with a limited number of eliminated harmonics. In this paper it is demonstrated that using very low switching frequency, the SHMPWM technique is able to generate output signals with better harmonic performance compared to the SHEPWM technique in a wide range of the modulation index.

In the paper, the flexibility of the SHMPWM technique has been exploited considering different criteria to determine the switching angles to be applied to the three-level converter. One of the strategies (S1) was defined to improve the results of the SHEPWM for all the harmonics that are not zeroed. A second strategy (S2), has been also introduced in order to reduce as much as possible the filter requirements for low order harmonics above the maximum limit imposed by the grid code.

The simulation and experimental results show that the maximum output values of the harmonics using the SHMPWM technique up to  $19^{th}$  are below the limits imposed by the applied grid codes. These harmonics are eliminated using SHEPWM. Therefore, these harmonics do not need to be filtered using both techniques. On the other hand, the non-eliminated harmonics obtained using SHEPWM have much higher values compared with those obtained using the SHM-PWM technique using S1. This fact leads to a reduction in the maximum power supported by the elements of the tuned filters to be used. The consequence is a significant reduction in cost, size and weight of the filtering system required to fulfil the grid codes. Finally, the results obtained for strategy S2 show that any filtering shape can be applied to determine the switching angles for the SHMPWM technique. S2 objective

was to achieve a great reduction of non-eliminated low order harmonics and this goal has been reached. Experimental results validating the proposed concepts are included.

# ACKNOWLEDGMENT

The authors gratefully acknowledge financial support provided by the Spanish Ministry of Science and Technology under project TEC2006-03863 and by the Andalusian Government Research Council under project EXC/2005/TIC-1172.

#### REFERENCES

- J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt and S. Kouro, "Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [2] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo and M. M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Magazine*, vol. 2, no. 2, pp. 28–39, June 2008.

- [3] D. Krug, S. Bernet, S. S. Fazel, K. Jalili and M. Malinowski, "Comparison of 2.3-kV Medium-Voltage Multilevel Converters for Industrial Medium-Voltage Drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2979–2992, Dec. 2007.

- [4] H. S. Patel and R. G. Hoft, "Generalized techniques of harmonic elimination and voltage control in thyristor inverters-Part 1: Harmonic elimination," *IEEE Trans. Ind. Applicat.*, vol. IA–9, pp. 310–317, May/June 1973.

- [5] L. G. Franquelo, J. Napoles, R. Portillo, J. I. Leon and M. A. Aguirre, "A Flexible Selective Harmonic Mitigation Technique to Meet Grid Codes in Three-Level PWM Converters," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 3022–3029, Dec. 2007.

- [6] S. Kirkpatrick, C. D. Gelatt Jr. and M. P. Vecchi, "Optimization by Simulated Annealing," *Science*, vol. 220, no. 4598, pp. 671–680, 1983.

- [7] Kay-Soon Low and Tze-Shyan Wong, "A Multiobjective Genetic Algorithm for Optimizing the Performance of Hard Disk Drive Motion Control System," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1716– 1725, June 2007.

- [8] K. Sundareswaran, K. Jayant and T. N. Shanavas, "Inverter Harmonic Elimination Through a Colony of Continuously Exploring Ants," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2558–2565, Oct. 2007.

- [9] M. Huang, F. Romeo, and A. Sangiovanni-Vincentelli, "An efficient general cooling schedule for simulated annealing," in *IEEE International Conference on Computer-Aided Design*, pp. 381–384, 1986.

- [10] K.L. Shi and Hui Li, "Optimized PWM strategy based on genetic algorithms," *IEEE Trans. Ind. Electron.*, vol. 52, no. 5, pp. 1458–1461, Oct. 2005.

- [11] H. Akagi, "Active harmonic filters," in *IEEE Proceedings of the IEEE*, vol. 93, no. 12, pp. 2128–2141, Dec. 2005.

- [12] L. Asiminoaei, E. Aeloiza, P.N. Enjeti and F. Blaabjerg, "Shunt Active-Power-Filter Topology Based on Parallel Interleaved Inverters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1175–1189, Mar. 2008.

- [13] Shu Zeliang, Guo Yuhua and Lian Jisan, "Steady-State and Dynamic Study of Active Power Filter With Efficient FPGA-Based Control Algorithm," *IEEE Trans. Ind. Electron.*, vol. 55, no. 6, pp. 1527–1536, Apr. 2008.

- [14] J. K. Steinke, "Use of an LC Filter to Achieve a Motor-friendly Performance of the PWM Voltage Source Inverter," *IEEE Trans. Energy Conversion*, vol. 14, no. 3, pp. 3022–3029, Sep. 1999.

- [15] M. Prodanovic and T. C. Green, "Control and filter design of three-phase inverters for high power quality grid connection," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 373–380, Jan. 2003.

- [16] J.R. Rodriguez, J. Pontt, R. Huerta, G. Alzamora, N. Becker, S. Kouro, P. Cortes and P. Lezana, "Resonances in a high-power active-front-end rectifier system," *IEEE Trans. Ind. Electron.*, vol. 52, no. 2, pp. 482–488, Apr. 2005.

- [17] E. Twining and D. G. Holmes, "Grid Current Regulation of a Three-Phase Voltage Source Inverter With an LCL Input Filter," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 888–895, May 2003.

- [18] V. G. Agelidis, A. I. Balouktsis and C. Cossar, "On Attaining the Multiple Solutions of Selective Harmonic Elimination PWM Three-Level Waveforms Through Function Minimization," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 996–1004, Mar. 2008.

- [19] A. J. Watson, P. W. Wheeler and J. C. Clare, "A Complete Harmonic Elimination Approach to DC Link Voltage Balancing for a Cascaded Multilevel Rectifier," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2946–2953, Dec. 2007.

- [20] Zhong Du, L. M. Tolbert, J. N. Chiasson and B. Ozpineci "Reduced Switching-Frequency Active Harmonic Elimination for Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 55, no. 4, pp. 1761–1770, April 2008.

- [21] M. Dahidah and V. G. Agelidis, "Generalized Formulation of Multilevel Selective Harmonic Elimination PWM: Case I - Non-Equal DC Sources," in 37<sup>th</sup> IEEE Power Electronincs Specialists Conference, Jeju (Korea), Jun. 2006, pp. 1472–1477.

- [22] S. Sirisukprasert, Jih-Sheng Lai and Tian-Hua Liu, "Optimum harmonic reduction with a wide range of modulation indexes for multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 875–881, Aug. 2002.

- [23] D. R. Alexander and S. M. Williams, "An optimal PWM algorithm implementation in high performance 125 kVA inverter," in *Eighth Annual Applied Power Electronics Conference and Exposition 1993* (APEC'93), 7–11 Mar. 1993, pp. 771–777.

- [24] J. Pontt, J. Rodriguez and R. Huerta, "Mitigation of noneliminated harmonics of SHEPWM three-level multipulse three-phase active front end converters with low switching frequency for meeting standard IEEE-519-92," *IEEE Trans. Power Electron.*, vol. 19, no. 6, pp. 1594–1600, Nov. 2004.

- [25] CENELEC EN 50160, "Voltage characteristics of electricity supplied by public distribution systems," 2001.

- [26] CIGRE WG 36-05, "Harmonics, characteristic parameters, methods of study, estimates of existing values in the network," Electra no.77, 1981, S.35-54.

- [27] J. Nápoles, R. Portillo, J. I. Leon, M. A. Aguirre and L. G. Franquelo, "Implementation of a closed loop SHMPWM Technique for Three Level Converters," in the 34<sup>th</sup> IEEE Annual Conference of the Industrial Electronics Society (IECON'08), pp. 3260–3265, 10–13 Nov. 2008, Orlando (USA).

**Javier Napoles** was born in Seville in 1978. He obtained the Telecommunications Engineer degree from the University of Seville, Spain, in 2005. He is currently pursuing the PhD degree in electrical engineering at the Power Electronics Group, University of Seville. In 2005, he joined to the Department of Electronic Engineering, Seville University, working on R+D projects. His interests include the development of techniques and algorithms to improve the energy quality from utility grid specially focused to harmonic content implemented on FPGA.

Jose I. Leon (S'04, M'07) was born in Cádiz, Spain, in 1976. He received the B.S. and M.S. and PhD degrees in telecommunications engineering from the University of Seville (US), Spain, in 1999, 2001 and 2006 respectively. In 2002, he joined the Power Electronics Group, US, working in R&D projects. Currently, he is an Associate Professor with the Department of Electronic Engineering, US. His research interests include electronic power systems, modeling, modulation and control of power converters and industrial drives.

**Ramon Portillo** (S'06) was born in Seville, Spain, in 1974. He received the Industrial Engineer degree from the University of Seville (US), Seville, Spain, in 2002. He is currently working toward the Ph.D. degree in electrical engineering in the Power Electronics Group, US. In 2001, he joined the Power Electronics Group, US, working in R+D projects. Since 2002, he has been an Associate Professor with the Department of Electronic Engineering, US. His research interests include electronic power systems applied to energy conditioning and generation,

power quality in renewable generation plants, applications of fuzzy systems in industry and wind farms, and modeling and control of power-electronic converters and industrial drives.

Leopoldo G. Franquelo (M'84, SM'96, F'05) was born in Málaga, Spain. He received the M.Sc. and Ph.D. degrees in electrical engineering from the University de Seville (US), Seville, Spain in 1977 and 1980 respectively. His current research interest lies on modulation techniques for multilevel inverters and its application to power electronic systems for renewable energy systems. He was the Vice-President of the Industrial Electronics Society (IES) Spanish Chapter (2002 - 2003), member at Large of the IES AdCom (2002 - 2003). He was the Vice-

President for Conferences of the IES (2004 - 2007), in which he has also been a Distinguished Lecturer since 2006. He has been an Associated Editor for the IEEE Transactions on Industrial Electronics since 2007. Since January 2008 he is President Elect of IEEE Industrial Electronics Society.

**Miguel A. Aguirre** (M'97) was born in Madrid, Spain in 1963. He obtained the Master degree in 1991, in Electrical and Electronic Engineering by the University of Sevilla, Spain. He obtained the PhD degree in 1994 in the same University. He is currently teaching digital microelectronics in the Electronic Engineering Department of the University of Sevilla, as Assistant Professor. He is the author of more than 10 publications in the IEEE. He made his thesis in algorithm and heuristics for placement and routing integrated, and currently he is working

in tools for dependable design of integrated circuits.