Blumenschein, N. A., Moser, N. A., Heller, E. R., Miller, N. C., Green, A. J., Popp, A., Crespo, A., Leedy, K., Lindquist, M., Moule, T., Dalcanale, S., Mercado, E., Singh, M., Pomeroy, J. W., Kuball, M., Wagner, G., Paskova, T., Muth, J. F., Chabak, K. D., & Jessen, G. H. (2019). Self-Heating Characterization of β-Ga2O3 Thin-Channel MOSFETs by Pulsed I-V and Raman Nanothermography. *IEEE Transactions on Electron Devices*, *67*(1), 204-211. https://doi.org/10.1109/TED.2019.2951502

Peer reviewed version

Link to published version (if available): 10.1109/TED.2019.2951502

Link to publication record in Explore Bristol Research PDF-document

This is the author accepted manuscript (AAM). The final published version (version of record) is available online via IEEE at dx.doi.org/10.1109/TED.2019.2951502. Please refer to any applicable terms of use of the publisher.

# University of Bristol - Explore Bristol Research General rights

This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/red/research-policy/pure/user-guides/ebr-terms/

# Self-Heating Characterization of β-Ga<sub>2</sub>O<sub>3</sub> Thin-Channel MOSFETs by Pulsed I-V and Raman Nanothermography

Nicholas A. Blumenschein, Neil A. Moser, Eric R. Heller, Nicholas Miller, Andrew J. Green, Andreas Popp, Antonio Crespo, Kevin Leedy, Miles Lindquist, Taylor Moule, Elisha Mercado, Manikant Singh, James W. Pomeroy, Martin Kuball, Gunter Wagner, Tania Paskova, John F. Muth, Kelson D. Chabak, and Gregg H. Jessen

field-effect transistors (MOSFETs) were evaluated using both DC and pulsed I-V measurements. The reported pulsed I-V technique was used to study self-heating effects in the MOSFET channel. The device was analyzed over a large temperature range of 23 to 200°C. A relationship between dissipated power and channel temperature was established, and it was found that the MOSFET channel was heating up to 208°C when dissipating 2.5 W/mm of power. The thermal resistance of the channel was found to be 73°C-mm/W. The results are supported with experimental Raman nano-thermography and thermal simulations and are in excellent agreement with pulsed I-V findings. The high thermal resistance underpins the importance of optimizing thermal management in future Ga<sub>2</sub>O<sub>3</sub> devices.

*Index Terms*—Channel temperature, gallium oxide, MOSFET, pulsed I-V measurements

#### I. INTRODUCTION

**R**ESEARCH efforts on the gallium oxide beta ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) polymorph are continuously growing because of its thermal and chemical stability, optical transparency, and bulk production capabilities using melt growth methods [1].  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has a lot of promise for high-power device applications because of its wide bandgap (E<sub>g</sub>) of ~ 4.9 eV and estimated critical electric field (E<sub>C</sub>) of 8 MV/cm, resulting in a Baliga's Figure-of-Merit (BFOM) of 3444 [2]. Following the first Ga<sub>2</sub>O<sub>3</sub> transistor demonstrations [3], a report by Green *et al.*

<sup>s</sup>Submitted for review on 2/26/2019. This work was funded in part by the National Science Foundation under Grant No. DMR-1506159 and in part by The U.S. Department of Defense. (*Corresponding author: Nicholas A. Blumenschein*).

N. A. Blumenschein, T. Paskova, and J. F. Muth are with the Department of Electrical and Computer Engineering, North Carolina State University, Raleigh, NC 27695 USA. (e-mail: nablumen@ncsu.edu).

N. A. Moser, E. R. Heller, N. Miller, A. J. Green, A. Crespo, K. Leedy, M. Lindquist, K. D. Chabak, and G. H. Jessen are with the Sensors Directorate, Air Force Research Laboratory, Wright-Patterson AFB, OH 45433 USA.

A. Popp and G. Wagner are with the Leibniz-Institut f

ür Kristallz

üchtung, Berlin, Germany.

T. Moule, E. Mercado, M. Singh, J. W. Pomeroy, and M. Kuball are with the Centre for Doctoral Training in Condensed Matter Physics, University of Bristol, Bristol, United Kingdom. validated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as a high-power semiconductor material by fabricating a MOSFET with a breakdown electric field exceeding 3.8 MV/cm, which was the first demonstration of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> having a higher breakdown field than both GaN (3 MV/cm) and SiC (3.18 MV/cm) [4]. These excellent material properties have allowed for the development of a wide variety of semiconductor devices such as high-voltage Schottky barrier diodes (SBDs) [5]–[7] and transistors with high current density [8]-[11], high breakdown voltage [3], [4], [12]–[15], radio frequency operation [11], [16], and vertical topology [17], [18]. Recently, work by Lv *et al.* demonstrated a sourcefield-plated Ga<sub>2</sub>O<sub>3</sub> MOSFET with a record-setting power figure-of-merit (V<sub>br</sub><sup>2</sup>/R<sub>on,sp</sub>) of 50.4 MW/cm<sup>2</sup> [19].

One concern with  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is its low anisotropic thermal conductivity [20], [21], posing additional challenges in designing high-power Ga<sub>2</sub>O<sub>3</sub> devices with capability to extract enough heat to prevent thermal-related failures such as oxide breakdown. It has been proposed that effective heat extraction in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> will likely require a combination of top-side and back-side thermal solutions [2], [22], [23]. To evaluate these methods of heat removal, it is imperative to quantify the channel temperature of Ga<sub>2</sub>O<sub>3</sub> devices during operation independent of the thermal solution. Previous reports have shown success measuring channel temperature using methods such as Raman thermography [22], thermo-reflectance imaging [24], and electrical measurements [25]. Pulsed I-V characterization of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs has been reported at higher power operation by suppressing trapping and thermal effects [9]. Joh et al. reported on a simple pulsed I-V method that showed the ability to accurately measure the channel temperature of GaN high-electron mobility transistors (HEMTs) [26]. This method is beneficial because it does not require any special device layout or geometry, it can be used to measure packaged devices, and provides the channel temperature rather than a spatially averaged temperature. In this work, we apply the pulsed I-V measurement technique to Ga<sub>2</sub>O<sub>3</sub> MOSFETs and prove its capability as a universal method to estimate the channel temperature. Raman nanothermography was used to validate these results. This is the first report of Ga<sub>2</sub>O<sub>3</sub> MOSFET channel temperature measurement that was verified using two separate

experimental methods.

# II. EXPERIMENTAL DETAILS

#### A. Device Details

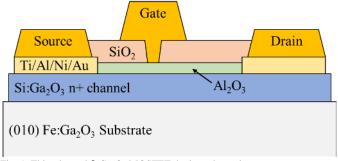

Metal-organic chemical vapor phase epitaxy (MOVPE) was used for homoepitaxial growth of a Si-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film channel on a (010) Fe-doped Ga<sub>2</sub>O<sub>3</sub> substrate. The channel thickness and donor concentration was 65 nm and  $2 \times 10^{18}$  cm<sup>-3</sup>, respectively. Ohmic contacts were formed by depositing a Ti/Al/Ni/Au (20/100/50/50 nm) metal stack, followed by rapid thermal annealing (RTA) for one minute at 470 °C in a N<sub>2</sub> atmosphere. The ohmic contact resistance was estimated to be ~ 11  $\Omega$  mm using TLM test structures. From Hall measurements, the sheet concentration and mobility of the film were found to be  $1.33 \times 10^{13}$  cm<sup>-2</sup> and 90 cm<sup>2</sup>/V-s, respectively. A 20 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric was deposited by atomic layer deposition (ALD). A 90 nm SiO<sub>2</sub> layer was deposited using plasma-enhanced chemical vapor deposition (PECVD) to serve as a field oxide layer in the ungated access regions. A 0.14  $\mu$ m gate length (L<sub>G</sub>) was formed in the SiO<sub>2</sub> layer by etching a trench with CF<sub>4</sub> reactive ion etching (RIE) with the ALD Al<sub>2</sub>O<sub>3</sub> serving as an etch stop. A 0.7 µm wide Ni/Au metal stripe was evaporated over the trench to form a T-shaped gate electrode. The Au pad layer was electroplated to a thickness of  $\sim 5 \,\mu m$  to serve as a heat sink. Fig. 1 shows an illustration of the depletion-mode MOSFET structure with source-to-drain ( $L_{SD}$ ) and gate-source ( $L_{GS}$ ) length of 8  $\mu$ m and  $\sim 0.5 \ \mu m$ , respectively.

Fig. 1. Thin-channel β-Ga<sub>2</sub>O<sub>3</sub> MOSFET device schematic.

### B. Pulsed I-V Measurement Technique

Pulsed I-V measurements were performed at temperatures ranging from 23°C to 200°C using a DiVA D265 dynamic IV analyzer equipped with a gold-plated thermal baseplate. Simultaneous control of gate/drain voltage switching times were possible for sub-µs pulsewidths. This capability allowed the use of previously reported pulsed IV method that showed the feasibility in gathering transistor channel temperature information through pulsed IV measurements [26]. The technique involves a calibration step and measurement step. The goal of the calibration step is to gather temperaturedependent IV data without self-heating effects. To ensure that this was the case, we pulsed from zero quiescent gate/drain voltage conditions (V<sub>GSQ</sub>, V<sub>DSQ</sub> = 0V) and minimized the time in which the non-quiescent voltages (V<sub>GS</sub>, V<sub>DS</sub>) were active using a 200 nanosecond pulse width and 0.02% duty cycle. Previous experiments on GaN HEMTs showed that these pulsewidth and duty cycle conditions resulted in channel temperature measurements where an error of approximately  $6^{\circ}$ C was observed [26]. This error was reduced to ~  $0.5^{\circ}$ C when shortening the pulsewidth to 100 ns. Unfortunately, we were unable to use a shorter pulsewidth because of equipment limitations. However, we observed no self-heating effects when using a 200 ns pulsewidth, indicated by the complete linearity of the pulsed I<sub>D</sub>-V<sub>DS</sub> curves up to a 15 V bias. By complying with these measurement conditions, we could assume that power dissipation did not affect the device temperature; thus, the temperature of the transistor channel was the same as that of the baseplate ( $T_{CH} = T_{Baseplate}$ ). The IV characteristic was measured by applying a  $V_{GS} = 0$  V and sweeping the drain voltage from 0 to 15 V. The on-resistance  $(R_{ON})$  was determined at each temperature from the  $I_D$ - $V_{DS}$ curve slope. Another key parameter used in this work was the maximum drain current (I<sub>D,max</sub>), which we have chosen to define as  $I_D$  at  $V_{DS}$  = 15 V. Once these calibration measurements were complete, a temperature-dependent relationship was identified for both R<sub>ON</sub> and I<sub>D,max</sub>. The second part of the measurement technique required the use of nonzero quiescent drain bias conditions to induce self-heating in the channel while keeping T<sub>Baseplate</sub> at a constant 23°C. Here,  $V_{DSQ}$  and  $V_{DS}$  were both varied from 0 to 15 V. Since  $T_{CH}$  was unknown, the dissipated power ( $P_D = V_{DSQ} \times I_{DQ}$ ) was calculated for each V<sub>DSQ</sub> and used to create a relationship similar to that in the calibration step (P<sub>D</sub> vs. R<sub>ON</sub>, I<sub>D,max</sub>). Thus, by using the  $T_{CH}$ -dependent data of the calibration step, the channel temperature was estimated using the P<sub>D</sub>-dependent data of the measurement step.

### C. Raman Thermography Measurement Technique

Peak temperature in the MOSFET channel was extracted using Raman nano-thermography. Titanium dioxide (TiO<sub>2</sub>) nanoparticles with a 30 nm diameter were used to measure the temperature at four distinct locations on the MOSFET surface above the channel. The nanoparticles were distributed onto the device using a suspension of 99.98% pure TiO<sub>2</sub> particles mixed in methanol. Sonication of this suspense ensured a uniform density of particles throughout the methanol. The particle-ethanol suspense was drop cast onto the channel. The low density and small size of the TiO<sub>2</sub> particles minimize their effect on channel temperature. During device operation, owing to their low heat capacity, TiO<sub>2</sub> particles reach thermal equilibrium with the device channel almost instantaneously. The Raman peak shift of the particles is used to extract channel temperature. The temperature calibration method used has been previously described elsewhere [27]–[30]. During these measurements the wafer was mounted to an electrically grounded baseplate at a temperature of 25°C. Self-heating effects were evaluated in the device using DC bias conditions  $(V_G = 0 V, V_{DS} = 2 - 8V \text{ in steps of } 2V)$ . Experiments were carried out using a 532 nm Ar+ laser and 0.5 NA objective lens with a  $0.64 \,\mu m$  spot size on the sample surface.

# III. RESULTS

#### A. Pulsed I-V Characterization

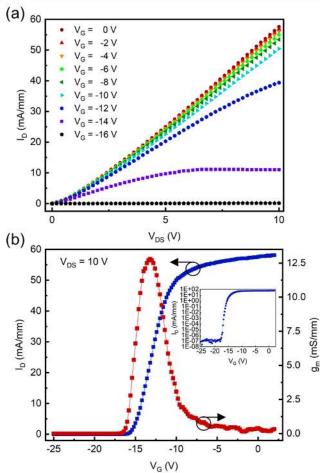

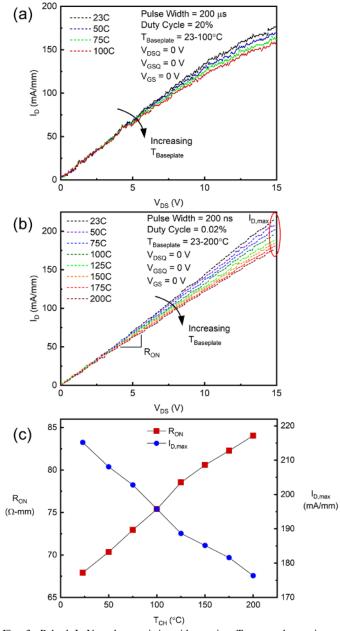

Fig. 2(a) shows the MOSFET DC I-V characteristic of a representative device when varying V<sub>DS</sub> from 0 to 10 V and V<sub>G</sub> from -16 to 0 V in 2 V increments. Fig. 2(b) shows the corresponding transfer characteristic while biasing the device at  $V_{DS} = 10$  V. The inset shows the  $I_D$  transfer characteristic plotted on a log scale. A peak gm of 12.8 mS/mm was observed at  $V_{GS}$  = - 13.2 V. A threshold voltage of -15.1 V was found through linear extrapolation of the I<sub>D</sub>-V<sub>G</sub> curve. Fig. 3(a) shows the  $I_D$ - $V_{DS}$  characteristic when using a bias pulsewidth of 200  $\mu$ s and varying T<sub>Baseplate</sub> from 23 to 100°C. Immediately observed was an expected temperature dependence where RON increased and ID,max decreased with  $T_{CH}$ . However, it can be seen that the slope of the curve does not remain linear up to  $V_{DS} = 15$  V, and instead begins to saturate as it should if a DC bias were applied. This is due to the large 200 µs pulsewidth and 20% duty cycle, where unwanted power dissipation is

3(b), a 200 ns pulsewidth (0.02% duty cycle) was chosen for I<sub>D</sub>-V<sub>DS</sub> characteristic measurements. The desired linear IV relationship for the entire temperature range was observed. The R<sub>ON</sub> had an RT value of 67.9  $\Omega$ -mm that increased to 84  $\Omega$ -mm at 200°C (24% increase) whereas I<sub>D,max</sub> had an RT value of 215.2 mA/mm that decreased to 176.4 mA/mm at 200°C (22% decrease). Figure 3(c) shows a plot of R<sub>ON</sub> and I<sub>D,max</sub> versus T<sub>CH</sub>.

Fig. 2. (a) DC  $I_D$ -V<sub>DS</sub> characteristic while varying V<sub>G</sub> from -16 to 0 Volts and (b) Transfer characteristic when applying a 10V V<sub>DS</sub>. Inset shows  $I_D$  plotted on

causing heat to build up in the channel. Reducing the pulsewidth into the sub- $\mu$ s range has the benefit of minimizing T<sub>CH</sub> self-heating, as has been previously demonstrated for AlGaN/GaN devices [31]. For these reasons, as shown in Fig.

a log scale.

Fig. 3. Pulsed  $I_D$ -V<sub>DS</sub> characteristic with varying  $T_{Baseplate}$  when using a pulsewidth of (a) 200  $\mu$ s and (b) 200 ns. (C)  $R_{ON}$ ,  $I_{D,max}$  parameters obtained from  $I_D$ -V<sub>DS</sub> characteristic and plotted versus  $T_{CH}$ .

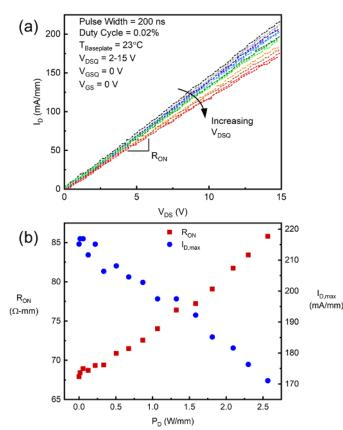

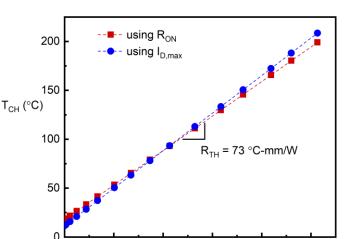

In the measurement step we used the same pulse conditions of 200 ns and 0.02% duty cycle, but also set the baseplate temperature to 23°C and used a non-zero  $V_{DSQ}$  to dissipate increasing amounts of power in the device. Fig. 4(a) shows the I<sub>D</sub>-V<sub>DS</sub> characteristic under these conditions for a V<sub>DSQ</sub> ranging from 2 to 15 V. The dissipated power was calculated for each V<sub>DSQ</sub> condition using P<sub>D</sub> = V<sub>DSQ</sub> × I<sub>DQ</sub> then plotted versus R<sub>ON</sub> and I<sub>D,max</sub> as shown in Fig. 4(b). Using the R<sub>ON</sub>-T<sub>CH</sub> and I<sub>D,max</sub>-T<sub>CH</sub> data from Fig. 3(c), along with the R<sub>ON</sub>-P<sub>D</sub> and I<sub>D,max</sub>-P<sub>D</sub> data from Fig. 4(b), we were able to extract a family of equations [(1) - (4)]. From (1) – (4) we then obtained (5) and (6), which relate P<sub>D</sub> and T<sub>CH</sub>. Interestingly, (5) and (6) were nearly identical even though they were obtained separately using R<sub>ON</sub> and I<sub>D,max</sub>. Fig. 5 shows the estimated T<sub>CH</sub> as a function of P<sub>D</sub> as obtained from (5) and (6). The thermal resistance (R<sub>TH</sub>) was extracted from the slope of the two T<sub>CH</sub>-P<sub>D</sub> curves using a least squares fit over the whole dataset, and estimated as the average value of 73 °C-mm/W.

Fig. 4. (a) Pulsed  $I_D$ -V<sub>DS</sub> characteristic when  $V_{DSQ}$  = 0-15 V and (b) resulting  $R_{ON}$ ,  $I_{D,max}$  versus  $P_D$  data.

$$R_{ON} = 0.09 \cdot T_{CH} + 65.96 \tag{1}$$

$$I_{D \max} = -0.22 \cdot T_{CH} + 218.86 \tag{2}$$

$$R_{ON} = 6.64 \cdot P_D + 67.63 \tag{3}$$

$$I_{D,\max} = -16.87 \cdot P_D + 216.33 \tag{4}$$

$$T_{CH} = 70.63 \cdot P_D + 17.73 \tag{5}$$

$$T_{CH} = 76.78 \cdot P_D + 11.52 \tag{6}$$

Fig. 5. Two independent estimations of  $T_{CH}$  that were found through  $R_{ON}$  and  $I_{D,max}$ . The resulting thermal resistance of 73°C-mm/W was found from the  $T_{CH}$ -P<sub>D</sub> slope.

1.0

1.5

P<sub>D</sub> (W/mm)

2.0

2.5

#### B. Raman Thermography

0.0

0.5

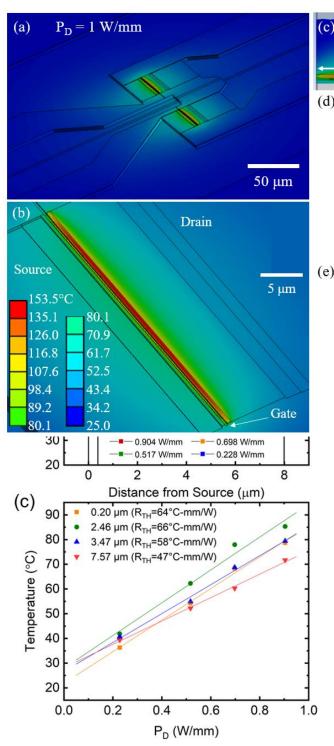

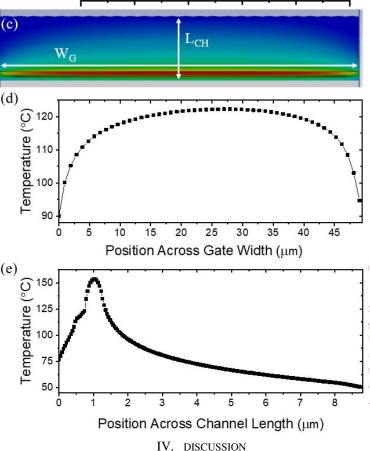

Fig. 6(a) shows the four locations of TiO<sub>2</sub> nanoparticles on the device surface during Raman thermography measurements. The Raman spectra of the TiO<sub>2</sub> particles was measured at each distinct location as a function of P<sub>D</sub>. Four varying amounts of P<sub>D</sub> were used (0.228, 0.517, 0.698, and 0.904 W/mm). Fig. 6(b) shows the resulting  $T_{CH}$  data as a function of TiO<sub>2</sub> nanoparticle location. The source, gate, and drain locations have also been denoted here using black arrows. The maximum T<sub>CH</sub> was observed on the drain-side of the gate at a distance of 2.46 µm from the edge of the source contact for every amount of P<sub>D</sub>. This is consistent with previous thermal characterization reports on Ga<sub>2</sub>O<sub>3</sub> MOSFETs [22]. The  $T_{CH}$  measured at distances of 0.20 and 3.47 µm were all relatively similar in comparison for every  $P_D$ .

The pulsed I-V technique described in this work results in an average  $T_{CH}$  (and  $R_{TH}$ ), whereas the Raman thermography measurement technique provides spatial information laterally across the channel. To better understand these two separate  $T_{CH}$ -P<sub>D</sub> datasets the spatial  $T_{CH}$  information in Fig. 6(b) was plotted as a function of P<sub>D</sub> as shown in Fig. 6(c). The R<sub>TH</sub> found at each TiO<sub>2</sub> nanoparticle location is shown on the figure, and varies from 47 – 66 °C-mm/W. Colored lines show the linear fits for each TiO<sub>2</sub> nanoparticle location and their slopes were used to estimate R<sub>TH</sub>.

Fig. 7 shows comparative  $T_{CH}$ -P<sub>D</sub> data measured using the two techniques. The pulsed I-V data shown is an average of the two datasets shown in Fig. 5, where an  $R_{TH}$  of 73 °C-mm/W is observed. An average  $T_{CH}$  was taken for each TiO<sub>2</sub> particle to study how the Raman nano-thermography technique might vary from the pulsed I-V method. Taking this average resulted in an  $R_{TH}$  of 59 °C-mm/W, which is 19.2% lower than the value found when using pulsed I-V. It is likely that these two  $R_{TH}$  values would converge if more TiO<sub>2</sub> nanoparticles were used in the Raman measurements in areas underneath the drain-edge of the gate where the majority of thermal effects are

Fig. 6. (a) Position of TiO<sub>2</sub> particles on device surface indicated by red X, (b)  $T_{CH}$  data found by Raman thermography measurements using four different amounts of dissipated power at each distinct TiO<sub>2</sub> particle position, and (c)  $T_{CH}$ -P<sub>D</sub> data at each TiO<sub>2</sub> location. Colored lines show linear approximations used to find R<sub>TH</sub> for each TiO<sub>2</sub> location on the device surface.

observed. This point is further proven when looking at the thermal simulations in Fig. 8. Fig. 8(a)-(c) shows thermal simulations at varying levels of resolution with  $P_D = 1$  W/mm. Fig. 8(d) shows the temperature profile along the gate width of the device centered at the drain-edge of the gate. This result

This set of measurements were performed on a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET with a specific device geometry. However, the nature of the measurement technique of providing a reference from the baseplate temperature for very short pulse durations allows channel temperature measurements to be applied to devices with similar geometries. Others have reported similar pulsed I-V methods that were used to identify the R<sub>TH</sub> of Ga<sub>2</sub>O<sub>3</sub> MOSFETs [25]. These findings along with data obtained through Raman thermography [22] and simulation [32] can be seen in Table I. Some additional device layout-specific parameters are shown for comparison purposes.

The R<sub>TH</sub> data shown in Table I summarizes the available Ga<sub>2</sub>O<sub>3</sub> MOSFET R<sub>TH</sub> data that has been published to-date. The data shown here includes (A) this work, (B) pulsed I-V data from Wong et al. [25], (C) simulation data from Singh et al. [32], and (D) Raman thermography data from Pomeroy et al. [22]. An R<sub>TH</sub> value was not reported for Device C, but rather a plot of channel temperature as a function of power dissipation at an ambient temperature of 25°C. To compare the results for these four devices, we used the method described in this work to find the R<sub>TH</sub> of Device C. Interestingly, this resulted in an R<sub>TH</sub> of 116°C-mm/W, which was significantly higher than that reported by the other three papers. There are many variables that can alter R<sub>TH</sub> (e.g. channel dimensions, substrate, ambient temperature, etc.). However, it appears that Devices B and C had a near-identical device layout, a (010)-oriented Fe-doped Ga<sub>2</sub>O<sub>3</sub> substrate, and only a minor 5°C ambient temperature

| TABLE I                   |                                                |         |        |        |

|---------------------------|------------------------------------------------|---------|--------|--------|

| Parameter                 | A [this work]                                  | B [25]  | C [32] | D [22] |

| R <sub>TH</sub> (°C-mm/W) | 73 / 59                                        | 48 / 56 | 116*   | 88     |

| T <sub>Ambient</sub> (°C) | 23 / 25                                        | 20/125  | 25     | 25     |

| Meas. Tech.               | PIV / Raman                                    | PIV     | Sim.   | Raman  |

| Substrate                 | (010) Fe-doped $Ga_2O_3$ with 650 µm thickness |         |        |        |

| d <sub>CH</sub> (nm)      | 65                                             | 300     | 300    | 300    |

| $N_{D} (cm^{-3})$         | 2E18                                           | 3E17    | 3E17   | 3E17   |

| $L_{SD}$ ( $\mu m$ )      | 8                                              | 22      | 22     | 44     |

| $L_{G}\left(\mu m\right)$ | 0.14                                           | 2       | 2      | 4      |

| $L_{GD}$ ( $\mu m$ )      | 7.36                                           | 15      | 15     | 30     |

| L <sub>GS</sub> (µm)      | 0.5                                            | 5       | 5      | 10     |

| $W_{G}\left(\mu m\right)$ | 50                                             | -       | 500    | 200    |

| # of Fingers              | 2                                              | 1       | -      | 1      |

| d <sub>Al2O3</sub> (nm)   | 20                                             | 20      | 20     | 20     |

| H <sub>FP</sub> (nm)      | 90                                             | -       | 400    | 400    |

Comparison of this work (Device A) with previously reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET thermal resistance values and corresponding device fabrication properties. H<sub>FP</sub> represents the field-plate height.

\*  $R_{TH}$  not reported; estimated here by linear fitting of  $T_{CH}$ - $P_D$  data.

difference. Device B used a similar approach to that first reported by Joh *et al.*, but since a linear  $I_{DS}$ - $T_{CH}$  relationship was not observed, they instead altered the technique by using a  $V_{DS}$ -dependent  $I_{DS}$ - $T_{CH}$  calibration. From this calibration data,

they were able to obtain a relationship between channel temperature and DC power density, resulting in an  $R_{TH}$  of 48 °C-mm/W at 20°C. The data for Device C was found using single pulse thermal simulations where the channel temperature transient was evaluated at various amounts of power dissipation. The  $R_{TH}$  of 88°C-mm/W reported for Device D is similar to what was found in this work, despite some major device fabrication differences.

As seen in Table I, the devices tested in this work are more tightly scaled than those previously examined elsewhere, with smaller L<sub>G</sub> and higher channel doping leading to a smaller and more tightly confined depletion region. During Ga<sub>2</sub>O<sub>3</sub> MOSFET operation the majority of heat will be generated below the gate on the drain-side of the channel, and we expect that the physically small region for this thermal load will contribute to a larger temperature gradient and larger differences overall. As shown in Fig. 6(b), this is where we observed the highest T<sub>CH</sub>. We believe this is one reason for the significant R<sub>TH</sub> difference observed between the pulsed I-V results of this work and those from Device B in Table I. Device B had channel dimensions that were quite large in comparison to the MOSFET analyzed here, and since the pulsed I-V method provides an average R<sub>TH</sub> of the channel, the heat created at the drain-side below the gate region has a lessened impact on RTH.

#### V.CONCLUSION

Pulsed I-V measurements were performed to evaluate selfheating effects in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin-channel MOSFETs. Characterization was performed within a wide temperature range of 23 to 200°C using sub-µs pulsewidths. The  $I_{D,max}$  and  $R_{ON}$  were measured at each temperature, then used to identify a  $T_{CH}$ -P<sub>D</sub> relationship. The  $T_{CH}$  was found to have a linear dependence on P<sub>D</sub>, and a maximum  $T_{CH}$  of 208°C was observed for a P<sub>D</sub> of 2.56 W/mm. The MOSFET channel was found to have a  $R_{TH}$  of 73°C-mm/W, which is in agreement with previous reports that analyzed channel temperature in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. Additional self-heating characterization was performed using Raman nano-thermography, which resulted in an average  $R_{TH}$  of 59°C-mm/W. Further reducing the  $R_{TH}$  in Ga<sub>2</sub>O<sub>3</sub> devices by developing more efficient thermal management approaches will be important for improving performance. This work describes one possible thermal characterization method that can be used to evaluate new heat extraction concepts.

#### REFERENCES

- Z. Galazka, "β-Ga2O3 for wide-bandgap electronics and optoelectronics," *Semicond. Sci. Technol.*, vol. 33, no. 11, p. 113001, Oct. 2018, doi: 10.13385/j.cnki.vacuum.2018.06.15.

- [2] M. Higashiwaki and G. H. Jessen, "Guest editorial: the dawn of gallium oxide microelectronics," *Appl. Phys. Lett.*, vol. 112, no. 6, p. 060401, Feb. 2018, doi: 10.1063/1.5017845.

- [3] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Gallium oxide (Ga2O3) metal-semiconductor field-effect transistors on single-crystal β-Ga2O3 (010) substrates," *Appl. Phys. Lett.*, vol. 100, no. 1, p. 13504, Jan. 2012, doi: 10.1063/1.3674287.

- [4] A. J. Green, K. D. Chabak, E. R. Heller, R. C. Fitch, M. Baldini, A. Fiedler, K. Irmscher, G. Wagner, Z. Galazka, S. E. Tetlak, A. Crespo, K. Leedy, and G. H. Jessen, "3.8-MV/cm breakdown strength of MOVPE-grown Sn-doped β-Ga2O3 MOSFETs," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 902–905, July 2016, doi: 10.1109/LED.2016.2568139.

- [5] K. Sasaki, M. Higashiwaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Ga2O3 Schottky barrier diodes fabricated by using single-crystal β-Ga2O3 (010) substrates," *IEEE Electron Device Lett.*, vol. 34, no. 4, pp. 493–495, Apr. 2013, doi: 10.1109/LED.2013.2244057.

- [6] K. Konishi, K. Goto, H. Murakami, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "1-kV vertical Ga2O3 field-plated Schottky barrier diodes," *Appl. Phys. Lett.*, vol. 110, no. 22, p. 222104, Mar. 2017, doi: 10.1063/1.4998311.

- [7] Z. Hu, H. Zhou, Q. Feng, J. Zhang, C. Zhang, K. Dang, Y. Cai, Z. Feng, Y. Gao, X. Kang, and Y. Hao, "Field-plated lateral β-Ga2O3 Schottky barrier diode with high reverse blocking voltage of more than 3 kV and high DC power figure-of-merit of 500 MW/cm2," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1564–1567, Oct. 2018, doi: 10.1109/LED.2018.2868444.

- [8] Z. Xia, C. Joishi, S. Krishnamoorthy, S. Bajaj, Y. Zhang, and M. Brenner, S. Lodha, and S. Rajan, "Delta doped β-Ga<sub>2</sub>O<sub>3</sub> field effect transistors with regrown ohmic contacts," *IEEE Electron Device Lett.*, vol. 39, no. 4, pp. 568–571, Apr. 2018, doi: 10.1109/LED.2018.2805785.

- [9] N. A. Moser, J. P. McCandless, A. Crespo, K. D. Leedy, A. J. Green, E. R. Heller, K. D. Chabak, N. Peixoto, and G. H. Jessen, "High pulsed current density β-Ga2O3 MOSFETs verified by an analytical model corrected for interface charge," *Appl. Phys. Lett.*, vol. 110, no. 14, pp. 0–5, Apr. 2017, doi: 10.1063/1.4979789.

- [10] H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, "Highperformance depletion/enhancement-mode β-Ga2O3 on insulator (GOOI) field-effect transistors with record drain currents of 600/450 mA/mm," *IEEE Electron Device Lett.*, vol. 38, no. 1, pp. 103–106, Jan. 2017, doi: 10.1109/LED.2016.2635579.

- [11] K. D. Chabak, D. E. Walker, A. J. Green, A. Crespo, M. Lindquist, K. Leedy, S. Tetlak, R. Gilbert, N. A. Moser, and G. Jessen, "Sub-micron gallium oxide radio frequency field-effect transistors," 2018 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), 2018, pp. 1–3, doi: 10.1109/IMWS-AMP.2018.8457153.

- [12] K. D. Chabak, J. P. McCandless, N. A. Moser, A. J. Green, K. Mahalingam, A. Crespo, N. Hendricks, B. M. Howe, S. E. Tetlak, K.

Leedy, R. C. Fitch, D. Wakimoto, K. Sasaki, A. Kuramata, and G. H. Jessen, "Recessed-gate enhancement-mode  $\beta$ -Ga2O3 MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 67–70, Jan. 2018, doi: 10.1109/LED.2017.2779867.

- [13] K. Zeng, A. Vaidya, and U. Singisetti, "1.85 kV breakdown voltage in lateral field-plated Ga2O3 MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 9, pp. 1385–1388, Sep. 2018, doi: 10.1109/LED.2018.2859049.

- [14] K. D. Chabak, N. A. Moser, A. J. Green, D. E. Walker, S. E. Tetlak, E. Heller, A. Crespo, R. Fitch, J. P. McCandless, K. Leedy, M. Baldini, G. Wagner, Z. Galazka, X. Li, and G. H. Jessen, "Enhancement-mode Ga2O3 wrap-gate fin field-effect transistors on native (100) β-Ga2O3 substrate with high breakdown voltage," *Appl. Phys. Lett.*, vol. 109, no. 21, Nov. 2016, doi: 10.1063/1.4967931.

- [15] M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Field-plated Ga2O3 MOSFETs with a breakdown voltage of over 750 V," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 212-215, Feb. 2016, doi: 10.1109/LED.2015.2512279.

- [16] A. J. Green, K. D. Chabak, M. Baldini, N. Moser, R. Gilbert, R. C. Fitch, G. Wagner, Z. Galazka, J. P. McCandless, A. Crespo, K. Leedy, and G. H. Jessen, "β-Ga2O3 MOSFETs for radio frequency operation," *IEEE Electron Device Lett.*, vol. 38, no. 6, pp. 790–793, June 2017, doi: 10.1109/LED.2017.2694805.

- [17] Z. Hu, K. Nomoto, W. Li, N. Tanen, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H. G. Xing, "Enhancement-mode Ga2O3 vertical transistors with breakdown voltage > 1 kV," *IEEE Electron Device Lett.*, vol. 39, no. 6, pp. 869-872, June 2018, doi: 10.1109/LED.2018.2830184.

- [18] M. H. Wong, K. Goto, H. Murakami, Y. Kumagai, and M. Higashiwaki, "Current aperture vertical β-Ga2O3 MOSFETs fabricated by N- and Siion implantation doping," *IEEE Electron Device Lett.*, vol. PP, no. c, pp. 1–1, Dec. 2018, doi: 10.1109/LED.2018.2884542.

- [19] Y. Lv, X. Zhou, S. Long, X. Song, Y. Wang, S. Liang, Z. He, T. Han, X. Tan, Z. Feng, H. Dong, X. Zhou, Y. Yu, S. Cai, and M. Lie, "Sourcefield-plated β-Ga2O3 MOSFET with record power figure of merit of 50.4 MW/cm2," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 83-86, Jan. 2019, doi: 10.1109/LED.2018.2881274.

- [20] N. Blumenschein, M. Slomski, P. P. Paskov, F. Kaess, M. H. Breckenridge, J. F. Muth, and T. Paskova, "Thermal conductivity of bulk and thin film β-Ga2O3 measured by the 3ω technique," *Proc. SPIE*, vol. 10533, p. 10533, Feb. 2018, doi: 10.1117/12.2288267.

- [21] M. Slomski, N. Blumenschein, P. P. Paskov, J. F. Muth, and T. Paskova, "Anisotropic thermal conductivity of β-Ga2O3 at elevated temperatures: effect of Sn and Fe dopants," *J. Appl. Phys.*, vol. 121, no. 23, p. 235104, June 2017, doi: 10.1063/1.4986478.

- [22] J. W. Pomeroy, C. Middleton, M. Singh, S. Dalcanale, M. J. Uren, M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, M. Higashiwaki, and M. Kuball, "Raman thermography of peak channel temperature in β-Ga2O3 MOSFETs," *IEEE Electron Device Lett.*, vol. 40, no. 2, pp. 189–192, Feb. 2019, doi: 10.1109/LED.2018.2887278.

- [23] B. Chatterjee, A. Jayawardena, E. Heller, D. W. Snyder, S. Dhar, and S. Choi, "Thermal characterization of gallium oxide Schottky barrier diodes," *Rev. Sci. Instrum.*, vol. 89, no. 11, p. 114903, Nov. 2018, doi: 10.1063/1.5053621.

- [24] J. Chen, Z. Xia, S. Rajan, and S. Kumar, "Analysis of thermal characteristics of gallium oxide field-effect-transistors," *Proc. 17th Intersoc. Conf. Therm. Thermomechanical Phenom. Electron. Syst. ITherm* 2018, no. 10, pp. 392–397, 2018, doi: 10.1109/ITHERM.2018.8419544.

- [25] M. H. Wong, Y. Morikawa, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Characterization of channel temperature in Ga2O3 metal-oxide-semiconductor field-effect transistors by electrical measurements and thermal modeling," *Appl. Phys. Lett.*, vol. 109, no. 19, p. 193503, Nov. 2016, doi: 10.1063/1.4966999.

- [26] J. Joh, J. A. Del Alamo, U. Chowdhury, T. M. Chou, H. Q. Tserng, and J. L. Jimenez, "Measurement of channel temperature in GaN highelectron mobility transistors," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 2895–2901, Dec. 2009, doi: 10.1109/TED.2009.2032614.

- [27] W. F. Zhang, Y. L. He, M. S. Zhang, Z. Yin, and Q. Chen, "Raman scattering study on anatase TiO2 nanocrystals," *J. Phys. D. Appl. Phys.* vol. 33, no. 8, pp. 912-916, Mar. 2000, doi: 10.1088/0022-3727/33/8/305.

- [28] R.B. Simon, J. W. Pomeroy, and M. Kuball, "Diamond micro-Raman thermometers for accurate gate temperature measurements," *Appl. Phys. Lett.*, vol. 104, no. 21, p. 213503, May 2014, doi: 10.1063/1.4879849.

- [29] J. Anaya, T. Bai, Y. Wang, C. Li, M. Goorsky, T. L. Bougher, L. Yates, Z. Cheng, S. Graham, K. D. Hobart, T. I. Feygelson, M. J. Tadjer, T. J. Anderson, B. B. Pate, and M. Kuball, "Simultaneous determination of the lattice thermal conductivity and grain/grain thermal resistance in polycrystalline diamond," *Acta Materialia*, vol. 139, pp. 215-225, Oct. 2017, doi: 10.1016/j.actamat.2017.08.007.

- [30] J. Dallas, G. Pavlidis, B. Chatterjee, J. S. Lundh, M. Ji, J. Kim, T. Kao, T. Detchprohm, R. D. Dupuis, S. Shen, S. Graham, and S. Choi, "Thermal characterization of gallium nitride p-i-n diodes," *Appl. Phys. Lett.*, vol. 112, no. 7, p. 073503, Feb. 2018, doi: 10.1063/1.5006796.

- [31] G. J. Riedel, J. W. Pomeroy, K. P. Hilton, J. O. Maclean, D. J. Wallis, M. J. Uren, T. Martin, and M. Kuball, "Nanosecond timescale thermal dynamics of AlGaN/GaN electronic devices," *IEEE Electron Device Lett.*, vol. 29, no. 5, pp. 416–418, May 2008, doi: 10.1109/LED.2008.919779.

- [32] M. Singh, M. A. Casbon, M. J. Uren, J. W. Pomeroy, S. Dalcanale, S. Karboyan, P. J. Tasker, M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, M. Higashiwaki, and M. Kuball, "Pulsed large signal RF performance of field-plated Ga2O3 MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1572–1575, Oct. 2018, doi: 10.1109/LED.2018.2865832.