## Serialization Management Driven Performance in Best-Effort Hardware Transactional Memory Systems

by

Matthew Gaudet

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science

Department of Computing Science University of Alberta

©Matthew Gaudet, 2014

## **Abstract**

Serialization Management is the Best-Effort Hardware Transactional Memory (BE-HTM) counterpart to Software Transactional Memory (STM) Contention Management. A serialization manager uses non-speculative serialization to provide a forward-progress guarantee while simultaneously attempting to provide high application performance. Historically, non-speculative serialization management has been done through a simple policy of allowing a fixed number of retries. This thesis investigates the proposition that application performance can be improved through better Serialization Management.

This thesis explores seven serialization managers and their tuning parameters on Blue Gene/Q's BE-HTM system using the Stanford Transactional Applications for Multi-Processing (STAMP) and the Recognition, Mining and Synthesis (RMS-TM) benchmark suites. It presents the first large-scale investigation of Serialization Management for BE-HTM in the literature. This investigation experiments with a large number of values for each tuning parameter on multiple platforms. The main finding is that program performance can be improved by changing the serialization manager. However, performance is actually dominated by the tuning of parameters for each manager and this tuning depends on the benchmark, the thread count, and the platform.

# **Preface**

Parts of Chapter 4 have been previously submitted to the 2013 ACM Student Research Competition Grand Finals, titled *Transactional Event Profiling in a Best-Effort Hardware Transactional Memory System*.

Appendix A is a collaborative work, with authorship shared among Amy Wang, myself, Peng Wu, Martin Ohmacht, José Nelson Amaral, Christopher Barton, Raul Silvera, and Maged M. Michael. I ran the experimentation and data analysis for the paper, with the majority of writing having been done by the remaining authors. It has been accepted for publication in the *IEEE Transactions on Computers*, however it has not yet appeared at the time of thesis submission, and so is included as an appendix.

It's like, French is a great idea, but nobody is going to invent French if they're constantly being attacked by bears. Do you see? SYSTEMS HACKERS SOLVE THE BEAR MENACE. Only through the constant vigilance of my people do you get the freedom to think about croissants and subtle puns involving the true father of Louis XIV.

— James Mickens, *The Night Watch*

# Acknowledgements

First and foremost, I must thank my parents. They raised me well, and helped guide me just enough to let me find my path.

Andrea, my long-time partner, has been a wonderful support throughout this process.

My supervisor José Nelson Amaral has guided me continuously for more than six years now, ever since he took me on as a summer student – a program that set me on the path I have followed until today. He has been an excellent mentor, and I do not believe I could have achieved a fraction of what I have without him.

Thanks to Peng Wu, for her excellent guidance and insights, and to Amy Wang for laying the ground work upon which this thesis was built.

I would also like to thank a number of others who each helped me in ways large and small to get through my Masters program: Kit Barton, Martin Ohmacht, Maged Micheal, Wang Chen, Marcel Mitran, Jerry Zheng, Ian Gartley, Alan Li, Joran Siu, Yan Luo, Yi Zheng, Arthur Zimek, Ricardo Campello, Jörg Sander and Manon Gaudet.

IBM must be thanked for being generous in their support. Hundreds of thousands of experiments were performed over the course of this thesis, and would have been impossible without them.

This thesis has been funded in part by an Alberta Innovates Graduate Student Scholarship from Alberta Technology Futures as well as a Canada Graduate Scholarship from the Natural Sciences and Engineering Research Council of Canada.

# **Table of Contents**

| 1 | Intr | oduction 1                                                       |

|---|------|------------------------------------------------------------------|

|   | 1.1  | Transactional Memory                                             |

|   |      | 1.1.1 Software Transactional Memory 6                            |

|   |      | 1.1.2 Best-Effort Hardware Transactional Memory                  |

|   | 1.2  | Performance in TM systems                                        |

|   | 1.3  | Programming Models and Forward Progress                          |

|   | 1.4  | Programming Models and Forward Progress for Best-effort HTMs . 9 |

|   | 1.5  | Non-speculative Serialization and the Serialization Manager 11   |

|   | 1.6  | Serialization-Manager-Driven Performance                         |

|   | 1.0  | octanization manager billion renormance                          |

| 2 | Bacl | kground 14                                                       |

|   | 2.1  | Race Conditions                                                  |

|   | 2.2  | Transactional Memory                                             |

|   | 2.2  | Transactional Memory                                             |

|   |      | 2.2.2 Hardware Transactional Memory 20                           |

|   | 2.2  | Blue Gene/Q                                                      |

|   | 2.3  |                                                                  |

|   |      | 2.3.1 Hardware Support                                           |

|   |      | 2.3.2 Software Support                                           |

| 2 | The  | Effect of Serialization Management on Performance 28             |

| 3 |      | Execution Diffelle                                               |

|   | 3.1  | Evaluation Pitfalls                                              |

|   | 3.2  | New Serialization Managers                                       |

|   | 3.3  | Answering the Research Questions: My Approach 30                 |

|   | 3.4  | Experimental Methodology                                         |

|   |      | 3.4.1 Metrics                                                    |

|   | 3.5  | Benchmarks                                                       |

|   |      | 3.5.1 STAMP                                                      |

|   |      | 3.5.2 RMS-TM                                                     |

|   | 3.6  | Benchmark Characterization                                       |

|   |      | 3.6.1 Contention                                                 |

|   |      | 3.6.2 Capacity Overflow                                          |

|   |      |                                                                  |

| 4 | The  | Transactional Event Profiler 39                                  |

|   | 4.1  | TEP Design and Implementation                                    |

|   | 4.2  | Limitations of the TEP approach 40                               |

|   |      | 4.2.1 Probe Effects                                              |

|   |      | 4.2.2 Hardware Limitations                                       |

|   | 4.3  | A Sample of Event Log Analyzers                                  |

|   |      | 4.3.1 Visualizing Event Rates                                    |

|   |      | 4.3.2 Visualizing and Comparing Dynamic Transaction Execution    |

|   |      | Lengths                                                          |

|   |      | 4.3.3 Micro-level analysis and visualization                     |

|   |      | 1000 - 1 1 1 1 1 1 1 1 TO                                        |

|     | 4.4          | 4.3.4 Visualizing Parameter Evolution                  | 49<br>50 |

|-----|--------------|--------------------------------------------------------|----------|

| 5   | Expl         | ored Serialization Managers                            | 51       |

|     | 5.1          | Max-Retry                                              | 51       |

|     | 5.2          | SerializationControl                                   | 51       |

|     | 5.3          | Limit, inspired by Karma                               | 52       |

|     | 5.4          | LIMITMEAN and LIMITMEANST                              | 53       |

|     | 5.5          | Best-Effort Adaptive Transactional Scheduling (BE-ATS) | 54       |

|     | 5.6          | Percentage Of Effective Work (PEW)                     | 56       |

|     | 5.7          | Other Investigated Serialization Managers              | 57       |

| 6   |              | ager-Independent Policies                              | 59       |

|     | 6.1          | Rollback Delay                                         | 59       |

|     | 6.2          | Capacity Serialization                                 | 62       |

| 7   | Seria        | alization Manager Tunings                              | 66       |

|     | <b>7.</b> 1  | Tuning Max-Retry                                       | 66       |

|     |              | 7.1.1 Mode Generalizability                            | 67       |

|     | 7.2          | Tuning SerializationControl's Blacklisting Threshold   | 70       |

|     | 7.3          | Tuning Limit's Per-Transaction Execution-Cycle Budget  | 73       |

|     | <i>7</i> .4  | Tuning $M$ in LimitMean and LimitMeanST                | 75       |

|     | <i>7</i> .5  | Tuning $\alpha$ in BE-ATS                              | 81       |

|     | 7.6          | Tuning PEW's $T$ and $\alpha$                          | 85       |

|     | 7.7          | Tuning, a summary                                      | 89       |

| 8   | Seria        | alization-Manager-Driven Performance Effects           | 90       |

|     | 8.1          | Performance Unpredictability                           | 90       |

|     | 8.2          | Stable Trends                                          | 91       |

|     | 8.3          | Wasted-Work Hypothesis                                 | 93       |

|     | 8.4          | Serialization Management and Performance               | 96       |

| 9   | Rela         | ted Work                                               | 100      |

|     | 9.1          | HTM Performance Analyses                               | 100      |

|     | 9.2          | Non-Speculative Serialization                          |          |

|     |              | 9.2.1 Hardware Systems with Non-speculative Execution  |          |

|     |              | 9.2.2 STM Analogues to Non-speculative Execution       | 102      |

|     | 9.3          | HTM Serialization Enhancements                         | 103      |

|     | 9.4          | Transactional Profiling                                | 104      |

| 10  | Stud         | y Limitations                                          | 105      |

| 11  | Futn         | ire Work                                               | 107      |

|     | 11.1         | Formalization and Abstraction                          | 107      |

|     | 11.2         | Invasive Serialization Managers                        | 107      |

|     | 11.3         | Hardware Non-speculative Serialization                 | 108      |

| 12  | Con          | clusion                                                | 109      |

| Bil | Bibliography |                                                        |          |

| $\mathbf{A}$ | Softv | vare Support and Evaluation of Hardware Transaction Memory on |    |

|--------------|-------|---------------------------------------------------------------|----|

|              | Blue  | Gene/Q 11                                                     | 18 |

|              | A.1   | Introduction                                                  | 18 |

|              | A.2   | Transactional Memory Programming Model                        | 21 |

|              | A.3   | Hardware Transactional Memory Implementation in BG/Q 12       | 23 |

|              |       | A.3.1 Hardware Support for Transactional Execution in L2 12   | _  |

|              |       | A.3.2 Causes of Transactional Execution Failures              | -  |

|              | A.4   | Software Support for TM Programming Model                     | -  |

|              | •     | A.4.1 Managing Transaction Abort and Retry 12                 |    |

|              |       | A.4.2 Sandboxing of Speculative Execution                     | _  |

|              |       | A.4.3 Ensuring Forward Progress via Irrevocable Mode 13       |    |

|              |       | A.4.4 Runtime Adaptation                                      |    |

|              | A.5   | Experimental Setup and Benchmarks                             | _  |

|              | A.6   | Long- vs. Short-Running TM Mode                               |    |

|              |       | A.6.1 Loss of cache locality                                  |    |

|              |       | A.6.2 Capacity overflow                                       |    |

|              |       | A.6.3 Conflict detection granularity                          |    |

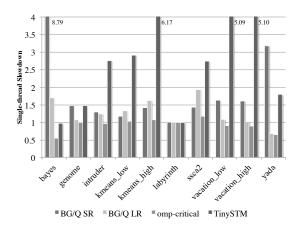

|              | A.7   | Single-thread TM Overhead                                     |    |

|              | ,     | A.7.1 Cache performance penalty                               |    |

|              |       | A.7.2 Capacity overflow                                       |    |

|              |       | A.7.3 Transaction entry and exit overhead                     |    |

|              | A.8   | Scalability                                                   |    |

|              |       | A.8.1 Locks                                                   |    |

|              |       | A.8.2 BG/Q TM                                                 |    |

|              |       | A.8.3 TinySTM                                                 |    |

|              | A.9   | Related Work                                                  |    |

|              | _     | Conclusion                                                    |    |

# **List of Tables**

| 3.1<br>3.2 | Aborts per commit and Capacity-overflow aborts per commit in the STAMP and RMS-TM benchmarks run with MAX-RETRY set to allow 10 retries with capacity-induced serialization and rollback delay | 34         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | enabled                                                                                                                                                                                        | 37         |

| 5.1        | Dismissed potential policies, grouped by reason for rejection                                                                                                                                  | 58         |

| A.2        | Benchmark Descriptions                                                                                                                                                                         | 132<br>138 |

| A.4<br>A.5 | execution                                                                                                                                                                                      | 145<br>149 |

|            | (1 thread)                                                                                                                                                                                     | 150        |

# **List of Figures**

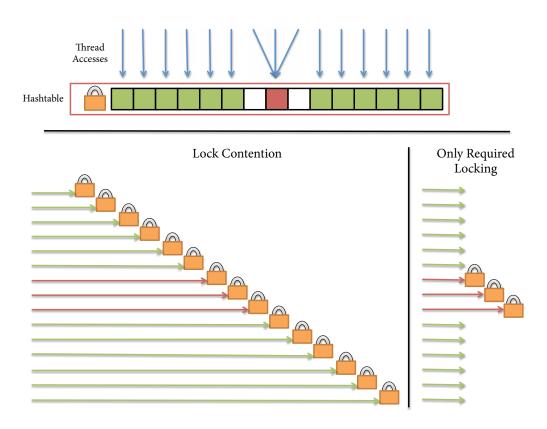

| 1.1               | Lock Contention visualized on a hashtable. The accesses in green would produce spurious locking, but the accesses in red require some synchronization. White buckets are not accessed by any thread                                                                                                            | 4              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.1<br>2.2<br>2.3 | Snippet of execution showing a data race with lost updates An example of STM instrumentation                                                                                                                                                                                                                   | 15<br>18<br>21 |

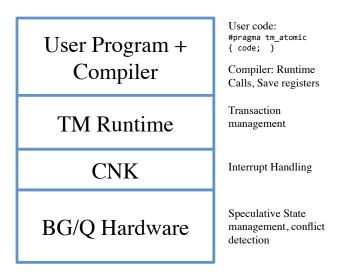

| 2.4               | BG/Q Transactional Memory Stack                                                                                                                                                                                                                                                                                | 23             |

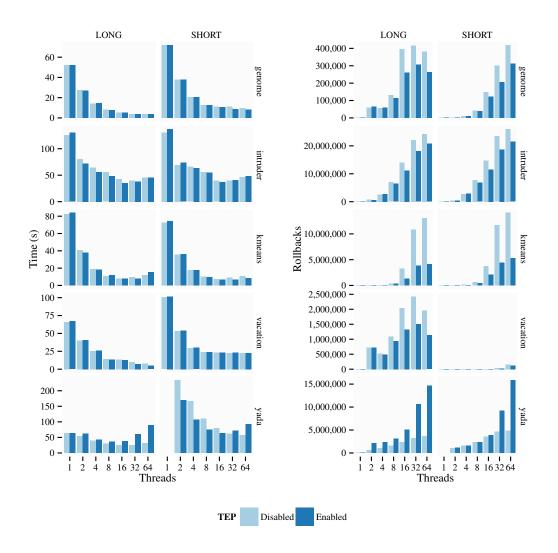

| 4.1               | Comparing runtime and rollback counts for STAMP benchmarks run both with (dark blue bars) and without (light blue bars) Transactional Event Profiling, using MAX-RETRY allowing 10 retries as the                                                                                                              |                |

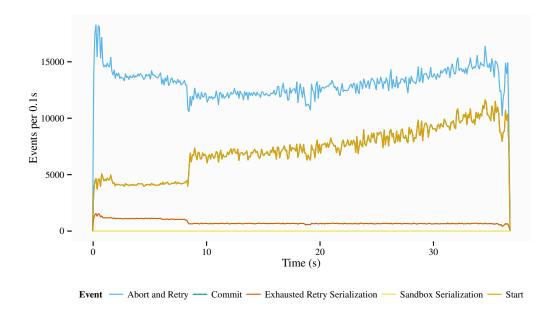

| 4.2               | serialization manager, in both Long and Short running mode Event rates for yada demonstrating program phases and consistent rate of serialization. Run with 16 threads in long-running mode with MAX-RETRY and 10 allowed retries                                                                              | 43             |

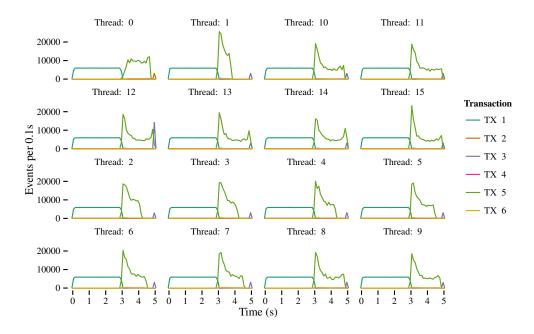

| 4.3               | Transaction rates for genome showing how transaction activity can vary across application threads. Run with 16 threads in long running                                                                                                                                                                         | 45             |

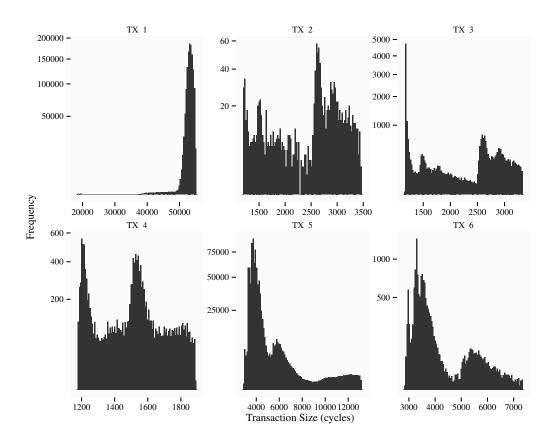

| 4.4               | mode, using the MAX-RETRY with 10 retries allowed Histogram of dynamic transaction execution times for the six static                                                                                                                                                                                          | 46             |

| 4.5               | transactions in genome                                                                                                                                                                                                                                                                                         | 47             |

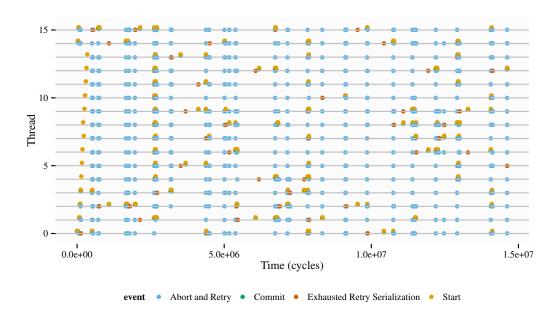

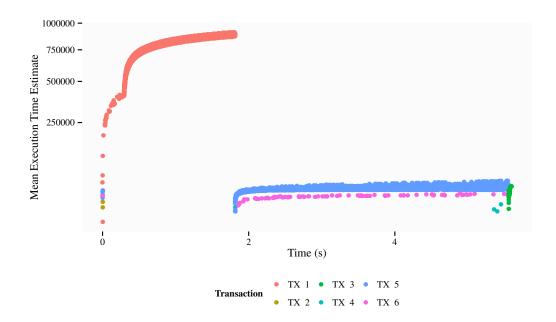

| 4.6               | time for yada Run with 16 threads and no rollback delays in Long Running Mode                                                                                                                                                                                                                                  | 48<br>49       |

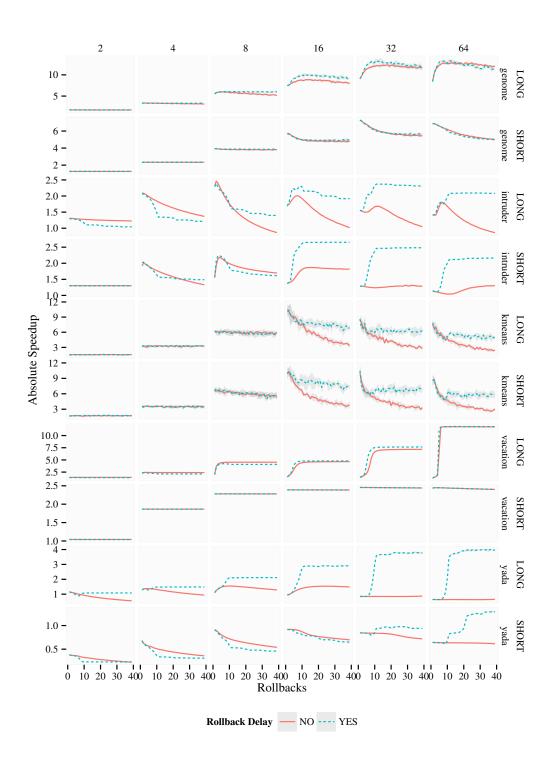

| 6.1               | The relationship between allowed-rollbacks and absolute speedup, showing the effect of exponential backoff. Using MAX-RETRY and no capacity serialization.                                                                                                                                                     | 61             |

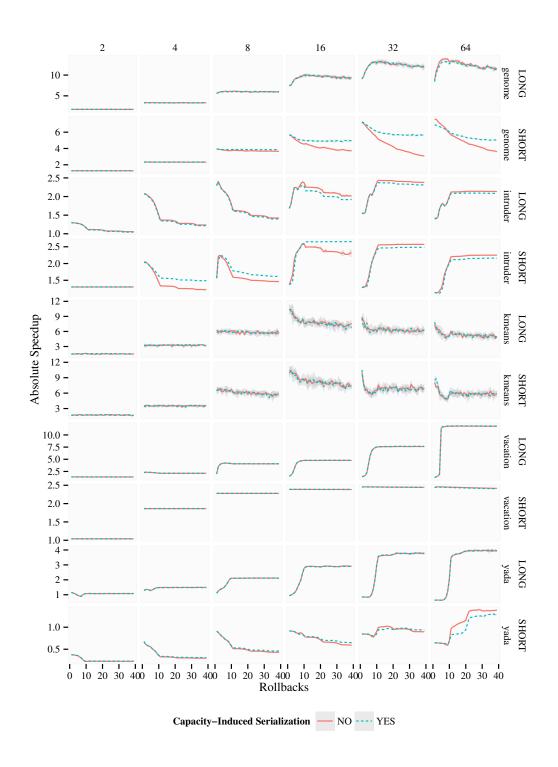

| 6.2               | The relationship between allowed-rollbacks and absolute speedup, showing the effect of capacity-induced serialization on the STAMP                                                                                                                                                                             |                |

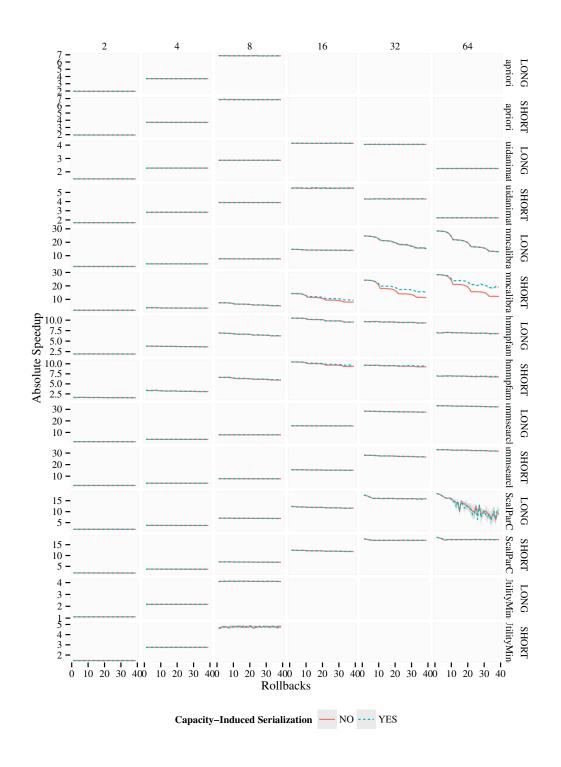

| 6.3               | benchmarks. Using MAX-RETRY and exponential-backoff The relationship between allowed-rollbacks and absolute speedup, showing the effect of capacity-induced serialization on the RMS-TM benchmarks. Using MAX-RETRY and exponential-backoff. apriori, fluidanimate and utilitymine are excluded for space rea- | 64             |

|                   | sons, as well as showing no effect                                                                                                                                                                                                                                                                             | 65             |

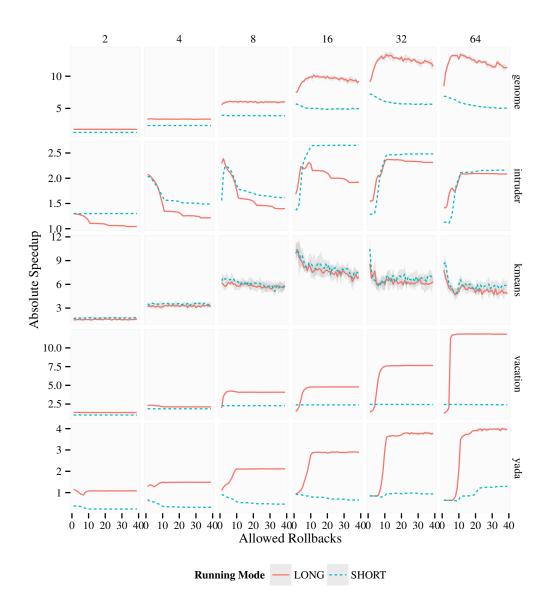

| 7.1        | Absolute Speedup for STAMP relative to the number of allowed-rollbacks in MAX-RETRY for both short and long-running mode. vacation-high and kmeans-high are elided because their behaviour                                                                                                                                        |          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

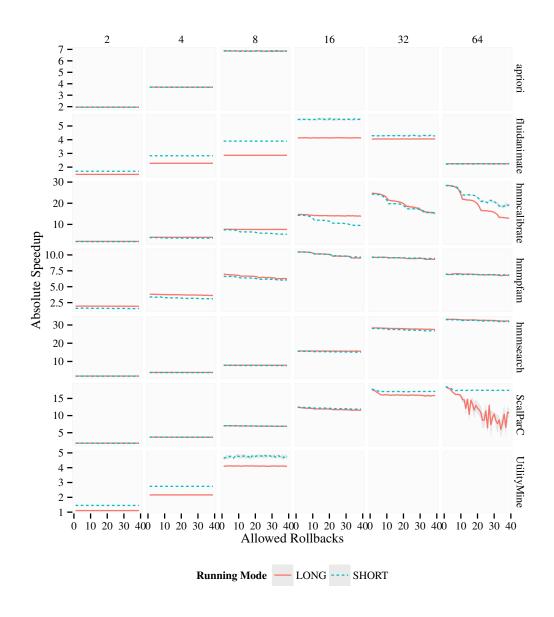

| 7.2        | is indistinguishable from their low contention counterparts Absolute Speedup for RMS-TM relative to the number of allowed-rollbacks in Max-Retry for both short and long-running mode.                                                                                                                                            | 68       |

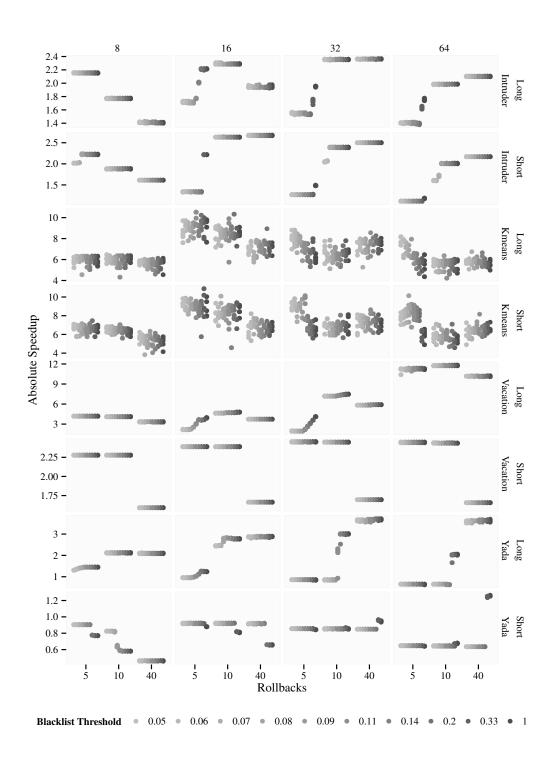

| 7.3        | Absolute speedup of the STAMP benchmarks, relative to Threshold                                                                                                                                                                                                                                                                   | 69       |

| 7.4        | and allowed rollbacks in SerializationControl                                                                                                                                                                                                                                                                                     | 72<br>72 |

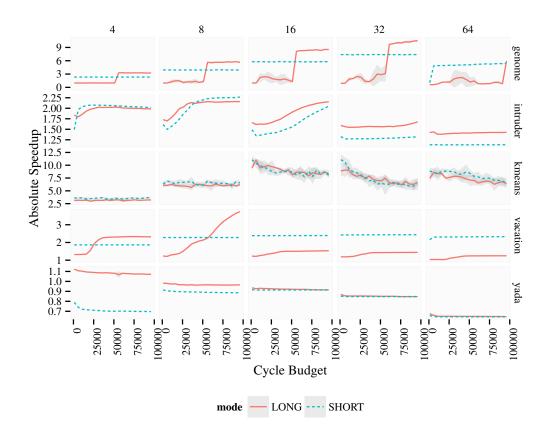

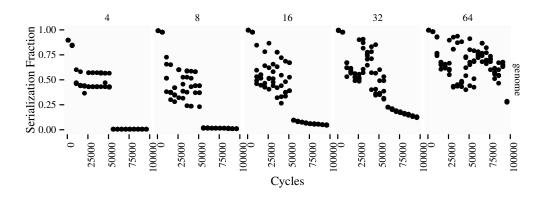

| 7.5        | Serialization fraction for genome in long running mode, relative to the cycle budget in Limit showing the dramatic effect of achieving                                                                                                                                                                                            | 73       |

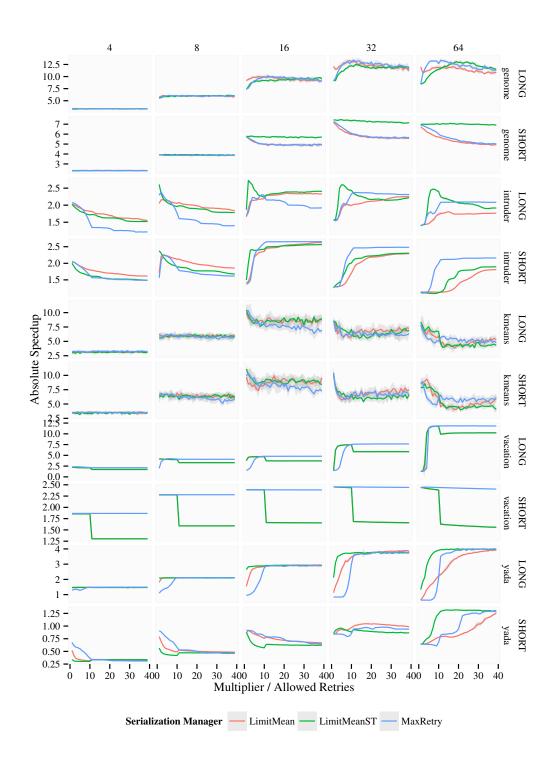

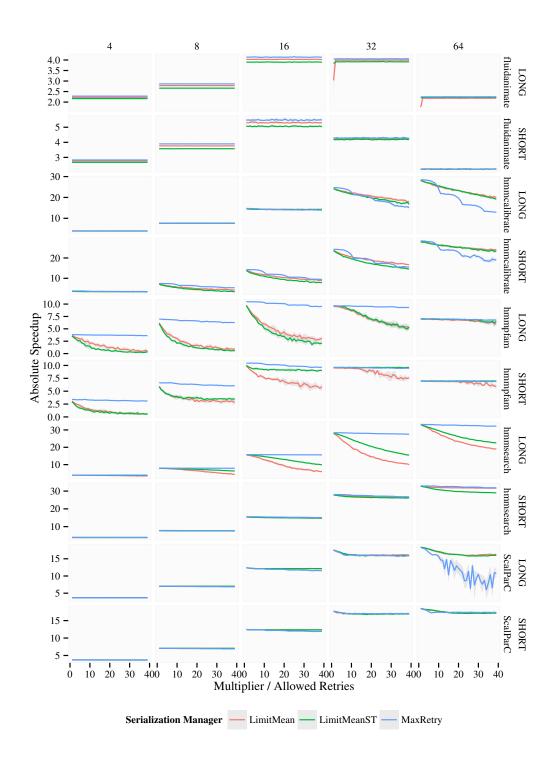

| 7.6        | Absolute Speedup for the STAMP benchmarks relative to $M$ or allowed retries when run with Limit, LimitMean or LimitMeanST. The results for 2 threads are elided because they don't vary much over                                                                                                                                | 74       |

| 7.7        | the range values explored                                                                                                                                                                                                                                                                                                         | 77       |

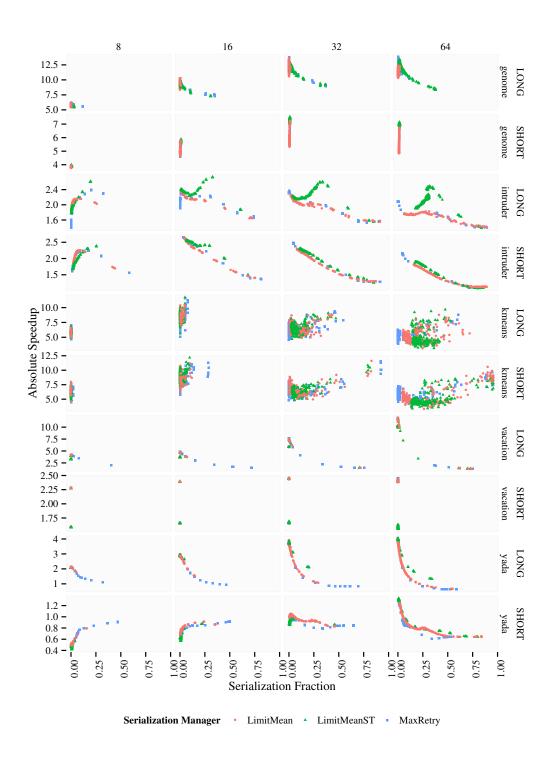

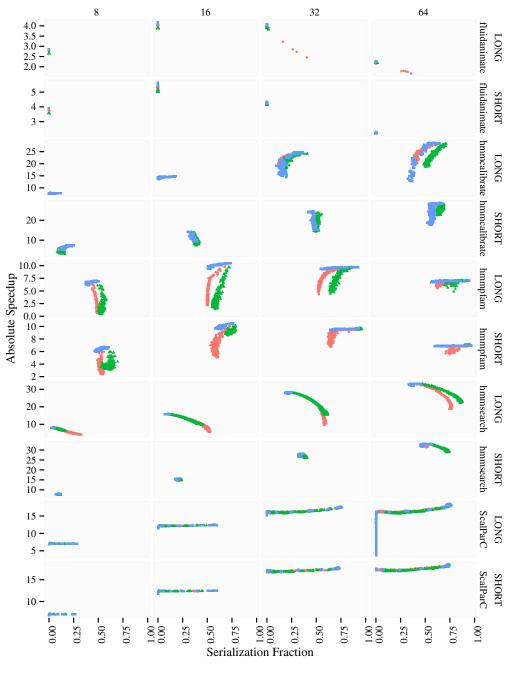

| 7.8        | are excluded because they don't see any change from policy or tuning. Absolute Speedup as related to serialization fraction for STAMP benchmarks run with the Max-Retry, Limitmean and LimitmeanST serialization managers with $M$ or allowed retries between 1                                                                   | 78       |

| 7.9        | and 39                                                                                                                                                                                                                                                                                                                            | 79       |

| 7.10       | speedup                                                                                                                                                                                                                                                                                                                           | 80       |

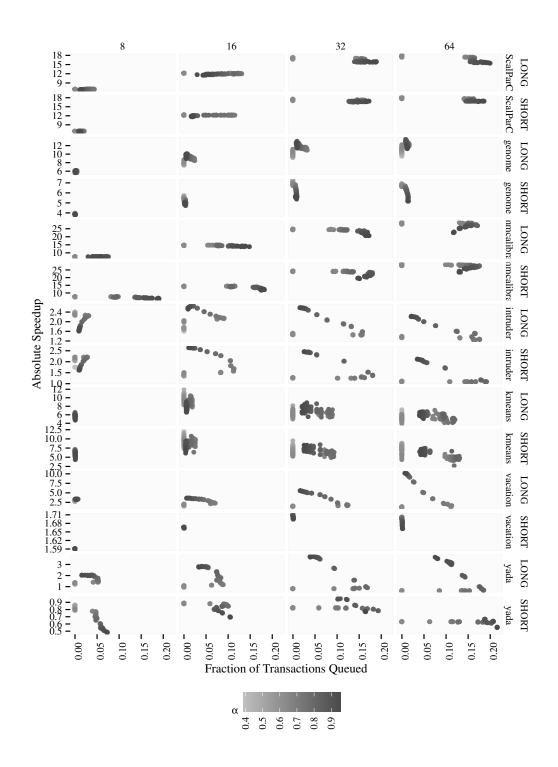

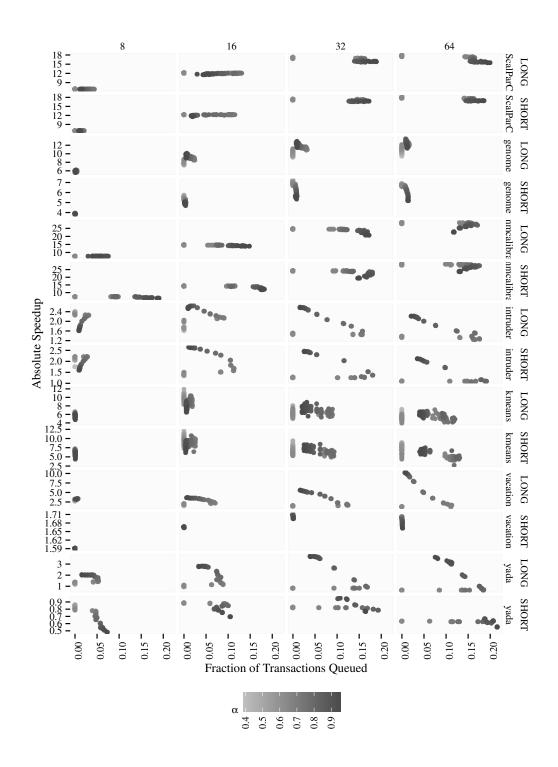

| 7.11       | low contention versions presented here                                                                                                                                                                                                                                                                                            | 83       |

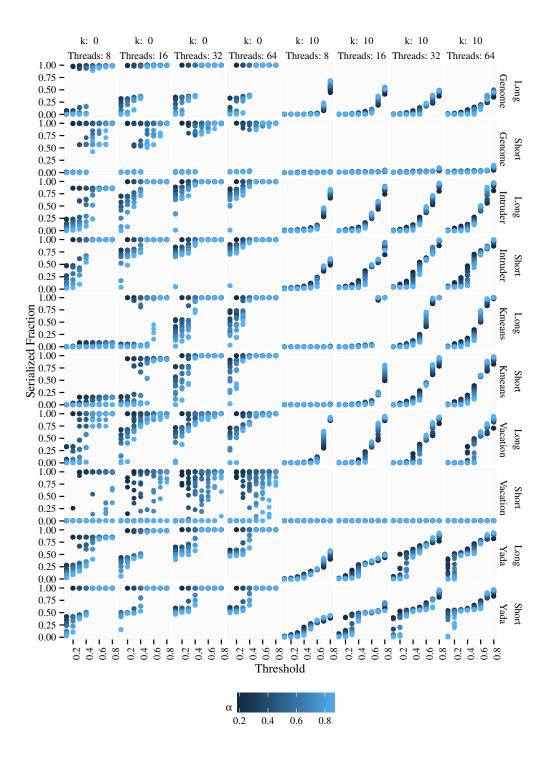

| 7.12       | lute speedup in the RMS-TM and STAMP benchmarks Varying the threshold and alpha parameters in STAMP running PEW for two values of <i>k</i> in Long and Short Running mode, for 8-64                                                                                                                                               | 84       |

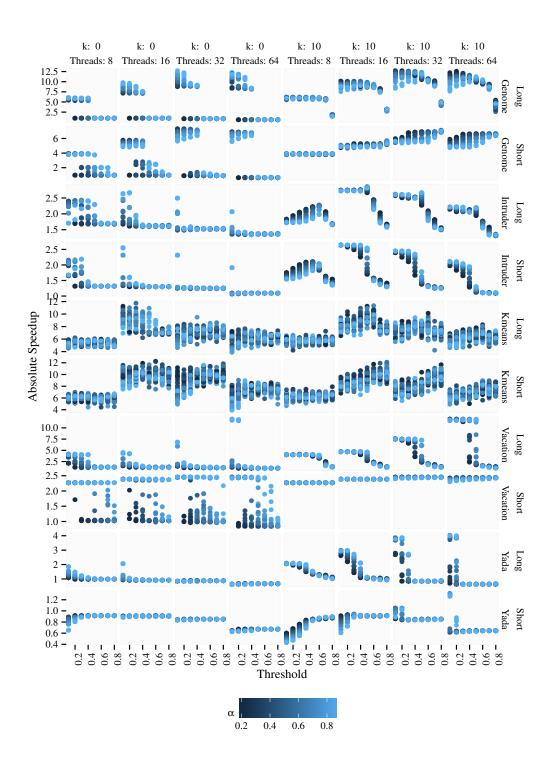

| 712        | threads. Results for 1-4 threads and the RMS-TM benchmarks are not presented because they are insensitive to parameter values Varying the threshold and alpha parameters in PEW for two values                                                                                                                                    | 87       |

| 7.13       | of $E$ in Short Running mode, showing serialization fraction                                                                                                                                                                                                                                                                      | 88       |

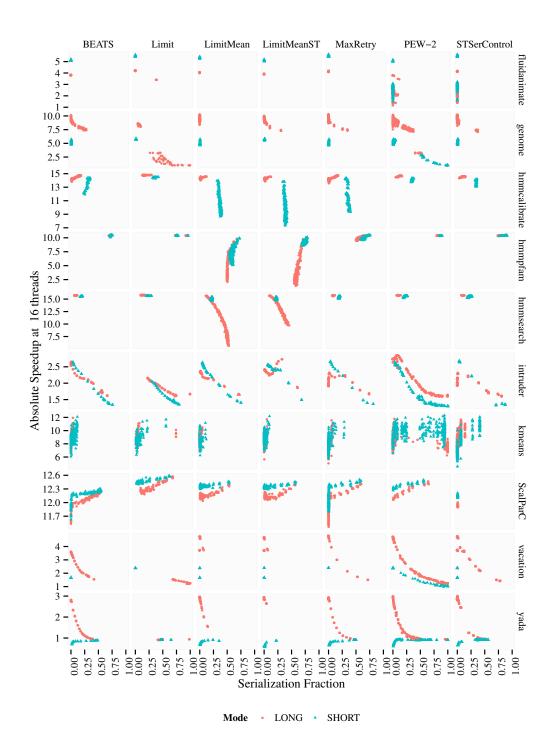

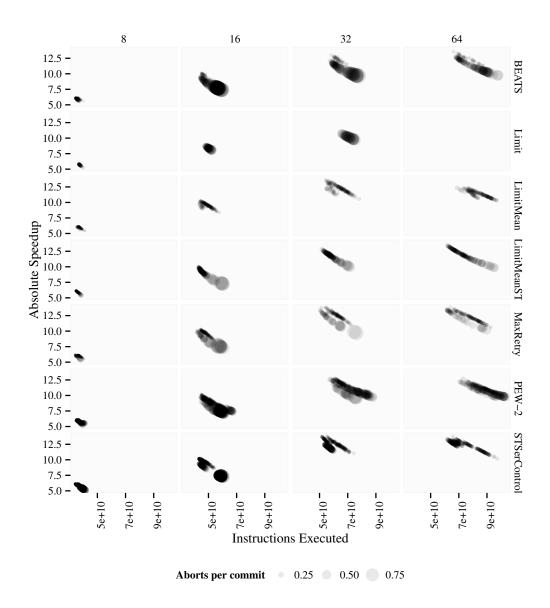

| 8.1<br>8.2 | Serialization Fraction and its relationship to absolute speedup for 16 threads, run in both long and short running mode Instructions Executed compared to Absolute Speedup for genome run with 8-64 threads in long running, plotting the top 30% of executions, where the size of each point corresponds to the number of Aborts | 92       |

|            | per commit, with smaller dots having fewer aborts                                                                                                                                                                                                                                                                                 | 94       |

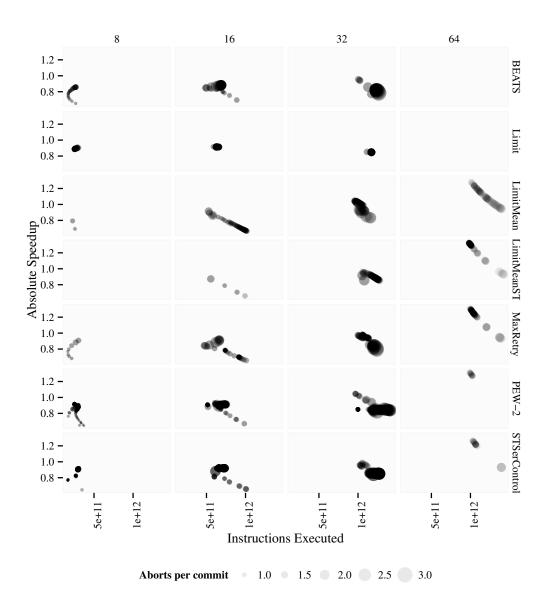

| 8.3  | Instructions Executed compared to Absolute Speedup for yada run with 8-64 threads in short-running mode, plotting the top 30% of executions, where the size of each point corresponds to the number |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

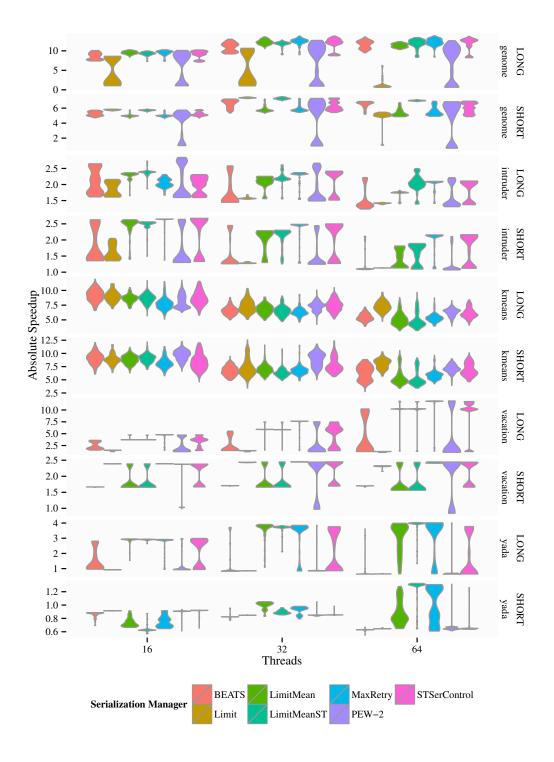

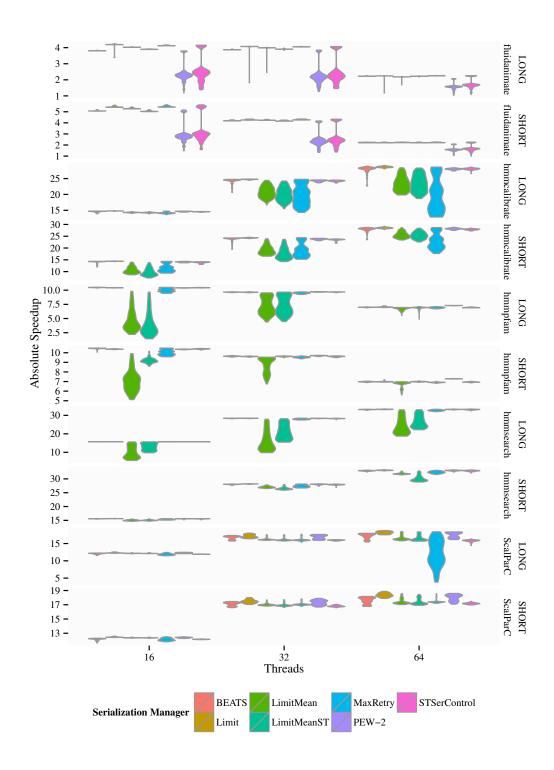

| 8.4  | of Aborts per commit, with smaller dots having fewer aborts Absolute Speedup distribution for STAMP benchmarks over all serialization managers and all their tunings displayed as violin plot       | 95  |

|      | (exponential-delay and capacity-induced serialization enabled)                                                                                                                                      | 98  |

| 8.5  | Absolute Speedup distribution for RMS-TM benchmarks over all serialization managers and all their tunings displayed as violin plot                                                                  |     |

|      | (exponential-delay and capacity-induced serialization enabled)                                                                                                                                      | 99  |

| A.1  | The main transaction of STAMP/kmeans benchmark using the BG/Q                                                                                                                                       |     |

|      | TM annotation                                                                                                                                                                                       | 122 |

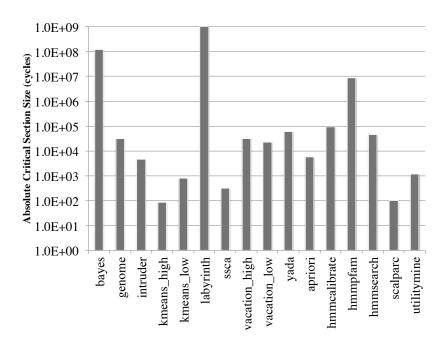

| A.2  | Transactional Memory Execution Overview                                                                                                                                                             | 128 |

| A.3  | Average time spent (in cycles) per dynamic instance of critical sec-                                                                                                                                |     |

|      | tions in the STAMP and RMS-TM benchmark suites                                                                                                                                                      | 134 |

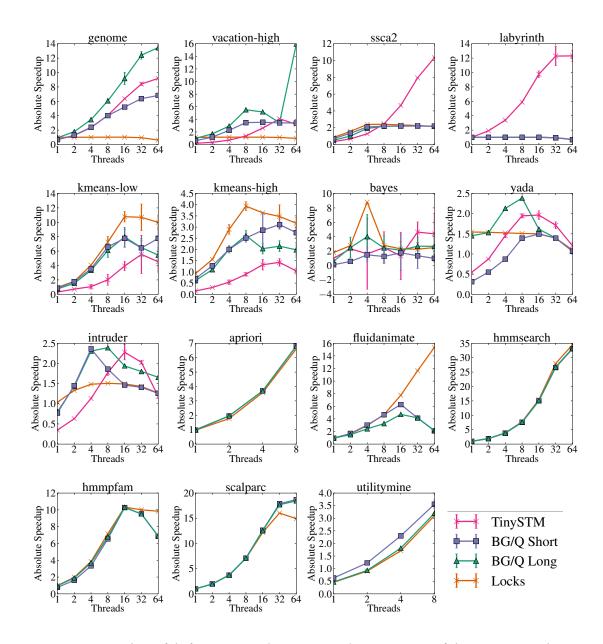

| A.4  | Speedup of different critical section implementations of the STAMP                                                                                                                                  |     |

|      | and RMS-TM benchmark suites over the original sequential ver-                                                                                                                                       |     |

|      | sion of the benchmarks (vacation-low results were similar to                                                                                                                                        |     |

|      | vacation-high and hmmcalibrate were similar to hmmsearch                                                                                                                                            | l   |

|      | — both are omitted)                                                                                                                                                                                 | 136 |

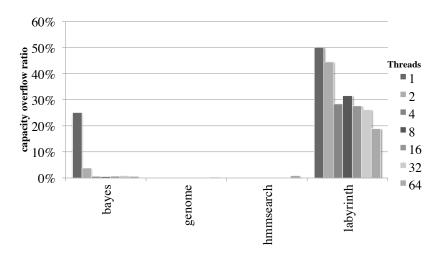

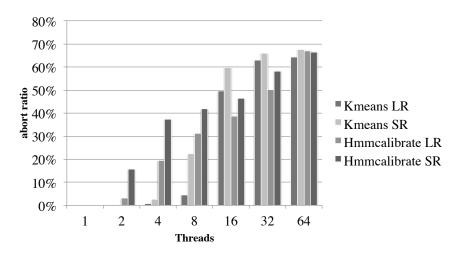

| A.5  | LR mode: ratio of total transactions aborted due to capacity overflow.                                                                                                                              | 137 |

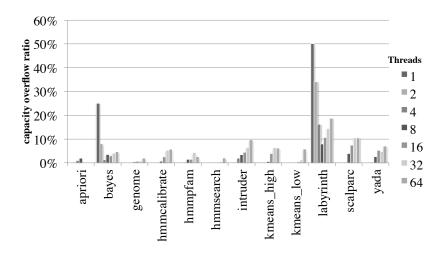

| A.6  | SR mode: ratio of total transactions aborted due to capacity overflow.                                                                                                                              | 137 |

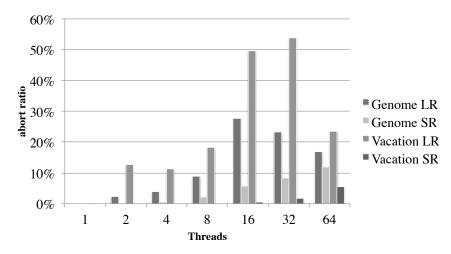

| A.7  | The abort ratio of genome and vacation                                                                                                                                                              | 139 |

| A.8  | The abort ratio of kmeans and calibrate                                                                                                                                                             | 140 |

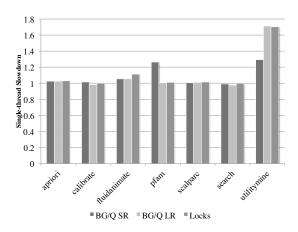

| A.9  | Single-thread slowdown of the RMS-TM benchmarks                                                                                                                                                     | 142 |

| A.10 | Single-thread slowdown of the STAMP benchmarks                                                                                                                                                      | 142 |

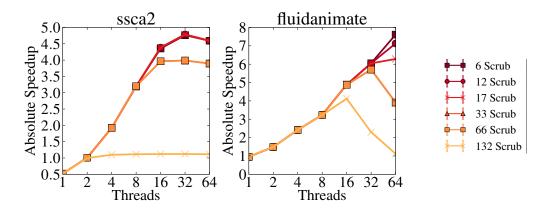

| A.11 | Effect of varying scrub intervals for ssca2and fluidanimate                                                                                                                                         | 149 |

# **List of Listings**

| 2.1 | Race Condition Demonstration           | 14 |

|-----|----------------------------------------|----|

| 2.2 | Race Condition Output                  | 15 |

| 2.3 | Pseudo Assembly of Race Condition loop | 15 |

| 2.4 | A TM pragma example                    | 25 |

# Chapter 1

# Introduction

For almost five decades computer architecture has followed a trend dubbed Moore's Law, under which the number of transistors in a computer processor has doubled roughly every two years [54]. For much of the lifetime of Moore's Law, gains in transistor counts were accompanied by increases to processor clock speeds leading to a long period in which software would be made faster purely though hardware improvements. In the last decade, however, frequency scaling slowed dramatically due to concerns about power usage and heat dissipation [12, 60]. While Moore's law has continued to dramatically increase the transistor count in microprocessors, the new transistors are being funnelled into multiple cores as opposed to the improvement of performance of a single monolithic core.

The transition from frequency-scaling to 'core-scaling' has necessitated that software begin to change — and become parallel — in order to exploit new generations of processors.

Parallel programming, however, has a reputation for being difficult. Paul E. McKenny divides the tasks a programmer faces when programming in parallel into four categories [51]:

- 1. **Work Partitioning:** This is the task of splitting the algorithm and its inputs into pieces that can be run in parallel across threads, processes or computers. This thesis discusses parallel *threads*, which are streams of execution that happen concurrently in the same memory space.

- 2. **Resource Partitioning & Replication:** This is the task of ensuring that the

required resources are partitioned or replicated for the parallel tasks to remove the requirement of access control.

- 3. **Interacting With Hardware** refers to the necessary understanding of the underlying hardware and it's limitations when programming in parallel. Depending on the model of parallel programming, this interaction ranges from a very small to very large fraction of the parallel programming task.

- 4. **Parallel Access Control**, which is required to avoid **race conditions** on shared resources. A race condition is an uncontrolled interleaving of parallel access to a shared resource, which is considered an error in most domains because the result being computed will vary on seemingly random timing fluctuations that change the interleaving of accesses occurring between threads<sup>1</sup>.

For the purposes of this thesis *shared-memory* machines are assumed. A shared-memory machine is a type of parallel architecture where all the processors working on a problem work in a shared address space, as opposed to distributed parallel computation where processors working in parallel do not share memory and, instead, must communicate explicitly through messages.

In a shared-memory machine, a *race-condition* interleaving typically involves **instructions accessing memory** across two or more threads in the machine. These race conditions are called *data races* and are discussed further in Section 2.1. Higher-level programming abstractions may also be subject to race-conditions, and thus semantically require similar parallel access control, however this thesis focuses on memory-level data races.

In order to avoid data races some form of control must be applied to shared resources. There are a number of synchronization primitives that can be used, however a *lock* is the most common [51]. Lock variables allow a single thread to declare ownership of a resource. While a lock is held, other threads attempting to acquire the same lock should either wait for the lock to become unlocked or proceed down an alternate path of execution that does not require access to the resource.

<sup>&</sup>lt;sup>1</sup>Algorithms can be created to be race-tolerant so that either races do not affect results or the results are acceptable even in the face of races. However, it is difficult to ensure that such algorithms are correct.

Lock-based programming has been successfully used for parallel programming, however, the paradigm does have some challenges:

- From the perspective of correctness, locks can be misused in such a way that progress can no longer be made. This failure condition is called a *deadlock*, and is caused by a cycle of lock dependencies created by two or more threads. In the simplest version of this situation two threads each hold a lock that the other thread requires for progress. Another related failure condition that also applies to a number of other programming systems is called *livelock*, which describes a situation where threads become looped in a cycle of actions without making progress.

- From the perspective of productivity, locks require large amounts of programmer effort to achieve maximum performance.

A pathology in lock-based programming is *lock contention*. This is when multiple threads require the same lock simultaneously to make progress. The other threads must simply wait to acquire the lock in order to proceed, because, by definition, only one thread can hold the lock. Lock contention can dramatically affect program performance if the contended lock is on the critical path. While lock contention can be inherent in an algorithm or data-structure, sometimes lock-contention can be the result of protecting too much data with the same lock. If multiple threads are waiting for the lock, but all the threads are to access different data, then the lock contention is spurious.

Figure 1.1 illustrates the problem with a hash-table that has a single lock. The accesses to be performed by fifteen threads are indicated by arrows pointing to the hashtable buckets. Of the fifteen accesses, all but three are to different buckets, and thus such accesses do not require synchronization. The bottom left part of the figure shows the resulting lock contention: all the threads wait to acquire the single lock. This is true even for threads that have independent accesses. The bottom right of Figure 1.1 shows how performance can be dramatically improved by locking only where conflicts can occur, as only three of the fifteen locking operations are *required*.

Figure 1.1: Lock Contention visualized on a hashtable. The accesses in green would produce spurious locking, but the accesses in red require some synchronization. White buckets are not accessed by any thread.

To work around spurious lock contention in a program, typically the single contended lock must be broken into multiple locks, each protecting a set of hash table buckets, in order to still guarantee safety. For example, if the contended lock is guarding access to a large array or hashtable, then *lock striping* could be applied to break the array or table into chunks, each guarded by its own lock [41]. Splitting locks must be carefully considered, however, because multiple locks combined with poor lock-discipline can introduce bugs that did not exist in the single-lock version of the algorithm.

From the perspective of performance, locks add computation and memory

accesses to memory locations that are not needed by the algorithm. These

accesses are a waste of resources and time in the absence of contention on the

data.

The difficulties imposed by deadlock and contention raise the burden of parallelization on the programmer. However, reducing the burden of parallelization is highly desirable because parallelization appears to be the main driver of future performance.

### 1.1 Transactional Memory

One proposed approach to parallelization with a reduced programming burden is called **Transactional Memory** (TM) [40].

Transactional Memory introduces a high-level construct called a *transaction*. A transaction is a region of code whose execution semantically cannot overlap with another transaction. A transaction must run in **isolation** from other transactions, must not be able to see partial results computed in another transaction, and must *commit* its results indivisibly (*atomically*) so that partial state cannot be seen.

Transactions are a higher-level construction in comparison with locks. Locks are akin to imperative programming, in that the user instructs the system **how** to achieve safe interleaving. In contrast TM programming is akin to declarative programming, where the user tells the system **what** is required for safe execution, leaving the actual mechanics to the system.

A side effect of this higher level of abstraction is that TM systems can provide improved performance by *optimistically* allowing execution to overlap. The TM system then can monitor the reads and writes performed by parallel executing transactions. Whenever a transaction attempts to execute an operation that would violate the isolation guaranteed offered by TM, one or more transactions can be *aborted*, and rolled-back to transaction start. A rollback resets the state of execution to what it was at the beginning of the transaction. Once the transaction has been rolled back, it may retry in hopes of succeeding on the next attempt, or it may switch to an alternate method of synchronization. This model is similar to database transactions, hence the name Transactional Memory.

First proposed in 1993 by Herlihy and Moss as a hardware modification, the idea has gained much popularity in the research community, which has been active in the area for the last 20 years [40]. In order to allow exploitation of TM for systems that already use locks, Transactional Lock Elision (TLE) can be used to replace lock pairs with transactions.

When discussing transactions, it is important sometimes to distinguish between the source code level transaction and an instance of a transaction at execution time. In this thesis I will refer to the the former, a region of code in the program text, as a *static transaction*. During program execution, a static transaction will likely be executed many times (*i.e.* being in a loop or function call), generating a unit of computation that must be executed in isolation and committed atomically. In this thesis I call this a *dynamic transaction*.

### 1.1.1 Software Transactional Memory

One of the popular pieces of TM research in the last two decades has been the exploration of Software Transactional Memory (STM) [66]. The promise of STM is to provide a high-level transactional construct on existing machines with no hardware changes. In STM systems the detection and rollback of conflicts is achieved through the use of a software library and the instrumentation of reads and writes in the program. This instrumentation can be done by the user, or automatically by an STM-aware compiler.

#### 1.1.2 Best-Effort Hardware Transactional Memory

One of the most recent developments<sup>2</sup> in the area of Transactional Memory has been the appearance of commercially available, user-accessible, Hardware Transactional Memory (HTM) systems.

While Transactional Memory was originally specified as a hardware feature, the cost of producing hardware has meant that TM research has been done through either Software Transactional Memory or through system simulators for HTM.

In the last two years three HTM systems have shipped: IBM's Blue Gene/Q, IBM zEC12 and Intel's Haswell-based processors [44, 45, 74]. In a short while, IBM will be shipping a third platform with TM support, the POWER8 processors [14]. One characteristic that these three systems share is that they are all 'Best-Effort' HTM systems (BE-HTM). Best-effort HTM means that they do not guarantee that any transaction may be completed speculatively [25]. This is a practical side effect of these being early HTM designs adapted to existing architectures. These machines all can store only limited amounts of speculative state, and will abort a transaction that exceeds that amount of speculative state. The architectures also restrict the state changes that may occur within a transaction to those that can be easily buffered, typically in one of the data caches or buffers.

### 1.2 Performance in TM systems

Transactional-Memory performance often depends on perspective. While creating a new transactional program, it would be unfair to not account for the productivity gains brought by the simpler synchronization model.

However, if one is considering converting an existing lock-based program to transactions as a way of improving performance, then comparing against the performance of the lock-based version is important. This thesis does not focus on comparing against different synchronization mechanisms so much as it focuses on performance among different transactional variants, and therefore the performance

<sup>&</sup>lt;sup>2</sup>Azul Systems shipped a version of their Vega processor with HTM several years ago, however it was deployed completely transparently to the user, and has not been widely evaluated in the research community.

study focuses on *absolute speedup*, *i.e.* ratio of wall-clock running time of the parallel implementation to the wall-clock running time of the fastest available sequential implementation.

In general, TM performance is dominated by two elements.

- TM systems can optimistically run, possibly conflicting, transactions speculatively in parallel. One component of transactional performance is what proportion of transactions that started have successfully committed, as opposed to aborting and rolling back to the starting point.

- 2. The overhead to set up and execute a transaction speculatively in a TM system is higher than that of a simple locking solution. This overhead comes from sources such as instrumentation in the Software Transactional Memory (STM) case, or from mechanisms required to provide forward progress in BE-HTMs. This overhead varies from system to system. It is relatively high hundreds of cycles for STM systems and BG/Q, and quite low tens of cycles for Intel Haswell, and zEC12.

A transaction that rarely, or never, aborts is an excellent candidate for TM in a comparison against a lock-based implementation that suffers from lock contention. However, if a TM is used to elide a lock that is never contended, then the TM overhead could turn this lock elision into a net loss.

On the other hand, a transaction that aborts in the majority of its attempts to execute could still be a net-gain, if the alternative is a lock-based version of the program where waiting on the lock dominates the execution time.

In general, it is speculation that is key to the promise of TM's productivity and performance. Speculation is the key to TM's productivity because it allows programmers to declaratively specify the synchronization required, with the system providing the actual safety guarantee. It is key to the performance of TM systems because successful speculations allow computation to proceed in spite of the *appearance* of required synchronization, even though unsuccessful speculation may waste execution cycles.

## 1.3 Programming Models and Forward Progress

There are two different programming paradigms for STM systems: user-instrumented and compiler-instrumented STM systems. While the former generally has better performance because it allows a skilled user to instrument only the required accesses for safety, the latter provides an excellent programming model. In a compiler-instrumented STM system, the user needs only to indicate to the compiler which regions of code cannot overlap in execution. Instrumentation is done automatically by the compiler, and forward progress is guaranteed by the runtime system.

An important question in STM systems is: When a conflict between two or more transactions occurs, what transaction(s) should be rolled back? The answer to this question has important consequences. An inappropriate answer can cause starvation — where a particular thread is unable to make progress; livelock — where the system as a whole is unable to make progress because it is trapped in a cycle of execution states; or simply poor performance. Attempts to answer this question in STM systems came to be known largely as the area of Contention Management, which explores policies, called contention managers, that decide which in-flight transactions to rollback [42]. Contention Management has been a rich area of research in STM systems.

An STM system with a correctly designed contention manager can always guarantee forward progress. For example, a contention manager that always ensures that the eldest transaction involved in a conflict is not aborted will trivially guarantee forward progress.

Forward progress is a very important property for TM systems because programming without it would be substantially more difficult, requiring the programmer to provide an alternate path that doesn't require a transaction, leading to an increased amount of code and maintenance burden.

## 1.4 Programming Models and Forward Progress for Besteffort HTMs

When programming for a best-effort HTM system there are different possibilities for programming models that can be provided to programmers. One of the most accessible programming models for programmers is a model that provides a high-level model similar to that of a compiler-instrumented STM.

In this programming model a user is only responsible for specifying the boundaries of a transaction. In order to avoid putting platform-dependent burdens on the programmer, this model allows transaction bodies to contain any code, including *irrevocable actions* or code that generate so much speculative state that the hardware will not be able to store such state.

Irrevocable actions are those that the system cannot rollback or buffer appropriately. For instance, executing a function that prints to a terminal is an irrevocable action: once the text appears on the terminal, the action cannot be undone. Irrevocable operations can take many forms, such as a reference to a memory-mapped I/O address that cannot reasonably be buffered, or system calls that cannot be rolled back.

To understand how useful it is to allow irrevocable actions inside a transaction, consider a program where an irrevocable operation that appears inside a transaction is only rarely executed at runtime: *e.g.* a warning message printed on an exceptional result.

The code is greatly simplified by allowing the irrevocable operation to appear within the transaction region. Allowing irrevocable operations inside a transaction is also a great advantage when legacy code is converted to transactions. An unpleasant alternative would be for the runtime to signal a fatal error upon encountering an irrevocable operation, or for the compiler to require no irrevocable actions statically. Either case would likely require significant programmer's effort to rewrite code to make it transactional.

Similarly the ability to specify transactions that require more speculative state than is available in the hardware allows the creation of TM applications that can be ported to other systems, even though its performance may be affected by the hardware limitations in the new system.

The freedom to specify transactions outside the limits of the hardware in a TM programming model improves programmability but puts the burden of providing forward-progress guarantee on the platform.

# 1.5 Non-speculative Serialization and the Serialization Manager

In a best-effort HTM system, a contention manager would not suffice to provide a forward-progress guarantee. The nature of a best-effort HTM means that a strategy similar to STM cannot always ensure forward progress because when a transactional execution failure occurs in a best-effort HTM, there is no guarantee that any of the aborted transactions may be able to continue execution. For instance, consider a capacity-limited transaction, *i.e.* a transaction that creates more speculative state than the hardware can store. No matter which conflict-resolution policy the contention manager uses, forward progress will never occur without additional action from the system. Therefore the only failure-proof way to guarantee forward progress is to execute such a transaction non-speculatively.

*Non-speculative serialization* is a technique that allows a transaction to safely run non-speculatively if the transaction is deemed unable to succeed in a hardware transaction. It is called *serialization* because, to avoid a failure of isolation semantics, there is at most one non-speculative transaction running at any moment. Concurrent speculative transactions may not commit until after the non-speculative transaction completes<sup>3</sup>.

Though non-speculative serialization has been described before, there has been very little discussion of how to decide **when** non-speculative serialization is to occur. Most previous publications that discuss non-speculative serialization for forward progress use a simple policy that limits retries to some maximum value [78].

This thesis introduces the concept of a *serialization manager* as the BE-HTM counterpart to the STM contention manager. Similar to the specification of contention managers, serialization managers separate the responsibility for forward-progress from the responsibility for correctness. The serialization manager is the policy, along

<sup>&</sup>lt;sup>3</sup>Non-speculative serialization assumes that all threads accessing shared data structures use transactions. Non-speculative serialization will not match the hardware isolation semantics should there be a thread not using transactions when writing shared-data, as that non-speculative thread is invisible to the TM system and cannot be held-back while the transaction executes. This could be fixed at great cost by serializing the whole system, however the proportional response is to consider this case a programming error.

with any required state, that decides, when a transaction aborts, if the aborted transaction should be retried speculatively or if non-speculative serialization is required.

## 1.6 Serialization-Manager-Driven Performance

Improved STM Contention Management can improve program performance by making better decisions about what transactions to abort when conflicts occur [42]. This thesis argues that improved Serialization Management may also be able to improve BE-HTM performance because serialization<sup>4</sup> forms a key safety net in the face of high contention. The thesis also argues that better decisions about when to serialize can improve performance while guaranteeing forward-progress.

A key tension in a serialization manager design is the tradeoff between forward progress and speculation. An upper bound on execution time would be desirable to prevent inefficient use of resources and lots of wasted work. However, such upper bound comes at a cost because performance in a BE-HTM system is rooted in speculation. Enforcing the upper bound may eliminate beneficial speculation. If the upper bound is too high the program wastes work. If it is too low the overzealous serialization manager eliminates too much speculative execution.

This thesis presents six new serialization managers — and one that has been the default used in previous explorations of non-speculative serialization — along with the first through exploration of Serialization Management in the literature. The evaluation explores a large number of values for each parameter of each manager on a TM architecture that has two different modes, each having different conflict-detection granularity and access latencies. These two modes are considered for the purposes of this thesis to be two different, though closely related, platforms for TM. This TM implementation was the first commercially available offering of HTM, introduced by IBM, and equipped the IBM BG/Q machine — a machine that was the top-performing computer in the world circa 2013. The thorough evaluation of these serialization managers, along with their tuning on multiple platforms, provides insight into the amount, and type, of control afforded to a serialization manager.

$<sup>^4</sup>$ For the remainder of this thesis we will use the terms serialization and non-speculative serialization interchangeably.

The remainder of this thesis is structured as follows:

**Chapter 2** provides more background on race conditions, Transactional Memory and the experimental platform for this thesis, Blue Gene/Q.

**Chapter 3** discusses the problem further, generating some smaller research questions to help guide the study. Once the research questions are established, the research methodology is described.

**Chapter 4** introduces a tool that was designed and built to help explore questions around serialization.

**Chapter 5** introduces the serialization managers.

**Chapter 6** introduces a pair of modifications that can be made to all serialization managers, and evaluates them on the MaxRetry manager, before recommending they both be adopted for all serialization managers.

**Chapter 7** evaluates the new serialization managers across parameter values for those managers that have parameters.

**Chapter 8** contains the experimental results, where our research questions are answered.

**Chapter 9** discusses related work.

**Chapter 10** discusses some limitations to the thesis.

**Chapter 11** discusses directions for future work.

Chapter 12 concludes the thesis.

The thesis relies heavily on the contents of *Software Support and Evaluation of Hardware Transactional Memory on Blue Gene/Q* for background. For ease of reference I have included it as Appendix A.

# Chapter 2

# Background

This chapter provides background on race conditions, Transactional Memory and the Blue Gene/Q's Transactional Memory system to support the reader through the rest of the thesis.

#### 2.1 Race Conditions

A race condition is an uncontrolled interleaving of accesses to a shared resource, where at least one of the accesses modifies the shared resource. In this thesis the interleaving discussed is between instructions accessing memory in a shared-memory machine that has more than one processor. Shared-memory race conditions can be classified as Read-after-Write (RAW), Write-after-Write (WAW) or Write-after-Read (WAR).

#### **Listing 2.1: Race Condition Demonstration**

```

int main(int argc, char** argv) {

int iterations = atoi(argv[1]);

printf("Running with %d iterations\n",iterations);

int counter = 0;

#pragma omp parallel for

for (int i=0; i < iterations; i++) {

counter = counter+1; // Racy Update

}

printf("%s: Counter is %d, expected %d\n",

counter == iterations ? "PASSED" : " FAILED",

counter,

iterations);

}</pre>

```

Listing 2.1 shows a simple program that suffers from a data race that may cause updates to the variable counter to be lost, leading to a mismatch between the expected and actual value in the output of the program, contained in Listing 2.2.

#### **Listing 2.2: Race Condition Output**

```

> g++ -fopenmp race_condition.c -o race

> OMP_NUM_THREADS=1 ./race 90000000

Running with 90000000 iterations

PASSED: Counter is 90000000, expected 90000000

> OMP_NUM_THREADS=2 ./race 90000000

Running with 90000000 iterations

FAILED: Counter is 50095286, expected 90000000

```

To show in more detail how this race affects the values computed by the program, Listing 2.3 contains a pseudo-assembly of the loop body that contains the race condition. Figure 2.1 shows an interleaving of instructions between two threads where the update intended by Thread 1 is lost. An update was lost because both threads loaded, incremented, and stored the same value, a WAW race.

#### Listing 2.3: Pseudo Assembly of Race Condition loop

```

/* Initialize variables */

[counter], 0

ST

R0,0 /* R0 will be the loop variable i */

L:

R1, [counter]

LD

ADD

R1,1

[counter],R1

ST

ADD

R0,1

R0, [iterations]

CMP

BEQ

L

. . .

```

Figure 2.1: Snippet of execution showing a data race with lost updates.

```

(a) Thread 1

(b) Thread 2

T1: LD

R1, [counter]

T1:

T2:

T2: LD

R1, [counter]

T3: ADD

R1,1

T3: ADD

R1,1

[counter],R1

T4: ST

T4:

T5: ST

[counter],R1

T5:

```

## **2.2** Transactional Memory

Transactional processing has existed for a long time, with one of the earliest widely deployed examples being the SABRE airline reservation system of the early 1960s [9]. Since SABRE the area has gone through much evolution, with large amounts of formalization driven by the development and evolution of relational databases.

Part of the formalization of relational databases was the description of four properties to guarantee consistent processing of transactions: Atomicity, Consistency, Isolation and Durability, known as ACID [34, 35, 37].

**Atomicity** A transaction is atomic if the changes it makes to storage appear to happen indivisibly: either all the changes must be seen at once, or none of the changes can be seen.

**Consistency** The system remains consistent after the execution of a transaction. If a transaction would leave the system in an inconsistent state, then the transaction is not allowed to complete. For instance, a transaction that changes a set of records in a database must appropriately change all required records.

**Isolation** Transactional isolation is the inability of any component of the system to see partial results from an in-progress transaction. Isolation is a key part of proving consistency because, without isolation, invalid results could be produced by using invalid temporary results produced during the execution of a transaction.

**Durability** Once a transaction commits the results are preserved even in the event of a system crash.

As can be seen from the D in the ACID definitions, historically transaction processing has referred to persistent data, mostly stored in files on hard drives and tapes. The first three properties — Atomicity, Consistency and Isolation — are powerful concepts and were adapted to transient storage and parallel programming.

Though atomic updates for single variables had existed in various forms in computer architecture (such as Compare-and-Swap, Test-and-Set, or Load-linked/Store

Conditional) previously, the Oklahoma Update<sup>1</sup> was different in providing a form of atomic updates to multiple values [73]. In an example of independent discovery, Herlihy and Moss described *Transactional Memory* at almost the same time, differing from the Oklahoma Update mostly in implementation and terminology [40].

Herlihy and Moss' description of Transactional Memory has been more persistent than the Oklahoma update. Herlihy and Moss added six instructions to an architecture's ISA: Load-transactional (LT) that loads a memory location and marks the location as transactionally read, Load-transactional-exclusive (LTX) that loads a memory location marking it as read and hinting that it will be updated, Store-transactional (ST) that writes speculatively to a location, Commit (Commit) that commits a transaction if all the values written and read are still valid. In addition, the Herlihy and Moss paper also added two instructions that are less important for our discussion here: Abort (Abort) that discards transactional state, and Validate (Validate) that tests whether or not the currently executing transaction's read- and write-sets are valid, aborting if not. A transaction is implicitly started at the first transactional access and continues until Commit, Abort or a failed Validate.

Similar to Compare-and-Swap, a transaction can fail if another thread has altered any of the values in the read set or the write set while the transaction is in flight. In Herlihy's and Moss' paper validation occurs on the execution of a Commit instruction that can return TRUE, if the transaction is committed, or FALSE if the transaction commit failed and the speculative state has been discarded. If a transaction fails it is up to the programmer to handle this case, either retrying or choosing an alternate method of synchronization.

Both the Oklahoma Update and Herlihy's Transactional Memory provide Atomicity, Consistency and Isolation<sup>2</sup> to those values loaded and stored transactionally.

Though the advantage of transaction-inspired parallel programming could be seen, both the Oklahoma Update and Transactional Memory were specified as hardware features. Hardware being both complicated and expensive to build meant that research

<sup>&</sup>lt;sup>1</sup>Referring to the song *All 'Er Nuthing* from the musical *Oklahoma!*

<sup>&</sup>lt;sup>2</sup>To be precise, the Oklahoma Update does not provide Isolation because the authors describe a situation under which a failed update could lead to variables becoming inaccessible. However, the authors also sketch a fault-tolerance system that can work around this situation and provide isolation.

on Hardware Transactional Memory work was done on hardware simulators until much later.

#### 2.2.1 Software Transactional Memory

However, Transactional Memory was not forgotten. Effort simply moved towards providing the transactional memory paradigm using software, leading to the research area of Software Transactional Memory (STM), which has remained active to this day [66]. The goal of STM systems is to provide the transactional programming model on un-modified hardware by using a runtime system and instrumentation of reads and writes, done either by an STM compiler or by the user. An example of instrumentation is contained in Figure 2.2.

Figure 2.2: An example of STM instrumentation

Software Transactional Memory has followed its own evolution, and has introduced a number of concepts and design dimensions. One addition to the TM model was the idea of guaranteed forward progress. This addition meant that programmers no longer had to handle the case where the transaction aborted explicitly — rather the STM system would deal with retry and guarantee that the system would eventually commit every transaction.

One dimension in STM designs is the distinction between *strongly atomic* and *weakly atomic* STMs. This distinction refers to the STM system's guarantees regarding non-transactional access to memory locations in the read sets and write sets of inflight transactions [10].<sup>3</sup> A strongly atomic STM system acts like Herlihy's and Moss' TM design: a non-transactional access causes a transaction to abort if the transaction

<sup>&</sup>lt;sup>3</sup>Blundell *et al.* argue that the programming-language research area has historically used the term Atomicity to refer to what would be known in databases as Atomicity and Isolation. Thus, while the strong vs weak atomicity dichotomy appears to be an isolation issue, the name is nevertheless appropriate.

has the accessed location in its read set or write set. A weakly atomic STM system does not specify what occurs when there is a non-transactional access to a transactionally tracked location — typically the argument in defence of weakly atomic STMs is that the existence of such an access is a programming error.

Strongly atomic STM systems make it easier to interact with non-transactional code by ensuring that the TM execution remains correct in the face of conflict with non-transactional code. However, strong-atomicity increases the overhead incurred by a TM system. As a result, most high-performance STM systems are weakly atomic.

One of the keys to STM performance is the notion of *privatization*, which is the ability to have non-instrumented accesses inside a transaction. Privatization is important because instrumentation in an STM is costly in comparison to normal memory accesses. Privatized accesses are a powerful performance tool. However, they are difficult for an STM compiler to achieve and also STM programmers find it difficult to use them correctly.

The combination of automatic (or no) privatization and instrumentation creates a very simple programming model for transactions, as in Figure 2.2(b), where the programmer indicates the scope of the transaction, the contents are executed in isolation and the results are committed atomically. This programming model has been empirically validated as easier than locks for novice parallel programmers [61].

Though STM has existed for almost twenty years now, it has produced relatively little impact on day-to-day programming. A number of challenges faced by STM systems have prevented broad adoption. The instrumentation and the computation required for conflict detection introduce overhead, in STM systems, causes some concern about performance [17]. As well, interaction with non-transactional code and non-transactional libraries and kernels can be complicated depending on the atomicity model and guarantees provided by the TM system [10, 17, 24]. Efforts continue to improve STM performance through new TM systems such as SwissTM. Other efforts aim at shoring up the guarantees provided by TM systems through improved sandboxing and further investigation of strongly-atomic STM systems [8, 24, 29].

#### **Contention Managers**

The contention manager is the software component in a Software Transactional Memory system responsible for determining, when a conflict occurs, what subset of transactions need to be aborted. Contention management was first proposed by Herlihy *et al.* as a generic interface to guarantee progress in transactional systems [42]. One of the key concepts behind their original specification of contention managers was that the responsibility for correctness, and for forward progress, ought to be kept separate.

There has been a substantial amount of work done in this area because Contention Management can change the performance of STM systems [3, 43, 64, 70].

More recently, there have been a number of efforts surrounding Transactional Scheduling, a technique that takes a slightly different approach to forward-progress and performance [28,56,79]. Where contention managers control what occurs when conflicts are detected, Transactional Schedulers attempt to proactively avoid conflicts by delaying or moving transactions to avoid interleavings expected to conflict.

### 2.2.2 Hardware Transactional Memory

HTM research initially was limited to the development of system simulators due to the cost of implementing new designs in real silicon. These HTM simulators range vastly in capability and structure, from very limited forms of TM similar to the original Herlihy and Moss proposal all the way to unbounded HTM systems that allow arbitrary transaction sizes by allowing conflict detection at much higher levels in the memory-hierarchy: from evicted cache lines to swapped out pages [1, 55, 67].

In the last five years Hardware Transactional Memory has begun to appear outside of simulators. The first implementation was by Azul Systems, though it was not broadly described outside of a presentation and some patents, and was only used for Transactional Lock Elision in Java [21]. The next implementation was to be Sun's Rock processor, which was cancelled before it became commercially available, though not before some research into its HTM facilities [26].

IBM's Blue Gene/Q was the first commercially available HTM available. It is on this HTM that we based our study. Further details on the implementation of HTM in the BG/Q appear in Section 2.3 and Appendix A. IBM has since produced two more HTM implementations, one on zEC12, the current mainframe processor, and one on the upcoming POWER8 processor [14, 45]. Intel has also shipped an HTM implementation called 'Restricted Transactional Memory' (RTM) in its Haswell micro-architecture [44].

All existing HTM systems are strongly-atomic. In contrast to the original specification by Herlihy and Moss, all existing HTM systems provide a Begin instruction to start a transactional region. Within the transactional region *all* loads and stores are transactional, similar to the STM compiler programming model. Only zEC12 supports limited privatization in the form of a *Non-transactional Store instruction*

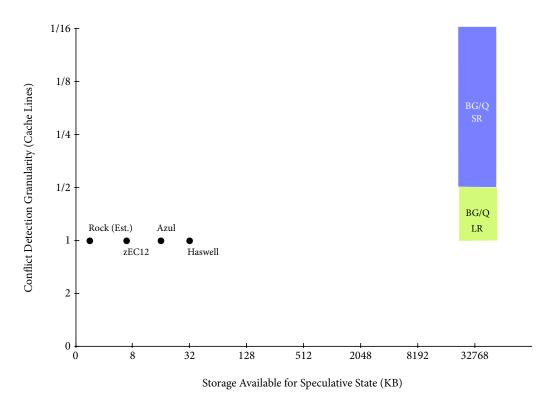

Figure 2.3: A rough summary of existing TM systems in the TM design space. This graphic does not address the additional dimensions of TM induced memory latency or TM overheads.

Figure 2.3 positions the existing TM systems on two dimensions of the design space: conflict-detection granularity and amount of storage available for speculative state. The conflict-detection granularity refers to how close together two accesses from different threads may be before the hardware signals a *false conflict* — a conflict

that is not present in the actual application but that occurs in the HTM because of the inability of the hardware to determine that two referenced locations are not the same location. In an ideal system there would be no false conflicts. However, in most HTM systems the conflict-detection granularity is some fraction of the cache-line size because this detection uses existing data caches. The storable speculative state in Figure 2.3 is the maximum space that can be occupied by data written by speculative writes.

The two shaded areas for BG/Q in Figure 2.3 indicate the ranges of conflict-detection granularity are a side effect of a configuration parameter supported by BG/Q, the *running-mode*. The running mode changes the behaviour of the TM system to favour either short-running or long-running transactions. The running modes of BG/Q are discussed in more detail in Section 2.3.1, but in brief the *long-running mode* (BG/Q LR in Figure 2.3) reduces the latency — the time it takes a cache to serve a request — of accesses within a transaction at the cost of affecting cache locality across transactions, while the *short running mode* (BG/Q SR in Figure 2.3) preserves locality across transactions at the cost of increased latency within transactions.

Latency is just one dimension not addressed by Figure 2.3. Other design parameters that are not included in the figure include when conflicts are detected or signalled (this can be either at the point where the conflict occurs, or when the transaction attempts to commit) and the overhead of the TM system and the code required to provide a forward-progress guarantee.

## 2.3 Blue Gene/Q

IBM's Blue Gene/Q is a supercomputing solution designed for the solution of petascale computational problems [39]. The core of the Blue Gene/Q system is the *compute node* consisting of a 1.6 GHz POWER A2 chip with 16 GB of memory running the Compute Node Kernel (CNK) [32]. These compute nodes are combined together in larger groupings to form the total Blue Gene/Q supercomputing system.

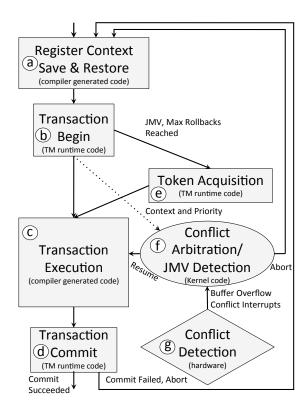

Blue Gene/Q shipped with a Transactional-Memory programming system that

functions within a single compute node<sup>4</sup>. Blue Gene/Q's TM support is implemented in four layers, shown in Figure 2.4, and described below.

Figure 2.4: BG/Q Transactional Memory Stack

### 2.3.1 Hardware Support

Each BG/Q compute node has 16 user-accessible POWER A2 cores, and each core has 16K of private L1 cache that is 8-way set-associative, with 64-byte cache lines. The cores all share a 32MB L2 cache that is 16-way set associative.

BG/Q's TM support is implemented in the L2 cache, which has been modified to be *multi-versioned* so that it can store multiple versions of the same physical line. Each version occupies a different L2 way [57]. By default (and in all our experimentation) six of the sixteen sets are reserved for holding non-speculative state. In this configuration the hardware guarantees that speculatively written ways lines will not be evicted by non-speculative writes<sup>5</sup>. The hardware supports *sandboxing* that allows hardware exceptions and access to memory-mapped I/O to be trapped and reduced to a transaction abort.

Transactions are identified by one of 128 Speculation IDs that form part of the cache tag. These Speculation IDs are managed by the L2 cache, which must reclaim

<sup>&</sup>lt;sup>4</sup>Across-node synchronization must therefore be achieved with a different method.

<sup>&</sup>lt;sup>5</sup>The hardware can be configured to allow speculative writes into up to 15 of 16 ways, however, if less than six ways are reserved for non-speculative state then non-speculative ways may evict speculatively written ways, aborting the corresponding transactions

them by walking the cache contents. The reclamation process, called *ID scrubbing*, happens at a fixed interval. Therefore the starting of a transaction may have to wait for a Speculation ID to be reclaimed. Reclamation occurs when all the lines marked with a Speculation ID are marked as invalid, or are merged into the non-speculative state.

When the cache directory finds that two transactions have conflicted, it updates the *conflict register*, a status register for the current associated Speculation ID, and triggers an interrupt that is handled by the kernel. The conflict register contains a status bit to indicate if the transaction failed because it would have required evicting a speculative line — called the capacity bit – and a bit that indicates if there was one, or multiple. conflicting transactions. If there are conflicting transactions, the Speculation ID of the conflicting transaction is also available in the conflict register.<sup>6</sup>

Only memory state is tracked transactionally. Thus, support to restore register values must be provided through compiler-generated code for register save and restore.

The L1 cache is unmodified from a standard A2 core. Thus BG/Q supports two transactional execution modes that change how the L1 cache is handled in order to correctly track speculative state:

Short-running mode evicts speculatively written lines from the L1, forcing subsequent reads and writes to go to the L2 cache. Short-running mode is named so because it preserves the contents of the L1 cache across transactions, at the cost of extra read-after-write latency inside the transaction — therefore this mode is suitable for short-running transactions.