# SiC JFET dc characteristics under extremely high ambient temperatures

Tsuyoshi Funaki,<sup>1a)</sup> Juan C. Balda,<sup>3</sup> Jeremy Junghans,<sup>3</sup> Avinash S. Kashyap,<sup>3</sup> Fred D. Barlow,<sup>3</sup> H. Alan Mantooth,<sup>3</sup> Tsunenobu Kimoto,<sup>2</sup> and Takashi Hikihara<sup>1</sup>

<sup>1</sup> Kyoto University, Dept. of Electrical Eng.

<sup>2</sup> *Kyoto University, Dept. of Electronic Science and Eng.*

Graduate school of Engineering, Katsura, Kyoto, 615-8510, Japan

<sup>3</sup> University of Arkansas, Dept. of Electrical Eng.

3217 Bell Engr. Center, Fayetteville, AR 72701, USA

a) funaki@kuee.kyoto-u.ac.jp

**Abstract:** This paper reports on the measured dc characteristics of a SiC JFET device from room temperature up to 450°C in order to evaluate the device's capability for high-temperature operation. The authors packaged SiC JFET bare die into a dedicated high-temperature package to be able to perform experiments under extremely high ambient temperatures. The experimental results show that the device can operate at 450°C, which is impossible for conventional Si devices, but the current capability of the SiC JFET diminishes with rising temperatures. For example, the saturation current becomes 20% at 450°C with respect to the value at the room temperature.

**Keywords:** SiC, JFET, high temperature operation, 450°C, packaging

**Classification:** Electron devices

#### References

- J. L. Hudgins et al., "An Assessment of Wide Bandgap Semiconductors for Power Devices," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 907– 914, 2003.

- M. Lades, "Modeling and Simulation of Wide Bandgap Semiconductor Devices: 4H/6H-SiC," Select. Topics Electron. Micromech., vol. 3, Shaker Verlag, Aachen, 2002.

- [3] A. Hefner et al., "SiC Power Diodes Provide Breakthrough Performance for a Wide Range of Applications," *IEEE Trans. Power Electron.*, vol. 16, no. 2, pp. 273–280, 2001.

- [4] P. Friedrichs et al., "Static and Dynamic Characteristics of 4H-SiC JFETs Designed for Different Blocking Categories," *Mater. Sci. Forum*, vol. 338-342, pp. 1243–1246, 2000.

- [5] P. Friedrichs et al., "Application-Oriented Unipolar Switching SiC Devices," *Mater. Sci. Forum*, vol. 389-393, pp. 1185–1190, 2000.

[6] B. Ray and R. L. Spyker, "High Temperature Design and Testing of a DC-DC Power Converter with Si and SiC Devices," 39th IEEE IAS Annual Meeting, #33p5, Seattle, Oct. 3-7, 2004.

### **1** Introduction

Silicon Carbide (SiC) has several superior characteristics when used as a semiconductor material [1, 2, 3]. In particular, SiC semiconductor devices are expected to have high temperature, high speed and high voltage operation capabilities, which are attributed to the wide bandgap of SiC, and cannot be obtained with conventional Si-based semiconductor devices. This paper focuses on the high temperature operation capability of SiC devices. Although it has been mentioned that SiC semiconductor devices are suitable for high temperature operation, there are few reports on relatively high temperature operation of SiC devices (i.e.,  $< 250^{\circ}$ C) [4]. Furthermore, there has been no report on the operation of gate controllable devices such as JFETs at extremely high ambient temperatures. The main reasons are that the SiC JFET is under development and the difficulty in packaging the device for high temperature operation. The latter requires not only that the SiC JFET bare dies be capable of operation at high temperatures, but also the package including the die attach and wire bonds. To this end, the authors mounted the SiC JFET supplied by SiCED [5, 6] in a dedicated thermally stable package. The dc characteristics of the SiC JFET under extremely high ambient temperature conditions up to 450°C were evaluated using an automated experimental setup for high temperature measurements.

# 2 Specification of the SiC JFET, Package and Measurement Setup

A SiC device can with stand high temperatures because of its material characteristics but it cannot form part of a circuit by itself without packaging that must be suitable for high temperature. The SiC JFET used in the experiments was supplied by SiCED, which was a research sample bare die. The JFET, usually supplied as a cascode device with a Si MOSFET and packaged in the general plastic IXYS i4 package, has a vertical device topology and 2.8 mm<sup>2</sup> surface area with rated 2.5 A drain current and 1200 V blocking voltage. The authors mounted the JFET bare die on a Ni plated JEDEC TO-258 package to allow high temperature operation. The die has Ni or Al based ohmic terminal contacts and metallization on its top surface. The drain terminal is the backside of the die with a final metallization layer consisting of Ni. This drain contact was bonded to the package. The source and gate have 3  $\mu$ m Al metallization and were wire bonded to the terminal of package with 3 mil Al wire.

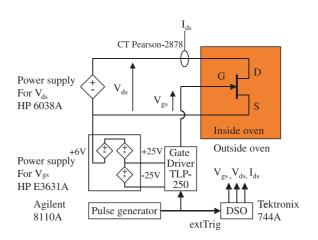

Figure 1 shows the experimental setup for measuring temperature dependency of the SiC JFET dc characteristics. All of the equipment and power

**Fig. 1.** Experimental setup for characterization of the SiC JFET.

supplies to the device are controlled by a PC with LabView and an IEEE-488 (GPIB) link. The measurements were performed automatically and the data were collected and processed by the PC. There are two power sources; one is used to supply the drain-source voltage (V<sub>ds</sub>) and the other is used to supply the gate–source voltage (V<sub>gs</sub>). V<sub>ds</sub> is swept from 0 V to 20 V to the respective V<sub>gs</sub>, and V<sub>gs</sub> was changed as the parameter. The power supply for V<sub>gs</sub> outputs two level voltages, the higher one is used for the parameter of V<sub>gs</sub>, and the lower voltage is used to off the JFET. A pulse generator can produce arbitrary width gate pulses and is set to 40  $\mu$ s to prevent self heating up of the device by conduction current. A digital storage oscilloscope is triggered by the gate signal produced by the pulse generator and performs data acquisition. The PC executes part of the numerical processing and data storage. The control procedures of the instruments in measuring device behaviors and in extracting parameters for the device model are programmed with LabView.

#### 3 JFET dc characteristics for high ambient temperatures

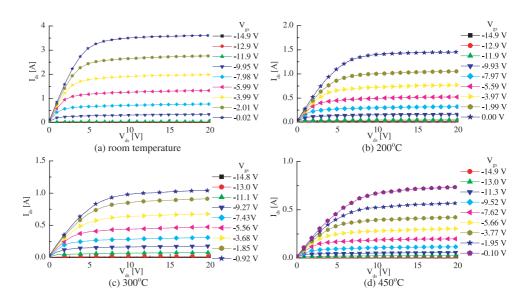

Figure 2 illustrates the I<sub>ds</sub>-V<sub>ds</sub> characteristics of a SiC JFET with the gate voltage V<sub>gs</sub> as a parameter at room, 200°C, 300°C and 450°C ambient temperatures, respectively. Fig. 2 (a) illustrates that the SiC JFET has pentodelike dc characteristics at room temperature. The threshold gate voltage is approximately V<sub>gs</sub> = -12 V, the saturation current for V<sub>gs</sub> = 0 V is about 3.5 A, and a drain-source resistance of approximately  $1.33 \Omega(\sim 37 \text{ m}\Omega \cdot \text{cm}^2)$ . Fig. 2 (b) and (c) shows the threshold gate voltage becomes approximately V<sub>gs</sub> = -13 V at 200°C and V<sub>gs</sub> = -14 V at 300°C, respectively. Fig. 2 (d) shows the dc characteristics when the ambient temperature is extremely high at 450°C, which is beyond the temperature capability of Si-based devices (i.e.,  $175^{\circ}$ C). The pentode-like characteristics of the SiC JFET slightly change to triode-like characteristics and the pinch off drain voltage at V<sub>gs</sub> = 0 V becomes unclear. The saturation current becomes 0.7 A, which is 20% of that at room temperature and the drain-source resistance increases to 10.0  $\Omega$  in

Fig. 2. DC characteristics of the SiC JFET as function of  $V_{gs}$ .

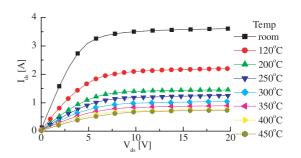

Fig. 3. Temperature dependency of the dc characteristics of the SiC JFET for  $V_{gs} = 0 V$ .

the linear region for  $V_{gs} = 0 V$ . The threshold gate voltage becomes slightly more negative to  $V_{gs} = -15 V$ .

Figure 3 shows the dc characteristics at  $V_{gs} = 0 V$  for different ambient temperatures. The saturation current decreases in accordance with increasing temperatures; such as 3.5 A at room temperature, 2.2 A at 120°C, 1.4 A at 200°C, 1.0 A at 300°C, and so on. The current reduction becomes smaller at high ambient temperatures. These results indicate that the JFET must be used with the rated current of 0.7 A when operated at 450°C. This figure also indicates that the voltage drop between the drain and source for an operation of 0.5 A changes from 0.7 V at room temperature to 6 V at 450°C leading to conduction losses at 450°C 10 times greater than those at room temperature. However, operation at these high temperatures for Si devices is impossible. The JFET does not require change of gate control since the threshold gate voltage changes by only a few volts, thus it is easy to use in high temperature applications.

## 4 Conclusion

This paper investigated the characteristics of a SiC JFET under ambient temperature conditions from room temperature up to 450°C confirming its normal operation. The conventional plastic package cannot be exposed to such high temperatures; therefore the authors packaged the SiC JFET bare die into a thermally stable package. The packaged JFETs were evaluated at the wide ambient temperature range of operation. The measured dc characteristic results indicated that the available current ratings of the SiC JFET decrease with increasing temperatures. The current rating becomes 20% at 450°C with respect to that at room temperature. The threshold gate voltage changes slightly lower with increasing the temperature. However, it can be easily managed by offsetting the gate voltage a few volts higher (negative direction). The ability of extremely high temperature operation shown in this paper indicates that SiC devices hold promise for many applications.

# Acknowledgments

One of the authors [T.F.] received support for this research from Kyoto University Venture Business Laboratory. This research was partially supported by the 21st Century COE Program 14213201 (Japan). The authors acknowledge the SiC JFET device supplied by Dr. P. Friedrichs (SiCED) and the experimental facilities by Dr. A. Lostetter (Arkansas Power Electronics International, Inc.). The authors from the University of Arkansas also acknowledge the support from the Office of Naval Research under Award No. N00014-04-1-0603 and the National Science Foundation under Award No. ECS-0424411.