Open access • Proceedings Article • DOI:10.1109/ISCAS.1999.780127

## Signal waveform characterization in RLC trees — Source link []

Yehea Ismail, Eby G. Friedman, Jose L. Neves

Institutions: University of Rochester

Published on: 30 May 1999 - International Symposium on Circuits and Systems

Topics: Elmore delay, RC circuit and RLC circuit

### Related papers:

- Elmore model for energy estimation in RC trees

- RLC Interconnect Delay with Temperature Distribution Effects

- Delay Models for MCM Interconnects When Response

- A new RLC buffer insertion algorithm

- Coupling Aware Explicit Delay Metric for On- Chip RLC Interconnect for Ramp input

# Signal Waveform Characterization in *RLC* Trees

Yehea I. Ismail, Eby G. Friedman, and Jose L. Neves<sup>1</sup>

Department of Electrical and Computer Engineering University of Rochester Rochester, New York 14627

Abstract - Closed form solutions for the 50% delay, rise time, overshoot characteristics, and settling time of signals in an *RLC* tree are presented. These solutions have the same accuracy characteristics as the Elmore delay for *RC* trees and preserves the simplicity and recursive characteristics of the Elmore delay. The solutions introduced here cover all damping conditions of an *RLC* circuit including the underdamped response, which is not considered by the Elmore delay due to the non-monotone nature of the response. Also, the solutions have significantly improved accuracy compared to the Elmore delay for an overdamped response. The solutions introduced here for *RLC* trees can be practically used for the same application that the Elmore delay is used in *RC* trees.

#### I. Introduction

It has become well accepted that interconnect delay dominates gate delay in current deep submicrometer VLSI circuits [1]-[9]. With the continuous scaling of technology and increased die area, this situation is expected to become worse. In order to properly design complex circuits, more accurate interconnect models and signal propagation characterization are required. Initially, interconnect has been modeled as a single lumped capacitance in the analysis of the performance of on-chip interconnects. Currently, RC models are used for high resistance nets and capacitive models are used for low resistance interconnect [10], [11]. However, inductance is becoming more important with faster on-chip rise times and longer wire lengths. Wide wires are frequently encountered in clock distribution networks and in upper metal layers. These wires are low resistive wires that can exhibit significant inductive effects. Furthermore, performance requirements are pushing the introduction of new materials for low resistance interconnect [12]. Inductance is therefore becoming an integral element in VLSI design methodologies, see e.g., [6], [13], [14].

An interconnect line in a VLSI circuit is in general a tree rather than a single line. Thus, the process of characterizing signal waveforms in tree structured interconnect is of primary importance. One of the more popular delay models used within industry for RC trees is the Elmore delay model [15], [16]. Despite not being highly accurate, the Elmore delay is widely used by industry for fast delay estimation. With IC's composed of tens of millions of gates it is impractical to use time consuming methods to accurately evaluate the delay at each node in the circuit. The Elmore delay model is therefore used to quickly estimate the relative delays of different paths in the circuit, permitting more exhaustive simulations to be performed for only the critical paths. Also, the Elmore delay is widely used as a delay model for the synthesis of VLSI circuits such as buffer insertion in RC trees and wire sizing [17]-[28]. The wide use of the Elmore delay as a basis for VLSI design methodologies is primarily because the Elmore delay has a high degree of *fidelity* [17]: an optimal or near-optimal solution reached by a design methodology

This research was supported in part by the National Science Foundation under Grant No. MIP-9610108, a grant from the New York State Science and Technology Foundation to the Center for Advanced Technology - Electronic Imaging Systems, and by grants from the Xerox Corporation, IBM Corporation, and Intel Corporation. <sup>1</sup>IBM Microelectronics 1580 Route 52 East Fishkill, New York 12533

based on the Elmore delay is also near-optimal based on a more accurate (*e.g.*, SPICE-computed [24]) delay for routing constructions [25] and wire sizing optimizations [23]. Simulations [26] have shown that the clock skew derived under the Elmore delay model has a high correlation with SPICE-derived skew data.

The popularity of the Elmore delay is primarily due to the existence of a simple tractable formula for the delay [29] that has recursive properties [27], making the calculation of the circuit delays highly efficient even in large circuits. However, no equivalent formula for delay calculation has been determined for *RLC* trees which satisfies all of these properties. The absence of an equivalent delay model for *RLC* trees is primarily due to the fact that the Elmore delay does not cover non-monotone responses [15] which can occur in *RLC* circuits. The focus of this paper is therefore the introduction of a simple tractable delay formula for *RLC* trees that preserves the useful characteristics. The rise time of the signals in an *RLC* tree is also characterized as well as the overshoots and the settling time (for an underdamped response).

This paper is organized as follows. In section II, an equivalent second order approximation of an *RLC* tree is developed. Closed form solutions for the 50% delay, rise time, overshoot characteristics, and settling time of the signals within an *RLC* tree are introduced in section III. Finally, some conclusions are offered in section IV.

#### II. Second Order Approximation for RLC Trees

In 1948, Elmore [15] introduced a general approach for calculating the propagation delay of a linear system given its transfer function. If the transfer function of the system is G(s), the normalized transfer function g(s) is G(s)/G(0), which can generally be described as

$$g(s) = \frac{1 + a_1 s + a_2 s^2 + \dots + a_n s^n}{1 + b_1 s + b_2 s^2 + \dots + b_m s^m},$$

(1)

where  $a_i$  and  $b_i$  are real and m > n. For a monotone system and a unit step input Elmore showed that the 50% propagation delay can be approximated by  $T_p = b_i - a_i$ . In 1987, Wyatt [16] used the relationships that  $b_1$  and  $a_1$  are

$$b_1 = \sum_{i=1}^m \frac{1}{p_i}$$

and  $a_1 = \sum_{i=1}^n \frac{1}{z_i}$ , (2)

respectively, where  $p_i$  and  $z_i$  are the poles and zeros of the transfer function, respectively. Thus, Wyatt treated  $T_p = b_1 - a_1$  as the reciprocal of the dominant pole (the pole that has the smallest absolute value) of the system. Using this approximation, the unit step response of the system becomes

$$e(t) = 1 - \exp(-\frac{t}{T_D}), \qquad (3)$$

which models a 50% propagation delay as equal to  $0.693T_D$  rather than  $T_D$  as anticipated by Elmore. The Wyatt approximation is therefore more accurate than the Elmore delay. For an *RC* tree, the time constant  $T_D$  at node *i* is calculated in [29] and given by

$$T_{Di} = \sum_{k} C_k R_{ik} , \qquad (4)$$

where k is an index that covers each capacitor in the circuit and  $R_{\mu}$  is the common resistance from the input to the nodes *i* and *k*. Thus,

Wyatt's approximate first order transfer function for an RC tree is

$$g_{i}(s) = \frac{1}{s \sum_{k} C_{k} R_{ik} + 1}$$

(5)

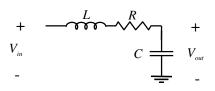

The Elmore (Wyatt) delay does not properly characterize RLC networks due to the possibility of a non-monotone response of an RLC network [15]. To illustrate this point, consider the simple single section RLC circuit depicted in Fig. 1. This circuit has a second order transfer function given by

$$g(s) = \frac{1}{s^2 LC + sRC + 1}.$$

(6)

Note that the coefficient of  $s^{l}$  is *RC*, which does not include the inductance *L*. Thus, the Elmore time constant (and thus the Wyatt approximation) does not depend on the inductance. However, inductance can have a significant effect on the response of the circuit. To clarify the effect of inductance, the transfer function of the circuit can be reconfigured as

$$g(s) = \frac{\omega_n^2}{s^2 + s2\zeta\omega_n + \omega_n^2},\tag{7}$$

where

$$\zeta = \frac{1}{2} \frac{RC}{\sqrt{LC}}$$

and  $\omega_n = \frac{1}{\sqrt{LC}}$  (8)

The poles of the transfer function are

$$P_{1,2} = \omega_n [-\zeta \pm \sqrt{\zeta^2 - 1}].$$

(9)

Note that if  $\zeta$  is less than one, the poles are complex and oscillations occur in the response which violates the monotone response condition of the Elmore delay. In that case the response is underdamped and overshoots occur. If  $\zeta$  is greater than one, the poles are real and the response is an overdamped response. If  $\zeta$  is equal to one, the response is a critically damped response.  $\zeta$  is called the damping factor of the system. From (8), as the inductance increases,  $\zeta$  decreases which violates the assumption of a monotonic response.

Fig. 1. Simple RLC circuit

At least a second order approximation is required to characterize a non-monotone response, because a non-monotone response involves complex poles which appear in conjugate pairs in a real system. Thus, a second order system such as (7) is used to approximate a system with a non-monotone response. It is therefore necessary to determine  $\zeta$  and  $\omega_n$  in order to make the second order approximation as accurate as possible as compared to the exact transfer function.

Matching the moments of a transfer function to the moments of a higher order system permits the transfer function to approximate any linear system, see *e.g.*, [30]. The greater the number of moments that are matched, the better the transfer function approximates the system. The transfer function in (7) is thus expanded in powers of *s* where the first two moments of the transfer function are equated to the first two moments of the system which are assumed to be  $m_1$  and  $m_2$ . The expansion of the transfer function in (7) is

$$g(s) = 1 - s \left(\frac{2\zeta}{\omega_n}\right) + s^2 \left(\frac{-1 + (2\zeta)^2}{\omega_n^2}\right) - \dots = 1 + m_1 s + m_2 s^2 + \dots$$

(10)

The parameters that characterize the second order approximation of a non-monotonic system,  $\zeta$  and  $\omega_n$ , can be calculated in terms of the moments of the non-monotonic system and are

$$\zeta = \frac{-m_1}{2} \frac{1}{\sqrt{m_1^2 - m_2}}$$

and  $\omega_n = \frac{1}{\sqrt{m_1^2 - m_2}}$  (11)

Hence, for a system with a non-monotonic response a second order approximation can be found if the first and second moments of the system are known.

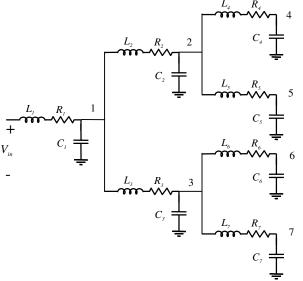

Fig. 2. General RLC tree

For the general *RLC* tree shown in Fig. 2, the voltage drop at any node *i* as compared to the input voltage is

$$V_{in}(s) - V_i(s) = \sum_{k} C_k V_k(s) s[R_{ki} + L_{ki}s], \qquad (12)$$

where  $L_{ik}$  is the common inductance from the input to the nodes *i* and *k*. If the input is a unit impulse,  $V_{in}(s)$  is equal to 1.0 and the voltages at the nodes of the tree are the unit impulse responses of these nodes. Thus, the normalized transfer function  $g_i(s)$  at node *i* is given by  $V_i(s)$  and is

$$g_i(s) = 1 - \sum_k C_k V_k(s) s[R_{ki} + L_{ki}s] = 1 + m_1^i s + m_2^i s^2 + \dots$$

(13)

The first and second moments at node *i* can be found from

$$m_1^i = \frac{dg_i(s)}{ds}\Big|_{s=0}$$

and  $m_2^i = \frac{1}{2!} \frac{d^2 g_i(s)}{ds^2}\Big|_{s=0}$  (14)

Differentiating (13) with respect to *s* and substituting s = 0,

$$m_{1}^{i} = -\sum_{k} C_{k} R_{ik} V_{k}(s) \Big|_{s=0},$$

$$m_{2}^{i} = -\sum_{k} C_{k} R_{ik} \frac{dV_{k}(s)}{ds} \Big|_{s=0} - \sum_{k} C_{k} L_{ik} V_{k}(s) \Big|_{s=0}.$$

(15)

Note that  $V_k(s) \mid_{s=0} = 1$ , and that  $dV_k(s)/ds \mid_{s=0} = m_1^k$  since  $V_k(s) = g_k(s) = 1 + m_1^k s + m_2^k s^2 + \dots$ . Thus, the first and second moments of a general *RLC* tree at node *i* are

$$m_{1}^{i} = -\sum_{k} C_{k} R_{ik} ,$$

$$m_{2}^{i} = \sum_{k} \sum_{j} C_{k} R_{ik} C_{j} R_{kj} - \sum_{k} C_{k} L_{ik} .$$

(16)

Since Elmore (Wyatt) approximates the first term in  $m_2^i$  by

$\left(\sum_{k} C_{k} R_{ik}\right)^{2}$  (this approximation can be seen in the coefficient of

$s^2$  if (5) is expanded into powers of *s*), a similar approach is used here. Thus, the second moment is approximated by

$$m_2^i = \left(\sum_k C_k R_{ik}\right)^2 - \sum_k C_k L_{ik}$$

(17)

Substituting the first and second moments of a general *RLC* tree into (11),  $\zeta_i$  and  $\omega_{ii}$  which characterize a second order approximation of the transfer function at node *i* are

$$\zeta_{i} = \frac{1}{2} \frac{\sum_{k} C_{k} R_{ik}}{\sqrt{\sum_{k} C_{k} L_{ik}}} \quad \text{and} \quad \omega_{ni} = \frac{1}{\sqrt{\sum_{k} C_{k} L_{ik}}} \quad (18)$$

Note the analogy with  $\zeta$  and  $\omega_n$  for a single *RLC* section in (8). The time constants *RC* and  $\sqrt{LC}$  are replaced by the summations of the equivalent time constants in the tree. Note also that (18) becomes (8) for a single section. This second order approximation has the same accuracy characteristics as that of the Elmore (Wyatt) approximation for an *RC* tree. For a step input and a supply voltage of  $V_{DD}$ , the time domain response at node *i* derived from the second order approximation is

$$S_{i}(t) = V_{DD} + \frac{V_{DD}}{2\sqrt{\zeta_{i}^{2} - 1}} \left[ \frac{\exp[\omega_{m}t(-\zeta_{i} + \sqrt{\zeta_{i}^{2} - 1})]}{-\zeta_{i} + \sqrt{\zeta_{i}^{2} - 1}} - \frac{\exp[\omega_{m}t(-\zeta_{i} - \sqrt{\zeta_{i}^{2} - 1})]}{-\zeta_{i} - \sqrt{\zeta_{i}^{2} - 1}} \right].$$

(19)

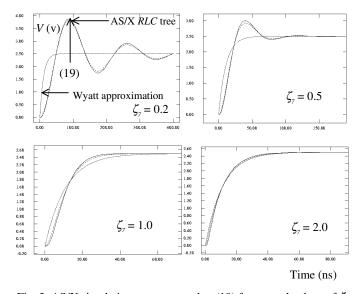

This closed form solution is compared to AS/X [31] simulations of the tree shown in Fig. 2 at output node 7. The simulations are shown in Fig. 3 for a balanced tree with several values of  $\zeta_7$  (the equivalent damping factor at node 7). The Elmore (Wyatt) solution is also shown for comparison. Note the accuracy that the solution exhibits as compared to the AS/X simulations for the case of a balanced tree. The error in the propagation delay is less than 3% for this balanced tree example. This solution becomes less accurate for unbalanced *RLC* trees. In general this solution for *RLC* trees has the same accuracy characteristics as that of the Elmore (Wyatt) delay with respect to *RC* trees. Note also that the solution in (19) tends to the Elmore (Wyatt) approximation for large  $\zeta_i$  (low inductance effects), which shows that the general solution introduced here for an *RLC* tree includes the special case of an *RC* tree.

Fig. 3. AS/X simulations as compared to (19) for several values of  $\zeta$ . The Elmore (Wyatt) solution is also shown.

#### III. Signal Characterization in RLC Trees for a Step Input

The time domain step response in (19) is used to characterize the 50% delay and the rise time of signals within an *RLC* tree. The rise time is defined here as the time for the signal to rise from 10% to 90% of the final value. The overshoots and the settling time for the case of an underdamped response are also characterized. In the step response described by (19), note that time is always multiplied by  $\omega_{n}$ .

Thus, if the time is scaled by  $\omega_{ni}$ , the step response at node *i* with a supply voltage of  $V_{DD}$  becomes a function of only one variable  $\zeta_i$  and is

$$S_{i}'(t) = V_{DD} + \frac{V_{DD}}{2\sqrt{\zeta_{i}^{2} - 1}} \left[ \frac{\exp[t'(-\zeta_{i} + \sqrt{\zeta_{i}^{2} - 1})]}{-\zeta_{i} + \sqrt{\zeta_{i}^{2} - 1}} - \frac{\exp[t'(-\zeta_{i} - \sqrt{\zeta_{i}^{2} - 1})]}{-\zeta_{i} - \sqrt{\zeta_{i}^{2} - 1}} \right],$$

(20)

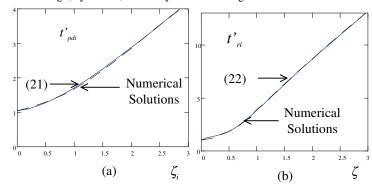

where  $S_i'(t)$  is the time scaled response at node *i* and *t'* is time scaled by  $\omega_{ni}$ . The time scaled 50% delay and rise time can be calculated by equating  $S_i'(t)$  to  $0.5V_{DD}$ ,  $0.1V_{DD}$ , and  $0.9V_{DD}$ , respectively. The time scaled 50% delay at node *i* and the rise time are only functions of one variable,  $\zeta_i$ . The 50% delay and the rise time calculated for several values of  $\zeta_i$  are plotted as functions of  $\zeta_i$  in Fig. 4. A curve fitting method is applied to characterize the time scaled 50% delay and rise time as functions of  $\zeta_i$  and these functions are

$$t'_{pdi} = 1.047e^{-\frac{\zeta_i}{0.85}} + 1.39\zeta_i,$$

(21)

$$t'_{ri} = 6.017e^{-\frac{\zeta_i^{1.35}}{0.4}} - 5e^{-\frac{\zeta_i^{1.25}}{0.64}} + 4.39\zeta_i,$$

(22)

where  $t'_{pdi}$  and  $t'_{ri}$  are the time scaled 50% delay and rise time at node *i*, respectively. The 50% delay and rise time at node *i* can be found by dividing  $t'_{adi}$  and  $t'_{ri}$  by  $\omega_{ai}$  and are

$$t_{pdi} = (1.047e^{-\frac{\zeta_i}{0.85}} + 1.39\zeta_i) / \omega_{ni}, \qquad (23)$$

$$t_{ri} = (6.017e^{-\frac{\zeta_i^{1.55}}{0.4}} - 5e^{-\frac{\zeta_i^{1.25}}{0.64}} + 4.39\zeta_i)/\omega_{ni}.$$

(24)

Note that the 50% delay and the rise time at node i can be described as

$$t_{pdi} = (1.047e^{-\frac{5i}{0.85}}) / \omega_{ni} + 0.695 \sum_{k} C_k R_{ik} , \qquad (25)$$

$$t_{ri} = (6.017e^{\frac{\zeta_i \cdots}{0.4}} - 5e^{\frac{\zeta_i \cdots}{0.64}}) / \omega_{ni} + 2.195\sum_k C_k R_{ik} .$$

<sup>(26)</sup>

For large  $\zeta_i$  (low inductance effects), these solutions approach the Elmore (Wyatt) approximation of the 50% delay and the rise time for an *RC* tree at node *i*. This relationship demonstrates that the general solutions for the 50% delay and the rise time introduced here includes the Elmore (Wyatt) delay for the special case of an *RC* tree. Note also that the general solutions introduced here includes all types of responses (underdamped non-monotone, critically damped, and overdamped) in one continuous equation, which is useful in applications such as buffer insertion, wire sizing, and other VLSI-based design, synthesis, and analysis methodologies.

Fig. 4. Numerical solutions as compared to (21) and (22) versus  $\zeta_{i}$ . a) The time scaled 50% delay,  $t'_{pdl}$ , compared to (21). b) The time scaled rise time,  $t'_{ri}$ , compared to (22).

For the case of an underdamped non-monotone response ( $\zeta_{\zeta} \leq 1$ ), overshoots and undershoots occur which must also be characterized. Also, another parameter can be used to characterize non-monotone responses which is defined as the time when the oscillations about the

steady state are smaller than x of the steady state value. This parameter is usually called the settling time and x is typically chosen to be 0.1 [32]. The value of the maximum or minimum oscillations can be found by differentiating (19) with respect to time and equating the result to zero. The values for the maximum or minimum oscillations at node i as a percentage of the final value are given by

$$\mathscr{O}_{i} = (-1)^{n+1} \cdot 100 \exp\left(-\frac{n\pi\zeta_{i}}{\sqrt{1-\zeta_{i}^{2}}}\right) \qquad n = 1, 2, \dots, \qquad (27)$$

where  $\mathcal{O}_i$  represents the maximum overshoots for *n* odd and minimum undershoots for *n* even at node *i*. The time at which the  $n^{th}$  overshoot occurs at node *i* is given by

$$t_{Oi} = \frac{n\pi}{\omega_{ni}\sqrt{1-\zeta_i^2}} \,. \tag{28}$$

The settling time can be calculated by equating  $\%O_i$  to  $x^*100$  to determine the value of *n* which represents the first overshoot that is less than *x* times the steady state value. The time of this overshoot is the settling time and can be calculated by substituting *n* from  $\%O_i = x^*100$  in (29). Thus, the settling time at node *i* is given by

$$t_{si} = \frac{-\ln(x)}{\zeta_i \omega_{ni}}$$

(29)

For  $x = 0.1, t_{i}$  is

$$t_{si} = \frac{2.3}{\zeta_i \omega_{ni}}$$

(30)

#### **IV. Conclusions**

A general method to characterize the response of a linear nonmonotone system that is equivalent to the Elmore delay is presented. The generated delay expressions for *RLC* trees have the same accuracy characteristics that the Elmore (Wyatt) approximation has for *RC* trees. Simple analytical expressions of signals in an *RLC* tree are provided for the 50% delay, rise time, overshoot characteristics, and settling time. These expressions consider both monotone and non-monotone signal responses. The delay expressions are continuous and hence are useful for design, analysis, and synthesis in VLSI-based design methodologies.

#### References

- J. M. Rabaey, Digital Integrated Circuits, A Design Perspective, Prentice Hall, Inc., New Jersey, 1996.

- [2] D. A. Priore, "Inductance on Silicon for Sub-Micron CMOS VLSI," Proceedings of the IEEE Symposium on VLSI Circuits, pp. 17-18, May 1993.

- [3] D. B. Jarvis, "The Effects of Interconnections on High-Speed Logic Circuits," *IEEE Transactions on Electronic Computers*, Vol. EC-10, No. 4, pp. 476 - 487, October 1963.

- [4] Y. Eo and W. R. Eisenstadt, "High-Speed VLSI Interconnect Modeling Based on S-Parameter Measurement," *IEEE Transactions* on Components, Hybrids, and Manufacturing Technology, Vol. CHMT-16, No. 5, pp. 555 - 562, August 1993.

- [5] A. Deutsch, et al., "High-Speed Signal Propagation on Lossy Transmission Lines," *IBM Journal of Research and Development*, Vol. 34, No. 4, pp. 601 - 615, July 1990.

- [6] A. Deutsch, et al., "Modeling and Characterization of Long Interconnections for High-Performance Microprocessors," *IBM Journal of Research and Development*, Vol. 39, No. 5, pp. 547 - 667, September 1995.

- [7] A. Deutsch et al., "When are Transmission-Line Effects Important for On-Chip Interconnections?," *IEEE Transactions on Microwave Theory and Techniques*, Vol. MTT-45, No. 10, pp. 1836-46, October 1997.

- [8] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Figures of Merit to Characterize the Importance of On-Chip Inductance," *Proceedings of the IEEE/ACM Design Automation Conference*, pp. 560 – 565, June 1998.

- M. P. May, A. Taflove, and J. Baron, "FD-TD Modeling of Digital Signal Propagation in 3-D Circuits with Passive and Active Loads,"

*IEEE Transactions on Microwave Theory and Techniques*, Vol. MTT-42, No. 8, pp. 1514 - 1523, August 1994.

- [10] T. Sakurai, "Approximation of Wiring Delay in MOSFET LSI," *IEEE Journal of Solid-State Circuits*, Vol. SC-18, No. 4, pp. 418 -426, August 1983.

- [11] G. Y. Yacoub, H. Pham, and E. G. Friedman, "A System for Critical Path Analysis Based on Back Annotation and Distributed Interconnect Impedance Models," *Microelectronic Journal*, Vol. 18, No. 3, pp. 21 - 30, June 1988.

- [12] J. Torres, "Advanced Copper Interconnections for Silicon CMOS Technologies," *Applied Surface Science*, Vol. 91, No. 1, pp. 112 -123, October 1995.

- [13] C. F. Webb et al., "A 400MHz S/390 Microprocessor," Proceedings of the IEEE International Solid-State Circuits Conference, pp. 448 – 449, February 1997.

- P. J. Restle and A. Duetsch, "Designing the Best Clock Distribution Network," *Proceedings of the IEEE VLSI Circuit Symposium*, pp. 2 – 5, June 1998.

- [15] W. C. Elmore, "The Transient Response of Damped Linear Networks," *Journal of Applied Physics*, Vol. 19, pp. 55 - 63, January 1948.

- [16] J. L. Wyatt, Circuit Analysis, Simulation and Design, Elsevier Science Publishers, North-Holland, 1987.

- [17] J. Cong, L. He, C-K. Koh, and P. Madden, "Performance optimization of VLSI Interconnect," *Integration, The VLSI Journal*, Vol. 21, pp. 1 - 94, November 1996.

- [18] J. Cong and K. S. Leung, "Optimal wire sizing under the distributed Elmore delay model," *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design*, pp. 634 - 639, November 1993.

- [19] J. Cong and C-K. Koh, "Simultaneous Driver and Wire Sizing for Performance and Power Optimization," *IEEE Transactions on Very Large Scale Integration (VLSI)*, Vol. 2, No. 4, pp. 408 - 423, December 1994.

- [20] K. D. Boese, A. B. Kahng, and G. Robins, "High Performance Routing Trees with Identified Critical Sinks," *Proceedings of the IEEE/ACM Design Automation Conference*, pp. 182 – 187, June 1993.

- [21] K. D. Boese, A. B. Kahng, B. A. McCoy, and G. Robins, "Rectilinear Steiner Trees with Minimum Elmore Delay," *Proceedings of the IEEE/ACM Design Automation Conference*, pp. 381 – 386, June 1994.

- [22] S. S. Sapatnekar, "RC Interconnect Optimization Under the Elmore Delay Model," *Proceedings of the IEEE/ACM Design Automation Conference*, pp. 387 – 391, June 1994.

- [23] J. Cong and L. He, "Optimal Wire Sizing for Interconnects with Multiple Sources," *Proceedings of the IEEE International Conference on Computer-Aided Design*, pp. 586 – 574, November 1995

- [24] L. W. Nagel, "SPICE2: A Computer Program to Simulate Semiconductor Circuits," *Technical Report ERL-M520*, UC-Berkeley, May 1975

- [25] K. D. Boese, A. B. Kahng, B. A. McCoy, and G. Robins, "Fidelity and Near-Optimality of Elmore-Based Routing Constructions," *Proceedings of the IEEE International Conference on Computer Design*, pp. 81 – 84, October 1993.

- [26] J. Cong, A. B Kahng, C.-K. Koh and C.-W. A. Tsao, "Bounded-Skew Clock and Steiner Routing Under Elmore Delay," *Proceedings* of the IEEE International Conference On Computer-Aided Design, pp. 66 - 71, January 1995.

- [27] L. P. P. P. van Ginneken, "Buffer Placement in Distributed RC-tree Networks for Minimal Elmore Delay," *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 865 - 868, May 1990.

- [28] C. J. Alpert, "Wire Segmenting for Improved Buffer Insertion," Proceedings of the IEEE/ACM Design Automation Conference, pp. 588-593, June 1997.

- [29] J. Rubinstein, P. Penfield, Jr., and M. Horowitz, "Signal Delay in RC Tree Networks," *Proceedings of the IEEE/ACM Design Automation Conference*, pp. 202 – 211, June 1983.

- [30] L. T. Pillage and R. A. Rohrer, "Delay Evaluation with Lumped Linear RLC Interconnect Circuit Models," *Proceedings of the Caltech Conference on VLSI*, pp. 143-158, May 1989.

- [31] AS/X User's Guide, IBM Corporation, New York, 1996.

- [32] B. C. Kuo, *Automatic Control Systems, A Design Perspective,* Prentice Hall of India, New Delhi 1989.