# Silicon-Germanium Avalanche Receivers With fJ/bit Energy Consumption

Daniel Benedikovic, Léopold Virot, Guy Aubin, Jean-Michel Hartmann, Farah Amar, Xavier Le Roux, Carlos Alonso-Ramos, Éric Cassan, Delphine Marris-Morini, Frédéric Boeuf, Jean-Marc Fédéli, Bertrand Szelag, and Laurent Vivien

Abstract—Fast, low-noise and sensitive avalanche photoreceivers are needed for surging short-reach photonic applications. Limitations concerning bandwidth, throughput and energy consumption should be overcome. In this work, we comprehensively study the performance opportunities provided by avalanche p-i-n photodetectors with lateral silicon-germanium-silicon heterojunctions. Our aim is to circumvent the need for chip-bonded electronic amplifiers. In particular, we demonstrate that avalanche photodetectors based on silicon-germanium-silicon heterostructures yield reliable opto-electrical performances, with high gain-bandwidth products up to 480 GHz and low effective ionization ratios down to 0.15. Moreover, they improve power sensitivities for high-speed optical signals and have a low energy dissipation of only a few fJ per received information bit. These results pave the way for high-performing receivers for energy-aware data links, in nextgeneration short-distance data communications.

Index Terms—Group-IV semiconductors, Integrated photonics, Avalanche photodetectors, Energy consumption, Short-reach communications, CMOS technology.

# I. INTRODUCTION

HE relentless demands of data-hungry devices as in data centers [1], high-performance computers and servers [2] or big data clouds and storages [3] places exponential requirements on electrical wire signaling. Data overflow in metal wires is a

Manuscript received June 15, 2021; revised September 3, 2021; accepted September 10, 2021. Date of publication September 16, 2021; date of current version October 15, 2021. This work was supported by the Slovak Research and Development Agency under Project PP-COVID-20-0100: DOLORES.AI: The pandemic guard system. (Corresponding author: Daniel Benedikovic.)

Daniel Benedikovic is with the Department Multimedia and Information-Communication Technologies, University of Žilina, 01026 Žilina, Slovakia, and also with the Université Paris-Saclay, CNRS, Centre de Nanosciences et de Nanotechnologies, 91120 Palaiseau, France (e-mail: daniel.benedikovic@uniza.sk).

Léopold Virot, Jean-Michel Hartmann, Jean-Marc Fédéli, and Bertrand Szelag are with the University Grenoble Alpes and CEA, LETI, Université Paris-Saclay, 38054 Grenoble, France (e-mail: leopold.virot@cea.fr; jean-michel.hartmann@cea.fr; jean-marc.fedeli@cea.fr; bertrand.szelag@cea.fr).

Guy Aubin, Farah Amar, Xavier Le Roux, Carlos Alonso-Ramos, Éric Cassan, Delphine Marris-Morini, and Laurent Vivien are with the, and also with the Université Paris-Saclay,CNRS, Centre de Nanosciences et de Nanotechnologies, 91120 Palaiseau, France (e-mail: guy.aubin@c2n.upsaclay.fr; farah.amar@c2n.upsaclay.fr; xavier.leroux@c2n.upsaclay.fr; carlos.ramos@c2n.upsaclay.fr; eric.cassan@c2n.upsaclay.fr; delphine.morini@u-psud.fr; laurent.vivien@c2n.upsaclay.fr).

Frédéric Boeuf is with the Technology R&D, STMicroelectronics SAS, 38920 Crolles, France (e-mail: frederic.boeuf@st.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSTQE.2021.3112494.

Digital Object Identifier 10.1109/JSTQE.2021.3112494

critical bottleneck that hampers the take-off of such devices. The benefits of optical interconnects extend from long-distance to short-distance systems. Components used in long-haul systems are too costly and complex to be adopted in short-reach systems, however. Short-reach architectures comprise opto-electrical and electro-optical input/output (I/O) interfaces connected to basic building blocks such as circuit transceivers. Future transitions to Tbps communications and exascale computing levels [4] set new challenges in the following fields: increase and optimization of use bandwidths with allocation and dynamic scaling, high throughput, low-energy consumption and performance-cost trade-offs [5], [6].

Integrated group-IV photonics is appealing for optical interconnects, in particular for optical transceivers. Transceivers combine transmitters and receivers in a single circuit. Their high-bit-rate and energy-aware operation is attractive for use in various types of devices. Photonic integration, thanks to group-IV semiconductors, should open a squeezing of complex functions into a single chip, while reducing process cost. Such integration also facilitates high-yield and large-scale electronicsphotonics production. It is indeed based on mature complementary metal-oxide-semiconductor (CMOS) microelectronics processes [7]-[10]. Better connectivity and optimization at different levels (device, circuit, and system-to-network) are needed, however. On a component level, several levers are available to tackle on-going challenges. Optimizing optical receivers is key. High-speed receivers can be fabricated at reduced cost in CMOS cleanrooms [11], [12]. However, they are still energy inefficient, for the most part [13]–[18].

A photonic receiver converts an incoming optical signal into an electrical one. Receiver designs are more complex for the digital-coherent systems used in long-haul communications. This is due to the multi-level modulation increasing spectral information density and to the digital signal processing (DSP) techniques used to compensate fiber-channel impairments [15]–[18]. In contrast, intensity-modulation and direct detection (IM-DD) receivers are preferred in short-distance connections, because of their simplicity [11]. Mainstream receivers are based on III/V [19], [20] or silicon-germanium (Si-Ge) photodiodes [21]. They are then used together with an additional electronic circuitry with trans-impendence (TIA), limiting (LA) or gain-controlled (GCA) amplifiers. Digital-coherent and IM-DD receivers have different performance attributes to be considered, depending on the device targeted. The total energy consumed per

transmitted information bit governs short-reach link scenarios [14].

Metal-semiconductor-metal (MSM) [22]–[25], p-i-n's [26]– [30], or avalanche photodetectors (APDs) [31]–[44] are widely used in Si-Ge receivers. MSM devices, having a Schottky barrier on Ge, typically have very high dark currents [22]–[24]. This not only limits the device sensitivity, but also dissipates a large amount of energy. P-i-n photodiodes are well-established options for digital-coherent and IM-DD receivers. They have very compact footprints and attractive opto-electrical performances. P-i-n devices are mature enough to yield high responsivities (up to the limit imposed by external quantum efficiency), fast responses and low dark-currents [26]–[30]. On the other hand, power sensitivity remains low or, at best, moderate for highspeed optical signals [30]. Enhancing p-i-n diode sensitivity may also help to improve the overall energy efficiency of the link by lowering the required transmitter power levels. To reduce energy consumption, the diode capacitance should be minimized [5], [7]. Moreover, p-i-n photodiodes generate currents or voltages that are not high enough to enable direct signal processing. Further electronic stages are thus needed [22], [23], [30]. Adding CMOS electronics amplifies p-i-n's output, with, however, an increased parasitic load at the receiver front-end [12]. This is critical for receivers as a higher parasitic capacitance at the input of an amplification stage may deteriorate the overall device bandwidth (limiting thus the detection speed). The device will also consumes far more energy. If the noise current of the p-i-n diode, i.e. the intrinsic noise of device itself, is low – below 1 µA - the performance of a p-i-n photo-receiver is then limited by the noise of its electronic components [45]–[48]. Major energy savings thus result from the suppression of such electronic stages. Receivers with APDs are also attractive. Such receivers rely on diodes that generates internal gain through photo-carrierinitiated impact ionization. Avalanching the photodiode helps in improving the overall device performance, alleviating the high thermal noise of electronic amplifiers. APDs use MSM [24], p-i-n's [32]-[34], [41], and separate absorption carrier multiplication (SACM) structures [31], [35]-[38], [42]-[44] together with, in some cases, electronic CMOS circuits. However, a prime concern of these devices is the trade-off between speed and optical power sensitivity. So-called "receiver-less" APDs, i.e. APDs without chip-bonded nor integrated circuit electronics, would be interesting in chip-scale interconnects, where highspeed, low-noise, and energy efficient operation is sought after.

In this work, we will thus comprehensively investigate the properties of p-i-n avalanche photodetectors with lateral Si-Ge-Si heterojunctions. In particular, we will demonstrate that Si-Ge-Si APDs yield fast, reliable and low-noise on-chip signal detection, improved sensitivity and a rather low fJ/bit energy consumption, without the need for additional electronic amplification components.

# II. PHOTODETECTOR STRUCTURE AND FABRICATION

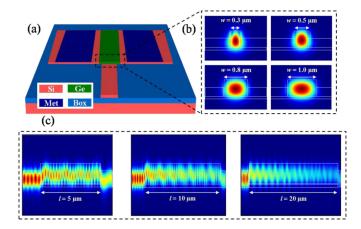

Our waveguide-integrated p-i-n APD is schematically shown in Fig. 1(a). APDs were fabricated on 200 mm silicon-on-insulator (SOI) wafers with 220 nm thick silicon (Si) layers and

Fig. 1. (a) Schematics of the p-i-n photodetector with a lateral Si-Ge-Si heterojunction. (b) Optical mode profiles of p-i-n photodetectors with various cross-sectional areas. (c) Optical mode propagation through p-i-n photodetectors with various lengths.

2 μm buried oxides (BOX's) using Si-foundry manufacturing processes [11], [29].

The 260 nm thick Ge films at the center of the diodes were epitaxially grown in cavities with ~60 nm thick Si floors at the waveguide ends. Those intrinsic Ge films were sandwiched between ion implanted p-type and n-type Si slabs. Metal plugs and contact electrodes were latter on processed on Si regions only. Details on device fabrication in our Si-foundry facility can be found in Refs. [29], [30]. Grating couplers and strip singlemode waveguides were used to efficiently butt-couple off-chip light into our w (width)  $\times l$  (length) photodetectors. Couplers and waveguides operated with an in-plane waveguide polarization (quasi-TE polarization) at 1.55 µm wavelength. Buttlight-coupled p-i-n photodetectors are robust devices, enabling flexible engineering of opto-electrical performances through changes of the in-plane diode geometry [29]. Fig. 1(b) shows mode profiles of the Si-Ge-Si photodetector for various intrinsic Ge region widths, while Fig. 1(c) show side views of the optical intensity flowing through various length butt-waveguidecoupled p-i-n photodetectors, modeled with a three-dimensional finite-difference time domain (3D FDTD) simulator.

# III. RESULTS AND DISCUSSION

### A. Current-Voltage Characteristics, Responsivity and Gain

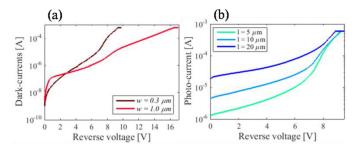

Typical static current-voltage characteristics for different Si-Ge-Si photodetectors are shown in Fig. 2(a) and 2(b) in the dark and light illuminated states, respectively. Low dark currents ( $i_d$ ) ranging from 60 to 200 nA at low operating voltages (from 0.5 V to 3 V) are obtained [48]. The dark current continuously rises up to 600  $\mu$ A levels, when getting close to the avalanche breakdown. Junction breakdown bias are inversely proportional to the intrinsic diode width. They are around 9 V and 16.5 V for 0.3  $\mu$ m and 1  $\mu$ m wide devices, respectively. An optical laser source emitting light at a 1.55  $\mu$ m wavelength was used to inject light into photodetectors thanks to a grating coupler and a butt-light-coupling scheme. The input optical power coupled

Fig. 2. Current-voltage characteristics (a) without and (b) with light coupled into the p-i-n photodetectors. 0.3  $\mu$ m wide and 20  $\mu$ m long or 1  $\mu$ m wide and 40  $\mu$ m long photodetectors were studied in (a). 0.3  $\mu$ m wide photodetectors with different lengths (5, 10 and 20  $\mu$ m) were probed in (b). The power coupled into the waveguide photodetectors was -14 dBm.

TABLE I

NOMINAL PHOTO-RESPONSIVITIES AT A UNITY GAIN

| Width/Length<br>[μm] | <i>l</i> = 5 | <i>l</i> = 10 | <i>l</i> = 20 | l = 40 |

|----------------------|--------------|---------------|---------------|--------|

| w = 0.3              | 0.021        | 0.051         | 0.21          | -      |

| w = 0.5              | -            | 0.085         | 0.35          | 0.51   |

| w = 0.8              | -            | -             | 0.47          | 0.73   |

| w = 1.0              | -            | -             | 0.76          | 1.16   |

Note: Reference responsivity is defined as net-light current over power coupled into the device at 0.5 V reverse bias.

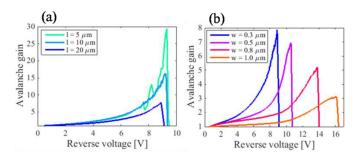

Fig. 3. Gain-voltage characteristics of p-i-n photodetectors for (a)  $0.3~\mu m$  wide devices with different lengths (5, 10 and 20  $\mu m$ ) and (b) 20  $\mu m$  long devices with different widths (0.3, 0.5, 0.8 and 1.0  $\mu m$ ).

into the devices was estimated to be -14 dBm. Responsivities and gains were quantified from photo-current-voltage measurements. The responsivity is the ratio between the net-light current and coupled input power ( $R = i_{\rm ph}/p_{\rm i}$ ), while the gain is the ratio between the photo-responsivity and its reference ( $M = R/R_{\rm r}$ ). Table I summarizes reference responsivities at unity gain under 0.5 V reverse bias for different p-i-n photodetectors.

Fig. 3 shows the avalanche multiplication gain as a function of operating reverse bias for different photodetector geometries. This includes variations in device lengths for 0.3  $\mu m$  wide structures (Fig. 3(a)) and variations in device widths for 20  $\mu m$  long devices (Fig. 3(b)).

For a fixed intrinsic Ge region width, the gain is larger in shorter devices. Meanwhile, for the same intrinsic Ge region length, the avalanche multiplication gain is lower in wider photodetectors. These trends are due to several factors and their interplay. First, and in line with the very low nominal

responsivities reported in Tab. I, shorter devices absorb less input power. A substantial part of the light thus scatters towards the Si regions, where the impact ionization occurs, resulting in a stronger avalanche effect. As the Si-Ge-Si photodiode is actually an extension of the Si waveguide, it is indeed clear from Fig. 1(c) that a significant amount of input power is present at the "waveguide" end in shorter diodes. Incident photons are then not fully absorbed by a short intrinsic zone. They are instead subjected to a stronger impact ionization. Nominal responsivities are improved to 0.62, 0.82, and 1.66 A/W with multiplication gains of 29.4, 16.2, and 7.9 for 5, 10, and 20 µm long devices with, nominally, a 0.3 μm wide intrinsic Ge zone. The evanescent tails of the quasi-TE mode otherwise have, as shown in Fig. 1(b), large overlaps with lateral Si slabs in narrow photodiodes. This may partially explain the higher multiplication gains in such structures. Although it is undesirable for low-voltage operation (due to the larger absorption loss) [48], a judicious narrowing of the intrinsic diode region might thus help in reaching better responsivities (under avalanche operation) in such devices. Electric fields are indeed strong in narrow Si-Ge-Si diodes. This, in turn, substantially contributes to diode avalanching, even at lower voltages. However, wider photodetectors show better modal confinement inside the intrinsic Ge region [29], [30], yielding a much better modal absorption coefficient [26]. This improves nominal diode responsivities, also in line with Tab. I values. As a result, improved responsivities up to 1.66, 2.42, 2.44, and 2.36 A/W were obtained through avalanche multiplications of 7.9, 6.9, 5.2, and 3.1 in 0.3, 0.5, 0.8, and 1 μm wide photodiodes with the same 20 μm length.

# B. Bandwidth, Gain-Bandwidth Product and Noise

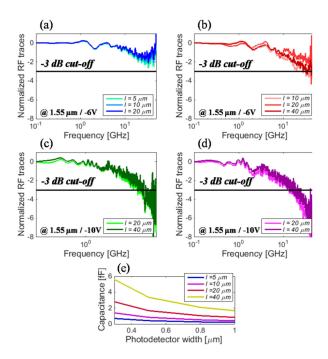

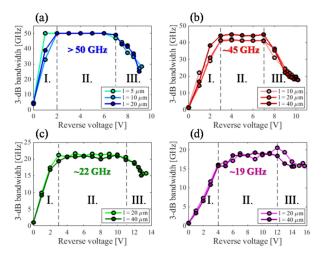

Bandwidth properties of Si-Ge-Si APD photodetectors were assessed using small-signal radio-frequency (RF) tests with a help of Lightwave Component Analyzer (LCA) by measuring the  $S_{21}$  response in the 0.1 up to 50 GHz range [29], [48]. Figs. 4(a) to 4(d) show normalized RF responses for different p-i-n APD geometries biased at reverse voltages of 6 V (0.3 and 0.5  $\mu$ m wide structures) and 10 V (0.8 and 1.0  $\mu$ m wide structures), respectively. Small-signal RF measurements were performed at a *C*-band wavelength of 1.55  $\mu$ m, with an optical input power coupled to the devices around -16.5 dBm.

Fig. 5 sums up -3-dB bandwidths as functions of operating reverse voltages for different Si-Ge-Si APD photodetectors.

In all cases, we can clearly distinguish three operation regimes. (I.) Under low-voltage operation, typically in the 0 to 4 V range, the cut-off frequency steadily increases with increasing voltage until the maximum bandwidth is reached [48]. The bias at which the maximum cut-off is reached changes with the intrinsic diode width. Sub-μm dimensions indeed facilitate the generation of high electrical fields inside the diode, helping in avalanching the diode at lower voltages. Maximum bandwidths are larger than 50 GHz (upper limit of our LCA) for 0.3 μm wide structures. Moreover, maximum bandwidths are equal to 45, 22, and 19 GHz for 0.5, 0.8, and 1 μm wide devices. Let us now exclude zero-bias operation and focus instead on the 1 to 4 V operating range. Built-in electrical fields are then

Fig. 4. Normalized frequency responses for different p-i-n APD geometries. (a) 0.3  $\mu$ m wide by 5, 10, and 20  $\mu$ m long, (b) 0.5  $\mu$ m wide by 10, 20, and 40  $\mu$ m long, (c) 0.8  $\mu$ m wide by 20 and 40  $\mu$ m, and (d) 1.0  $\mu$ m wide by 20 and 40  $\mu$ m long devices. (a) and (b) devices were biased at -6V, while(c) and (d) devices were biased at -10 V. The optical power injected into the device was -16.5 dBm at a 1.55  $\mu$ m emission wavelength. (e) Estimated junction capacitance of the diode versus the intrinsic region width.

Fig. 5. -3-dB bandwidth versus reverse voltage for p-i-n APD photodetectors with different lengths (see the insets) and various intrinsic region widths: (a) 0.3  $\mu$ m, (b) 0.5  $\mu$ m, (c) 0.8  $\mu$ m, and (d) 1.0  $\mu$ m. The optical power coupled into the devices was -16.5 dBm.

strong enough to effectively collect generated electron-hole pairs (region (I.) in Fig. 5 graphs). This is also in line with improved reference responsivities at 0.5 V reverse bias and beyond [30], [48]. For higher reverse bias, the -3-dB bandwidths remain stable, having reached their maxima (see region (II.) in Fig. 5 graphs). In this regime, photo-carriers generated by the diode reached their saturation velocity. In regimes (I.) and (II.), the

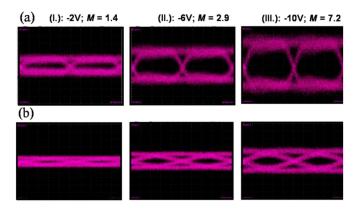

Fig. 6. Eye diagram apertures of  $w=0.5~\mu m$  and  $l=40~\mu m$  p-i-n avalanche photodetectors in regimes (I.), (II.) and (III.) for transmission bit rates of (a) 10 Gbps and (b) 40 Gbps. The optical power coupled into the devices was about -14.5 dBm.

avalanche multiplication gain slowly increases as well, because of continuous impact ionization, yet without impairing the device frequency response. Operating the diode at even higher voltages, i.e. in region (III.) of Fig. 5 graphs, exponentially amplifies the photo-current and the diode bandwidth starts to drop, because of the prevalent ionization build-up time. The bandwidth drop from its peak is much larger in 0.3 µm and 0.5 µm wide photodiodes than in their 0.8 µm and 1 µm wide counterparts. The bandwidth is indeed reduced from 50 and 45 GHz down to  $\sim$ 20 GHz in the former two configurations. This reduction is comparatively small in the latter two configurations, from 22 and 19 GHz down to  $\sim$ 15 GHz. This is likely due to the stronger electrical fields inside narrow than in wide detectors, with therefore higher overall multiplication gains. Moreover, and in line with previous low-voltage-only demonstrations [48], the frequency response of Si-Ge-Si heterostructure photodiodes operated in the avalanche mode only is the same for devices of same widths, but different lengths. It, however, decreases for wider structures. Heterostructure APDs thus seem not to be limited by the resistance-capacitance product (virtually the same frequency responses within Figs. 4(a) to 4(d)). The junction capacitance as a function of the intrinsic diode width is shown in Fig. 4(e). The APD speed is instead mainly restricted by the longer carrier transit time (considerably different frequency responses in Figs. 4(a) to 4(d)). Adjusting the photodetector length could therefore be harnessed to engineer the static photo-responses (responsivity and gain), without impacting the detection speed as the avalanche build-up time depends only on diode width and not on diode length. Experimental electrical eye diagram outputs for 0.5 μm wide and 40 μm long p-i-n APD heterostructure in the three operation regimes are shown in Fig. 6 for a pseudo-random bit sequence at 10 and 40 Gbps data rate.

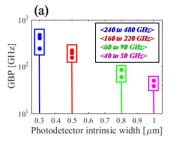

Fig. 7(a) shows Si-Ge-Si APD gain-bandwidth products (GBPs) for various intrinsic diode region widths. GBPs reached 480, 220, 90, and 50 GHz for p-i-n photodetectors with 0.3, 0.5, 0.8, and 1.0  $\mu$ m. High GBPs mean that APD are capable of high-speed operation with low noise level. APD's GBP and

Fig. 7. (a) Gain-bandwidth product as a function the intrinsic region width. (b) Estimated effective ionization ratio as a function of the avalanche multiplication gain for p-i-n photodetectors with different intrinsic zone widths.

noise are indeed depending, for a given material, on the ionization coefficients of electrons and holes within the diode's avalanching zone. They more precisely depend on the effective ionization factor (k), which is the ratio of ionization coefficients for electrons  $(\alpha)$  and holes  $(\beta)$ , i.e.  $k = \alpha I \beta$  [47], [49], [50]. For bulk Ge, k is close to unity  $(k \sim 0.9)$  as  $\alpha$  and  $\beta$  parameters are similar, particularly at high electrical fields. In contrast, the ultra-low k of Si (k < 0.1) is advantageously used in many APD designs at visible and near-IR wavelengths [21]. Fig. 7(b) shows the effective ionization coefficient as a function of the avalanche multiplication gain reachable in our heterostructured Si-Ge-Si APDs. Operating avalanche multiplication gains, extracted from measurements, are in the 1 to 8, 1 to 7, 1 to 4 and 1 to 3 ranges for 0.3, 0.5, 0.8 and 1  $\mu$ m wide photodetectors, respectively.

In Fig. 7(b), there is an exponential-like decay of the estimated k-factor as the avalanche multiplication gain increases. Such a trend is in line with GBP evolution (shown in Fig. 7(a)). Indeed, larger GBPs correspond to lower effective ionization ratios, and vice versa [31]–[37], [41]. From a device geometry point of view, narrower APDs have larger bandwidths and higher multiplication gains, while wider APD have transit-time-limited bandwidths and smaller avalanche multiplication factors. As a result, avalanche diode operation in a mode that has a marginal effect on the bandwidth, and thus on the device speed, corresponds also to the mode that yields low k values (and low avalanche excess noise). Then, the values of k-factor can be estimated as follows M < 1/k [49]. Indeed, high-speed and lownoise operation happening simultaneously is the most attractive practical scenario in an APD. Theoretically, ultra-low k-values of 0.13 - 0.15 only are expected for the smallest diode geometries. Low k values, stemming from an aggressive shrinking of the diode geometry, are also associated with low avalanche excess noises in Si-Ge-Si APDs. Such reduced excess noises would leverage strongly localized impact ionization at Si-Ge interfaces because of the dead-space effect [32], [34], [37], [41].

# C. APD Sensitivity and Optimal Operation

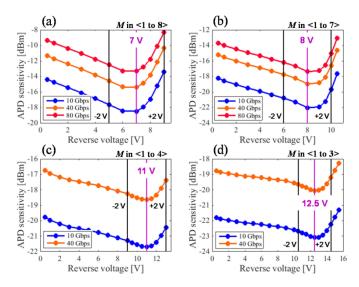

After evidencing high GBPs that would be due to low k-values, we then had a look at the sensitivity of those Si-Ge-Si APDs. Sensitivity analysis was carried out for various APD geometries to estimate their theoretical performances and determine their optimal operation point (defined at a reverse bias that yields the

Fig. 8. Calculated optical power sensitivities of p-i-n photodetectors with the following intrinsic region geometries: (a)  $0.3~\mu m \times 20~\mu m$ , (b)  $0.5~\mu m \times 40~\mu m$ , (c)  $0.8~\mu m \times 40~\mu m$ , and (d)  $1.0~\mu m \times 40~\mu m$ .

minimum device sensitivity). APDs had different geometries (width  $\times$  length): 0.3  $\mu$ m  $\times$  20  $\mu$ m, 0.5  $\mu$ m  $\times$  40  $\mu$ m, 0.8  $\mu$ m  $\times$  40 µm and 1 µm  $\times$  40 µm. The sensitivity to received optical power at a bit-error-rate (BER) of  $1 \times 10^{-9}$  was calculated using the model described in Refs. [51], for 10, 40, and 80 Gbps transmission bit rates. Fig. 8(a) to 8(d) show power sensitivities of Si-Ge-Si APDs as functions of operating reverse bias for different geometries and thus gain ranges: 1 to 8, 1 to 7, 1 to 4 and 1 to 3, respectively. Magenta and black vertical lines in Fig. 8 show optimum operation points and  $\pm 2$  V variations around them. Avalanching Si-Ge-Si p-i-n diodes always have a better sensitivity compared to reference points at 0.5 V bias. The sensitivity enhancement compared to the reference value is otherwise larger for device operating with higher multiplication gains, i.e. for narrower APD designs. For 10, 40, and 80 Gbps transmission bit rates, power sensitivities are equal to -18.5, -15.4, and -13.3 dBm for 0.3 μm wide and 20 μm long APDs (-22, -19, and -17.4 dBm for 0.5 μm wide and 40 μm long APDs), see Fig. 8(a) (Fig. 8(b)). The optimum operating points otherwise increase with the size of the intrinsic region, from 7 V up to 8V, 11 V and 12.5 V. Those operation optima are close to the boundaries between APD regimes (II.) and (III.) in Fig. 5 graphs showing the experimental bandwidths as functions of the reverse voltage. This means that high-speed and low-noise APD operation is feasible, this with the best-possible device sensitivity. Indeed, lower k-factors enable avalanche multiplication to be obtained before the speed limit, improving thereby the sensitivity to low optical signals. It is also clear, when looking at Fig. 8 graphs, that wider APDs yield better sensitivities for a fixed data rate. Those improved sensitivities are attributed to higher nominal photoresponsivities. The sensitivities for 10 and 40 Gbps bit rates are -21.7 and -18.7 dBm for 0.8 μm wide by 40 μm long diodes, and -23.1 and -20 dBm for 1µm wide by 40 µm long diodes. A stable APD operation is also of practical interest. According to

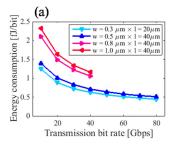

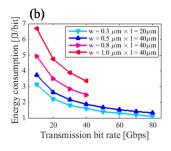

Fig. 9. Energy consumption as a function of transmission bit rate for different p-i-n avalanche-operated photodetectors: (a) at the optimal operation point and (b) under operation at 90% of the avalanche breakdown voltage.

sensitivity predictions, a negative bias variation of -2 V deteriorates the optimal sensitivity by an amount less than for positive bias variations (+2V). Although higher voltages can provide higher operating gains, further sensitivities improvements are hindered by high dark currents which then become limiting. In that situation, the APD sensitivity deviates far more from its optimum due to operation close to the avalanche breakdown. This suggests that sensitivity performance of heterostructured Si-Ge-Si APDs is mostly limited by dark currents instead of avalanche-related aspects such as ionization build-up time or excessively large multiplication avalanche noise.

# D. Energy Efficiency

Although APDs with electronic CMOS circuitry are used in short-reach interconnections, APDs without additional amplification stages are very compelling because of promising energy savings [2], [4], [5]. We further elaborate on that by analyzing the energy consumption of Si-Ge-Si photodetectors. The energy consumption ( $\eta_e$ ) is defined as a ratio of the by-product of a single driving voltage and total (signal and noise) current generated by the APD and given transmission bit rate [23], [51]:

$$\eta_e = \frac{u \cdot \left\langle i_o^2 \right\rangle}{br} \tag{1}$$

where u is the operating reverse voltage of single power supply, br is the transmission bit rate and  $\langle i_o^2 \rangle$  is the total current, i.e. signal and noise current, generated by the APD. The total current is characterized by the shot current noise  $\langle i_s^2 \rangle$  and thermal current noise  $\langle i_t^2 \rangle$ . Shot and thermal noise currents are given by  $\langle i_s^2 \rangle = 2qM^2(i_{ph}+i_d)F(M)\Delta f$  and  $\langle i_t^2 \rangle = \frac{(4k_BT\Delta f)}{R_l}$ , respectively. Here, q is the electron charge which is equal to  $1.60217662\times 10^{-19}$  C, M is the multiplication gain,  $i_{\rm ph}$  and  $i_{\rm d}$  are generated photo- and dark-current,  $F(M) = (k \cdot M) + (1-k)\cdot(2-1/M)$  is the avalanche excess noise,  $\Delta f$  the receiver bandwidth ( $\Delta f \approx br/2$  for a non-return-to-zero bit streams),  $k_{\rm B}$  is the Boltzmann constant, i.e.  $1.38064852\times 10^{-23} \, {\rm m}^2 {\rm kg s}^{-2} {\rm K}^{-1}$ , T is the room temperature, and  $R_1$  is the load resistance [47], [51].

Fig. 9 shows the estimated energy consumption of different Si-Ge-Si APDs as a function of detection bit rate. For this analysis, devices are either operated at the optimal reverse bias point (Fig. 9a) (i.e. corresponding to minimal power sensitivity) or at 90% of the avalanche breakdown voltage (Fig. 9(b)). APD geometries are the same as those used for the sensitivity

performance study. In all situations, the energy consumption of heterostructured APDs is very low, a few fJ/bit only. Wider APD devices (0.8 and 1 µm diodes) consume more energy than their narrower counterparts (0.3 and 0.5 μm). Energy consumption is otherwise less when operating Si-Ge-Si APDs at their optimal reverse biases (7, 8, 11, and 12.5 V), with therefore high-speed, low-noise, and high sensitivity, than at 90% of the avalanche breakdown (at 8.1, 9.9, 12.5, and 14.1 V, then). In particular, the estimated energy consumption of APDs operating at their optimal point is in the 1 to 1.5 fJ/bit range for 40 Gbps. At 90% of the avalanche breakdown, it is in the 1.7 to 3.6 fJ/bit range. The higher levels of dissipated energy in the latter case are due to sensitivity degradation, higher dark-currents and bandwidth-limited operation because of the avalanche build-up time. Nevertheless, the energy consumption of Si-Ge-Si APDs is in both situations, much lower than in conventional low-voltageoperated diodes [22], [23], [48] and can be competitive to other Si-Ge APD configurations with additional electronic amplification circuits [15]-[18], [42], [43]. This makes heterostructured Si-Ge-Si APDs promising for applications in short-reach chip interconnects, where the total energy is limited.

# IV. CONCLUSION

In summary, we conducted a comprehensive analysis of high-speed APDs based on p-i-n structures with lateral Si-Ge-Si heterojunctions. High-speed and low-noise opto-electrical performances were obtained simultaneously in those Si-foundry-compatible APDs, together with enhanced power sensitivities and really low energy consumption of a few fJ/bit. Low-cost heterostructured Si-Ge-Si photodetectors thus have a bright future in on-chip energy-hungry photonic systems.

# REFERENCES

- Q. Cheng, M. Bahadori, M. Glick, S. Rumley, and K. Bergman, "Recent advances in optical technologies for data centers: A review," *Optica*, vol. 5, no. 11, pp. 1354–1370, 2018.

- [2] S. Pasricha and M. Nikdast, "A survey of silicon photonics for energy-efficient manycore computing," *IEEE Des. Test*, vol. 37, no. 4, pp. 60–81, Aug. 2020.

- [3] M. Filer et al., "Low-margin optical networking at cloud scale [Invited]," J. Opt. Commun. Netw., vol. 11, no. 10, pp. C94–C108, 2019.

- [4] S. Bernabé et al., "Silicon photonics for terabit/s communication in data centers and exascale computers," Solid-State Electron., vol. 179, 2021, Art. no. 107928.

- [5] D. A. B. Miller, "Saving energy and increasing density in information processing using photonics," in *Proc. Opt. Fiber Commun. Conf.* 2020 OSA Tech. Dig., Optical Society of America, 2020, Paper Th1E.1.

- [6] E. Timurdogan et al., "400G silicon photonics integrated circuit transceiver chipsets for CPO, OBO, and pluggable modules," in Proc. Opt. Fiber Commun. Conf. (OFC) 2020 OSA Tech. Dig., Optical Society of America, 2020, Paper T3H.2.

- [7] R. G. Beausoleil, P. J. Kuekes, G. S. Snider, S.-Y. Wang, and R. S. Williams, "Nanoelectronic and nanophotonic interconnect," *Proc. IEEE*, vol. 96, no. 2, pp. 230–247, Feb. 2008.

- [8] A. H. Atabaki et al., "Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip," *Nature*, vol. 556, no. 7701, pp. 349–354, 2018.

- [9] W. Shi, Y. Tian, and A. Gervais, "Scaling capacity of fiber-optic transmission systems via silicon photonics," *Nanophotonics*, vol. 9, no. 16, pp. 4629–4663, 2020.

- [10] Q. Wilmart et al., "A complete Si photonics platform embedding ultra-low loss waveguides for O- and C-Band," J. Lightw. Technol., vol. 39, no. 2, pp. 532–538, Jan. 2021.

- [11] A. Rahim et al., "Open-access silicon photonics platforms in Europe," IEEE J. Sel. Topics Quantum Electron., vol. 25, no. 5, Sep. /Oct. 2019, Art. no. 8200818.

- [12] K. Giewont et al., "300-mm monolithic silicon photonics foundry technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 25, no. 5, Sep. /Oct. 2019, Art. no. 8200611.

- [13] K.-L. Lee, B. Sedighi, R. S. Tucker, H. (K.) Chow, and P. Vetter, "Energy efficiency of optical transceivers in fiber access networks [Invited]," *J. Opt. Commun. Netw.*, vol. 4, no. 9, pp. A59–A68, 2012.

- [14] B. Wang et al., "A low-voltage Si-Ge avalanche photodiode for high-speed and energy efficient silicon photonic links," J. Lightw. Technol., vol. 38, no. 12, pp. 3156–3163, Jun. 2020.

- [15] J. Zhang et al., "Compact low-power-consumption 28-Gbaud QPSK/16-QAM integrated silicon photonic/electronic coherent receiver," *IEEE Photon. J.*, vol. 8, no. 1, Feb. 2016, Art. No. 7100110.

- [16] O. Ishida, K. Takei, and E. Yamazaki, "Power efficient DSP implementation for 100G-and-beyond multi-haul coherent fiber-optic communications," in *Opt. Fiber Commun. Conf.*, OSA Technical Digest (online) (Optical Society of America, 2016, Paper W3G.3.

- [17] K. Kikuchi et al., "Silicon-photonics-based coherent optical subassembly (COSA) for ultra-compact coherent transceiver," in Proc. IEEE Compound Semicond. Integr. Circuit Symp., Miami, Florida, USA, Oct. 2017, pp. 1–3.

- [18] S. Saeedi, S. Menezo, and A. Emami, "A 25 Gbps 3D-integrated CMOS/silicon photonic optical receiver with -15 dBm sensitivity and 0.17 pJ/bit energy efficiency," in *Proc. IEEE Opt. Interconnects Conf.*, Apr. 2015, pp. 11–12, San Diego, CA, USA.

- [19] M. Nada, T. Yoshimatsu, F. Nakajima, K. Sano, and H. Matsuzaki, "A 42-GHz bandwidth avalanche photodiodes based on III-V compounds for 106-Gbit/s PAM4 applications," *J. Lightw. Technol.*, vol. 37, no. 2, pp. 260–265, Jan. 2019.

- [20] M. Nada et al., "High-speed III-V based avalanche photodiodes for optical communications—the forefront and expanding applications," Appl. Phys. Lett., vol. 116, 2020, Art. no. 140502.

- [21] D. Benedikovic *et al.*, "Silicon–germanium receivers for short-wave-infrared optoelectronics and communications," *Nanophotonics*, vol. 10, no. 3, pp. 1059–1079, 2021.

- [22] S. Assefa et al., "CMOS-integrated high-speed MSM germanium wave-guide photodetector," Opt. Exp., vol. 18, no. 5, pp. 4986–4999, 2010.

- [23] H. Pan et al., "High-speed receiver based on waveguide germanium photodetector wire-bonded to 90nm SOI CMOS amplifier," Opt. Exp., vol. 20, no. 16, pp. 18145–18155, 2012.

- [24] S. Assefa, F. Xia, and Y. A. Vlasov, "Reinventing germanium avalanche photodetector for nanophotonic on-chip optical interconnects," *Nature*, vol. 464, no. 7285, pp. 80–84, 2010.

- [25] J. Gosciniak and M. Rasras, "High-bandwidth and high-responsivity waveguide-integrated plasmonic germanium photodetector," *J. Opt. Soc. Amer. B*, vol. 36, no. 9, pp. 2481–2491, 2019.

- [26] H. Chen et al., "-1 V bias 67 GHz bandwidth Si-contacted germanium waveguide p-i-n photodetector for optical links at 56 Gbps and beyond," Opt. Exp., vol. 24, no. 5, pp. 4622–4631, 2016.

- [27] Y. Zhang et al., "A high-responsivity photodetector absent metalgermanium direct contact," Opt. Exp., vol. 22, no. 9, pp. 11367–11375, 2014.

- [28] S. Lischke et al., "High bandwidth, high responsivity waveguide-coupled germanium p-i-n photodiode," Opt. Exp., vol. 23, no. 21, pp. 27213–27220, 2015.

- [29] L. Virot et al., "Integrated waveguide PIN photodiodes exploiting lateral Si/Ge/Si heterojunction," Opt. Exp., vol. 25, no. 16, pp. 19487–19496, 2017

- [30] D. Benedikovic et al., "25 Gbps low-voltage hetero-structured silicongermanium waveguide pin photodetectors for monolithic on-chip nanophotonic architectures," Photon. Res., vol. 7, no. 4, pp. 437–444, 2019.

- [31] Y. Kang et al., "Monolithic germanium/silicon avalanche photodiodes with 340 GHz gain-bandwidth product," Nat. Photon., vol. 3, no. 59, pp. 59–63, 2009.

- [32] L. Virot et al., "Germanium avalanche receiver for low power interconnects," Nat. Commun., vol. 5, 2014, Art. no. 4957.

- [33] H. T. Chen et al., "High sensitivity 10Gb/s Si photonic receiver based on a low-voltage waveguide-coupled Ge avalanche photodetector," Opt. Exp., vol. 23, no. 2, pp. 815–822, 2015.

- [34] H. T. Chen et al., "25-Gb/s 1310-nm optical receiver based on a sub-5-V waveguide-coupled germanium avalanche photodiode," *IEEE Photon. J.*, vol. 7, no. 4, Aug. 2015, Art. no. 7902909.

- [35] Z. Huang *et al.*, "25 Gbps low-voltage waveguide Si–Ge avalanche photodiode," *Optica*, vol. 3, no. 8, pp. 793–798, 2016.

- [36] X. Zeng et al., "Silicon–germanium avalanche photodiodes with direct control of electric field in charge multiplication region," Optica, vol. 6, no. 6, pp. 772–777, 2019.

- [37] J. Zhang, B. P.-P. Kuo, and S. Radic, "64 Gb/s PAM4 and 160 Gb/s 16QAM modulation reception using a low-voltage Si-Ge waveguide-integrated APD," Opt. Exp., vol. 28, no 16, pp. 23266–23273, 2020.

- [38] B. Wang et al., "64 Gb/s low-voltage waveguide SiGe avalanche photodiodes with distributed Bragg reflectors," *Photon. Res.*, vol. 8, no. 7, pp. 1118–1123, 2020.

- [39] A. Samani et al., "Highly sensitive, 112 Gb/s O-band waveguide coupled silicon-germanium avalanche photodetectors," in Proc. Opt. Fiber Commun. Conf., Optical Society of America, 2019, Paper. Th3B.1.

- [40] O. Carpentier et al., "High gain-bandwidth waveguide coupled silicon germanium avalanche photodiode," in Proc. Conf. Lasers Electro-Opt., Optical Society of America, 2020, Paper. STh4O.3.

- [41] D. Benedikovic et al., "40 Gbps heterostructure germanium avalanche photo receiver on a silicon chip," Optica, vol. 7, no. 7, pp. 775–783, 2020.

- [42] S. Park et al., "50-Gbps receiver subsystem using Ge/Si avalanche photodiode and integrated bypass capacitor," in Proc. Opt. Fiber Commun. Conf., Optical Society of America, 2019, Paper. M3A.3.

- [43] S. A. Srinivasan et al., "Highly sensitive 56 Gbps NRZ O-band BiCMOS-silicon photonics receiver using a Ge/Si avalanche photodiode," in Proc. Opt. Fiber Commun. Conf., Optical Society of America, 2020, Paper. W4G.7.

- [44] S. A. Srinivasan *et al.*, "27 GHz silicon-contacted waveguide-coupled Ge/Si avalanche photodiode," *IEEE/OSA J. Light. Technol.*, vol. 38, no. 11, pp. 3044–3050, Jun. 2020.

- [45] S. Koester, J. Schaub, G. Dehlinger, and J. Chu, "Germanium-on-SOI infrared detectors for integrated photonic applications," *IEEE J. Sel. Top. Quantum Electr.*, vol. 12, no. 6, pp. 1489–1502, Nov./Dec. 2006.

- [46] S. J. Koester et al., "Ge-on-SOI-detector/Si-CMOS-amplifier receivers for high-performance optical-communication applications," J. Lightw. Technol., vol. 25, no 1, pp. 46–57, Jan. 2007.

- [47] L. Vivien and L. Pavesi, Handbook of Silicon Photonics. Boca Raton, CRC Press, 2013.

- [48] D. Benedikovic *et al.*, "Comprehensive study on chip-integrated germanium pin photodetectors for energy-efficient silicon interconnects," *IEEE J. Quantum Electron.*, vol. 56, no. 1, Feb. 2020, Art. no. 8400409.

- [49] R. B. Emmons, "Avalanche-photodiode frequency response," J. Appl. Phys., vol. 38, no.9, pp. 3705–3714, 1967.

- [50] R. J. McIntyre, "Multiplication noise in uniform avalanche diodes," *IEEE Trans. Electron Devices*, vol. 13, no. 1, pp. 164–168, Jan. 1966.

- [51] G. P. Agrawal, Fiber-Optics Telecommunication Systems, 3rd ed. New York, Wiley-Interscience, 2002.

Daniel Benedikovic received the M.Sc. and Ph.D. degrees in telecommunications from the University of Žilina, Slovakia, in 2011 and 2015, respectively. During his studies, he completed several successful educational and scientific internships with Aalto University, Finland, University of Málaga, Spain, and the National Research Council Canada, Canada. From 2015 to 2020, he was a Postdoc Research Fellow with the Centre de Nanosciences et de Nanotechnologies, CNRS, Université Paris-Saclay, France. He is currently a Senior Research Fellow and R&D Coordinator of optics/photonics with University of Žilina. His research interests include the development, design and characterization of active silicon-germanium devices and various passive silicon-based components and nanophotonic structures engineered with sub-wavelength grating metamaterials. He was the Recipient of the prestigious Nature Photonics Award at the IEEE International Conference on Group IV Photonics, Paris, France, in 2014.

Léopold Virot received the Engineer degree in optics, lasers, and plasma from Orléans University, France, in 2008 and the Ph.D. degree from Paris-Sud University, France, in 2014. He is currently working toward the Ph.D. degree in germanium on silicon avalanche photodetectors with STMicroelectronics and the Institut d'Electronique Fondamentale. He was a Research Engineer with Nanophotonics Laboratory, CEA-Leti, France. In 2015, he was a Postdoctoral Researcher with CEA-Leti, where he was involved in the integration of silicon photonics technology for MEMS and NEMS-based biosensing. Since 2018, he has been a Researcher with Silicon Photonics Integration Laboratory, CEA-Leti. His research interests mainly include silicon-based active and passive devices design, modeling and simulation for optical communications, quantum photonics, and emerging applications. He was the Recipient of the Young Researcher Award from the Solid State Devices and Materials (SSDM) Conference, Japan, in 2014.

Guy Aubin received the Engineer Diploma degree from the École Nationale Supérieure des Télécommunications de Bretagne (now IMT Atlantique), Brest, France, and the M.Sc. degree in information processing from the University of Rennes, France, in 1981. He taught electronics at university level during his National Service. In 1983, he was engaged with Orange Labs (formerly France Télécom R&D or CNET). He was the Head of Transmission Experimentation Group, Submarine Networks Department, Issy-les-Moulineaux. He contributed to several world premieres of optical transmission demonstrations in the laboratory and to field trials of successive generations of optical systems. In 1999, he moved to the Concept and Device for Photonics Laboratory, Bagneux, In 2001, he joined the Laboratory for Photonics and Nanostructures, Centre National de la Recherche Scientifique at Marcoussis, whose structure has been now included in the Centre of Nanoscience and Nanotechnology since 2016. There, he leads the Experimentations Fiber Optic and RF Team. His research interests include new functionalities for next-generation communication networks with innovative all-optical or optoelectronics devices.

Jean-Michel Hartmann explored, while working toward the Ph.D. degree with CEAIRIG, Grenoble, France, from 1994 to 1997, the atomic layer epitaxy of CdTe, MnTe, and MgTe for low dimensional structures. During his stay with Imperial College London, London, U.K., from 1997 to 1999, he investigated the gas source molecular beam epitaxy of Si/SiGe heterostructures for transport purposes. Since 1999, he has been a permanent position Researcher with CEA-LETI, Grenoble, where he is currently coordinating the Group-IV epitaxy activities for nanoelectronics and photonics.

**Farah Amar** received the master's degree in telecommunications and RF from Limoges University, Limoges, France, in 2016. In 2017, she joined the Centre for Nanoscience and Nanotechnology (C2N), a joint Laboratory of CNRS, University of Paris Sud, and University of Paris Saclay, France. She is currently an RF and Optoelectronic Engineer with Experimentations Fiber Optic and RF (EXPERFO) Team.

**Xavier Le Roux** joined the National Center of Scientific Research, as an Engineer, in 2004. He is currently working on the development and optimization of technological process dedicated to photonics applications and MEMS/NEMS.

Carlos Alonso-Ramos received the Ph.D. degree from the Universidad de Málaga, Spain, in June 2014, where he was involved in the development of high-performance integrated photonic circuits for chip interconnects and next-generation coherent transceivers. He is currently a CNRS Researcher with the Center for Nanoscience and Nanotechnology (C2N), Palaiseau, France. His research interests include the development of Si photonics devices and circuits in the near-and mid-infrared for applications in telecom, sensing, and quantum.

Éric Cassan has been a Professor with the University of Paris-Sud, France, since 2009. His research interests include silicon photonics, with a recent shift towards hybrid photonics on silicon for the realization of integrated optical sources and non-linear functions based on third order nonlinear effects.

**Delphine Marris-Morini** is currently a Professor with Paris Sud University, France. She has authored or coauthored more than 100 journal articles. Her research interests with the Center for Nanosciences and Nanotechnologies, include silicon photonics in the near-IR and mid-IR wavelength range. Since 2015, she has been in charge of the Group of Micro and Nanophotonic devices on silicon. She was the recipient of an ERC Starting Grant (INsPIRE) on Ge-rich photonic integrated chips towards the mid-IR wavelength range for sensing and spectroscopic application. She was also the recipient of the Bronze Medal from CNRS in 2013.

**Frédéric Boeuf** was born in 1972. He received the M.Eng. and M.Sc. degrees from the Institut National Polytechnique de Grenoble, France, in 1996 and the Ph.D. degree from the University Joseph Fourier of Grenoble, France, in 2000. Then, he joined STMicroelectronics, where he is involved in advanced devices physics and integration, advanced CMOS devices, and silicon photonics. He is currently a STMicroelectronics Fellow and also managing the Silicon Photonics Technologies Group inside STMicroelectronics's Technology and Design Platform Organization. He has authored or coauthored more than 250 technical articles.

Jean-Marc Fédéli received the Electronics Engineer Diploma degree from INPG Grenoble, in 1978. Then, he was involved with CEA-LETI in the development of various magnetic memories and magnetic components, as the Project Leader, the Group Leader, and a Program Manager. For two years, he acted as the Advanced Program Director with Memscap Company, for the development of RF-MEMS. Then, he returned to CEA-LETI in 2002, as a Coordinator of silicon photonic projects up to 2012. Under a larger research partnership, he works on many technological aspects on photonics on CMOS (Si rib and stripe waveguides, a-Si waveguides, and slot waveguides), Si modulators, Ge photodetectors, and InP integrated sources on Si. He is participating on different European projects, such as EPIXFAB for MPW circuit fabrication, and has coordinated the FP7 PLAT4M project on silicon photonics platform. Since 2014, he has been moved to sensing activities with photonics. He is currently a Technical Manager of the H2020 MIRPHAB pilot line on liquid and gas systems sensors. His H factor is around 35 with more than 200 publications and 50 patents. He has written three book chapters: one on magnetic recording and two on silicon photonics.

Bertrand Szelag received the master's degree in physics from the University of Lille, Lille, France, in 1994 and the Ph.D. degree in microelectronics from the University of Grenoble, France, in 1999. In 1997, he was a Visiting Researcher with Tohoku University, Sendai, Japan, where he was involved in the field of sub-100-nm CMOS transistor properties. In 1998, he joined Thomson Composants Specifiques. In 1999, he moved to STMicroelectronics to work on BiCMOS platform development for Analog/RF applications. He also developed devices for RF power applications. Since 2013, he has been with LETI, MINATEC Institute, Grenoble, France, as a Project Manager and a Senior Process Integration Researcher in the field of silicon photonic devices. He is currently the Head of Silicon Photonic Laboratory, CEA-LETI. He is also the author or coauthor of more than 50 articles in scientific journals and international conference proceedings in the field of CMOS, bipolar and DMOS transistors, and silicon photonic devices. His current research interests include high speed silicon modulator, germanium photodetectors, and hybrid III-V laser integration in silicon.

Laurent Vivien is currently the CNRS Director of Research with the Centre for Nanoscience and Nanotechnology (C2N), a joint Laboratory of CNRS, University of Paris Sud, France, and University of Paris Saclay, France. Since 2016, he has been also served as the Deputy Director of C2N and the Director of Photonics Department. His research interests include the development of fundamental concepts for silicon photonics, including optoelectronic and hybrid photonic devices. He demonstrated high-speed waveguide integrated germanium photodetectors and carrier depletion-based silicon modulators. He has also been at the forefront of the development of hybrid integration of carbon nanotubes on Si photonics platform and recently on high-speed Pockels effect in strained silicon waveguides. In 2015, he was the Recipient of the European Research Council (ERC) grant as a consolidator on the development of strained silicon photonics platform.