# SIMPLER MAGIC: Synthesis and Mapping of In-Memory Logic Executed in a Single Row to Improve Throughput

Rotem Ben-Hur<sup>(b)</sup>, Ronny Ronen<sup>(b)</sup>, *Fellow, IEEE*, Ameer Haj-Ali<sup>(b)</sup>, *Student Member, IEEE*, Debjyoti Bhattacharjee<sup>(b)</sup>, Adi Eliahu, Natan Peled, and Shahar Kvatinsky<sup>(b)</sup>, *Senior Member, IEEE*

Abstract—In-memory processing can dramatically improve the latency and energy consumption of computing systems by minimizing the data transfer between the memory and the processor. Efficient execution of processing operations within the memory is therefore, a highly motivated objective in modern computer architecture. This article presents a novel automatic framework for efficient implementation of arbitrary combinational logic functions within a memristive memory. Using tools from logic design, graph theory and compiler register allocation technology, we developed synthesis and in-memory mapping of logic execution in a single row (SIMPLER), a tool that optimizes the execution of in-memory logic operations in terms of throughput and area. Given a logical function, SIMPLER automatically generates a sequence of atomic memristor-aided logic (MAGIC) NOR operations and efficiently locates them within a single sizelimited memory row, reusing cells to save area when needed. This approach fully exploits the parallelism offered by the MAGIC NOR gates. It allows multiple instances of the logic function to be performed concurrently, each compressed into a single row of the memory. This virtue makes SIMPLER an attractive candidate for designing in-memory single instruction, multiple data (SIMD) operations. Compared to the previous work (that optimizes latency rather than throughput for a single function), SIMPLER achieves an average throughput improvement of 435x. When the previous tools are parallelized similarly to SIMPLER, SIMPLER achieves higher throughput of at least 5x, with 23x improvement in area and 20x improvement in area efficiency. These improvements more than fully compensate for the increase (up to 17% on average) in latency.

*Index Terms*—Logic design, logic synthesis, memristor-aided logic (MAGIC), memristive systems, memristor, memristive memory-processing unit (mMPU), throughput, von Neumann architecture.

Manuscript received January 21, 2019; revised May 24, 2019; accepted July 10, 2019. Date of publication July 30, 2019; date of current version September 18, 2020. This work was supported in part by European Research Council under the European Union's Horizon 2020 Research and Innovation Programme under Agreement 757259, and in part by the Israel Science Foundation under Grant 1514/17. This article was recommended by Associate Editor Y. Shi. (*Corresponding author: Rotem Ben-Hur.*)

R. Ben-Hur, R. Ronen, A. Eliahu, N. Peled, and S. Kvatinsky are with the Andrew and Erna Viterbi Faculty of Electrical Engineering, Technion – Israel Institute of Technology, Haifa 32000, Israel (e-mail: rotembenhur@campus.technion.ac.il; shahar@ee.technion.ac.il).

A. Haj-Ali is with the Faculty of Electrical Engineering and Computer Science, University of California at Berkeley, Berkeley, CA 94720 USA.

D. Bhattacharjee is with the School of Computer Science and Engineering, Nanyang Technological University, Singapore.

This article has supplementary downloadable material available at http://ieeexplore.ieee.org, provided by the author.

Digital Object Identifier 10.1109/TCAD.2019.2931188

# I. INTRODUCTION

BASIC assumption that has guided computer architects in the design of almost all modern computing systems is the separation between processing units and data storage units. In almost any computing system today, data is processed by the processor and stored inside the memory. Over the last few decades, computer architects have enjoyed orders of magnitude improvement in computer performance, e.g., processor speedup, reduced power consumption, and the downscale of system dimensions. This trend line was fueled by impressive technological achievements in the two principal computer components: 1) the processor and 2) the memory. Nowadays, however, it seems that both units have reached a scaling barrier, and that data processing performance is now limited mostly by the inevitable need to transfer data. The energy and delay associated with this data transfer are estimated to be several orders of magnitude higher than the cost of the computation itself [1]. This data transfer bottleneck is known as the memory wall.

Numerous methods for alleviating the memory wall have been explored. The most common method is to integrate several levels of cache memory near the processor. Cache memories can significantly reduce the amount of data transferred between the processor and the memory [2], but do not fully eliminate this need. A relatively more recent (and less prevalent) approach is to integrate processing units within memory elements. The idea of combining processing units within DRAM and SRAM cells was explored in [3]–[5]. However, the potential benefits of in-memory computing were not fully exploited in these works, as they still required data transfer between storage and processing elements. In most common technologies, conventional memory cells are in fact ill-suited for performing direct computations.

The breakthrough in the field of in-memory computing came with the emergence of new memory technologies that can be used to perform logic operations, in addition to their traditional data storage capabilities. Some of these technologies are based on novel electrical elements called memristors [6]. Memristors are used to modulate data into resistance, where high and low resistances represent logical "0" and "1," respectively. Memristors are actually passive elements with very promising capabilities. They can change their resistance as a result of the voltage applied across them, and their high density, nonvolatility, low power consumption, and CMOS fabrication

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

compatibility [7], [8] offer huge potential improvements over current cell technologies. Furthermore, memristors can be used to perform logic operations, enabling processing within the memory [9]–[12]. Resistive random access memories (RRAMs) [13] have paved the way for combining processing and memory, since they allow the same physical entities to be used for both [9]–[12].

An attractive approach for performing logic within a conventional memristive memory array is stateful logic, where logical states of logic gates are represented by resistance and the logic gates are constructed solely by memristors. The inputs of a logic gate are the logical states of the memristors before the execution of the logical operation associated with the gate. Likewise, the output of the gate is the state of the memristor after the execution of the logical operation associated with the gate.

Several stateful logic families compatible with memristive memories have been proposed in this context [14], [15]. A leading candidate among these is memristor-aided logic (MAGIC) [16]. MAGIC has been shown to outperform competing methods [17], while enabling a full implementation within a standard memristive memory array. The basic MAGIC gate executes a logical NOR operation. Since NOR is a complete logic function, a MAGIC NOR gate is sufficient for the execution of any logical operation within the memory: the desired logic function is divided into a sequence of MAGIC NOR operations. In what follows, we refer to a single execution of a function with specific inputs as a computation instance (or as an instance). MAGIC NOR gates can be applied anywhere within the memory array, using the same cells and structure, where the stored data functions as input for the logical operation.

The integration of data storage capabilities with MAGICbased processing within memristive memories has led to the development of the memristive memory processing unit (mMPU) [18]. This novel architecture replaces conventional DRAM memory with a memory that is, also capable of performing general-purpose computing. The mMPU consists of standard memristive memory arrays, with only minor modifications to the CMOS periphery and control circuits to allow support for computations as well as conventional data read and write operations. The mMPU is therefore, completely compatible with standard von Neumann architectures, as it can operate either as a hybrid memory-processing unit or as a standard memory. Nevertheless, the advantages of a memristive crossbar array, e.g., density and nonvolatility, are maintained in the mMPU architecture.

To perform a computation within the mMPU, a compute command is received by the mMPU controller [19]. The controller interprets the command and converts it into a sequence of MAGIC operations. It then sends the corresponding control signals to the memristive memory arrays to perform the actual logic operations. To realize the full potential of the mMPU, the desired computation must be converted into an efficient sequence of MAGIC operations. Such a sequence should involve a small number of computational steps, utilize only a limited area within the array, and consume low energy. Several such sequences were proposed for some popular arithmetic operations and shown to be relatively efficient. The studied functions include fixed-point addition and multiplication [17], [20], [21], and convolution [22]. However, all of these works relied on manual crafting and optimization of the sequence of operations, designed for a specific logical function. Obviously, this is neither a general, nor optimal, design methodology. Furthermore, manual designs are naturally time consuming and error-prone, hence prolonging the time-to-market of any future product.

Recent work has focused on automatic conversion of arbitrary logical functions to a sequence of executions within the memory. In [23] and [24], tools were developed to generate execution sequences for arbitrary logical functions, while minimizing the computational latency in a memristive memory setup. Latency is minimized for a single computation instance by exploiting parallelism features of in-memory stateful logic operations so to execute several NOR operations within an instance in a single cycle. However, because multiple rows and columns must be utilized, this optimized latency comes at the cost of disabling significant areas within the array, since many cells are unused for the computation. Additionally, numerous instances of the same logical function within a given memory array can only be executed serially in this method.

In this article, we take a different approach: we improve the performance of the mMPU by maximizing the *throughput* rather than minimizing the *latency*. We work under the single instruction, multiple data (SIMD) [2] concept, exploiting parallelism among different computation instances rather than optimizing a single instance of a given logical function. In this model, the mMPU will perform a series of identical computations (differing only in the input data) on many computation instances. We present a novel synthesis and mapping tool called synthesis and in-memory mapping of logic execution in a single row (SIMPLER).<sup>1</sup> SIMPLER unleashes the full potential of parallel computations offered by in-memory executions within a memristive array, in the SIMD setup.

As a synthesis tool, SIMPLER outperforms the previous work by performing *in parallel* multiple instances of computations associated with a given logical function. Thus, although the latency of a single computation instance may be slightly higher, the overall throughput of the array increases dramatically thanks to the ability to compute each instance in a different row in parallel. Such a configuration allows SIMD operations to be supported efficiently in an mMPU setup for the first time. The magnitude of this paradigm change is illustrated by a simple, realistic example: a system consisting of a 512-row memory array can execute 512 computation instances in parallel. Even at  $4 \times$  longer latency, the system provides an astonishing  $128 \times$  higher throughput.

SIMPLER represents a fundamental shift in the design of in-memory computing systems. New challenges that arise in this novel, throughput-oriented, approach are all solved using SIMPLER. In this context, SIMPLER makes the following contributions.

<sup>1</sup>The SIMPLER tool may be found at: https://github.com/ RotemBenHur/SIMPLER-MAGIC.git.

- Automates the process of generating in-memory MAGIC NOR execution sequences to improve the throughput of the computation and allow efficient SIMD executions.

- Compresses relatively complex computations into a single finite size memory row by efficient reuse of cells when necessary.

- Reduced Tool Complexity: SIMPLER uses efficient compiler like register allocation technology to generate an optimized mapping for huge computations within seconds.

Compared to the previous work that optimizes latency rather than throughput for a single function [24], [25], SIMPLER achieves an average throughput improvement of over  $435 \times$ for a memory array with 512 rows. When the previous tools are parallelized in a similar manner to SIMPLER, SIMPLER offers at least  $5 \times$  higher throughput and  $23 \times$  smaller area usage.

# II. PRELIMINARIES AND MOTIVATION

All in-memory computations in this article rely on the basic MAGIC NOR operation. We first explain MAGIC and how it motivates our choice to optimize throughput in Section II-A. Then, we describe a motivational example to explain and support this choice in Section II-B. Next, we survey the relevant related work in Section II-C. Finally, we formally define the problem this article solves in Section II-D.

### A. Preliminaries and Definitions

The MAGIC NOR gate is performed by applying voltage(s) to the input(s) and output memristors. The state of the output memory cell changes in accordance with the logical states of the memristors. The advantages of MAGIC over other stateful logic techniques include the separation between the input(s) and output memristors, the need for only a single execution voltage (called  $V_g$ ), and the lack of additional periphery elements [17]. The *N*-input NOR gate operation requires two steps (clock cycles).

- 1) A logical "1" is written to the output memristor by applying a voltage, denoted  $V_{w1}$ , across it.

- 2)  $V_g$  is applied to all N inputs, and the ground is connected to the output.

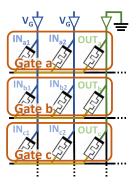

A single-input NOR is a NOT gate; hence, both *N*-input NOR and NOT gates may be executed by MAGIC. Fig. 1 illustrates the in-memory execution of three MAGIC NOR gates, each using three cells: two for the inputs and one for the output. The inputs and output of a single gate need not be located in adjacent cells; the only requirement is that they be located on the same row (MAGIC row operation), or column (MAGIC column operation). To perform both MAGIC row and MAGIC column operations, a transpose memory [17] is required.

Since a NOR operation spans the complete set of Boolean operations, a MAGIC NOR gate is sufficient to execute any desired logic function. Hence, MAGIC NOR may be used as the basic computing element for all kinds of processing within the memory by dividing the desired function into a sequence of MAGIC NOR operations (execution sequence). The execution

Fig. 1. Parallel execution of the three aligned MAGIC NOR gates.

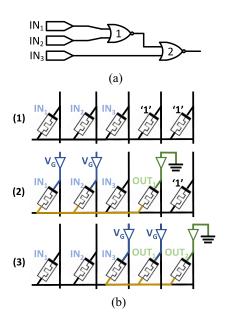

Fig. 2. Serial execution of two MAGIC NOR gates in a single row. (a) Two-gate netlist. (b) Execution of the netlist in three steps (clock cycles). 1) Writing a logical "1" to the output memristors (initialization). 2) Gate 1 execution—NOR( $IN_1$ ,  $IN_2$ ). 3) Gate 2 execution—NOR( $IN_3$ ,  $OUT_1$ ).

of a sequence of two two-input MAGIC NOR gates is shown in Fig. 2. These basic NOR operations are performed serially using the memory cells, where the output of the first MAGIC gate acts as one of the inputs of the second gate during the second stage (cycle) of the computation. Serially executing all the gates in the sequence may be time consuming. Aligning the inputs and outputs of different MAGIC NOR gates allows them to be executed in parallel, as illustrated in Fig. 1. Wisely exploiting this property may either improve the latency of a logic function or the throughput of an SIMD operation.

The latency may be improved by parallelizing several gates of the NOR execution sequence belonging to the same single instance, using multiple rows for the execution of a single instance [23]. The throughput may be improved by parallelizing the execution of many instances of the same logic function: each instance is placed in a different row.

In our context, throughput is defined as

Throughput =

$$\frac{\#instances}{Latency}$$

(1)

Fig. 3. (a) Single-bit full adder (1-bit FA) netlist. (b) Single 1-bit FA execution using an  $11 \times 3$  array. Each green cell initially stores the inputs. Each orange cell *gi* stores the result of gate *i*. Gates *g*1 and *g*2 (yellow rectangles) are executed in parallel during the first clock cycle, and gates *g*4 and *g*5 (gray rectangles) are executed in parallel during the second clock cycle. All other gates are executed serially. The total execution time is therefore 10 clock cycles, but parallelizing instances is difficult. (c) *N* 1-bit FA operations executed in parallel. Each FA operation is allocated to a single row. Each green cell initially stores the inputs. Since they are all aligned, all *N* FA operations are executed in a single clock cycle. Since there are enough columns for computation, no initialization cycles are necessary, and the execution time is 12 cycles, in accordance with the number of gates.

where #instances is the number of instances of the function performed in parallel (=#rows), and Latency is the number of clock cycles required for the computation. The throughput increases linearly with the number of instances.

When the row is wide enough to hold all the inputs and gates required to execute the desired function (number of columns  $\geq$  number of inputs + number of gates), the computation fits easily into that row, and the number of execution steps (clock cycles) is equal to the number of gates. However, if the row is not wide enough (number of columns < number of inputs + number of gates), the computation must be split into different rows or cells must be reused.

A cell can be reused when it stores data no longer needed for the rest of the computation, i.e., all its consumers have already been computed. A cell must be initialized before reuse. Because MAGIC requires that a logical "1" be initially written to the output memristor, a cell is reinitialized by writing a "1" to it. We assume that all desired cells within a row can be reinitialized in a single clock cycle, by applying  $V_{w1}$  to their columns and connecting the row to ground. Reinitializations that take more than a single-clock cycle is addressed in Section IV. The overall number of total cell initializations does not change because of cell reuse. Every MAGIC write has to be preceded by a cell initialization, so the total number of writes remains the same regardless of cell reuse; only their timing is different. Depending on the desired computation and the number of cells available for it, cell reuse may or may not suffice. The execution order of the gates of a given computation determines the number of cells that can be reused at a given time; thus, a mapping will be found only if the execution order of the gates is efficient. For large logic functions, all of the cells might still be

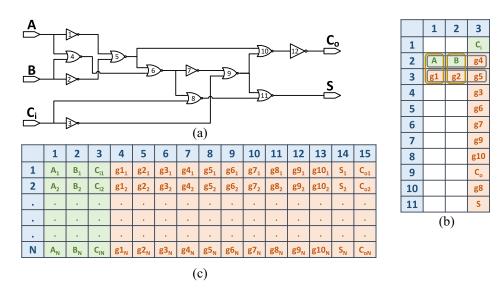

Fig. 4. Execution of the *1-bit full adder* netlist using a single row of the memory with nine columns, following the execution order detailed in Fig. 6. The states of the row during different stages of the computation are as follows. (a) Initial state of the row. (b) Serial calculation of the first six gates. (c) Initialization of the three gate results not required as inputs for future computations. (d) Serial calculation of the next three gates. (e) Initialization of the three gate results not required as inputs for future computations. (f) Serial calculation of the last three gates.

required for reinitialization, because there are no unneeded cells to free. Consequently, the tool fails to find a possible mapping.

Since the row has to be large enough for complex executions, the size of the memory array limits the complexity of the computations that can be executed in-memory. In conventional DRAM memories, the smallest unit is called an MAT. Usually, a DRAM MAT consists of an array of  $512 \times 512$ memory cells. In memristive memories, an MAT may contain up to  $512 \times 512$  cells in transistor-less memristive arrays and up to  $2048 \times 8192$  in 1T1R arrays [8]. Using a single MAT to execute a given function yields better latency and energy consumption. In contrast, distributing a single computation instance over more than a single MAT requires data transfer between the MATs, significantly reducing the benefits of in-memory computation [26]. However, the same computation can be parallelized over different data in different MATs. In this article, we consider an MAT size of  $512 \times 512$ . This size allows us to maintain the conventional DRAM structure while supporting in-memory execution of relatively large functions (large number of MAT columns) and improving the parallelism (large number of MAT rows). To show the potential of executing larger functions, we report some results with a  $1024 \times 1024$ MAT size.

### B. Motivational Example

To further clarify the definitions and explanations from the previous section, we describe an example of a single-bit full adder, consisting of 12 gates,<sup>2</sup> as described in Fig. 3(a). To improve the latency of a single instance of the full adder, it is executed using an  $11 \times 3$  memory array. Two pairs of NOR operations are parallelized, and the execution takes 10 clock cycles, as shown in Fig. 3(b).

The throughput of the full adder can be improved by executing N instances in parallel using an  $N \times 15$  array. Each instance is executed using a single row, and the number of execution steps (clock cycles) is 12, in accordance with the number of NOR and NOT gates (independent of the value of N), as demonstrated in Fig. 3(c). In this case, row size = 15 columns = 12 gates + 3 inputs; hence, no reinitialization cycles are required. A row with fewer than 15 columns is too small to execute all the gates. Cells must be reinitialized in this case. If, for example, the instance is executed using a 9-cell row, two reinitialization cycles will suffice when the execution order is chosen wisely, as described in Fig. 4. On the other hand, when the row size is less than 8, reinitialization will not help, and no mapping exists, regardless of the execution order.

### C. Related Work

Techniques for mapping an execution of complex functions into a limited-size MAT were previously proposed. The two leading approaches are: 1) to automatically improve the latency of a single computation instance by executing different gates of the same instance in parallel and 2) to manually improve the throughput by executing different instances of the same logic function in parallel.

In our previous work, we developed synthesis and inmemory mapping of logic execution for MAGIC (SIMPLE MAGIC) [23], a tool for improving the latency of a single instance by using both MAGIC row and column operations to exploit the parallelism within that instance. Without reusing cells, SIMPLE maps the gates of the same instance of a function to the memory array so that as many gates as possible of the same computing instance are aligned in either rows or columns; therefore, many gates can be performed in parallel. To achieve the best mapping, SIMPLE solves an optimization problem that minimizes the latency, area or/and energy. SIMPLE improves the latency by 48% on average as compared to a single row execution (without reusing cells).

Motivated by the computational burden of solving optimization problems, Yadav *et al.* [24] suggested heuristics for finding a mapping. Instead of generating the mapping with the maximum number of aligned gates (thus, with maximum parallelism and minimum latency), the unaligned gate outputs required as inputs for other gates were moved by adding copy cycles. Their method resulted in a latency increase of 4.9% and an average area increase of  $4.7\times$  as compared to serial execution using a single row.

To alleviate the copy cycles overhead, the authors of SAID [25] proposed an improved heuristics that uses a lookup table-based synthesis, based on a sum-of-products (SoP) representation, to increase the number of gates executed in parallel. SAID reduces the latency by 28% compared to serial execution using a single row, but increases the area by  $8.6 \times$ .

Talati *et al.* [17] proposed that each logic function be mapped into a single row. Parallelism within a single computation instance is not allowed, meaning that the gates are executed serially. Therefore, the latency of the execution (in terms of the number of clock cycles) equals the number of NOR and NOT gates in the execution sequence of that logic function, which is not minimized. Additionally, cell reuse is not supported. Unfeasibly wide rows are thus required to execute large logic functions. In [22], manually crafted algorithms that reuse cells are proposed to solve this problem.

Cell reuse allows larger functions to be feasibly executed inside the size-limited memory arrays. However, manual implementation of complex algorithms (with and without cell reuse) is very tedious and error prone. The variety of functions they can fit in a restricted memory row size is therefore, quite limited. In contrast, SIMPLER automatically generates the execution sequence that allows maximum cell reuse when necessary. For example, SIMPLER reduces the minimum required number of cells for the execution of an 8-bit multiplier from 77 (in [22]) to 65, and reduces the execution latency using a row size of 77 cells from 918 cycles to 699.

Efficient in-memory execution of SIMD operations yields significantly higher throughput than low latency execution of a single computation instance. This motivated our choice to automatically map the function execution into a single row.

# D. Problem Definition and Complexity

The problem we address in this article is similar to the problem discussed in [27]. The problem is generating an execution sequence *ES* that uses the minimum number of memory cells (smallest row). It is formally defined as follows.

Problem Statement 1: Given a data dependence graph G that represents a logical function, derive an execution sequence ES for G that is, optimal in the sense that the number of memory cells required for executing the graph is minimal.

For a general directed acyclic graph (DAG), the problem is known to be NP-complete [28]. We therefore, propose heuristics to find an optimized mapping in a linear complexity.

<sup>&</sup>lt;sup>2</sup>The best known full adder consists of nine two-input NOR Gates. We use a 12-gate full adder to better explain various aspects of the SIMPLER tool.

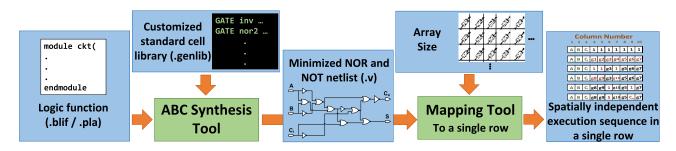

Fig. 5. SIMPLER general flow. The ABC synthesis tool receives an arbitrary logic function and a modified library, and produces a minimized NOR and NOT netlist. An in-house Python-based mapping tool receives the netlist along with the possible memory array size and produces the execution sequence.

# **III. SIMPLER MAPPING ALGORITHM**

The SIMPLER flow is divided into two main stages, as shown in Fig. 5.

1) ABC Synthesis Tool: Similarly to [23], the first stage is the ABC synthesis tool [29] with a modified cell library. ABC receives an arbitrary logic function in a .pla or .blif format, and produces a NOR and NOT netlist in a verilog format, while minimizing the number of gates.

2) *SIMPLER Mapping Tool:* The second stage is the SIMPLER mapping tool, an in-house Python script that does the following.

- Receives the minimized NOR and NOT netlist and the number of cells within the memory row dedicated to the computation.

- 2) Maps all netlist gates to that single row by determining the locations (column/cell number) of each input and output of the gate and the timing (clock cycle number) in which it is executed.

- 3) Adds reinitialization cycles when cells must be reused.

In the next sections, the SIMPLER mapping algorithm is described. Section III-A discusses the assumptions and considerations for optimizing the in-memory execution. In Section III-B, the mapping of the netlist gates into the memory row is described. The complexity of the algorithm is then discussed in Section III-C.

### A. Principles for Efficient Mapping Into the Memory

The mapping of a computation to the memory cells is produced by first determining the execution order of the gates and then deciding to which free cell each gate is allocated. The order influences the number of cells required for the entire execution, as some gates may be freed earlier than others; thus more cells may be reused during prior stages of the computation. To minimize the required number of cells, we use a register allocation technique that minimizes the number of registers necessary for a computation [30]. This technique requires first performing a reduction from the NOR and NOT netlist to a DAG

$$vertex_i \leftarrow gate_i$$

(2)

$$edge_i \leftarrow wire_i$$

(3)

for all *i* gates in the netlist. Therefore, the DAG's roots are the gates whose outputs are connected only to the function outputs, and its leaves are the gates whose inputs are connected

Fig. 6. Reduction from one-bit full adder netlist [Fig. 3(a)] to a DAG, where each vertex represents a gate and each blue edge represents a wire. The green arrows represent the direction the signals propagate in the original netlist. The FO and the CU are, respectively, the FO and the CU values of each vertex. The order of the execution sequence is determined according to the CU values.

only to the function inputs. Additionally, each vertex receives a fan out (FO) value according to the number of vertices its output is connected to. For example, a reduction of the one-bit full adder netlist from Fig. 3(a) to a DAG is shown in Fig. 6.

To maximize the number of cells that may be reused at a given time, the following two principles should be considered while determining the execution order.

- Use Depth-First Search (DFS) rather than breadth-first search (BFS) [31], i.e., start from the root node(s) and traverse along each branch as far as possible. A node V is inserted into the execution sequence on the way back up if either: 1) V is a leaf or 2) all children of V are in the sequence. For example, if the execution order of the DAG in Fig. 6 is determined according to BFS: g1 → g2 → g4 → g3 → g5, then after five cell allocations, only two may be reused (g1, g2). However, with DFS, the order is g1 → g2 → g5 → g4 → g6, and then after five cell allocations, four cells may be reused (g1, g2, g5, g4).

- 2) The Quality of the Execution Order Depends on the Order of Traversal Among the Node's Children: Our heuristic for determining the order is to first execute subgraphs that require more cells for their execution.

For example, in Fig. 6, g6 has two subgraphs: g5 and g4, which require, respectively, execution of three cells and a single cell. If subgraph g5 is executed first, then at least three cells are required for the execution of g6 [g5, g4, g6, in the cycle that g6 = NOR(g4, g5) is executed, since the cells of g1, g2 are reused]. On the other hand, if subgraph g4 is executed first, then at least four cells are required for the execution of g6 [g4, g1, g2, g5, in the cycle that g5 = NOR(g1, g2) is executed].

To determine the minimum number of cells required for the execution of each subgraph, our algorithm follows the generalized Strahler algorithm proposed in [30], which uses the Strahler number [32] to determine the minimal number of registers needed to compute an arithmetic expression tree. In the SIMPLER algorithm, this number is called cell usage (CU), and it is calculated for each vertex. The CU represents an estimation for the number of memory cells known to be sufficient for executing the subtree of each vertex. As previously stated, the execution of a MAGIC logic gate also requires a memory cell for its output. Therefore, CU + 1 of a vertex is the estimated sufficient number of memory cells for the entire execution of that vertex (after execution of all its descendants and reusing cells when possible). For example, as discussed in the previous paragraph, to execute g6 from Fig. 6, three cells are enough when choosing the right execution order (CU(g6) = 2).

The Strahler algorithm [30] is intended for trees only. However, in our case the netlist is reduced to a DAG, since some gates may be connected to several parents or ancestors, i.e., their FO is larger than 1. As a result, the CU + 1value does not predict the minimum number of cells accurately. For example, CU(g9) = 2, but when the execution order is  $g1 \rightarrow g2 \rightarrow g5 \rightarrow g4 \rightarrow g6 \rightarrow g7 \rightarrow g3 \rightarrow g9 \rightarrow g8$ , four cells are required when g9 is executed. The reason is that FO(g6) = 2; thus, while executing g9, g6 is still needed for the execution of g8. Therefore, g6 may not be freed after g7 is executed. Consequently, during the execution of g9, four cells are occupied by the following gates: g6, g7, g3, g9. As a result, determining the execution order according to the Strahler number alone, while perfectly correct, does not necessarily produce the optimal execution. More optimal cell ordering should be evaluated in the future work.

# B. Mapping Execution Sequence of Logic Functions Into Single Row

The mapping algorithm, presented in Algorithm 1, in Appendix A in the supplementary material, receives the netlist as a directed graph G = (V, E) representation (V and E are, respectively, the sets of nodes and edges), along with the number of cells dedicated for the computation (row size), and produces a mapping of the nodes to that limited-size row. In the initial state of the memory, when a computation is started, all inputs are stored in a single row, in adjacent cells. (This is not in fact mandatory for in-memory execution of MAGIC, but the algorithm works this way for simplicity and without loss of generality since the locations of the inputs are irrelevant because the mapping is arbitrary.) The mapping is done by traversing all vertices of the DAG twice: 1) once to determine the execution order by calculating a CU value for each vertex and 2) again, using the order imposed by the CU values, to allocate the vertices into the available memory cells. Both traversals are done by starting from all the DAG roots (the gates that produce an output of the netlist, e.g., vertices g12 and g11 in Fig. 6) to the leaves [gates connected only to the input(s) of the netlist, e.g., vertices g1-g4 in Fig. 6].

The stages of the mapping are as follows.

1) Stage 1—Compute the Cell Usage Value for Each Vertex: In this stage, the CU value is computed for each vertex, by function *ComputeCU*, as detailed in Algorithm 2, in Appendix A in the supplementary material. The CU is computed by traversing all of the vertices, starting from each one of the roots, and continuing to the leaves. A CU value is assigned to a vertex only if all its children were already given a CU value. The CU of a given vertex V is determined according to the following rules.

- 1) If V is a leaf (i.e., all of the inputs of V are also inputs of the function): CU(V) = 1.

- 2) *Else:* Sort all *N* children of *V* by descending order of their CU values. Then:

$CU(V) = \max{CU(V_{child,i}) + i - 1}, \forall i = (1 \text{ to } N).$ *Explanation:* When executing child *i*, all *i* - 1 children must already be allocated, and  $CU(V_{child,i})$  is the estimation of the number of cells necessary for executing child *i*'s subtree. Therefore, for the execution of child *i*, the number of cells is  $CU(V_{child,i}) + i - 1$ . Therefore, the number of cells sufficient for executing *V*'s subtree (CU(V)) is  $\max{CU(V_{child,i}) + i - 1}, \forall i = (1 \text{ to } N).$

An example of the CU values of a single-bit full adder is given in Fig. 6.

2) Stage 2—Allocate the Gates to the Memory Cells: In this stage, the gates are allocated to the memory cells, and each allocation is assigned an execution clock cycle number *t*. This number is assigned by functions AllocateRow and AllocateCell, which are detailed in Algorithms 3 and 4, in Appendix A in the supplementary material, respectively. The graph is traversed again, starting from the roots, and continuing to the leaves. The child with the larger CU value is traversed first. For example, when traversing the graph in Fig. 6, g5 is traversed before g4 from g6, since CU(g5) = 2 > CU(g4) = 1. When a gate whose children were already allocated to cells (i.e., executed) is reached, it can also be executed (since all its inputs are ready). For example, in Fig. 6, the execution order when starting with the root g11 is either:

- 1)  $g1 \rightarrow g2 \rightarrow g5 \rightarrow g4 \rightarrow g6 \rightarrow g8 \rightarrow g7 \rightarrow g3 \rightarrow g9 \rightarrow g11 \rightarrow g10 \rightarrow g12 \text{ or;}$

- 2)  $g1 \rightarrow g2 \rightarrow g5 \rightarrow g4 \rightarrow g6 \rightarrow g7 \rightarrow g3 \rightarrow g9 \rightarrow$  $g8 \rightarrow g11 \rightarrow g10 \rightarrow g12$

since CU(g8) = CU(g9); thus no priority between them is defined. In future work, priorities between vertices with equal CU values and priorities between different roots should be explored. The gate that is ready for execution is allocated to a free cell, and t is incremented by 1. If no free cells are left, the cells that store the outputs of the gates that are no longer needed are all reinitialized in a single cycle; thus t

TABLE I

COMPARISON BETWEEN SIMPLE MAGIC [23] WITH 512 × 512 MEMORY ARRAY SIZE AND SIMPLER, BOTH USING NOR2 NETLISTS

|            | Original Netlist |      | ABC SIMPLE MAGIC [23] |             |             |       |                                                                         |      |                  |                                                        |      | SIN                                            | Comparison - SIMPLER/SIMPLE |                                                        |       |         |       |       |         |

|------------|------------------|------|-----------------------|-------------|-------------|-------|-------------------------------------------------------------------------|------|------------------|--------------------------------------------------------|------|------------------------------------------------|-----------------------------|--------------------------------------------------------|-------|---------|-------|-------|---------|

| Benchmarks | #In              | #Out | #Gates                | #CycSinInst | #CycAllInst | #Inst | $\begin{bmatrix} TP \\ \left[\frac{\#Inst}{\#cyc}\right] \end{bmatrix}$ | #Mem | Area<br>[#cells] | AreaEff $\left[\frac{10^6}{\#cyc\cdot \#cells}\right]$ | #Cyc | $\frac{TP}{\left[\frac{\#Inst}{\#cyc}\right]}$ | Area=#Mem<br>[#cells]       | AreaEff $\left[\frac{10^6}{\#cyc\cdot \#cells}\right]$ | #Cyc  | AreaCom | SinTP | ParTP | AreaEff |

| 5xp1       | 7                | 10   | 112                   | 97          | 886         | 680   | 0.767                                                                   | 142  | 3x105            | 3.76                                                   | 119  | 4.30                                           | 39                          | 226                                                    | 13.4% | 8.08x   | 417x  | 5.61x | 60.1x   |

| clip       | 9                | 5    | 152                   | 136         | 742         | 510   | 0.687                                                                   | 184  | 3x148            | 3.18                                                   | 160  | 3.20                                           | 47                          | 139                                                    | 21.6% | 9.45x   | 435x  | 4.66x | 43.8    |

| cm150a     | 21               | 1    | 62                    | 51          | 570         | 1360  | 2.386                                                                   | 87   | 3x63             | 9.73                                                   | 67   | 7.64                                           | 39                          | 401                                                    | 11.8% | 4.85x   | 390x  | 3.20x | 41.2x   |

| cm162a     | 14               | 5    | 60                    | 46          | 530         | 1360  | 2.566                                                                   | 92   | 3x62             | 10.64                                                  | 64   | 8.00                                           | 35                          | 468                                                    | 12.1% | 5.31x   | 368x  | 3.12x | 44.0x   |

| cm163a     | 16               | 5    | 61                    | 45          | 522         | 1360  | 2.605                                                                   | 95   | 3x61             | 10.98                                                  | 66   | 7.76                                           | 36                          | 441                                                    | 12.6% | 5.08x   | 349x  | 2.98x | 40.2x   |

| misex l    | 8                | 7    | 78                    | 45          | 1380        | 864   | 0.626                                                                   | 112  | 14x21            | 2.58                                                   | 83   | 6.17                                           | 33                          | 383                                                    | 6.0%  | 8.91x   | 278x  | 9.85x | 148.1x  |

| parity     | 16               | 1    | 76                    | 37          | 1078        | 1050  | 0.974                                                                   | 107  | 20x12            | 4.05                                                   | 81   | 6.32                                           | 35                          | 370                                                    | 7.5%  | 6.86x   | 234x  | 6.49x | 91.3x   |

| x2         | 10               | 7    | 68                    | 36          | 1404        | 1512  | 1.077                                                                   | 86   | 12x14            | 4.45                                                   | 73   | 7.01                                           | 33                          | 435                                                    | 5.2%  | 5.09x   | 252x  | 6.51x | 97.9    |

|            |                  |      |                       |             |             |       |                                                                         |      |                  |                                                        |      |                                                |                             | Geomean:                                               | 10.3% | 6.48x   | 332x  | 4.88x | 63.2x   |

is also incremented by 1. Consequently, there is more space available for mapping the outputs of the next gates; thus, the gate is allocated, with another increment of t.

To determine that the output of a gate is not needed as input for future gates, the FO value is computed for each gate. When a gate is allocated, the FO values of all gates connected to its inputs are reduced by one. Therefore, during the initialization cycle, the cells of the gates with FO = 0 may be freed and reused, since they are not needed as inputs for any future gate. For example, the mapping of a single-bit full adder into 9 cells is given in Fig. 4. The total number of cycles is 14, 2 of which are dedicated for initialization. In the first initialization cycle, gates g1, g2, and g4 are reused. However, g5 and g6 cannot be freed yet, since FO(g5) = FO(g6) = 2 and during the first initialization cycle only one of their parents nodes was executed (g6 is parent of g5 and g8 is parent of g6).

When all the netlist gates are mapped, the mapping tool prints the produced mapping and the required number of initialization cycles. When there is no possible mapping, the tool reports it.

### C. SIMPLER Complexity

We evaluated SIMPLER complexity and found it to be O(|V|), where |V| is the number of vertices in the graph (# of gates). The analysis is as follows [where |E| is the number of edges (wires), and N is the row size used for allocation].

- 1) The maximum number of edges entering a vertex depends on the type of gate used: 2 and 4 for NOR gates with, respectively, 2 and 4 inputs. Hence,  $|E| < 4 \cdot |V|$  or  $O(|E|) \le O(|V|)$ .

- 2) We use DFS in both stages. Classical DFS has complexity of O(|V| + |E|); hence, in our case it is O(|V|).

- 3) In stage 1, for each vertex we sort the incoming edges according to the CU of the vertices they came from. Since the number of incoming edges is limited to 2 or 4, this is basically a (small) constant cost.

- 4) In stage 2, allocating a cell for a vertex involves searching for a free cell and changing its state as needed. The complexity of this search is O(1), achieved by using linked-lists to link all cells with the same state.

All in all, SIMPLER complexity is linear with the number of vertices in the graph. This low complexity results in a fast execution time. As an example, SIMPLER maps a graph with over 12K vertices, independent of the memory row size, in less than 0.6 s on a client notebook (HP EliteBook 840, Intel Core i7, 16-GB RAM, and 512-GB SATA SSD).

# IV. EXPERIMENTAL RESULTS AND EVALUATION

We evaluate the SIMPLER synthesis and mapping tool by calculating the latency, throughput, area, and area efficiency of each benchmark execution using the Python-based tool we developed. Additionally, we compare SIMPLER to other tools by assessing its ease of use and the time it takes to generate the mapping. The netlists we use consist of *N*-input NOR gates, where either: 1)  $N \in \{1, 2\}$ , i.e., NOT gates and two-input NOR gates (NOR2) or 2)  $N \in \{1, 2, 3, 4\}$  (NOR4). The evaluation consists of three parts.

- 1) Comparison to other mapping tools: SIMPLE MAGIC [23], Yadav *et al.* [24] (referred as *YADAV* for the rest of this article) and SAID [25]. For each comparison, we use the benchmark suites used by the original authors. For both SIMPLE and YADAV we use NOR2 netlists, and for SAID we use NOR4, similarly to each work. Tables I–III list the results of the comparison with, respectively, SIMPLE MAGIC, YADAV, and SAID.

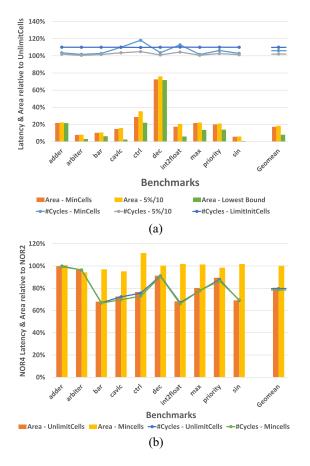

- 2) Evaluation of SIMPLER on the EPFL combinational benchmark suite [33]. EPFL is a quite large, modern benchmark suite designed to challenge modern logic optimization tools. The tradeoff between the area and the performance (latency and throughput) is examined. The SIMPLER tool is very efficient and produces the mapping for each of the EPFL benchmarks within seconds. The SIMPLER EPFL results are given for both NOR2 and NOR4. These results will be useful for comparison with future work, and are detailed in Table IV.

- 3) Comparison to Optimal SIMPLER (OptiSIMPLER)<sup>3</sup>: OptiSIMPLER tries to determine the minimum area (in terms of number of cells) required for the execution of a function using a single row of the memory by reusing cells, and then to find the minimal latency possible for this area. We developed OptiSIMPLER as part of this article on SIMPLER to assess SIMPLER's benefits. OptiSIMPLER works by solving an optimization

<sup>3</sup>The OptiSIMPLER tool may be found at: https://github.com/ debjyoti0891/arche.git.

TABLE II

Comparison Between YADAV [24] With 512 × 512 Memory Array Size (1024 × 1024 for Last Three Benchmarks) and SIMPLER, Both Using Nor2 Netlists

|            | Origi | nal Netlist | ABC    | YADAV [24]  |       |                                                                                                                      |      |                  |                                                                          |      | SIMPL                                                     | ER (this work         | )                                                                          | Co     | Comparison - SIMPLER/YADAV |       |       |         |

|------------|-------|-------------|--------|-------------|-------|----------------------------------------------------------------------------------------------------------------------|------|------------------|--------------------------------------------------------------------------|------|-----------------------------------------------------------|-----------------------|----------------------------------------------------------------------------|--------|----------------------------|-------|-------|---------|

| Benchmarks | #In   | #Out        | #Gates | #CycSinInst | #Inst | $ \begin{array}{c} \textbf{TP} \text{ (Upper Bound)} \\ \left[ \frac{\#Inst}{\#cyc} \cdot 10^3 \right] \end{array} $ | #Mem | Area<br>[#cells] | $\frac{\text{AreaEff}}{\left[\frac{10^6}{\# cyc \cdot \# cells}\right]}$ | #Cyc | $\frac{TP}{\left[\frac{\#Inst}{\#cyc} \cdot 10^3\right]}$ | Area=#Mem<br>[#cells] | $\frac{\text{AreaEff}}{\left[\frac{10^{6}}{\# cyc \cdot \# cells}\right]}$ | #Cyc   | AreaCom                    | SinTP | ParTP | AreaEff |

| c432       | 36    | 7           | 221    | 249         | 273   | 1096                                                                                                                 | 290  | 69x13            | 4.69                                                                     | 237  | 2160                                                      | 62                    | 71.4                                                                       | 95.2%  | 14.5x                      | 538x  | 2.0x  | 15.2x   |

| c499       | 41    | 32          | 594    | 631         | 64    | 101                                                                                                                  | 707  | 116x31           | 0.46                                                                     | 620  | 826                                                       | 110                   | 15.4                                                                       | 98.3%  | 32.7x                      | 521x  | 8.1x  | 33.3x   |

| c880       | 60    | 26          | 495    | 527         | 144   | 273                                                                                                                  | 613  | 107x14           | 1.33                                                                     | 512  | 1000                                                      | 142                   | 14.4                                                                       | 97.2%  | 10.5x                      | 527x  | 3.7x  | 10.9x   |

| c1355      | 41    | 32          | 594    | 681         | 72    | 106                                                                                                                  | 757  | 103x28           | 0.53                                                                     | 619  | 827                                                       | 111                   | 15.3                                                                       | 90.9%  | 26.0x                      | 563x  | 7.8x  | 28.6x   |

| c1908      | 33    | 25          | 569    | 594         | 75    | 126                                                                                                                  | 648  | 93x33            | 0.58                                                                     | 588  | 871                                                       | 122                   | 14.6                                                                       | 99.0%  | 25.2x                      | 517x  | 6.9x  | 25.4x   |

| c2670      | 233   | 140         | 967    | 892         | 17    | 19                                                                                                                   | 1183 | 340x29           | 0.12                                                                     | 891  | 575                                                       | 383                   | 3.1                                                                        | 99.9%  | 25.7x                      | 513x  | 30.2x | 25.8    |

| c3540      | 50    | 22          | 1393   | 1668        | 36    | 22                                                                                                                   | 1761 | 109x55           | 0.10                                                                     | 1434 | 357                                                       | 192                   | 3.8                                                                        | 86.0%  | 31.2x                      | 596x  | 16.5x | 36.3x   |

| c5315      | 178   | 123         | 1974   | 1931        | 46    | 24                                                                                                                   | 2251 | 547x22           | 0.05                                                                     | 2002 | 511                                                       | 351                   | 1.5                                                                        | 103.7% | 34.3x                      | 494x  | 21.5x | 33.1x   |

| c6288      | 32    | 32          | 2842   | 2916        | 160   | 55                                                                                                                   | 3104 | 49x115           | 0.06                                                                     | 2938 | 349                                                       | 149                   | 2.4                                                                        | 100.8% | 37.8x                      | 508x  | 6.4x  | 37.5x   |

| c7552      | 207   | 208         | 2241   | 2130        | 46    | 22                                                                                                                   | 2486 | 542x22           | 0.04                                                                     | 2227 | 460                                                       | 535                   | 0.9                                                                        | 104.6% | 22.3x                      | 490x  | 21.3x | 21.3x   |

|            |       |             |        | -           |       |                                                                                                                      |      |                  |                                                                          |      |                                                           |                       | Geomean:                                                                   | 97.4%  | 24.4x                      | 526x  | 9.3x  | 25.1x   |

TABLE III

Comparison Between SAID [25] With 512 × 512 Memory Array Size and SIMPLER, Both Using Nor4 Netlists

|            | Origi | Original Netlist |        | Original Netlist |       | Original Netlist                                                                                                     |      |                  | SAID [25]                                                                  |      |                                                                  |                       |                                                                            |        |         | ER (this worl | s)    | C       | Comparison - SIMPLER/SAID |  |  |  |

|------------|-------|------------------|--------|------------------|-------|----------------------------------------------------------------------------------------------------------------------|------|------------------|----------------------------------------------------------------------------|------|------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------|--------|---------|---------------|-------|---------|---------------------------|--|--|--|

| Benchmarks | #In   | #Out             | #Gates | #CycSinInst      | #Inst | $ \begin{array}{c} \textbf{TP} \text{ (Upper Bound)} \\ \left[ \frac{\#Inst}{\#cyc} \cdot 10^3 \right] \end{array} $ | #Mem | Area<br>[#cells] | $\frac{\text{AreaEff}}{\left[\frac{10^{6}}{\# cyc \cdot \# cells}\right]}$ | #Cyc | $\frac{\text{TP}}{\left[\frac{\#Inst}{\#cyc} \cdot 10^3\right]}$ | Area=#Mem<br>[#cells] | $\frac{\text{AreaEff}}{\left[\frac{10^{6}}{\# cyc \cdot \# cells}\right]}$ | #Cyc   | AreaCom | SinTP         | ParTP | AreaEff |                           |  |  |  |

| 9sym       | 9     | 1                | 207    | 160              | 77    | 481                                                                                                                  | 1026 | 70x46            | 2.04                                                                       | 218  | 2349                                                             | 57                    | 84.4                                                                       | 136.3% | 56.5x   | 376x          | 4.9x  | 41.5x   |                           |  |  |  |

| apex5      | 117   | 88               | 773    | 777              | 32    | 41                                                                                                                   | 2223 | 207x32           | 0.20                                                                       | 879  | 582                                                              | 260                   | 4.6                                                                        | 113.1% | 25.5x   | 453x          | 14.1x | 22.5x   |                           |  |  |  |

| clip       | 9     | 5                | 103    | 135              | 320   | 2370                                                                                                                 | 451  | 50x16            | 9.71                                                                       | 114  | 4491                                                             | 49                    | 187.7                                                                      | 84.4%  | 16.3x   | 606x          | 1.9x  | 19.3x   |                           |  |  |  |

| duke2      | 22    | 29               | 409    | 300              | 28    | 93                                                                                                                   | 1632 | 106x65           | 0.51                                                                       | 450  | 1138                                                             | 135                   | 17.3                                                                       | 150.0% | 51.0x   | 341x          | 12.2x | 34.0x   |                           |  |  |  |

| e64        | 65    | 65               | 389    | 134              | 252   | 1881                                                                                                                 | 394  | 24x40            | 8.15                                                                       | 474  | 1080                                                             | 143                   | 15.5                                                                       | 353.7% | 6.7x    | 145x          | 0.6x  | 1.9x    |                           |  |  |  |

| inc        | 7     | 9                | 92     | 55               | 560   | 10182                                                                                                                | 280  | 51x9             | 41.54                                                                      | 107  | 4785                                                             | 42                    | 233.3                                                                      | 194.5% | 10.9x   | 263x          | 0.5x  | 5.6x    |                           |  |  |  |

| misex3c    | 14    | 14               | 501    | 518              | 27    | 52                                                                                                                   | 2551 | 156x52           | 0.25                                                                       | 532  | 962                                                              | 115                   | 17.1                                                                       | 102.7% | 70.5x   | 499x          | 18.5x | 68.7x   |                           |  |  |  |

| rd73       | 7     | 3                | 99     | 150              | 252   | 1680                                                                                                                 | 379  | 56x18            | 6.94                                                                       | 108  | 4741                                                             | 44                    | 220.7                                                                      | 72.0%  | 22.9x   | 711x          | 2.8x  | 31.8x   |                           |  |  |  |

| sao2       | 10    | 4                | 118    | 79               | 144   | 1823                                                                                                                 | 559  | 54x32            | 7.68                                                                       | 128  | 4000                                                             | 53                    | 154.6                                                                      | 162.0% | 32.6x   | 316x          | 2.2x  | 20.1x   |                           |  |  |  |

| vg2        | 25    | 8                | 101    | 55               | 572   | 10400                                                                                                                | 280  | 23x19            | 43.63                                                                      | 115  | 4452                                                             | 61                    | 149.5                                                                      | 209.1% | 7.2x    | 245x          | 0.4x  | 3.4x    |                           |  |  |  |

|            |       |                  | -      | -                |       |                                                                                                                      |      |                  |                                                                            | -    |                                                                  |                       | Geomean:                                                                   | 142%   | 22.5x   | 360x          | 2.7x  | 15.8x   |                           |  |  |  |

TABLE IV

EPFL BENCHMARKS EXECUTED USING SIMPLER WITH DIFFERENT MEMORY ARRAY SIZES (#MINCELLS, #MINCELLS + max{5% of #MinCells, 10}), AND #MINCELLS WITH LIMITATION ON NUMBER OF SIMULTANEOUSLY INITIALIZED CELLS (LIMITINITCELLS). COMPARISON BETWEEN RESULTS OF NOR2 AND NOR4 NETLISTS

|            |                  |      |                  |              |          |       | NOR2           |           |                | NOR4  |              |       |       |                |                |       |                |       |

|------------|------------------|------|------------------|--------------|----------|-------|----------------|-----------|----------------|-------|--------------|-------|-------|----------------|----------------|-------|----------------|-------|

|            | Original Netlist |      | ABC UnlimitCells |              | MinCells |       | MinCells+5%/10 |           | LimitInitCells | ABC   | .BC Unlimit( |       | Min   | Cells          | MinCells+5%/10 |       | LimitInitCells |       |

| Benchmarks | #In              | #Out | #Gates           | #Cyc Area #C |          | #Cyc  | Area           | #Cyc Area |                | #Cyc  | #Gates       | #Cyc  | Area  | #Cyc Area #Cyc |                | Area  | a #Cyc         |       |

| adder      | 256              | 129  | 1531             | 1531         | 1787     | 1585  | 388            | 1560      | 398            | 1685  | 1529         | 1529  | 1785  | 1574           | 391            | 1557  | 401            | 1682  |

| arbiter    | 256              | 129  | 12798            | 12798        | 13054    | 13016 | 1016           | 12876     | 1054           | 14078 | 12330        | 12330 | 12586 | 12553          | 958            | 12416 | 994            | 13563 |

| bar        | 135              | 128  | 4051             | 4051         | 4186     | 4162  | 429            | 4115      | 444            | 4457  | 2711         | 2711  | 2846  | 2772           | 416            | 2751  | 431            | 2986  |

| cavlc      | 10               | 11   | 840              | 840          | 850      | 924   | 125            | 870       | 135            | 924   | 670          | 670   | 617   | 644            | 119            | 626   | 129            | 668   |

| ctrl       | 7                | 26   | 143              | 143          | 150      | 169   | 43             | 150       | 53             | 157   | 108          | 108   | 115   | 123            | 48             | 112   | 58             | 118   |

| dec        | 8                | 256  | 360              | 360          | 368      | 373   | 267            | 364       | 280            | 396   | 328          | 328   | 336   | 338            | 628            | 331   | 281            | 361   |

| int2float  | 11               | 7    | 294              | 294          | 305      | 332   | 53             | 307       | 63             | 324   | 197          | 197   | 208   | 219            | 54             | 206   | 64             | 217   |

| max        | 512              | 130  | 4200             | 4200         | 4712     | 4268  | 1020           | 4230      | 1046           | 4620  | 3268         | 3268  | 3780  | 3326           | 1034           | 3291  | 1061           | 3595  |

| priority   | 128              | 8    | 852              | 852          | 980      | 905   | 196            | 885       | 206            | 938   | 748          | 748   | 876   | 784            | 193            | 766   | 203            | 823   |

| sin        | 24               | 25   | 7915             | 7915         | 7939     | 8140  | 453            | 8019      | 475            | 8707  | 5463         | 5463  | 5487  | 5659           | 461            | 5539  | 483            | 6010  |

problem, using the Z3 SMT solver [34]. This tool evaluates the quality of SIMPLER's heuristics by comparing the minimum number of cells proposed by SIMPLER to the optimal solution generated by OptiSIMPLER. Since solving optimization problems is computationally cumbersome, its run-time has to be restricted. We allowed OptiSIMPLER to run no more than two days per benchmark. With this limit, OptiSIMPLER succeeds in mapping only small benchmarks (less than 100 gates). Therefore, it succeeds in running only the LGsynth91 benchmark suite [35]. OptiSIMPLER and SIMPLER are compared in Table V, where both map NOR4 netlists.

### A. Description of the Compared Previous Works

We compare SIMPLER to three previously developed mapping tools: SIMPLE MAGIC [23], YADAV [24], and SAID [25].

SIMPLE MAGIC [23]—solves an optimization problem that minimizes the latency of the execution of a function in-memory. As opposed to SIMPLER, SIMPLE uses several memory rows for the execution of a single computation instance, with the goal of reducing the latency of a single computation instance. For the same reasons as OptiSIMPLER, SIMPLE can map very small benchmarks only; thus, we evaluated SIMPLE using the LGsynth91 benchmark suite [35]. 22

9

27

Original Netlist АВС OptiSIMPLER SIMPLER (this work) Diff (SIMPLER-OptiSIMPLER) Benchmark #In #Out #Gates SAT - Area [#cells] UNSAT - Area [#cells] SAT - #Cyc MinCells - Area [#cells] #Cyc Area [#cells] #Cyc 7 7 13 -3 b1 4 16 cm138a 6 8 24 16 15 42 17 44 1 2 cm42a 14 14 4 10 15 30 16 31 16 49 25 24 74 27 67 -7 cmb conl 7 22 12 1137 13 -5 2 32 23 cordic 72 31 30 104 34 96 -8

48

13

77

28

23

10

29

10

TABLE V Comparison Between the Mapping With the Minimal Required Number of Cells (OptiSIMPLER), and SIMPLER, Using nor4 Netlists

| 2) | YADAV [24]—uses heuristics to map the execution           |

|----|-----------------------------------------------------------|

|    | of larger functions into the memory. It can process       |

|    | larger benchmarks than SIMPLE. The authors use the        |

|    | ISCAS85 benchmark suite [36] for their evaluation. To     |

|    | execute the larger benchmarks within an array with        |

|    | limited-size rows, several rows are used for a single     |

|    | computation instance and data is copied among the dif-    |

|    | ferent rows occasionally. Each copy of a single bit takes |

|    | two clock cycles (two NOT operations), thus increasing    |

|    | the execution latency.                                    |

25

9

56

18

23

10

30

10

3) SAID [25]—similar motivation and general approach as YADAV, but employing a different mapping technique and using the IWLS'93 benchmark set.

# B. Description of the Criteria for Efficient Mapping

5

21

16

decod

majority

mux

xor5

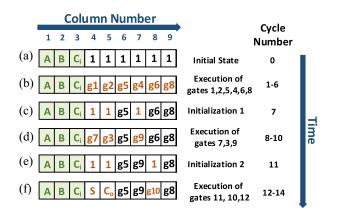

Latency is the number of cycles to complete a computation. An MAT (memory array) may contain several computation instances. The latency of executing all computation instances in the given MAT (#CycAllInst) is higher than the execution latency of a single computation instance (#CycSinInst), unless all computation instances can be executed in parallel. In SIMPLER, where all instances are simultaneously executed, the overall latency of all instances is equal to the latency of a single instance, which is equal to the number of executed gates + the number of initialization cycles (independent of the number of instances). However, in SIMPLE, YADAV, and SAID (which aimed to improve the latency of a single instance), when parallelized in a similar manner to SIMPLER, the latency of all computation instances increases with the number of instances. When the computation instances are aligned by rows (row alignment), MAGIC column operations of different instances are executed in parallel, and MAGIC row operations are serially executed, and vice versa when the instances are aligned by columns (col alignment), as shown in Fig. 7. Hence,  $\#CycAllInst = \#Cr \times \#Ir + \#Cc \times \#Ic$ , where #Cr and #Cc are, respectively, the number of cycles in which MAGIC row and MAGIC column operations are executed. #Ir and #Ic are, respectively, the number of instances that can be executed within the given MAT in the row alignment and col alignment configuration (i.e., respectively, two and three instances in Fig. 7). The tools developed by YADAV and SAID are not public; thus, we could not evaluate the exact #Cr and #Cc. Therefore, for both we optimistically assume a latency

56

13

78

Arithmetic average

0

0

-1

0.8

8

0

1

-1.1

Fig. 7.  $64 \times 64$  memory array. Each blue rectangle is a computation instance computed within the array. Each instance is executed using  $18 \times 27$  cells. The yellow lines represent a MAGIC column and the green lines a MAGIC row operation. When the instances are aligned by rows (row alignment), two instances can be aligned, since  $\lfloor 64/27 \rfloor = 2$ , e.g., (a) and (b). All aligned MAGIC column operations of the different row-aligned instances may be executed in parallel, whereas the MAGIC row operations of the different instances are aligned by columns (col alignment), three instances can be aligned, since  $\lfloor 64/18 \rfloor = 3$ , e.g., (a), (c), and (e). All aligned MAGIC row operations of the different columnaligned instances may be executed in parallel, whereas the MAGIC row operations of the different column aligned instances may be executed in parallel, whereas the MAGIC column operations of the different column-

equal to that of executing a single instance, which is a very loose lower-bound on the latency of executing all the instances. This bound can only be reached when each instance is executed using a single row. For the rest of the section, latency of SIMPLE refers to #CycAllInst, and of YADAV and SAID refers to #CycSinInst.

Throughput is the maximum number of instances that can be executed within the MAT within a given time unit, as stated in (1). Maximal throughput improvements can only be achieved for well-parallelizable code. To assess the practical benefit for a specific kernel/application, a comprehensive system analysis is needed. Additionally, physical restrictions [26] may also limit the number of rows that can be executed in parallel, thus reducing the throughput gain proportionally. In this article, we evaluate the throughput as if the maximum parallelism is possible, i.e., the number of instances equals the number of rows in the MAT (i.e., 512). For SIMPLE, YADAV, and SAID, we evaluated the throughput in two ways: first, the throughput for a single instance (SinTP), as these methods were originally intended to be executed that way. Additionally, we computed the throughput for as many instances as possible that are executed concurrently, within the given MAT (ParTP). ParTP is only the hypothetical potential

throughput of the existing methods should they employ parallel computation of different instances. Overall, *ParTP* favors the existing methods by giving them the extra benefit of running multiple computation instances in parallel (which may be unrealizable). Also, as previously mentioned, the latency of SAID and YADAV is a loose lower bound; hence, we use a quite optimistic upper-bound for the throughput potential of these two methods.

Area is determined by the number of columns  $\times$  the number of rows allocated for the execution of a single computation instance, including the area necessary for storing the function inputs, e.g.,  $18 \times 27 = 486$  in Fig. 7. For SIMPLER, the area is equal to the number of active memristors, since a single row execution enables the use of all available memristor cells for the computation. Therefore, when cell reuse is not required, the area is equal to the number of gates + the number of inputs. Otherwise, when cell reuse is required, the area is equal to the number of columns allocated for the computation (which is smaller than the allocated area with no reuse). On the other hand, for all three tools, the area is much larger than the number of active memristors. This is because the processing is distributed over several rows; hence, they do not use all the memristors in the array for the executions.

The *area efficiency* is calculated as  $(1/\text{Latency} \times \text{Area})$ .

# C. SIMPLER Results

Tables I-III (first three columns) list the number of inputs (#In), outputs (#Out), and the number of all gates (both twoinput NOR and NOT) after the ABC optimization (ABC, #Gates), which is equivalent to the number of pure execution steps (latency) in SIMPLER (that is, without reinitialization cycles). The next seven columns of Table I and six columns of Tables II and III, show the results for SIMPLE, YADAV, and SAID, using a memory array size of  $512 \times 512$  (the last three benchmarks in Table II uses a 1024 × 1024 array, according to the area required for the execution of YADAV). First, the latency necessary for execution is given. For SIMPLE, the number of cycles for executing a single instance (#CycSinInst) and the number of cycles for executing all instances in the MAT (#CycAllInst) are given in two different columns. As discussed in Section IV-B, the given latency for YADAV and SAID is a loose lower bound equal to the number of cycles for executing a single instance (#CycSinInst). The next columns show the maximum number of computation instances that fit the given array size (#inst), the throughput (TP), the number of active memristors used for the execution (#Mem), the area necessary for the computation of a single instance (Area), and the area efficiency (AreaEff). The next four columns list the results of the proposed SIMPLER synthesis tool, when executing within a row with the minimum number of cells required by SIMPLER for the execution of each benchmark (referred as #MinCells) and an additional max{5% of #MinCells, 10} cells. #Inst is not stated for each benchmark, since SIMPLER maps the computation to a single row; thus, the number of instances that can be executed concurrently equals the number of rows in the array (1024 for the last three benchmarks

in Table II, and 512 for all other benchmarks in Tables I–III). Area and #Mem are listed together in one column, as they are the same for SIMPLER since only a single row is used. Finally, the area efficiency (AreaEff) is listed.