# Simultaneous Co-Design of Distributed On-Chip Power Supplies and Decoupling Capacitors

Selçuk Köse and Eby G. Friedman

Department of Electrical and Computer Engineering

University of Rochester

Rochester, New York 14627

{kose,friedman}@ece.rochester.edu

Abstract—The effective design of power distribution networks has become highly challenging with each technology generation. The power delivery network is becoming large, making the system analysis process computationally complex. The large number of on-chip power supplies and intentional decoupling capacitors inserted throughout an integrated circuit further complicates the analysis of the power distribution network. To fully exploit the on-chip power supplies and decoupling capacitors, a new design methodology is required to simultaneously design the power distribution network that considers all of the power supplies and decoupling capacitors. Interactions among the power supplies, decoupling capacitors, and active circuitry are investigated in this paper utilizing a computationally efficient methodology. The effect of physical distance on the power supply noise is investigated. A design methodology for simultaneous placement of the on-chip voltage regulators and decoupling capacitors is also described in this paper. This methodology changes conventional practices where the power distribution network is designed first, followed by the placement of the decoupling capacitors.

#### I. Introduction

Multiple power supplies are widely used in high performance integrated circuits to provide current close to the load circuitry in high performance integrated circuits [1]. The number of on-chip power supplies is increasing, requiring innovative design methodologies to satisfy the stringent noise and power constraints of these high complexity integrated circuits [2], [3]. Placing the power supply on-chip eliminates losses due to the package parasitic impedances, improving the quality of the delivered power [1].

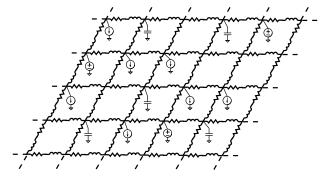

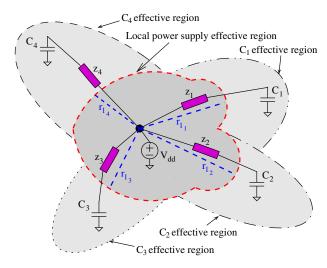

To provide multiple on-chip power supplies, linear voltage regulators are typically used which require small area with fast load regulation to realize point-of-load voltage delivery [4]. These power supplies alone, however, do not satisfy stringent power and noise constraints. Decoupling capacitors are therefore widely used as a local *reservoir of charge* which are self activated and supply current when the power supply level deteriorates [5]. Inserting decoupling capacitors into the power distribution network is a natural way to lower the power grid impedance at high frequencies [6]. A representative power delivery network with on-chip power supplies, decoupling capacitors, and load circuits is illustrated in Fig. 1.

Fig. 1. A uniform power distribution network with multiple on-chip power supplies, decoupling capacitors, and current loads. Current loads are used to model the active circuitry.

Tens of on-chip power supplies, hundreds-to-thousands of onchip decoupling capacitors, and millions-to-billions of active transistors are anticipated in the design of next generation high performance integrated circuits.

Power supplies and decoupling capacitors exhibit similar characteristics with some important differences such as the response time, decay rate of the capacitor, on-chip area, and power efficiency. On-chip power supplies require greater area, provide limited power efficiency, and exhibit slower response time as compared to decoupling capacitors. Decoupling capacitors, however, should be placed close to a power supply to recharge before the next switching event [5]. Additionally, the placement of the decoupling capacitors should consider the resonance formed by the decoupling capacitor and the power grid inductance which degrades the effectiveness of the decoupling capacitor [7]. Existing design methodologies for placing decoupling capacitors assume one or two on-chip power supplies [5] or one decoupling capacitor interacting with multiple power supplies [8]. These assumptions are inappropriate when point-of-load voltage regulation is implemented with multiple on-chip power supplies and decoupling capacitors. Design methodologies are therefore required to simultaneously place multiple on-chip power supplies and decoupling capacitors.

The effective radii of the decoupling capacitors have been developed for a single current path between a current load and a single decoupling capacitor in [5] and for a mesh structure considering a single decoupling capacitor in [8]. In this paper, not only the interactions among the power supplies, decoupling capacitors, and load circuitry but also the interactions among the power supplies and between the decoupling capacitors are

This research is supported in part by the National Science Foundation under Grant Nos. CCF-0541206, CCF-0811317, and CCF-0829915, grants from the New York State Office of Science, Technology and Academic Research to the Center for Advanced Technology in Electronic Imaging Systems, and by grants from Intel Corporation, Eastman Kodak Company, and Freescale Semiconductor Corporation.

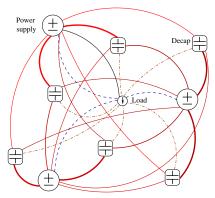

Fig. 2. Interactions among the on-chip power supplies, decoupling capacitors, and load circuitry. Thicker lines represent greater interaction. Note that the effect of a power supply or a decoupling capacitance on the load circuitry depends strongly on the physical distance.

considered. Those interactions considered in this paper are schematically shown in Fig. 2.

These interactions among the circuit components are complicated by the increasing number of components in the power delivery network. In this paper, interactions among the power supplies, decoupling capacitors, and current loads are investigated. A methodology is proposed to simultaneously determine the optimum location of the distributed power supplies and decoupling capacitors within the overall power distribution network, providing an integrated approach to delivering power.

The rest of this paper is organized as follows. The problem is formulated in Section II. Interactions among the on-chip power supplies, decoupling capacitors, and load circuitry are analyzed and a methodology for simultaneous power supply and decoupling capacitor placement is presented in Section III. Case studies examining the interactions among the power supplies, current loads, and decoupling capacitors are provided in Section IV. Some specific conclusions are drawn in Section V.

### II. PROBLEM FORMULATION

Power distribution networks are typically modeled as a uniformly distributed RL mesh structure. By exploiting the uniform nature of the power grid, the *euclidean distance* between the circuit components can be used to determine the effective impedance between arbitrary nodes. A closed-form expression for the effective impedance in an infinite resistive mesh is provided by Venezian in [9]. This expression is modified both to produce more accurate results and to include the inductance of the power grid as the power grid impedance depends strongly on the inductance at high frequencies. A closed-form expression to determine the effective impedance between two nodes,  $N_{x_1,y_1}$  and  $N_{x_2,y_2}$ , is

$$Z_{m,n} = z * \frac{1}{2\pi} * ln(n^2 + m^2) + 0.51469,$$

(1)

where

$$m = |x_1 - x_2|$$

and  $n = |y_1 - y_2|$ . (2)

z is the impedance of one segment of the grid. Applying this effective impedance concept, multiple current paths are

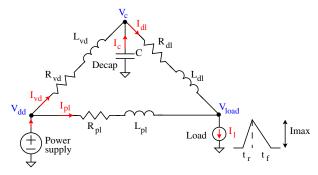

Fig. 3. Simplified interactions among a power supply, decoupling capacitor, and load circuit. The components are connected with the corresponding equivalent impedance in the power grid modeled by (1). The load current is modeled as a triangular current load with a rise time  $t_r$  and fall time  $t_f$ .

considered without increasing the computational complexity of the power grid analysis process.

The complicated power distribution network schematically illustrated in Fig. 2 is simplified to a network consisting of only equivalent impedances among the power supplies, decoupling capacitors, and load circuitry. Multiple current paths are efficiently considered using the simplified model in (1).

## III. SIMULTANEOUS POWER SUPPLY AND DECOUPLING CAPACITOR PLACEMENT

Interactions among a single power supply, decoupling capacitor, and current load are illustrated in Fig. 3. The equivalent parasitic resistance and inductance between the power supply and decoupling capacitor, power supply and load circuit, and decoupling capacitor and load circuit are represented as  $R_{vd}$  and  $L_{vd}$ ,  $R_{pl}$  and  $L_{pl}$ , and  $R_{dl}$  and  $L_{dl}$ , respectively. The load current  $I_l$  is

$$I_l = i_{dl} + i_{pl}. (3)$$

The current supplied from the decoupling capacitor and power supply is represented as  $i_{dl}$  and  $i_{pl}$ , respectively. The ratio of the current supplied to the active circuits from the power supplies and decoupling capacitors depends upon the physical distances, the parasitic impedance among these components, and the size of the decoupling capacitors.  $i_{dl}/i_l$  increases for greater  $R_{pl}$  and  $L_{pl}$ , enhancing the effect on the load circuit of the decoupling capacitors as compared to the effect of the power supplies.

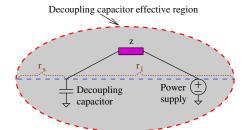

The effective region of a decoupling capacitor depends upon the location of those power supplies, decoupling capacitors, and load circuits in close proximity as well as the power grid impedance, and rise and fall times of the load currents. A uniform current distribution is assumed in this paper to simplify this analysis. The analysis can however be generalized to a non-uniform load current distribution. The effective region for a single decoupling capacitor with a single power supply is illustrated in Fig. 4. The effective region is not a uniform circle as previously proposed in [5], [8], but exhibits an elliptic shape due to the non-uniform location of the power supplies. This elliptic shape can be explained intuitively by examining Fig. 4. The current supplied to the load circuit in this elliptic region

Fig. 4. Elliptic structure to illustrate the effective region of a decoupling capacitors with a single power supply. The short radius  $(r_s)$  and long radius  $(r_l)$  depend upon the size of the capacitor and the effective impedance between the capacitor and power supply.

is provided by the decoupling capacitor and the local power supply. When the load circuit is moved out of this elliptic region, most of the load current is provided either by the local power supply or decoupling capacitor due to the increased parasitic impedance. When the load current is supplied both by the local power supply and the decoupling capacitor, the response is faster and more effectively suppresses the switching noise.

The elliptic shape also depends upon the technology parameters and the noise constraints. The area of the elliptical region is small when the noise constraints of the power distribution network are high. For example, when the maximum target noise of the power distribution system is 5% of the supply voltage, a smaller ellipse is formed as the effective region around the decoupling capacitor. Alternatively, the area of the elliptic region increases when the noise constraint is increased to 10% of the supply voltage. Consequently, elliptic equipotential shapes are formed around the decoupling capacitors and power supplies, denoting identical power supply voltage levels.

An elliptic region is described by a long and short radius represented as  $r_l$  and  $r_s$ , respectively, as shown in Fig. 4.  $r_l$  can be determined as

$$r_{l_{(n,m)}} = \frac{K * C}{R_{(x_1,y_1)} + k * L_{(x_1,y_1)}},$$

(4)

where C is the decoupling capacitance and the effective resistance and inductance between the decoupling capacitor and the power supply are represented as  $R_{(x_1,y_1)}$  and  $L_{(x_1,y_1)}$ , respectively. The horizontal and vertical distance from the decoupling capacitor to the power supply is represented as  $x_1$  and  $y_1$ , respectively. The effect of the transition time of the load current is embedded into the equation using k. K models the noise constraints, i.e., a smaller K is used for more stringent noise constrained circuits.

The effective region for a local power supply with four decoupling capacitors is illustrated with a dark shaded modified elliptic shape in Fig. 5. Since the power supply interacts with four different decoupling capacitors, the effective region is the overlap of the four different elliptic shapes. Since the effect of a decoupling capacitor on  $r_s$  is limited, the effective region of the power supply can be described with four different  $r_l$ , denoted as  $r_{l1}$ ,  $r_{l2}$ ,  $r_{l3}$ , and  $r_{l4}$ , to represent the effect of  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ , respectively. A similar analysis can

Fig. 5. Modified elliptic structure to illustrate the effective regions for a local power supply and decoupling capacitors. Note that the effective region for a local power supply is the overlap of the effective regions for the surrounding decoupling capacitors.

be performed when the system includes multiple decoupling capacitors and multiple power supplies. Each decoupling capacitor is affected by the remaining decoupling capacitors and power supplies. The effective region of a decoupling capacitor or power supply is therefore described as the overlap of the elliptic equipotential surfaces caused by each power supply and decoupling capacitor, as illustrated in Fig 5.

### IV. CASE STUDY

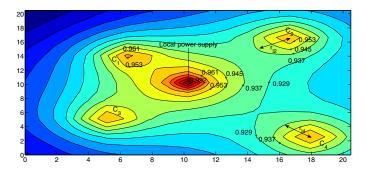

The proposed method of overlapping elliptic equipotential surfaces to determine the effective region has been verified with SPICE simulations. A uniform RL grid structure with 20 horizontal and vertical lines (20 x 20 mesh) is assumed in the analysis. The supply voltage is 1 volt and the uniformly distributed current loads switch at a 1 Ghz frequency with rise and fall times of 100 ps and 300 ps, respectively. A power distribution system with a local power supply and four decoupling capacitors is initially investigated. The power supply is placed at  $N_{(10,10)}$  and the decoupling capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  are placed at nodes  $N_{(6,14)}$ ,  $N_{(17,17)}$ ,  $N_{(5,5)}$ , and  $N_{(18,2)}$ , respectively. A simulation of the power distribution network is illustrated in Fig. 6.

Since the closest decoupling capacitor to the local power supply is  $C_1$ , the effective region of the power supply extends towards  $C_1$ . Alternatively, the effective region of the local power supply is limited towards  $C_4$  since  $C_4$  is farther from the local power supply. The long radius of the effective regions for  $C_2$  and  $C_4$  is shown in Fig. 6 as  $r_{l_2}$  and  $r_{l_4}$ , respectively. The ratio  $r_{l_2}/r_{l_4}$  is 1.2 as compared to 1.15 from (4), exhibiting an error of less than 5%.

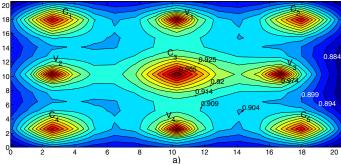

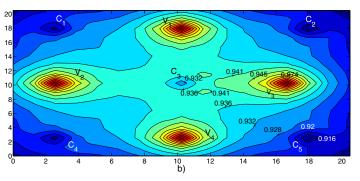

The effect of the transition time of the load current on the effectiveness of the decoupling capacitors and power supplies has also been investigated. A 20 x 20 power grid with five decoupling capacitors placed at  $N_{(3,3)}$ ,  $N_{(3,17)}$ ,  $N_{(10,10)}$ ,  $N_{(17,3)}$ , and  $N_{(17,17)}$  and four on-chip power supplies located at  $N_{(3,10)}$ ,  $N_{(10,3)}$ ,  $N_{(10,17)}$ , and  $N_{(16,10)}$  is evaluated. For rise and fall times of the load current of 50 ps and 150 ps,

Fig. 6. Effective region for a local power supply at  $N_{(10,10)}$  with four decoupling capacitors at  $N_{(17,17)}, N_{(18,2)}, N_{(5,5)}$ , and  $N_{(6,14)}$  in the power distribution network. Note the elliptic shapes around the decoupling capacitors and modified elliptic shape around the local power supply.

respectively, the effective region for the decoupling capacitors and power supplies is illustrated in Fig. 7a. Note that the effective region of the power supplies and decoupling capacitors exhibits similar behavior as the area of the surrounding equipotential surfaces are approximately the same. No resonance occurs and the decoupling capacitors are sufficiently close to the power supplies to be recharged before the next switching event.

The effective region of the power supplies and decoupling capacitors is depicted in Fig. 7b when the rise and fall transition times of the load current are increased to 200 ps and 600 ps, respectively. Note that the area of the effective region of the decoupling capacitors becomes smaller. The cause of the reduced effective region around the decoupling capacitors is that the equivalent transition times produce a resonance [7] formed by the decoupling capacitor and the power grid inductance. Also, the capacitors cannot fully recover before the next switching event. The resonance phenomenon is considered in (4) with k. The effective region around the onchip power supplies is not significantly affected by the change in transition time. Considering all of these distinct properties (such as resonance and the decay rate of the capacitor) of the decoupling capacitors and power supplies can significantly improve the quality of the power distribution network.

### V. CONCLUSIONS

A change in the design process of power distribution networks is necessary with the increase in the number of on-chip power supplies. This paper addresses the analysis and simultaneous co-placement of on-chip power supplies and decoupling capacitors in high performance integrated circuits. The effectiveness of a decoupling capacitor depends strongly on the distance between that decoupling capacitor and the neighboring on-chip power supplies. A closed-form expression is provided to determine the effective impedance between two nodes in a uniform *RL* power distribution network. The effective region for decoupling capacitors and power supplies exhibits an elliptic shape. A closed-form expression to determine the long radius of this elliptic shape is also provided. The error of this closed-form expression as compared to SPICE is less than 5%. The validity of the proposed method

Fig. 7. Effective region for multiple decoupling capacitors and power supplies. Four decoupling capacitors,  $C_1$ ,  $C_2$ ,  $C_4$ , and  $C_5$ , are located at the corners and one decoupling capacitor  $C_3$  is located in the middle of the power distribution network. The four power supplies are placed between the decoupling capacitors. The rise and fall transition times are a) 50 ps and 150 ps, and b) 200 ps and 600 ps, respectively.

of overlapping equipotential elliptic surfaces is verified with SPICE. The effective region of the decoupling capacitors is significantly affected by the transition time of the load current due to the resonance formed by the power grid inductance and decoupling capacitors.

### REFERENCES

- V. Kursun and E. G. Friedman, Multi-Voltage CMOS Circuit Design, New York: Wiley, 2006.

- [2] M. Popovich, A. V. Mezhiba, and E. G. Friedman, Power Distribution Networks with On-Chip Decoupling Capacitors, Springer, 2008.

- [3] S. Pant, D. Blaauw, and E. Chiprout, "Power Grid Physics and Implications for CAD," *IEEE Design and Test of Computers*, Vol. 24, No. 3, pp. 246–254, May 2007.

- [4] P. Hazucha et al., "Area-Efficient Linear Regulator with Ultra-Fast Load Regulation," *IEEE Journal of Solid-State Circuits*, Vol. 40, No. 4, pp. 933–940, April 2005.

- [5] M. Popovich, M. Sotman, A. Kolodny, and E. G. Friedman, "Effective Radii of On-Chip Decoupling Capacitors," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 16, No. 7, pp. 894-907, July 2008.

- [6] L. Smith et al., "Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology," *IEEE Transactions* on Advanced Packaging, Vol. 22, No. 3, pp. 284–291, August 1999.

- [7] E. Salman, E. G. Friedman, R. M. Secerenau, and O. L. Martin, "Worst Case Power/Ground Noise Estimation Using an Equivalent Transition Time for Resonance," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 56, No. 5, pp. 997–1004, May 2009.

- [8] A. Todri, M. Marek-Sadowska, F. Maire, and C. Matheron, "A Study of Decoupling Capacitor Effectiveness in Power and Ground Grid Networks," Proceedings of the IEEE International Symposium on Quality Electronic Design, pp. 653-658, March 2009.

- [9] G. Venezian, "On the Resistance between Two Points on a Grid," American Journal of Physics, Vol. 62, No. 11, pp. 1000–1004, November 1994