## Single-electron-based flexible multivalued logic gates

Cite as: Appl. Phys. Lett. **92**, 093101 (2008); https://doi.org/10.1063/1.2888164 Submitted: 02 October 2007 • Accepted: 21 November 2007 • Published Online: 03 March 2008

C. K. Lee, S. J. Kim, S. J. Shin, et al.

## ARTICLES YOU MAY BE INTERESTED IN

Single-electron transistor logic Applied Physics Letters **68**, 1954 (1996); https://doi.org/10.1063/1.115637

One electron-based smallest flexible logic cell Applied Physics Letters **101**, 183101 (2012); https://doi.org/10.1063/1.4761935

Complementary digital logic based on the "Coulomb blockade" Journal of Applied Physics **72**, 4399 (1992); https://doi.org/10.1063/1.352206

Lock-in Amplifiers up to 600 MHz

Appl. Phys. Lett. **92**, 093101 (2008); https://doi.org/10.1063/1.2888164 © 2008 American Institute of Physics.

## Single-electron-based flexible multivalued logic gates

C. K. Lee,<sup>1</sup> S. J. Kim,<sup>1</sup> S. J. Shin,<sup>1</sup> J. B. Choi,<sup>1,a)</sup> and Y. Takahashi<sup>2</sup>

<sup>1</sup>Department of Physics and Institute for Nano Science and Technology, Chungbuk National University, Cheongju 361-763, Republic of Korea

$^{2}$ The Graduate School of Information Science and Technology, Hokkaido University, Sapporo, Japan

(Received 2 October 2007; accepted 21 November 2007; published online 3 March 2008)

Single-electron transistor (SET)-based multivalued (MV) not-AND (NAND) and not-OR (NOR) logic cells were implemented on a silicon-on-insulator chip. Depending on the ways of connecting two SETs with a field-effect transistor, the voltage transfer characteristics show typical NAND or NOR gate functions for various input voltages, which are binary, MV, and binary-MV mixed. Moreover, the switching functionality of our NAND (NOR) can convert to OR (AND) operation by simply adjusting their initial input voltages. These flexible two-input logic gates are expected to provide four basic arithmetic cells for the SET MV logic gate family. © 2008 American Institute of Physics. [DOI: 10.1063/1.2888164]

The basic philosophy of single electronics is a manipulation of one electron charge and how to apply it to the digital electronics.<sup>1</sup> The single-electron multivalued (MV) memory or MV logic reflects such capability of controlling the discrete charge of an individual electron. The MV memory can be implemented by utilizing the threshold quantization in nanoscale floating dot-based memory,<sup>2</sup> while multiple switching of a single-electron transistor (SET) enables us to realize the MV logic schemes,<sup>3-6</sup> which have higher functionality with lower hardware complexity. Degawa et al.<sup>5</sup> has recently proposed a SET MV logic gate family which are quite usable as a fast arithmetic circuit operation with a small number of device elements. Here, we report on an implementation of Si SET-based flexible MV not-AND (NAND) and not-OR (NOR) gates which play a crucial role as essential device elements for the SET MV logic gate family. Depending on the ways of connecting two SETs with a fieldeffect transistor (FET), its voltage transfer characteristics displays typical NAND or NOR gate functions for various two SET input voltages, which are binary, MV and binary-MV mixed mode.

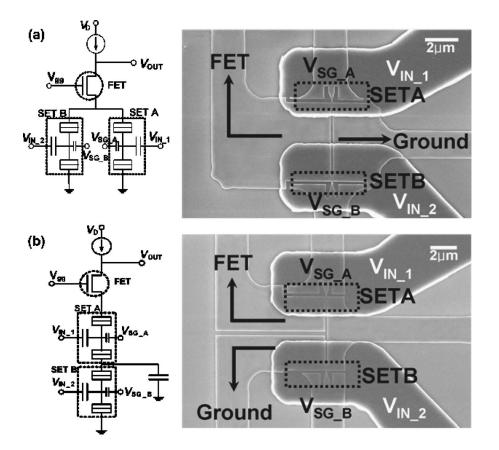

Combining SETs with a FET, two-input NAND and NOR gates were fabricated on silicon-on-insulator chips. The resulting SET/FET circuit comprises of two identical SETs [connected in series (parallel) for the NAND (NOR)], a FET, and a constant-current (CC) load, which are seen in Figs. 1(a) and 1(b) with their corresponding circuit layouts. The FET connected in series with the combination of two SETs was to attain the SET bias voltage under a range of Coulomb blockade. In the SET part, a Coulomb channel and a side gate for each SET were both defined in the same plane of the top Si with 50 nm thickness, as seen in Fig. 2(a). The Coulomb channel of 15 nm width/50 nm length for each SET was first designed by electron-beam lithography and finally formed by pattern-dependent oxidation.<sup>7,8</sup> A selective doping on only the side gates was followed with a nanopatterned e-beam resist as a mask to prevent the active channel from being highly doped.<sup>9</sup> The Coulomb channel of our SET is thus a standard low-doped region, and is free from possible strong electrostatic fluctuations rising from the randomly distributed high dopants.

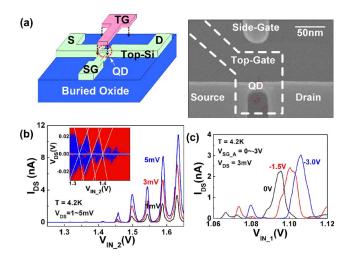

Figure 2(b) shows typical Coulomb oscillations for a SET element of the logic cells. Control of the phase of Coulomb current peaks of SET by using its side gate is seen in Fig. 2(c). Applying incremental side-gate voltage allows the phase of Coulomb peaks to shift, which enables to optimize the flexible multifunctionality of the devices. Drain current at 4.2 K, seen in Fig. 2(b), displays a large conductance peak value of  $G_p \sim 3 \ \mu$ S with a high peak-to-valley current ratio. This large current leads to  $R_i \sim 1/2G_p \sim 166 \text{ k}\Omega$ , for the junction resistance, which is within an order of magnitude of the theoretical quantum limit for displaying a clear Coulomb blockade. Typical value of the gate capacitance  $C_g$  is deduced from the Coulomb peak spacing  $\Delta V_g$  using the relationship  $C_{g} = e/\Delta V_{g}$ , which yields  $C_{g} \sim 2.1$  aF. By using the tunnel junction capacitance  $C_i \sim 0.6$  aF directly deduced from a measured charge stability diagram [an inset in the Fig. 2(b), we can estimate the intrinsic speed of the SET, which is  $\sim R_i C_t = 166 \text{ k}\Omega \times 3.3 \text{ aF} \sim 0.6 \text{ ps}$ , yielding to  $\sim 1.7$  THz speed, where  $C_t$  is the total capacitance of  $C_g$  $+2C_i$ . This high RC value was also evaluated in our previous SETs with similar geometry.<sup>8</sup> Note that this ultrafast intrinsic speed of the SET element is not the directly measured operating speed of its logic circuits. The actual operating frequency becomes far reduced mainly by the  $RC_I$  cutoff due to inevitable capacitance loading the SET output.

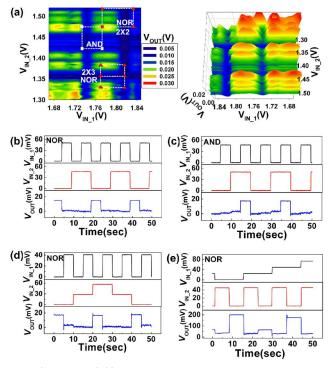

Figure 3 shows the data of the NOR gate; gray scale contour plot of the voltage output Vout measured at 4.2 K versus two SET input voltages of  $V_{in_1}$  and  $V_{in_2}$  and its voltage swing waveforms. The CC load current is set to 100 pA by a current-mode output of HP4155 with a compliance (voltage limit) of 30 mV, and the  $V_{gg}$  of the FET is set to 1.670 V. As seen in Fig. 3(a),  $V_{out}$  displays a periodic high/ low mosaic pattern as a function of two SET input voltages, corresponding to Coulomb-blockaded/tunneling current regimes; high for both SETs blockaded, while low for one or both SETs tunneled through. The voltage transfer characteristics are seen in Figs. 3(b)-3(d). The offset zero values of  $V_{\text{in 1}}$  and  $V_{\text{in 2}}$  for each mode can be selected from an operating point (low, low) in any periodic regions of the contour plot of  $V_{out}$ , for an instance, as seen by dot-lined areas in Fig. 3(a). The voltage transfer characteristics for NOR gate is seen in Fig. 3(b), for which the two-input voltages,  $V_{in 1}$  and  $V_{in 2}$ , were switched between the two points corresponding to 0 (low) and 1 (high), as shown in Fig. 3(a) with circles. Note

0003-6951/2008/92(9)/093101/3/\$23.00

<sup>&</sup>lt;sup>a)</sup>Electronic mail: jungchoi@chungbuk.ac.kr.

FIG. 1. Schematics and scanning electron micrograph (SEM) images of the SET/ FET hybrid circuits, each comprising of a FET with CC and two identical SETs which are connected in parallel for (a) NOR and in series for (b) NAND gate, respectively.

that the NOR function can be switched to AND function by simply shifting two initial SET input voltages down to onestep lower levels, as seen by points with squares in Fig. 3(a). Its voltage swing waveform is seen in Fig. 3(c). For the multilevel logic functionality, Fig. 3(d) shows the voltage transfer characteristics for a  $2 \times 3$  binary-MV mixed mode, for which  $V_{\text{in_1}}$  was switched between the two values (0 and 1; binary input) and the other input voltage of  $V_{\text{in_2}}$  was switched among the three values (0, 1, and 2; MV input). They were selected from operating points with triangles, as shown in Fig. 3(a). It is noted that the circuit always produces binary outputs even for MV inputs. For MV output

FIG. 2. (Color online) (a) Schematic and SEM image of the SET element. (b) Coulomb oscillations of the SET for NOR gate measured at 4.2 K. Its charge stability diagram is shown in the inset. (c) Control of the phase of Coulomb current peaks by a side-gate voltage attached to each SET element of NAND gate.

signal, we need to employ the additional components such as inverting adder or latched quantizer.<sup>5</sup> The number of multilevels was observed to decrease with increasing CC load. For

FIG. 3. (Color online) (a) Gray scale contour and three-dimensional plot of the  $V_{out}$  vs two SET input voltages of  $V_{in_1}$  and  $V_{in_2}$ . [(b) and (c)] The voltage transfer characteristics of NOR and AND functions for a 2×2 binary input modes. (d) The voltage transfer characteristics of NOR function for a 2×3 binary-MV mixed mode. (e) Reducing the current leakage in the FET by using a postannealing instead of rapid thermal annealing resulted in increasing the output of the NOR gate up to ~200 mV for a 2×4 binary-MV mixed mode.

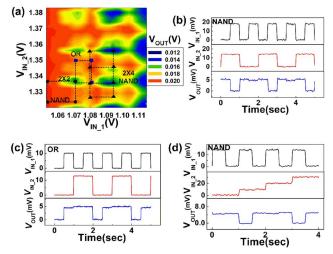

FIG. 4. (Color online) (a) Gray scale contour plot of the  $V_{out}$  vs two SET input voltages of  $V_{in,1}$  and  $V_{in,2}$ . [(b) and (c)] The voltage transfer characteristics of NAND and OR functions for a 2×2 binary input modes. (d) The voltage transfer characteristics of NAND function for a 2×4 binary-MV mixed mode.

a CC load of 100 pA, we could exploit 4 Coulomb oscillations, resulting in eight multilevel functionality. The CC load could be increased up to 5 nA, for which 2 Coulomb oscillations could be used to yield four MV levels.

Figure 4(a) is gray scale contour plot of the voltage output for NAND gates. The CC load is set to 100 pA with a voltage limit of 20 mV and the  $V_{gg}$  of FET is set to 841 mV. Similar to the NOR gate, the  $V_{out}$  displays a periodic high/low pattern versus two SET input voltages. The voltage transfer characteristics are seen in Fig. 4(b) for  $2 \times 2$  binary inputs and in Fig. 4(d) for  $2 \times 4$  binary-MV mixed mode. They were taken from operating points with circles and triangles, respectively, as shown in Fig. 4(a). Similar to NOR-to-AND conversion, the NAND function can be converted into OR by shifting two SET input voltages up to one-step higher levels, as seen by points with squares in Fig. 4(a). Its voltage swing waveform is seen in Fig. 4(c). Tuning ranges of the input voltages for the mode conversions ( $\sim 40 \text{ mV}$  for NOR/AND and  $\sim 20 \text{ mV}$  for NAND/OR for our devices) can be further increased for the stability of operation. Since the input level spacing corresponds to the Coulomb oscillation period, it can be increased by reducing the topgate-Coulomb channel capacitance. We have actually made an enhancement in the tuning range of the input up to ~360 mV by increasing the Coulomb oscillation period of the SET with a reduced gate capacitance  $C_g$ =0.44 aF. It is also noted that the output voltages (~30 mV for NOR and ~10 mV for NAND) are very low. Such a low value of output is mainly due to a leakage in the FET part. By using the postannealing, we have reduced the current leakage in the FET and obtained a threshold with better sharpness, resulting in the output of the NOR gate increased up to ~200 mV, as seen in Fig. 3(e), for a 2×4 binary-MV mixed mode.

As seen in the above data of NAND and NOR gates, the MV logics implemented by SETs are thus very flexible and effective since they fully utilize the periodic mosaic patterns of the output resulting from the multiple switching on/off, which is a unique inherent feature of the SET and is quite different from the single threshold or single negative differential resistance peak in the traditional complimentary metaloxide semiconductor and resonant tunneling transistor.

We thank Dr. H. Inokawa, Dr. A. Fujiwara, and Dr. Y. Ono for helpful discussions. This work was supported by Korea Ministry of Science and Technology through the Frontier 21 National Program for Tera-level NanoDevices (TND), Global Partnership Program (GPP) for Nano- and Optoelectronics, and in part by a research grant of the Chungbuk National University in 2006.

- <sup>1</sup>D. V. Averin and K. K. Likarev, *Single Charge Tunneling*, edited by H. Grabert and M. H. Devoret (Plenum, New York, 1992), p. 311.

- <sup>2</sup>L. Guo, E. Leobandung, and S. Y. Chou, Science **275**, 649 (1997)

- <sup>3</sup>M. Akazawa, K. Kanami, T. Yamada, and Y. Amemiya, IEICE Trans. Electron. **E82-C(9)**, 1607 (1999).

- <sup>4</sup>H. Inokawa, A. Fujiwara, and Y. Takahashi, IEEE Trans. Electron Devices **50**, 462 (2003).

- <sup>5</sup>K. Degawa, T. Aoki, T. Higuchi, H. Inokawa, and Y. Takahashi, IEICE Trans. Electron. **E87-C(11)**, 1827 (2004).

- <sup>6</sup>S. Mahapatra and A. M. Ionescu, IEEE Trans. Nanotechnol. 4, 705 (2005).

- <sup>7</sup>Y. Ono, Y. Takahashi, K. Yamazaki, M. Nagase, H. Namatsu, K. Kurihara, and K. Murase, IEEE Trans. Electron Devices **47**, 147 (2000).

- <sup>8</sup>K. S. Park, S. J. Kim, I. B. Paik, W. H. Lee, J. S. Kang, Y. B. Jo, S. D. Lee, C. K. Lee, J. B. Choi, J. H. Kim, K. H. Park, W. J. Cho, M. G. Jang, and S. J. Lee, IEEE Trans. Nanotechnol. **4**, 242 (2005).

- <sup>9</sup>S. J. Shin, J. J. Lee, R. S. Chung, M. S. Kim, E. S. Park, J. B. Choi, N. S.

- Kim, K. H. Park, S. D. Lee, N. Kim, and J. H. Kim, Appl. Phys. Lett. **91**, 053114 (2007).