# This is a self-archived version of an original article. This version may differ from the original in pagination and typographic details.

Author(s): Witulski, Arthur F.; Ball, Dennis R.; Galloway, Kenneth F.; Javanainen, Arto; Lauenstein, Jean-Marie; Sternberg, Andrew L.; Schrimpf, Ronald D.

Title: Single-Event Burnout Mechanisms in SiC Power MOSFETs

Year: 2018

Version: Accepted version (Final draft)

**Copyright:** © IEEE 2018

Rights: In Copyright

Rights url: http://rightsstatements.org/page/InC/1.0/?language=en

#### Please cite the original version:

Witulski, A. F., Ball, D. R., Galloway, K. F., Javanainen, A., Lauenstein, J.-M., Sternberg, A. L., & Schrimpf, R. D. (2018). Single-Event Burnout Mechanisms in SiC Power MOSFETs. IEEE Transactions on Nuclear Science, 65(8), 1951-1955. https://doi.org/10.1109/tns.2018.2849405

### Single-Event Burnout Mechanisms in SiC Power MOSFETs

Arthur F. Witulski, Dennis R. Ball, Kenneth F. Galloway, Arto Javanainen, Jean-Marie Lauenstein, Andrew L. Sternberg, and Ronald D. Schrimpf

*Abstract:* Heavy-ion induced single-event burnout (SEB) is investigated in high-voltage silicon carbide power MOSFETs. Experimental data for 1200 V SiC power MOSFETs show a significant decrease in SEB onset voltage for particle LETs greater than 10 MeV-cm<sup>2</sup>/mg, above which the SEB threshold voltage is nearly constant at half of the rated maximum operating voltage for these devices. TCAD simulations show a parasitic BJT turn-on mechanism, which drives the avalanching of carriers and leads to runaway drain current, resulting in SEB.

*Index Terms*—Single event effects, heavy ions, silicon carbide, single-event burnout, power devices, power MOSFETs, device simulations, TCAD.

#### I. INTRODUCTION

SILICON CARBIDE (SiC) has excellent properties for power device applications. Compared to silicon, SiC has higher critical breakdown electric field and higher thermal conductivity [1]. SiC devices are ideally suited to high voltage, high power-density power converter applications, both at ground level and in space. However, the sensitivity of SiC power devices (MOSFETs and diodes) to ion irradiation has been found to be higher than might be expected from consideration of material properties.

Silicon-based power MOSFETs, on exposure to heavyion irradiation, may experience catastrophic failure, either single event gate rupture (SEGR) or single event burnout (SEB), above a certain gate and/or drain bias. These failures are well understood with the latter linked to the parasitic bipolar junction transistor, which is an integral part of the device structure [2-5].

Submitted 09/28/2017. Support for this work at Vanderbilt provided by NASA ESI Grant No: NNX17AD09G, at NASA Goddard by the NEPP Program, and at U. Jyväskylä by ESA/ESTEC Contract No. 4000111630/14/NL/PA and Academy of Finland Project No. 2513553.

A.F. Witulski, D.R., Ball, K.F. Galloway, A. Javanainen, A.L. Sternberg, and R.D. Schrimpf are with the Department of Electrical Engineering and Computer Science and the Institute for Space and Defense Electronics, Vanderbilt University, VU Station B 351824, 2301 Vanderbilt Place, Nashville, TN 37235-1824, USA.

A. Javanainen is also with University of Jyvaskyla, Department of Physics, P.O. Box 35, FI-40014, University of Jyvaskyla, Finland.

J-M. Lauenstein is with the NASA Goddard Space Flight Center, Code 561.4, Greenbelt, MD 20771, USA.

SiC power MOSFETs may also undergo catastrophic SEB when exposed to energetic heavy ions or protons. [6-11]. Lauenstein *et al.* [9] point out that two types of ion-induced single-event effects are observed in SiC power MOSFETs: degradation and catastrophic failure. They also say that "at this time the primary failure mode is unclear and that "Signatures are similar across manufacturers and part types: [the] mechanism is more fundamental than geometry or process quality." There have also been some previous efforts at modeling SEB and SEGR effects in SiC power MOSFETs [12].

In this work, we investigate the mechanisms of heavy ion-induced degradation in SiC power MOSFETs using published data plus the addition of new data and new TCAD simulations, which are used to understand the dependence of SEB on ion linear energy transfer (LET) and reverse bias voltage. Parasitic bipolar action can successfully explain the physical mechanisms of SEB in these devices.

## II. EXPERIMENTAL DATA ON SEB FOR SiC MOSFETs

The devices considered here are SiC MOSFETs from Wolfspeed, the C2M0080120D (1200 V, 80 m $\Omega$ ). The irradiation tests were performed at the Lawrence Berkeley National Laboratory (LBNL) 88-inch cyclotron and at the RADEF facility at the University of Jyvaskyla, Finland. For all tests, the ion beam was at normal incidence and in vacuum. The characteristics of the ion beams used are given in Table 1.

Table 1. Characteristics of the ion beams used in this work. The onset bias for SEB is given in the last column.

|       | Ion | Energy | LET(SiC)                  | SEB    |

|-------|-----|--------|---------------------------|--------|

|       |     | [MeV]  | [MeV/mg/cm <sup>2</sup> ] | onset  |

|       |     |        |                           | bias   |

| LBNL  | В   | 108    | 1.0                       | 1100 V |

| LBNL  | Ar  | 400    | 10.4                      | 600 V  |

| RADEF | Ν   | 139    | 2.0                       | 850 V  |

| RADEF | Ne  | 186    | 3.9                       | 650 V  |

| RADEF | Ar  | 373    | 10.8                      | 525 V  |

| RADEF | Xe  | 1217   | 62.4                      | 525 V  |

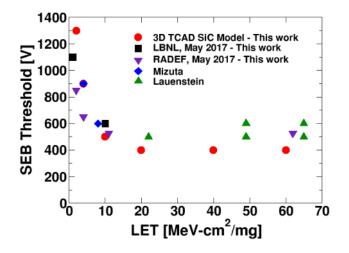

For the SEB test, the devices were monitored with the source and gate grounded, and the drain biased during irradiation. The observed SEB onset bias data are given in Table 1. These data are also shown in Fig. 1, and compared to published data and TCAD simulation results (discussed in the next section). The data from this work match the trend evident in the previously published data, where the onset voltage for SEB failure threshold increases significantly at decreasing LET.

Figure 1. Approximate SEB bias threshold voltages for 1200 V SiC MOSFETs measured in ion beams comparing 3D TCAD SEB simulations to measured data. Previous data shown in Fig. 1 is from Mizuta [8] and Lauenstein [9].

In Fig. 1, the high LET points from 23 to 66 MeVcm<sup>2</sup>/mg are from Lauenstein *et al.* [9], illustrating the single event burnout (SEB) failure of a number of commercially available 1200 V SiC power MOSFETs. Note that all devices fail at voltages significantly below the device rated voltage of 1200 V.

Data from Mizuta *et al.* [8] are also shown in Fig. 1. They tested the same 1200 V SiC MOSFET and observed SEB at 600 V for Ne ions at LET = 6.9 MeVcm<sup>2</sup>/mg and at 900 V for N ions at LET = 3.6 MeVcm<sup>2</sup>/mg. They tested with LET values between 3.6 and 73.1 MeV-cm<sup>2</sup>/mg. For their proton tests, they observed that SEBs were "mainly caused by spallation fragments close to Na and Al ions, and SEBs were observed at around 80% of the rated voltage." In addition to SEB, permanent damage in SiC MOSFETs occurs as an increase in drain leakage current with higher LET ions similar to leakage in SiC Schottky Barrier diodes [13]. No leakage current increase was observed for lower LET ions including protons [7] before SEBs were observed.

#### **III. SIMULATION RESULTS**

A 3D model of a 1200 V SiC power DMOSFET was developed in the Synopsys Sentaurus suite of TCAD

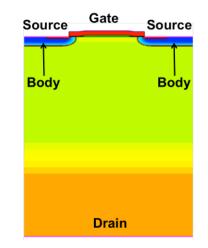

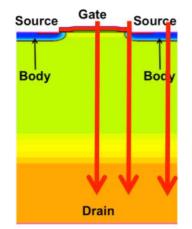

tools [14], based on information from Wolfspeed and from the published literature. Figure 2 illustrates the structure of the power MOSFET simulated via a 2D cross-section of the device, which is uniform in the third dimension (not shown) due to a striped cell design. For these simulations, the depth of the structure is  $1\mu m$ , and Table 2 contains the simulation parameters.

Figure 2. Representative 2D cross-section from Synopsys Sentaurus SiC 3D SiC power MOSFET TCAD model. The device is uniform in the third dimension.

Table 2: Parameters used in TCAD simulations

| Parameter               | Value                                         |  |

|-------------------------|-----------------------------------------------|--|

| 4H-SiC                  | Bandgap=3.26 eV                               |  |

| N-Epi Doping/Depth      | $10^{15} \text{ cm}^{-3}$ , 10 $\mu \text{m}$ |  |

| Body Doping/Depth       | $10^{18} \text{ cm}^{-3}, 1 \ \mu\text{m}$    |  |

| N+ Drain Doping         | $10^{19} \mathrm{cm}^{-3}$                    |  |

| Ion Track Radius/Length | 50 nm, 15 μm                                  |  |

| Impact Ionization Model | Anisotropic Avalanche                         |  |

The single-event simulation matrix varied the heavy ion charge deposition from 0.007 pC/um to 0.042 pC/um (which can be converted to LET = 1 MeV-cm<sup>2</sup>/mg to 60) MeV-cm<sup>2</sup>/mg), and drain bias from 400 V to 1600 V, in 100 V increments. The heavy ion strike occurs 100 ps after the simulation begins, giving the device simulation ample time to achieve steady state, and the Gaussian track radius is 50 nm spatially with a 2 ps Gaussian time parameter. Anisotropic impact ionization models developed specifically for 4H-SiC [14,15], which are critical for simulating breakdown, were employed. Thermal equations (lattice heating) were not considered for this study. Figure 3 shows the simulated heavy-ion induced drain current as a function of time for LET = 10MeV-cm<sup>2</sup>/mg at 700 V and 800 V drain bias, with and without impact ionization turned on. The runaway drain current at 800 V with the SiC impact ionization model turned on indicates that SEB has occurred, whereas the device recovers with impact ionization turned off, or if the device is biased at 700 V.

10 700V Impact Ionization 800V No Impact Ionization 10 800V Impact Ionization Drain Current [A/µm] 10 10 10 10<sup>°°</sup> 100 200 300 400 500 600 700 800 Time [s]

Figure 3. TCAD heavy ion simulations of SiC power MOSFET, showing SEB at 800 V at LET=5 MeV-cm<sup>2</sup>/mg with the impact ionization model turned on during TCAD simulation, and device recovery at other conditions.

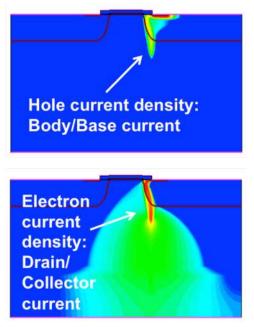

Figure 4. A 2D cross-section TCAD simulation result 250 ps after the strike occurs, showing hole current density (A/cm<sup>2</sup>) (top), electron current density (bottom) with the impact ionization model turned off, for LET=5 MeV-cm<sup>2</sup>/mg at  $V_D$ =800 V. Blue indicates a current density of 1 A/cm<sup>2</sup> while red indicates a current density of 10<sup>6</sup> A/cm<sup>2</sup>.

With the impact ionization model turned on, at a bias of 700 V, the drain current decays immediately after the strike, and approximately half a nanosecond after the strike has occurred, the device has largely recovered. For a bias of 800 V without the ionization model, the drain current shows a slight recovery as the device moves from drift collection into a state where impact ionization can begin, and then increases indefinitely and never exits the SEB state, which in a physical device would result in thermal damage.

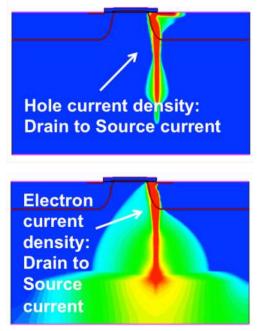

Figure 5. A 2D cross-section TCAD simulation result 250 ps after the strike occurs, showing hole current density (A/cm<sup>2</sup>) (top), electron current density (bottom) with the impact ionization model turned on, for LET=5 MeV-cm<sup>2</sup>/mg at  $V_D$ =800 V. Blue indicates a current density of 1 A/cm<sup>2</sup> while red indicates a current density of 10<sup>6</sup> A/cm<sup>2</sup>.

The importance of impact ionization to the burn-out process is apparent in Figs. 4 and 5, which show 2D cross-section TCAD time slices 250 ps after the strike occurs, or 350 ps of simulation time corresponding to the time scale in Fig. 3. This time was chosen to highlight the differences between the two cases. Much earlier, and the two cases look very similar and hard to distinguish any significant differences. Much later and the impact ionization simulation has advanced so far that the device has started to become flooded with carriers and is difficult to use as a comparison against the no impact ionization case. Figure 4 shows hole current density  $(A/cm^2)$  (top) and electron current density (bottom) without impact ionization turned on, for LET = 10 MeV $cm^2/mg$  at  $V_D = 800$  V. Figure 5 illustrates a 2D crosssection TCAD time slice after the strike occurs, with hole current density  $(A/cm^2)$  (top) and electron current density (A/cm<sup>2</sup>) (bottom) with impact ionization turned on, again for LET = 10 MeV-cm<sup>2</sup>/mg at  $V_D = 800$  V. Both electrons and holes exhibit significantly higher current densities with the impact ionization model active, revealing the presence of a cylinder of current from the ion strike on the source down to the highlydoped drain region. Without impact ionization turned on in the simulation, SEB does not occur with these parameters.

As shown in Fig. 1, at LET = 20 MeV-cm<sup>2</sup>/mg and higher, according to the TCAD model, the TCAD model predicts the drain bias required for SEB is approximately 500 V, which shows excellent agreement with data from this work and previously published work [8,9]. Of particular interest is the independence of the SEB bias level on LET above 20 MeV-cm<sup>2</sup>/mg, as illustrated by the plateau or shelf in Fig. 1. However, below LET = 20 MeV-cm<sup>2</sup>/mg, both simulation and data show a very sharp increase in the drain bias required for SEB, indicating that SEB is highly sensitive to LET and drain bias in this region.

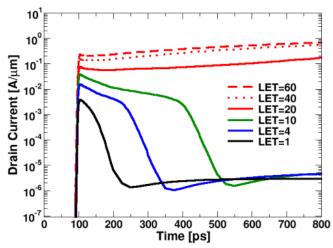

TCAD simulation results shown in Fig. 6 further illustrate that SEB is a function of device reverse bias and ion LET. The ion is assumed to pass through the source, body and drain. The bias is fixed at 500 V and the LET is varied from 1 to 60 MeV-cm<sup>2</sup>/mg. These simulation results show drain current transients as a function of time. At 500 V, SEB does not occur at an LET of 10 MeV-cm<sup>2</sup>/mg or below, but does occur at LETs of 20 MeV-cm<sup>2</sup>/mg and above. Data (presented in Fig. 1) do not indicate a threshold sensitivity to bias once 500 V is passed for higher LETs. This bias creates an electric field high enough to initiate impact ionization provided that a particle with sufficient LET passes through the device. Simulation results in Fig. 6 show a drain current peak that shows some dependence on particle LET at a given bias, however, the peak current effect occurs after the threshold drain bias for SEB has already been attained, so it does not affect the threshold.

Figure 6. TCAD heavy ion simulations of a SiC power MOSFET, showing a drain current transient as a function of LET with the drain biased at 500 V. At LETs of 20 MeV- $cm^2/mg$  and greater, the drain current runs away, indicating SEB. The impact ionization model is active during simulation.

In addition to bias and LET dependence, SEB in SiC power MOSFETs also depends on strike location,

similar to silicon power MOSFETs [16]. The simulated effect of ion strike location (shown in Fig. 7) on SEB is shown in Table 3. All strikes are at normal incidence, and both strike location and LET are varied for these simulations. For a given bias, increasing LET over the threshold value leads to an increasing area of sensitivity. This occurs because the charge generated by the ion strike must be sufficient to turn on the parasitic bipolar transistor locally. As the strike location moves farther from the sensitive area, the particle LET must increase for SEB to occur so that the deposited charge that diffuses to the sensitive region is sufficient to trigger burnout. Combined with a suitable electric field (from drain bias), the parasitic BJT can turn on and carrier avalanching can further drive current flow and SEB.

Figure 7. 2D cross-section of TCAD model, with arrows indicating varied strike locations for single events. In all cases, ion is at normal incidence. The impact ionization model is activated.

| Location       | Center | Source/ | Body/ |

|----------------|--------|---------|-------|

|                | Gate   | Body    | Drain |

| LET=4 @ 1400 V | No     | SEB     | No    |

| LET=10 @ 800 V | No     | SEB     | No    |

| LET=20 @ 500 V | No     | SEB     | No    |

| LET=60 @ 500 V | SEB    | SEB     | SEB   |

Table 3: TCAD simulation results indicating SEB as a function of location, LET, and bias

#### IV. DISCUSSION

SEB in power MOSFETs occurs as a result of impact ionization driving rapidly escalating current flow in a device, ultimately leading to the device failing catastrophically. For vertical power devices, there is an inherent parasitic bipolar junction transistor (BJT) that can turn on during a single event strike [2-4], amplifying the current arising from the ion energy deposition, initiating impact ionization, and ultimately leading to device breakdown.

Although the effects of impact ionization are well understood in silicon devices, SiC devices exhibit different characteristics due to the wider bandgap and anisotropic material properties. It is important to use impact ionization models in TCAD that model the anisotropic effects in SiC [17].

With impact ionization models turned off, considerable ion-generated current flows in the device, but the device recovers to the off-state (see Fig. 3). A case where the parasitic BJT has turned on, is shown by the hole and electron current densities in Fig. 4 The heavy-ion generated carriers are sufficient to raise the potential in the body, forward biasing the body/source junction, and providing a path for holes to flow into the source in the form of base current. As the simulation progresses, the carriers recombine, and the parasitic BJT turns off because there is no sustainable injection of charge and the device will recover.

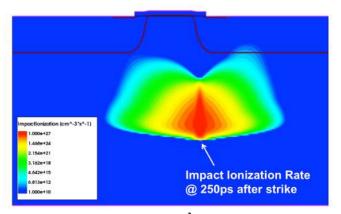

Figure 8. Impact ionization (per cm<sup>2</sup>-s) at the epi/drain junction at 250 ps after the strike occurs for LET=10 MeV-cm<sup>2</sup>/mg at  $V_D$ =800 V. Impact ionization rate ranges from 10<sup>10</sup> cm<sup>-3</sup>·s<sup>-1</sup> (blue color) to 10<sup>27</sup> cm<sup>-3</sup>·s<sup>-1</sup> (red color).

With the impact ionization model turned on (Fig. 5), the significant increase in current density compared to the simulation without impact ionization is a result of avalanche multiplication at the epi/substrate junction, as shown in Fig. 8. The condition for impact ionization is created by charge carrier transport following the strike, and is initiated by localized high electric fields arising from the drain bias. The charge carriers flooding the epi region cause the maximum electric field to relocate from the p-body/epi junction (pre-strike) to the epi/substrate junction as shown by the current generation profile in Fig. 5, with impact ionization rate shown in Fig. 8. In this simulation, the parasitic BJT turns on and the electric field is high enough that impact ionization can begin, such that carrier multiplication occurs quickly. In other device structures, it may be possible to initiate this process without the effective gain of the parasitic bipolar [18]. In Fig. 5, the current from the generated carriers shorts the source to the drain. The electron and hole current flow is a direct path from source to drain, and the avalanching effects cause the currents to continue increasing, leading to a catastrophic SEB failure. In a TCAD simulation, there is no way to differentiate between parasitic BJT current and current generated from avalanching carriers. Thus, it is important to simulate both cases, with and without impact ionization, to understand the mechanisms causing failure.

#### V. SUMMARY AND CONCLUSIONS

The TCAD model developed in this work shows close agreement between simulated SEB and measured SEB as a function of particle LET and bias for a variety of ion-beam experiments on the same 1200 V device. For LET values above 20 MeV-cm2/mg and greater, the SEB threshold is relatively insensitive to LET. However, at low LET, both the TCAD model and data show that SEB is highly sensitive to both LET and bias.

TCAD simulations without impact ionization models turned on show parasitic bipolar action that results in a transient pulse that lasts for approximately a nanosecond, but as carriers recombine, the device recovers fully to its pre-strike condition. TCAD simulations with impact ionization models turned on show that the parasitic BJT and the impact ionization in the epitaxial-drain junction interact to initiate avalanche multiplication, leading to sustained bipolar action and continuously increasing drain current that results in SEB.

Turn-on of the parasitic bipolar transistor inherent in the SiC power MOSFET structure successfully explains the physical mechanisms leading to catastrophic SEB in the devices considered in this work.

#### VI. ACKNOWLEDGEMENT

We would like to thank Robert Reed and Dan Fleetwood at Vanderbilt, Ari Virtanen at the University of Jyvaskyla, Véronique Ferlet-Cavrois at ESA, Dave Grider, Dan Lichtenwalner, and Brett Hull at Wolfspeed, Ashok Raman and Robert Arslanbekov at CFDRC, and Ray Ladbury at NASA Goddard Space Flight Center for very useful discussions of SEB in SiC power devices.

#### VII. REFERENCES

- A. Elasser and T.P. Chow, "Silicon Carbide Benefits and Advantages for Power Electronic Circuits and Systems," *Proc. IEEE*, vol. 90, no. 6, pp. 969-986, Jun. 2002.

- [2] G. H. Johnson, J. H. Hohl, R. D. Schrimpf, and K. F. Galloway, "Simulating single-event burnout of n-channel power MOSFET's," *IEEE Trans. Elect. Dev.*, vol. 40, no. 5, pp. 1001-1008, May 1993.

- [3] G. H. Johnson, J. M. Palau, C. Dachs, K. F. Galloway, and R. D. Schrimpf, "A review of the techniques used for modeling single-event effects in power MOSFET's," *IEEE Trans. Nucl. Sci.*, vol. 43, no. 2, pp. 546-560, Apr. 1996.

- [4] S. Liu, M. Boden, D. A. Girdhar, and J. L. Titus, "Single-event burnout and avalanche characteristics of power DMOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3379-3385, Dec. 2006.

- [5] J.L. Titus, "Updated Perspective of Single Event Gate Rupture and Single Event Burnout in Power MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1912–1928, Jun. 2013.

- [6] G. Sölkner, W. Kaindl, M. Treu, and D. Peters, "Reliability of SiC power devices against cosmic radiation-induced failure," *Mat. Sci. Forum*, vols. 556-557, pp. 851-856, Sep. 2007.

- [7] M. C. Casey, J. Lauenstein, A. D. Topper, E. P. Wilcox, H. Kim, A. M. Phan, and K. A. Label, "Single-Event Effects in Silicon Carbide Power Devices," presented at IEEE Nuclear and Space Radiation Effects Conf., July 2013, and 2012 NASA NEPP Electronic Technology Workshop, nepp.nasa.gov.

- [8] E. Mizuta, S. Kuboyama, H. Abe, Y. Iwata, T. Tamura, and A. S. Device, "Investigation of Single-Event Damages on Silicon Carbide (SiC) Power MOSFETs," *IEEE Trans Nucl. Sci.*, vol. 61, no. 4, pp. 1924–1928, Aug. 2014.

- [9] J-M. Lauenstein, M. C. Casey, A. D. Topper, E. P. Wilcox, A. M. Phan, S. Ikpe, and K. A. LaBel, "Silicon Carbide Power Device Performance Under Heavy-Ion Irradiation," presented at IEEE Nuclear and Space Radiation Effects Conf., Jul. 2015.

- [10] A. Bolotnikov, P. Losee, A. Permuy, G. Dunne, S. Kennerly, B. Rowden, J. Nasadoski, M. Harfman-Todorovic, R. Raju, F. Tao, P. Cioffi, F.J. Mueller, and L. Stevanovic, "Overview of 1.2kV 2.2kV SiC MOSFETs targeted for industrial power conversion applications," *Proc. 2015 IEEE Applied Power Electronics Conference and Exposition*, pp. 2445-2452, Charlotte, NC, Mar. 2015.

- [11] A. Akturk, R. Wilkins, J. McGarrity, and B. Gersey, "Single Event Effects in Si and SiC Power MOSFETs Due to Terrestrial Neutrons," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 1, pp. 529-535, Jan. 2017.

- [12] Xiaohu Zhang, "Failure Mechanism Investigation for Silicon Carbide Power Devices," Ph.D. Dissertation, U. Maryland, 2006.

- [13] A. Javanainenm K.F. Galloway, C. Nicklaw, A.L. Bosser, V. Ferlet-Cavrois, J-M. Lauenstein, F. Pintacuda, R.A. Reed, R.D. Schrimpf, R.A. Weller, and A. Virtanen, "Heavy Ion Induced Degradation in SiC Schottky Diodes: Bias and Energy Deposition Dependence," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 1, pp. 415–420, Jan. 2017.

- [14] Synopsys TCAD tools, <u>www.synopsys.com</u>

- [15] T. Hatakeyama, T. Watanabe, T. Shinohe, K. Kojima, K.Arai, and N. Sano, "Impact Ionization Coefficients of 4H Silicon Carbide," *Applied Phys. Lett.*, vol. 85, pp. 1380-1382, Aug. 2004.

- [16] M. Allenspach, C. Dachs, G.H. Johnson, R.D. Schrimpf, E. Lorfevre, J.M. Palau, J.R. Brews, K.F. Galloway, J.L. Titus, and C.F. Wheatley, "SEGR and SEB in N-Channel Power MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 43, no. 6, pp. 2927–2931, Dec. 1996.

- T. Hatakeyama, J. Nishio, C. Ota, and, T. Shinohe, "Physical Modeling and Scaling Properties of 4H-SiC Power Devices," pp. 171-174, *Proc. SISPAD 2005*, pp. 171-174, Tokyo, Japan, Sep. 2005.

- [18] T. Shoji, S. Nishida, K. Hamada, and H. Tadano, "Analysis of neutron-induced single-event burnout in SiC power MOSFETs," *Micro. Rel.*, vol. 55, pp. 1517-1521, 2015.