Open access • Proceedings Article • DOI:10.1109/WCADM.1995.514642

## Single-rail handshake circuits — Source link <a> □</a>

Anna Peeters, K. van Berkel

Institutions: Eindhoven University of Technology, Philips

Published on: 30 May 1995

Topics: Asynchronous system, Handshake and Asynchronous communication

#### Related papers:

- Handshake Circuits: An Asynchronous Architecture for VLSI Programming

- An asynchronous low-power 80C51 microcontroller

- Communicating Sequential Processes

- · Programming in VLSI: from communicating processes to delay-insensitive circuits

- · Reductivity arguments and program construction

# Single-rail handshake circuits

Citation for published version (APA):

Peeters, A. M. G. (1996). *Single-rail handshake circuits*. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR461274

DOI:

10.6100/IR461274

Document status and date:

Published: 01/01/1996

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 30. May. 2022

# Single-Rail Handshake Circuits

Ad M.G. Peeters

# Single-Rail Handshake Circuits

# Ad M. G. Peeters

Peeters, Adrianus Marinus Gerardus.

Single-Rail Handshake Circuits / Ad M. G. Peeters. Proefschrift Technische Universiteit Eindhoven. Met lit. opg. - Met samenvatting in het Nederlands.

ISBN 90-74445-28-4

Trefw.: IC-design, VLSI, asynchronous circuits.

# Single-Rail Handshake Circuits

#### PROEFSCHRIFT

TER VERKRIJGING VAN DE GRAAD VAN DOCTOR

AAN DE TECHNISCHE UNIVERSITEIT EINDHOVEN,

OP GEZAG VAN DE RECTOR MAGNIFICUS,

PROF. DR. J.H. VAN LINT,

VOOR EEN COMMISSIE AANGEWEZEN

DOOR HET COLLEGE VAN DEKANEN

IN HET OPENBAAR TE VERDEDIGEN

OP WOENSDAG 12 JUNI 1996 OM 16.00 UUR

#### DOOR

ADRIANUS MARINUS GERARDUS PEETERS

GEBOREN TE DONGEN

Dit proefschrift is goedgekeurd door de promotoren:

prof. dr. M. Rem

en

prof. S. B. Furber

en door de copromotor:

dr. ir. C. H. van Berkel.

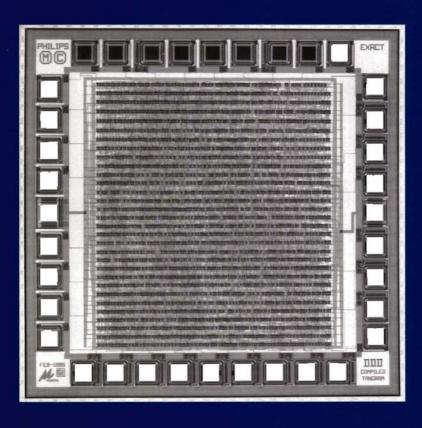

The work described in this thesis has been carried out at Philips Research Laboratories Eindhoven while the author was employed on EXACT (ESPRIT project 6143) by Eindhoven University of Technology, under the auspices of the research school IPA (Institute for Programming research and Algorithmics).

# Contents

| Pr | eface                 |                                | V  |  |  |  |  |  |  |

|----|-----------------------|--------------------------------|----|--|--|--|--|--|--|

| 1  | Intro                 | duction                        | 1  |  |  |  |  |  |  |

|    | 1.1                   | Tangram project                | 2  |  |  |  |  |  |  |

|    | 1.2                   | Roadblocks                     | 3  |  |  |  |  |  |  |

|    | 1.3                   | Challenges                     | 4  |  |  |  |  |  |  |

|    | 1.4                   | Contributions                  | 5  |  |  |  |  |  |  |

|    | 1.5                   | Overview                       | 6  |  |  |  |  |  |  |

| 2  | Tang                  | Tangram Handshake Circuits 7   |    |  |  |  |  |  |  |

|    | 2.1                   | VLSI Programming               | 7  |  |  |  |  |  |  |

|    | 2.2                   | Handshake circuits             | 11 |  |  |  |  |  |  |

|    | 2.3                   | Tangram                        | 18 |  |  |  |  |  |  |

|    | 2.4                   | Tangram handshake circuits     | 23 |  |  |  |  |  |  |

| 3  | Sing                  | e-Rail Data Encoding           | 25 |  |  |  |  |  |  |

|    | 3.1                   | Single rail                    | 25 |  |  |  |  |  |  |

|    | 3.2                   | Handshake channels             | 26 |  |  |  |  |  |  |

|    | 3.3                   | Two phase                      | 27 |  |  |  |  |  |  |

|    | 3.4                   | Four phase                     | 28 |  |  |  |  |  |  |

|    | 3.5                   | Single track                   | 32 |  |  |  |  |  |  |

|    | 3.6                   | Minimum-power schemes          | 32 |  |  |  |  |  |  |

|    | 3.7                   | Extended data-valid schemes    | 33 |  |  |  |  |  |  |

|    | 3.8                   | Synchronous data-valid schemes | 34 |  |  |  |  |  |  |

|    | 3.9                   | Options                        | 35 |  |  |  |  |  |  |

| 4  | Handshake Circuits 37 |                                |    |  |  |  |  |  |  |

|    | 4.1                   | Structure                      | 37 |  |  |  |  |  |  |

|    | 4.2                   | Assignment                     | 39 |  |  |  |  |  |  |

|    | 4.3                   | Communication                  | 50 |  |  |  |  |  |  |

ii Contents

|   | 4.4        | Iteration                               | 54               |

|---|------------|-----------------------------------------|------------------|

|   | 4.5        | Selection                               | 55               |

|   | 4.6        | Sharing                                 | 58               |

|   | 4.7        | Conclusion                              | 61               |

| 5 | Han        | dshake Components                       | 63               |

|   | 5.1        | •                                       | 63               |

|   | 5.2        | 1                                       | 71               |

|   | 5.3        |                                         | 79               |

|   | 5.4        | •                                       | 90               |

|   | 5.5        | *****                                   | 98               |

|   | 5.6        | F                                       | 05               |

| _ | Doc        | on Flour                                | 07               |

| 6 | 6.1        | <b>-</b>                                | υ <i>τ</i><br>07 |

|   | 6.2        | e                                       |                  |

|   | 6.3        | Tangram compilation                     | uo<br>14         |

|   | 6.4        | ī                                       | 14<br>19         |

|   | 6.5        | · 1                                     | 19<br>23         |

|   |            | $\mathcal{E}$                           | 23<br>28         |

|   | 6.6        | $\mathcal{E}$                           |                  |

|   | 6.7<br>6.8 |                                         | 29<br>29         |

|   | 0.0        | Conclusion                              | 29               |

| 7 | Dem        |                                         | 33               |

|   | 7.1        |                                         | 33               |

|   | 7.2        | Diagram                                 |                  |

|   | 7.3        | Tangram program                         |                  |

|   | 7.4        |                                         | 37               |

|   | 7.5        | Gate netlist                            | 38               |

|   | 7.6        | Measurements                            | 44               |

|   | 7.7        | Evaluation                              | 47               |

|   | 7.8        | Conclusion                              | 51               |

| 8 | Con        | clusion 1                               | 53               |

|   | 8.1        | Comparison                              | 53               |

|   | 8.2        |                                         | 65               |

|   | 8.3        | e                                       | 67               |

|   | 8.4        |                                         | 67               |

|   | 8.5        | • • • • • • • • • • • • • • • • • • • • | 68               |

|   | 8.6        | Remaining issues                        | 69               |

| Contents         | iii |

|------------------|-----|

| Bibliography     | 171 |

| Summary          | 179 |

| Samenvatting     | 183 |

| Curriculum Vitae | 187 |

iv Contents

# **Preface**

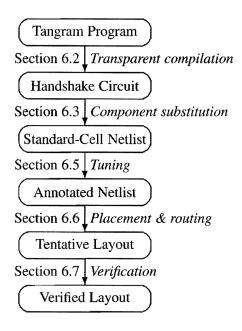

In the Tangram project at Philips Research Laboratories Eindhoven, silicon compilation and asynchronous circuit techniques are combined to enable the fast design of low-power circuits. VLSI designers using the Tangram system are offered a powerful programming language, called Tangram, a compiler from Tangram to standard-cell netlists, and several tools that give fast and accurate feedback on performance aspects such as area, time, energy, and testability.

Handshake circuits form an intermediate representation in the compilation from Tangram to silicon. At this level one can still choose between various handshake protocols and data encodings. The first version of the Tangram system was based on the combination of a four-phase handshake protocol and double-rail data encoding.

These double-rail handshake circuits successfully demonstrated the low-power potential of compiled asynchronous circuits. The low-power advantage, however, came at too high costs, namely an unacceptable area overhead and a dedicated standard-cell library.

The challenge that was formulated for the research documented in this thesis was to remove these two roadblocks towards exploitation. To this end single-rail techniques were investigated and applied to handshake circuits.

The thesis introduces single-rail implementations of handshake circuits as a cost-effective way to realize low-power asynchronous circuits. The thesis presents an overview of several ways to combine single-rail data encoding with handshake protocols. A design-flow from Tangram to single-rail realizations in a generic standard-cell library is defined. This flow is applied successfully to a demonstrator IC: an error-detector that is part of a DCC player.

Much of the research that is documented in this dissertation was carried out in the context of EXACT<sup>1</sup>. The aim of this ESPRIT project was to demonstrate the low-power promise of asynchronous VLSI circuits. The single-rail DCC chip was used as one of the demonstrators in EXACT.

<sup>&</sup>lt;sup>1</sup>EXploitation of Asynchronous Circuit Technologies (ESPRIT project 6143)

# Acknowledgements

Throughout the years the Tangram Team at Philips Nat.Lab. has always been an inspirational environment to work in. I am especially indebted to Kees van Berkel for inviting me 'to spend a brief period' in the team, to learn more about asynchronous circuit design. This was is July 1991, and since then I have learned a lot and was allowed to work on some challenging problems. I would like to thank Eric van Utteren and the members of the team, Ronan Burgess, Joep Kessels, Marly Roncken, Frits Schalij, Hans van Gageldonk, and Rik van de Wiel, for their support and the pleasant cooperation.

Ever since my M.Sc. work in the Parallelism and Architecture group at Eindhoven University, Martin Rem has encouraged me to write a Ph.D. thesis on asynchronous silicon compilation. I am most grateful to him for this continuous support and for his help in focusing the thesis on single-rail handshake circuits.

I want to thank the members of the thesis committee —which, in addition to Martin Rem and Kees van Berkel, consisted of Steve Furber, Emile Aarts, and Jochen Jess— for the effort they put into judging this thesis.

During the period that I worked for EXACT, Andrew Bailey has been an ideal colleague. We had a lot of interesting discussions, not only on asynchronous circuit design, but also on politics, religion, and other facts of life.

The members of the Eindhoven VLSI club are acknowledged for the regular Friday-morning discussions. Rudolf Mak and Tom Verhoeff taught me to be critical. Jo Ebergen introduced me into the interesting field of asynchronous and delayinsensitive circuit design.

Manchester University was one of the partners in EXACT and during my work I had the opportunity to pay some visits to the AMULET group. The discussions with Steve Furber, Craig Farnsworth, Shiv Sikand, and Doug Edwards helped me in understanding more about micropipeline techniques.

ESPRIT Working Group 7225 (ACiD) is gratefully acknowledged for funding my visits to Manchester University and to workshops and conferences.

There is a lot more to life than working, and for me, running has become one of the major other occupations. It has always been an excellent way to relax after or during a working day and to find new inspiration. On the other hand, the sort of work I have been doing enabled me to train a lot and to turn running into a way of life. Although running is often considered to be an individual sport, I have always experienced it as a team sport, for which I would like to thank a lot of friends, especially the former Asterix core, the current PSV running group, the Nat.Lab. runners, and their respective trainers.

# Chapter 1

# Introduction

The market for portable consumer-electronic products is booming, and is expected to continue to grow at a high rate for many years to come. Portable telephones, digital assistants, notebooks, video games, buzzers, and portable digital audio, are products that already today are affordable to a lot of people. Several key technologies have made the introduction of all these portable devices possible. Display technology, audio and video compression, and IC technology are some of these enabling technologies.

Power consumption is a major issue for all these portable products. Low power consumption of a device may enable the use of less batteries, which results in a lighter and more appealing product, or alternatively, the product may be recharged less frequently.

An important source of power consumption is the digital signal processing inside these portable products. The ever decreasing dimensions of especially CMOS IC-technology have enabled the integration of more and more digital functions. Although CMOS was originally preferred because of its low-power consumption in comparison with other technologies, power consumption of digital CMOS ICs has now become a main concern. Digital ICs demand an ever increasing portion of the power budget of portable devices.

One of the alternatives that is investigated to reduce the power consumption of digital ICs is not to use a clock to drive the operation of the IC, but to apply asynchronous techniques instead. Although these techniques generally introduce some area overhead because they require some circuitry to replace the control by a clock, the extra cost may be affordable if it results in a significant reduction in energy consumption. Furthermore, the circuits should be implementable against reasonable design-costs, which in general means within a short design time.

This dissertation introduces single-rail implementation of handshake circuits

as a means to realize area-efficient low-power asynchronous VLSI circuits. Neither 'single-rail' nor 'handshake circuits' is a new concept, but the combination of the two is, especially in the context in which it is applied in this thesis, namely that of a silicon compiler and a standard-cell layout style.

Part of the work described here has been reported earlier in two papers at the 1995 London *Asynchronous Design Methodologies* working conference [65, 10]. For references to asynchronous literature the public 'asynchronous' bibliography as maintained at Eindhoven University of Technology has been used [64].

# 1.1 Tangram project

The project 'VLSI Programming and Silicon Compilation' at Philips Research Labs Eindhoven was initiated in 1986. The central idea was —and still is—to view VLSI design as a programming activity. This can be achieved by combining a powerful programming language and a good silicon compiler for that language. In the course of the project a VLSI programming language called 'Tangram' has been defined and a compiler from Tangram to VLSI circuits has been implemented. In the rest of the thesis the project is referred to as 'Tangram project.'

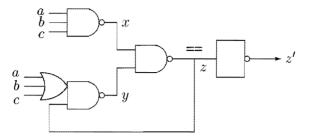

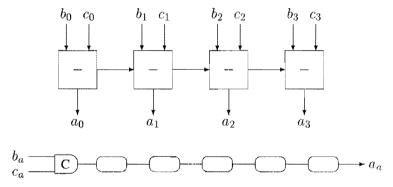

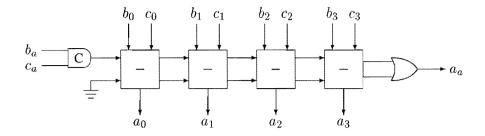

Handshake circuits form the intermediate representation in the fully automatic compilation of Tangram programs to VLSI circuits, and where introduced by Van Berkel in [8]. A handshake circuit is a network of handshake components, connected by point-to-point handshake channels. In such a circuit, all communication takes place via handshaking. VLSI programs written in Tangram are translated in a transparent way into handshake circuits, which are subsequently, on a component-by-component basis, replaced by gate netlists.

Handshake circuits can be realized in silicon in different ways. One of the degrees of freedom is the timing assumptions that are made in this mapping. The only timing assumption that was made originally in the implementation of handshake circuits was that of the *isochronic fork*, which is a fork (branch in a wire to different inputs) for which the difference in the delays between the two branches is shorter than the delays through the gates to which the fork is an input. The isochronic fork is introduced by Burns and Martin [20, 57] and is considered to be an essential and the 'weakest possible' compromise to true delay insensitivity [56] if such circuits are to be realized in CMOS, the dominating IC-technology of today. The resulting circuits are generally called *quasi delay insensitive* (QDI) [19]. Implementation aspects of isochronic forks are well understood [56, 7].

The restriction to QDI implementation of handshake circuits implies that for data communication a delay-insensitive encoding of the data should be used [82]. The most natural coding scheme then is the double-rail code, in which two wires per

1.2. Roadblocks 3

bit are used, one to signal the communication of a '0,' the other for communicating a '1.' Double-rail operations on data, such as addition, require complex cells, not normally available in a standard-cell library. Therefore, a dedicated asynchronous cell library was developed.

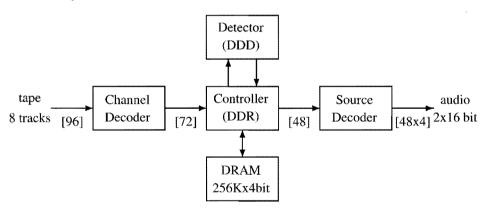

With this approach a number of interesting circuits have been realized. In 1987 the feasibility of the approach was demonstrated with working silicon [6]. This led to the definition of the VLSI-programming language Tangram, the implementation of a compiler from Tangram to handshake circuits, the development of a cell library, the implementation of a compiler for handshake circuits, and the implementation of a tool set to support this design flow. A second demonstrator IC, used to validate the tools and the flow, was reported in 1993 [14]. In terms of complexity the most-notable Tangram-compiled ICs are the chips for the error decoder of the Digital Compact Cassette (DCC) player [11].

The DCC chip set proved that designs of industrially-relevant complexity could be handled by the tools and that interfaces to synchronous environments, standard protocols, and standard DRAMs could be straightforwardly implemented. More importantly, however, the circuits demonstrated an interesting power advantage over a commercial synchronous equivalent: the asynchronous circuit used only a fifth of the energy for the equivalent function.

## 1.2 Roadblocks

Although low power was recognized as a key advantage of Tangram circuits, two roadblocks prohibited practical application and exploitation of Tangram VLSI programming. The most important barrier was the 70 to 100% area overhead of the double-rail circuits over synchronous implementations of the same functions. This overhead is not industrially acceptable, even when the circuits are five times more energy efficient.

A second, increasingly important, obstacle was the use of the dedicated asynchronous standard-cell library, while the trend in industry has been towards generic standard-cell libraries. Such a library comprises standard logic gates (NAND, NOR, AND, OR, XOR), some complex gates (AND-OR-INVerts), inverters and buffers of a range of driving capabilities, and special functions such as adders, multiplexers, decoders, latches, and D-types. The advantage of generic libraries is that a design can easily (fast and cheap) be retargeted to different versions of a given technology (low power, high performance, minimal area), to different technologies (CMOS in various feature sizes, FPGA, gate array), and to different manufacturers.

Both the area overhead and the need for a dedicated cell library are due to the double-rail encoding of data that has been used. Since double-rail uses two wires

per bit in the encoding of data, the area of such a circuit is about twice that of a circuit in which only one wire per bit is used. (Each wire has to be driven by some cell, and hence implies transistors and circuit area.)

# 1.3 Challenges

The goal that was set for the work described in this thesis was to greatly reduce the area overhead of handshake circuits and, simultaneously, to map them onto a generic standard-cell library. Both points are essential when striving for acceptance, application, and production of asynchronous circuits on a larger scale.

The main candidate for area reduction is the datapath, where we should switch from an encoding based on two wires per bit to one that uses only one wire per bit. *Single-rail* data encoding [72], which uses one wire per bit, plus one additional wire to signal the validity of the data, is such an encoding. This form of data encoding is also known as bundled data [75] and was already applied in the sixties in the Macromodule project [74]. Especially for wide datapaths, single-rail encoding should lead to a reduction in the number of wires and transistors, and thus to a smaller area.

The choice for single-rail encoding introduces a new timing assumption. In QDI implementations we only had to consider isochronic forks, but in single-rail we have to take a more quantitative look at delays. The use of a data-valid wire introduces the *bundling constraint* [75]: the data-valid signal must arrive later than the valid data. This implies that the delay through the data-valid path should be larger than the worst-case delay that can be encountered in the datapath.

The bundling constraint implies new verification obligations in the design flow, especially in the context of the standard-cell layout style that we pursue. In this style, the actual delay of gates is only known when the layout is completed and before that we have to resort to estimated wire loads. We have to take the sensitivity of the delays to these estimates into account, most notably in comparing the delay of the datapath with that of the data-valid signal. If we want to minimize the verification effort, we have to combine optimistic estimates for the data-valid wire (low loads, short wires) with pessimistic estimates for the actual data (high loads, long wires). From this observation it is clear that one of the challenges in single-rail implementations is to combine manageable verification effort with acceptable performance.

An important advantage of single-rail datapaths is that datapath operators such as adders and exclusive ors can be found in any generic standard-cell library. This motivates our choice to try and implement *all* handshake components, both control and data, using only such a generic cell library.

The double-rail datapath was identified as the main source for area inefficien-

1.4. Contributions 5

cies. The control path, however, must also taken into account when trying to reduce the area of handshake-circuit implementations. In going from a dedicated to a generic library the circuit area of the control is likely to increase. One possible remedy is to identify frequently occurring combinations of handshake components and to substitute these by more economic implementations. Another approach that might help is to exploit the richness of the generic library through peephole optimization.

Low power is considered to be the key strength of asynchronous circuits. We therefore also strive to improve the power efficiency of handshake circuit implementations. Area reduction, however, *is* the main concern, because the 70–100% area overhead of double-rail circuits is a serious handicap. We furthermore believe that, to some extent, less area implies shorter wires and thus less power and potentially more speed.

Another challenge in the step from double-rail to single-rail is *not* to affect the compilation from Tangram to handshake circuits, thereby keeping this compilation independent of the actual implementation style of the handshake circuit.

We furthermore want to maintain the push-button aspect of the compilation from handshake circuit to layout. This means that we should minimize the effort for post-layout verification. The safety margins in the data bundling, and the sensitivity to variation in processing and operation parameters are, therefore, important aspects of the single-rail design-flow.

Finally, the testability of single-rail circuits (against production faults) is of utmost importance when striving for practical applications.

#### 1.4 Contributions

Throughout the thesis a systematic approach to single-rail handshake circuits is introduced. In going from double-rail to single-rail we basically increase the engineering content of handshake circuit implementations. This improves area, timing, and energy quality of the resulting VLSI circuits at the cost of a well-identified and manageable increase in design effort.

The main contributions of the research documented in this thesis are the following:

- An inventory of single-rail handshake protocols, leading to a surprisingly rich domain to choose from.

- The identification of a four-phase handshake protocol in which all four phases are productive (functional), thus removing an often mentioned disadvantage of four-phase handshaking, namely the redundancy of the return-to-zero phase.

- The definition and implementation of a push-button single-rail design flow, targeted at a generic standard-cell library.

- A single-rail demonstrator in the form of fully functional silicon.

## 1.5 Overview

In this chapter we have given some context and defined the main target of the research that is reported in the rest of the thesis. The structure of the thesis is as follows.

- Chap 2. Introduction to the Tangram VLSI-programming approach. This chapter briefly introduces the VLSI-programming language Tangram, handshake circuits, the compilation from Tangram to these handshake circuits, and an overview of the Tangram toolbox.

- Chap 3. Discussion of single-rail data encoding. Takes stock of various ways to implement handshake channels. Various single-rail data-valid schemes are introduced.

- Chap 4. Implementation of single-rail handshake circuits. The choice of a 'good' data-valid scheme, based on the compilation scheme from Tangram to handshake circuits. The implementations of assignments, communication, iteration, and selection are discussed.

- Chap 5. Implementation of handshake components, based on a data-valid scheme for the handshake channels. The delay assumptions in the implementation of the components are made explicit.

- Chap 6. Single-rail design-flow, with emphasis on the role of peephole optimization at various levels of representation.

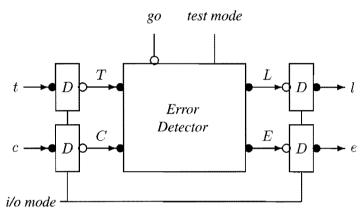

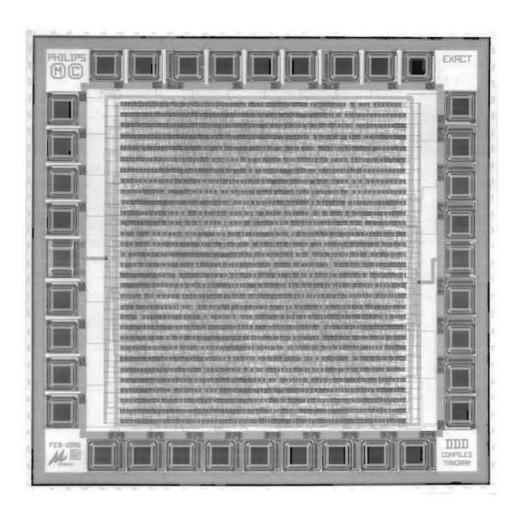

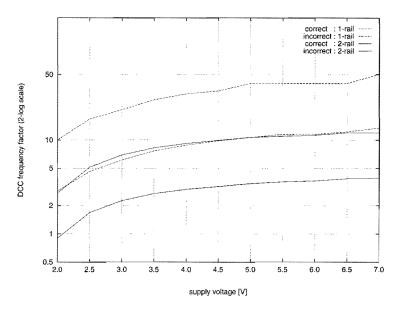

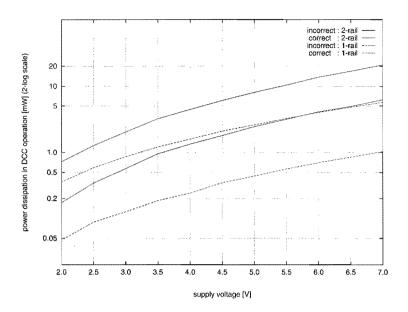

- Chap 7. The viability of single-rail handshake circuits is demonstrated by the implementation of a DCC error detector.

- Chap 8. Single-rail handshake circuits are compared with various other (synchronous and asynchronous) circuit technologies. This leads to an identification of the strengths, weaknesses, opportunities, and threats of single-rail handshake circuits. The chapter ends with an identification of the main remaining issues on the route to exploitation of asynchronous circuits.

# Chapter 2

# Tangram Handshake Circuits

Handshake circuits are the central architecture in the Tangram project. They form the intermediate representation in the compilation from Tangram to VLSI circuits. Essentially, handshake circuits abstract from all VLSI aspects, thus separating Tangram compilation aspects from VLSI technology details.

This chapter briefly sketches the role of Tangram as a VLSI-programming language. Subsequently, handshake circuits, as introduced by Van Berkel [8], are discussed. The compilation from Tangram programs to handshake circuits is addressed, which results in the identification of Tangram handshake circuits: handshake circuits as they can be obtained by compilation from a Tangram program. The efficient implementation of these Tangram handshake circuits is the subject of the rest of this thesis.

# 2.1 VLSI Programming

Silicon compilation, that is, the automatic generation of VLSI circuits from descriptions written in a high-level programming language, demands a powerful programming language and a good compiler. The programming language should abstract from VLSI circuit and technology details, thus allowing the designer to concentrate on application and programming issues. The silicon compiler should be able to translate these programs into *efficient* VLSI circuits automatically, which induces requirements for the programming language.

Two extreme approaches to silicon compilation can be identified. The first is to combine a traditional programming language, like C or Pascal, with a powerful compiler (or, perhaps more accurately, a synthesizer) that extracts parallelism, chooses efficient data-encodings, optimizes the amount of sharing, et cetera. The advantage of this style is that it puts minimal burden on the designer (programmer).

An important disadvantage is that it generally is unclear how to steer the compiler, for example towards a low-power solution. A small change in the input program that was thought to improve a design aspect, may actually decrease the quality of the resulting circuit. A familiar cause for this may be an unexpected side effect: the change may disable optimizations that have been applied to the original program.

The approach that has been chosen in the Tangram project represents the other extreme. It is based on a more dedicated programming language in combination with a highly *transparent* silicon compiler, which allows the designer to infer circuit costs and performance directly from the program. The language (Tangram) is similar to a traditional programming language but in addition

- offers language constructs to explicitly deal with parallelism, at any level of granularity;

- supports synchronized (CSP-like [43]) communication via channels;

- makes the sharing of hardware resources explicit, both for control structures and the datapath; and

- offers provisions for tuple construction and selection, type casting, and type fitting, which can be used to choose the most appropriate and efficient data encoding.

The transparency of the compiler enables the designer to evaluate the silicon area, timing, power consumption, and testability of the compiled circuit at the program level. This high-level feedback is an essential requirement to allow the designer to make trade-offs and to explore the design space.

This approach to silicon compilation is called *VLSI programming* [5], and the designer of such a program is referred to as a *VLSI programmer*.

The VLSI programmer typically is a system expert in the application field for which the design is intended. Detailed VLSI knowledge is not required, since this is hidden in the tools and the libraries. However, some silicon awareness (insight into the area and energy properties of a VLSI design) is essential to arrive at cost-effective solutions.

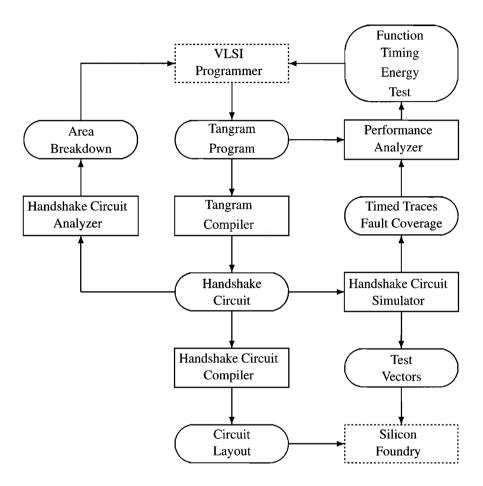

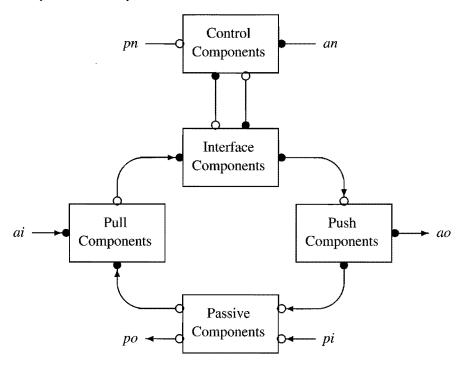

To support the VLSI programmer in the exploration, a set of tools have been defined and developed. These tools, and the VLSI programmer's view on the design flow are illustrated in Fig. 2.1.

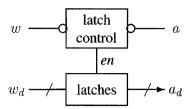

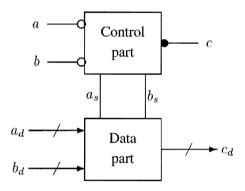

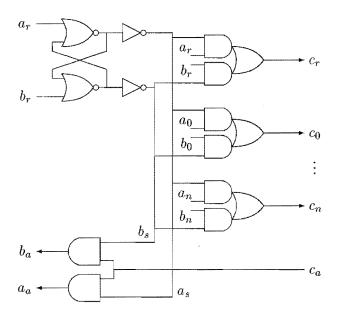

**Tangram Compiler.** This compiler implements the syntax-directed translation of Tangram programs into handshake circuits, as described in [6, 16, 8].

For each production rule of the Tangram syntax a corresponding translation rule to handshake circuits exists in the compiler. This translation is therefore

Figure 2.1: The Tangram Toolbox: boxes denote tools, ovals denote (design) representations.

highly transparent, and allows one to relate performance criteria like timing, area, power, and testability directly to the Tangram program.

- Handshake Circuit Simulator. This discrete event simulator is based on detailed functional, timing, energy, and test models of handshake components. The test-coverage part of this simulator is described in detail by Van de Wiel [79]. The other design aspects have also been modeled in VHDL, which makes cosimulation of Tangram generated circuits and other designs relatively straightforward.

- **Performance Analyzer.** This is a tool with a high-quality graphical user interface that is used to link simulation results to the Tangram program. After simulation, the VLSI-programmer can use this interactive tool to evaluate the performance and the energy consumption of the Tangram program, and to identify possible bottlenecks and 'hot spots.'

- *Handshake Circuit Analyzer.* This tool generates area statistics from a handshake circuit. In contrast to the other performance criteria, area information is not translated back to the Tangram level.

- Handshake Compiler. Compilation from handshake circuits to layout consists of several steps, which are detailed in Chapter 6. This compilation forms the central theme of this thesis and can be partitioned into two phases: component substitution and layout generation. Component substitution is the mapping of handshake components onto a cell library and is part of the Tangram tool set. The netlist that results from this phase can be input in any commercially available CAD framework for placement, routing, simulation, and verification.

In addition to the tools shown in the diagram and mentioned above there is also a faster simulator that can be used for functional and coarse-grain timing simulation. This simulator is based on the direct compilation of Tangram to C, without using handshake circuits as intermediate. The timing information is linked to the Tangram program using the same performance analyzer as for the handshake circuit simulator. A VLSI programmer typically uses this tool during the initial phase of the design, when fast iteration is more important than high accuracy.

In the final stage of the design other simulators, based on representations that are more detailed than the handshake circuit (netlist, layout) are also used. These simulations are typically part of a standard CAD framework, and are not dedicated to asynchronous or handshake circuits.

#### 2.2 Handshake circuits

Handshake circuits form the intermediate representation in the compilation from Tangram programs to VLSI. It is the central architecture throughout this thesis. In this section we introduce handshake channels, handshake components (which communicate via such channels), and handshake circuits (networks of handshake components).

#### 2.2.1 Handshake channels

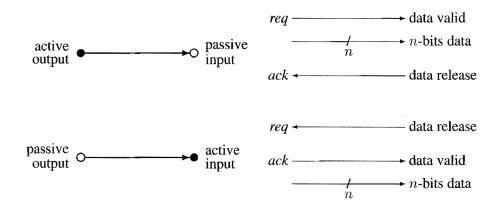

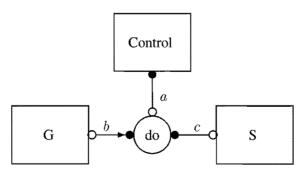

Handshake signaling is a communication mechanism that establishes point-to-point synchronization. A handshake involves two partners which play different roles, called *active* and *passive*. The partners exchange so-called *request* and *acknowledge* signals. The passive partner waits for a request to arrive and after receipt of a request responds with sending an acknowledge. The active partner starts with issuing a request and then waits for the corresponding acknowledge to arrive. Such a combination of a request and an acknowledge is called a handshake.

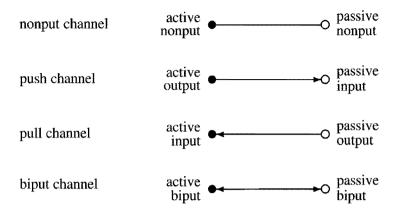

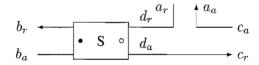

Throughout this thesis we assume the active and passive roles to be fixed, which means that one partner will always be active, and the other will always be passive. The communication medium between the partners is called a *handshake channel*. We conform to the convention to denote an active handshake partner with a fat dot (•), and a passive partner with an open circle (O), see Fig. 2.2.

Figure 2.2: A handshake channel represents the communication medium between an active and a passive handshake partner.

Those who are used to think in terms of Petri-nets [67], places, and tokens, may think of handshake communication as the exchange of tokens. Initially the active partner has the token. Sending a request is then interpreted as passing the token from the active to the passive partner. An acknowledge is represented by sending the token from the passive to the active partner. The fat dots and open circles can then be thought of as indicating the initial distribution of the tokens.

A handshake essentially synchronizes the active and the passive partner. In addition to pure synchronization, handshakes can also establish data communication between the partners by encoding data in the request, in the acknowledge, or in both.

Handshake channels with no data encoded are called *nonput* channels. They connect two so-called nonput handshake partners, one active, one passive. A hand-

shake on a nonput channel establishes a synchronization only; no data is communicated.

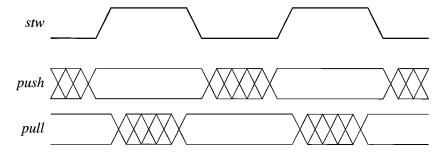

The second type of handshake channels are those with data encoded in the request. These channels connect an active sender and a passive receiver. So, the sender takes the initiative for a communication action. One might say that the sender *pushes* the data through the channel, therefore these channels are referred to as  $push^1$  channels. From a data-flow point of view push channels are *data driven*.

On a *pull*<sup>1</sup> handshake channel data is encoded in the acknowledge. Such a channel connects a passive sender and an active receiver. The sender issues data after receiving a request from the receiver, so one could say that the receiver *pulls* the data through the channel. From a data-flow point of view pull channels are *demand driven*.

The fourth type of handshake channels are *biput* channels, on which data is encoded in both the request and the acknowledge. One handshake then establishes the exchange of values between the two partners. The active partner now initiates the handshake by sending data to the passive partner. The passive partner then responds by sending data back. The handshake partners alternatingly act as sender and receiver.

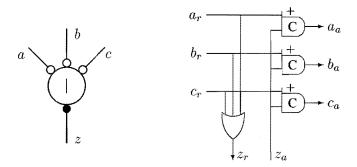

The four types of handshake channels are depicted in Fig. 2.3. On data channels, arrows indicate the direction(s) of data-flow. In the context of Tangram only nonput, push, and pull channels are applied. Biput channels do not recur in the rest of the thesis. For push and pull handshake channels, the data that can be communicated on such a channel is called the *type* of the channel.

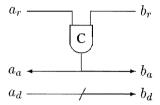

For a handshake channel a we use  $a_r$  to denote the request of a, and  $a_a$  for its acknowledge. If a is a push channel, the communication of a value x (encoded in the request), is denoted by  $a_r(x)$ . Similarly, the communication of a value x on pull channel a is denoted by  $a_a(x)$ .

Now that we have introduced symbols to denote events on handshake channels, we can use *traces* to record sequences of events that can be observed on handshake channels. The allowed sequences of events can then be specified using *commands*. Traces and commands are introduced by example, rather than via a separate formal section. For Trace Theory as used throughout this thesis the reader is referred to Van de Snepscheut [78], Hoare [44], Kaldewaij [47], Ebergen [29], or Verhoeff [83].

The handshake protocol prescribes that a handshake is initiated with a request and ended by an acknowledge. The allowed sequence of events on a nonput handshake channel a can thus be described by command  $*(a_r; a_a)$ . In this command

<sup>&</sup>lt;sup>1</sup>The names push and pull were coined by Joep Kessels. Previously, these type of channels were referred to as straight and anti, respectively. Push and pull are also used as strategies in flow-shop control. A drawback of the push-oriented strategy then is the accumulation of unsold products. Other familiar terms, especially in the market place, are Technology Push and Market Pull.

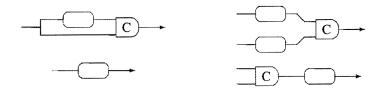

Figure 2.3: Symbols for the four types of handshake channels

the semicolon indicates that an acknowledge is allowed only after the request has occurred, and the star denotes repetition.

Throughout the thesis we use explicit typing of push and pull channels, especially in specifications, for which we use commands. All commands in which data plays a role are of the form  $|[D \mid C]|$ , where D (for declaration) introduces variables of some appropriate type, and C is a command in which these variables occur. For a push channel a of type T the behavior is prescribed by  $|[x:T|*(a_r(x);a_a)]|$ . This command describes the alternating of requests in which data of type T is encoded and acknowledges. Similarly, pull channel b of the same type is specified by command  $|[x:T|*(b_r;b_a(x))]|$ .

#### 2.2.2 Handshake components

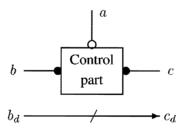

Handshake components are components that use handshake channels to communicate with their environment. The interface of a handshake component to a handshake channel is called a *handshake port*. These ports are either active or passive, depending on whether the component plays the active or the passive role on that channel.

If data is encoded on a handshake channel, then the handshake ports are input or output ports, depending on whether the channel is push or pull, and whether the port is active or passive. For a handshake port connecting to handshake channel a, we use the following conventions to denote the type of the port.

| notation      | port activity | channel type |

|---------------|---------------|--------------|

| $a^{\circ}$   | passive       | nonput       |

| $a^{ullet}$   | active        | nonput       |

| $a^{\circ}?T$ | passive       | push, $T$    |

| $a^{ullet}!T$ | active        | push, $T$    |

| $a^{\circ}!T$ | passive       | pull, $T$    |

| $a^{ullet}?T$ | active        | pull, $T$    |

We use commands to specify the behavior (that is, the allowed sequences of events at the external interface) of handshake components. One restriction that all components satisfy is that the handshake protocol on all handshake channels involved is obeyed. This can always be readily verified from the command specifications that are given.

In the commands, input and output events can be distinguished. For passive ports, the request events are inputs and the acknowledge events are outputs. On active ports this is the other way around, which means that requests are outputs and acknowledges are input.

The *sequencer* is used to implement sequential composition of Tangram. It is a handshake component with one passive nonput port and two active nonput ports. The specification and the symbol for a sequencer with ports a, b, and c are shown below.

$$SEQ(a^{\circ}, b^{\bullet}, c^{\bullet}) = \\ *(a_r; b_r; b_a; c_r; c_a; a_a)$$

$$b \longrightarrow \bullet \bullet \bullet \bullet \bullet \bullet$$

When this sequencer is activated along channel a it first performs a handshake along b, then a handshake along c, and then signals successful termination by completing the handshake along a. In the symbol for the sequencers we label the handshake channel that is first activated with a '\*.'

From the command one can derive the behavior on the individual channels. If we focus on channel b, for instance, the behavior is characterized by  $*(b_r;b_a)$ . The sequencer thus satisfies the handshake protocol on channel b. This can be checked for all handshake channels that the sequencer connects to. Other handshake components can be verified in a similar way.

The *parallel* component implements Tangram's parallel composition. Its handshake interface is the same as that of the sequencer, that is, it has three nonput ports, one passive and two active. When activated along its passive port, it initiates handshakes on its active ports, then waits till both handshakes have completed, and signals this by sending an acknowledge on its passive channel. Its specification us-

ing a command and the symbol for the component are shown below. Notice that in commands, sequential composition (denoted by ';') has higher priority than parallel composition (denoted by '||').

$$\begin{aligned} \operatorname{PAR}(a^{\circ}, b^{\bullet}, c^{\bullet}) &= \\ *(a_{r}; (b_{r}; b_{a} \parallel c_{r}; c_{a}); a_{a}) \end{aligned} \qquad b \qquad b \qquad c$$

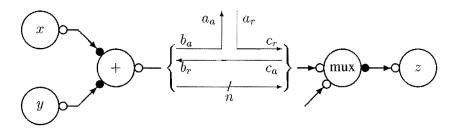

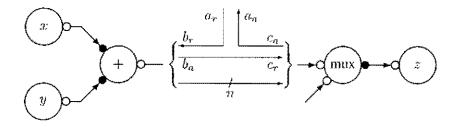

The sequencer and the parallel are both examples of control components. Of course, there are also handshake components that deal with data. An example of a data component is the *adder*, whose specification and symbol are given next. This component operates in a demand-driven fashion. It awaits a request on its result channel before it collects the operands, computes the result, and outputs this on the result channel.

$$\begin{array}{l} \text{ADD}(a^{\circ}!T_{a},b^{\bullet}?T_{b},c^{\bullet}?T_{c}) = \\ |[x:T_{b},y:T_{c}\\ |*(a_{r};(b_{r};b_{a}(x) \parallel c_{r};c_{a}(y));a_{a}(x+y)) \\ |] \end{array}$$

The adder is an example of a parameterized component. The inputs and output each have their own type, in which the type of the output is determined by that of the inputs. This is discussed in more detail in Chapter 5.

One may observe that the specification of the adder is very similar to that of the parallel component. The communication behavior is essentially the same; the only difference is that the adder encodes data in the acknowledges.

The *transferrer* is a handshake component with three different kinds of handshake ports, a passive nonput port, an active pull port and an active push port. When activated along its passive channel it actively fetches data from its pull port and subsequently forwards this data along its push port. The transferrer thus transfers data upon request and —in handshake circuits— is an interface between control and data components, or, phrased differently, between the control and the datapath. The symbol and command specification are given below.

$$\operatorname{TRF}(a^{\circ}, b^{\bullet}?T, c^{\bullet}!T) = \\ |[x:T|*(a_r; b_r; b_a(x); c_r(x); c_a; a_a)]| \qquad b \longrightarrow c$$

The behavior of the transferrer, as specified in the command, is similar to that of the sequencer. The sequences of events are basically the same; in addition the transferrer has data encoded in the acknowledge of its input channel and in the request of its output channel.

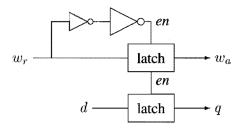

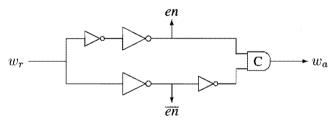

The components addressed so far illustrate how operations on data can be performed, how data can be transferred, and how this can be controlled. An essential component that is missing is one to *store* data. The *handshake variable* implements exactly this. Its specification and symbol are given next.

$$\begin{aligned} \operatorname{VAR}(a^{\circ}?T,b^{\circ}!T) &= \\ |[x:T \mid *(a_{r}(x);a_{a} \mid b_{r};b_{a}(x))]| \end{aligned} \qquad a \longrightarrow b$$

A variable can be engaged in a *write* handshake (on channel *a*) or a *read* handshake, and the environment must guarantee that these two will always be mutually exclusive. During a write handshake the content of the variable is updated; during a read handshake it is inspected.

All components, except the variable, are *receptive* [8]. This means that on all channels, if the handshake protocol on that channel allows for an input to occur, the component is willing to accept that input. (For a passive port, the request is the input, for an active port the acknowledge is the input.) More precisely, if a trace that is specified by the command can be extended with an input as far as the handshake protocol is concerned, then this extension is also specified by the command. The parallel component, for example, initially and after completion of a full cycle, can accept a request on its passive channel. On both active channels, an acknowledge is anticipated directly after the corresponding request is sent.

The specification of the variable as given in the command above implies that the variable is *not* receptive. During a read handshake, for instance, the component is not receptive for a write request. Tangram's compilation scheme guarantees mutual exclusion between read and write accesses [16, 8]. Therefore the non-receptive variable always suffices in the Tangram context.

#### 2.2.3 Handshake circuits

Handshake channels can be used to connect handshake components into networks of handshake components that are called *handshake circuits*. The connections that are made by a handshake channel are point-to-point, and of course the type of the channel should match that of the handshake ports of the components. Furthermore, a channel must connect an active port to a passive port. A push handshake channel, for instance, can only connect an active output port to a passive input port.

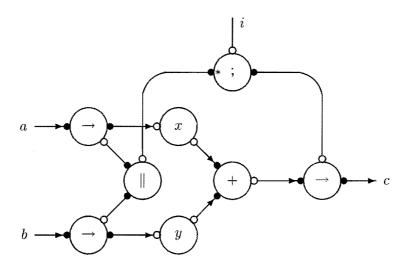

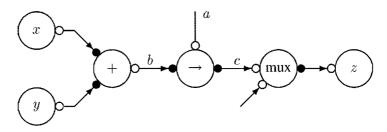

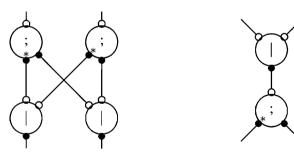

Figure 2.4: An example handshake circuit, built from the components introduced earlier in this chapter.

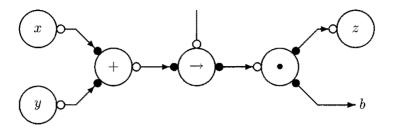

With the handshake components that have been introduced in the previous section, we can for instance build the handshake circuit of Fig. 2.4. When activated via channel i, this circuit first activates the left branch of the sequencer, which in turn activates two transferrers in parallel. These transferrers operate independently. The top transferrer collects a value from channel a and stores this in variable x, the other transferrer stores the value collected from b in y. After both transferrers have completed, the acknowledges are combined in the parallel and sent to the sequencer. This component then sends a request via its right-hand channel, which activates the transferrer that connects to output channel c. The transferrer collects its output from the adder, which in turn collects its input (the operands) from x and y.

The above description of an operational cycle is rather verbose. We can also specify the behavior of such a handshake circuit as if it where a handshake component. This requires abstraction from internal detail and structure. The formal side of this (parallel composition and hiding) falls outside the scope of this thesis. For this the reader is referred to Van Berkel [8]. A command that specifies the handshake circuit of Fig. 2.4 is the following.

```

\begin{array}{l} |[\,x:T_a,y:T_b\,\\ |\,*\,(i_r\,;(a_r\,;a_a(x)\,\parallel b_r\,;b_a(y))\,;c_r(x+y)\,;c_a\,;i_a)\,\\ ]| \end{array}

```

Designing handshake circuits by abutting handshake components is not a very

productive way of designing these circuits. It makes more sense to design these circuits in an algorithmic language and to use a compiler to generate the handshake circuits.

The programming language should abstract from the handshaking details, such as the exact interleaving of the request and acknowledge events and the assignment of active and passive roles to handshake ports. Shorthands should, for instance, be offered for 'collect a value from channel a and store this in variable x.' This naturally leads to a CSP-like language, in which the operation of the handshake circuit can be described as  $(a?x \mid b?y)$ ; c!(x+y).

# 2.3 Tangram

Tangram is a VLSI programming language that abstracts from handshake circuits and enables the design of a circuit as a programming activity. Programs written in Tangram can automatically be compiled to handshake circuits.

A key strength of Tangram compilation is the transparency of the compilation scheme. The basic idea is that for each Tangram construct there is a handshake component that implements the same function. This transparency is illustrated in the first two examples in this section. Two additional examples illustrate the expressive power of Tangram.

A complete definition of Tangram, together with a description of the performance characteristics (in terms of area, time, and energy) of the corresponding silicon as they can be derived from a Tangram program, can be found in the Tangram manual [71].

#### 2.3.1 Adder revisited

In the previous section we only gave the command that corresponds to the handshake circuit shown in Fig. 2.4. To obtain a complete (compilable) Tangram program we have to add typing information and declarations. A Tangram program that actually compiles to the handshake circuit of Fig. 2.4 is shown below, in which we have chosen to input eight-bit operands and to output a nine-bit result.

```

int8 = type [0..255]

int9 = type [0..511]

(a?int8 & b?int8 & c!int9).

begin

x,y : var int8

(a?x || b?y) ; c!(x+y)

end

```

2.3. Tangram 19

#### 2.3.2 Wagging buffer

The wagging FIFO is included as an example to illustrate the sharing of control and datapaths in handshake circuits compiled from Tangram. The Tangram program for a wagging FIFO is shown below.

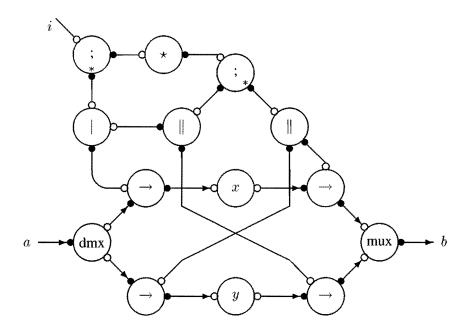

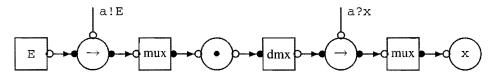

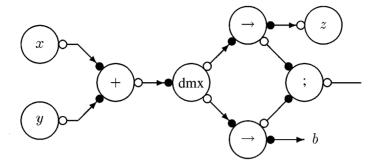

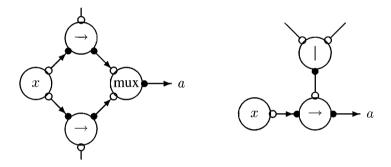

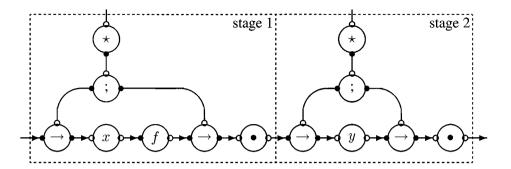

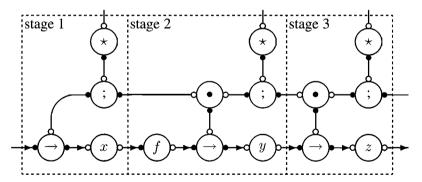

In this program we encounter three inputs from channel a, two of the form a?x and one a?y. Incoming messages on channel a are alternatingly sent to variables x and y. The program also contains two outputs to channel b, one from variable x and one from y. Compilation of this Tangram program to a handshake circuit yields the circuit of Fig. 2.5.

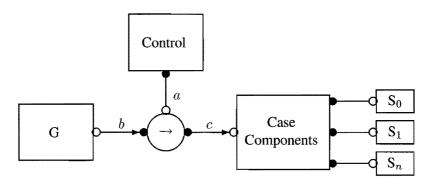

This handshake circuit contains three so-called *mixer* handshake components. A mixer component has three handshake ports, two passive (say a and b) and one active (say c). The command that specifies the behavior of the mixer is

```

*(a_r; c_r; c_a; a_a \mid b_r; c_r; c_a; b_a).

```

This command specifies the *nonput mixer*. In addition, data may be encoded in the request or the acknowledge, in which case the component is a *multiplexer* or a *demultiplexer*, respectively.

Mixer components are used for sharing. The component labeled 'dmx' in the handshake circuit in Fig. 2.5 is a demultiplexer. It splits the input stream on channel a to variables x and y. On the output side a multiplexer (labeled 'mux') merges data from x and y onto channel b.

The datapath of the handshake circuit is connected to the control path via four transferrers, which each control one of the data transfers of the Tangram program. Since there are two occurrences of a?x, the corresponding transferrer has to be shared via a control mixer (labeled '|').

Channel i represents the initiation channel, which is used to activate the hand-shake circuit. The component labeled ' $\star$ ' is a *repeater* and implements the forever do od construct of the program. The handshake circuit clearly represents the syntactic structure of the Tangram program. Each handshake component, apart from

Figure 2.5: Handshake circuit for wagging FIFO

the mixers, can directly be related to the program. The mixers are required to implement sharing of hardware, which in the Tangram program shows as multiple occurrences of a construct.

#### 2.3.3 Galois Field arithmetic

Tangram offers only two data types: booleans and integers from a specified range. Any other data type that is required can be programmed based on these two basic types, using tuple construction and selection, and type casting and fitting.

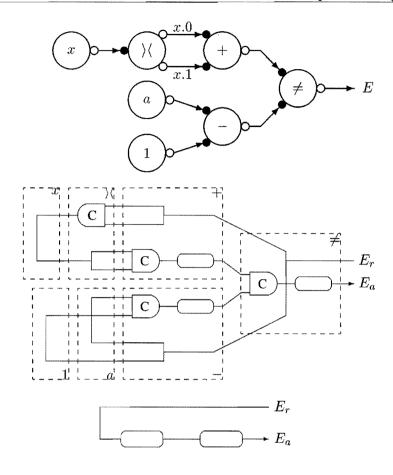

The construction of a user-defined type is exemplified in the Tangram program given in Fig. 2.6, which introduces the Galois Field data type for  $GF(2^8)$ . This data type is used, for instance, in the Compact Disc program as discussed in [49] and the DCC decoder program from [11], which is used as basis for the demonstrator discussed in Chapter 7.

A Galois Field is characterized by a root of an irreducible polynomial. For the field described here this is polynomial  $1+x^2+x^3+x^4+x^8$ , and the root is denoted by  $\alpha$ . Galois Field symbols are represented in the Tangram program as tuples of eight booleans. This type is called gfsym. Tupling in Tangram is denoted by << >>, in which items are separated by commas. The program introduces two con-

2.3. Tangram 21

```

/* Definition of GF data type plus operations */

= type <<bool, bool, bool, bool, bool, bool, bool, bool>>

/* some useful GF constants */

& gff

= const false

& gft

= const true

= const <<gff,gff,gff,gff,gff,gff,gff>>

& gfzero

& gfalpha = const <<gft,gff,gft,gft,gff,gff,gff>>

/* GF functions */

& gfiszero = func (s: gfsym): bool.

-(((s.0+s.1)+(s.2+s.3))+((s.4+s.5)+(s.6+s.7)))

= func (s: gfsym): gfsym.

<<s.7,s.0,s.1,s.2,s.3,s.4,s.5,s.6>>

= func (s,t: gfsym): gfsym.

<<s.0#t.0,s.1#t.1,s.2#t.2,s.3#t.3,

s.4#t.4,s.5#t.5,s.6#t.6,s.7#t.7>>

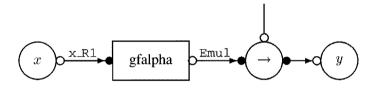

& mulalpha = func (s: gfsym): gfsym.

<<s.7, s.0, s.1#s.7, s.2#s.7, s.3#s.7, s.4, s.5, s.6>>

& divalpha = func (s: gfsym): gfsym.

<<s.1,s.0#s.2,s.0#s.3,s.0#s.4,s.5,s.6,s.7,s.0>>

```

Figure 2.6: Definition of Galois Field data type plus operations in Tangram.

stants of type gfsym: gfzero, which is the all-zero word, and gfalpha, which is the representation of  $\alpha$  in gfsym.

Function gfiszero implements the check whether a gfsym equals gfzero. This function illustrates the use of tuple selection (denoted by a dot and the appropriate index, starting from 0) and the use of boolean operators for logical or (+) and negation (-). Rotation to the left over one position is defined in gflrot. The other three functions implement addition (bit-wise exclusive or, denoted by #), multiplication by  $\alpha$ , and division by  $\alpha$ . In addition to the functions shown here the CD and DCC programs require functions for inversion of a gfsym and multiplication of two gfsyms.

The Galois Field example illustrates that the definition of data types in a Tangram program does not differ from the definition of an abstract data type in any other programming language.

## 2.3.4 Carry-select adder

Tangram offers four basic operations for integers: addition (+), subtraction (-), negation (-), and comparison (=, <>, <, >, <=, >=). For these basic operations the VLSI programmer should be aware of their performance characteristics. The transparency of the compilation from Tangram to VLSI circuits can then be used to reason about the performance of (the silicon corresponding to) a Tangram program. The

```

/* type USi : UnSigned, i bits */

/* type Bi : Boolean, i bits */

& BB9

= type <<bool, B9>>

/* < 2<sup>8</sup> */

& US8

= type [0..255]

= type [0..511]

/* < 2<sup>9</sup> */

& US9

/* < 2<sup>16</sup> */

= type [0..65535]

& US16

& US8US8 = type <<US8,US8>>

& US8B = type <<US8,bool>>

& US16B = type <<US16,bool>>

().

begin

x,y,z : var US16

& cout : var bool

/* carry-select implementation of z := x+y */

<<z,cout>> :=

begin

sumlow = val (x cast US8US8.0 + y cast US8US8.0) cast US8B

& sumhigh0 = val (x cast US8US8.1 + y cast US8US8.1) cast B9

& sumhigh1 = val ( <<1,x cast US8US8.1>> cast US9

+ <<1,y cast US8US8.1>> cast US9

) cast BB9.1

= val sumlow.1

& sgn

& sqnb

= val -sumlow.1

& sumhigh = val << sumhigh1.0 * sgn + sumhigh0.0 * sgnb

, sumhigh1.1 * sgn + sumhigh0.1 * sgnb

, sumhigh1.2 * sgn + sumhigh0.2 * sgnb

, sumhigh1.3 * sgn + sumhigh0.3 * sgnb

, sumhigh1.4 * sgn + sumhigh0.4 * sgnb

, sumhigh1.5 * sgn + sumhigh0.5 * sgnb

, sumhigh1.6 * sgn + sumhigh0.6 * sgnb

, sumhigh1.7 * sgn + sumhigh0.7 * sgnb

, sumhigh1.8 * sgn + sumhigh0.8 * sgnb

>>

<<sumlow.0,sumhigh >> cast US16B

end

end

```

Figure 2.7: Tangram program using carry-select addition.

adder that is offered, for instance, is a simple ripple-carry adder (this is the simplest implementation of addition of two numbers). Should the programmer require a different (faster) adder, then this can be programmed in Tangram rather straightforwardly. The implementation of z:=x+y with a carry-select adder, for instance, can be programmed in Tangram as shown in Fig. 2.7.

The carry-select Tangram program illustrates the use of a powerful language construct, namely type casting. This allows one to cast an expression to another type of the same size, in which the size is the number of bits used in the (unique) bit-vector representation. This requires that the VLSI programmer knows that integers in Tangram are represented as bit vectors, with the low-order bit representing the least-significant bit. This ordering of bits within a symbol is similar to the Big Endian ordering of bytes within a word [24].

With this information in mind the program can easily be understood. The program is based on splitting the 16-bit addition in two parts of 8 bits each. The low-order bits are added using the standard ripple-carry adder and the result is available as sumlow. For the high-order bits two values are computed, one based on a 'zero' carry-in (sumhigh0), the other based on a 'one' carry-in (sumhigh0). Based on the carry-out of the low-order addition (sumlow.1) the appropriate high-order addition is selected.

Another integer operation that is not directly supported in Tangram is multiplication. Tangram does allow, however, for the definition of a wide range of multipliers with various performance characteristics. An extensive treatment of Tangram programs for multiplication is given by Haans in [38].

Other examples of VLSI-programming in Tangram, with emphasis on programming for low power, can be found in reports by Van Berkel and Rem [17] and Kessels [48]. The examples given in this section illustrate the expressive power of Tangram. Common programs, such as those for integer multiplication and Galois Field arithmetic, could be put in a library of Tangram definitions, from which a VLSI programmer can then directly include a solution with the required performance characteristics.

# 2.4 Tangram handshake circuits

This thesis addresses the implementation of so-called *Tangram handshake circuits*. These are handshake circuits as they can be generated from a Tangram program. The restriction to Tangram handshake circuits allows us to exploit properties of the compilation scheme from Tangram to handshake circuits in the implementation. We try to keep the implementation of handshake circuits as general as possible, but at some points the restriction to Tangram allows for efficient implementations that

would not be suited in a more general context. The properties of the compilation scheme that are exploited are the following.

First of all, the Tangram compiler assures mutual exclusion between read and write accesses to handshake variables. For the Tangram programs this implies that so-called auto-assignments (like x:=x+1) are decomposed into two assignments (like x:=x+1; x:=x+1). This master-slave decomposition is implemented in the Tangram compiler. Removing this restriction from the Tangram compiler would require the introduction of master-slave variables, which in addition to normal read and write cycles allow for *read-modify-write* cycles.

Secondly, Tangram does not allow input communications in expressions. This implies that if an input has to be processed, it first has to be stored in a variable. This restriction could easily be removed from the language, since at the handshake circuit level inputs could easily be allowed in expressions. In the implementation of Tangram handshake circuits, however, we can take advantage of the restriction.

A third property of handshake circuits compiled from Tangram is that mixers of any type (nonput, multiplexer, demultiplexer) can be implemented non-receptively. The compiler assures mutual exclusion of mixer requests on different passive ports. The implementation of receptive mixers would require arbiter circuits to resolve possible conflicts.

# Chapter 3

# Single-Rail Data Encoding

For a cost-effective implementation of handshake circuits the efficient implementation of data storage, manipulation, and communication is of utmost importance. Single-rail implementations are promising since they only require one wire per bit for the data encoding, in contrast with double rail, for which two wires per bit are needed.

In this chapter single-rail data communication is introduced. The combination of single-rail with handshaking is then illustrated on two- and four-phase handshake protocols. In subsequent chapters, four-phase single-rail implementations of handshake components and handshake circuits are introduced. It turns out that the combination of single-rail and four-phase handshake protocols allows for a wide range of choices.

# 3.1 Single rail

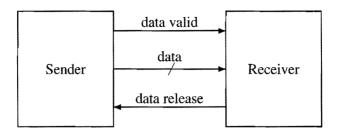

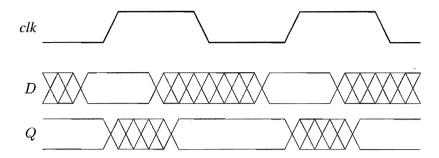

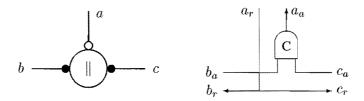

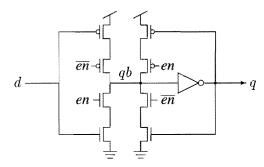

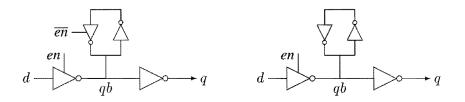

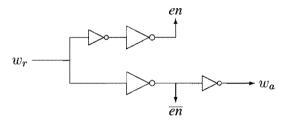

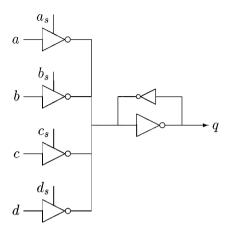

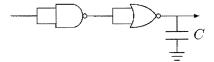

In a single-rail data interface, schematically depicted in Fig. 3.1, one wire per bit is used to represent data. In addition to this there must be a means for the sender to inform the receiver that the data is stable and valid (called the *data-valid* signal), and a means for the receiver to indicate that this data is no longer required (the *data-release* signal).

The exchange of information between sender and receiver is organized as follows. The sender first puts valid data on the wires and then informs the receiver about this by sending a data valid signal. The receiver can then process this data and inform the sender when the data is no longer required by sending a data release signal.

The relation between sender and receiver in the single-rail protocol is essentially symmetrical. The sender may take an indefinite amount of time to prepare

Figure 3.1: Single-rail data interface between sender and receiver.

new data. After the issue of the data-valid signal, however, it has to keep the data stable. The receiver can then prolong the data-valid period as long as required to fully assimilate the new data. Only after the issue of the data release signal by the receiver, the sender is relieved from its task to keep the data stable, and new data may be prepared.

The single-rail data communication scheme was already applied in the Macromodules project [23]. The scheme was then called *data validation* and the control signals were called *initiation* (valid) and *completion* (release) [74].

The term *single rail* was first used by Seitz to contrast it with double-rail encoding [72]. Sutherland, in his Turing Award lecture [75], popularized the use of the single-rail data encoding scheme under the name *bundled data*. This name emphasizes the importance of the so-called *bundling constraint*, that is, the obligation for the data-valid signal to arrive later than the data itself.

Both Seitz and Sutherland refer to the data valid wire as the request, and to the data release wire as the acknowledge. Per data transfer this is indeed a natural way to denote these signals, since a data communication then is initiated by a request and ended by an acknowledge. In the next section the relation between the handshake protocol and the single-rail scheme is discussed. Request and acknowledge are then signals that are distinguished in the handshake protocol and the interpretation as data valid and data release depends on the direction of the data flow.

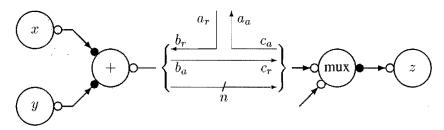

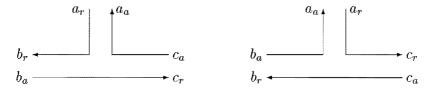

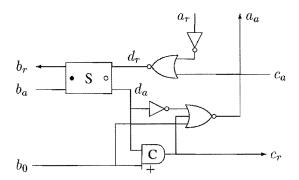

## 3.2 Handshake channels

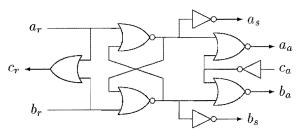

Tangram handshake circuits feature two kinds of handshake channels with data, namely, push and pull channels, cf. Chapter 2. These two types of handshake channels are shown in Fig. 3.2, together with the relation between the request and acknowledge of the handshake channel and the data valid and data release of the single-rail scheme. On push channels (Fig. 3.2, top) the data-valid signal is encoded in the request, and the data-release signal in the acknowledge. On pull channels (Fig. 3.2,

Figure 3.2: Single-rail push (top) and pull (bottom) handshake channels.

bottom) this is the other way around.

A communication on a push channel is initiated by the sender and starts with the issue of a data-valid signal. After assimilation of the new data the receiver responds by sending an acknowledge, which is interpreted as the data-release signal. On the handshake channel the data is thus valid *during* the handshake.

Communication on a pull handshake channel is initiated by the receiving party, which thereby requests new data. The first-ever request may be interpreted as a redundant data-release signal. The handshake is completed when the receiver acknowledges the request by issuing a data-valid signal. This implies that data is valid between handshakes and that the sender thus prepares new data during the handshake.

In literature on handshaking, communication data via pull channels is generally not addressed. Apparently, communicating data with handshakes in a demand-driven way is not very common. Martin, however, mentions that 'contrary to common belief, it is simpler to implement input commands with active ports than with passive ports' [57, Sec. 20.4].

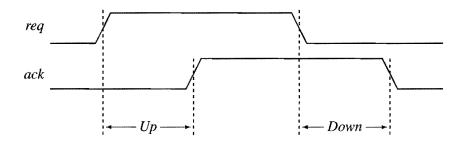

## 3.3 Two phase

In the two-phase handshake protocol a request and an acknowledge wire are used to implement the handshaking between the active and the passive partner. If we assume both wires to be low initially, then the sequence of events that can be observed on such a channel is depicted in Fig. 3.3. Up and down handshakes can be distinguished, where after an up handshake both wires are high and after each down handshake both wires are low. Of course other initializations are also possible, and

Figure 3.3: Two-phase handshaking

in particular it is not essential for the wires to start in the same state.

In the two-phase handshake protocol all transitions are functional, that is, each request followed by an acknowledge constitutes a complete handshake. Two-phase handshaking is also known as transition, two-stroke<sup>1</sup>, two-cycle<sup>1</sup>, and non-return-to-zero (NRZ)<sup>2</sup> signaling.

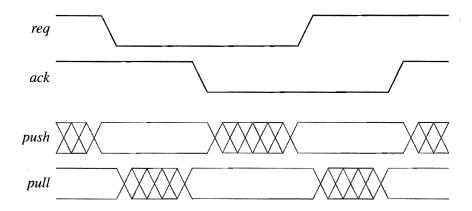

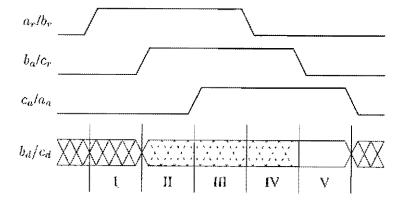

Since all transitions are functional the direction of dataflow directly determines the assignment of data valid and release to the handshake signals. On push channels every request event signals the beginning, and every acknowledge the end of a data-valid period. On pull channels this is the other way around. The timing diagrams for push and pull two-phase single-rail channels are depicted in Fig. 3.4, which shows a down handshake followed by an up handshake.

The data on the push channel is valid when the request and the acknowledge are in a different state (which can be detected with an exclusive-OR), whereas on the pull channel the data is valid when the request and the acknowledge are in the same state (which can be detected by an exclusive-NOR).

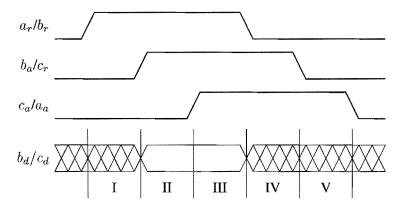

## 3.4 Four phase

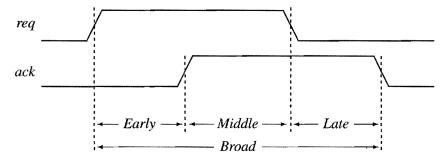

A complete cycle in a four-phase handshake involves four (sequential) events, hence the name. One four-phase handshake consists of an up handshake followed by a down handshake, as shown in Fig. 3.5. (Of course other initial states could be chosen.) The down handshake is also referred to as the *return-to-zero* phase. Since four events

<sup>&</sup>lt;sup>1</sup>Originally referring to combustion engines in which a complete fuel cycle in a cylinder requires only two piston strokes.

<sup>&</sup>lt;sup>2</sup>Adopted from digital magnetic recording techniques. NRZ refers to a mode of recording in which the direction of writing current is reversed for every change in the binary sequence. One direction of surface magnetization then corresponds to a '1,' the other to a '0.' In NRZI encoding, the current is reversed only when a '1' is recorded. See Hoagland [42] for details.

Figure 3.4: Data-valid schemes for two-phase single-rail channels. (The data is valid during the non-hashed periods.)

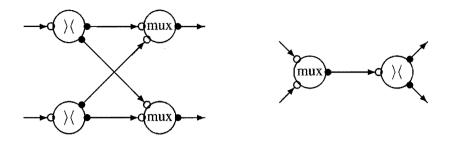

are used to designate a handshake, half of these events are essentially functionally redundant. Three interpretations can be distinguished that differ as to which events are labeled redundant. These interpretations are depicted in Fig. 3.5. In the *early* interpretation the return-to-zero phase is assumed to be functionally redundant. One might interpret this as a functional phase followed by a cooling down. The *late* view, in contrast, assumes the up handshake to be functionally redundant, such that a complete handshake can be interpreted as a warming up followed by a functional phase.

Figure 3.5: Four-phase handshaking

Four-phase handshake protocols are also known as return-to-zero (RTZ)<sup>3</sup>, four-

<sup>&</sup>lt;sup>3</sup>In digital magnetic recording, return-to-zero (RZ) recording refers to a mode in which a '1' is recorded by saturating a spot in one direction, and a '0' by saturating a spot in the reverse direction. Interestingly, a feature of this RZ encoding is that it allows for self-clocking, because an output signal is obtained during each bit interval. As Hoagland [42] put it: 'The RZ recording method (...) does

stroke<sup>4</sup>, four-cycle<sup>4</sup>, and level signaling.

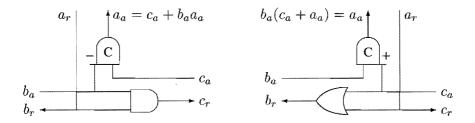

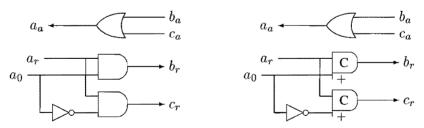

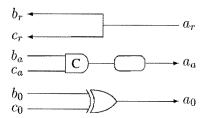

#### 3.4.1 Push channels

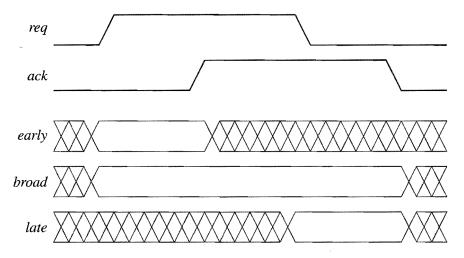

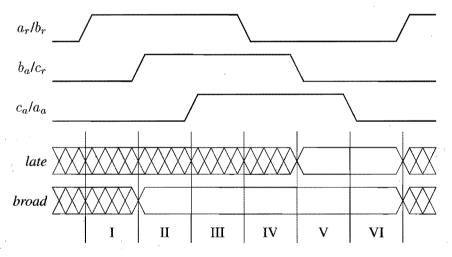

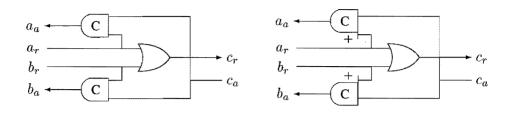

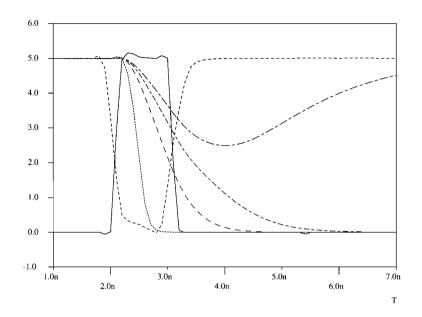

On a push channel the data-valid signal is encoded in the request and the data-release signal in the acknowledge. In the two-phase protocol this left us with only one choice, but in a four-phase protocol three conventions can be distinguished. If  $req\uparrow$  is the data-valid signal, we can choose  $ack\uparrow$  or  $ack\downarrow$  as the data-release signal. In case  $req\downarrow$  is the data-valid signal we can only choose  $ack\downarrow$  as the data-release signal. These three conventions will be called early, broad, and late, respectively, and are depicted in the form of a timing diagram in Fig. 3.6.

The term 'broad' has been borrowed from Brunvand [18]. Early and late were coined by Craig Farnsworth. Early is referred to as narrow by Brunvand.

Figure 3.6: Data-valid schemes for *push* single-rail channels.

Although the data-valid periods are defined by the events that signal the beginning and the ending of such a period, the data-valid period can in all three cases be characterized by a Boolean function, by looking at the state of the control wires only. On a broad push channel, for instance, the data is valid when req + ack. On an early channel the data-valid period is defined by req \* ack, on a late channel by  $\overline{req} * ack$ .

possess a capability for almost asynchronous operation.'

<sup>&</sup>lt;sup>4</sup>Referring to combustion engins in which a complete fuel cycle in a cylinder requires four separate piston strokes, namely intake, compression, power, and exhaust.

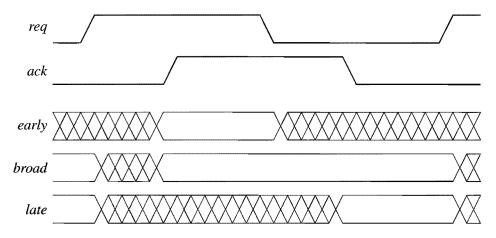

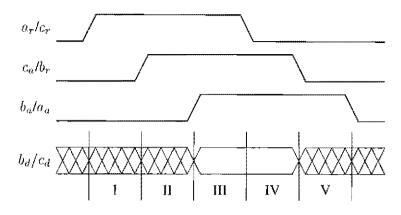

#### 3.4.2 Pull channels

On a pull channel the data-valid signal is encoded in the acknowledge and the data-release signal in the request. In the two-phase protocol this leads to the observation that the data thus is valid between two handshakes, not during a handshake as on a push channel. In the four-phase protocol we can again identify three different data-valid schemes. The data-valid period can begin at  $ack\uparrow$  and then end at  $req\downarrow$  of the same handshake, or at  $req\uparrow$  of the next handshake. The other choice is that the period begins at  $ack\downarrow$  and ends at  $req\uparrow$  of the next handshake. These three conventions are also called early, broad, and late, respectively, and are depicted as a timing diagram in Fig. 3.7.

The early convention for pull channels can also be called the *middle* data-valid scheme, since the data is valid during the middle phase of the handshake protocol, namely from  $ack \uparrow till \ req \downarrow$ . Like on push channels, the data-valid period can be defined by looking at the *state* of the request-acknowledge signals. The broad data-valid period, for instance is characterized by  $ack + \overline{req}$

Figure 3.7: Data-valid schemes for pull single-rail channels.

#### 3.4.3 Double rail

Although the double-rail data-encoding scheme can be applied in both two- and four-phase handshake protocols, it is generally only used in combination with four-phase handshaking. The up-going phase of the handshake is then used to assert the data, and in the return-to-zero phase all wires are reset. The data on a double-rail channel is completely defined if all pairs of wires are in a complementary state. If

all wires are low the channel is inactive, and the two wires of a pair must never be high at the same time.

If the data on a double-rail channel is completely defined, one might say that the data is valid, in the sense that the status of the one-wires encodes the message, and the zero-wires hold the complement (bitwise inverse) of the message. Both on push and on pull channels this interpretation of when the data is valid corresponds with the early data-valid scheme as defined for single-rail channels.

## 3.5 Single track