# UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

Single thread performance in the multi-core era

### Permalink

https://escholarship.org/uc/item/5620h0n6

### Author Porter, Leonard Emerson

# Publication Date 2011

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

### Single Thread Performance in the Multi-core Era

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

### Leonard Emerson Porter

Committee in charge:

Professor Dean Tullsen, Chair Professor Chung-Kuan Cheng Professor Sadik C. Esener Professor Steven Swanson Professor Michael B. Taylor

2011

Copyright Leonard Emerson Porter, 2011 All rights reserved. The dissertation of Leonard Emerson Porter is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2011

DEDICATION

To Lori.

### EPIGRAPH

The liberally educated person is one who is able to resist the easy and preferred answers, not because he is obstinate but because he knows others worthy of consideration. —Allan Bloom

# TABLE OF CONTENTS

| Signature Pa  | age .   |                                                                              | iii             |

|---------------|---------|------------------------------------------------------------------------------|-----------------|

| Dedication .  |         |                                                                              | iv              |

| Epigraph .    |         |                                                                              | v               |

| Table of Cor  | ntents  |                                                                              | vi              |

| List of Figur | res .   |                                                                              | ix              |

| List of Table | es      |                                                                              | х               |

| Acknowledge   | ement   | s                                                                            | xi              |

| Vita and Pu   | ıblicat | ions                                                                         | xvi             |

| Abstract of   | the Di  | issertation                                                                  | xviii           |

| Chapter 1     |         | oduction                                                                     | 1               |

|               | 1.1     | Leveraging Parallel Memory Hardware to<br>Support Speculative Multithreading | 2               |

|               | 1.2     | Improving SpMT Performance by Reducing Thread Mi-<br>gration Cost            | 5               |

|               | 1.3     | Branch Prediction Accuracy with Fewer Resources                              | 5               |

|               | 1.4     | Thread Scheduling on Multi-core Processors                                   | 6               |

|               | 1.5     | Contributions                                                                | 8               |

| Chapter 2     | Map     | oping Out a Path from Hardware Transactional Memory                          |                 |

|               | to S    | peculative Multithreading                                                    | 11              |

|               | 2.1     | Related Work                                                                 | 13              |

|               |         | 2.1.1 Speculative Multithreading Background                                  | 14              |

|               |         | 2.1.2 Speculative Multithreading                                             | 16              |

|               |         | 2.1.3 Transactional Memory                                                   | 17              |

|               | 2.2     | SpMT Execution Model                                                         | 19              |

|               |         | 2.2.1 Speculative Thread Selection                                           | 20              |

|               |         | 2.2.2 Handling Register Dependences                                          | 22              |

|               | 2.3     | Methodology                                                                  | 23              |

|               | 2.4     | Leveraging TM for SpMT                                                       | 24              |

|               |         | 2.4.1 Baseline Transactional Memory Design                                   | 25<br>26        |

|               | <u></u> | 2.4.2 Baseline TM SpMT Performance                                           | 26<br>26        |

|               | 2.5     | Accelerating SpMT2.5.1Ordered Transactions                                   | $\frac{26}{27}$ |

|               |         |                                                                              | <i>4</i>        |

|           | 2.5.2 Data Forwarding for Ordered Transactions $\dots$ 28                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 2.5.3 Effectiveness of Line Granularity TM for SpMT 29                                                                                                       |

|           | 2.5.4 Eliminating False Sharing                                                                                                                              |

|           | 2.5.5 Word Granularity Results                                                                                                                               |

|           | 2.5.6 Byte Granularity Results                                                                                                                               |

|           | 2.5.7 Word Granularity for Unordered Transactions . 32                                                                                                       |

|           | $2.5.8  \text{Write Update}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                |

|           | 2.5.9 Summary of HTM Designs                                                                                                                                 |

|           | 2.6 Generality of Results                                                                                                                                    |

|           | 2.7 Chapter Summary $\dots \dots \dots$                      |

| Chapter 3 | Improving Speculative Multithreading Memory Behavior 44                                                                                                      |

|           | $3.1  \text{Methodology} \dots \dots$                  |

|           | 3.2 Motivation $\ldots \ldots 45$                                                      |

|           | 3.3 Related Work $\ldots \ldots 48$                                                           |

|           | 3.3.1 Reducing Migration Costs                                                                                                                               |

|           | 3.3.2 Cache Performance for SpMT                                                                                                                             |

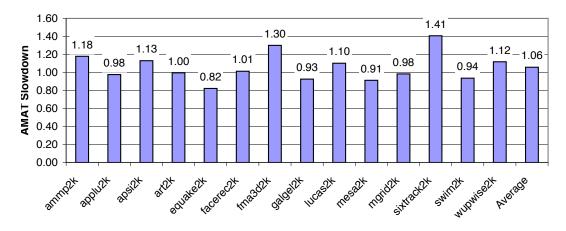

|           | 3.4 Background - Hardware Support for WSM                                                                                                                    |

|           | 3.4.1 WSM Hardware $\ldots \ldots 50$                                                         |

|           | 3.4.2 Memory Logger Policies                                                                                                                                 |

|           | 3.5 WSM for Speculative Multithreading                                                                                                                       |

|           | $3.5.1$ WSM Policies $\ldots \ldots 53$                                                       |

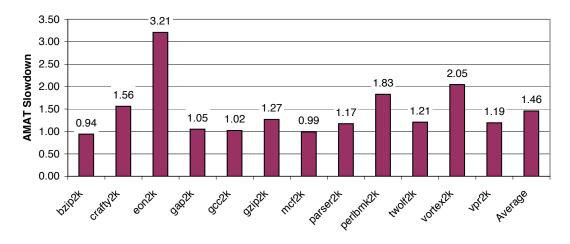

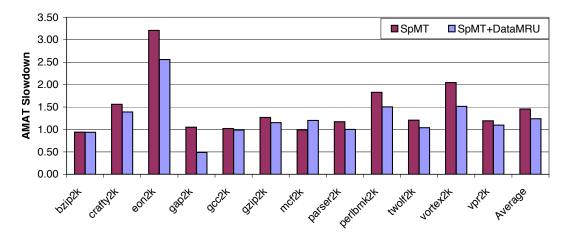

|           | 3.5.2 WSM Impact on AMAT $\ldots \ldots \ldots \ldots \ldots 54$                                                                                             |

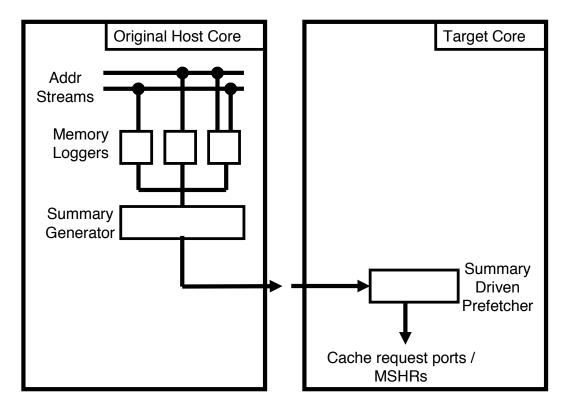

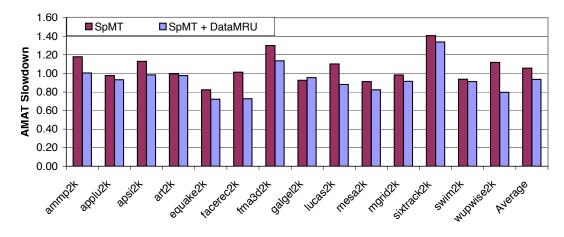

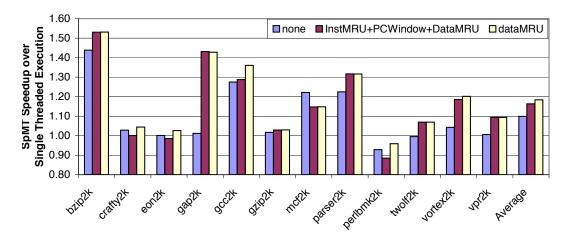

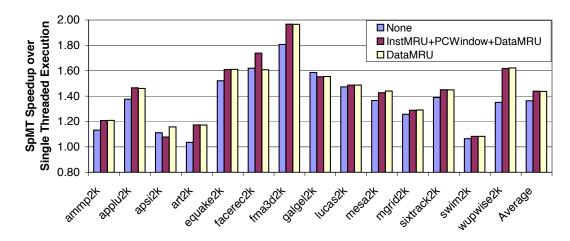

|           | 3.5.3 WSM Impact on SpMT Speedup                                                                                                                             |

|           | 3.5.4 Generality of WSM Results                                                                                                                              |

|           | 3.6 Chapter Summary $\ldots \ldots 58$                                                        |

| Chapter 4 | Creating Artificial Global History to Improve Branch Predic-                                                                                                 |

|           | tion Accuracy $\ldots \ldots \ldots$         |

|           | 4.1 Motivation $\ldots \ldots \ldots$        |

|           | $4.1.1  \text{Source Code Example} \dots \dots$        |

|           | 4.2 Background and Related Work                                                                                                                              |

|           | 4.3 Resetting the GHR $\ldots \ldots \ldots$ |

|           | 4.3.1 Hardware RLBC Identification                                                                                                                           |

|           | 4.3.2 Static Analysis of RLBC Points                                                                                                                         |

|           | $4.4  \text{Methodology} \dots \dots$                  |

|           | 4.4.1 Branch Predictors                                                                                                                                      |

|           | 4.4.2 History Tuning $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 74$                                                                            |

|           | 4.4.3 Benchmark Selection                                                                                                                                    |

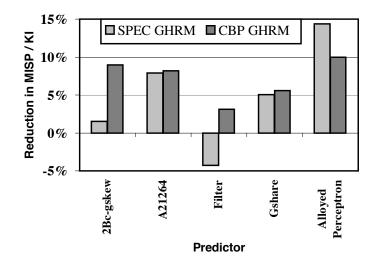

|           | 4.5 Results $\ldots \ldots 74$                             |

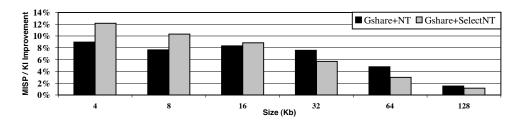

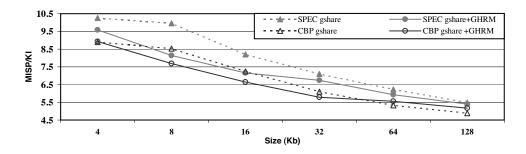

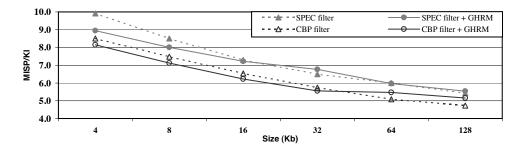

|           | $4.5.1  \text{Predictor Size}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              |

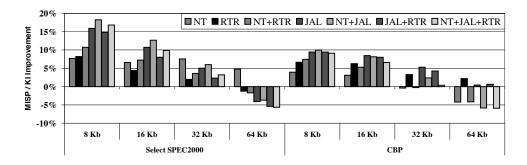

|           | 4.5.2 Heuristic Configuration                                                                                                                                |

|           | $4.5.3  \text{Other Predictors}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                            |

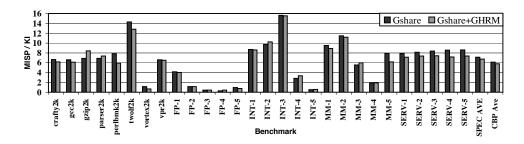

|              | 4.5.4 Non-Select Benchmarks                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 4.5.5 Result Summary 81                                                                                                                                |

|              | 4.6 Chapter Summary                                                                                                                                    |

| Chapter 5    | Exploiting Hetereogeneity for Improved Throughput, Energy,                                                                                             |

|              | and Fairness                                                                                                                                           |

|              | 5.1 Related Work                                                                                                                                       |

|              | 5.2 Methodology $\ldots \ldots \ldots$ |

|              | 5.3 Motivation $\dots \dots \dots$                     |

|              | 5.4 Exploiting Heterogeneity                                                                                                                           |

|              | 5.5 Policies for Coschedule Prediction                                                                                                                 |

|              | 5.5.1 Scheduling Policies                                                                                                                              |

|              | 5.5.2 Profiling Requirements                                                                                                                           |

|              | 5.6 Evaluation                                                                                                                                         |

|              | 5.6.1 Nehalem                                                                                                                                          |

|              | 5.6.2 Nehalem Case Study                                                                                                                               |

|              | 5.6.3 Westmere $\dots \dots \dots$                     |

|              | 5.7 Chapter Summary                                                                                                                                    |

| Chapter 6    | Thesis Summary                                                                                                                                         |

| Bibliography |                                                                                                                                                        |

### LIST OF FIGURES

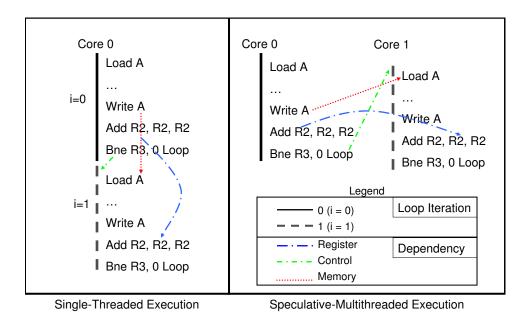

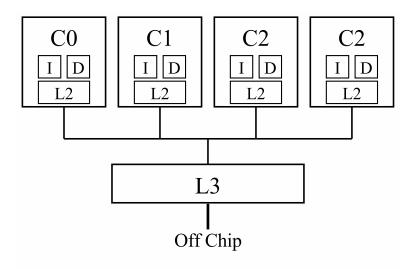

| Figure 1.1: | Speculative Multithreading Example                       | $\frac{3}{7}$ |

|-------------|----------------------------------------------------------|---------------|

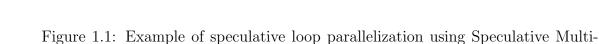

| Figure 1.2: | Multi-core Hardware                                      | 1             |

| Figure 2.1: | Speculative Multithreading Example Revisited             | 14            |

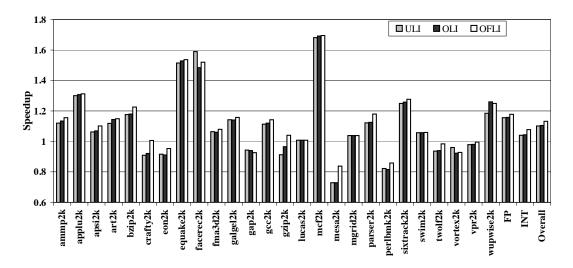

| Figure 2.2: | SpMT Speedup for line-granularity HTM designs            | 28            |

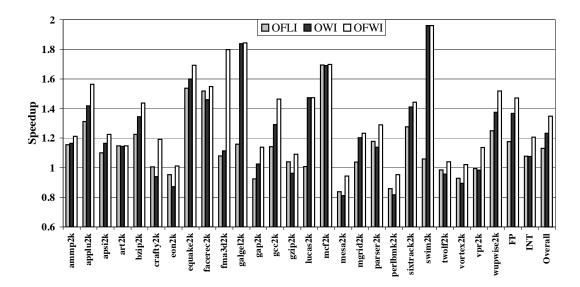

| Figure 2.3: | SpMT Speedup for word-granularity HTM designs            | 30            |

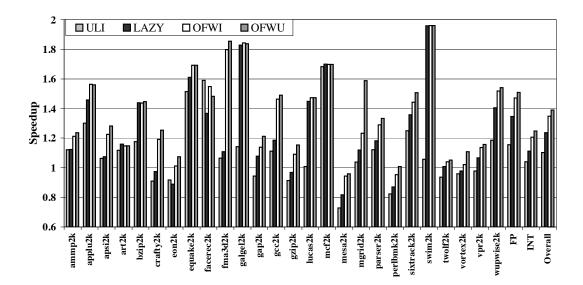

| Figure 2.4: | SpMT Speedup for word-update HTM designs                 | 37            |

| Figure 2.5: | Bookkeeping Bits per HTM Design                          | 39            |

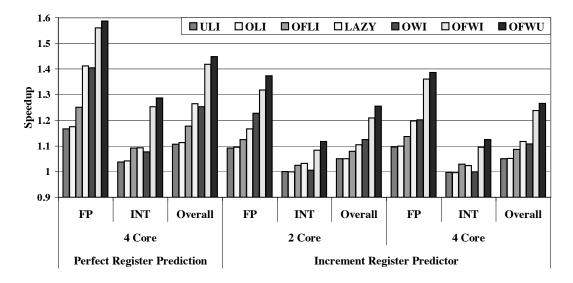

| Figure 2.6: | Average SpMT Speedup varying architectural features      | 41            |

| Figure 3.1: | SpMT Average Memory Access Time Slowdown SPECint         | 47            |

| Figure 3.2: | SpMT Average Memory Access Time Slowdown SPECfp          | 48            |

| Figure 3.3: | WSM Hardware                                             | 51            |

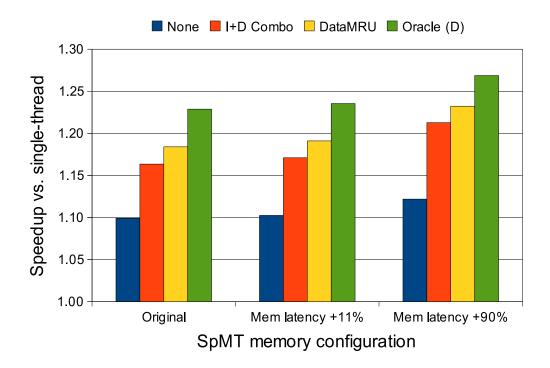

| Figure 3.4: | Impact of WSM policies on SpMT Speedup for SPECint       | 53            |

| Figure 3.5: | SPECint AMAT slowdown with and without WSM               | 54            |

| Figure 3.6: | SPECfp AMAT slowdown with and without WSM $\ldots$ .     | 55            |

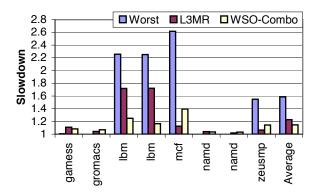

| Figure 3.7: | SPECint per benchmark SpMT Speedup with WSM              | 56            |

| Figure 3.8: | SPECfp per benchmark SpMT Speedup with WSM               | 56            |

| Figure 3.9: | SPECint SpMT Speedup with WSM                            | 57            |

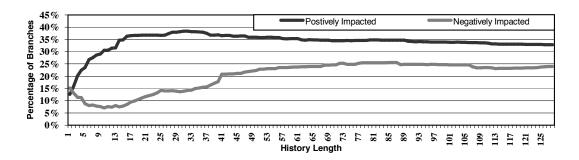

| Figure 4.1: | Impact of history on dynamic branches                    | 63            |

| Figure 4.2: | Branch history function example from gcc                 | 65            |

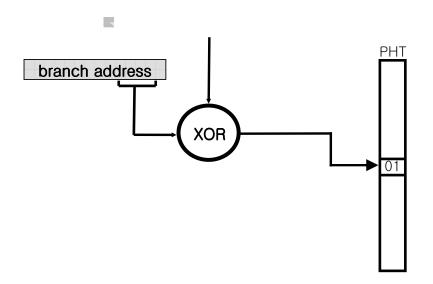

| Figure 4.3: | Diagram of the <i>gshare</i> branch predictor            | 66            |

| Figure 4.4: | Effectiveness of profiling for backward branch selection | 71            |

| Figure 4.5: | Mispredict rates for different size gshare predictors    | 75            |

| Figure 4.6: | Mispredict rates for different size filter predictors    | 75            |

| Figure 4.7: | Mispredict improvements per benchmark                    | 77            |

| Figure 4.8: | Misprediction reductions from different heuristics       | 78            |

| Figure 4.9: | Misprediction reduction for various predictors           | 79            |

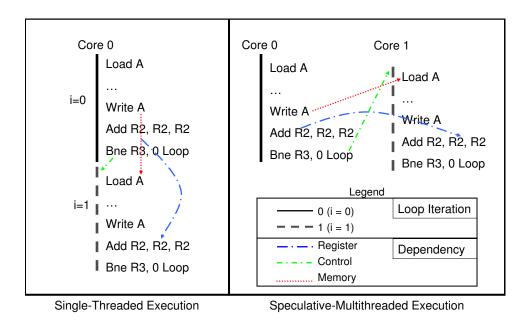

| Figure 5.1: | Nehalem Cache Layout                                     | 89            |

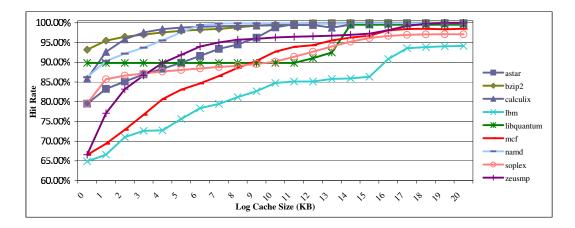

| Figure 5.2: | Cache Hit Rates per Benchmark                            | 91            |

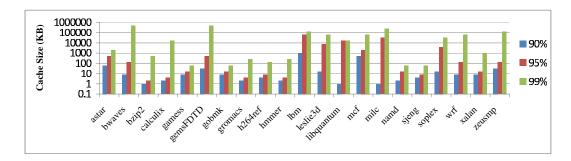

| Figure 5.3: | Working Set Sizes per Benchmark                          | 91            |

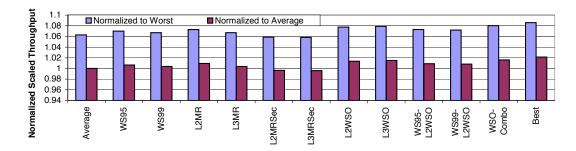

| Figure 5.4: | Nehalem Normalized Scaled Throughput                     | 98            |

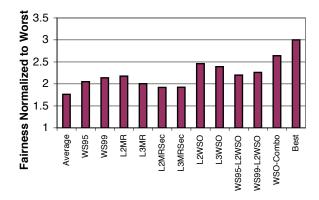

| Figure 5.5: | Nehalem Fairness Normalized to Worst                     | 99            |

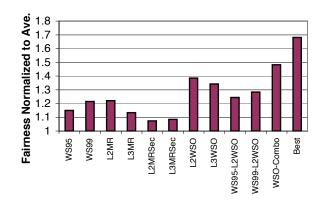

| Figure 5.6: | Nehalem Fairness Normalized to Average                   | 99            |

| Figure 5.7: | Nehalem Coschedule Example                               | 100           |

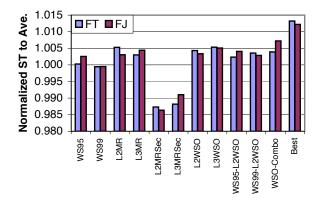

| Figure 5.8: | Westmere Normalized Scaled Throughput                    | 102           |

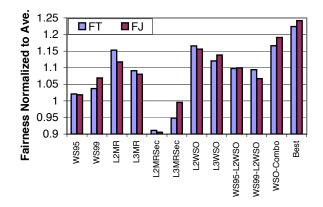

| Figure 5.9: | Westmere Normalized Fairness                             | 103           |

### LIST OF TABLES

| Table 2.1: | HTM Classifications                                                                                               | 19 |

|------------|-------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2: | SpMT Architectural Specifications                                                                                 | 23 |

| Table 2.3: | Squashes caused by coherence actions in three HTM designs $% \left( {{{\rm{A}}_{{\rm{B}}}}_{{\rm{A}}}} \right)$ . | 29 |

| Table 4.1: | Characteristics of 2Bc-gskew predictor                                                                            | 73 |

| Table 4.2: | Mispredict reductions varying predictor size                                                                      | 76 |

| Table 4.3: | Gshare and Filter heuristic configurations                                                                        | 76 |

| Table 4.4: | Best heuristics for each predictor                                                                                | 79 |

| Table 5.1: | Nehalem and Westmere Architectural Features                                                                       | 87 |

| Table 5.2: | Related field for selected SPEC2006 benchmarks                                                                    | 88 |

| Table 5.3: | Summary of the value of heterogeneity                                                                             | 93 |

| Table 5.4: | Metric Correlations with Scaled Throughput and Fairness                                                           | 94 |

#### ACKNOWLEDGEMENTS

Before beginning, I want to stress that any attempt to acknowledge all the amazing people — family, mentors, friends, and colleagues — who have contributed to my education is foolish. Words can scarcely describe how much I owe to each of you and I lament the serial nature of writing in its inherent ordering. Everyone who has been part of my life and my journey in graduate school has been valuable to me and I can only apologize as my attempt to convey this sentiment undoubtedly falls short.

I firstly want to thank my advisor, Dean Tullsen, for his unparalleled wisdom, integrity, and professionalism. Learning from him has been nothing shy of an honor and privilege. I cannot thank him enough for his unwavering faith in me that persisted even in the worst of times — through failed experiments and unprofitable research directions. I am going to miss our many conversations about research, teaching, family, and sports.

I have been immensely fortunate to have a number of mentors, in addition to Dean, throughout my graduate career: specifically Allan Snavely, Beth Simon, and John Glick. Although I have only recently begun working with Allan, I thank him for his guidance and mentoring in HPC research. Beth has provided me with amazing advice throughout the years. She, too, has shown amazing faith in me, involving me in major teaching projects well before I thought myself capable. I cannot thank her enough for teaching me that we can apply the same standards of research to education that we do to computer science. Lori and I will miss the dinners with you and Chris.

John was the original inspiration for me to attend graduate school in computer science as my advisor at USD. As a testament to his patient guidance, he was there for me when I was trying to pick a major, when I was trying to decide on graduate schools, when I was struggling in graduate school, and when I was trying to decide which faculty position to accept. He's been amazing at providing me with support and opportunities, including the priceless opportunity to teach at USD. I will miss our many lunches at Peabody's.

I also want to thank the additional members of the thesis committee —

Sadik Esener, Chung-Kuan Cheng, Steven Swanson, and Michael Taylor — for reviewing my thesis, overseeing my dissertation, and for spending many of their valuable hours assisting with the quality of this thesis.

My wife, to whom this thesis is dedicated, has provided me with unfathomable patience, love, and support throughout graduate school. I could not have done this without her. For all that she has endured, I fervently believe universities should grant spousal degrees (Ph.D. Survivors, or Ph.D.S. for short). I cannot thank her enough for her reassurances that we could finish, for her uncanny ability to make me laugh, and for all we have learned about life together.

As I become "Dr. Porter," I cannot help but think of this title as still reserved for my father. We lost him far too early and I so wish he could have been here to see me graduate. There is no doubt in my mind that I would never have been in this place in life without him. He taught me to have an insatiable thirst for knowledge and to approach life both rationally and philosophically. I owe him so much for teaching me the value of hard work, the importance of family, and the value of humility. I still marvel at (and aspire to) his unique ability to earn the respect of fellow physicists, soldiers, and small-town carpenters alike. At the end of my life, I will consider myself a success if I am half the scholar, citizen, and father he was.

My mother complemented my father well, and it's easy to see why they had such a happy marriage (and family) together. She is the very definition of nurturing. I have her to thank for life itself, and there has never been a moment in my life where I doubted her faith, love, or willingness to do anything she can to support me. I'd also like to thank her for her support, both emotionally and financially during graduate school.

My big sister is an amazing friend, mentor, and confidant. She has always been there for me and I cannot thank her enough for her support. I still have much to learn from her, whether it be lessons in good leadership, lessons in grammar, or the artistic value of 80s music. I thank her husband, Rick, as well, for his support through the years; he is both an amazing leader and person.

My in-laws, Lori's family, are nothing shy of unique. They are far too

numerous to name, but they have accepted me into the family and have treated me exceptionally well. I am so thankful that they are all part of my life. I want to especially thank Bonnie, Lonnie, and Bob for their role in Lori being the amazing person that she is.

My friends have had a uniquely defining influence on my life. Stemming from high school, I have had the distinct pleasure of such amazing friends as Ivan, Erin, Kyle, Corin, Beth, Mahru, Jen, Eri, Tim, Tom, Anne, Nick, Art, Steph, Kaleb, Aaron, and Shae. Many of them endured my friendship during high school and have surprisingly seemed willing to stick around as my friends even today. I think friendships as strong as ours, that last as long as ours, are rare, and I am truly privileged to have all of them in my life.

From my Navy days, I have to thank Rich, Alex, Barry, Jon, Brian, Martin, Bill, Frank, Stew, and, especially, Bob. Although many of us have lost touch, I will value our bonds as soldiers all of my life.

Lastly, I have to thank my friends at UCSD who have made graduate school not just bearable, but enjoyable. Jeff, thank you for teaching me what it means to be a good software engineer, for setting the example for perseverance through adversity, and for being so patient with me as I familiarized myself with the simulator and as I crawled my bike up Torrey Pines. Jack, you are a great friend. You have and will make tremendous contributions to our field during your career. I wish I had your insight and I will sorely miss our lunches. I thank Brian for commiserating with me and for teaching me so much about his field. I'm going to miss our afternoon coffee trips. I'd also like to thank Hung-wei, Bumyong, and the rest of Dean's lab for our many chats. Lastly, I thank Cynthia and Dan for all the great computer science education research we've worked on together.

To the group: Mikey, Laura, Evan, and Sandie, thank you for all our fun adventures together — Settlers weekends, lunches, marathons, 50ks, triathlons, wine tastings, Rock Band! I hope we will continue to stay in touch even as we all go our separate ways.

In summary, the journey of my life that led to this dissertation is best described as a story of relationships — relationships with family, friends, colleagues, and mentors. To all of you who have played a role in this journey, you have my eternal appreciation.

Chapter 2 contains material from "Mapping Out a Path from Hardware Transactional Memory to Speculative Multithreading", by Leo Porter, Bumyong Choi, and Dean M. Tullsen, which appears in *Proceedings of the Eighteenth International Conference on Parallel Architectures and Compilation Techniques (PACT)*. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

Chapter 3 contains material from "Fast Thread Migration via Cache Working Set Migration", by Jeffrey A. Brown, Leo Porter, and Dean M. Tullsen, which appears in *Proceedings of the Seventeenth International Symposium on High Performance Computer Architecture*. The dissertation author was the secondary investigator and author of this paper. The material in this chapter is copyright ©2011 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions@acm.org.

Chapter 4 contains material from "Creating Artificial Global History to Improve Branch Prediction Accuracy", by Leo Porter and Dean M. Tullsen, which appears in *Proceedings of the Twenty-Third International Conference on Supercomputing.* The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright O2009 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapter 5 contains material from "Exploiting Thread Heterogeneity for Improved Throughput, Energy, and Fairness on Multicore Processors", by Leo Porter, Allan Snavely, Anthony Gamst, and Dean M. Tullsen, which has been submitted for possible publication by the Association for Computing Machinery in *Proceedings of* the International Conference for High Performance Computing, Networking, Storage and Analysis (SC 11). The dissertation author was the primary investigator and author of this paper.

### VITA AND PUBLICATIONS

| 2000      | Bachelor of Arts, Computer Science<br>University of San Diego                 |

|-----------|-------------------------------------------------------------------------------|

| 2000-2004 | Officer<br>United States Navy                                                 |

| 2005-2010 | Teaching Assistant<br>University of California, San Diego                     |

| 2006-2011 | Research Assistant<br>University of California, San Diego                     |

| 2006      | Intern<br>Microsoft Research, Redmond                                         |

| 2007      | Master of Science, Computer Science<br>University of California, San Diego    |

| 2009      | Adjunct Professor, Computer Science Department<br>University of San Diego     |

| 2010      | Summer Graduate Teaching Fellow<br>University of California, San Diego        |

| 2011      | Master TA, CSE Department<br>University of California, San Diego              |

| 2011      | Doctor of Philosophy, Computer Science<br>University of California, San Diego |

### PUBLICATIONS

Leo Porter, Cynthia Bailey Lee, Beth Simon, Daniel Zingaro, "Peer Instruction: Do Students Really Learn from Peer Discussion in Computing?", *In Seventh International Computing Education Research Workshop (ICER)*, August, 2011.

Leo Porter, Cynthia Bailey Lee, Beth Simon, Quintin Cutts, Daniel Zingaro, "Experience Report: A Multi-classroom Report on the Value of Peer Instruction", *Proceedings of the Sixteenth Annual Conference on Innovation and Technology in Computer Science Education (ITiCSE)*, June 2011.

Jeffrey A. Brown, Leo Porter, Dean M. Tullsen, "Fast Thread Migration via Cache Working Set Prediction", *Proceedings of the Seventeenth International Symposium* on High Performance Computer Architecture (HPCA), February 2010. Beth Simon, Paivi Kinnunen, Leo Porter, Dov Zazkis, "Experience Report: CS1 for Majors with Media Computation", *Proceedings of the Fifteenth Annual Conference* on Innovation and Technology in Computer Science Education (ITiCSE), June 2010.

Leo Porter, Bumyong Choi, Dean M. Tullsen, "Mapping Out a Path from Hardware Transactional Memory to Speculative Multithreading", *Proceedings of the Eighteenth International Conference on Parallel Architectures and Compilation Techniques (PACT)*, September 2009.

Leo Porter, Dean M. Tullsen, "Creating Artificial Global History to Improve Branch Prediction Accuracy", *Proceedings of the Twenty-Third International Conference on Supercomputing (ICS)*, June 2009.

Bumyong Choi, Leo Porter, Dean M. Tullsen, "Accurate Branch Prediction for Short Threads", *Proceedings of the Thirteenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*, March 2008.

#### ABSTRACT OF THE DISSERTATION

#### Single Thread Performance in the Multi-core Era

by

Leonard Emerson Porter

Doctor of Philosophy in Computer Science

University of California, San Diego, 2011

Professor Dean Tullsen, Chair

The era of multi-core processors has begun. These multi-core processors represent a significant shift in processor design. This shift is a change in the design focus from reducing individual program (thread) latency to improving overall workload throughput. For over three decades, programs automatically ran faster on each new generation of processor because of improvements to processor performance. However, in this last decade, many of the techniques for improving processor performance reached their end. As a result, individual core performance has become stagnant, causing diminished performance gains for programs which are single-threaded.

This dissertation focuses on improving single-thread performance on parallel hardware. To that end, I first introduce modifications to a new form of parallel memory hardware, Transactional Memory, which can improve the viability of Speculative Multithreading — a technique for using idle cores to improve singlethreaded execution time. These modifications to Transactional Memory improve Speculative Multithreading effectiveness by a factor of three. I further improve the performance of Speculative Multithreading by addressing a primary source of performance loss — the loss of thread state due to frequent thread migrations between cores. By predicting the cache working-set at the point of migration, we can improve overall program performance by nine percent. Recognizing the demand for transistors to be dedicated to shared or parallel resources (more cores, better interconnect, larger shared caches), I next propose a method of improving branch prediction accuracy for smaller branch predictors. I demonstrate that there are regions of program execution where long histories hurt prediction accuracy. I provide effective heuristics for predicting these regions — in some cases enabling comparable accuracies from predictors of half the size. I then address the problem of contention among coscheduled threads for shared multi-core resources. To reduce resource contention, I propose a new technique for thread scheduling on multi-core processors with shared last level caches which improves the overall throughput, energy efficiency, and fairness of the coschedule.

# Chapter 1

# Introduction

The age of multi-core processors has begun. As such, modern processors can execute more threads simultaneously than ever before. Modern processors contain both many individual cores and simultaneous multithreaded cores, i.e., each core can execute multiple threads. For example, Intel's Nehalem processor has 4-8 cores, each of which is capable of executing two threads and Sun's Niagara 3 has 16 cores, each of which can execute 8 threads. With this, the nature of modern processor design now focuses on improving overall system throughput rather than improving a single thread's performance — the latter being the primary focus of processor design until around 2005.

In today's multi-core processors, many thread contexts lead to increased overall throughput when there are sufficient threads available for execution. However, these additional thread contexts do not aid the execution of any single thread. Single threads remain highly relevant as many applications exist as legacy binaries (often single-threaded), many applications are difficult and/or expensive to parallelize, and some applications simply lack fundamental parallelism. In addition, even for those applications which are parallelizable, Amdahl's Law teaches us that as we improve the non-serial portions of these highly parallelizable applications, the serial component will begin to dominate performance [HM08].

Opportunities exist to improve single-thread performance using parallel hardware. Parallel hardware provides a large number of thread contexts and many of these contexts will be idle due to a lack of available threads. We can leverage these idle resources to improve the performance of single-threaded programs.

Improving single-thread performance in the new multi-core landscape demands solutions to a number of central questions:

- 1. Can we use idle thread contexts to improve the performance (execution time) of a single thread?

- 2. Can we reallocate transistors from single-thread optimizations to parallel components (more cores, larger shared caches, better interconnect) without sacrificing single-threaded performance?

- 3. When threads share resources (common in multi-core designs), how can we schedule threads to avoid resource contention?

This dissertation focuses on answering, in part, these questions. It addresses methods for improving single thread performance using the abundant parallel hardware in multi-core processors. These methods include addressing the roadblocks and challenges related to speculatively parallelizing single threads, providing accurate branch predictions with less hardware, and scheduling threads together given limited shared hardware. Each of these points will be elaborated upon in the following sections.

# 1.1 Leveraging Parallel Memory Hardware to Support Speculative Multithreading

Speculative Multithreading (SpMT) is a promising new technique for improving single-thread performance by leveraging idle parallel hardware [SBV95, AD98, HHS<sup>+</sup>00, KT98, MGQS<sup>+</sup>08, MGT98, PO05, SR01, SM98, SAHL04]. SpMT aims at splitting a single thread into multiple threads which can be executed in parallel. By dividing the execution into threads that are executed in parallel, performance gains become possible.

Unlike traditional parallelism where dependencies between parallel threads are rare (if ever), speculative parallelism targets the domain where dependencies

threading. Dependencies across loop-iterations are shown by the arrows.

be uncommon.

are frequent. These frequent dependencies are often either manageable or predictable, and those dependencies which cannot be managed or predicted need to

Loops are a common target of SpMT and provide a useful example (see Figure 1.1). In single-threaded execution, each loop iteration is executed in serial and values are passed from one loop iteration to the next. There are three types of dependencies between loops: control dependencies (branches), memory dependencies (stores and loads), and register dependencies (register producing and register consuming instructions). In SpMT, loop iterations may be selected to be executed in parallel. Unlike serial execution where dependencies are commonly addressed via serial commit, SpMT requires dependencies be handled between threads. Control dependencies and register dependencies are highly predictable, but memory dependencies create considerable challenges.

Memory dependencies are commonly addressed in SpMT proposals by adding special-purpose memory hardware which is designed to detect dependencies and support recovery from misspeculation. This hardware is a significant barrier for widespread SpMT adoption due to its cost.

At the same time, Transactional Memory (TM) [HM93, AAK+05, BGH+08, CTTC06, HF03, HWC+04, MCC+05, MHW05, RHL05, ST95, YBM+07] has been recently proposed for multi-core processors to aid in parallel execution. TM provides two key features:

- 1. *TM provides an easier interface for parallel programming.* It replaces locks with easier to understand transaction semantics (begin transaction and end transaction).

- 2. *TM provides support for optimistic concurrency*. Unlike locks that serialize execution of critical sections by allowing only one thread to execute at a time to prevent a potential conflict between threads, TM allows all threads to execute a critical section and only aborts if a true conflict exists.

Transactional Memory has been proposed using either hardware (HTM), software (STM), or hybrids of both. In this work we focus on HTM implementations as STM is likely too slow for latency-sensitive speculative threads.

HTM has already appeared in one real processor [TC08] because of its benefits for parallel execution. We recognize that we can leverage this investment in parallel memory hardware to provide SpMT at a fraction of the cost of adding SpMT support to traditional memory designs. In Chapter 2 we evaluate the potential for HTM to provide SpMT and demonstrate that its current support for dependency handling offers limited SpMT performance. We present a number of key additions to HTM which improve the performance of SpMT. In doing so, we propose a new HTM design which is capable of high performance in both transactionally parallel programs [RRW08] and speculatively parallelized single threads [PCT09]. Using two cores, basic register prediction, and averaged over the SPEC CPU2000 benchmarks, SpMT using prior eager-detect HTM designs offers only a 5% improvement in performance, whereas our new HTM design offers a 26% improvement. Although our new HTM design from the previous section improved SpMT performance greatly, it continued to suffer performance losses from the migration of execution from one core to another. This is a common problem for any technique which aims to improve performance by migrating threads and is especially problematic for SpMT because of its frequency of thread migrations.

Modern processors learn about the behavior of threads as they execute and, as a result, are capable of executing long threads efficiently. However, when threads are short and/or migrate frequently, this disrupts the ability of the processor to learn about the threads. There are two key hardware components designed to learn thread behavior. The first is branch prediction hardware, which learns the behavior of branches. The second is caches, which learn the behavior of memory.

The first of these challenges, branch prediction, was addressed in our prior work. The second of these challenges, cache behavior, remains a critical problem. In Chapter 3 we propose a number of techniques for improving the memory performance of speculative threads. We demonstrate that a recent proposal, workingset-migration [BPT11], can be used to reduce the average memory delay in SpMT by 50% for select SPEC CPU2000 benchmarks. This reduction in SpMT memory delay translates to a 9% improvement in whole program performance.

# 1.3 Branch Prediction Accuracy with Fewer Resources

The shift in focus to parallel performance over single-thread performance causes architects to reevaluate transistor usage throughout the processor. In reevaluating the transistor usage, the primary question is how much utility does each transistor provide in terms of overall processor performance. For example, by reducing the number of transistors dedicated to non-critical components that provide marginal performance gains, you may be able to better use those saved transistors (and the power associated with them) to build another core, a better core inter-connect, or larger caches.

Deep pipelines place heavy stress on branch prediction as they force hardware to speculate on branch outcomes many cycles before branches are resolved. Misspeculation has the severe consequence of flushing an entire pipeline — in effect losing many cycles worth of work. As a result, branch prediction hardware became a major hardware component in single-core design as pipeline depth increased.

We now have to revisit this design choice from the past, aiming to scale back the hardware cost of branch prediction. The critical question then becomes, can we still provide high branch prediction accuracy, and hence high single-thread performance, using fewer resources. To this end, we examine the value of history for branch prediction accuracy in Chapter 4. Many modern branch predictors use global history to index prediction tables [YP93, CEP96, Kes99, LCM97, McF93, SFKS02, SM99, JL02, EM98, Sez05]. Although history is valuable for many branches (hence the development of history-based predictors), we demonstrate that there are periods during program execution where history breaks down. We propose a simple technique based on heuristics that improves the performance of existing branch predictors and, in some cases, enables the same branch prediction accuracy with half the hardware. This frees transistors (and their associated power) for potential reallocation elsewhere in the processor.

## 1.4 Thread Scheduling on Multi-core Processors

In the previous section, we discussed the challenge of achieving high single thread performance as resources are diverted from components which only benefit a single thread to components which benefit processor-wide performance. Many of these components which benefit processor-wide performance are shared. In this section, we discuss the complementary problem of how to use scheduling to ensure these shared resources are used effectively.

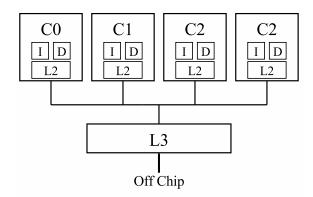

Modern multi-core processors have resources that are dedicated to one core (private) or are shared among multiple cores (shared). Figure 1.2 is an example of

Figure 1.2: Cache layout on a modern (Nehalem) processor.

the cache layout on a recent multi-core processor. In this example, the L1 (I and D) and L2 levels of cache are private to each core, whereas all cores share the L3 and off chip bandwidth.

Shared resources can be a significant source of contention between threads scheduled on different cores of the same processor. This contention can impact overall processor throughput, individual thread performance, overall fairness (do all contending threads suffer equally?), and overall energy efficiency. As such, deciding which threads should be scheduled together (coscheduled) becomes a critical decision for anyone concerned with the single-threaded performance within that coschedule.

In Chapter 5, we recognize that coscheduling threads with similar memory characteristics is almost always the wrong choice as they require the same shared resources and will therefore experience significant contention. We demonstrate that scheduling heterogeneous threads can alleviate this contention and provide superior performance. We then propose a metric which can be used to predict which heterogeneous coschedules offer high throughput (99% of best possible), fairness (48% better than average), and energy efficiency (99% of best possible). These results are consistent on both Nehalem [KDMK08] and Westmere [KBM<sup>+</sup>10]

processors under multiple scheduling assumptions. An additional advantage of our metric is that it can be determined through a single profiling pass and yet provides useful predictions for scheduling on multi-core processors with diverse processor characteristics.

## **1.5** Contributions

This dissertation provides the following contributions:

### Chapter 2

- We evaluate the potential for Hardware Transactional Memory to support Speculative Multithreading (SpMT) and demonstrate that Hardware Transactional Memory, as currently proposed, offers poor SpMT performance (5% whole program improvement using two cores).

- We propose and examine a number of modifications to Hardware Transactional Memory to determine which are critical for SpMT and which are not. Those we identify to be critical are both inexpensive and offer significantly improved SpMT performance (26% whole program improvement using two cores).

- The value to SpMT of these modifications is shown to be consistent across different numbers of cores, different core architectures, and different register predictor assumptions.

### Chapter 3

• SpMT introduces additional memory slowdowns due to frequent thread migrations and line invalidations. To address this problem, we evaluate a recent proposal for generic thread migration, Working Set Migration, in the context of SpMT. We examine a number of heuristics for Working Set Migration and, although many of these heuristics are shown to be ineffective for SpMT, we identify one that significantly improves SpMT memory performance. Adding this feature to our memory design from the previous chapter reduces average memory access time by 50% and improves whole program performance by 9%.

### Chapter 4

- The majority of branch predictors today use global history to inform their predictions. Although many branches are correlated with previous branches, we identify regions of execution where branch correlation is limited, causing history to become essentially noise. For many branch predictors, this noise interferes with both prediction and training, resulting in worse prediction accuracy.

- We propose simple and nearly free techniques for identifying these regions which, when combined with smaller branch predictors, can improve their accuracy. In some cases, a branch predictor modified to use our techniques can offer prediction accuracy comparable with traditional branch predictors of twice the size.

#### Chapter 5

- We demonstrate that the coscheduling of threads which are homogeneous is almost always the wrong choice on multi-core processors with shared cache resources. Coscheduling homogeneous threads can cause resource contention which results in poor overall processor throughput, poor energy efficiency, and poor fairness. Heterogeneous coscheduling can reduce such contention and improve all three of these performance metrics.

- For use in heterogeneous coscheduling decisions, we propose the Cache Hit Rate Vector (CHRV) to classify the memory behavior of a program. The CHRV has the advantage that it can be determined with a single profile pass and yet is still useful for scheduling decisions on multiple processor architectures.

- We propose and examine a number of metrics for use in coscheduling decisions. A novel metric which leverages the CHRV, WSO-Combo, provides

the best coscheduling decisions of the metrics examined. By using this metric to inform our scheduler, coschedules are selected which offer 99% of the best possible throughput, 99% of the best possible energy efficiency, and 48% better than average thread fairness.

In whole, these chapters address a number of the key challenges to single-threaded performance in the multi-core era.

# Chapter 2

# Mapping Out a Path from Hardware Transactional Memory to Speculative Multithreading

In the previous chapter, we offered Speculative Multithreading as a potential solution to the question: "Can we use idle thread contexts to improve the performance of a single thread?" In this chapter, we focus on the memory system required for Speculative Multithreading. Specifically, we examine the potential for leveraging Hardware Transactional Memory to provide the memory hardware required by Speculative Multithreading.

Speculative Multithreading (SpMT) is a promising technique for improving single thread performance by leveraging idle parallel resources. However, the cost of handling memory dependences is a significant barrier for wide-spread adoption. In this Chapter, we investigate the potential for using Transactional Memory (TM) for SpMT.

TM has been proposed as a powerful programming primitive for shared memory multiprocessors to replace traditional lock-based synchronization [HM93, AAK+05, BGH+08, CTTC06, HWC+04, MCC+05, MHW05, RHL05, YBM+07, HF03, HLMS03, ST95]. Prior research has examined software transactional memory [ST95, HF03, HLMS03] and hardware transactional memory [HM93, AAK+05, BGH+08, CTTC06, HWC+04, MCC+05, MHW05, RHL05, YBM+07]. TM has

gained significant interest in both academia and industry because of the potential to make programming the coming multi-core and many-core processors easier [HCW<sup>+</sup>04] and more effective [HM93]. These factors led SUN to propose inclusion of hardware support for transactional memory in their Rock processor [TC08]. We expect other implementations to follow.

Speculative Multithreading (SpMT) [SBV95, HHS<sup>+</sup>00, MGQS<sup>+</sup>08, PO05, SM98, KT98, SR01, MGT98, AD98, SAHL04] is another architectural alternative that becomes increasingly attractive as we enter the multi-core era more fully. It provides the hope of exploiting available parallel cores to increase the performance of a single thread of execution. Serial code will increasingly be a limiting factor both in terms of power and performance [HM08].

Given the imminent arrival of hardware support for TM, we would like to leverage that hardware to add support for true speculative multithreading, at a lower incremental cost than supporting speculative multithreading from scratch. The focus of this work is to map out a path from HTM to SpMT. What are the elements that we would need to add to a memory design that supported HTM in order to allow SpMT? How should they work in an HTM context? Which of those elements are crucial and which are not?

It has been stated and demonstrated that transactional memory provides support for speculative multithreading, or thread level speculation via its support for opportunistic concurrency [CTTC06, CCM<sup>+</sup>06, HWC<sup>+</sup>04, MCC<sup>+</sup>05, PCC07]. That is, if two iterations of a loop both access shared data within a transaction, but the accesses conflict in only a small number of cases, the iterations will execute in parallel when there is no conflict, and cause transactions to abort and execute in series when the conflict exists. Thus, the traditional domain of TM is code that is truly parallel (dynamically). It does not support the parallel execution of code where frequent and numerous dependences exist. It also requires significant compiler or programmer support to identify and properly exploit opportunities for thread-level speculation.

To perform this study, we create an architecture for speculative multithreading that executes unmodified single-threaded binaries, relies on prediction for register dependence handling, and relies on the memory subsystem to handle memory dependences. We use this SpMT framework in concert with a number of HTM designs. In addition to the designs previously proposed, we examine a number of intermediate steps along the path from HTM to full SpMT support and show the performance potential at each step. We ultimately define a unique architecture which efficiently supports both TM and dependency-rich SpMT.

Assuming this speculative multithreading approach, we evaluate HTMs which feature eager conflict detection (also assuming enough architectural support to be able to execute in this environment) using SPEC CPU2000 binaries and found that a limited speedup of 10% can be obtained on two cores. The primary weaknesses of traditional HTMs in a SpMT environment are their inability to differentiate more speculative threads from less speculative threads, false sharing, cold cache effects whenever a new thread is initiated on a core, the delayed notification of potential dependencies, and the inability to forward available values when loaded by a more speculative thread. By introducing improvements to HTM with eager conflict detection, we are able to achieve more than a 3x increase in the effectiveness of SpMT (resulting in a speedup of 36% on two cores).

The improvements considered along the path from TM to SpMT include word-granularity tracking of memory coherence, support for ordered transactions, forwarding of values to higher ordered transactions, and a write-update cache coherence protocol.

This chapter is organized as follows. Section 2.1 discusses related work. The assumed SpMT architecture is outlined in Section 2.2. The methodology is provided in Section 2.3. In Section 2.4, the baseline transactional memory is discussed. Improvements to hardware TM are detailed in Section 2.5 with associated performance results. Section 2.6 addresses the generality of these results.

# 2.1 Related Work

Our work relates to previous proposals for Speculative Multithreading and Transactional Memory. The work in each area is described in the following sections,

Figure 2.1: Example of speculative loop parallelization using Speculative Multithreading. Dependences across loop-iterations are shown by the arrows.

following a brief background on Speculative Multithreading.

### 2.1.1 Speculative Multithreading Background

Speculative Multithreading was first proposed by Sohi et al. [SBV95] as an architecture tailored for splitting sequential execution into speculatively parallel threads. Revisiting our example from the introduction, Figure 2.1 is an example of the speculative parallelization of a loop. In this example, the first iteration of the loop (i = 0) is executed non-speculatively on Core 0. A speculative thread is created to execute the second iteration of the loop (i = 1) on Core 1. From this example, we can see that there are a number of requirements for a Speculative Multithreading architecture. These requirements include:

- The identification of an instruction which will trigger the spawn and execution of the speculative thread. This instruction is commonly called the Spawn Point (SP) [MG02]. Which segments of execution are selected for speculative threads depends on the SpMT hardware. In this example, a loop iteration has been selected and the SP would be the first instruction in the loop. Another common target for speculative threads is a function call. For function calls, the non-speculative thread executes the function and the speculative thread begins execution after the function returns. Any two points can result in a speculative thread in the Mitosis architecture [MGQS<sup>+</sup>08].

- The identification of the point in execution to merge/validate the speculative thread. This is commonly referred to as the Control Quasi-Independent Point (CQIP) and is the first instruction of the speculative thread. For loop iterations, as in this example, the CQIP is the same as the SP and is the first instruction in the loop.

- Register Live-Ins need to be known to identify which register values must be passed from parent thread to child thread or predicted at spawn. The register live-in in our example is register R2 which is consumed by the "Add" instruction in the speculative thread and produced by the "Add" instruction in the non-speculative thread. There are a number of ways to manage register dependences which are discussed in the following section.

- Memory dependences need to be detected and managed. In our example, there is a dependence on address "A" because the parent thread produces the value (Write A) which is subsequently consumed (Load A) by the child thread. Various memory hardware designs (discussed in the following section) manage conflict detection and management differently. The primary issue is that if the speculative thread reads "A" and uses it before the correct value is produced by the non-speculative thread, corrective action is required. This action may require the squashing of the entire speculative thread, or just the flushing of a few instructions [SAHL04].

Each SpMT proposal in the literature manages each of these requirements differently. Given this basic background, we can discuss these proposals in more detail.

### 2.1.2 Speculative Multithreading

As mentioned in the previous section, Speculative Multithreading [SBV95, HHS<sup>+</sup>00, MGQS<sup>+</sup>08, PO05, SM98, KT98, SR01, MGT98, AD98, SAHL04] provides the ability to parallelize otherwise serial code. Previous studies in the speculative multithreading literature produce speculative threads either using a compiler or hand tuning [SBV95, HHS<sup>+</sup>00, MGQS<sup>+</sup>08, PO05, SM98], statically using binary instrumentation [KT98], or else the speculative threads are identified entirely in hardware [AD98, MGT98, SAHL04]. When most SpMT proposals encounter an inter-thread dependence conflict, the speculative thread is squashed; however, Dynamic Multithreading only squashes, then re-executes, those instructions affected by the dependence [AD98, SAHL04].

Register dependences can be identified statically which enables a number of potential solutions. Since register dependencies can be determined by the compiler, the values can be explicitly forwarded between threads so long as the speculative thread is stalled before the consumption of the value [SBV95]. The stalling of the thread to wait for a register value can be a performance bottleneck which motivated the use of register prediction [MG00]. Another solution to the register dependency problem comes from a recent SpMT proposal, the Mitosis architecture [MGQS<sup>+</sup>08]. Mitosis uses compiler support to produce a short thread, the precomputation slice, which executes before the start of the speculative thread. The precomputation slice computes register live-ins to avoid explicit forwarding or prediction at the cost of executing additional instructions.

Memory dependences pose a significant challenge for SpMT as they generally cannot be identified until runtime and thus require additional support. A number of memory designs for SpMT have been proposed, starting with the Address Resolution Buffer (ARB) [FS96, SBV95]. The ARB benefits from simple memory address disambiguation, but a single centralized data cache for multiple cores may represent a bottleneck. To address this issue, multiple memories which buffer speculative state in local data caches were proposed to provide improved performance [CMT00, HHS<sup>+</sup>00, VGSS01]. The Stanford Hydra CMP [HHS<sup>+</sup>00] is a hybrid which allows private L1 caches to contain speculative contents but maintains all speculative data in dedicated buffers adjacent to the L2. These buffers are maintained consistent with the L1 contents via a write-through L1 store policy. The Speculative Versioning Cache (SVC) [VGSS01] uses cache coherency modifications combined with per-line or per-word pointers to ensure speculative data is buffered, conflicts are detected, and ordering information remains.

Our work shares many of the same goals as memories designed uniquely for SpMT. However, none of these models support TM code, and, of course, do not leverage a potential transactional hardware base.

## 2.1.3 Transactional Memory

Optimistic Concurrency — the execution of multiple threads in parallel with the aim that conflicts are infrequent — is an aim of both SpMT and Transactional Memory. Hardware Transactional Memory (HTM) was proposed by Herlihy and Moss as a simpler means of synchronization capable of performing optimistic concurrency [HM93]. This hardware model has been adopted by more recent TM proposals including LTM [AAK+05], UTM [AAK+05], PTM [CNV+06], LogTM [MBM<sup>+</sup>06], and VTM [RHL05]. While these proposals vary significantly in their interaction with software transactional memory, ability to handle contextswitches and transactional overflow, and support for nested transactions, their conflict detection semantics are similar and can all be represented for this work by a single hardware model (the ULI model, described in Section 2.4.1). These designs use eager conflict detection; they detect conflicts at the time they occur. Other designs, discussed soon, use lazy conflict detection; they buffer conflict information and, as a result, detect conflicts after they occur. LogTM-SE [YBM+07] proposes eager conflict detection based on hashed signatures at block granularity. This reduces the storage requirements on caches to track read-set and write-set information. However, a conflict in LogTM-SE is the same as in our ULI model.

TokenTM [BGH<sup>+</sup>08] avoids modifying coherence protocols by using tokens to track conflicts. Again, the notion of a conflict in TokenTM is the same as our ULI model. Hybrid Transactional Memory [DFL<sup>+</sup>06], the likely model of hardware support for SUN's proposed Rock Processor [TC08], also has conflict detection semantics similar to our ULI model.

FlexTM [SDS08] separates conflict detection and conflict management. In some benchmarks, our LAZY design achieves stronger performance than our eager design. For these cases, switching between eager and lazy conflict management could be useful. However, the software overheads for FlexTM may hinder performance.

Dependence Aware TM (DATM) [RRW08] offers some of the features recommended in this work. However, there are key differences. DATM adheres to transactional semantics which offer weaker guarantees than those required by our SpMT architecture. Most notably, stale data read by a transaction can persist in a cache and be read by a non-transaction. In addition, DATM requires bus requests for most transactional requests even in the case of a cache hit whereas our recommended design (OFWI, discussed in Section 2.5.4) does so only in the event of conflicts on that line. Lastly, our recommended design (OFWI) allows previous transactions to overwrite words written by later transactions whereas DATM does not. The impact of this last limitation is discussed in Section 2.5. Most importantly, however, DATM and our conclusions are complementary. The features added by DATM are shown to aid transactional parallelism and the features added by our designs are shown to aid speculative parallelism. The overlap of many of these features emphasizes their importance.

Transactional Coherence and Consistency (TCC) has been proposed as an alternative to traditional per-memory operation coherence [HWC<sup>+</sup>04, MCC<sup>+</sup>05]. In TCC, all memory operations are grouped into transactions. The transactional data is buffered at each core during a transaction. When the transaction commits, all transactional data is broadcast on a shared bus ensuring an atomic commit. Other cores observing this broadcast update their cache values similar to a write-update coherence protocol. Conflict detection in TCC is performed when the

| HTM                   | Conflict  | Our Corresponding |

|-----------------------|-----------|-------------------|

| Proposal              | Detection | HTM Design        |

| LTM, UTM, PTM, LogTM, |           |                   |

| LogTM-SE, TokenTM,    | Eager     | ULI               |

| VTM, and Hybrid TM    |           |                   |

| TCC and Bulk          | Lazy      | LAZY              |

Table 2.1: Correspondence of previously proposed HTM designs to the designs proposed later in this chapter.

broadcast occurs (commonly referred to as "lazy" conflict detection). The conflict detection is performed at word granularity by broadcasting word addresses and the new data for that word address. Similar to TCC, Bulk [CTTC06] also performs lazy conflict detection at word granularity with write update but does so using hashed signatures rather than cache line bits to reduce the amount of data broadcast at commit time. These proposals are represented by our LAZY model (Section 2.5.8).

Our HTM designs represent a number of existing proposals. Again, many of these proposals differ in details largely orthogonal to their potential to support SpMT. A summary of the existing designs, their manner of conflict-detection, and our corresponding design appears in Table 2.1.

The ability of Transactional Memory to support Speculative Multithreading is mentioned in TCC [HWC<sup>+</sup>04, MCC<sup>+</sup>05] and Bulk [CTTC06]. Transaction sizes in the context of speculative parallelism are addressed in [CCM<sup>+</sup>06]. Recent work extends programming language loop constructs to provide support for speculative multithreading [PCC07]. Bulk also uses HTM for compiler-based SpMT [CTTC06]. However, none of these mechanisms provide full support for the parallel execution of dependent threads.

# 2.2 SpMT Execution Model

This section describes our SpMT execution model and the minimum architectural support needed by any of the memory designs to be able to execute in our SpMT architecture. The focus of the rest of this chapter is the design of the memory architecture itself; however, this section primarily details other aspects of the architecture necessary to fully support speculative multithreading, and what assumptions were made about that architectural support.

## 2.2.1 Speculative Thread Selection

Prior proposals have assumed varying degrees of compiler support [SBV95, AD98, HHS<sup>+</sup>00, KT98, MGQS<sup>+</sup>08, MGT98, PO05, SR01, SAHL04, SM98]. We fully believe that compiler support will maximize the potential performance of speculative multithreading. However, for this study we assume no compiler or software support to identify speculative threads. Assuming no support provides a general SpMT model that allows us to examine our different memory designs in a fashion unbiased by the compiler, as we are not able to structure the code (even unintentionally) to favor one model. Additionally, this approach significantly expands the domain of SpMT — enabling parallel execution of legacy uniprocessor code, allowing the use of a single binary for a family of architectures that support different levels of SpMT, etc.

Our strict insistence on no compiler support causes our results to be potentially pessimistic compared to a system that allows compiler involvement. Even simple compiler support on single-thread binaries that moves or removes problem memory operations could greatly increase available SpMT parallelism. The bottom line, though, is that achieving the highest possible SpMT speedups is not the goal of this research. Rather, we are trying to understand the support in the transactional memory subsystem necessary to achieve the full potential of SpMT. The absolute magnitude of the speedups achieved is less significant.

Following the terminology of [MG02], a speculative thread is characterized by two PC addresses: the point in execution where a new thread will be created, called the Spawning Point (SP), and the point in the program where the new thread will begin executing, called the control quasi-independent point (CQIP). The new thread ends when it reaches another thread's CQIP and validates that dependences between the two threads were handled correctly. Compared to transactional execution, the entire thread essentially becomes a single transaction, and either completes execution atomically or is squashed/aborted in its entirety. Speculative threads have been initiated at loop iterations, loop continuations, and function calls in the past [MG02]. The Mitosis architecture [MGQS<sup>+</sup>08] can construct a SP-CQIP pair from any two arbitrary points in the program. However, without compiler support, our options are more limited. We target loop iterations and function call continuations, as they can be easily identified at run time and have been shown to be good candidates [MG02]. Out-of-order spawns are possible when a less speculative thread encounters a spawnpoint.

When an executing thread fetches an instruction whose address is a spawn point, we determine if an idle core is available. If one is available, we transmit any program state needed by the new thread (e.g., register live-ins) and start the speculative thread on that core after a communication and fetch delay.

When the parent thread encounters the CQIP of its child it stops fetching and waits for the CQIP to be committed. When the CQIP is committed, the child thread is validated. Validation includes the checking of any register live-ins and ensuring that the speculative thread was not squashed due to a memory dependence conflict. Speculative threads validated by non-speculative threads become nonspeculative. Speculative threads wait to commit until they become non-speculative

A confidence counter is maintained to indicate the frequency at which a spawn point results in a committed or squashed speculative thread. Spawn points which frequently squash are ignored after reaching a number of consecutive failures but are still given a small chance of re-execution. We found that allowing nine consecutive failures and giving a five percent chance for retry of failed spawnpoints was successful at reducing interference from frequently squashing threads.

To maintain a desirable speculative thread length, threads greater than ten instructions and less than ten thousand instructions are targeted. This can be accomplished by recording the length of previously executed threads.

Threads may be squashed due to dependence issues (discussed below), a system call by the non-speculative thread, or when the non-speculative thread has transactional state overflow. A squash of any thread causes all more speculative threads to be squashed. Speculative threads may be paused (caused to stop execution until made non-speculative) if they encounter a system call or cause a transaction overflow.

A store miss request can be issued at execute, preemptively loading the cache line, or at commit. By requesting the line during execute, the request latency is partially hidden rather than delaying the store entirely to commit. All memory designs assume this realistic optimization. This introduces the possibility of squashes due to wrong-path write miss requests for all of our memory designs except those which handle conflict detection at thread commit[CTTC06, HWC<sup>+</sup>04, MCC<sup>+</sup>05].

Our simulator assumes a centralized structure for speculative thread coordination which we refer to as the Global Speculative Thread Supervisor (GSTS). Important thread information (thread ordering, CQIP of children, etc.) is distributed to each core to avoid unnecessary communication with the GSTS. In a general TM system, parallel transactions can typically commit in any order that does not produce conflicts. Because we must maintain sequential semantics, we must commit threads in execution order. Support for this already exists in some TM proposals [CTTC06, HWC<sup>+</sup>04, MCC<sup>+</sup>05]. An overall notion of thread ordering allows for committing of threads in order, a necessary feature for SpMT. This is different than having the memory coherence know and account for that order which is addressed in a later section. For example, if coherence were to be made aware of thread ordering, more speculative threads may be able to safely write to addresses read by less speculative threads. This is a useful distinction in thread ordering, both because the overall thread ordering is necessary and coherence-aware thread ordering is an optimization, and also because the former is easily supported in the GSTS, and the latter requires coherence modification.

## 2.2.2 Handling Register Dependences

Because we execute an unmodified single-threaded binary, the code, although executed in parallel, assumes a single unified register file. As a result, there will be register dependences that cross thread boundaries. Prior work has managed these dependences in various ways including explicit forwarding [SBV95, Vij98, ZCSM02], hardware prediction [MG02], and software precomputation [MGQS<sup>+</sup>08].

| Cores                  | 2          | I cache miss penalty | 20 cyc             |

|------------------------|------------|----------------------|--------------------|

| Fetch width/core       | 4          | D cache              | 32k, 4 way         |

| INT instruction queue  | 64 entries | D cache miss penalty | 20 cyc             |

| FP instruction queue   | 64 entries | shared L2 cache      | 2  MB, 8  way      |

| Reorder Buffer entries | 128        | L2 miss penalty      | $75 \mathrm{~cyc}$ |

| FP registers per core  | 132        | L3                   | 4 MB, 8 way        |

| Fork penalty           | 10  cyc    | L3 miss penalty      | 315  cyc           |

| Cache line size        | 64 bytes   | Victim cache entries | 8                  |

| I cache                | 32k, 4 way |                      |                    |

Table 2.2: Architectural Specification

In this research we initially want to decouple the register dependence problem (which is orthogonal to the memory design) and thus adopt a very simple model for our initial results — register dependences are handled by prediction and all predictions are correct. We consider the case of a realistic, but not particularly aggressive, predictor in Section 2.6 and show that all the key conclusions of the chapter still hold. We should note that the assumption of perfect or near-perfect prediction is not an absurd one — the Mitosis register prediction model [MGQS<sup>+</sup>08], because it leverages code from the spawning thread, can be made to be arbitrarily accurate. However, this causes a larger delay in thread spawn.

# 2.3 Methodology

To evaluate the performance of our various models of speculative multithreading, we added support for SpMT, including the full suite of memory designs, to the SMTSIM simulator [Tul96]. The SMTSIM simulator has extensive support for both multithreaded and multi-core execution, and for this study it is configured for multi-core. Speculative threads are executed on available cores on a CMP with a varying number of in-order execution cores. Table 2.2 gives the configuration details of the default architecture we simulate.

The simulator models spawning at instruction fetch, exposes wrong-path memory operations to coherence, and squashes threads in reaction to various memory coherence operations. It also models the effect of spawn points fetched on the wrong path (a result of the design decision to spawn threads when the spawn point is fetched rather than at commit) by ensuring that the target core is occupied and unavailable for execution until the branch mispredict is discovered.

We use the SPEC CPU2000 benchmarks, specifically the Alpha binaries for SimpleScalar [ALE02]. Using reference inputs, we simulate the execution of one hundred million instructions starting at the standard SimPoint [SPHC02].

# 2.4 Leveraging TM for SpMT