# Sleepy Stack: a New Approach to Low Power VLSI Logic and Memory

A Thesis Presented to The Academic Faculty

by

## Jun Cheol Park

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology August 2005

## Sleepy Stack: a New Approach to Low Power VLSI Logic and Memory

Approved by:

Professor Vincent J. Mooney III, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Abhijit Chatterjee School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Paul E. Hasler School of Electrical and Computer Engineering *Georgia Institute of Technology*  Professor John Dorsey School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Michael Niemier College of Computing Georgia Institute of Technology

Date Approved: June 24, 2005

To my wife, Jaemin Lee,

for her love, support and sacrifices.

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude and appreciation to everyone who made this thesis possible. Most of all, I would like to thank my advisor, Professor Vincent J. Mooney III, for his guidance of my research and his patience during my Ph.D. study at Georgia Tech. With his knowledge and experience, he has guided me to successfully achieve my research objective.

Second, I would like to thank my thesis committee members, Professor Abhijit Chatterjee, Professor Paul E. Hasler, Professor John Dorsey, and Professor Michael Niemier for their critical evaluation and valuable suggestions. Especially Professor Chatterjee and Professor Hasler served me as reading committee members and gave me invaluable feedback for my thesis.

Third, I would like to thank all my colleagues in the Hardware/Software Codesign Group and the COPAC group for their support and friendship. Especially, Kiran Puttaswamy, Sudarshan K. Srinivasan, Pinar Korkmaz, and Philipp Pfeiffenberger helped me to make valuable results during my Ph.D. at Georgia Tech.

Last, but most importantly, I would like to specially thank to my wife Jaemin Lee for her love and support during my Ph.D. She encouraged me to finish my Ph.D. research.

# TABLE OF CONTENTS

| DE  | DICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TION     |                                                                  | iii |  |  |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------|-----|--|--|--|--|

| AC  | KNO                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WLED     | GEMENTS                                                          | iv  |  |  |  |  |

| LIS | ST OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TABL     | ES                                                               | ix  |  |  |  |  |

| LIS | ST OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FIGUI    | RES                                                              | x   |  |  |  |  |

| LIS | ST OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SYMB     | BOLS OR ABBREVIATIONS                                            | xiv |  |  |  |  |

| SUI | MMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RY.      |                                                                  | XV  |  |  |  |  |

| I   | INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RODU     | CTION                                                            | 1   |  |  |  |  |

|     | 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Proble   | m Statement                                                      | 3   |  |  |  |  |

|     | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Contri   | butions                                                          | 4   |  |  |  |  |

|     | 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Thesis   | Organization                                                     | 5   |  |  |  |  |

| Π   | MO                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TIVATI   | ON                                                               | 7   |  |  |  |  |

| ш   | NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TATION   | AND BACKGOUND                                                    | 11  |  |  |  |  |

|     | 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Leakag   | ge power                                                         | 11  |  |  |  |  |

|     | 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SRAM     | I cell leakage paths                                             | 14  |  |  |  |  |

|     | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Switch   | ing power and delay tradeoffs                                    | 15  |  |  |  |  |

| IV  | PRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EVIOUS   | SWORK                                                            | 18  |  |  |  |  |

|     | 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Static 1 | Power Reduction VLSI Research                                    | 18  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.1.1    | Static Power Reduction Research for Generic Logic Circuits       | 18  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.1.2    | Static Power Reduction Research for SRAM                         | 22  |  |  |  |  |

|     | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Power    | Reduction Research Using Voltage Scaling and Pipelining Caches . | 29  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.1    | HYPER-LP                                                         | 30  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.2    | Multiple $V_{dd}$ and $V_{th}$ Optimization                      | 31  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.3    | Low-Power Pipelined Cache                                        | 33  |  |  |  |  |

|     | 1.3 Thesis Organization5MOTIVATION7NOTATION AND BACKGOUND113.1 Leakage power113.2 SRAM cell leakage paths143.3 Switching power and delay tradeoffs15PREVIOUS WORK184.1 Static Power Reduction VLSI Research184.1.1 Static Power Reduction Research for Generic Logic Circuits184.1.2 Static Power Reduction Research for SRAM224.2 Power Reduction Research Using Voltage Scaling and Pipelining Caches294.2.1 HYPER-LP304.2.2 Multiple $V_{dd}$ and $V_{th}$ Optimization31 |          |                                                                  |     |  |  |  |  |

| $\mathbf{V}$ | SLE | EPY S  | TACK STRUCTURE                                                      | 36 |

|--------------|-----|--------|---------------------------------------------------------------------|----|

|              | 5.1 | Sleepy | v stack approach                                                    | 36 |

|              |     | 5.1.1  | Sleepy stack structure                                              | 37 |

|              |     | 5.1.2  | Sleepy stack operation                                              | 38 |

|              | 5.2 | Analy  | tical comparison of sleepy stack inverter vs. forced stack inverter | 39 |

|              |     | 5.2.1  | Delay model                                                         | 40 |

|              | 5.3 | Summ   | ary                                                                 | 42 |

| VI           | APF | PLYINC | G SLEEPY STACK                                                      | 44 |

|              | 6.1 | Apply  | ing sleepy stack to logic circuits                                  | 44 |

|              |     | 6.1.1  | Benchmark circuits                                                  | 44 |

|              |     | 6.1.2  | Prior low-leakage techniques considered for comparison purposes     | 47 |

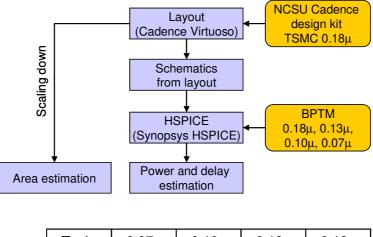

|              |     | 6.1.3  | Experimental methodology                                            | 51 |

|              | 6.2 | Apply  | ing sleepy stack to SRAM                                            | 57 |

|              |     | 6.2.1  | Sleepy stack SRAM structure                                         | 58 |

|              |     | 6.2.2  | Methodology                                                         | 61 |

|              | 6.3 | Summ   | ary                                                                 | 63 |

| VII          | SLE | EPY S  | TACK EXPERIMENTAL RESULTS                                           | 64 |

|              | 7.1 | Experi | imental results for general logic circuits                          | 64 |

|              |     | 7.1.1  | Impact of technology scaling                                        | 64 |

|              |     | 7.1.2  | Impact of $V_{th}$                                                  | 68 |

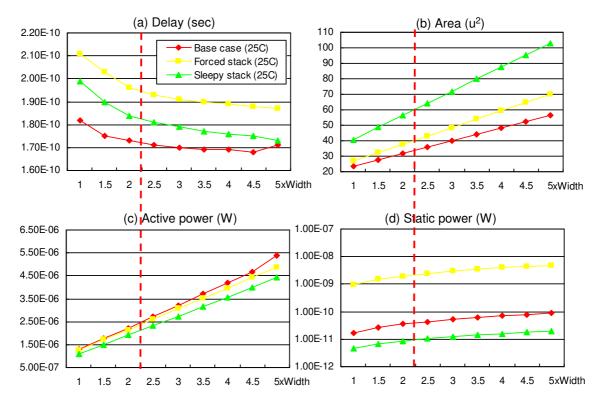

|              |     | 7.1.3  | Impact of transistor width                                          | 70 |

|              | 7.2 | Experi | imental results for SRAM                                            | 72 |

|              |     | 7.2.1  | Area                                                                | 72 |

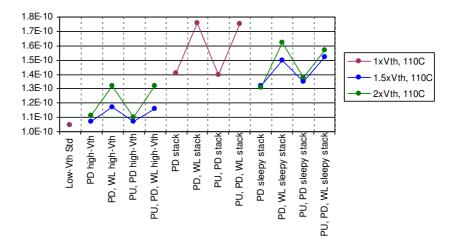

|              |     | 7.2.2  | Cell read time                                                      | 73 |

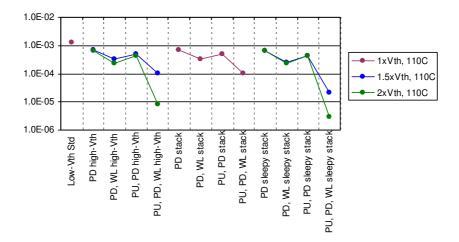

|              |     | 7.2.3  | Leakage power                                                       | 74 |

|              |     | 7.2.4  | Tradeoffs in low-leakage techniques                                 | 76 |

|              |     | 7.2.5  | Active power                                                        | 78 |

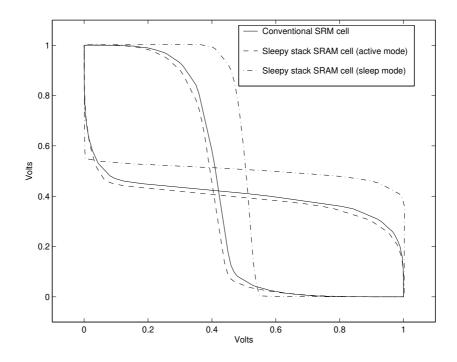

|              |     | 7.2.6  | Static noise margin                                                 | 78 |

|     | 7.3        | Summ   | ary                                               |

|-----|------------|--------|---------------------------------------------------|

| VII | I LO       | W-POV  | VER PIPELINED CACHE (LPPC) ARCHITECTURE 81        |

|     | 8.1        | Backg  | round of a Pipelined Cache                        |

|     | 8.2        | Low-P  | Power Pipelined Cache Architecture                |

|     |            | 8.2.1  | Low-power pipelined cache energy savings          |

|     |            | 8.2.2  | Pipelining techniques for LPPC                    |

|     |            | 8.2.3  | Pipelining penalties and solutions for LPPC       |

|     | 8.3        | Summ   | ary                                               |

| IX  |            |        | TER PIPELINED CACHE (LPPC) EXPERIMENTAL SETUP AND |

|     | кез<br>9.1 |        |                                                   |

|     | 9.1        | 9.1.1  | Processor Model         90                        |

|     |            | 9.1.2  | Cache Delay Model         95                      |

|     |            | 9.1.2  | Architecture Configurations and Benchmarks        |

|     | 9.2        |        | mental Results                                    |

|     |            | 9.2.1  | Performance results                               |

|     |            | 9.2.2  | Impact of instruction distribution on performance |

|     |            | 9.2.3  | Cache power results                               |

|     |            | 9.2.4  | Processor power results                           |

|     | 9.3        | Summ   | ary                                               |

| X   | SLE        | EPY S  | TACK PIPELINED CACHE                              |

|     | 10.1       | Appro  | ach                                               |

|     | 10.2       | Desigr | n methodology                                     |

|     |            | 10.2.1 | Sleepy stack SRAM                                 |

|     |            | 10.2.2 | Pipelined cache model                             |

|     | 10.3       | Result | s                                                 |

|     |            | 10.3.1 | SRAM power consumption                            |

|     |            | 10.3.2 | Pipelined cache performance                       |

|     | 10.4       | Summ   | ary                                               |

| XI CONCLUSION       |                          |

|---------------------|--------------------------|

| APPENDICES          |                          |

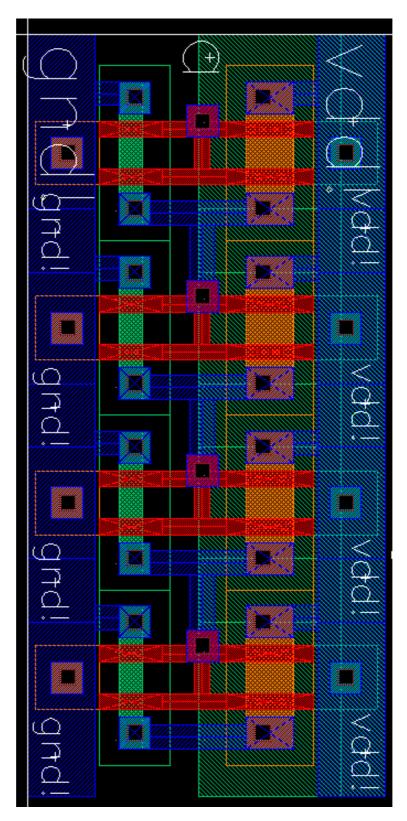

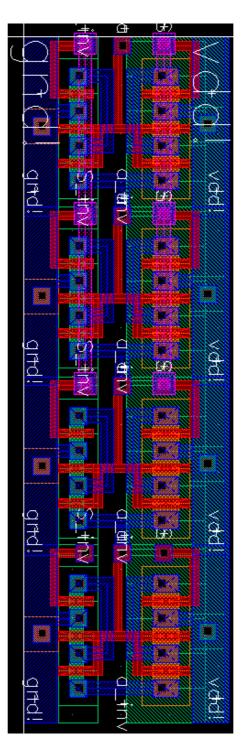

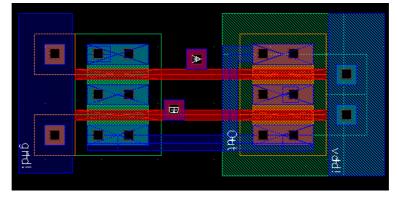

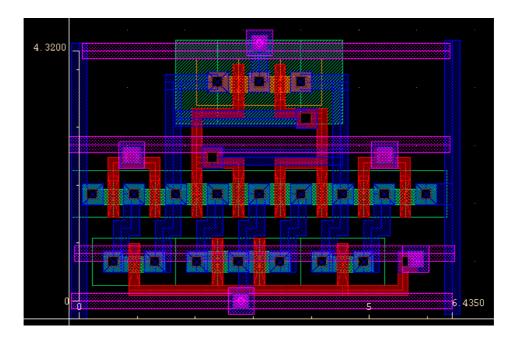

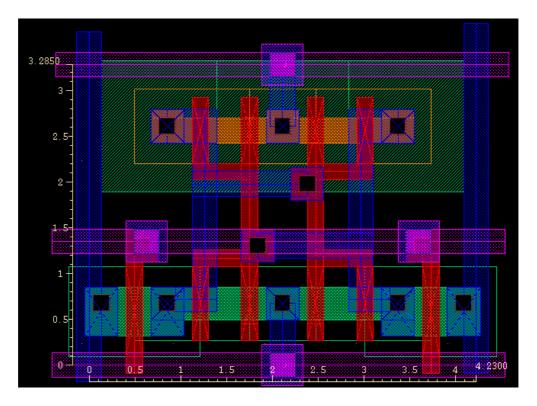

| APPENDIX A — CHAIN  | OF FOUR INVERTERS LAYOUT |

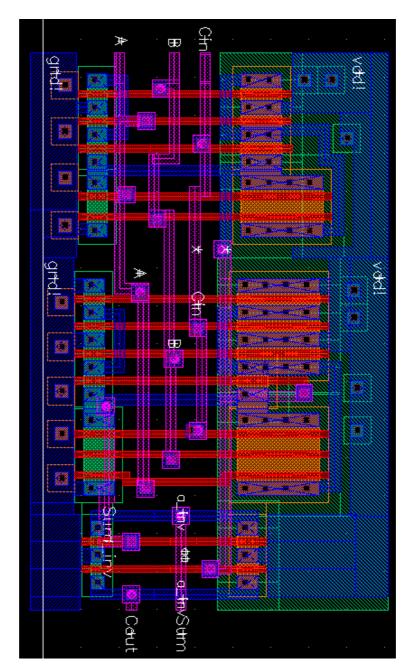

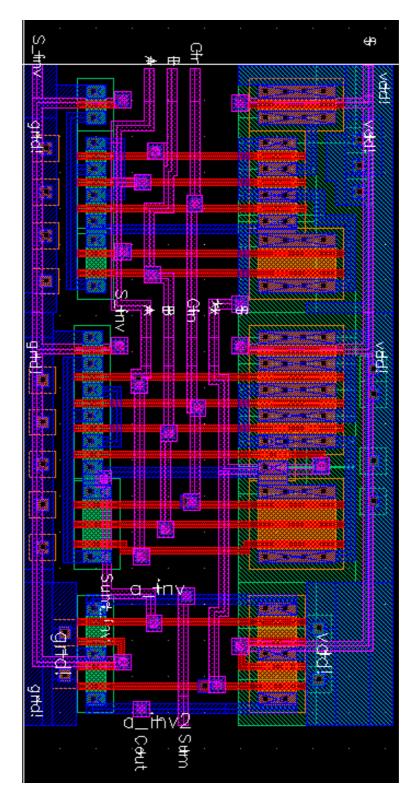

| APPENDIX B — FULL A | DDER LAYOUT              |

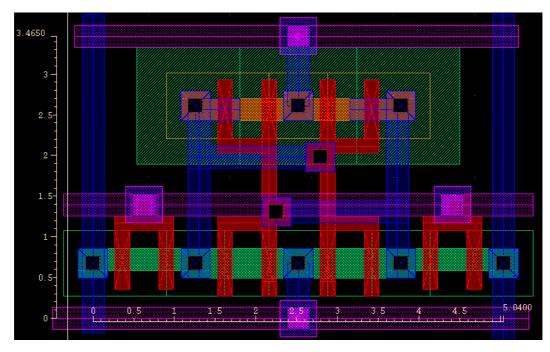

| APPENDIX C — NAND A | AND NOR LAYOUT           |

| APPENDIX D — SRAM ( | CELL LAYOUT              |

| REFERENCES          |                          |

| PUBLICATIONS        |                          |

# LIST OF TABLES

| Table 1  | Power and area results from Chapter 7                     | 8   |

|----------|-----------------------------------------------------------|-----|

| Table 2  | Energy consumption scenario of a cell phone $(0.07\mu)$   | 8   |

| Table 3  | Leakage model parameters (0.5 $\mu$ tech)                 | 13  |

| Table 4  | Input sets for a 4:1 multiplexer static power measurement | 56  |

| Table 5  | Sleepy stack technique on a SRAM cell                     | 58  |

| Table 6  | Applied SRAM techniques                                   | 62  |

| Table 7  | Results for a chain of 4 inverters $(0.07\mu)$            | 65  |

| Table 8  | Results for a 4:1 multiplexers $(0.07\mu)$                | 67  |

| Table 9  | Results for a 4-bit adders $(0.07\mu)$                    | 68  |

| Table 10 | Layout area                                               | 72  |

| Table 11 | Cell read time                                            | 73  |

| Table 12 | Leakage power                                             | 74  |

| Table 13 | Tradeoffs (1.5x $V_{th}$ , 110° $C$ )                     | 76  |

| Table 14 | Tradeoffs (2.0x $V_{th}$ , 110° $C$ )                     | 77  |

| Table 15 | Active power                                              | 78  |

| Table 16 | Static noise margin                                       | 78  |

| Table 17 | Cache configuration parameters                            | 95  |

| Table 18 | Simplescalar configurations                               | 98  |

| Table 19 | Benchmarks                                                | 99  |

| Table 20 | Execution cycles                                          | 101 |

| Table 21 | Simplescalar configurations for sleepy stack SRAM         | 114 |

| Table 22 | SRAM power consumption                                    | 115 |

| Table 23 | SRAM delay                                                | 116 |

| Table 24 | Pipelined cache active power per benchmark                | 117 |

# LIST OF FIGURES

| Figure 1  | Subthreshold leakage of an nFET                                                  | 11 |

|-----------|----------------------------------------------------------------------------------|----|

| Figure 2  | (a) A single transistor (left) and (b) stacked transistors (right)               | 12 |

| Figure 3  | SRAM cell leakage paths                                                          | 14 |

| Figure 4  | Sleep transistor technique                                                       | 19 |

| Figure 5  | Zigzag technique                                                                 | 20 |

| Figure 6  | Forced stack inverter                                                            | 21 |

| Figure 7  | Asymmetric SRAM cell                                                             | 23 |

| Figure 8  | ABC-MTCMOS                                                                       | 24 |

| Figure 9  | SRAM cell with nMOS gated- $V_{dd}$                                              | 26 |

| Figure 10 | Drowsy cache                                                                     | 27 |

| Figure 11 | Before (up) and after (down) applying EDR paradigm                               | 32 |

| Figure 12 | (a) Forced stack inverter (left) and (b) Sleep transistor inverter (right)       | 37 |

| Figure 13 | (a) Sleepy stack active mode (left) and (b) sleep mode (right)                   | 38 |

| Figure 14 | (a) Inverter logic circuit (left) and (b) RC equivalent circuit (right)          | 40 |

| Figure 15 | (a) Forced stack technique inverter (left) and (b) RC equivalent circuit (right) | 40 |

| Figure 16 | (a) Sleepy stack technique inverter (left) and (b) RC equivalent circuit (right) | 41 |

| Figure 17 | Chain of 4 inverters                                                             | 45 |

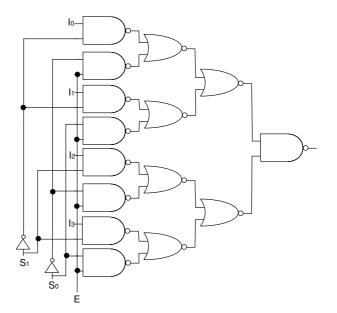

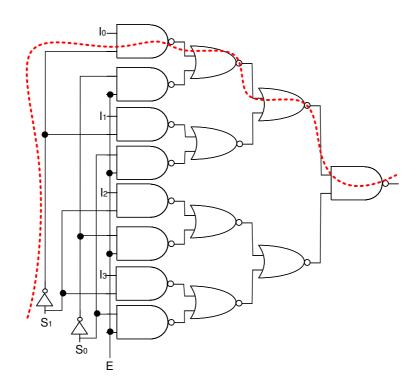

| Figure 18 | 4:1 multiplexer                                                                  | 45 |

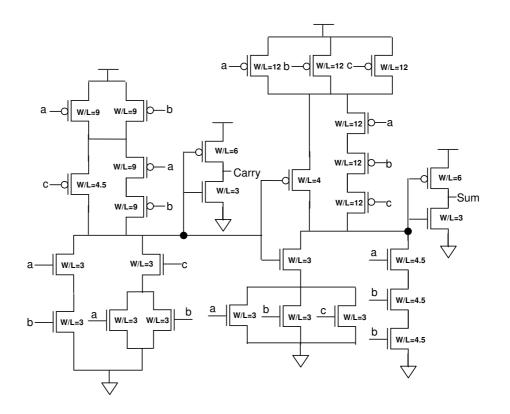

| Figure 19 | 1-bit full adder                                                                 | 46 |

| Figure 20 | Base case                                                                        | 47 |

| Figure 21 | Sleepy stack                                                                     | 48 |

| Figure 22 | Forced stack                                                                     | 49 |

| Figure 23 | Sleep                                                                            | 49 |

| Figure 24 | Zigzag                                                                           | 50 |

| Figure 25 | Experimental methodology                                                         | 51 |

| Figure 26 | 4:1 multiplexer critical path                                                    | 53 |

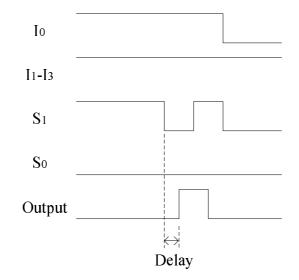

| Figure 27 | Input/output waveform for 4:1 multiplexer 5                                                                                                                                                      | 3 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

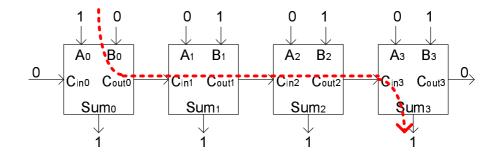

| Figure 28 | Inputs of 4-bit adder for critical path delay measurement                                                                                                                                        | 4 |

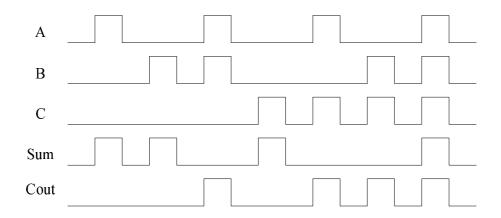

| Figure 29 | Waveforms of 1-bit adder for dynamic power measurement                                                                                                                                           | 5 |

| Figure 30 | SRAM cell and leakage paths                                                                                                                                                                      | 8 |

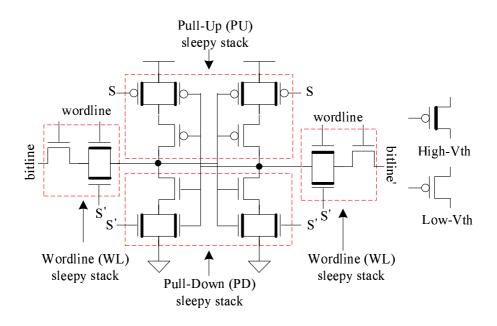

| Figure 31 | Sleepy stack SRAM cell                                                                                                                                                                           | 9 |

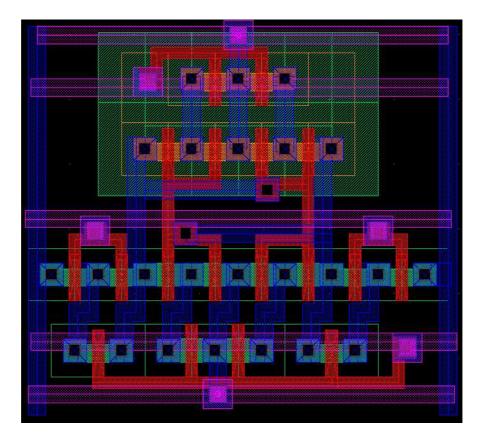

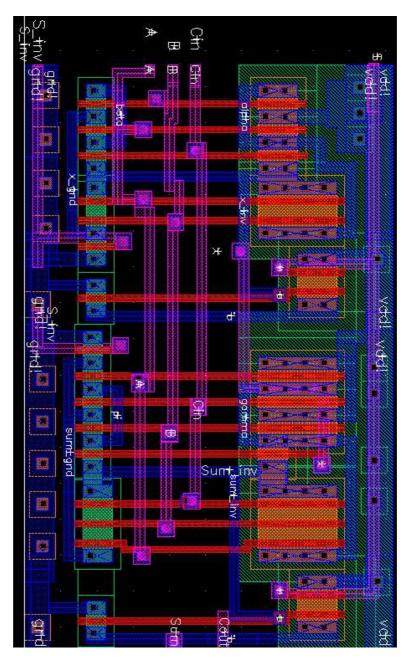

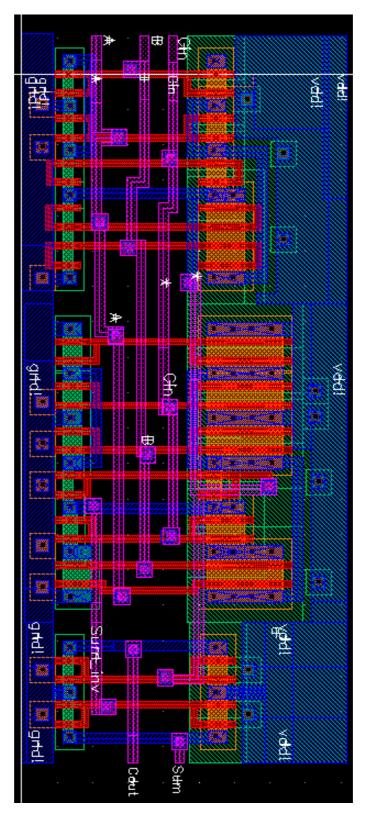

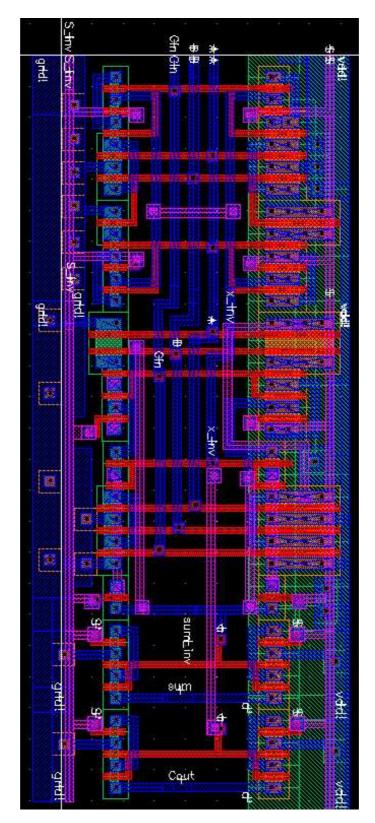

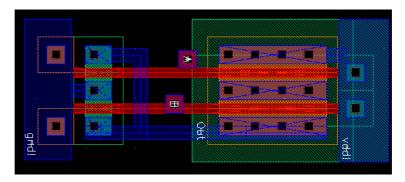

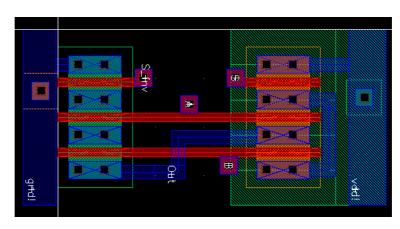

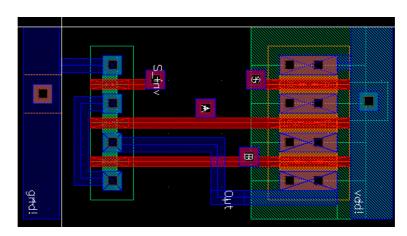

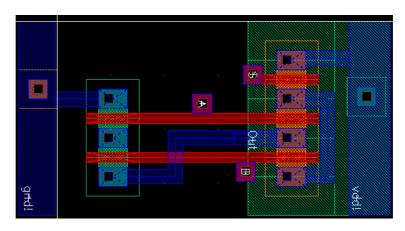

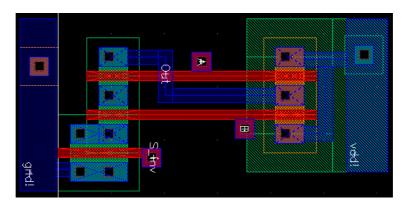

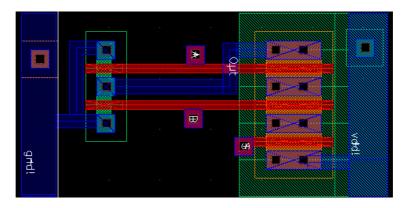

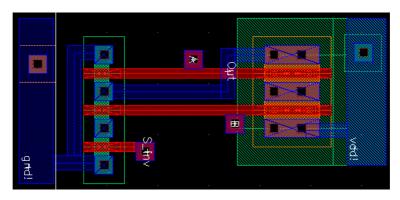

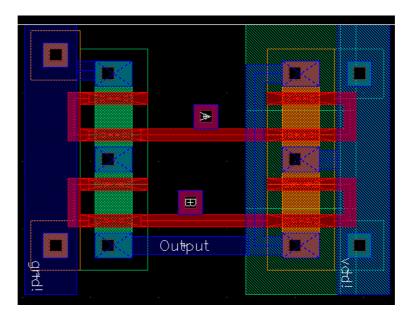

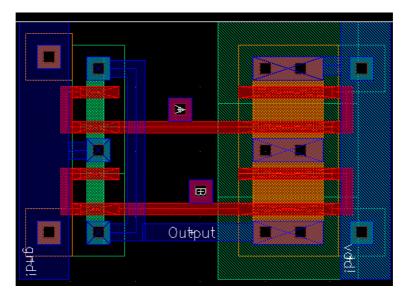

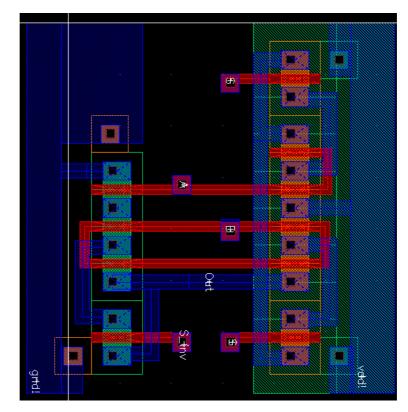

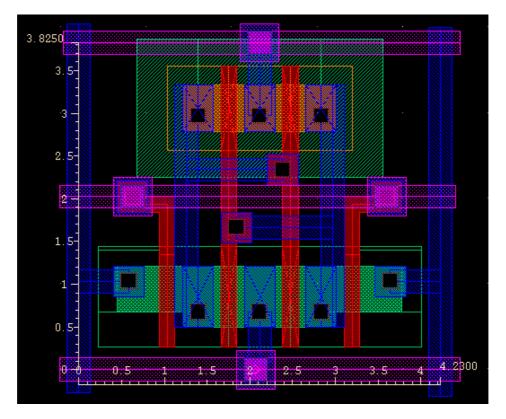

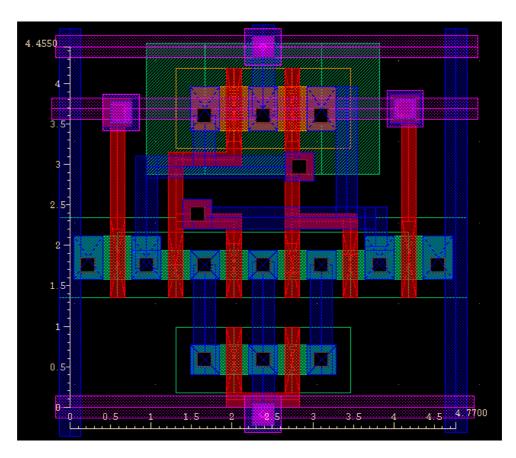

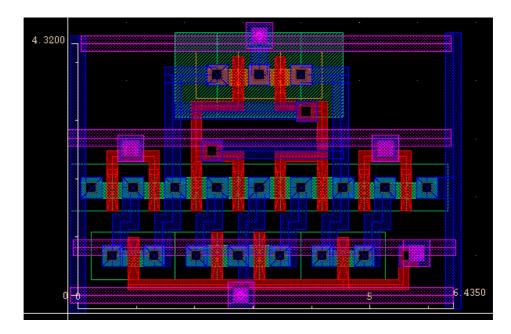

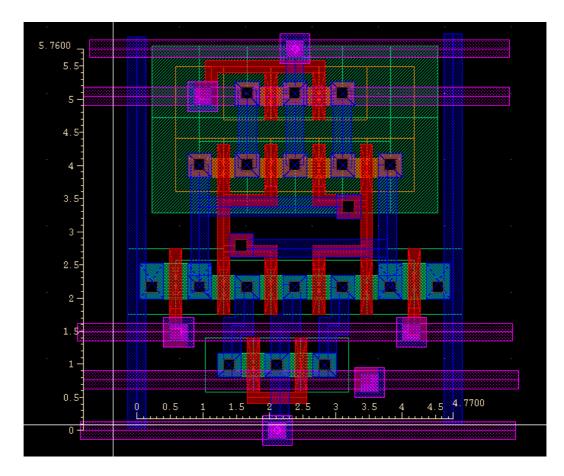

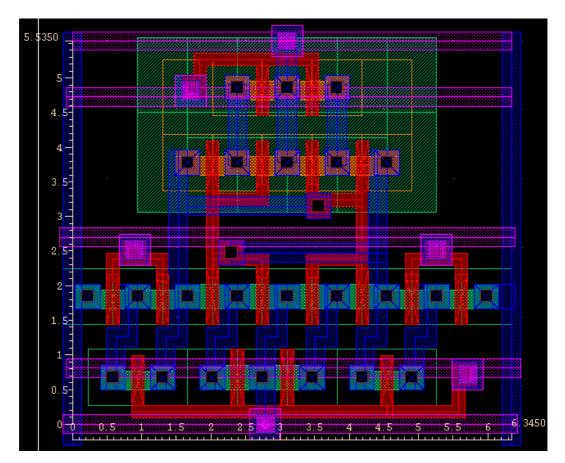

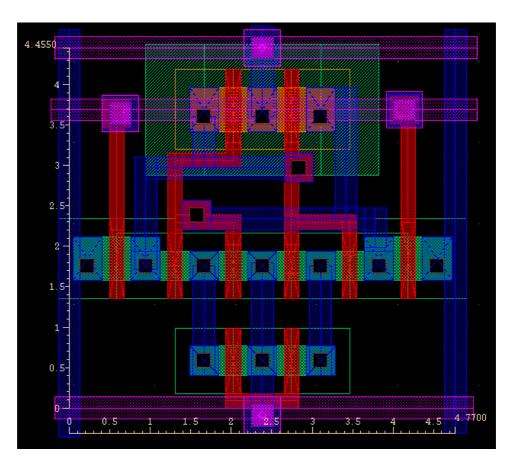

| Figure 32 | Sleepy stack SRAM cell layout                                                                                                                                                                    | 0 |

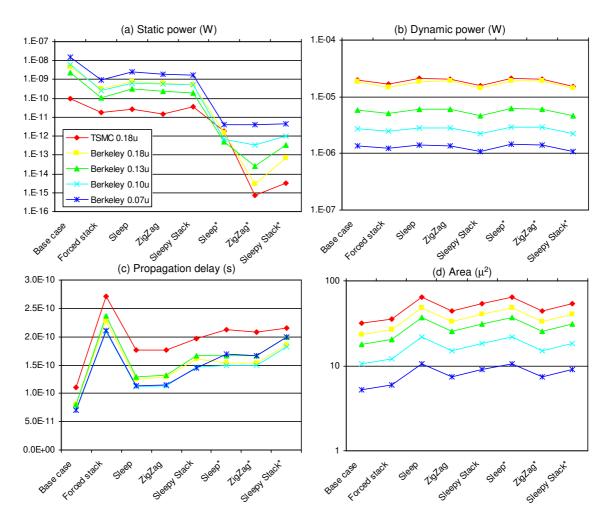

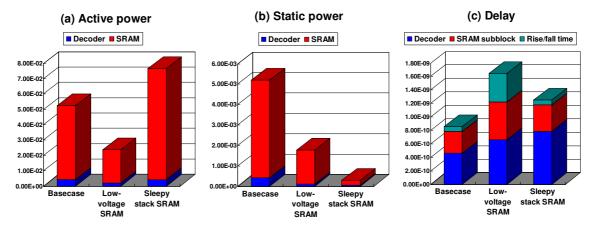

| Figure 33 | Results for a chain of 4 inverters (*dual $V_{th}$ )                                                                                                                                             | 5 |

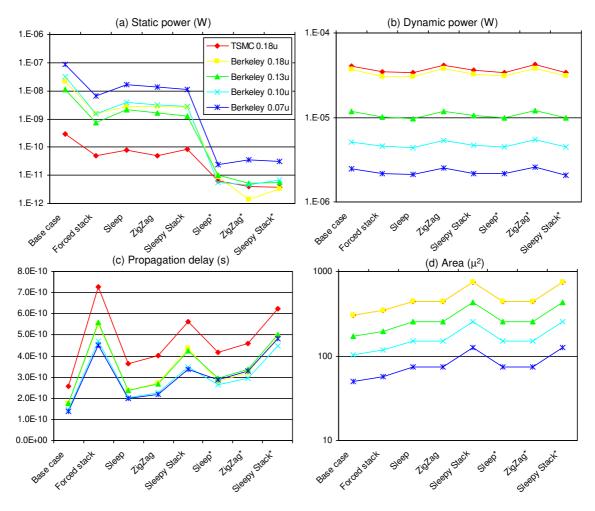

| Figure 34 | Results for a 4:1 multiplexers (*dual $V_{th}$ )                                                                                                                                                 | 6 |

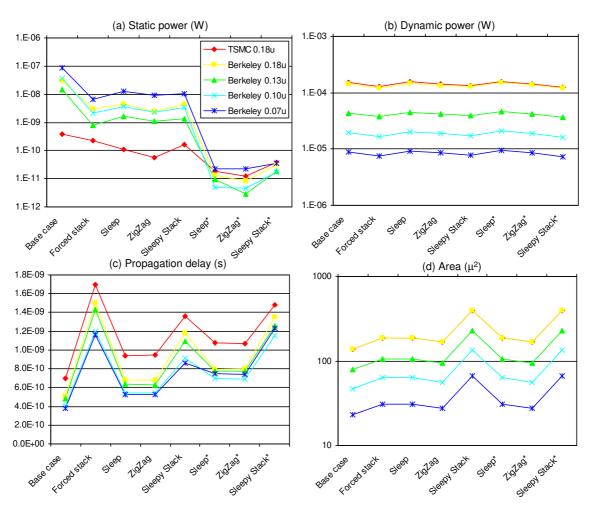

| Figure 35 | Results for a 4-bit adders (*dual $V_{th}$ )                                                                                                                                                     | 7 |

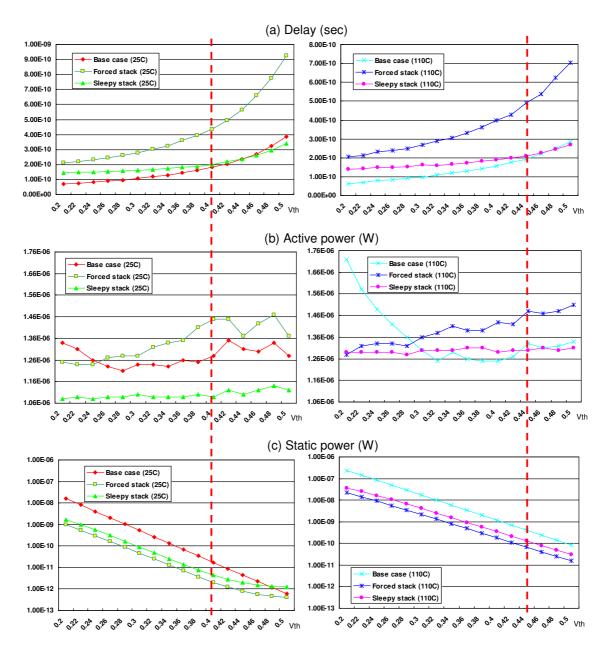

| Figure 36 | Results from a chain of 4 inverters while varying $V_{th}$                                                                                                                                       | 9 |

| Figure 37 | Results from a chain of 4 inverters while varying width                                                                                                                                          | 1 |

| Figure 38 | Worst case (at $110^{\circ}C$ ) cell read time comparison $\ldots \ldots \ldots$ | 3 |

| Figure 39 | Worst case (at $110^{\circ}C$ ) leakage comparison                                                                                                                                               | 5 |

| Figure 40 | Static noise margin analysis                                                                                                                                                                     | 9 |

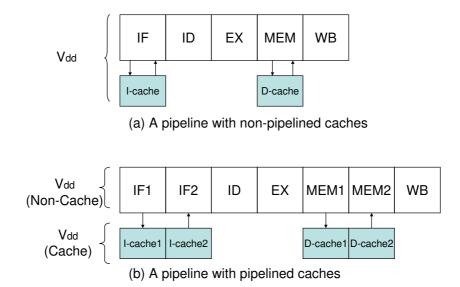

| Figure 41 | Non-pipelined and pipelined cache architectures                                                                                                                                                  | 2 |

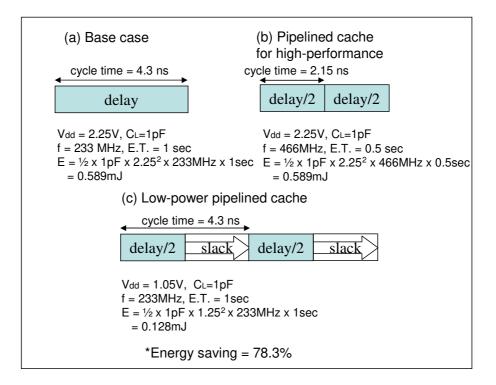

| Figure 42 | Illustration of energy of a pipelined cache                                                                                                                                                      | 5 |

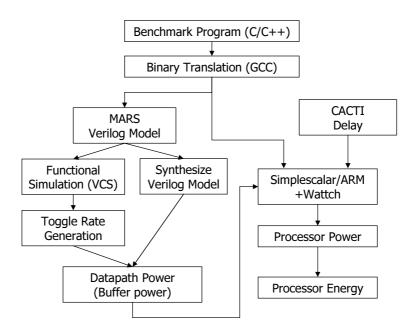

| Figure 43 | Performance and power simulation infrastructure                                                                                                                                                  | 2 |

| Figure 44 | Latch-based cache pipelining                                                                                                                                                                     | 6 |

| Figure 45 | Delay of a latch-pipelined(left) and wave-pipelined(right) cache 9                                                                                                                               | 7 |

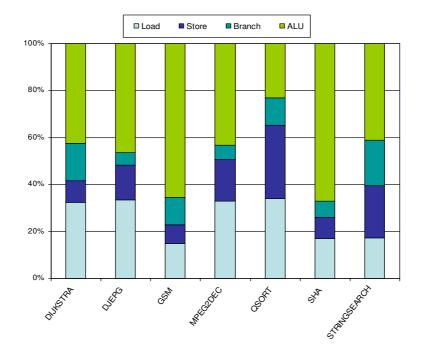

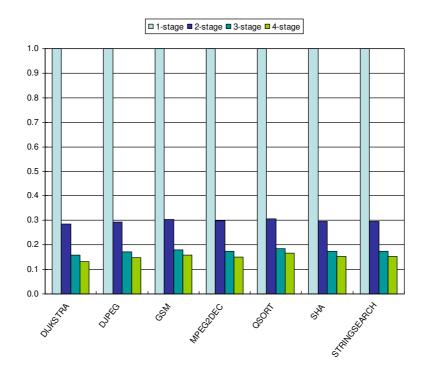

| Figure 46 | Dynamic instruction distribution                                                                                                                                                                 | 2 |

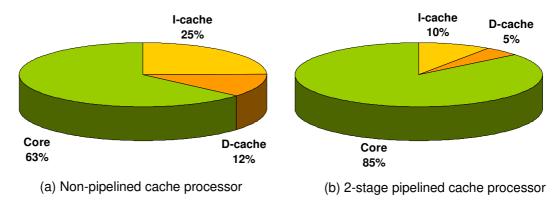

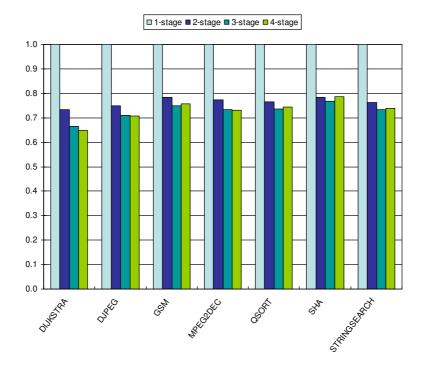

| Figure 47 | Normalized cache power consumption according to the cache pipeline stage                                                                                                                         | 4 |

| Figure 48 | Processor power distribution                                                                                                                                                                     | 4 |

| Figure 49 | Normalized processor power consumption according to the cache pipeline stage                                                                                                                     | 5 |

| Figure 50 | Normalized Processor energy consumption according to the cache pipeline stage                                                                                                                    | 6 |

| Figure 51 | Pipelined cache adjusted power consumption                                                                                                                                                       | 7 |

| Figure 52 | Non-pipelined and sleepy stack pipelined cache architectures 10                                                                                                                                  | 9 |

| Figure 53 | SRAM structure                                                                                                                                                                                   | 1 |

| Figure 54 | SRAM performance comparison               |

|-----------|-------------------------------------------|

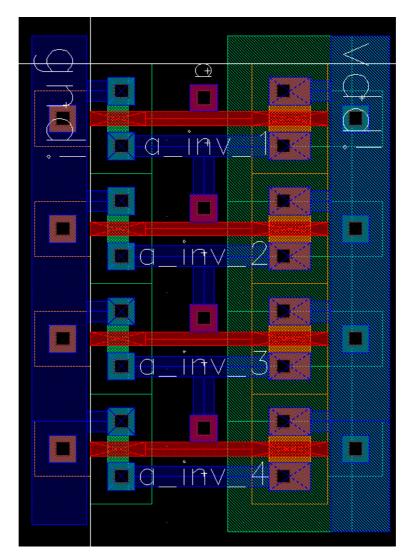

| Figure 55 | Base case 4 inverters                     |

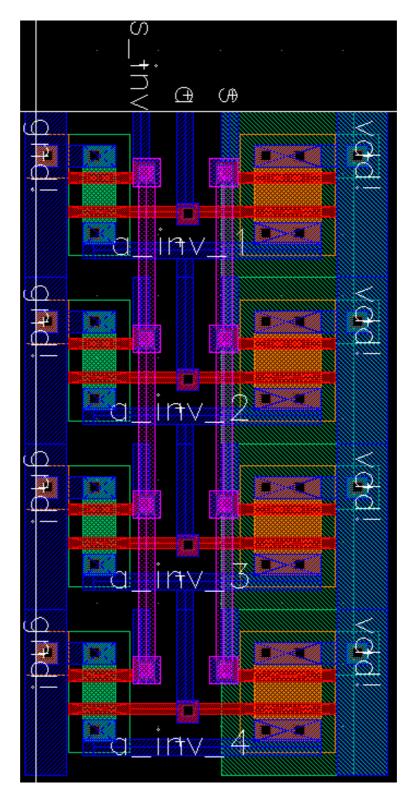

| Figure 56 | Sleep approach 4 inverters                |

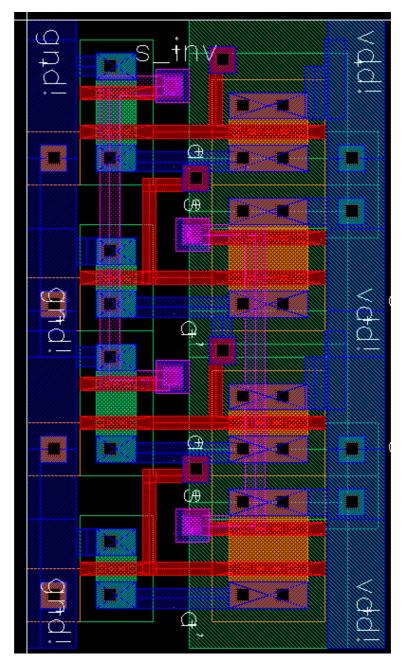

| Figure 57 | Zigzag approach 4 inverters               |

| Figure 58 | Forced stack approach 4 inverters         |

| Figure 59 | Sleepy stack approach 4 inverters         |

| Figure 60 | Base case full adder                      |

| Figure 61 | Sleep approach full adder                 |

| Figure 62 | Zigzag approach full adder                |

| Figure 63 | Forced stack approach full adder          |

| Figure 64 | Sleepy stack approach full adder          |

| Figure 65 | Base case NAND                            |

| Figure 66 | Base case NOR                             |

| Figure 67 | Sleep approach NAND                       |

| Figure 68 | Sleep approach NOR                        |

| Figure 69 | Zigzag approach NAND with pull-up sleep   |

| Figure 70 | Zigzag approach NAND with pull-down sleep |

| Figure 71 | Zigzag approach NOR with pull-up sleep    |

| Figure 72 | Zigzag approach NOR with pull-down sleep  |

| Figure 73 | Forced stack approach NAND                |

| Figure 74 | Forced stack approach NOR                 |

| Figure 75 | Sleepy stack approach NOR                 |

| Figure 76 | 6-T conventional SRAM cell                |

| Figure 77 | PD sleepy stack SRAM cell                 |

| Figure 78 | PD, WL sleepy stack SRAM cell             |

| Figure 79 | PU, PD sleepy stack SRAM cell             |

| Figure 80 | PU, PD, WL sleepy stack SRAM cell         |

| Figure 81 | PD forced stack SRAM cell                 |

| Figure 82 | PD, WL forced stack SRAM cell             |

| Figure 83 | PU, PD forced stack SRAM cell     | 144 |

|-----------|-----------------------------------|-----|

| Figure 84 | PU, PD, WL forced stack SRAM cell | 144 |

## LIST OF SYMBOLS OR ABBREVIATIONS

**ABC-MTCMOS** Auto-Backgate-Controlled Multi-Threshold CMOS.

- **ACC** Asymmetric-Cell Cache.

- **BTB** Branch Target Buffer.

- **CMOS** Complementary Metal Oxide Semiconductor.

- **DIBL** Drain Induced Barrier Lowering.

- **EDR** Energy-Delay Ratio.

- **FBB** Forward-Body Bias.

- **ITRS** International Technology Roadmap for Semiconductors.

- **LPPC** Low-Power Pipelined Cache.

- **MTCMOS** Multi-Threshold-voltage CMOS.

- **RBB** Reverse-Body Bias.

- **RTL** Register Transfer Level.

- **SRAM** Static Random Access Memory.

- **VLSI** Very Large Scale Integration.

- **ZBB** Zero-Body Bias.

#### SUMMARY

The main objective of this thesis is to provide new low power solutions for Very Large Scale Integration (VLSI) designers. Especially, we focus on leakage power reduction. Although leakage power was negligible at  $0.18\mu$  technology and above, in nanoscale technology, such as  $0.07\mu$ , leakage power is almost equal to dynamic power consumption.

In this thesis, we present a novel circuit structure we call "sleepy stack." The sleepy stack structure dramatically reduces leakage. The sleepy stack is a combination of two wellknown low-leakage techniques which are the forced stack technique and the sleep transistor technique. The sleepy transistor technique can achieve ultra-low leakage power consumption, but loses logic state during sleep mode. Meanwhile, the forced stack technique saves leakage power consumption by stacking transistors and retains logic state. However, the forced stack technique cannot use high- $V_{th}$  without incurring a dramatic delay increase (>6.2X); however, if only low- $V_{th}$  transistors are used, the leakage power savings of this technique are small. By combining two prior techniques, however, the sleepy stack technique can achieve (i) ultra-low leakage power consumption while (ii) saving state. One of the main advantages of the sleepy stack technique is a use of high- $V_{th}$  transistors for key places. Utilizing high- $V_{th}$  transistors, the sleepy stack technique can achieve around 200X leakage power reduction with similar delay as the forced stack technique using low- $V_{th}$  transistors (when applied to generic logic circuits targeting  $0.07\mu$  technology). Since the sleepy stack technique comes with area and delay overhead compared to a conventional Complementary Metal Oxide Semiconductor (CMOS) technique, the sleepy stack technique can be applicable to a design that requires ultra-low leakage power consumption with quick response time and is able to pay the associated area and delay cost.

One of the advantages of the sleepy stack technique is saving state. Therefore, the sleepy stack technique can be applicable memory design, i.e., Static Random Access Memory (SRAM). When we apply the sleepy stack to SRAM cell design, we can observe new Pareto points which have not been presented prior to the research in this thesis. Although the sleepy stack incurs some delay and area overheads, the sleepy stack SRAM cell can achieve ultra-low leakage power consumption while suppressing two main leakage paths in an SRAM cell. When compared to a high- $V_{th}$  SRAM cell, which is the best prior statesaving SRAM cell, the sleepy stack SRAM cell achieves  $5.13 \sim 2.77X$  greater leakage reduction with  $32 \sim 19\%$  delay increase (at  $110^\circ$  using  $0.07\mu$  technology). Alternatively, by increasing sleepy stack transistor widths, the sleepy stack SRAM cell can achieve approximately the same delay as high- $V_{th}$  SRAM yet achieves  $2.49 \sim 2.26X$  leakage reduction over high- $V_{th}$  SRAM. Unfortunately, there is a cost of 140% area increase.

Along with the sleepy stack structure, we propose a architectural level low power technique we name Low-Power Pipelined Cache (LPPC). Originally, a pipelined cache was proposed to reduce cache pipeline stage delay and thus improve processor performance. However, we use the reduced cache delay to reduce power consumption. Our strategy is to pipeline caches without changing cycle time; instead, we lower cache supply voltage to save power consumption. Although we may increase the depth of a pipelined cache to achieve large power reduction, total energy savings associated with increasing pipeline depth may limited due to the pipelining penalties and lower limit of supply voltage. We obtain an optimal depth of the pipelined cache in our experimental configuration targeting an embedded processor; the result we find is that a two stage pipelined cache achieves maximum energy reduction (70% cache power savings).

The sleepy stack structure achieves ultra-low leakage power consumption with some area and delay overheads. To reduce the delay overhead while achieving low-leakage power, we combine LPPC and the sleepy stack. When targeting  $0.07\mu$  technology, the sleepy stack pipelined cache achieves 17X leakage power reduction with 4% execution

cycle increase and 31% active power increase compared to conventional SRAM. Using a pipelined cache, we can hide most of the delay overhead induced by the sleepy stack, which is 33%. The result indicates that total energy is saved when the device spends at least three times as much time in sleep mode as in active mode.

In summary, this thesis presents heretofore unexplored methods for low-power VLSI design. In particular, the sleepy stack approach provides what may be the best solution for VLSI designers concerned about the twin problems of low static power and maintenance of VLSI logic state during sleep mode. For such a two-headed problem, the sleepy stack approach can provide two orders of magnitude (100X) or more static power reduction over the best prior approach; however, there is a cost – potentially quite small – in terms of delay increase and area overhead. In short, sleepy stack principles provide heretofore unknown Pareto points for consideration in VLSI design.

## **CHAPTER I**

#### INTRODUCTION

Power consumption is one of the top concerns of Very Large Scale Integration (VLSI) circuit design, for which Complementary Metal Oxide Semiconductor (CMOS) is the primary technology. Today's focus on low power is not only because of the recent growing demands of mobile applications. Even before the mobile era, power consumption has been a fundamental problem. To solve the power dissipation problem, many researchers have proposed different ideas from the device level to the architectural level and above. However, there is no universal way to avoid tradeoffs between power, delay and area, and thus designers are required to choose appropriate techniques that satisfy application and product needs.

Power consumption of CMOS consists of dynamic and static components. Dynamic power is consumed when transistors are switching, and static power is consumed regardless of transistor switching. Dynamic power consumption was previously (at 0.18 $\mu$  technology and above) the single largest concern for low-power chip designers since dynamic power accounted for 90% or more of the total chip power. Therefore, many previously proposed techniques, such as voltage and frequency scaling, focused on dynamic power reduction. However, as the feature size shrinks, e.g., to  $0.09\mu$  and  $0.065\mu$ , static power has become a great challenge for current and future technologies. Based on the International Technology Roadmap for Semiconductors (ITRS) [30], Kim et al. report that subthreshold leakage power dissipation of a chip may exceed dynamic power dissipation at the 65nm feature size [38].

One of the main reasons causing the leakage power increase is increase of subthreshold leakage power. When technology feature size scales down, supply voltage and threshold voltage also scale down. Subthreshold leakage power increases exponentially as threshold voltage decreases. Furthermore, the structure of the short channel device lowers the threshold voltage even lower. In addition to subthreshold leakage, another contributor to leakage power is gate-oxide leakage power due to the tunneling current through the gate-oxide insulator. Since gate-oxide thickness will be reduced as the technology decreases, in nanoscale technology, gate-oxide leakage power may be comparable to subthreshold leakage power if not handled properly. However, we assume other techniques will address gate-oxide leakage; for example, high-k dielectric gate insulators may provide a solution to reduce gate-leakage [38]. Therefore, this thesis focuses on reducing subthreshold leakage power consumption.

In this dissertation, we provide novel circuit structure named "sleepy stack" as a new remedy for designers in terms of static power. The sleepy stack has a novel structure that combines the advantages of two major prior approaches, the sleep transistor technique and the forced stack technique. However, unlike the sleep transistor technique, the sleepy stack technique retains the original state; furthermore, unlike the forced stack technique, the sleepy stack technique can utilize high- $V_{th}$  to achieve more than two orders of magnitude leakage power reduction compared to the forced stack. Unfortunately, the sleepy stack technique rows with delay and area overheads. Therefore, the sleepy stack technique provides new Pareto points to designers who require ultra-low leakage power consumption and are willing to pay some area and delay cost. In this thesis, we explore the basic structure of the sleepy stack. Also, we study various sleepy stack circuits including generic logic circuits and memory. We discuss the advantages and disadvantages of the sleepy stack and a technique to reduce the delay overhead.

Along with the sleepy stack structure, we introduce in this dissertation an architectural level power reduction technique. One of the most effective dynamic power reduction techniques is lowering the supply voltage of CMOS transistors because the power consumption of CMOS transistors increases quadratically proportional to the supply voltage. However, lowering the supply voltage incurs an increase in transistor switching delays. Therefore,

designing CMOS circuits typically necessitates tradeoffs between performance (in terms of delay) and power consumption. Although CMOS circuits are governed by such tradeoffs, it is possible for a system to selectively lower supply voltage without compromising performance at the architectural level. The strategy is to lower supply voltage for circuits in non-critical paths while maintaining supply voltage for circuits in critical path(s); thus, available surplus slack in non-critical paths are removed. In our particular case, we observe that by pipelining the caches, we can obtain large surplus slack, which allows for large dynamic power savings. This new low-power cache technique is named Low-Power Pipelined Cache (LPPC). By apply sleepy stack instead of lowering supply voltage, LPPC can be used to save leakage power consumption.

#### 1.1 Problem Statement

This research work addresses new low power approaches for Very Large Scale Integration (VLSI) logic and memory. Power dissipation is one of the major concerns when designing a VLSI system. Until recently, dynamic power was the only concern. However, as the technology feature size shrinks, static power, which was negligible before, becomes an issue as important as dynamic power. Since static power increases dramatically (indeed, even exponentially) in nanoscale silicon VLSI technology, the importance of reducing leakage power consumption cannot be overstressed. A well-known previous technique called the sleep transistor technique cuts off  $V_{dd}$  and/or Gnd connections of transistors to save leakage power consumption. However, when transistors are allowed to float, a system may have to wait a long time to reliably restore lost state and thus may experience seriously degraded performance. Therefore, retaining state is crucial for a system that requires fast response even while in an inactive state. Our research provides new VLSI techniques that achieve ultra-low leakage power consumption while maintaining logic state, and thus can be used for a system with long inactive times but a fast response time requirement.

#### **1.2** Contributions

In this dissertation, we present two low-power techniques, (i) the sleepy stack technique for static power reduction and (ii) the low-power pipelined cache (LPPC) for dynamic and/or static power reduction. The two techniques provide new weapons to designers whose primary concern is low power.

The following items are the main contributions of this research:

- **Design of sleepy stack for logic circuits.** We develop a novel low-leakage technique we call "sleepy stack." The sleepy stack technique is applied to generic logic circuits, and we achieve between two and three orders of magnitude leakage power reduction compared to the best prior state saving technique we could find (namely, the forced stack technique).

- Design of a sleepy stack SRAM cell. Static Random Access Memory (SRAM) is a power hungry component in a VLSI chip. Therefore, we apply the sleepy stack technique to SRAM design. Since the sleepy stack technique comes with area and delay penalties, we explore many possible sleepy stack SRAM cell combinations and provide new Pareto points that can be used by designers who want extremely low leakage power consumption (and are willing to pay a cost of some area and/or delay increase).

- Design of a novel low power pipelined cache (LPPC). We design a novel lowpower pipelined cache (LPPC). LPPC applies pipelining to a cache while lowering supply voltage of a cache to reduce dynamic power or using sleepy stack SRAM to reduce leakage power. We also optimize the number of cache pipeline stages using a specific architecture that we explore.

- **Design of novel sleepy stack pipelined cache.** We design a novel sleepy stack pipelined cache. We utilize the LPPC to save leakage power consumption by using

sleepy stack SRAM. Although the sleepy stack SRAM shows some delay overhead, by using the LPPC we can hide the delay overhead, and thus we can achieve very low leakage cache power consumption with small performance overhead.

### 1.3 Thesis Organization

The thesis is organized into eleven chapters.

CHAPTER I: INTRODUCTION. This chapter introduces power consumption issues in VLSI. This chapter also summarizes the contributions of this thesis. Finally, this chapter explains organization of the thesis.

CHAPTER II: MOTIVATION. This chapter addresses our motivation for this research.

CHAPTER III: NOTATION AND BACKGROUND. This chapter explains important notation and background used throughout this dissertation.

CHAPTER IV: PREVIOUS WORK. This chapter describes previous work in power reduction research and explains key differences between our solutions and previous work.

CHAPTER V: SLEEPY STACK STRUCTURE. This chapter introduces the novel sleepy stack leakage reduction technique. First, the structure of the sleepy stack is described followed by a detailed explanation of sleepy stack operation. An analytical delay model of the sleepy stack is derived and compared to the forced stack technique using an inverter circuit.

CHAPTER VI: APPLYING SLEEPY STACK. This chapter explores various applications of the sleepy stack approach. The applications/uses include generic logic circuits and memory circuits. For each application/use of the sleepy stack, comparisons with the best known prior low-leakage techniques are carried out using benchmark circuits. We explain the experimental methodology used.

CHAPTER VII: SLEEPY STACK EXPERIMENTAL RESULTS. This chapter discusses the experimental results from various applications of the sleepy stack approach. The sleepy stack technique is empirically compared to well-known previous approaches. The comparisons are assessed in terms of area, dynamic power, static power and area while changing numerous VLSI and CMOS circuit parameters.

CHAPTER VIII: LOW-POWER PIPELINED CACHE (LPPC) ARCHITECTURE.

This chapter introduces our new dynamic power reduction technique "low-power pipelined cache" and explains low power mechanism of the LPPC. The pipelining techniques for LPPC are discussed, and lastly, this chapter explores pipelining penalties and the solutions of the LPPC.

CHAPTER IX: LOW-POWER PIPELINED CACHE (LPPC) EXPERIMENTAL SET-

UP AND RESULTS. This chapter covers experimental methodology and LPPC results. In the experimental methodology, processor and cache models are explained followed by the architectural configurations and benchmarks used to evaluate the LPPC approach. Finally, the chapter provides experimental results for the low-power pipelined cache architecture compared to a non-pipelined cache architecture as well as a low-voltage pipelined cache architecture.

CHAPTER X: SLEEPY STACK PIPELINED CACHE. This chapter discusses combining the sleepy stack technique and the low-power pipelined cache technique. The proposed cache structure is explained and explored in terms of performance and power.

CHAPTER XI: CONCLUSION. This chapter summarizes the major accomplishments of this thesis.

### **CHAPTER II**

### **MOTIVATION**

Historically, in the 1980's CMOS technology took over the mainstream of VLSI design because CMOS consumes far less power than its predecessors (nMOS, bipolar, etc.). Although this advantage still holds, power dissipation of CMOS has nonetheless become a problem.

For a long time, dynamic power accounted for more than 90% (typically, over 99%) of total chip power, and thus was frequently used as the metric for total power consumption for technologies  $0.18\mu$  and above. However, as technology scales down to tens of nanometers, leakage power becomes as important as dynamic power. Therefore, many ideas have been proposed to tackle the leakage power problem. Although cutting off transistors from power rails, e.g., using the sleep transistor technique, is one of the possible solutions, losing state during inactive mode incurs long wake-up time and thus may not be appropriate for a system that requires fast response times.

To provide a motivational scenario to illustrate the possible impact of this thesis, let us compare the impact of static (leakage) power consumption in the context of a cell phone example. We assume that in general, the cell phone we consider is always on (i.e., 24 hours a day). However, the actual usage time of the cell phone is very limited. If we assume a 500 minute calling plan with 500 minutes total used per month, the cell phone is active only 1.15% (500min/(30days \* 24hours \* 60min)) of the total on-time. This means that during rest – 98.85% of the time – the cell phone is non-active; however, due to static power consumption, during rest (standby) the cell phone still consumes energy and reduces battery life. In technology such as  $0.07\mu$ , the impact of leakage power is huge.

Let us consider an energy consumption scenario of a cell phone predicted based on

|             | *                   | r work that sa<br>forced stack) | ves state              | Our approach<br>(sleepy stack) |                       |                        |  |

|-------------|---------------------|---------------------------------|------------------------|--------------------------------|-----------------------|------------------------|--|

|             | Active<br>power (W) | Leakeage<br>power (W)           | Area (u <sup>2</sup> ) | Active<br>power (W)            | Leakeage<br>power (W) | Area (u <sup>2</sup> ) |  |

| 4 Inverters | 1.25E-06            | 9.81E-10                        | 5.97E+00               | 1.09E-06                       | 4.56E-12              | 9.03E+00               |  |

| 512B SRAM   | 5.22E-04            | 5.39E-06                        | 2.00E+01               | 5.80E-04                       | 3.24E-07              | 3.66E+01               |  |

**Table 1:** Power and area results from Chapter 7

**Table 2:** Energy consumption scenario of a cell phone  $(0.07\mu)$

|                             | Best prior work that saves state<br>(forced stack) |                       |                        |                       | Our approach<br>(sleepy stack) |                       |                        |                       |

|-----------------------------|----------------------------------------------------|-----------------------|------------------------|-----------------------|--------------------------------|-----------------------|------------------------|-----------------------|

|                             | Active<br>power (W)                                | Leakeage<br>power (W) | Area (u <sup>2</sup> ) | Energy (J)<br>(Month) | Active<br>power (W)            | Leakeage<br>power (W) | Area (u <sup>2</sup> ) | Energy (J)<br>(Month) |

| Processor<br>logic circuits | 1.38E-01                                           | 1.02E-01              | 6.61E+05               | 2.65E+05              | 1.47E-01                       | 5.74E-04              | 1.21E+06               | 5.87E+03              |

| 32KB SRAM                   | 5.54E-03                                           | 4.15E-02              | 6.61E+05               | 1.06E+05              | 6.09E-03                       | 2.44E-03              | 1.21E+06               | 6.44E+03              |

| Total                       | 1.43E-01                                           | 1.43E-01              | 1.32E+06               | 3.72E+05              | 1.53E-01                       | 3.01E-03              | 2.42E+06               | 1.23E+04              |

our experimental results which will be presented in Chapter 7. Specifically, Table 1 shows some specific results from Chapter 7 for  $0.07\mu$  technology at  $25^{\circ}C$ . Table 2 shows our hypothetical energy consumption scenario. We compare two different techniques which are the forced stack technique (best prior work that saves state) and the sleepy stack technique (our approach).

First, we assume a single chip containing an embedded processor core in  $0.07\mu$  technology. The chip largely consists of logic circuits and a 32KB SRAM; note that we exclude I/Os and the pad frame. Furthermore, we only consider here the digital chip; i.e., the liquid crystal display, Radio Frequency (RF) circuitry, etc., are all ignored.

Second, we assume that SRAM and logic circuits each occupy half of the digital chip area, respectively. We estimate 32KB SRAM area based on SRAM cell area which we will present in Chapter 7 – note that in all cases we exclude test, e.g., our SRAM does not include Built-In Self Test (BIST). The forced stack 32KB SRAM area is  $6.61 \times 10^5 \mu^2$ , and the sleepy stack SRAM area is  $1.21 \times 10^6 \mu^2$ . Then we estimate that the processor logic gates occupy the same amount of area as the 32KB SRAM as shown in the area columns of Table 2. Third, we also assume that at  $0.07\mu$  technology leakage power consumption is as much as active power consumption when we use the forced stack technique. We multiply forced stack leakage values from Table 1 by a factor (specifically, 939), so that forced stack leakage power becomes the same as forced stack active power, i.e., 143mW. Then we apply the same factor (939) to the sleepy stack leakage power from Table 1, resulting in sleepy stack leakage power of 3.01mW. In other words, while Table 1 is based on Berkeley Predicted Technology Model (BPTM) [7], we instead assume a scenario where leakage power equals active power (which is, we believe, a hypothetical situation we may possibly see in the future.)

Now, recalling that our cell phone is active 500 minutes per month and thus inactive 42700 minutes per month, we calculate forced stack digital chip energy per month as follows:

$$Energy1 = 143mW * (500 * 60sec) + 143mW * (42700 * 60sec)$$

(1)

$$= 37.2KJ \tag{2}$$

Similarly, we calculate sleepy stack digital chip energy per month as follows:

$$Energy2 = 153mW * (500 * 60sec) + 3.01mW * (42700 * 60sec)$$

(3)

$$= 1.23KJ \tag{4}$$

The result predicts that the ultra-low leakage power technology, i.e., sleepy stack, saves 30X total energy consumption compared to the best prior work, i.e., forced stack. Therefore, potentially, the ultra-low leakage power technique can extend by 30X the cell phone battery life in this motivational example. There is a cost for this 30X savings, however: note that the overall are increases 83% (from  $1.32mm^2$  to  $2.42mm^2$  – see Table 2).

Although there already exist many low-leakage techniques, the best prior low-leakage technique in terms of leakage power reduction, the sleep transistor technique, loses logic state during sleep mode. Therefore, the sleep transistor technique requires non-negligible

time to wake-up the device from the sleep mode. If we consider an emergency calling situation to use cell phone, this wake-up time may not be acceptable. Therefore, an ultra-low-leakage technique that can save state even in non-active mode can be quite important in nanoscale technology VLSI.

In this dissertation, we use circuit as well as architectural techniques to reduce leakage power consumption. Especially, our technique can retain logic state and thus fast response time can be achieved even during non-active mode. The technique can be applicable to generic logic circuits as well memory, i.e., SRAM, since our technique can retain state.

In this chapter, some motivation for the importance of this research is provided. In the next chapter, we explain expressions, notation and background important for this thesis.

## **CHAPTER III**

#### NOTATION AND BACKGOUND

In this chapter, we explain important notation and VLSI background used in this dissertation. First, we introduce subthreshold leakage power consumption on which our research focuses. Next, we explain the background underlying a particular leakage power model able to explain the stack effect, which is an important leakage reduction factor in our research. We then explain the body-bias effect. Furthermore, we explain subthreshold leakage power consumption of a conventional 6 Transistor (6-T) SRAM cell. Finally, we explain switching power and delay tradeoffs of CMOS circuits.

### 3.1 Leakage power

In this section, we explain notation and background relevant to leakage power consumption.

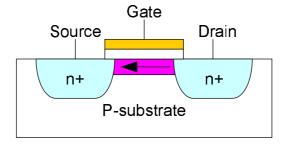

Figure 1: Subthreshold leakage of an nFET

Although dynamic power is dominant for technologies at  $0.18\mu$  and above, leakage (static) power consumption becomes another dominant factor for  $0.13\mu$  and below. One of the main contributors to static power consumption in CMOS is subthreshold leakage current shown in Figure 1, i.e., the drain to source current when the gate voltage is smaller than the transistor threshold voltage. Since subthreshold current increases exponentially as the threshold voltage decreases, nanoscale technologies with scaled down threshold voltages

will severely suffer from subthreshold leakage power consumption.

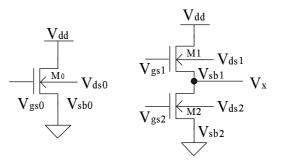

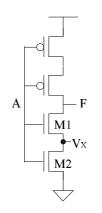

Figure 2: (a) A single transistor (left) and (b) stacked transistors (right)

Subthreshold leakage can be reduced by stacking transistors, i.e., taking advantage of the so-called "stack effect" [34]. The stack effect occurs when two or more stacked transistors are turned off together; the result is reduced leakage power consumption.

Let us explain an important stack effect leakage reduction model. The model we explain here is based on the leakage models in [34] and [46]. For a turned off single transistor shown in Figure 2(a), leakage current ( $I_{sub0}$ ) can be expressed as follows:

$$I_{sub0} = A e^{\frac{1}{nV_{\theta}} (V_{gs0} - V_{th0} - \gamma V_{sb0} + \eta V_{ds0})} (1 - e^{-V_{ds0}/V_{\theta}})$$

(5)

$$= A e^{\frac{1}{nV_{\theta}}(-V_{th0}+\eta V_{dd})} \tag{6}$$

where  $A = \mu_0 C_{ox} (W/L_{eff}) V_{\theta}^2 e^{1.8}$ , *n* is the subthreshold swing coefficient, and  $V_{\theta}$  is the thermal voltage.  $V_{gs0}$ ,  $V_{th0}$ ,  $V_{bs0}$  and  $V_{ds0}$  are the gate-to-source voltage, the zero-bias threshold voltage, the base-to-source voltage and the drain-to-source voltage, respectively.  $\gamma$  is the body-bias effect coefficient, and  $\eta$  is the Drain Induced Barrier Lowering (DIBL) coefficient.  $\mu$  is zero-bias mobility,  $C_{ox}$  is the gate-oxide capacitance, W is the width of the transistor, and  $L_{eff}$  is the effective channel length [60]. (Note that throughout this thesis we assume  $\mu_n = 2\mu_p$ , i.e., nMOS carrier mobility is twice pMOS carrier mobility. Also note that we use a W/L ratio based on a actual transistor size, in which way a W/L ratio properly characterizes circuit models used in this thesis.) We assume  $1 >> e^{-V_{ds0}/V_{\theta}}$ .

Let us assume that the two stacked transistors  $(M_1 \text{ and } M_2)$  in Figure 2(b) are turned off. We also assume that the transistor width of each of  $M_1$  and  $M_2$  is the same as the transistor width of  $M_0$  ( $W_{M0} = W_{M1} = W_{M2}$ ). Two leakage currents  $I_{sub1}$  of the transistor  $M_1$  and  $I_{sub2}$  of the transistor  $M_2$  can be expressed as follows:

$$I_{sub1} = A e^{\frac{1}{nV_{\theta}}(V_{gs1} - V_{th0} - \gamma V_{sb1} + \eta V_{ds1})} (1 - e^{-V_{ds1}/V_{\theta}})$$

(7)

$$= A e^{\frac{1}{nV_{\theta}}(-V_{x}-V_{th0}-\gamma V_{x}+\eta(V_{dd}-V_{x}))}$$

(8)

$$I_{sub2} = A e^{\frac{1}{nV_{\theta}}(V_{gs2} - V_{th0} - \gamma V_{sb2} + \eta V_{ds2})} (1 - e^{-V_{ds2}/V_{\theta}})$$

(9)

$$= A e^{\frac{1}{nV_{\theta}}(-V_{th0}+\eta V_x)} (1 - e^{-V_x/V_{\theta}}).$$

(10)

where  $V_x$  is the voltage at the node between M1 and M2, and we assume  $1 >> e^{-V_{ds1}/V_{\theta}}$ .

Now consider leakage current reduction between  $I_{sub0}$  and  $I_{sub1} (= I_{sub2})$ . The reduction factor X can be expressed as follows:

$$X = \frac{I_{sub0}}{I_{sub1}} = \frac{Ae^{\frac{1}{nV_{\theta}}(-V_{th0} + \eta V_{dd})}}{Ae^{\frac{1}{nV_{\theta}}(-V_x - V_{th0} - \gamma V_x + \eta (V_{dd} - V_x))}} = e^{\frac{V_x}{nV_{\theta}}(1 + \gamma + \eta)}$$

(11)

$V_x$  in Equation 11 can be derived by letting  $I_{sub1} = I_{sub2}$  and by solving the following equation:

$$1 = e^{\frac{1}{nV_{\theta}}(\eta V_{dd} - V_x(1+2\eta+\gamma))} + e^{-V_x/V_{\theta}}$$

(12)

If all the parameters are known, we can calculate stack effect leakage power reduction using Equations 11 and 12. As an example, we consider leakage model parameter values targeting  $0.5\mu$  technology in Table 3 obtained from [34]. From Equation 12, we calculate

| Tuble 5. Dealage model parameters ( $0.5\mu$ teen) |         |

|----------------------------------------------------|---------|

| Parameter                                          | Value   |

| $V_{dd}$                                           | 1V      |

| $V_{th}$                                           | 0.2V    |

| n (subthreshold slope coeffcient)                  | 1.5     |

| $\eta$ (DIBL coeffcient)                           | 0.05V/V |

| $\gamma$ (body-bias effect coeffcient)             | 0.24V/V |

**Table 3:** Leakage model parameters  $(0.5\mu \text{ tech})$

$V_x = 0.0443V$ , and from Equation 11, we obtain leakage reduction factor X = 4.188.

Although the reduction is 4.188X at  $0.5\mu$  technology, the reduction increases at nanoscale technology because  $\eta$  increases as technology feature size shrinks.

Threshold voltage of a CMOS transistor can be controlled using body bias. In general, we apply  $V_{dd}$  to the body (e.g., an n-well or n-tub) of pMOS and apply Gnd to a body (e.g., p-well or p-substrate) of nMOS. This condition, in which source voltage and body voltage of a transistor are the same, is called Zero-Body Bias (ZBB). Threshold voltage at ZBB is called ZBB threshold voltage. When body voltage is lower than source voltage by biasing negative voltage to body, this condition is called Reverse-Body Bias (RBB). Alternatively, when body voltage is higher than source voltage by biasing positive voltage to a transistor, threshold voltage increases, and when FBB applied to a transistor, threshold voltage increases, and when FBB applied to a transistor, threshold voltage decreases. This phenomenon is called body-bias effect, and this is frequently used to control threshold voltage dynamically [72].

In this section, Section 3.1, we explained subthreshold leakage power consumption, the stack effect, and body-bias effects which can alter subthreshold leakage power consumption. In the next section, we explain leakage current of an SRAM cell.

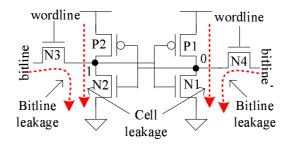

### 3.2 SRAM cell leakage paths

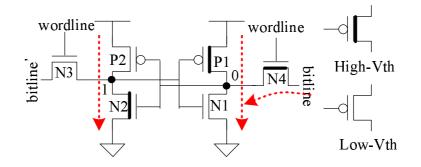

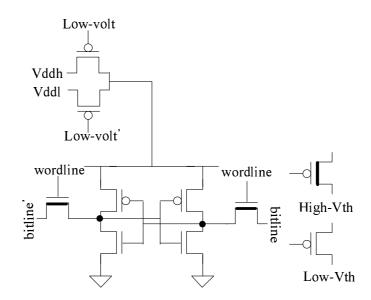

Figure 3: SRAM cell leakage paths

In this section, we explain the major subthreshold leakage components in a 6-T SRAM cell. The subthreshold leakage current in an SRAM cell is typically categorized into two kinds [37] as shown in Figure 3: (i) cell leakage current that flows from  $V_{dd}$  to Gnd internal

to the cell and (ii) bitline leakage current that flows from bitline (or bitline') to *Gnd*.

Although an SRAM cell has two bitline leakage paths, the bitline leakage current and bitline ' leakage current differ according to the value stored in the SRAM bit. If an SRAM cell holds '1' as shown in Figure 3, the bitline leakage current passing through N3 and N2 is effectively suppressed due to two reasons. First, after precharging bitline and bitline' both to '1,' the source voltage and the drain voltage of N3 are the same, and thus potentially no current flows through N3. Second, two stacked and turned off transistors (N2 and N3) induce the stack effect. Meanwhile, for this case where the SRAM bit holds value '1,' a large bitline' leakage current flows passing through N4 and N1. If, on the other hand, the SRAM cell holds '0,' a large bitline leakage current flows while bitline' leakage accounts for approximately 35% of SRAM cell leakage power consumption.

In this section, Section 3.2, we explain the two major types of leakage paths in an SRAM cell (cell leakage and bitline leakage). In next section, we explain tradeoffs between switching power and delay.

### 3.3 Switching power and delay tradeoffs

In this section, we explain tradeoffs between switching power and delay.

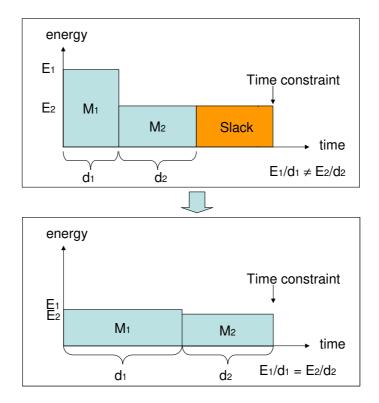

In CMOS, power consumption consists of leakage power and dynamic power – note that dynamic power includes both switching power and short-circuit power. Switching power is consumed when a gate charges its output load capacitance, and short-circuit power is consumed when a pull-up network and a pull-down network are on together for an instant while transistors are turning on and off. For  $0.18\mu$  channel lengths and above, leakage power is very small compared to dynamic power. Furthermore, short-circuit power is also less than 10% of the dynamic power for a typical CMOS design, and the ratio between dynamic power and short-circuit power does not change as long as the ratio between supply voltage and threshold voltage remains the same [50]. Since, for  $0.18\mu$  and above, short-circuit power and leakage power are relatively small compared to switching power, CMOS power consumption of a particular CMOS gate under consideration can be represented by the following switching power ( $P_{switching}$ ) equation for  $0.18\mu$  and above:

$$P_{switching} = p_t C_L V_{dd}^2 f \tag{13}$$

where  $C_L$ ,  $V_{dd}$ , and f denote the load capacitance of a CMOS gate, the supply voltage and the clock frequency, respectively [15]. Notation  $p_t$  denotes the switching ratio of a gate output; this switching ratio represents the number of times the particular gate's output changes from Gnd to  $V_{dd}$  per second – please note that when output capacitance discharges from  $V_{dd}$  to Gnd, switching power is not consumed because power from  $V_{dd}$  is not used (e.g., discharging to Gnd does not consume battery power). The switching ratio varies according to the input vectors and benchmark programs, and thus an average value of each benchmark may be used as a switching ratio.

Equation 13 shows that lowering  $V_{dd}$  decreases CMOS switching power consumption quadratically. However, this power reduction unfortunately entails an increase in the gate delay in a CMOS circuit as shown in following approximated equation:

$$T_d \propto \frac{V_{dd}}{(V_{dd} - V_{th})^{\alpha}} \tag{14}$$

where  $T_d$ ,  $V_{th}$ , and  $\alpha$  denote the gate delay in a CMOS circuit, the threshold voltage and velocity saturation index of a transistor, respectively. It is well-known that while  $\alpha$  has values close to 2 for above  $2.0\mu$ , for  $0.25\mu \alpha$  is between 1.3 and 1.5, and for below  $0.1\mu \alpha$  is close to 1 [35], [59]. However, instead of scaling down a  $\alpha$  value along with the technology feature size, CMOS technology may take a constant  $\alpha$  value to avoid the hotcarrier related problem [59]. A constant  $\alpha$  value could be accomplished by changing  $V_{th}$ because  $\alpha$  is a function of gate-source voltage [8]. If we scale down  $V_{dd}$ , switching power in Equation 13 decreases, while the gate delay in Equation 14 increases. Therefore, CMOS circuit speed can be traded with switching power consumption as shown in Equations 13 and 14.

When there exist tradeoffs between multiple criteria, e.g., power and delay, we may say one design is better than another design in specific criteria. The point of design space is called a Pareto point if there is no point with one or more inferior objective [40].

In this thesis we estimate leakage power consumption by measuring static power when transistors are not switching. Furthermore, we estimate active power consumption by measuring power when transistors are switching. This active power include dynamic power consumption and leakage power consumption.

In this chapter we explained important notation and VLSI background used in this thesis. In the next section, we explain previous low-power research related to our research.

### **CHAPTER IV**

#### **PREVIOUS WORK**

In this chapter, we review important prior work that is closely related to our research. Furthermore, the previous work is compared to our research. First we explore the prior work targeting leakage power reduction, and then we finish by studying previous techniques relevant to low-power pipelined caches.

#### 4.1 Static Power Reduction VLSI Research

In this section, we discuss previous low-power techniques that primarily target reducing leakage power consumption of CMOS circuits. Techniques for leakage power reduction can be grouped into two categories: (i) state-saving techniques where circuit state (present value) is retained and (ii) state-destructive techniques where the current Boolean output value of the circuit might be lost [38]. A state-saving technique has an advantage over a state-destructive technique in that with a state-saving technique the circuitry can immediately resume operation at a point much later in time without having to somehow regenerate state. We characterize each low-leakage technique according to this criterion. We study low-leakage techniques for generic logic circuits followed by low-leakage SRAM designs separately.

#### 4.1.1 Static Power Reduction Research for Generic Logic Circuits

This section explains previously proposed low-leakage techniques for generic logic circuits. As introduced, previously proposed work can be divided into techniques that either (i) save state or (ii) destroy state. Although our research focuses on techniques which save state, we also review the state-destructive techniques for the purposes of comparison.

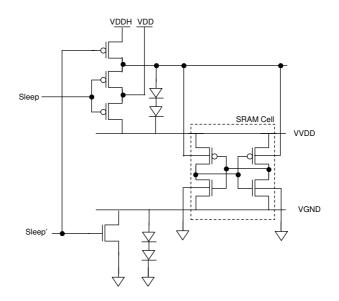

#### 4.1.1.1 Sleep transistor

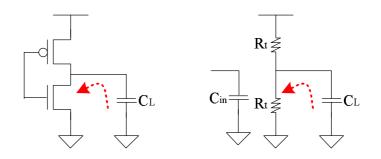

Figure 4: Sleep transistor technique

State-destructive techniques cut off transistor (pull-up or pull-down or both) networks from supply voltage or ground using sleep transistors [45]. These types of techniques are also called gated- $V_{dd}$  and gated-Gnd (note that a gated clock is generally used for dynamic power reduction). Motoh et al. propose a technique they call Multi-Threshold-Voltage CMOS (MTCMOS) [45], which adds high- $V_{th}$  sleep transistors between pull-up networks and  $V_{dd}$  and between pull-down networks and ground as shown in Figure 4 while logic circuits use low- $V_{th}$  transistors in order to maintain fast logic switching speeds. The sleep transistors are turned off when the logic circuits are not in use. By isolating the logic networks using sleep transistors, the sleep transistor technique dramatically reduces leakage power during sleep mode. However, the additional sleep transistors increase area and delay. Furthermore, the pull-up and pull-down networks will have floating values and thus will lose state during sleep mode. These floating values significantly impact the wakeup time and energy of the sleep technique due to the requirement to recharge transistors which lost state during sleep (this issue is nontrivial, especially for registers and flip-flops).

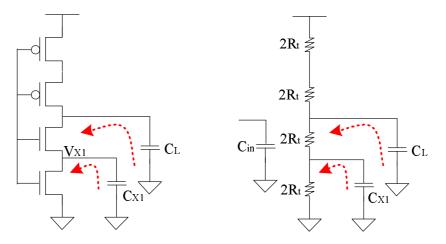

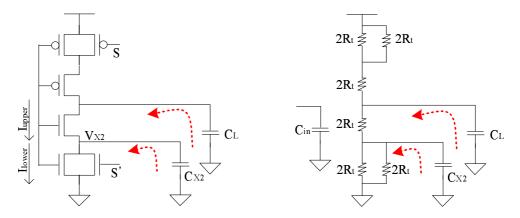

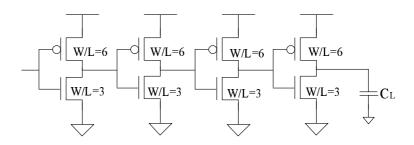

#### Comparison with prior work using sleep transistors

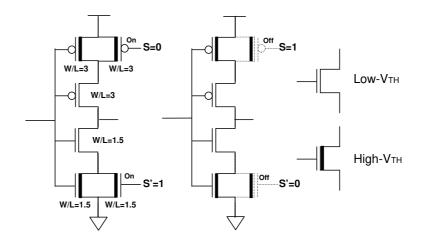

The sleep transistor technique and the sleepy stack technique both achieve roughly the same (100X or more) static power savings over conventional CMOS. However, unlike the

sleep transistor technique, the sleepy stack technique saves logic state during low leakage mode (sleep mode), and this is a significant advantage over the state-destructive sleep transistor technique. The sleep transistor technique requires non-negligible power consumption to restore lost state. Further, the wake-up time of the sleep transistor technique is significant, while the sleepy stack technique needs only a very small extra wake-up time (a few clock cycles).

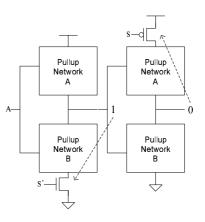

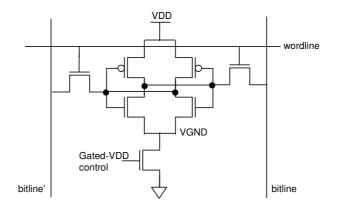

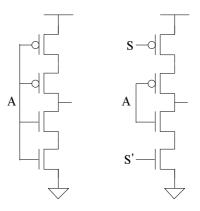

4.1.1.2 Zigzag

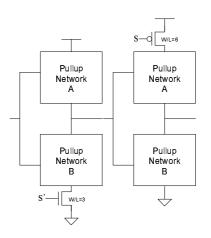

Figure 5: Zigzag technique

To reduce the wake-up cost of the sleep transistor technique, the zigzag technique is introduced [41]. The zigzag technique reduces the wake-up overhead by choosing a particular circuit state (e.g., corresponding to a "reset") and then, for the exact circuit state chosen, turning off the pull-down network for each gate whose output is high while conversely turning off the pull-up network for each gate whose output is low. For example, the zigzag technique in Figure 5 assume that the input 'A' is asserted such that the output values result as shown in the figure. If the output is '1,' then a pull-down sleep transistor is applied; if the output is '0,' then a pull-up sleep transistor is applied. By applying, prior to going to sleep, the particular input pattern chosen prior to chip fabrication, the zigzag technique retains the particular state chosen prior to chip fabrication, any other arbitrary state during regular operation is lost in

#### power-down mode.

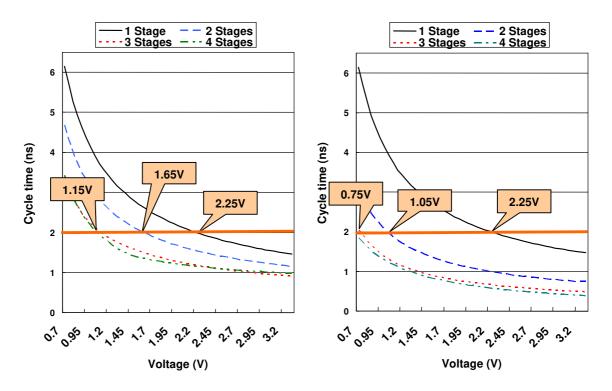

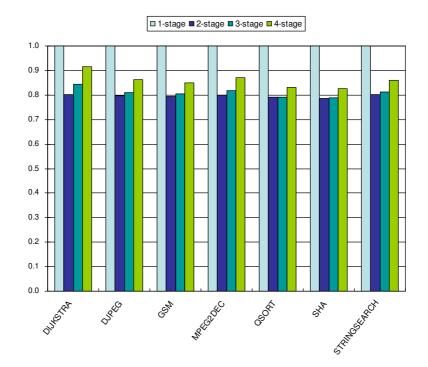

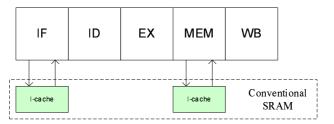

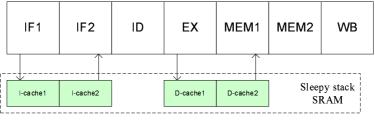

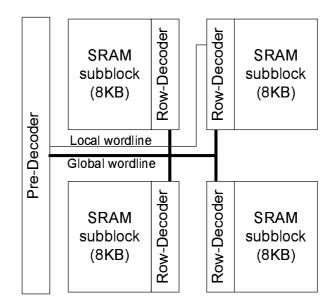

#### Comparison with prior work using zigzag