# Sliding-Mode Control Design of a Boost–Buck Switching Converter for AC Signal Generation

Domingo Biel, Member, IEEE, Francesc Guinjoan, Member, IEEE, Enric Fossas, and Javier Chavarria

Abstract—This paper presents a sliding-mode control design of a boost-buck switching converter for a voltage step-up dc-ac conversion without the use of any transformer. This approach combines the step-up/step-down conversion ratio capability of the converter with the robustness properties of sliding-mode control. The proposed control strategy is based on the design of two sliding-control laws, one ensuring the control of a full-bridge buck converter for proper dc-ac conversion, and the other one the control a boost converter for guaranteeing a global dc-to-ac voltage step-up ratio. A set of design criteria and a complete design procedure of the sliding-control laws are derived from small-signal analysis and large-signal considerations. The experimental results presented in the paper evidence both the achievement of step-up dc-ac conversion with good accuracy and robustness in front of input voltage and load perturbations, thus validating the proposed approach.

*Index Terms*—boost-buck switching converter, dc-ac step-up conversion, sliding-mode control.

### I. INTRODUCTION

NINTERRUPTIBLE power supplies (UPS) or ac power sources constitute the most classical applications of power conditioning systems designed to supply an ac load from a dc source. The design of these systems involves the design of both a high-efficiency switching power stage circuit and a control subsystem in order to achieve a suitable dc–ac conversion in the desired output frequency range. Concerning the generated output voltage, low harmonic distortion, and robustness in front of input voltage and load perturbations (evaluated in terms of fast transient behavior and steady-state accuracy) are commonly requested features.

Usually, the power stage circuits in charge of performing the dc–ac conversion are based on a full-bridge buck switching converter topology. Regarding the control subsystem, several control schemes oriented to ensure a proper tracking of an external sinusoidal reference have been suggested. For instance, many tracking control techniques based on high-frequency pulsewidth

Manuscript received July 29, 2003; revised December 13, 2003. This work was supported in part by the Spanish Ministry of Science and Technology and in part by the European Union from FEDER funds under Grant DPI2000-1503-CO3-2,3 and Grant DPI2003-08887-CO3-01. This paper was recommended by Associate Editor M. K. Kazimierczuk.

- D. Biel is with the Departamento d'Enginyeria Electrònica, Escola Politècnica Superior d'Enginyeria de Vilanova la Geltrú, Barcelona 08800, Spain (e-mail: biel@eel.upc.es).

- J. Chavarria is with Sony Corporation, Barcelona 98232, Spain.

- F. Guinjoan is with the Departamento d'Enginyeria Electrónica, Escola Tècnica Superior d'Enginyers de Telecomunicació, Barcelona 08034, Spain (e-mail: guinjoan@eel.upc.es)

- E. Fossas is with the Institut d'Organització i Control de Sistemes Industrials, 08028 Barcelona, Spain (e-mail: fossas@ioc.upc.es)

Digital Object Identifier 10.1109/TCSI.2004.832803

modulation (PWM) have been proposed in the past for buckbased dc-ac converters [1]-[5]. However, these control strategies are designed by means of a power-stage model, thus leading to output waveforms being sensitive to power stage parameter variations, such as the output load. On the other hand, slidingmode control techniques have been proposed as an alternative to PWM control strategies in dc-dc switching regulators since they make these systems highly robust to perturbations, namely variations of the input voltage and/or in the load [6]-[8]. Taking advantage of these properties, sliding-mode control has also been applied to the design of high-efficiency buck-based dc-ac converters, where a switching dc-dc converter is forced to track, by means of an appropriate sliding-mode control action, an external sinusoidal [12]-[18]. Nevertheless, the full-bridge buck converter topology limits the ac output voltage amplitude to values lower than the dc input voltage, except in the vicinity of the output filter resonant frequency [19].

When ac amplitudes higher than the dc input voltage are required, the classical design combines a step-up turns ratio transformer and a buck converter in the dc—ac conversion circuit. However, this approach entails some drawbacks related to the transformer nonidealities (leakage inductances, limited bandwidth,...) and increases the weight and size of the converter circuit. Alternatively, transformerless step-up conversion topologies could be considered. Nonetheless, although sliding-mode control has been successfully applied to switching dc—dc converters exhibiting a step-up voltage conversion ratio such as the boost converter [8], [22], the coupled-inductor Čuk converter [9] and the boost—buck converter [10], [11], preliminary studies have shown the analytical difficulties in applying sliding-mode control techniques to these power stages for a dc—ac step-up conversion ratio [20], [21].

In order to overcome the drawbacks exposed above, this work focuses on a sliding-mode control design for a cascade connection between a boost dc–dc converter with a full-bridge buck inverter, as a transformerless power stage for a dc-ac step-up conversion, this being referred as a boost-buck dc-ac converter. Starting from the sliding-control-law design proposed by Carpita et al. [12] for a full-bridge buck-based dc-ac conversion, the work here reported presents how a well-known linear sliding-control law for a single boost dc-dc converter has to be designed when the previous cascade connection conversion is considered. Therefore, by properly combining the step-up/step-down conversion ratio of the boost-buck dc-ac converter with the robustness properties of sliding-mode control, a step-up dc-ac voltage conversion robust in front of input voltage and/or load perturbations can be generated in a large frequency range without the use of any transformer.

1057-7122/04\$20.00 © 2004 IEEE

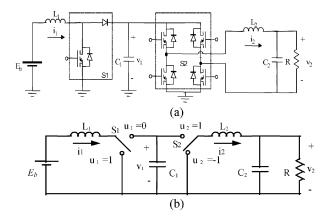

Fig. 1. (a) Cascade connection of a boost converter with a full-bridge buck inverter. (b) Circuit model.

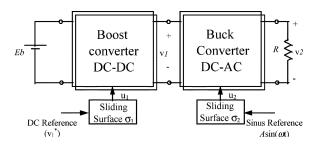

Fig. 2. Block diagram of a boost-buck dc-ac converter.

The paper is organized as follows. The next section presents the boost–buck dc–ac converter sliding-control strategy. Collecting the results of previous studies [12]–[19], Section III designs a sliding-control law of the buck stage, whereas Section IV focuses on a complete design procedure for the boost one. Finally, the last two sections present both simulation and experimental results validating the approach, and the conclusions of this work.

#### II. BOOST-BUCK SLIDING-CONTROL STRATEGY

Fig. 1(a) shows the boost–buck dc–ac converter circuit consisting in the cascade connection of a boost dc–dc converter with a full-bridge buck inverter. For analysis purposes, the converter can be represented by the circuit model shown in Fig. 1(b), where S1 is a conventional power switch and S2, corresponds to the full bridge switch to ensure the bipolarity of the ac output.

If  $u_1$  and  $u_2$  stand for the control signals of S1 and S2, respectively, the system can be represented by the following set of differential equations:

$$\begin{cases}

L_1 \frac{di_1}{dt} = E_b - v_1 \cdot (1 - u_1) \\

C_1 \frac{dv_1}{dt} = i_1 \cdot (1 - u_1) - i_2 \cdot u_2 \\

L_2 \frac{di_2}{dt} = v_1 \cdot u_2 - v_2 \\

C_2 \frac{dv_2}{dt} = i_2 - \frac{v_2}{R}

\end{cases}$$

(1)

where  $u_1 \in \{0,1\}$  and  $u_2 \in \{-1,1\}$ . As shown in Fig. 2, this work considers the design of two sliding-mode control laws for the  $u_1$  and  $u_2$  variables.

Recalling the results of previous studies [10]–[17], a first sliding-control law will be designed to control the full bridge

switch of the buck stage (control variable  $u_2$ ) for tracking an external sinusoidal reference, thus providing a dc—ac conversion. A second law will be designed to control the dc—dc boost stage (control variable  $u_1$ ) in order to set the intermediate voltage  $v_1$  at a large enough value to ensure a global ac output voltage amplitude to dc input voltage step-up ratio.

The design of the sliding-control laws will be carried out by applying the equivalent control concept [6], [7]. This technique can be summarized in the following three steps for the case of one control variable u.

- The first step is the choice of a switching surface  $\sigma(x,t)=0$  (where x is the system state vector) that provides the desired asymptotic behavior.

- Obtaining the equivalent control  $u_{\rm eq}$  by applying the invariance condition  $(d\sigma/dt)|_{\sigma=0}=0$  constitutes the second step.

The existence of the equivalent control  $u_{\rm eq}$  assures the feasibility of a sliding motion over the switching surface  $\sigma(x,t)=0$ . On the other hand, besides describing the averaged dynamic behavior of the power stage over the switching surface, the equivalent control enables obtaining the sliding domain, given by

$$\min \{u^-, u^+\} < u_{eq} < \max \{u^-, u^+\}$$

where  $u^-$  and  $u^+$  are the control values for  $\sigma < 0$  and  $\sigma > 0$  respectively. The sliding domain is the state plane region where the sliding motion is ensured.

• Finally, the control law is obtained by guaranteeing the Lyapunov stability criteria, i.e.,  $d\sigma^2/dt < 0$ .

According to the aforementioned three steps, the design procedure of the two sliding-control laws is given in the following sections.

#### III. DC-AC BUCK STAGE SLIDING-CONTROL DESIGN

There are several works reported in the literature dealing with sliding control of buck-based dc-ac converters [12]–[19]. In order to track a user-defined sinusoidal voltage reference  $V_{\rm ref}(t) = A \cdot \sin(\omega \, t)$  at the buck stage output, i.e.  $v_2 = V_{\rm ref}(t)$ , the following switching surface and the corresponding control law proposed by Carpita *et al.* [15] is adopted in this paper:

$$\sigma_2(v_2, t) = a_1 \cdot (V_{\text{ref}}(t) - v_2) + a_2 \cdot \left(\frac{dV_{\text{ref}}(t)}{dt} - \frac{dv_2}{dt}\right) \tag{2}$$

where  $a_1 > 0$  and  $a_2 > 0$  are the design parameters. The sliding motion over the switching surface is given by

$$\sigma_2(v_2, t) = 0 \Rightarrow v_2(t) = V_{\text{ref}}(t) + \mu \cdot e^{-a_1 \cdot t/a_2}$$

(3)

thus leading to the desired steady-state behavior. As (3) points out, the sliding-mode dynamic behavior depends on the  $a_2/a_1$  time constant, which has to be as low as possible; however, as it is reported by the authors, if the time constant is too low, the state vector can leave the switching surface due to the bounds on control. A complete set of design considerations of these switching surface parameters can be found in [15].

The corresponding equivalent control resulting from the application of the invariance condition to  $\sigma_2(v_2, t)$  is given by

$$\frac{d\sigma_2}{dt} = 0 \Rightarrow u_{2\text{eq}} = \frac{L_2 C_2}{v_1} \left[ \frac{a_1}{a_2} \left( \frac{dV_{\text{ref}}}{dt} - \frac{dv_2}{dt} \right) + \frac{d^2 V_{\text{ref}}}{dt^2} + \frac{v_2}{L_2 C_2} + \frac{1}{RC_2} \frac{dv_2}{dt} \right] \tag{4}$$

whereas the sliding domain can be obtained by imposing  $\min \{u^-, u^+\} < u_{2eq} < \max \{u^-, u^+\}$ , or equivalently

$$-1 < u_{2eq} < 1.$$

(5)

Finally, the power converter will reach the sliding surface if  $d\sigma_2^2/dt < 0$ , this leading to the following switching control law:

$$u_2 = \begin{cases} +1, & \text{if } \sigma_2 > 0 \\ -1, & \text{if } \sigma_2 < 0. \end{cases}$$

(6)

## A. Steady-State Design Constraints

In the subsequent developments the sub-index "ss" stands for steady-state variables. In accordance to the sliding-mode control theory, if the sliding domain is preserved the previous control law will lead the buck stage to the desired steady-state sliding motion, where the following relation holds:

$$v_{2ss}(t) = V_{ref}(t) = A \cdot \sin(\omega t). \tag{7}$$

The design must evidently preserve the steady-state sliding domain of the buck power stage which can be deduced by restricting expressions (4) and (5) to the steady-state behavior given by (7). Accordingly, (4) can be written as

$$u_{2\text{eqss}} = \frac{L_2 C_2}{v_{1\text{ss}}} \left[ \frac{d^2 V_{\text{ref}}}{dt^2} + \frac{1}{RC_2} \frac{dV_{\text{ref}}}{dt} + \frac{V_{\text{ref}}}{L_2 C_2} \right].$$

(8)

From (5), (7), and (8), it can be easily proved that the steady-state sliding domain of the buck power stage is given by [17]

$$-v_{1ss} < \frac{L_2}{R} \cdot \frac{dv_{2ss}}{dt} + (1 - L_2 \cdot C_2 \cdot \omega^2) \cdot v_{2ss} < v_{1ss}$$

(9)

or equivalently, according to (7)

$$\frac{A}{v_{1\rm ss}} < \gamma(\omega) \tag{10}$$

where

$$\gamma(\omega) = \frac{1}{L_2 \cdot C_2} \cdot \frac{1}{\sqrt{\frac{\omega^2}{(R \cdot C_2)^2} + \left(\omega^2 - \frac{1}{L_2 \cdot C_2}\right)^2}}$$

(11)

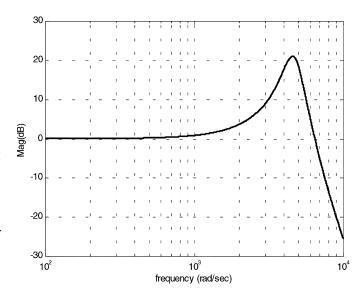

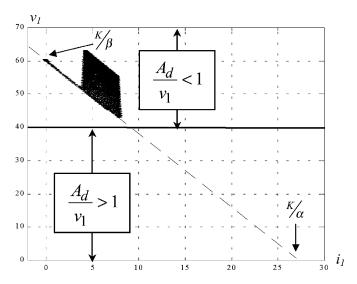

is the frequency response of the buck converter output filter, being  $\omega$  the desired output frequency. Fig. 3 shows the plot of the steady-state sliding domain boundary given by (10)–(11) for fixed values of  $L_2$ ,  $C_2$  and R.

From this plot, the following conclusions can be drawn:

Fig. 3. Gain Bode diagram of  $\gamma$  ( $\omega$ ). Parameters:  $L_2=750~\mu\text{H}, C_2=60~\mu\text{F}$  and  $R=10~\Omega$

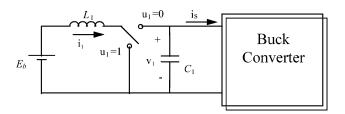

Fig. 4. Definition of the current  $i_S$ .

- The steady-state sliding regime is ensured for the values of  $A/v_{\rm 1ss}$  lying below the plot of the frequency response of the buck converter output filter. It can be noticed that below the resonant frequency the ratio  $A/v_{\rm 1ss}$  must verify  $A/v_{\rm 1ss} \leq 1$ , in agreement with the step-down characteristic of the buck switched converter.

- If load variations are considered, the design has to take into account the most restrictive sliding domain that corresponds, according to (11), to the minimum load value [19].

It can be pointed out that the steady-state average value of the boost output voltage,  $v_{1\rm ss}$ , must be time-varying. This statement can be proved by analyzing the boost output current (or, equivalently, the buck input one), referred as  $i_S$  and defined as shown in Fig. 4.

According to (1), this current is given by

$$i_S = u_2 \cdot i_2. \tag{12}$$

Therefore, provided that the buck converter has reached its corresponding steady-state sliding motion, the steady-state boost output current can be written as

$$i_{\rm ss} = u_{\rm 2egss} \cdot i_{\rm 2ss}.\tag{13}$$

On the other hand, from (1), the following relation can be easily deduced assuming that the converter has reached the steady state:

$$i_{1ss} \cdot \left[ E_b - L_1 \cdot \frac{di_{1ss}}{dt} \right] = v_{1ss} \cdot \left[ C_1 \cdot \frac{dv_{1ss}}{dt} + i_{ss} \right].$$

(14)

If  $v_{\rm 1ss}$  is a constant value, then,  $i_{\rm 1ss}$  will be unbounded and the system will become unstable [21]. As a consequence, for the case of a design requiring  $A/v_{\rm 1ss} \leq 1$ , two main constraints affecting the boost output voltage  $v_{\rm 1ss}$  can be highlighted from the previous steady-state analysis, namely, the following.

- Referring to Fig. 1, if an amplitude A higher than the dc input voltage  $E_b$  is desired, the boost stage would carry out a large enough step-up voltage ratio  $v_1/E_b$ .

- Since the voltage  $v_{\rm 1ss}$  is time varying so is the ratio  $A/v_{\rm 1ss}$ . This ratio must be kept into the boundaries of the buck stage sliding domain, thus overcoming the loss of the buck stage sliding motion.

As a result, the boost stage sliding control will be designed in compliance with these constraints, as it is developed in the following section.

# IV. BOOST STAGE SLIDING-CONTROL DESIGN

### A. Switching Surface, Sliding Domain and Control Law

Referring to Fig. 4 and according to (1), the boost stage dynamics can be modeled by the following set of differential equations:

$$\begin{cases} L_1 \frac{di_1}{dt} = E_b - v_1 \cdot (1 - u_1) \\ C_1 \frac{dv_1}{dt} = i_1 \cdot (1 - u_1) - i_S \end{cases}$$

(15)

where the current  $i_S$  is given by (12).

The following switching surface, previously reported in the literature for controlling the dc-dc boost stages [8], [22], is adopted in this paper:

$$\sigma_1(i_1, v_1, t) = \alpha \cdot i_1 + \beta \cdot v_1 - \delta \cdot v_a - K = 0 \tag{16}$$

where  $dv_a/dt = v_1^* - v_1$ ,  $v_1^*$  is the desired dc steady-state value of the voltage  $v_1$  for a global  $A/E_b$  step-up conversion and  $(\alpha, \beta, \delta, K)$  are the sliding surface design parameters. The corresponding sliding motion is given by  $\sigma_1(i_1, v_1, t) = 0$ .

The equivalent control  $u_{1\rm eq}$  is obtained by applying the invariance condition, and can be expressed as

$$u_{1\text{eq}} = \frac{\alpha C_1(v_1 - E_b) - \beta L_1(i_1 - i_S) + L_1 C_1 \delta(v_1^* - v_1)}{\alpha C_1 v_1 - \beta L_1 i_1}$$

(17)

whereas the sliding domain can be deduced by imposing  $\min\{u^-,u^+\} < u_{1\mathrm{eq}} < \max\{u^-,u^+\}$ , or equivalently in this case  $0 < u_{1\mathrm{eq}} < 1$ , this leading to the following restrictions:

A.

$$\operatorname{sgn} \left[ \alpha C_1 v_1 - \beta L_1 i_1 \right] \cdot \left[ \alpha C_1 (v_1 - E_b) - \beta L_1 (i_1 - i_s) + L_1 C_1 \delta(v_1^* - v_1) \right] > 0.$$

B.

$$\operatorname{sgn}\left[\alpha C_1 v_1 - \beta L_1 i_1\right] \cdot \left[\alpha C_1 E_b - \beta L_1 i_S - L_1 C_1 \delta(v_1^* - v_1)\right] > 0.$$

Finally, the switching control law can be derived applying  $d\sigma_1^2/dt < 0$ , this resulting in

$$u_1 = \begin{cases} +1, & \text{if } \sigma_1 \cdot \left[ \frac{\alpha}{L_1} \cdot v_1 - \frac{\beta}{C_1} \cdot i_1 \right] < 0 \\ 0, & \text{if } \sigma_1 \cdot \left[ \frac{\alpha}{L_1} \cdot v_1 - \frac{\beta}{C_1} \cdot i_1 \right] > 0. \end{cases}$$

(18)

The parameters  $(\alpha, \beta, \delta, K)$  must be designed at least to keep the ratio  $A/v_1$  into the buck stage steady-state sliding domain given by (10)–(11). Since the output voltage amplitude A is fixed by the user, an analysis of the intermediate voltage  $v_1$  dynamic behavior in front of input voltage and load perturbations is mandatory. Accordingly, the following sections are oriented to deduce several design criteria for the parameters  $(\alpha, \beta, \delta, K)$  by considering the influence of small and large perturbations of either the input voltage or the load over voltage  $v_1$ .

# B. Design Criteria According to Small-Signal Dynamics Analysis

This case analyzes the dynamic behavior of the intermediate voltage  $v_1$  in front of small perturbations of the input voltage and the load, under the following assumptions.

- The power system dynamics remains on the sliding surfaces given by (2) and (16), therefore the expressions (4) and (17) corresponding to the equivalent controls prevail.

- The amplitude of the perturbations is small enough to approximate the dynamic behavior of the voltage  $v_1$  by a linear model.

Under these assumptions, the equivalent dynamics of the closed-loop boost stage can be described by

$$\begin{cases}

L_{1} \frac{di_{1}}{dt} = E_{b} - v_{1} \cdot (1 - u_{1eq}) \\

C_{1} \frac{dv_{1}}{dt} = i_{1} \cdot (1 - u_{1eq}) - i_{S} \\

\sigma_{1}(i_{1}, v_{1}, t) = \alpha \cdot i_{1} + \beta \cdot v_{1} - \delta \cdot v_{a} - K = 0

\end{cases}$$

(19)

where  $u_{1\mathrm{eq}}$  is given by (17), and in this case  $i_S = u_{2\mathrm{eq}} \cdot i_2$ , since the power system remains on the sliding surfaces. The small signal analysis is carried out in a conventional way, by splitting the variables into their dc–dc steady-state and their perturbed counterparts. In this sense, the small signal analysis corresponding to load perturbations can be carried out in terms of the buck input current  $i_S$ , since a load perturbation results in an input current one. Therefore, the variables of (19) can be written as

$$E_{b} = E_{b}^{*} + \hat{E}_{b}$$

$$i_{s} = i_{s}^{*} + \hat{i}_{s}$$

$$i_{1} = i_{1}^{*} + \hat{i}_{1}$$

$$v_{1} = v_{1}^{*} + \hat{v}_{1}$$

$$v_{a} = v_{a}^{*} + \hat{v}_{a}$$

$$u_{1eq} = u_{1eq}^{*} + \hat{u}_{1eq}$$

(20)

where, for any variable x,  $x^*$  and  $\hat{x}$  stands for the dc steady-state and the perturbed values of x respectively. The steady-state values can be deduced taking into account that both  $E_b^*$  and  $v_1^*$  as well as the load R and the desired sinusoidal output amplitude A are user-defined parameters. Accordingly, the dc steady-state

value of  $u_{1\text{eq}}^*$  corresponds to the equivalent steady-state duty-cycle of a boost converter and can be expressed as

$$u_{1\text{eq}}^* = \frac{v_1^* - E_b}{v_1^*} \tag{21}$$

whereas, according to (14),  $i_S^*$  is given by

$$i_S^* = \frac{A^2}{2Rv_1^*}.$$

(22)

At last,  $i_1^*$  can be deduced assuming no losses in the boost stage, i.e,

$$i_1^* = \frac{v_1^*}{E_b} i_S^* \quad \Leftrightarrow \quad i_1^* = \frac{A^2}{2RE_b}.$$

(23)

Finally, by replacing (20) into (19) and neglecting higher order terms of perturbed variables, the closed-loop system defined by (19) can be represented by the following linear one:

$$\begin{cases}

L_{1} \frac{d\hat{i}_{1}}{dt} = \hat{E}_{b} - \hat{v}_{1} + v_{1}^{*} \cdot \hat{u}_{1\text{eq}} + \hat{v}_{1} \cdot u_{1\text{eq}}^{*} \\

C_{1} \frac{d\hat{v}_{1}}{dt} = \hat{i}_{1} - i_{1}^{*} \cdot \hat{u}_{1\text{eq}} - \hat{i}_{1} \cdot u_{1\text{eq}}^{*} - \hat{i}_{S} \\

\frac{d\hat{v}_{a}}{dt} = -\hat{v}_{1} \\

\alpha \cdot \hat{i}_{1} + \beta \cdot \hat{v}_{1} - \delta \cdot \hat{v}_{a} = 0.

\end{cases}$$

(24)

The dynamic behavior of  $\hat{v}_1$  with respect to input voltage and load perturbations can be inferred from (21)–(24) and can be expressed in the form of the following closed-loop transfer functions:

$$G_i(s) = \frac{\hat{V}_1(s)}{\hat{I}_S(s)} = \frac{-2RE_b\alpha v_1^* s}{\Delta(s)}$$

(25a)

$$G_E(s) = \frac{\hat{V}_1(s)}{\hat{E}_b(s)} = \frac{\alpha A^2 s}{\Delta(s)}$$

(25b)

where

$$\Delta(s) = \left(2RE_b \alpha C_1 v_1^* - \beta L_1 A^2\right) s^2 + \left(2RE_b^2 \beta + \frac{\alpha A^2 E_b}{v_1^*}\right) s + 2RE_b^2 \delta.$$

(26)

As can be seen, these transfer functions exhibit one closed-loop zero at the origin, thus confirming the robust-ness of the sliding-control law in front of input voltage and current (i.e output load) step perturbations. Furthermore, these transfer functions can be used to derive the following design restrictions.

1) Small-Signal Stability: The poles must be located in the left-half plane, this leading to the following constraint:

$$\frac{A^2}{2RE_b^2v_1^*} \cdot (\delta \cdot L_1 \cdot v_1^* - \alpha \cdot E_b) < \beta < \alpha \cdot \frac{2RC_1 \cdot E_b \cdot v_1^*}{L_1 \cdot A^2}.$$

(27)

2) Overdamped Small-Signal Dynamics: In order to preserve the buck inverter steady-state sliding domain given by (10), it would be desirable to guarantee a slightly overdamped dynamics of  $v_1$  in front of input voltage and load perturbations. This design criterion requires the poles of the closed-loop

transfer functions (25a) and (25b) to be real, whatever the values of R and  $E_b$  are. According to (25a)–(25b) these poles are the roots of

$$[2RE_{b}\alpha C_{1}v_{1}^{*} - \beta L_{1}A^{2}]s^{2} + \left[2RE_{b}^{2}\beta + \frac{\alpha A^{2}E_{b}}{v_{1}^{*}} - \delta L_{1}A^{2}\right]s + 2RE_{b}^{2}\delta = 0 \quad (28)$$

which can be rewritten as 1 + F(s) = 0 where

$$F(s) = R \cdot \frac{\left[2E_b\alpha C_1 v_1^*\right] \cdot s^2 + \left[2E_b^2\beta\right] \cdot s + 2E_b^2\delta}{\left[-\beta L_1 A^2\right] \cdot s^2 + \left[\frac{\alpha A^2 E_b}{v_1^*} - \delta L_1 A^2\right] \cdot s}$$

(29)

therefore the root locus of F(s) in terms of the load parameter R will correspond to the roots of (28). Since the poles of F(s) given by  $\mathbf{s}=0$  and  $s=[(\alpha\cdot E_b)/(\beta\cdot L_1\cdot v_1^*)-\delta/\beta]$  are real, the root locus will lie on the real left-half plane axis (thus leading to an overdamped response) for any value of R if the zeros of F(s) are real as well. This condition can be accomplished if the design verifies

$$\beta^2 \ge \frac{4 \cdot \alpha \cdot C_1 \cdot v_1^* \cdot \delta}{E_b}.\tag{30}$$

3) Steady-State Design: The previous small-signal analysis can also be applied to infer additional design criteria when the power converter operates in steady-state. When the buck converter is in steady-state sliding motion, the output boost stage current  $i_{SS}$  is given by (13), which can be written from (1), (7)–(8), assuming that  $\hat{v}_{1\rm ss} \ll v_1^*$ , in terms of its dc and ac counterparts as

$$i_{\rm ss} = i_{\rm ss}^* + \hat{i}_{\rm ss}$$

where

$$i_{ss}^* = \frac{A^2}{2v_1^* R}$$

$$\hat{i}_{ss} = K(\omega) \cdot \sin(2\omega t + \theta)$$

$$K(\omega) = \frac{A^2}{2v_1^* R} \left[ (L_2 C_2 \omega)^2 + \left( \frac{L_2 \omega}{R} \right)^2 + \left( L_2 C_2 \omega^2 - 1 \right)^2 \left( 1 + R^2 C_2^2 \omega^2 \right) \right]^{1/2}$$

(31)

therefore  $i_{\rm ss}$  is sinusoidal time-dependent and exhibits a ripple at twice the desired output frequency, thus leading to a ripple of the voltage  $v_{\rm 1ss}$  at the same frequency given by (25a), namely

$$\left|\hat{V}_{1ss}(2j\omega)\right| = |G_i(2j\omega)| \cdot K(\omega) \tag{32}$$

thus evidencing the time dependence of the intermediate steady-state voltage  $v_{\rm 1ss}$  pointed out in Section III. This voltage ripple amplitude can lead the ratio  $A/v_{\rm 1ss}$  beyond the steady-state sliding domain boundary of the buck dc–ac converter given by (10), thus leading to a loss of sliding motion. Therefore, in order to counteract this possibility, a proper attenuation of  $|G_i(2j\omega)|$

has to be designed, this involving according to (25a) the surface parameters  $(\alpha, \beta, \delta)$  as well as the boost converter components  $L_1$  and  $C_1$ . The following design procedure is suggested assuming that the next parameters are known.

The desired output voltage amplitude and frequency noted as  $A_d$  and  $\omega_d$ , respectively.

The input voltage  $E_b$ , the buck inductor and capacitor values  $L_2$  and  $C_2$  and the dc steady-state boost output voltage  $v_1^*$ .

The minimum load value, noted as  $R_{\min}$ .

Taking into account these previous assumptions, the maximum current ripple is also known from (31), namely

$$K(\omega_d) = \frac{A_d^2}{2v_1^* R_{\min}} \left[ (L_2 C_2 \omega_d)^2 + \left( \frac{L_2 \omega_d}{R_{\min}} \right)^2 + \left( L_2 C_2 \omega_d^2 - 1 \right)^2 \left( 1 + R_{\min}^2 C_2^2 \omega_d^2 \right) \right]^{1/2}$$

(33)

from which the corresponding voltage amplitude can be deduced according to (32), i.e.,

$$\left|\hat{V}_{1ss}(2j\omega_d)\right| = |G_i(2j\omega_d)| \cdot K(\omega_d). \tag{34}$$

The design procedure starts by fixing a desired value of  $|\hat{V}_{1\mathrm{ss}}(2j\omega_d)|$  such that

•  $|\hat{V}_{1\mathrm{ss}}(2j\omega_d)|$  is in compliance with the small-signal analysis validity range. Regarding the voltage ripple as a steady-state perturbation, this constraint can be usually satisfied by fixing a perturbation level at most of 10% of the dc steady-state value, therefore

$$\left| \hat{V}_{1 \text{ss}}(2j\omega_d) \right| = \lambda \cdot v_1^* \quad \text{where} \quad \lambda \le 0, 1.$$

(35)

• The sliding domain of the buck inverter is preserved, i.e.  $A_d/v_1 < 1$ , this leading to:

$$v_1^* - \left| \hat{V}_{1ss}(2j\omega_d) \right| > A_d \tag{36}$$

or, equivalently according to (35)

$$\lambda < 1 - \frac{A_d}{v_1^*}.\tag{37}$$

Consequently,  $\lambda$  is selected to verify the most restrictive of the constraints (35) and (37). Subsequently, the value of the desired attenuation can be known from (34) and (35), i.e.,

$$|G_i(2j\omega_d)| = \frac{\lambda v_1^*}{K(\omega_d)}.$$

(38)

Accordingly, the unknown parameters of the transfer function  $G_i(s)$  given in (25a) must be designed to fulfill (38). In order to simplify the design, this transfer function is rewritten in a normalized form as follows:

$$G_i(s) = \frac{-G_1 \cdot s}{s^2 + 2\xi \omega_n \cdot s + \omega_n^2} \tag{39}$$

$$G_{i}(s) = \frac{-G_{1} \cdot s}{s^{2} + 2\xi\omega_{n} \cdot s + \omega_{n}^{2}}$$

where

$$G_{1} = \frac{2R_{\min}E_{b}\alpha v_{1}^{*}}{(2 \cdot R_{\min}E_{b}\alpha C_{1}v_{1}^{*} - \beta L_{1}A_{d}^{2})}$$

(40)

Fig. 5. Simulation of a load step change from open circuit to  $R=5\,\Omega$ . Parameters:  $L_1 = 1 \text{ mH}, C_1 = 1000 \,\mu\text{F}, L_2 = 750 \,\mu\text{H}, C_2 = 60 \,\mu\text{F},$  $E_b = 24 \text{ V}, \text{ A} = 40 \text{ V}, \omega = 2\pi 50 \text{ rad/s}, \alpha = 0.8, \beta = 0.0228, \delta = 1.573,$ = 1,  $a_1 = 2000$ ,  $a_2 = 1$ , and  $v_1^* = 60$  V.

Fig. 6. Simulation of a load step change from open circuit to  $R=5~\Omega.$ Parameters:  $L_1=1$  mH,  $C_1=1000\mu$ F,  $L_2=750\mu$ H,  $C_2=60$   $\mu$ F,  $E_b=24$  V, A=40 V,  $\omega=2\pi50$  rad/s,  $\alpha=0.8$ ,  $\beta=0.35$ ,  $\delta=1.573$ ,  $\vec{K} = 21, a_1 = 2000, a_2 = 1, \text{ and } v_1^* = 60 \text{ V}.$

$$\omega_n^2 = \frac{2R_{\min}E_b^2\delta}{(2 \cdot R_{\min}E_b\alpha C_1 v_1^* - \beta L_1 A_d^2)}$$

(41)

$$2\xi\omega_n = \frac{\left(2R_{\min}E_b^2\beta + \frac{\alpha A_d^2 E_b}{v_1^*} - \delta L_1 A_d^2\right)}{\left(2 \cdot R_{\min}E_b\alpha C_1 v_1^* - \beta L_1 A_d^2\right)}.$$

(42)

Therefore, from (39), the attenuation  $|G_i(2j\omega_d)|$  satisfies

$$|G_i(2j\omega_d)| = \frac{2\omega_d G_1}{|-4\omega_d^2 + 4\xi j\omega_n \omega_d + \omega_n^2|}.$$

(43)

The design is simplified by assuming that the ripple frequency  $2\omega_d$  lies on the high frequency attenuation range of  $|G_i(j\omega)|$ . In this case, (43) can be approximated by

$$|G_i(2j\omega_d)| \cong \frac{G_1}{2\omega_d}. (44)$$

Fig. 7. (a) Buck inverter power stage circuit. (b) Boost converter power stage circuit.

According to this assumption, the following value of  $\omega_n$  has been arbitrarily selected:

$$\omega_n = \frac{\omega_d}{5} \tag{45}$$

this enabling the design of real poles (i.e, an overdamped response) with a damping factor  $\xi$  such that  $\xi\cong 1$  in order to fulfill the approximation given in (44). Therefore, from (38) and (44), the value of  $G_1$  can be deduced as

$$G_1 = \frac{2\omega_d \lambda v_1^*}{K(\omega_d)} \tag{46}$$

whereas, according to (40), (41), and (45), the following design relations holds:

$$\delta = \frac{\alpha v_1^* \omega_n^2}{E_b G_1} = \frac{\alpha v_1^* \omega_d^2}{25 E_b G_1} \qquad C_1 = \frac{1}{G_1} + \frac{\beta \cdot L_1 \cdot A_d^2}{2R E_b \alpha v_1^*}. \tag{47}$$

These design relationships can be applied only under smallsignal perturbation assumptions. When large-signal perturbations are considered, other design criteria complementing the previous ones arise, as it is highlighted in the next section.

# C. Design Criteria According to the Large-Signal Transient Response

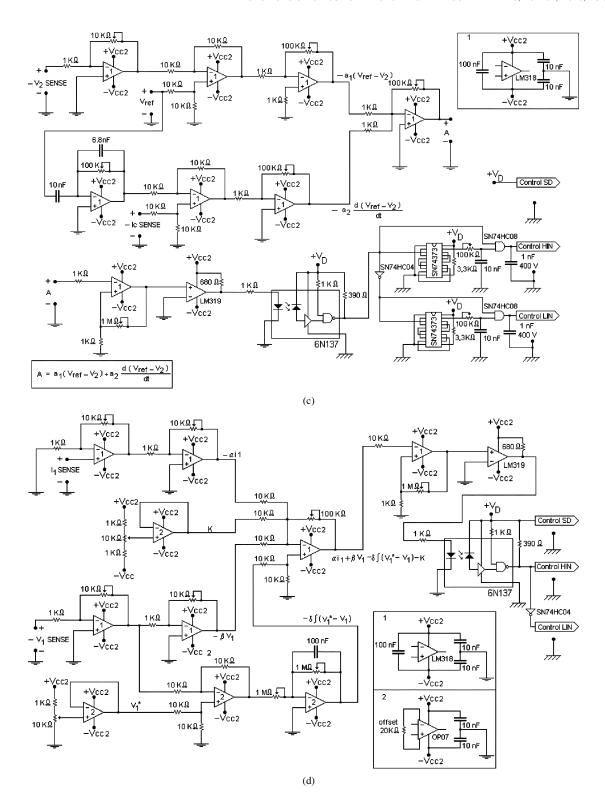

In order to infer additional design criteria, the following example is presented to illustrate the large-signal behavior of the power stage in the state plane under the sliding-control laws given in (6) and (18). This example considers a boost-buck dc-ac power stage with the following parameter values:  $L_1=1$  mH,  $C_1=1000~\mu\text{F},~L_2=750~\mu\text{H},~C_2=60~\mu\text{F},~R=1000~\Omega$  (i.e, open circuit) and  $E_b=24~\text{V}$ ; the desired output

Fig. 7 (Coninued.) (c) Buck inverter control circuit. (d) Boost converter control circuit.

signal parameters are fixed to  $A_d=40~\rm V$  (this corresponding to a global voltage step-up dc-ac conversion from a 24-V dc to 80 Vpp) and  $\omega_d=2\pi 50~\rm rad/s$ , being the dc component of the boost output voltage set to  $v_1^*=60~\rm V$ . Additionally, the buck switching surface parameters are  $a_1=2000,~a_2=1~\rm whereas$  those corresponding to the boost one have been

deliberately selected to hold a pair of conjugate poles according to (30), namely  $\alpha=0.8,\ \beta=0.0228,\ \delta=1.573,\ K=1.$  Fig. 5 shows the Matlab® simulation of he boost converter state variables  $(i_1,v_1)$  when, starting from the open circuit steady-state defined by  $(i_1^*=0\ A;\ v_1^*=60\ V)$ , a load step change from open circuit to  $R=5\ \Omega$  is applied at  $t=t_0$ .

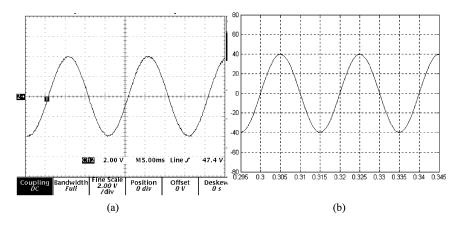

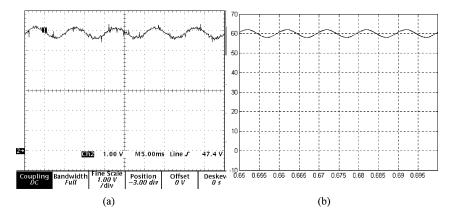

Fig. 8. (a) Measured and (b) Matlab simulation of the steady-state output voltage  $v_2$ . Scaling factor K=0.1.

Fig. 9. (a) Measured and (b) Matlab simulation of the steady-state intermediate voltage  $v_1$ . Scaling factor K=0.1.

Although a full analytical description is extremely cumbersome, the dynamic behavior shown in Fig. 5 can be interpreted by initially neglecting the state variables ripple as follows.

t = t<sub>0</sub><sup>-</sup>: prior to the load step change, the boost converter is in the steady state corresponding to open circuit; therefore, according to (16), the following relation holds:

$$S_1(i_1, v_1, t_0^-) = \alpha \cdot i_1 + \beta \cdot v_1 - \delta \cdot \int_0^{t_0^-} (v_1^* - v_1) dt - K = 0$$

(48)

and particularly, for the open-circuit steady state (namely,  $i_1^*=0~{\rm A};\,v_1=v_1^*)$

$$\beta \cdot v_1^* - \delta \cdot \int_0^{t_0^-} (v_1^* - v_1) dt - K = 0. \tag{49}$$

- t<sub>0</sub> < t ≤ t<sub>1</sub>: after the load step and during a time-interval

∆t = t<sub>1</sub> t<sub>0</sub> the state trajectory remains on the switching

surface S<sub>1</sub>(i<sub>1</sub>, v<sub>1</sub>, t<sub>0</sub>) = 0. The main reasons for this behavior are as follows.

- a) The boost converter quickly recovers the switching surface  $S_1(i_1, v_1, t_0^-) = 0$  due to the sliding-control action.

- b) The integrative term does not change significantly and can be approximated by its steady-state value, namely

$$\int_{0}^{t_0 + \Delta t} (v_1^* - v_1) dt \cong \int_{0}^{t_0^-} (v_1^* - v_1) dt. \tag{50}$$

Since the relation (48) holds, the state plane trajectory can be written, according to (49), as

$$v_1 \cong -\frac{\alpha}{\beta} \cdot i_1 + v_1^* \tag{51}$$

this corresponding to the equation of a straight line in the plane  $(i_1, v_1)$  with a slope of  $-\alpha/\beta$  and a constant term given by  $v_1^*$ .

• For  $t \ge t_1$  the integrative term increases and the system leaves the straight line given in (51) evolving with a second order underdamped dynamics, according to the complex poles location, to the new equilibrium point.

Fig. 5 also shows how, even remaining on the straight line defined in (51), the boost output voltage  $v_1$  falls below the level of the sinusoidal amplitude  $A_d$ , thus leading to a buck sliding motion loss since in this case  $A_d/v_1 > 1$ . This behavior suggests that the absolute value of the slope must be as low as possible to overcome this possibility. In accordance with this qualitative analysis, the values of  $\alpha$  and  $\beta$  are designed so that

$$\beta = \frac{\alpha \cdot i_1^*|_{R = R\min}}{v_1^* - A_d - |\hat{v}_1|_{\max}}$$

(52)

thus corresponding to a straight line in the plane  $(v_1,i_1)$  defined by the points according to the open circuit and the  $R_{\min}$  load values, thus preserving the buck converter sliding domain in the worst case. On the other hand, the value of K has been rbitrarily fixed to set the integrative term value to zero in open circuit steady-state operation; therefore, from (49)

$$K = \beta \cdot v_1^*. \tag{53}$$

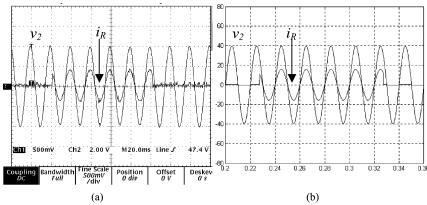

Fig. 11.(a) Measured and (b) Matlab simulation of the output signal  $v_2$  and the load current  $i_R$  for a load step change (open circuit –  $R=10~\Omega$  – open circuit). Voltage scaling factor K=0.1, current scaling factor  $K=100~\mathrm{mV/A}$ .

Fig. 12. Zoom of the (a) measured and (b) Matlab simulation of the output voltage  $v_2$  and load current  $i_R$  for a load step change (  $R=10~\Omega$ -open circuit). Voltage scaling factor K=0.1, current scaling factor K=0.1 V/A.

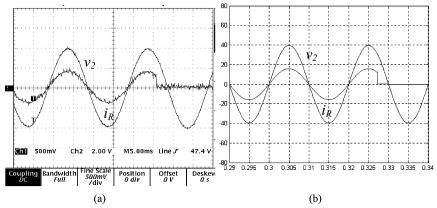

Fig. 13. (a) Measured and (b) Matlab simulation of the intermediate voltage  $v_1$  and the converter input current  $i_1$  for an input voltage step from 50 to 24 V. Voltage scaling factor K = 0.1, current scaling factor K = 0.1 V/A. Transient dynamics of the power supply have been included in the Matlab® simulations.

In order to validate this design criteria, Fig. 6 shows the Matlab simulation of  $(i_1,v_1)$  for a new set of values of K and  $\beta$  modified according to (52) and (53), in front of the same load perturbation. As can be seen, the buck sliding domain is preserved, whereas the boost dynamics exhibits the expected overdamped behavior and reaches the new equilibrium point  $(v_1^*, i_1^* = A_d^2/2RE_b)$ .

#### D. Suggested Design Procedure

Provided that the values of the following parameters are known:  $A_d$ ,  $\omega_d$ ,  $R_{\min}$ ,  $E_b$ ,  $v_1^*$ ,  $C_2$ ,  $L_2$ , and collecting the results

of the previous sections, the following design procedure is proposed.

- Fix  $\alpha$  and  $L_1$

- Determine  $\lambda$  and  $\hat{v}_{1\,\mathrm{max}}$  according to (35) and (37)

- Determine K and  $\beta$  according to (52) and (53)

- Determine  $K(\omega_d)$  and  $G_1$  according to (33) and (46)

- Determine  $\delta$  and  $C_1$  according to (47).

# V. SIMULATION AND EXPERIMENTAL RESULTS

The proposed design has been tested by means of both Matlab® simulations and measurements carried out on a

Fig. 14. (a) Measured and (b) Matlab simulation of the intermediate voltage  $v_1$  and the converter input current  $i_1$  for an input voltage step from 24 to 50 V. Voltage scaling factor K = 0.1, current scaling factor K = 0.1 V/A. Transient dynamics of the power supply have been included in the Matlab simulations.

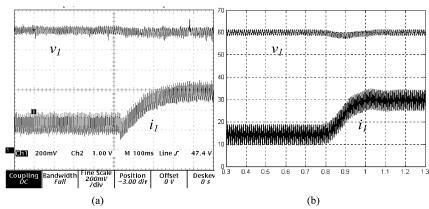

Fig. 15. (a) Measured and (b) Matlab simulation of the output voltage  $v_2$  and the output current  $i_R$  when the converter is loaded with a full-wave rectifier. Voltage scaling factor K = 0.1, current scaling factor K = 0.1 V/A.

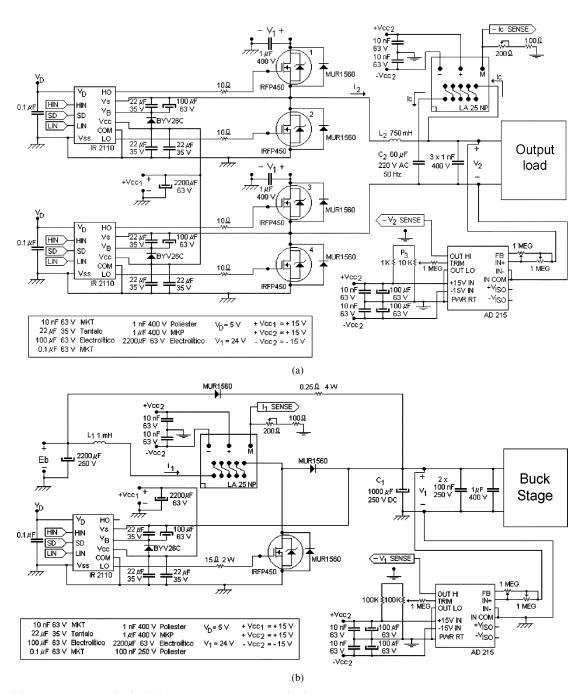

laboratory prototype which experimental set-up is shown in Fig. 7(a)–(d). The circuit parameters have been fixed in accordance with the design procedure exposed in the paper, and are as follows.

- Output signal and minimum load:  $A_d=40~{\rm V}$  and  $\omega_d=2\pi50~{\rm rad/s},~R_{\rm min}=10~\Omega.$

- Input voltage and intermediate voltage:  $E_b = 24 \text{ V}, v_1^* = 60 \text{ V}.$

- Steady-state intermediate voltage ripple  $\hat{v}_{1SSpp} = 4.8 \text{ V}_{pp} \ (i.e, \lambda = 4\%)$

- boost–buck power stage:  $L_1=1$  mH,  $C_1=\mu 1000$  F,  $L_2=\mu 750$  H,  $C_2=\mu 60$  F,

- Sliding surfaces parameters:  $\alpha=0.8,$   $\beta=0.1515,$   $\delta=7,$  K=9,  $a_1=12,$   $a_2=0.005$

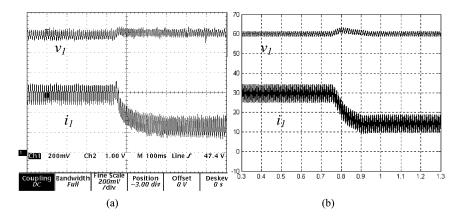

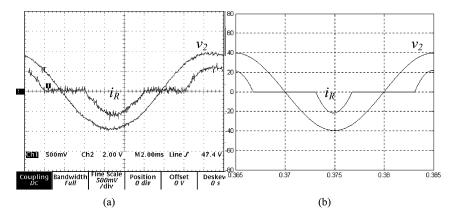

Fig. 8 shows the measured and the simulation of the steady-state dc–ac converter output voltage  $v_2$ , which confirms the achievement of a step-up conversion from 24 V dc to (80 V<sub>pp</sub>, 50 Hz) ac with good accuracy. Similarly, Fig. 9 shows the measured and the simulation of the intermediate steady-state voltage  $v_{1SS}$  which can be approximated by  $v_{1SS}\approx 60+2, 3\sin(2\pi\cdot 100\cdot t)$ , thus exhibiting as expected the desired ripple amplitude at twice the output frequency. As far as the transient dynamics in front of load perturbations is concerned, Figs. 10–12 show the measured and the simulation of the converter response in front of a load step change from open circuit to  $10~\Omega$  and back to open circuit. Particularly, Fig. 10 shows both the input current  $i_1$  and the intermediate voltage  $v_1$  which does not exhibit any over-

shoot. Fig. 11 corresponds to the measured and the simulation of the output voltage  $v_2$  and the load current in front of the same load perturbation profile, whereas Fig. 12 shows a zoom of these output variables evidencing the robustness of the output voltage in front of load perturbations. On the other hand, Figs. 13 and 14 show the intermediate voltage  $v_1$  and the input current  $i_1$  for a input voltage step from 50 to 24 V and from 24 to 50 V, respectively, where the dynamics of the power supply transients has been included in the simulations.

As it can be seen, the input voltage step does not modify significantly the intermediate voltage  $v_1$ , thus preserving the sliding domain of the buck converter. Finally, Fig. 15 shows the output voltage and the output current when the boost–buck dc–ac converter is loaded with a full-wave rectifier, highlighting the robustness of the output voltage in front of nonlinear loads as well. In this sense, a total harmonic distortion (THD) of 0.5% for the resistive load and of 1.8% for the full wave rectifier have been also measured. Finally, it can be pointed out that all the simulation results are close to the measured ones, thus confirming the usefulness of the presented analytical approach.

# VI. CONCLUSION

This paper has presented a sliding-mode control design of a boost-buck dc-ac switching converter for a voltage step-up dc-ac conversion without the use of any transformer. The proposed approach has been based on the design of two sliding-control laws, one ensuring the control of the full-bridge buck converter for a proper dc–ac conversion, and the other one to control the boost converter for guaranteeing a global dc-ac voltage step-up ratio. Taking advantage of previous results for the buck sliding-mode control design, the work has been mainly focused on the design of a sliding-control law for the boost converter, which has been oriented to preserve the buck sliding motion. This design has been performed through a small-signal dynamic analysis and has taken into account the large-signal behavior of the boost stage in the state plane. As a result, a set of design criteria and a complete design procedure have been suggested. Furthermore, the simulation and experimental results presented in the paper are in close agreement and have shown the achievement of a step-up conversion from 24 V dc to (80 V<sub>pp</sub>, 50 Hz) ac with a good accuracy and low THD for both resistive and nonlinear loads, as well as robustness in front of input voltage and load perturbations, thus validating the proposed design. In this sense, the approach presented in the paper can be applied for a robust and accurate dc-ac step-up transformerless conversion involving other output voltage amplitudes and frequencies by applying the design procedure exposed in the paper, and changing accordingly the buck converter sinusoidal voltage reference.

#### REFERENCES

- [1] A. Capel, J. C. Marpinard, J. Jalade, and M. Valentin, "Large-signal dynamic stability analysis of synchronized current-controlled modulators. Application to sine-wave power inverters," *ESA J.*, vol. 7, pp. 63–74, 1083

- [2] A. Kawamura and R. G. Hoft, "Instantaneous feedback controlled PWM inverter with adaptative hysteresis," *IEEE Trans. Ind. Applicat.*, vol. IA-20, pp. 706–712, Mar. 1984.

- [3] K. P. Gokale, A. Kawamura, and R. G. Hoft, "Dead-beat microprocessor control of PWM inverter for sinusoidal output waveform synthesis," *IEEE Trans. Ind. Applicat.*, vol. IA-23, pp. 901–910, May 1985.

- [4] P. Maussion et al., "Instantaneous feedback control of a single-phase PWM inverter with nonlinear loads by sine wave tracking," in Proc. IECON'89, 1989, pp. 130–135.

- [5] K. Jezernik, M. Milanovic, and D. Zadravec, "Microprocessor control of PWM inverter for sinusoidal output," in *Proc. Eur. Power Electronics Conf. (EPE)*, 1989, pp. 47–51.

- [6] H. Sira-Ramirez, "Sliding motions in bilinear switched networks," *IEEE Trans. Circuits Syst.*, vol. CAS-34, pp. 919–933, Aug. 1987.

- [7] V. I. Utkin, Sliding mode and their applications in variable structure systems. Moscow, U.S.S.R: Mir, 1978.

- [8] R. Venkataramanan, A. Sabanovic, and S. Cuk, "Sliding mode control of dc-to-dc converters," in *Proc. IECON*'85, 1985, pp. 251–258.

- [9] L. Martínez-Salamero, J. Calvente, R. Giral, A. Poveda, and E. Fossas, "Analysis of a bidirectional coupled-inductor Cuk converter operating in sliding mode," *IEEE Trans. Circuits Syst.*, vol. 45, pp. 355–363, Apr. 1908

- [10] A. E. Van der Groef, P. P. J. Van der Bosch, and H. R. Visser, "Multi-input variable structure controllers for electronic converters," in *Proc. EPE'91*, Firenze, Italy, 1991, pp. I-001–I-006.

- [11] R. Leyva, J. Calvente, and L. Martínez-Salamero, "Tracking en el convertidor boost-buck de dos conmutadores," in *Proc. Seminario Anual Automática, Electrónica Industrial e Instrumentación (SAAEI)*, 1997, pp. 233–238.

- [12] M. Carpita, M. Marchesioni, M. Oberti, and L. Puguisi, "Power conditioning system using sliding-mode control," in *Proc. PESC'88*, 1988, pp. 623–633.

- [13] E. Fossas and J. M. Olm, "Generation of signals in a buck converter with sliding-mode control," in *Proc. Int. Symp. Circuits and Systems*, 1994, pp. 157–160.

- [14] K. Jezernik and D. Zadravec, "Sliding mode controller for a single phase inverter," in *Proc. APEC'90*, 1990, pp. 185–190.

- [15] M. Carpita and M. Marchesoni, "Experimental study of a power conditioning using sliding-mode control," *IEEE Trans. Power Electron.*, vol. 11, pp. 731–742, Sept. 1996.

- [16] F. Boudjema, M. Boscardin, P. Bidan, J. C. Marpinard, M. Valentin, and J. L. Abatut, "VSS approach to a full bridge buck converter used for ac sine voltage generation," in *Proc. IECON'89*, 1989, pp. 82–89.

- [17] H. Pinheiro, A. S. Martins, and J. R. Pinheiro, "A sliding-mode controller in single phase voltage source inverters," in *Proc. IECON'94*, 1994, pp. 394–398.

- [18] L. Malesani, L. Rossetto, G. Spiazzi, and A. Zuccato, "An ac power supply with sliding-mode control," *IEEE Ind. Applicat. Mag.*, vol. 2, pp. 32–38, Sept./Oct. 1996.

- [19] D. Biel, E. Fossas, F. Guinjoan, A. Poveda, and E. Alarcón, "Applicaction of sliding-mode control to the design of a buck-based sinusoidal generator," *IEEE Trans. Ind. Electron.*, vol. 48, pp. 563–571, June 2001.

- [20] E. Fossas and D. Biel, "A sliding-mode approach to robust generation on dc-to-dc converters," in *Proc. IEEE Conf. Decision Control*, 1996, pp. 4010–4012.

- [21] E. Fossas and J. M. Olm, "Asymptotic tracking in dc-to-dc nonlinear power converters," *Discrete Continuous Dyn. Syst.*, ser. B, vol. 2, no. 2, pp. 295–307, 2002.

- [22] V. I. Utkin, J. Guldner, and J. Shi, Sliding Mode Control in Electromechanical Systems. London, U.K.: Taylor & Francis, 1999.

Domingo Biel (S'97–M'99) received the B.S, M.S., and Ph.D. degrees in telecomunications engineering from the Universidad Politècnica de Cataluña, Barcelona, Spain, in 1990, 1994, and 1999, respectively. His thesis dissertation research was on the application of sliding-mode control to the signal generation in dc-to-dc switching converters.

He is currently an Associate Professor in the Departamento de Ingenieria Electrónica, Escuela Politécnica Superior d'Enginyeria, Universitad Politecnica de Catalunya, where he teaches power

electronics and control theory. He is the author/coauthor of several communications in international congresses and workshops. His research interests are related to nonlinear control, sliding-mode control and power electronics.

Francisco Guinjoan (M'92) received the Ingeniero de Telecomunicación and Doctor Ingeniero de Telecomunicación degrees from the Universitad Politècnica de Cataluña, Barcelona, Spain, in 1984 and 1990, respectively, and the Docteur es Sciences degree from the Université Paul Sabatier, Toulouse, France, in 1992.

He is currently an Associate Professor in the Departamento de Ingenieria Electrónica, Escuela Técnica Superior de Ingenieros de Telecomunicación Barcelona, Universitad Politècnica de

Cataluña, where he teaches power electronics. His research interests include power electronics modeling, nonlinear circuit analysis and control, and analog circuit design.

Enric Fossas was born in Aiguafreda, Spain, in 1959. He received the graduate and Ph.D. degrees in mathematics from Universitad de Barcelona, Barcelona, Spain, in 1981 and 1986, respectively.

In 1986, he joined the Department of Applied Mathematics, Universitad Politecnica de Cataluña, Barcelona, Spain. In 1999, he moved to the Institute of Industrial and Control Engineering and to the Department of Automatic Control and Computer Engineering at the same university, where he is presently an Associate Professor.

His research interests include nonlinear control theory and applications, particularly variable-structure systems, with applications to switching converters.

Javier Chavarria was born in Tortosa, Spain, in 1978. He received the degree in technical telecommunications engineering in 2001 from the Escola Politècnica Superior d'Enginyeria de Vilanova la Geltrú, Barcelona, Spain, in 2001, where, since 2002, he is working toward the M.S. degree in electronics.

He was a Researcher in the Department of Electronic Engineering, Escola Politècnica Superior d'Enginyeria de Vilanova la Geltrú,. From 2001 to 2002, he was with the Technologic Innovation

Center in Static Converters and Operations (CITCEA), Universitad Politecnica de Cataluña, Barcelona, Spain. Since 2002, he is with Sony Corporation, Barcelona.

Dr. Chavarria won two prizes from the Official College of Telecommunications Engineers, Spain, while at CITCEA. He is a member of the Spanish Official College of Technical Telecommunications Engineers (COITT).