Received February 27, 2020, accepted March 12, 2020, date of publication March 16, 2020, date of current version April 16, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.2980814

# Sliding-Mode Control Strategy for Three-Phase Three-Level T-Type Rectifiers With DC Capacitor Voltage Balancing

SERTAC BAYHAN<sup>®</sup>1, (Senior Member, IEEE), AND HASAN KOMURCUGIL<sup>®</sup>2, (Senior Member, IEEE)

<sup>1</sup>Qatar Environment and Energy Research Institute, Hamad Bin Khalifa University, Doha, Qatar <sup>2</sup>Department of Computer Engineering, Eastern Mediterranean University, Famagusta 996628, Turkey

Corresponding author: Sertac Bayhan (sbayhan@hbku.edu.qa)

This work was supported by the Qatar National Library.

**ABSTRACT** A sliding mode control (SMC) strategy with dc capacitor voltage balancing is proposed for three-phase three-level T-type rectifiers. The proposed SMC strategy is designed in the *abc* frame rather than the *dq* frame. In this case, the necessity of three-phase current transformations is eliminated. The proposed SMC is based on the errors of the line currents. The amplitude of line current references is generated by controlling the dc voltage using a proportional-integral (PI) controller. In order to obtain unity power factor, the generated reference amplitude is multiplied by the corresponding sinusoidal waveform obtained from the phase locked loop (PLL) operating with grid voltages. The dc capacitor voltage balancing is achieved by adding a proportional control term into the line current reference obtained for each rectifier leg. The performance of the proposed control strategy is validated by simulations and experiments during steady-state, transients caused by load change, and unbalanced grid conditions. The results show that the proposed control strategy offers excellent steady-state and dynamic performances with low THD in the line currents, zero steady-state error in the output voltage, and very fast dynamic response.

**INDEX TERMS** Three-level T-type rectifier, proportional-integral control (PI), sliding mode control.

#### I. INTRODUCTION

Three-phase ac-dc rectifiers are widely employed in various industrial applications due to their advantages such as controllable dc-link voltage, sinusoidal line currents with reasonably low total harmonic distortion (THD), and unity power factor. There are two types of rectifiers: current-source type [1] and voltage-source type [2]. While a three-phase two-level current-source type rectifier uses six unidirectional switches, a three-phase two-level voltage-source rectifier uses six bidirectional switches. However, the voltage-source rectifier topology is very popular due to its simple structure and ease of control [2]–[5]. In order to achieve dc voltage control, sinusoidal line currents with low THD and unity power factor, the two-level rectifiers should be operated with high switching frequencies. However, this would increase acoustic noise and switching losses. The acoustic noise can be

The associate editor coordinating the review of this manuscript and approving it for publication was Alfeu J. Sguarezi Filho.

reduced at the expense of increasing the volume and weight of the passive components. On the other hand, the performance of a two-level rectifier is not good at medium and high voltages.

In the last two decades, multilevel converters are emerged as an alternative topology to be employed at medium and high voltage levels [6]. As in the case of two-level converters, voltage-source based multilevel converters are more popular which can be categorized as neutral point clamped (NPC) [7]–[9], flying capacitor (FC) [10], cascaded H-bridge (CHB) [11], packed-U-cell (PUC) [12], T-type [13], and hybrid type [14]–[16].

Among these multilevel converter topologies, the T-type converter merits attention due to its significant advantages such as low switching losses, reduced component count, better efficiency and reduced control complexity. If the efficiency and cost are important, then a T-type converter is a good choice in low voltage applications rather than an NPC converter [17]. Also, the T-type converter topology

has reduced component count compared to three-level NPC converter topology in [18]. Comparing NPC- and T-type converters, one can see that both topologies use four switches in one converter leg. However, unlike the T-type converters, the NPC converters need additional two clamping diodes per converter leg. The clamping of neutral point to positive or negative dc voltages is achieved by the clamping diodes in an NPC converter. In a T-type converter, an active bidirectional switching device connected between the midpoint of each converter leg and midpoint of series connected dc-link capacitors is used to achieve this voltage clamping. Hence, the T-type converters have reduced component count than the NPC converters which implies that T-type converters have smaller losses than that of NPC-type converters [17].

In spite of attractive features of multilevel converters, the dc capacitor voltage balancing is essential which increases the controller complexity. In [7], the dc capacitor voltage balancing is accomplished via predictive control strategy for an NPC-type rectifier. The authors in [8] proposed a modulation strategy to balance the capacitor voltages in an NPC-type rectifier. However, the regulation of dc voltage and line currents can be achieved by employing three proportionalintegral (PI) controllers. In [9], an  $H_{\infty}$  controller is proposed to balance the dc capacitor voltages of an NPC-type rectifier. It is reported that the control of an NPC-type rectifier requires three control loops, namely, instantaneous power tracking loop, dc voltage regulation loop, and dc capacitor voltage balancing loop. The objective of instantaneous power tracking loop is to achieve instantaneous active and reactive power tracking. The objective of the dc voltage regulation loop is to ensure output voltage regulation such that that the sum of dc capacitor voltages is equal to the reference output voltage. Finally, the voltage balancing loop eliminates the imbalance between the dc capacitor voltages. Similar requirements also exist in FC-type rectifier [10], and CHB-type rectifier [11]. Although the PUC-type rectifier topology is the simplest topology among the multilevel rectifier topologies, but it is not mature yet and did not find any application in the industry due to its complicated control structure [12].

In the last few years, three-level T-type rectifiers are increasingly stuided in the literature [13], [19]–[27]. In [13] and [19], open-switch fault detection and tolerance control techniques are proposed to improve the reliability of the three-level T-type rectifier during an open-switch fault. In [20], open-switch fault tolerance control methods are compared. In [21], a proportional-resonant (PR) control is used to damp the resonance in the LLCL filter. Although the T-type converter topology exists in the literature more than one decade, there are not many studies addressing its application as rectifier. The other studies devoted for three-level T-type rectifiers are based on EMI filter size minimization [22], improved modulation scheme for neutral-point potential balancing and circulating current suppression [23], and carrier-based [24] and open-circuit [19] fault-tolerant control methods with neutral-point voltage oscillations suppression.

The authors in [25] proposed predictive observer based control method for single-phase T-type rectifier. Although the proposed method exhibits good performance, its implementation is complicated. Furthermore, it is sensitive to the system parameters.

Since T-type rectifier is emerged a few years ago, its control is not studied extensively. In this study, sliding mode control (SMC) of three-phase three-level T-type rectifier is proposed. The main advantages of SMC include fast dynamic response, easy implementation, robustness against disturbances and variations in the system parameters. Although the SMC is recognized as one of the popular and powerful control tools in wide range of power converters [28]–[32], its adoption for T-type rectifiers is found only in [33] where the dynamic response is fast and unity power factor operation is accomplished satisfactorily. However, the presented SMC is sensitive to the disturbances. Furthermore, steady-state error exists in the dc voltage. On the other hand, the proposed SMC is fundamentally different from the existing SMC methods which are generally based on a state variable and its derivative.

In this study, a SMC strategy is proposed to regulate the dc voltage, achieve the line current control and dc capacitor balancing control. While dc voltage control is accomplished by a PI controller, the line currents are controlled by SMC in the abc frame. The formulation of the proposed SMC is intentionally made in abc frame to eliminate the transformations that would be needed in the dq frame. The reference amplitude of the line currents is produced by the PI controller. The produced reference amplitude is then multipled with the corresponding sinusoidal waveforms which are generated via a phase locked loop (PLL) synchronized with the grid voltages. The waveforms obtained from each multiplication are used as reference line current for each phase. The imbalance between dc capacitor voltages are eliminated by adding the dc capacitor voltage error with the reference line current for each phase. Simulation and experimental results are presented to confirm the validity and effectiveness of the proposed SMC method.

#### **II. OPERATION PRINCIPLE OF A T-TYPE RECTIFIER**

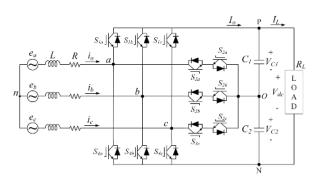

Fig. 1 shows the circuit diagram of three-phase three-level T-type rectifier which consists of four switches per leg. Similar to the conventional two-level rectifiers, the inductor L connected between grid and midpoint of each phase achieves boost operation. The resistance of inductor is denoted by R and capacitors are represented by  $C_1$  and  $C_2$ .

Considering the combination of switching states, the rectifier can produce three different pole voltages  $v_{kO}$  (k=a, b, c) which exist when the midpoint of each leg is connected to positive (P), neutral (O) and negative (N) points. Table 1 shows the operating states, switching states and generated pole voltage levels. When the switches  $S_{1k}$  and  $S_{2k}$  are turned ON and  $S_{3k}$  and  $S_{4k}$  are turned OFF, the rectifier operates in the P state which produces pole voltage equal to  $v_{kO} = V_{dc}/2$ . On the other hand, when  $S_{2k}$  and  $S_{3k}$  are turned

FIGURE 1. Three-phase three-level T-type rectifier.

TABLE 1. Operating states, switching states and pole voltages.

| Operating<br>State | $S_{Ik}$ | $S_{2k}$ | $S_{3k}$ | $S_{4k}$ | $v_{kO}$            |

|--------------------|----------|----------|----------|----------|---------------------|

| P                  | ON       | ON       | OFF      | OFF      | $V_{dc}/2$          |

| О                  | OFF      | ON       | ON       | OFF      | 0                   |

| N                  | OFF      | OFF      | ON       | ON       | -V <sub>dc</sub> /2 |

ON and  $S_{1k}$  and  $S_{4k}$  are turned OFF, the rectifier operates in the O state producing pole voltage equal to 0V. Finally, when  $S_{1k}$  and  $S_{2k}$  are turned OFF and  $S_{3k}$  and  $S_{4k}$  are turned ON, the rectifier is in the N state which produces pole voltage  $v_{kO} = -V_{dc}/2$ . Hence, by using different switching combinations a five-level  $(0, \pm V_{dc}/2, \pm V_{dc})$  line-to-line voltage can be produced.

#### **III. MODELING OF T-TYPE RECTIFIER**

Operation of the rectifier can be described by the following ac-side equation [34]

$$\mathbf{e} = L\frac{d\mathbf{i}}{dt} + R\mathbf{i} + \mathbf{v} \tag{1}$$

where

$$\mathbf{e} = \begin{bmatrix} e_a & e_b & e_c \end{bmatrix}^{\mathrm{T}}, \quad \mathbf{i} = \begin{bmatrix} i_a & i_b & i_c \end{bmatrix}^{\mathrm{T}}, \quad \mathbf{v} = \begin{bmatrix} v_{an} & v_{bn} & v_{cn} \end{bmatrix}^{\mathrm{T}}$$

(2)

The three-phase grid voltages are defined as

$$e_a = E_m \cos(\omega t) \tag{3}$$

$$e_b = E_m \cos(\omega t - 2\pi/3) \tag{4}$$

$$e_b = E_m \cos(\omega t + 2\pi/3) \tag{5}$$

where  $E_m$  denotes the amplitude of the grid voltages. The voltages  $v_{an}$ ,  $v_{bn}$ , and  $v_{cn}$  are expressed as

$$v_{an} = v_{aO} + v_{On} \tag{6}$$

$$v_{bn} = v_{bO} + v_{On} \tag{7}$$

$$v_{cn} = v_{cO} + v_{On} \tag{8}$$

Applying Kirchhoff's current law at the positive terminal of load and neutral-point, one can find the following dc-side equations

$$C_1 \frac{dV_{C1}}{dt} = I_0 - I_L \tag{9}$$

$$C_2 \frac{dV_{C2}}{dt} = C_1 \frac{dV_{C1}}{dt} + I_n \tag{10}$$

$$I_{n} = C_{2} \frac{dV_{C2}}{dt} - C_{1} \frac{dV_{C1}}{dt} = C \frac{dv_{e}}{dt}$$

(11)

where  $I_n$  is the neutral-point current,  $v_e = V_{C2} - V_{C1}$  is the dc capacitor voltage error. It is assumed that  $C = C_1 = C_2$ . Equation (11) implies that dc capacitor voltage error is influenced by the neutral-point current  $I_n$ .

As explained in Introduction, there are three control objectives for three-level T-type rectifier. These objectives are regulation of dc voltage ( $V_{dc}$ ), control of line currents such that they are in phase with the corresponding grid voltages (achievement of unity power factor) and compensation of imbalance between dc capacitor voltages. Hence, there should be totally four loops in the controller.

#### IV. DESIGN OF CONTROL STRATEGY

## A. OUTPUT VOLTAGE CONTROL AND REFERENCE LINE CURRENT GENERATION

The control of output dc voltage is achieved by a PI controller. It is well known that PI controllers offer good dynamic response as well as zero steady-state error in controlling a dc quantity. In this study, the PI controller processes output voltage error  $(V_{dc}^* - V_{dc})$  and produces the reference amplitude of the line currents as

$$I^* = K_p(V_{dc}^* - V_{dc}) + K_i \int (V_{dc}^* - V_{dc})dt$$

(12)

where  $V_{dc}^*$  is the reference of  $V_{dc}$ ,  $K_p$  is the proportional gain and  $K_i$  is the integral gain. In order to achive the unity power factor operation, the actual three-phase line currents must be in phase with the corresponding grid voltages. In the proposed controller, the use of reference line currents is essential. The sinusoidal signals synchronized with the grid voltages are obtained by using PLL. Then, the reference line current for each phase can be produced by multiplying the corresponding sinusoidal signals with  $I^*$  as follows

$$i_a^* = I^* \cos(\omega t) \tag{13}$$

$$i_b^* = I^* \cos(\omega t - 2\pi/3)$$

(14)

$$i_c^* = I^* \cos(\omega t + 2\pi/3)$$

(15)

#### B. DC CAPACITOR VOLTAGE BALANCING

As mentioned in Section I, the balancing of dc capacitor voltages is essential in the three-level T-type rectifier. It should be noted that this voltage balancing requirement is not only necessary for the T-type rectifiers, but also required for other multilevel rectifier topologies. The objective is to eliminate the dc value in  $v_e$ . When  $I_n$  is positive, while  $V_{C1}$  is decreased,  $V_{C2}$  is increased (see equation (11)). Similarly, when  $I_n$  is negative, while  $V_{C1}$  is increased,  $V_{C2}$  is decreased. In this study, this fact is used to achieve  $v_e = 0$  V which balances the dc capacitor voltages. The neutral-point current is expressed in terms of line currents as follows [35]

$$I_n = d_a i_a + d_b i_b + d_c i_c \tag{16}$$

where  $d_k$  is the on-time duty cycle for each phase. Hence, considering (11) and (16), one can see that  $v_e$  is influenced by the line currents. Therefore, if the reference line currents in (13)-(15) are modified with a feedback control term which involves  $v_e$ , then the variations in  $v_e$  will be eliminated when the line currents track their references.

Now, let the reference line currents in (13)-(15) are modified as follows

$$i_{am}^* = I^* \cos(\omega t) + K_e v_e \tag{17}$$

$$i_{bm}^* = I^* \cos(\omega t - 2\pi/3) + K_e v_e$$

(18)

$$i_{cm}^* = I^* \cos(\omega t + 2\pi/3) + K_e v_e$$

(19)

where  $K_e v_e$  is the feedback control term generated by a proportional controller with a gain  $K_e$  which is less than zero for stability. In this case, the line currents will track  $i_{km}^*$  ( $i_{am}^*$ ,  $i_{bm}^*$ ,  $i_{cm}^*$ ) instead of  $i_k^*$  ( $i_a^*$ ,  $i_b^*$ ,  $i_c^*$ ). Clearly,  $i_{km}^*$  decreases when  $v_e > 0$  and increases when  $v_e < 0$ . Assuming that the line current control is accomplished ( $i_k = i_{km}^*$ ) successfully, then the value of  $v_e$  is made zero by the proportional control loop in the steady-state. This fact can be shown mathematically as follows. Assuming that the line currents track their references ( $i_k = i_{km}^*$ ) and using (11), equation (16) can be written as

$$\frac{dv_e}{dt} = \frac{1}{C} \left( d_a i_a^* + d_b i_b^* + d_c i_c^* \right) + \frac{1}{C} \left( d_a + d_b + d_c \right) K_e v_e \tag{20}$$

Since  $\frac{1}{C} \left( d_a i_a^* + d_b i_b^* + d_c i_c^* \right) = 0$  in a balanced three-phase system, then (20) reduces to

$$\frac{dv_e}{dt} = \frac{1}{C} \left( d_a + d_b + d_c \right) K_e v_e \tag{21}$$

It is evident that (21) is a first-order differential equation whose solution is given by

$$v_{\ell}(t) = v_{\ell}(0)e^{\lambda t} \tag{22}$$

where  $\lambda = (d_a + d_b + d_c) \frac{K_e}{C}$ . Since  $(d_a + d_b + d_c) > 0$ , C > 0, and  $K_e < 0$ , then  $v_e(t)$  converges to zero.

#### C. LINE CURRENT CONTROL USING SMC

In this study, the line current control is achieved by using sliding mode control. Now, let the sliding surface functions be defined as follows

$$\sigma_a = i_a - i_{am}^* \tag{23}$$

$$\sigma_b = i_b - i_{bm}^* \tag{24}$$

$$\sigma_c = i_c - i_{cm}^* \tag{25}$$

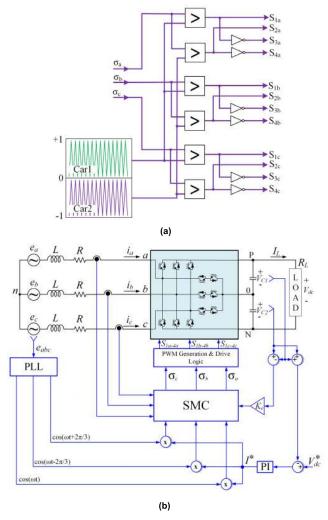

The modulating signals are sliding surface functions ( $\sigma_a$ ,  $\sigma_b$ ,  $\sigma_c$ ) which are compared with level shifted triangular carrier signals to produce the required pulse width modulation (PWM) signals. The sliding mode occurs if the existence conditions are satisfied. Generally, existence conditions are derived from the sliding surface function ( $\sigma_k$ ) and its derivative which should have opposite signs around the sliding line.

Hence, the sliding mode is stable if the following condition holds [36], [37]

$$\sigma_k \frac{d\sigma_k}{dt} < 0 \tag{26}$$

Now, let us show that the condition in (26) holds for phase a. Substituting the derivative of (23) into (26) gives

$$\sigma_a \left( \frac{di_a}{dt} - \frac{di_{am}^*}{dt} \right) < 0 \tag{27}$$

Since  $I^*$ ,  $V_{C1}$  and  $V_{C2}$  are constant in the steady-state, then the derivative of (17) can be written as

$$\frac{di_{am}^*}{dt} = -\omega I^* \sin(\omega t) \tag{28}$$

The expression for  $di_a/dt$  can be derived from (1) as follows

$$\frac{di_a}{dt} = \frac{1}{L} \left( E_m \cos(\omega t) - Ri_a - v_{an} \right) \tag{29}$$

Now, substituting (28) and (29) into (27) and assuming that line current tracks its reference ( $i_a = i_{am}^*$ ), we obtain

$$\sigma_a \left( \sqrt{(E_m - RI)^2 + (\omega LI)^2} \cos(\omega t + \theta) - v_{an} \right) < 0 \quad (30)$$

where phase shift  $\theta$  is given by

$$\theta = \tan^{-1} \left( \frac{-\omega LI}{(E_m - RI)} \right) \tag{31}$$

Equation (30) can be rewritten as

$$\sqrt{(E_m - RI)^2 + (\omega LI)^2} \cos(\omega t + \theta) < v_{an}$$

(32)

It is worth noting that the three-level T-type rectifier under consideration is a boost type rectifier which means that its output voltage is always greater than its input voltage. The voltage  $v_{an}$  at the ac-side of the rectifier is written in terms of the on-time duty cycles and dc voltage as follows

$$v_{an} = \frac{V_{dc}}{6} (2d_a - d_b - d_c) \tag{33}$$

Hence, since the fundamental of  $v_{an}$  is always greater than  $\sqrt{(E_m - RI)^2 + (\omega LI)^2}$ , then (32) is always satisfied and the proposed control strategy provides a stable operation for the rectifier. On the other hand, the chattering which is the main obstacle in SMC is solved by employing the method presented in [32]. Unlike the hysteresis current control, the proposed SMC generates PWM signals by comparing level shifted carrier signals with the line current errors without using any band. However, the chattering can also be tackled by using the second-order SMC method in [38].

FIGURE 2. Three-phase three-level T-type rectifier with: (a) the PWM generation block and (b) the proposed SMC strategy.

## D. DETERMINATION OF LINE CURRENT AMPLITUDE AND MAXIMUM ALLOWABLE OUTPUT VOLTAGE

On the other hand, the expression for the line current amplitude can be obtained by considering the power balance of the rectifier as follows. The input power delivered by the three-phase grid into the rectifier is

$$P_{in} = \frac{3}{2} E_m I \tag{34}$$

Neglecting the switching losses in the rectifier, while some part of  $P_{in}$  is absorbed by R, the remaining part of  $P_{in}$  is absorbed by the load. Therefore, using power balance concept, we can obtain the following expression

$$\frac{3}{2}E_mI = \frac{3}{2}RI^2 + V_{dc}I_L \tag{35}$$

Equation (35) is a quadratic equation which is written as

$$I^2 - \frac{E_m I}{R} + \frac{2V_{dc} I_L}{3R} = 0 (36)$$

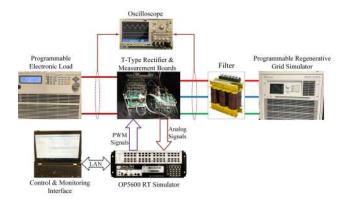

FIGURE 3. Experimental prototype.

**TABLE 2.** System and control parameters.

| Description and Symbol                | Value   |  |  |

|---------------------------------------|---------|--|--|

| Grid voltage amplitude, $E_m$         | 120√2 V |  |  |

| Inductance, L                         | 1mH     |  |  |

| Inductor resistance, R                | 0.1Ω    |  |  |

| DC capacitors, $C_1 = C_2$            | 470μF   |  |  |

| Load resistance, $R_L$                | 40Ω     |  |  |

| DC-link voltage reference, $V_{dc}^*$ | 400V    |  |  |

| PI gains, $K_p$ and $K_i$             | 2,180   |  |  |

| Imbalance compensation gain, $K_e$    | -0.1    |  |  |

| Switching frequency, $f_{sw}$         | 5kHz    |  |  |

The expression for I can be obtained by solving (36) as follows

$$I_{1,2} = \frac{\frac{E_m}{R} \pm \sqrt{\frac{E_m^2}{R^2} - \frac{8I_L V_{dc}}{3R}}}{2}$$

(37)

It is obvious from (37) that there are two solutions for I which depend on the operating point of the rectifier. These solutions will be real if the following condition is satisfied

$$\left(\frac{E_m}{R}\right)^2 > \frac{8I_L V_{dc}}{3R} \tag{38}$$

The maximum value of dc voltage can be determined as

$$V_{dc} < \frac{3E_m^2}{8RI_L} \tag{39}$$

In other words,  $V_{dc}$  cannot exceed  $3E_m^2/8RI_L$ . Equation (39) can be used to find the maximum dc voltage value that the rectifier can provide. For instance,  $V_{dc}$  cannot be greater than 540V when  $E_m = 120\sqrt{2}$ V,  $R = 1\Omega$ , and  $I_L = 20$ A. The block diagram of the PWM generation and proposed control strategy are shown in Fig. 2.

### **V. SIMULATION AND EXPERIMENTAL RESULTS**

The theoretical considerations and feasibility of the proposed control strategy are validated by computer simulations using

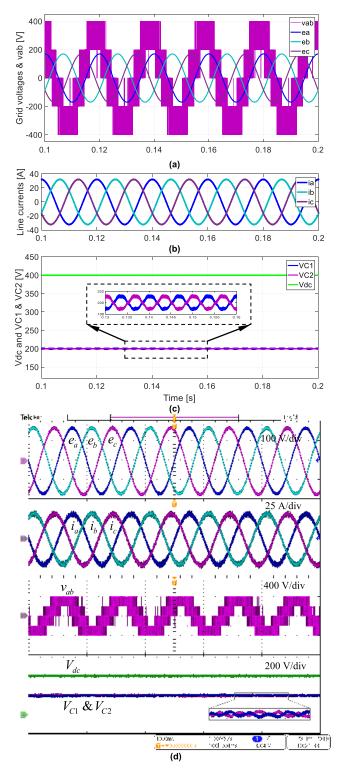

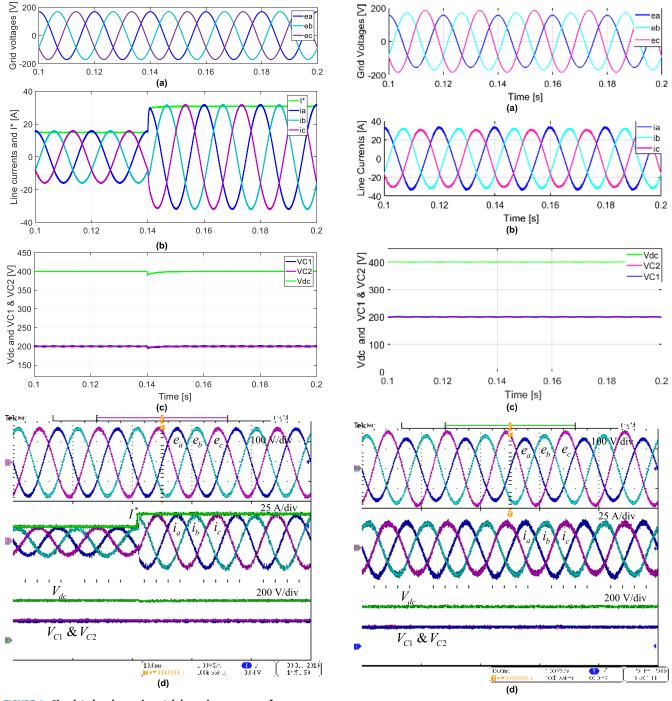

**FIGURE 4.** Simulated and experimental steady-state responses of  $(e_a, e_b, e_c)$ ,  $v_{ab}$ ,  $(i_a, i_b, i_c)$ ,  $(V_{C1}, V_{C2})$ , and  $V_{dc}$  under  $20\Omega$  resistive load. (a)-(c) Simulation, (d) Experiment.

Matlab/Simulink and experiments. The experimental results were obtained from a setup which was built to realize the system shown in Fig. 2(b). Fig. 3 shows the experimental prototype together with the equipment used to realize the

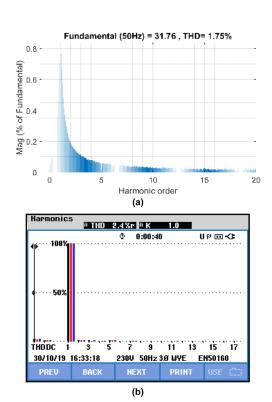

FIGURE 5. Simulated and experimental spectrums of line currents corresponding to Fig. 4. (a) Simulation, (b) Experiment.

proposed system. The proposed control technique was developed through the Matlab/Simulink environment and executed through OPAL-RT OP5600 real-time simulator, which was used as the main controller in this study. A programmable electronic load (Chroma-63804) is employed to emulate the DC side load. A regenerative grid simulator (Chroma61860) is used to emulate the grid. The T-Type rectifier was built by GeneSic hybrid SiC Schottky rectifier/Si IGBT modules. The gate drives and measurement boards (from Taraz Technologies) are used between OPAL-RT controller and T-Type rectifier to adapt the PWM and analog signal levels. Tektronix MSO4100 series oscilloscope is used to collect the experimental waveforms. The simulation and experimental results are obtained by using the system and control parameters presented in Table 2.

Fig. 4 shows simulated and experimentally obtained steady-state responses of grid voltages  $(e_a, e_b, e_c)$ , line currents  $(i_a, i_b, i_c)$ , line-to-line voltage between phase a and phase b  $(v_{ab})$ , capacitor voltages  $(V_{C1}, V_{C2})$ , and output voltage  $(V_{dc})$  under a  $20\Omega$  resistive load.

It obvious from Figs. 4(c) and (d) that the first control objective (i.e.: regulation of dc output voltage) is achieved. The output voltage is regulated at  $V_{dc}^* = 400\,\mathrm{V}$ . The second control objective (i.e.: sinusoidal line currents with unity power factor) is also satisfied. It is evident from Fig. 4(a), (b) and (d) that the line currents are sinusoidal and in phase with grid voltages. This means that the unity power factor requirement is satisfied. The theoretical value of I computed from (37) is 32.03A which is in good agreement

**FIGURE 6.** Simulated and experimental dynamic responses of  $(e_a, e_b, e_c)$ ,  $(i_a, i_b, i_c)$ ,  $I^*$ ,  $(V_{C1}, V_{C2})$ , and  $V_{dc}$  for an abrupt change in  $R_L$  from  $40\Omega$  to  $20\Omega$ : (a)-(c) Simulation, (d) Experiment.

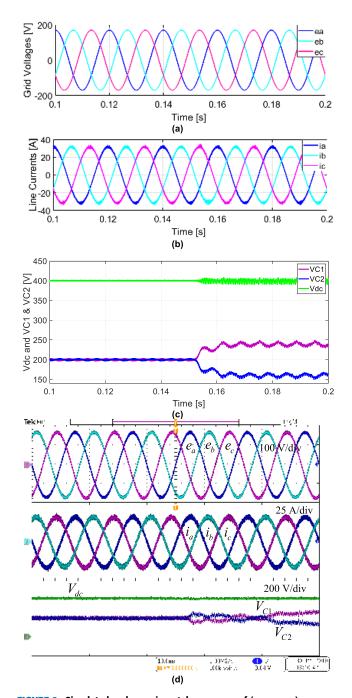

**FIGURE 7.** Simulated and experimental steady-state responses of  $(e_a, e_b, e_c)$ ,  $(i_a, i_b, i_c)$ ,  $(V_{C1}, V_{C2})$ , and  $V_{dc}$  for an unbalanced grid voltages under  $20\Omega$  resistive load. (a)-(c) Simulation, (d) Experiment.

with the simulation and experimental results. The line-to-line voltage  $(v_{ab})$  obtained by simulation and experimentally has five levels  $(\pm 400\,\mathrm{V},\,\pm 200\,\mathrm{V})$  and  $0\,\mathrm{V})$  which agrees well with the values in Table 1. The third control objective (i.e.: dc capacitor balancing) is also satisfied. Figs. 4(c) and (d) show the dc capacitor voltages which are balanced at 200V (half of  $V_{dc}$ ).

The harmonic spectrum and THD of line currents are depicted in Fig. 5. Clearly, the harmonic components are negligibly small. The computed and measured THD values are 1.75% and 2.4%, respectively. The experimental THD is higher than that obtained by simulation. The main reason of this difference comes from the non-ideal environment in the experimental setup such as measurement errors, unforeseen

**FIGURE 8.** Simulated and experimental responses of  $(e_a, e_b, e_c)$ ,  $(i_a, i_b, i_c)$ ,  $(V_{C1}, V_{C2})$ , and  $V_{dc}$  with and without imbalance compensation control under  $20\Omega$  resistive load. (a)-(c) Simulation, (d) Experiment.

noise, dead-time effect and real rectifier which cannot operate same as in the simulation model. However, the measured THD value is within the range of international standard [39].

Fig. 6 shows the dynamic responses of grid voltages, line currents, reference amplitude  $(I^*)$ , dc capacitor voltages, and dc output voltage for an abrupt change in the load resistance  $(R_L)$  from  $40\Omega$  to  $20\Omega$ . As shown in Figs. 6(b) and (d), the line currents exhibit very fast response to this load change so as to track their references. The reference amplitude produced

by the PI controller is quite fast. Except for the transition period, the output voltage regulation is achieved as shown in Figs. 5(c) and (d). Clearly, the dynamic response of output voltage is slower than that of the line currents. However, such behavior is quite normal as the inner loop (current control) is usually much faster than the outer loop (dc voltage control) in such systems. On the other hand, the dc capacitor voltages are almost not influenced from the load change and are balanced at 200V.

Fig. 7 shows the steady-state responses of the line currents under unbalanced grid voltages. The amplitudes of grid voltages are  $110\sqrt{2}$ ,  $120\sqrt{2}$ , and  $130\sqrt{2}$ , respectively. Despite the  $\pm 8.3\%$  unbalanced grid voltages, the line currents are slightly affected and they are almost balanced. On the other hand, the other variables such as output voltage and dc capacitor voltages are controlled successfully.

Fig. 8 shows the dynamic responses of grid voltages, line currents, dc capacitor voltages, and output voltage obtained with and without capacitor voltage balancing control. Figs. 8(a), (b) and :(c) show the simulation results where the capacitor voltage balancing control was enabled from t = 0.1sto t = 0.155s and disabled during the interval from t = 0.155sto t = 0.2s. It is apparent that the output voltage, line current and capacitor voltage control are achieved successfully. However, when the capacitor voltage balancing control is disabled at t = 0.155s, an imbalance exists in the capacitor voltages such that the upper capacitor voltage  $(V_{C1})$  becomes larger than the lower capacitor voltage  $(V_{C2})$ . The experimental result corresponding to this case is presented in Fig. 8(d). Comparing simulation and experimental results obtained when the capacitor voltage balancing control was active, one can see that both results are in good agreement. On the other hand, although the simulation and experimental results obtained without capacitor voltage balancing control agree well, there is a slight difference in the behavior of capacitor voltages immediately after the capacitor voltage balancing control is disabled. Nevertheless, addition of  $V_{C1}$  and  $V_{C2}$ always equal to  $V_{dc}$ .

#### VI. CONCLUSION

A SMC approach is presented for three-phase three-level Ttype rectifiers with capacitor voltage balancing control. The proposed SMC strategy is formulated in the abc frame rather than the dq frame. The consequence of designing the current control strategy in the abc frame eliminates the three-phase current transformations that would be needed if the design is made in the dq frame. The dc voltage regulation is achieved by a PI controller which guarantees zero steady-state error in the output voltage. On the other hand, another important contribution of this work is the dc capacitor voltages balancing which is accomplished by using a proportional control. The proportional control feeds the dc capacitor voltages error through a suitable gain into the line current references. As a consequence of this feedback, the imbalance between the capacitor voltages is eliminated. The effectiveness of the proposed control strategy is validated by simulation and

experimental studies during steady-state, transients caused by load change, and unbalanced grid. The results show excellent steady-state as well as dynamic performances with low THD in the line currents, zero steady-state error in the output voltage, and very fast dynamic response.

#### **REFERENCES**

- B. Guo, F. Wang, and E. Aeloiza, "A novel three-phase current source rectifier with delta-type input connection to reduce the device conduction loss," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1074–1084, Feb. 2016

- [2] H. Komurcugil and O. Kukrer, "Lyapunov-based control for three-phase PWM AC/DC voltage-source converters," *IEEE Trans. Power Electron.*, vol. 13, no. 5, pp. 801–813, Sep. 1998.

- [3] H. Komurcugil and O. Kukrer, "A novel current-control method for three-phase PWM AC/DC voltage-source converters," *IEEE Trans. Ind. Electron.*, vol. 46, no. 3, pp. 544–553, Jun. 1999.

- [4] C. Sui, Y. He, and M. Chen, "Analysis of current distortion of three-phase voltage source rectifiers and its application in fault diagnosis," *IEEE Access*, vol. 8, pp. 4065–4075, 2020.

- [5] J. Liang, H. Wang, and Z. Yan, "Grid voltage sensorless model-based predictive power control of PWM rectifiers based on sliding mode virtual flux observer," *IEEE Access*, vol. 7, pp. 24007–24016, 2019

- [6] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Pérez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [7] J. D. Barros, J. F. A. Silva, and E. G. A. Jesus, "Fast-predictive optimal control of NPC multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 2, pp. 619–627, Feb. 2013.

- [8] A. Hamid Bhat, P. Agarwal, N. Langer, and D. Sharma, "Capacitor voltage balancing of a three-phase neutral-point clamped bi-directional rectifier using optimised switching sequences," *IET Power Electron.*, vol. 6, no. 6, pp. 1209–1219, Jul. 2013.

- [9] Y. Yin, J. Liu, J. A. Sánchez, L. Wu, S. Vazquez, J. I. Leon, and L. G. Franquelo, "Observer-based adaptive sliding mode control of NPC converters: An RBF neural network approach," *IEEE Trans. Power Electron.*, vol. 34, no. 4, pp. 3831–3842, Apr. 2019.

- [10] C. A. Teixeira, D. G. Holmes, and B. P. McGrath, "Single-phase semi-bridge five-level flying-capacitor rectifier," *IEEE Trans. Ind. Appl.*, vol. 49, no. 5, pp. 2158–2166, Sep. 2013.

- [11] C. Liu, J. Wang, G. Cai, M. Wang, N. Huang, and F. Zhao, "Novel individual voltage balancing control scheme for multilevel cascade activefront-end rectifier," *IET Power Electron.*, vol. 7, no. 1, pp. 50–59, Jan. 2014.

- [12] Y. Ounejjar, K. Al-Haddad, and L. A. Dessaint, "A novel six-band hysteresis control for the packed u cells seven-level converter: Experimental validation," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3808–3816, Oct. 2012.

- [13] J.-S. Lee and K.-B. Lee, "An open-switch fault detection method and tolerance controls based on SVM in a grid-connected T-type rectifier with unity power factor," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 7092–7104, Dec. 2014.

- [14] J.-I. Itoh, Y. Noge, and T. Adachi, "A novel five-level three-phase PWM rectifier with reduced switch count," *IEEE Trans. Power Electron.*, vol. 26, no. 8, pp. 2221–2228, Aug. 2011.

- [15] D. Mukherjee and D. Kastha, "A reduced switch hybrid multilevel unidirectional rectifier," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 2070–2081, Mar. 2019.

- [16] H. Cheng, J. Kong, P. Wang, and C. Wang, "Hybrid control scheme for three-phase multilevel unidirectional rectifier under unbalanced input voltages," *IEEE Access*, vol. 7, pp. 29989–30001, 2019.

- [17] M. Schweizer and J. W. Kolar, "Design and implementation of a highly efficient three-level T-type converter for low-voltage applications," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 899–907, Feb. 2013.

- [18] M. Schweizer, T. Friedli, and J. W. Kolar, "Comparative evaluation of advanced three-phase three-level inverter/converter topologies against twolevel systems," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5515–5527, Dec. 2013.

- [19] J. Chen, C. Zhang, X. Xing, and A. Chen, "A fault-tolerant control strategy for T-type three-level rectifier with neutral point voltage balance and loss reduction," *IEEE Trans. Power Electron.*, early access, 2019, doi: 10.1109/TPEL.2019.2955600.

- [20] J.-S. Lee, U.-M. Choi, and K.-B. Lee, "Comparison of tolerance controls for open-switch fault in a grid-connected T-type rectifier," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5810–5820, Oct. 2015.

- [21] P. Alemi, S.-Y. Jeong, and D.-C. Lee, "Active damping of LLCL filters using PR control for grid-connected three-level T-type converters," J. Power Electron., vol. 15, no. 3, pp. 786–795, May 2015.

- [22] D. O. Boillat, F. Krismer, and J. W. Kolar, "EMI filter volume minimization of a three-phase, three-level T-type PWM converter system," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2473–2480, Apr. 2017.

- [23] K. Sun, X. Lin, Y. Li, Y. Gao, and L. Zhang, "Improved modulation mechanism of parallel-operated T-type three-level PWM rectifiers for neutral-point potential balancing and circulating current suppression," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 7466–7479, Sep. 2018.

- [24] J. Chen, C. Zhang, A. Chen, X. Xing, and F. Gao, "A carrier-based fault-tolerant control strategy for T-Type rectifier with neutral-point voltage oscillations suppression," *IEEE Trans. Power Electron.*, vol. 34, no. 11, pp. 10988–11001, Nov. 2019.

- [25] S. A. Khan, Y. Guo, and J. Zhu, "Model predictive observer based control for single-phase asymmetrical T-Type AC/DC power converter," *IEEE Trans. Ind. Appl.*, vol. 55, no. 2, pp. 2033–2044, Mar./Apr. 2019.

- [26] S. Foti, A. Testa, G. Scelba, V. Sabatini, A. Lidozzi, and L. Solero, "A low THD three-level rectifier for gen-set applications," *IEEE Trans. Ind. Appl.*, vol. 55, no. 6, pp. 6150–6160, Nov./Dec. 2019.

- [27] S. A. Khan, Y. Guo, Y. P. Siwakoti, D. D.-C. Lu, and J. Zhu, "A disturbance rejection based control strategy for five-level T-type hybrid power converters with ripple voltage estimation capability," *IEEE Trans. Ind. Electron.*, early access, 2019, doi: 10.1109/TIE.2019.2942550.

- [28] H. Komurcugil, "Rotating-sliding-line-based sliding-mode control for single-phase UPS inverters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3719–3726, Oct. 2012.

- [29] M. Salimi, A. Zakipour, N. R. Abjadi, and J. Soltani, "Hyper-plane sliding mode control of the DC–DC buck/boost converter in continuous and discontinuous conduction modes of operation," *IET Power Electron.*, vol. 8, no. 8, pp. 1473–1482, Aug. 2015.

- [30] H. Komurcugil, S. Ozdemir, I. Sefa, N. Altin, and O. Kukrer, "Sliding-mode control for single-phase grid-connected LCL-filtered VSI with double-band hysteresis scheme," *IEEE Trans. Ind. Electron.*, vol. 63, no. 2, pp. 864–873, Feb. 2016.

- [31] J. Liu, S. Vazquez, L. Wu, A. Marquez, H. Gao, and L. G. Franquelo, "Extended state observer-based sliding-mode control for three-phase power converters," *IEEE Trans. Ind. Electron.*, vol. 64, no. 1, pp. 22–31, Jan. 2017.

- [32] H. Komurcugil and S. Biricik, "Time-varying and constant switching frequency-based sliding-mode control methods for transformerless DVR employing half-bridge VSI," *IEEE Trans. Ind. Electron.*, vol. 64, no. 4, pp. 2570–2579, Apr. 2017.

- [33] E. V. N. De Souza, E. C. Dos Santos, J. A. A. Dias, and E. L. L. Fabricio, "Sliding mode control applied on a three-level single-phase T-converter rectifier," in *Proc. IEEE 13th Brazilian Power Electron. Conf., 1st South*ern Power Electron. Conf. (COBEP/SPEC), Nov. 2015, pp. 1–6.

- [34] H. Komurcugil and S. Bayhan, "Sliding mode control strategy for three-phase three-level T-type PWM rectifiers with capacitor voltage imbalance compensation," in *Proc. 45th Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Oct. 2019, pp. 5020–5025.

- [35] S. Xu, J. Zhang, Y. Huang, and J. Jatskevich, "Dynamic average-value modeling of three-level T-type grid-connected converter system," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 4, pp. 2428–2442, Dec. 2019.

- [36] H. Komurcugil, S. Biricik, and N. Guler, "Indirect sliding mode control for DC–DC SEPIC converters," *IEEE Trans Ind. Informat.*, vol. 16, no. 6, pp. 4099–4108, Jun. 2020.

- [37] V. Utkin, J. Guldner, and J. Shi, Sliding Mode Control in Electromechanical Systems. London, U.K.: CRC Press, 1999.

- [38] S. Ding, W. X. Zheng, J. Sun, and J. Wang, "Second-order sliding-mode controller design and its implementation for buck converters," *IEEE Trans. Ind. Informat.*, vol. 14, no. 5, pp. 1990–2000, May 2018.

- [39] IEEE 519 Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems, IEEE Standard 519-2014, 1993.

**SERTAC BAYHAN** (Senior Member, IEEE) received the bachelor's degree in valedictorian, and the M.Sc. and Ph.D. degrees in electrical engineering from Gazi University, Ankara, Turkey, in 2008 and 2012, respectively.

In 2008, he joined the Electronics and Automation Engineering Department, Gazi University, as a Lecturer, where he was promoted to an Assistant Professor and an Associate Professor, in 2013 and 2017, respectively. From 2014 to 2018, he also

worked with Texas A&M University, Qatar, as an Associate Research Scientist. He is currently working with the Qatar Environment and Energy Research Institute (QEERI), as a Scientist. He has led several international projects. He has authored 150 high-impact journal and conference papers. His research interests include the areas of advanced control of PV systems, microgrids, and smart grid applications. He is a coauthor of two books and four book chapters. Because of the visibility of his research, he has been elected as the Chair of IES Power Electronics Technical Committee. He also serves as an Associate Editor for the IEEE Transactions on Industrial Electronics, the IEEE Journal of Emerging and Selected Topics In Industrial Electronics, and the IEEE IES Industrial Electronics Technology News, and Guest Editor for the IEEE Transactions on Industrial Informatics.

HASAN KOMURCUGIL (Senior Member, IEEE) received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from Eastern Mediterranean University (EMU), Famagusta, Turkey, in 1989, 1991, and 1998, respectively. In 1998, he joined the Computer Engineering Department, EMU, as an Assistant Professor, where he was promoted to an Associate Professor and a Professor, in 2002 and 2008, respectively. From 2004 to 2010, he was the Head of the Computer Engineer-

ing Department, EMU. In 2010, he played an active role in preparing the department's first self-study report for the use of Accreditation Board for Engineering and Technology. From 2010 to 2019, he has served as the Board Member of Higher Education, Planning, Evaluation, Accreditation and Coordination Council (YODAK) North Cyprus. He is currently a fulltime Professor with the Computer Engineering Department, EMU. His research interests include power electronics and innovative control methods for power converters. He was a recipient of the Best Presentation Recognitions at the 41st and 42nd Annual Conferences of the IEEE Industrial Electronics Society, in 2015 and 2016, respectively. He was a corresponding Guest Associate Editor of Emerging Electric Machines and Drives for Smart Energy Conversion in the IEEE Transactions on Energy Conversion. He is also a Guest Editor of Identification and Observation Informatics for Energy Generation, Conversion, and Applications and Recent Advances on Sliding Mode Control and Its Applications in Modern Industrial Systems in the IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS. He is also an Associate Editor of the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS and the IEEE TRANSACTIONS ON Industrial Informatics.

. . .