Open access • Proceedings Article • DOI:10.1109/PESC.2004.1354761

# Small-signal z-domain analysis of digitally controlled converters — Source link <a> ☐</a>

D.M. Van de Sype, K. De Gusseme, A.R. Van den Bossche, Jan Melkebeek

**Institutions:** Ghent University

Published on: 20 Jun 2004 - Power Electronics Specialists Conference

Topics: Digital control, Digital signal processor, Frequency domain, Converters and Control system

### Related papers:

- Quantization resolution and limit cycling in digitally controlled PWM converters

- Small-signal Laplace-domain analysis of uniformly-sampled pulse-width modulators

- · Impact of digital control in power electronics

- High-frequency digital PWM controller IC for DC-DC converters

- · Modeling of Quantization Effects in Digitally Controlled DC-DC Converters

## Small-Signal z-Domain Analysis of Digitally Controlled Converters

David M. Van de Sype\*, Koen De Gussemé, Alex P. Van den Bossche, and Jan A. Melkebeek Electrical Energy Laboratory

Department of Electrical Energy, Systems and Automation, Ghent University St-Pietersnieuwstraat 41, B-9000 Gent, Belgium \*Email: VandeSype@Lambda.UGent.be

Abstract—As the performance of digital signal processors has increased rapidly during the last decade, there is a growing interest to replace the analog controllers in low power switching converters by more complicated and flexible digital control algorithms. Compared to high power converters, the control loop bandwidths for converters in the lower power range are generally much higher. Because of this, the dynamic properties of the uniformly-sampled pulse-width modulators used in low power applications become an important restriction to the maximum achievable bandwidth of control loops. Though frequency- and Laplace-domain models for uniformly-sampled pulse-width modulators are very valuable as they improve the general perception of the dynamic behavior of these modulators, the direct discrete design of the digital compensator requires a zdomain model for the combination modulator and converter. For this purpose a new exact small-signal z-domain model is derived. In accordance with the zero-order-hold equivalent commonly used for 'regular' digital control systems, this z-domain model gives rise to the development of a uniformly-sampled pulse-widthmodulator equivalent of the converter. This z-domain model is characterized by its capability to quantify the different dynamics of the converter for different modulators, its ease of use and its ability to predict the values of the control variables at the true sampling instants of the real system.

### I. INTRODUCTION

For reasons of price, control circuits for low power switching power supplies (<3 kW) are almost always implemented using analog circuits. As the price/performance ratio of digital signal processors has decreased rapidly during the last decade, the interest for digital control of switching power supplies in the low power range has grown [1], [2]. When applying digital control to a switching power supply, the different switches in the supply are often controlled by a digital or uniformlysampled pulse-width modulator. Consequently, the dynamics of a digitally controlled switching power supply are influenced by two nonlinear effects: quantization effects and modulation effects. As the effects of quantization in digital control of switching power supplies have been addressed before [3], [4], this study focuses on modulation effects. Frequencyand Laplace-domain models of the modulators [5] provide insight in the fundamental dynamic behavior of uniformlysampled pulse-width modulators. However, the design of the compensator must be performed in the Laplace-domain. This Laplace transfer function is afterwards translated into a discrete equivalent by approximation methods such as the trapezoidal-rule, pole-zero mapping, etc. To avoid this indirect design method for the discrete compensator, a z-domain model for the combination converter-modulator is required. Discretetime models have already been reported [6] but their use in control is limited because of the presence of matrix exponentials and other highly nonlinear vector functions. Though

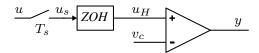

Fig. 1. A general uniformly-sampled pulse-width modulator

approximations of this bilinear discrete-time model such as [7] provide a good solution to this problem, the usability of these models is further restrained because they are only derived for an end-of-on-time modulator and because they describe the behavior of the control variable values at the beginning of the switching cycle instead of at the sampling instants of the real digital control system. After all, the sampling instants in a real digital control system can be positioned anywhere in the switching cycle.

To overcome these problems a new exact small-signal z-domain model is derived based on the Laplace-domain analysis presented in [5]. In accordance with the zero-order-hold equivalent commonly used for 'regular' digital control systems, this z-domain model gives rise to the development of a uniformly-sampled pulse-width-modulator equivalent of the converter. This z-domain model is characterized by its capability to quantify the different dynamics of the converter for different modulators, its ease of use as this approach uses only the modified z-transform rather than complex functions, and its ability to predict the values of the control variables at the true sampling instants of the real system. The method is validated and demonstrated on a digitally controlled buck converter by comparing the samples predicted by the model with the simulated waveforms retrieved from a Simulink model.

### II. Uniformly-Sampled Pulse-Width Modulators

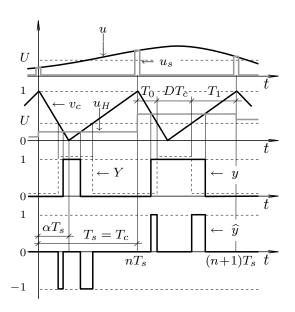

The pulse-width modulators embedded in modern digital signal processors (e.g. TMS320C2XX of Texas Instruments, ADSP2199X of Analog Devices, DSP568XX of Motorola, etc.) operate all in a similar fashion. If we disregard quantization effects, a model for the uniformly-sampled pulsewidth modulator is shown in Fig. 1. The input u(t), a continuous function of time, is sampled with a frequency  $\omega_s$  synchronously to the pulse-width modulation (Fig. 1). For the derivation of the z-domain model only modulators with a switching frequency equal to the sampling frequency  $\omega_s$  (single-update-mode) are considered. The sampled input  $u_s(t)$  is sent to a zero-order-hold circuit (ZOH). Finally, the PWM waveform is generated by comparing the output of the ZOH  $u_H(t)$  to the value of the carrier waveform  $v_c(t)$ , a triangular waveform. Depending on the shape of the carrier waveform

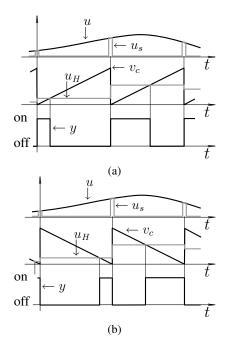

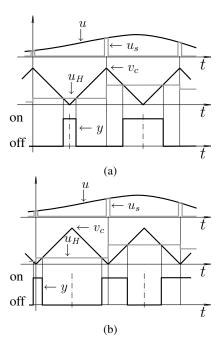

Fig. 2. The single-update-mode sawtooth-carrier modulators. (a): end-of-on-time, (b): begin-of-on-time

$v_c(t)$  different types of uniformly-sampled pulse-width modulators can be obtained. In commercial digital controllers two possibilities are commonly offered: the carrier waveform is either a sawtooth-carrier Fig. 2 or an isosceles-triangular-carrier Fig. 3. When the carrier  $v_c$  is a sawtooth carrier the commonly available types are the end-of-on-time modulator Fig. 2(a) and the begin-of-on-time modulator Fig. 2(b). For modulators with an isosceles-triangular-carrier waveform, two modulators can be identified: the symmetric-on-time modulator Fig. 3(a) and the symmetric-off-time modulator Fig. 3(b).

### III. Z-DOMAIN ANALYSIS

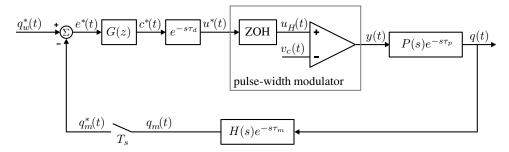

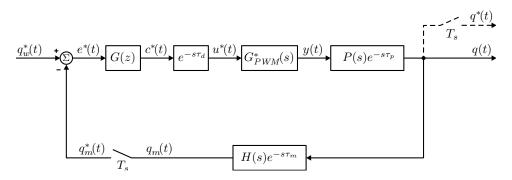

If we assume that the response of the output of the converter q(t) to a change in the output of the uniformly-sampled pulsewidth modulator can be described by the Laplace transfer function  $P(s)e^{-s\tau_p}$ , the schematic of the control loop can be represented as in Fig. 4. The controlled output of the converter q(t) is converted by a measurement with transfer function  $H(s)e^{-s au_m}$  into the measured output  $q_m(t)$ . The latter is sampled by the analog-to-digital converter of the microcontroller; the output of the sampler is  $q_m^*(t)$ . Comparing this measured value to its desired value  $q_w^*(t)$  yields the sampled error  $e^*(t)$ . The digital compensator with pulse-transfer function G(z)derives the control output  $c^*(t)$  from this error. To account for the duration of the control calculations (calculations for the output of G(z) in the processor, a calculation delay  $\tau_d$  is introduced. The delayed control signal  $u^*(t)$  is the sampled input of the modulator. The latter transforms the sampled input  $u^*(t)$  into the switching function y(t), a continuous function of time. If the pulse-width modulator can be modelled by a pulseto-continuous transfer function  $G_{PWM}^*(s)$  describing in the Laplace domain the change of the modulator output y(t) as a function of the sampled input  $u^*(t)$ , the model of Fig. 4 can be simplified to that of Fig. 5. Note that this pulse-to-continuous

Fig. 3. The single-update-mode triangular-carrier modulators. (a): symmetric-on-time, (b): symmetric-off-time

transfer function for the modulator  $G^*_{PWM}(s)$  is in accordance with the model commonly employed for a regular control system with zero-order-hold  $(G^*_{ZOH}(s) = (1-e^{-sT_s})/s)$ .

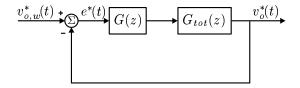

If a hypothetical sampler with sampling period  $\omega_s$  is introduced on the output of the converter q(t), the sampled output  $q^*(t)$  is obtained. By using the z-transform, the sampled output  $q^*(t)$  can be expressed as a function of the commanded output  $q^*_w(t)$ :

$$\frac{Q(z)}{Q_w(z)} = \frac{G(z)\mathcal{Z}\left\{e^{-s(\tau_d + \tau_p)}G_{PWM}^*(s)P(s)\right\}}{1 + G(z)\mathcal{Z}\left\{e^{-s(\tau_d + \tau_p + \tau_m)}G_{PWM}^*(s)P(s)H(s)\right\}},$$

(1)

with Q(z) and  $Q_w(z)$  the z-transforms of  $q^*(t)$  and  $q_w^*(t)$ , respectively. Equation (1) clearly shows that the problem of calculating the sampled output of a converter with a digital control loop can be reduced to the problem of finding the z-transform of

$$G_{tot}(z) = \mathcal{Z}\left\{e^{-sT_{\Delta}}G_{PWM}^{*}(s)R(s)\right\}$$

(2)

or the calculation of the z-transform of the characteristic system as depicted in Fig. 6. Before the z-transform for the characteristic system can be calculated, the pulse-to-continuous transfer function of a uniformly-sampled pulse-width modulator must be derived.

The derivation of the pulse-to-continuous transfer function  $G_{PWM}^*(s)$  of the digital pulse-width modulator is based upon the small-signal Laplace-domain analysis presented in [5]. This Laplace-domain analysis uses the waveforms of the general single-update-mode modulator (Fig. 7). This modulator has a triangular waveshape as carrier waveform  $v_c(t)$  determined by the period  $T_c$  and the ratio  $\alpha$ . The ratio  $\alpha$  is the duration of the falling edge of the triangle relative to the period  $T_c = T_s$  (Fig. 7). Choosing  $\alpha$  equal to 0, 1/2 and 1 allows to obtain the waveforms for the end-of-on-time

Fig. 4. A model for the control loop of a digitally controlled converter with the pulse-width modulator modelled by a pulse-to-continuous transfer function

Fig. 5. A model for the control loop of a digitally controlled converter with the pulse-width modulator modelled by a pulse-to-continuous transfer function

Fig. 6. The characteristic system consisting of a linear system, a transportation delay and the uniformly sampled pulse-width modulator

Fig. 7. The key waveforms for a general single-update-mode modulator

modulator, the symmetric-on-time modulator and the beginof-on-time modulator respectively. Hence, three out of four different single-update-mode modulators can be analyzed in a unified way.

The input of the modulator u(t) is separated into a steady-state part U (a constant) and a small excursion to this steady-

state

$$\widehat{u}(t)$$

, or

$$u(t) = U + \widehat{u}(t). \tag{3}$$

The resulting output of the modulator y(t) can also be separated into a steady-state portion Y(t) (the response to U) and a small excursion to the steady-state  $\widehat{y}(t)$ , or

$$y(t) = Y(t) + \widehat{y}(t). \tag{4}$$

By using the Laplace-domain analysis of [5], the small-signal output  $\widehat{y}(t)$  of the modulator can be expressed as a function of the sampled version  $\widehat{u}^*(t)$  of the small-signal input  $\widehat{u}(t)$  of the modulator (see [5])

$$\hat{Y}(s) = T_s \left( \alpha e^{-sT_0} + (1 - \alpha)e^{-s(T_s - T_1)} \right) \hat{U}^*(s),$$

(5)

with  $T_0$ ,  $T_1$  and  $\alpha$  defined in Fig. 7. In accordance with the analysis used for a zero-order-hold in a 'regular' digital control system [8], a pulse-to-continuous Laplace transfer function can be derived from the equation above

$$G_{PWM}^{*}(s) = \frac{\widehat{Y}(s)}{\widehat{U}^{*}(s)} = T_{s} \left( \alpha e^{-sT_{0}} + (1 - \alpha)e^{-s(T_{s} - T_{1})} \right).$$

(6)

If (6) is substituted in (2), the z-domain model for the characteristic system can be calculated.

### A. The UPWM-equivalent for the end-of-on-time modulator

As an example the z-domain model of the characteristic system is derived for an end-of-on-time modulator. For this modulator the following applies:  $\alpha=0$  and  $T_1=(1-D)T_s$ , with D (= U) the average duty-ratio. With these parameter values, substitution of (6) in (2) yields

$$G_{tot}(z) = T_s \mathcal{Z} \left\{ e^{-sT_{\Delta}} R(s) e^{-sDT_s} \right\}$$

$$= T_s \mathcal{Z} \left\{ e^{-s(\zeta + D)T_s} R(s) \right\}, \tag{7}$$

TABLE I

THE UPWM-EQUIVALENT OF THE CHARACTERISTIC SYSTEM: (a) THE END-OF-ON-TIME MODULATOR, (b) THE BEGIN-OF-ON-TIME MODULATOR

$\begin{array}{|c|c|c|}\hline \text{condition} & G_{tot}(z) \\ \hline 0 < \zeta < (1-D) & T_s R(z, 1-D-\zeta) \\ \hline \end{array}$

case

1

2

TABLE II

THE UPWM-EQUIVALENT OF THE CHARACTERISTIC SYSTEM: (a) THE SYMMETRIC-ON-TIME MODULATOR, (b) THE SYMMETRIC-OFF-TIME MODULATOR

(a)

| case | condition                                     | $G_{tot}(z)$                                                                                             |

|------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 1    | $0 < \zeta < \frac{1}{2}(1-D)$                | $\frac{T_s}{2} \left[ R(z, \frac{1}{2}(1+D) - \zeta) + R(z, \frac{1}{2}(1-D) - \zeta) \right]$           |

| 2    | $\frac{1}{2}(1-D) < \zeta < \frac{1}{2}(1+D)$ | $\frac{T_s}{2} \left[ R(z, \frac{1}{2}(1+D) - \zeta) + z^{-1}R(z, 1 + \frac{1}{2}(1-D) - \zeta) \right]$ |

| 3    | $\frac{1}{2}(1+D) < \zeta < 1$                | $\frac{T_s}{2}z^{-1}\Big[R(z,1+\frac{1}{2}(1+D)-\zeta)+R(z,1+\frac{1}{2}(1-D)-\zeta)\Big]$               |

(b)

| case | condition                                | $G_{tot}(z)$                                                                                                     |

|------|------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 1    | $0 < \zeta < \frac{D}{2}$                | $\frac{T_s}{2} \left[ R\left(z, \frac{1}{2}(2-D) - \zeta\right) + R\left(z, \frac{1}{2}D - \zeta\right) \right]$ |

| 2    | $\frac{D}{2} < \zeta < \frac{1}{2}(2-D)$ | $\frac{T_s}{2} \left[ R(z, \frac{1}{2}(2-D) - \zeta) + z^{-1}R(z, 1 + \frac{1}{2}D - \zeta) \right]$             |

| 3    | $\frac{1}{2}(2-D) < \zeta < 1$           | $\frac{T_s}{2}z^{-1}\Big[R(z,1+\frac{1}{2}(2-D)-\zeta)+R(z,1+\frac{1}{2}D-\zeta)\Big]$                           |

with  $\zeta T_s = T_\Delta$ . As in most cases the total delay  $T_\Delta$  is smaller than the sampling period  $T_s$ ,  $\zeta$  is comprised between 0 and 1 and two cases can be distinguished

$$\begin{cases}

G_{tot}(z) = T_s \mathcal{Z} \left\{ e^{-s(\zeta+D)T_s} R(s) \right\} & \text{for } \zeta+D < 1 \\

G_{tot}(z) = T_s z^{-1} \mathcal{Z} \left\{ e^{-s(\zeta+D-1)T_s} R(s) \right\} & \text{for } \zeta+D > 1

\end{cases}$$

(8)

If the modified z-transform of R(s) is defined as

$$R(z,m) = \mathcal{Z}_m\{R(s)\} = \mathcal{Z}\left\{e^{-s(1-m)T_s}R(s)\right\}, \qquad (9)$$

equation (8) can be transformed into

$$\begin{cases}

G_{tot}(z) = T_s R(z, 1 - D - \zeta) & \text{for } \zeta + D < 1 \\

G_{tot}(z) = T_s z^{-1} R(z, 2 - D - \zeta) & \text{for } \zeta + D > 1

\end{cases}$$

(10)

This model  $G_{tot}(z)$  is the uniformly-sampled pulse-width-modulator equivalent or UPWM-equivalent for an end-of-on-time modulator of the transfer function  $R(s)e^{-sT_{\Delta}}$ . A summary of the z-domain models of the characteristic system for an end-of-on-time modulator with their corresponding conditions is shown in Table I(a).

The UPWM-equivalent for the begin-of-on-time modulator, the other sawtooth-carrier modulator, can be derived in a similar way. Though the calculation is omitted, the results are tabulated in Table I(b). Note that the z-domain models for the

begin-of-on-time modulator can be deduced from the z-domain models for the end-of-on-time modulator by substituting the average duty ratio D in the latter with the complement of the average duty-ratio 1-D, and vice-versa (compare Tables I(a) and I(b)).

B. The UPWM-equivalent for the symmetric-on-time modulator

As another example the UPWM-equivalent of the characteristic system for a triangular-carrier modulator, the symmetric-on-time modulator, is derived. The waveforms of the symmetric-on-time modulator can be obtained by choosing  $\alpha = 1/2$  in Fig. 7. For this modulator the parameters  $T_0$  and  $T_1$  are defined as  $T_0 = T_1 = \frac{T_s}{2}(1-D)$ . By using  $T_\Delta = \zeta T_s$  the UPWM-equivalent of the characteristic system can be expressed as

$$G_{tot}(z) = \frac{T_s}{2} \mathcal{Z} \left\{ \left( e^{-s\left(\zeta + \frac{1-D}{2}\right)T_s} + e^{-s\left(\zeta + \frac{1+D}{2}\right)T_s} \right) R(s) \right\}.$$

(11)

Depending on whether the different delays in (11) are larger than the sampling period  $T_s$  or not, and taking into account that  $\zeta$  is almost always smaller than 1, three different cases can be distinghuised. In the first case, defined by  $0 < \zeta < \frac{1}{2}(1-D)$ , equation (11) can be rewritten by using the definition for the

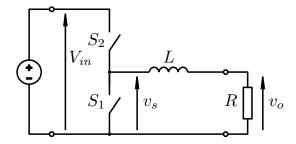

Fig. 8. A buck converter with a first order filter

modified z-transform of (9)

$$G_{tot}(z) = \frac{T_s}{2} \left[ R\left(z, \frac{1}{2}(1+D) - \zeta\right) + R\left(z, \frac{1}{2}(1-D) - \zeta\right) \right]. \quad (12)$$

If the following applies  $\frac{1}{2}(1-D) < \zeta < \frac{1}{2}(1+D)$ , the second transportation delay in (11) becomes larger than the sampling period  $T_s$ . Consequently, the UPWM-equivalent of the characteristic system becomes

$$G_{tot}(z) = \frac{T_s}{2} \left[ R\left(z, \frac{1}{2}(1+D) - \zeta\right) + z^{-1}R\left(z, 1 + \frac{1}{2}(1-D) - \zeta\right) \right].$$

(13)

In the last case were  $\zeta$  is comprised between  $\frac{1}{2}(1+D)$  and 1, both delays in (11) are larger than the sampling period. Hence, the UPWM-equivalent of the characteristic system can be expressed as

$$G_{tot}(z) = \frac{T_s}{2} z^{-1} \left[ R\left(z, 1 + \frac{1}{2}(1+D) - \zeta\right) + R\left(z, 1 + \frac{1}{2}(1-D) - \zeta\right) \right]. \tag{14}$$

The z-domain models of the characteristic system for the symmetric-on-time modulator (12)–(14) with their corresponding conditions are recapitulated in Table II(a).

Similar calculations are performed to derive the z-domain models of the characteristic system for a symmetric-off-time modulator. Though the derivation of these models is not explicitly repeated, the results are summarized in Table II(b). Similar to sawtooth-carrier modulators, the UPWM-equivalents for the symmetric-off-time modulator can be obtained by replacing D with its complement 1-D in the UPWM-equivalents for the symmetric-on-time modulator, and vice-versa (compare Tables II(a) and II(b)).

## IV. MODEL VALIDATION

To show the validity of the approach, the discrete UPWM-equivalent is deduced for the buck converter of Fig. 8 with a first order output filter. If the input voltage  $V_{in}$  of the converter is a constant, the Laplace transfer function of its output can be written as (see also Figs. 4 and 5)

$$P(s) = \frac{V_{in}}{1 + sL/R} = \frac{V_{in}}{1 + s\tau}.$$

(15)

Under the assumption that the transfer function of the measurement is given by

$$H(s)e^{-s\tau_m} = 1, (16)$$

Fig. 9. Block diagram for the digitally controlled buck converter

the pulse-transfer function of the closed loop system can be written as

$$\frac{Q(z)}{Q_w(z)} = \frac{V_o(z)}{V_{o,w}(z)}

= \frac{G(z)\mathcal{Z}\left\{e^{-s(\tau_d + \tau_p)}G_{PWM}^*(s)P(s)\right\}}{1 + G(z)\mathcal{Z}\left\{e^{-s(\tau_d + \tau_p)}G_{PWM}^*(s)P(s)\right\}}.$$

(17)

To calculate this transfer function, the delay  $\tau_d + \tau_p$  and the type of modulator used must be known.

Assume that during normal operation the average duty ratio D of the converter is between 0.5 and 1, and that the following condition applies for the delay

$$\tau_d + \tau_p = \zeta T_s \ge 0.35 T_s,\tag{18}$$

than the type of modulator and its corresponding UPWM-equivalent can be chosen.

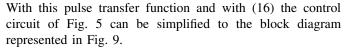

If the different cases for the z-domain models in Tables I and II are compared, it is clear that "case 1" guarantees the fastest dynamics of the system. After all, in the other cases an extra pole appears in the origin, indicating an extra delay of a sampling period. Hence, the fastest response of the closed loop system is achievable with a modulator for which the "case 1" condition can be met. Keeping in mind the required duty-ratio range and condition (18), the beginof-on-time modulator (Table I(b), case 1) is the best choice. If only triangular-carrier modulators are considered (Table II), the "case 1" condition can never be met. Hence, for these type of modulators the best solution is to look for a modulator for which the "case 2" condition is fulfilled. Consequently, the fastest usable triangular-carrier modulator is the symmetricon-time modulator (Table II(a), case 2). For both the beginof-on-time modulator and the symmetric-on-time modulator the discrete UPWM-equivalent of the buck converter with a first order filter is derived and simulated in this section.

### A. The begin-of-on-time modulator

To calculate the UPWM-equivalent of the buck converter of Fig. 8, an expression for the modified pulse transfer function of the first order system (15) is required:

$$P(z,m) = \mathcal{Z} \Big\{ P(s)e^{-s(1-m)T_s} \Big\}$$

$$= V_{in} \frac{1}{\tau} e^{-\frac{mT_s}{\tau}} \frac{1}{z - e^{-\frac{T_s}{\tau}}}.$$

(19)

Hence, the discrete UPWM-equivalent of the buck converter with a first order filter and with a begin-of-on-time modulator becomes (Table I(b), case 1)

$$G_{tot}(z) = V_{in} \frac{T_s}{\tau} e^{-\frac{(D-\zeta)T_s}{\tau}} \frac{1}{z - e^{-\frac{T_s}{\tau}}}.$$

(20)

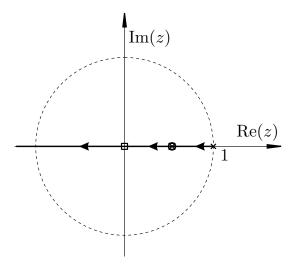

Fig. 10. The root locus for a buck converter with a first order filter, a begin-of-on-time modulator and a discrete controller

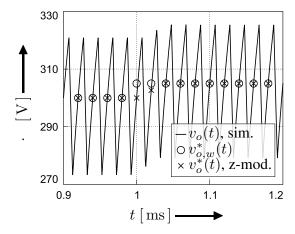

Fig. 11. The closed-loop response of the buck converter with a first order filter and a begin-of-on-time modulator to a step in the commanded output voltage  $(v_{o,w}^*(t))$ : the simulated model  $(v_o(t), \text{sim.})$  and the z-domain model  $(v_o^*(t), \text{z-mod.})$

If the steady-state error of the control loop of Fig. 9 must be zero, the controller G(z) requires a pole at z=1. Furthermore, a zero of the controller can be used to compensate for the pole of the process (20) at  $z=e^{-\frac{T_s}{\tau}}$ . The resulting controller is

$$G(z) = K \frac{z - e^{-\frac{T_s}{\tau}}}{z - 1}. (21)$$

The root locus of the closed loop system for a variable gain K is depicted in Fig. 10. Apart from the hidden mode at  $z = e^{-\frac{T_s}{\tau}}$  there remains only one closed loop pole that can be placed in the origin by choosing the gain of the controller as follows

$$K = \frac{1}{V_{in}} \frac{T_s}{\tau} e^{(D_o - \zeta) \frac{T_s}{\tau}},$$

(22)

with  $D_o$  the design value for the average duty ratio. Consequently the closed-loop system will behave as a delay of one sampling period or, the response is a dead-beat response. If the average duty-ratio D differs from its design value  $D_o$ , the loop

Fig. 12. The root locus for a buck converter with a first order filter, a symmetric-on-time modulator and a discrete controller

Fig. 13. The closed-loop response of the buck converter with a first order filter and a symmetric-on-time modulator to a step in the commanded output voltage  $(v_{o,w}^*(t))$ : the simulated model  $(v_o(t), \text{ sim.})$  and the z-domain model  $(v_o^*(t), \text{ z-mod.})$

gain will increase or decrease (20). As a result the position of the closed-loop pole in the origin will alter depending on the average value of the duty ratio. Nevertheless, with a duty-ratio range of 0.5 up to 1 and with a design value for the average duty-ratio of  $D_o\!=\!0.75$  this effect only results in a slight change in closed-loop response.

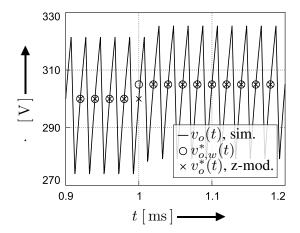

To verify the theoretical results the closed loop step response of the buck converter is simulated with Simulink. The simulated waveforms are compared to the results obtained with the z-domain model. For the simulation the following parameters were used

$$\begin{cases} V_{in} = 400 \text{ V}, & T_s = 20 \text{ } \mu\text{s}, \\ L = 1 \text{ mH}, & R = 32 \text{ } \Omega, \\ \zeta = 0.375, & D_o = 0.75. \end{cases}$$

(23)

The result is depicted in Fig. 11  $(D=D_o)$ . A comparison between the waveforms obtained with the Simulink model (the solid lines) and the step response of the z-domain model (crosses) shows that the z-domain model accurately predicts the closed-loop behavior of the digitally controlled buck

converter. Moreover, the step response is clearly a dead-beat response.

### B. The symmetric-on-time modulator

If a triangular-carrier modulator is to be used, the best choice is the symmetric-on-time modulator. The discrete UPWM-equivalent for the buck converter with a first order filter and a symmetric-on-time modulator can be calculated with (19) and Table II(a), case 2 (keeping in mind condition (18)):

$$G_{tot} = V_{in} \frac{T_s}{2\tau} e^{-\left(\frac{1}{2}(1+D)-\zeta\right)\frac{T_s}{\tau}} \cdot \frac{z + e^{-(1-D)\frac{T_s}{\tau}}}{z\left(z - e^{-\frac{T_s}{\tau}}\right)}.$$

(24)

This pulse transfer function does not only contain the same pole as the system of (20), but it also contains an extra pole in the origin and an extra zero. A dead-beat controller for this system is of the following form

$$G(z) = K \frac{z \left(z - e^{-\frac{T_s}{\tau}}\right)}{(z - 1)(z - a)},$$

(25)

with

$$a = -e^{-(1-D_o)\frac{T_s}{\tau}}. (26)$$

However, due to important changes in the position of the system zero at  $z=-e^{-(1-D)\frac{T_s}{\tau}}$  caused by the various values the average value of the duty ratio D may adopt (24), the closed-loop behavior may change drastically. To avoid this, it is better to choose a somewhat slower controller with a settling time of 2 sampling periods. To achieve this the closed-loop system should have a double pole in the origin, or the root locus should have a breakpoint in the origin. A root locus has a breakpoint in the origin if (for  $D\!=\!D_o$ )

$$\frac{\mathrm{d}}{\mathrm{d}z}(G(z)G_{tot}(z))\Big|_{z=0} = 0. \tag{27}$$

This equation yields a value for a

$$a = -\frac{e^{-(1-D_o)\frac{T_s}{\tau}}}{1 + e^{-(1-D_o)\frac{T_s}{\tau}}}.$$

(28)

The root locus of the closed loop poles with this value for a is depicted in Fig. 12. Besides the hidden mode at  $z=e^{-\frac{T_s}{\tau}}$ , the two closed-loop poles of the system coincide in the origin for

$$K = \frac{(1+a)}{V_{in}} \cdot \frac{2\tau}{T_s} e^{\left(\frac{1}{2}(1+D_o)-\zeta\right)\frac{T_s}{\tau}}.$$

(29)

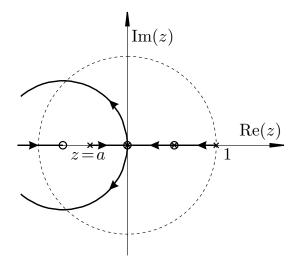

The simulation is performed for  $\zeta$ =0.5, while the other parameters are chosen according to (23). The closed-loop step response for the buck converter is shown in Fig. 13 (for D= $D_o$ ). The comparison between the simulation results (solid line) and the results predicted by the z-domain model

reveals the good agreement. As indicated above the settling time for a step response is equal to 2 sampling periods.

#### V. CONCLUSION

As the performance of digital signal processors has increased rapidly during the last decade, there is a growing interest to replace the analog controllers in low power switching converters by more complicated and flexible digital control algorithms. Compared to high power converters, the control loop bandwidths for converters in the lower power range are generally much higher. Because of this, the dynamic properties of the uniformly-sampled pulse-width modulators used in low power applications become an important restriction to the maximum achievable bandwidth of control loops. Though frequency- and Laplace-domain models for uniformly-sampled pulse-width modulators are very valuable as they improve the general perception of the dynamic behavior of these modulators, the direct discrete design of the digital compensator requires a z-domain model for the combination modulator and converter. For this purpose a new exact small-signal zdomain model is derived. In accordance with the zero-orderhold equivalent commonly used for 'regular' digital control systems, this z-domain model gives rise to the development of a uniformly-sampled pulse-width-modulator equivalent of the converter. This z-domain model is characterized by its capability to quantify the different dynamics of the converter for different modulators, its ease of use and its ability to predict the values of the control variables at the true sampling instants of the real system. The obtained z-domain models are compared with the results retrieved from simulation models of a buck converter with a first order filter.

### REFERENCES

- , "Power supply 'Digital Control'-Real or Virtual," RAP session, 18th Ann. Appl. Power Electron. Conf. and Exp. (APEC2003), Miami Beach, USA, Feb. 9-13, 2003.

- [2] , "Special issue on digital control in power electronics," *IEEE Trans. Power Electron.*, Vol. 18, No. 1, Part II of Two Parts, Jan. 2003.

- [3] D.A. Grant, M. Stevens, and J.A. Houldsworth, "The effect of word length on the harmonic content of microprocessor-based PWM waveform generators," *IEEE Trans. Ind. Applic.*, Vol. 21, No. 1, Jan./Feb. 1985, pp. 218–225.

- [4] A.V. Peterchev, S.R. Sanders, and J.A. Houldsworth, "Quantization resolution and limit cycling in digitally controlled PWM converters," *Proceedings IEEE 32nd Annual Power Electr. Spec. Conf.*, Vancouver, Canada, 2001, on cd-rom.

- [5] D.M. Van de Sype, K. De Gussemé, A.P. Van den Bossche, J.A. Melkebeek, "Small-signal Laplace-domain analysis of uniformly-sampled pulsewidth modulators," *Proc. of the 35th Ann. Power Electron. Spec. Conf.*, Aachen, Germany, 2004, on cd-rom.

- [6] G.C. Verghese, M.E. Elbuluk, and J.G. Kassakian, "A general approach to sampled-data modeling for power electronic circuits," *IEEE Trans. Power Electron.*, Vol. 1, Apr. 1986, pp. 76–89.

- [7] V. Rajasekaran, J. Sun, and B.S. Heck, "Bilinear discrete-time modeling for enhanced stability prediction and digital control design," *Trans. Power Electron.*, Vol. 18, No. 1, Jan. 2003, pp. 381–389.

- [8] G.F. Franklin, J.D. Powell, and M. Workman, "Digital control of dynamic systems," Addison Wesley Longman, California, USA, 3rd edition, 1998.