## SOFT-SWITCHING SOLID STATE TRANSFORMER (S4T)

A Thesis Presented to The Academic Faculty

by

Hao Chen

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December, 2016

## COPYRIGHT © 2016 BY HAO CHEN

## SOFT-SWITCHING SOLID STATE TRANSFORMER (S4T)

Approved by:

Dr. Deepak M. Divan, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Thomas G. Habetler School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. J. Rhett Mayor School of Mechanical Engineering *Georgia Institute of Technology*  Dr. Maryam Saeedifard School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Ronald G. Harley School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: 10/03/2016

Dedicated to

my beloved parents

#### ACKNOWLEDGEMENTS

My journey of doctoral study at Georgia Tech has never been short of amazing experiences and great challenges. Without the inspiration, support, and advice from many people, these challenges could never have been conquered and no milestones of the journey could have been reached. This thesis is a result of the many experiences that I gained from these people, to whom I would like to express my acknowledgements.

First and foremost, I would like to extend my deepest gratitude to my advisor, Dr. Deepak Divan, for his encouragement, inspiration, and guidance throughout my doctoral study. Working on several projects under his support helped me to obtain valuable skills and confidence. He has been always instrumental in giving prompt suggestions whenever I sought guidance from him. The most valuable experience I learned from him is to know the importance of identifying problems, rather than just understanding how to solve them. It is my great honor to be one of his students and to be part of the newly-established Center for Distributed Energy at Georgia Tech that is directed by him. I sincerely believe that the fruitful experience I gained from him will continuously benefit me during my coming career as an engineer.

Further, I would like to extend my sincere thanks to my committee members Dr. Thomas Habetler, Dr. Maryam Saeedifard, Dr. Ronald Harley, and Dr. Rhett Mayor for squeezing the time out of their busy schedules to provide their valuable suggestions and feedback for my thesis.

Particularly, I would like to thank Dr. Ronald Harley for his support and guidance at the early stage of my PhD studies. His careful guidance and persistent attitude on advising students, doing research, and serving in academia have been highly beneficial to me. I am also grateful to Frank Lambert for all his support and guidance while I was working on several projects at NEETRAC. Especially helpful to me during this time was Suresh Sharma, who has given me great encouragement and valuable advice at the end of my doctoral program and during my job hunting process.

I very much appreciate my colleagues Prasad Kandula, Anish Prasai, Amrit Iyer, Rohit Moghe, and Frank Kreikebaum, for their help in carrying out experiments, writing papers, and sharing knowledge.

Sincere thanks should also go to my friends Liang Du, Yi Du, Dawei He, Zhaoyu Wang, Nan Liu, Yi Deng, Heng Yang, Chen Jiang, Liyao Wu, Qichen Yang, Jinyuan Tian, Xiangyu Han, Hang Shao, Jingfan Sun, Chanyeop Park, Sathish Jayaraman, Shreyas Bhalchandra, Kavya Ashok, Nishant Bilakanti for their help, support, and inspiration.

Finally, I would like to express my special gratitude to my parents. They have given their sincere support and great encouragement for my PhD study.

# TABLE OF CONTENTS

| ACKNO   | WL        | EDGEMENTS                                   | IV    |

|---------|-----------|---------------------------------------------|-------|

| LIST OF | <b>ТА</b> | BLES                                        | XIII  |

| LIST OF | F FIG     | GURES                                       | XIV   |

| SUMMA   | RY        |                                             | XXVII |

| CHAPTI  | ER 1      | : INTRODUCTION AND RESEARCH OBJECTIVES      | 1     |

| 1.1.    | Ga        | Ivanic Isolation in the Electric Grid       | 1     |

| 1.2.    | So        | lid State Transformer                       | 2     |

| 1.3.    | Pr        | oblem Statement                             | 4     |

| 1.4.    | Re        | search Scope and Objectives                 | 4     |

| 1.5.    | Οι        | Itline of Chapters                          | 6     |

| CHAPTI  | ER 2      | : REVIEW OF LITERATURE AND PREVIOUS         |       |

| WORK.   | •••••     |                                             |       |

| 2.1.    | Int       | roduction                                   |       |

| 2.2.    | Hi        | gh-Frequency Isolation Link                 |       |

| 2.3.    | D         | C to Single-Phase AC Conversion             | 9     |

| 2.      | 3.1.      | Multi-Stage Topology                        | 9     |

| 2.      | 3.2.      | Single-Stage Topology                       | 11    |

| 2.4.    | D         | C to Three-Phase AC Conversion              | 15    |

| 2.      | 4.1.      | Multi-Stage Topology                        | 15    |

| 2.      | 4.2.      | Single-Stage Topology                       |       |

| 2.5.    | Si        | ngle-Phase AC to Three-Phase AC Conversion  |       |

| 2.      | 5.1.      | Multi-Stage Topology                        |       |

| 2.      | 5.2.      | Reduced-Stage Topology                      |       |

| 2.6.    | Si        | ngle-Phase AC to Single-Phase AC Conversion |       |

| 2.      | 6.1.      | Multi-Stage Topology                        |       |

| 2.      | 6.2.      | Single-Stage Topology                       |       |

| 2.7.    | Th        | ree-Phase AC to Three-Phase AC Conversion   |       |

| 2.      | 7.1.      | Multi-Stage Topology                        |       |

| 2.      | 7.2.      | Single-Stage Topology                       |       |

| 2.8.    | M         | ulti-Port Topology                          |       |

| 2.9.   | Scaling to High Voltage                                         |    |

|--------|-----------------------------------------------------------------|----|

| 2.10.  | Impact of Parasitic Elements                                    | 39 |

| 2.11.  | Comparisons of Topologies                                       | 41 |

| 2.     | 11.1. Topology Comparison for Various Circuit Configurations    | 41 |

| 2.     | 11.2. Comparison of Topologies Based on Functional Capabilities |    |

|        | and Device Rating                                               | 42 |

| 2.12.  | Conclusions                                                     |    |

| СНАРТІ | ER 3: ISOLATED DYNAMIC CURRENT (DYNA-C) SST                     | 44 |

| 3.1.   | Introduction                                                    | 44 |

| 3.2.   | Dyna-C Topology                                                 | 44 |

| 3.3.   | Principle of Operation                                          |    |

| 3.4.   | Leakage Management                                              | 49 |

| 3.5.   | Issues with the Dyna-C Topology                                 | 52 |

| 3.     | 5.1. Converter Loss                                             | 52 |

| 3.     | 5.2. Device Stress at Phase-Leg Transitions                     | 53 |

| 3.     | 5.3. Voltage Bump at Phase-Leg Transitions                      | 53 |

| 3.     | 5.4. Device Stress at Leakage Management Transitions            | 54 |

| 3.6.   | Conclusions                                                     | 55 |

| CHAPTI | ER 4: HARD-SWITCHING ISSUES FOR SILICON-                        |    |

| CARBID | DE DEVICES                                                      | 56 |

| 4.1.   | Introduction                                                    | 56 |

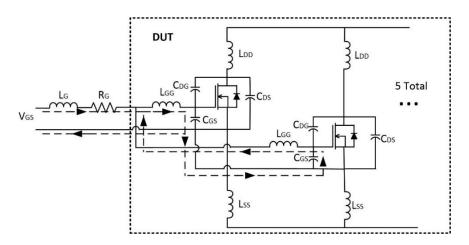

| 4.2.   | Test Fixture and Detailed Circuit Model with Parasitic          |    |

|        | Elements                                                        | 57 |

| 4.3.   | Hard-Switching Issues                                           | 61 |

| 4.     | 3.1. Drain-Source Voltage and Current Spikes and Resonance      | 61 |

| 4.     | 3.2. Gate-Source Voltage Resonance                              | 64 |

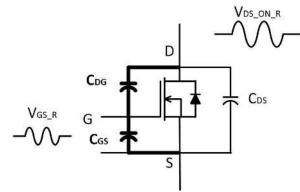

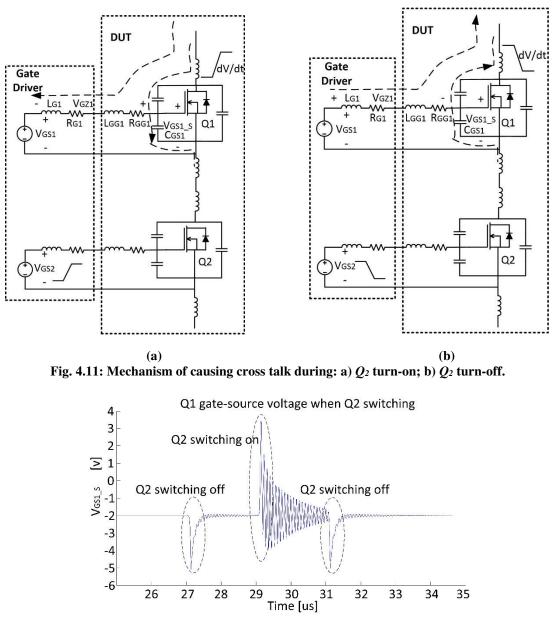

| 4.     | 3.3. Phase Leg Cross Talk                                       | 65 |

| 4.     | 3.4. Gate-Driver Noise                                          | 67 |

| 4.     | 3.5. Electromagnetic Interference (EMI)                         | 69 |

| 4.4.   | Conclusions                                                     | 71 |

| CHAPTI | ER 5: ZERO-CURRENT-SWITCHING SOLID STATE                        |    |

| TRANSE | FORMER                                                          | 73 |

|    | 5.1.  | Introduction                                            | 73  |

|----|-------|---------------------------------------------------------|-----|

|    | 5.2.  | Topology                                                | 73  |

|    | 5.3.  | Principle of Operation                                  | 74  |

|    | 5.4.  | Simulation Results                                      |     |

|    | 5.5.  | Discussion                                              | 79  |

|    | 5.6.  | Conclusions                                             | 80  |

| Cl | НАРТЕ | R 6: ZERO-VOLTAGE-SWITCHING SOLID STATE                 |     |

| TI | RANSF | ORMER                                                   | 81  |

|    | 6.1.  | Introduction                                            | 81  |

|    | 6.2.  | A ZVS Auxiliary Resonant Circuit for the Dyna-C         | 82  |

|    | 6.3.  | Topology of the S4T                                     |     |

|    | 6.4.  | Topology Variations                                     | 85  |

|    | 6.5.  | Principle of Operation                                  | 87  |

|    | 6.6.  | Full Range of Soft Switching                            |     |

|    | 6.7.  | Unique Attributes of the S4T                            |     |

|    | 6.7   | 7.1. Ease of Control                                    |     |

|    | 6.7   | 7.2. Robustness                                         |     |

|    | 6.7   | 7.3. Fast Dynamic Response                              |     |

|    | 6.7   | 7.4. Modular Design                                     |     |

|    | 6.8.  | Conclusions                                             |     |

| Cl | НАРТЕ | R 7: ANALYSIS AND CONTROL OF THE S4T                    | 101 |

|    | 7.1.  | Introduction                                            | 101 |

|    | 7.2.  | Analysis of the Converter                               | 101 |

|    | 7.2   | 2.1. Optimal Transformer Magnetizing Current Level      | 102 |

|    | 7.2   | 2.2. Switching Ripple of the Magnetizing Current        | 103 |

|    | 7.2   | 2.3. Boundary Conditions for Continuous Conduction Mode |     |

|    |       | Operation                                               | 104 |

|    | 7.3.  | Analysis of the Transformer Leakage Effect              | 104 |

|    | 7.4.  | Control of the Converter                                |     |

|    | 7.5.  | Conclusions                                             | 110 |

| Cl | НАРТЕ | R 8: CONVERTER DESIGN FOR THE S4T                       |     |

|    | 8.1.  | Introduction                                            |     |

|    |       |                                                         |     |

| 8.2.  | De    | sign of Power Stage                                           | . 111 |

|-------|-------|---------------------------------------------------------------|-------|

| 8     | .2.1. | Semiconductor Devices                                         | . 111 |

| 8     | .2.2. | Converter Switching Frequency                                 | . 113 |

| 8     | .2.3. | Gate Driver                                                   | . 113 |

| 8     | .2.4. | Filters                                                       | . 114 |

| 8     | .2.5. | Snubbers                                                      | . 115 |

| 8     | .2.6. | Sensors                                                       | . 116 |

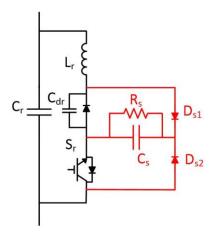

| 8.3.  | De    | sign of the Auxiliary Resonant Circuit                        | . 117 |

| 8     | .3.1. | Design of the Resonant Inductor $L_r$ and the Resonant        |       |

|       |       | Capacitor <i>C<sub>r</sub></i>                                | . 117 |

| 8     | .3.2. | Design of the Snubber for the Auxiliary Device S <sub>r</sub> | . 122 |

| 8.4.  | De    | sign of Controller                                            | . 124 |

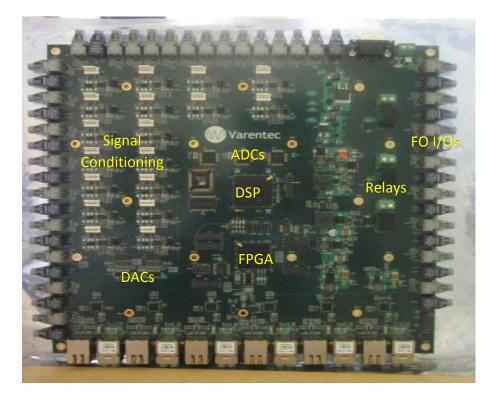

| 8     | .4.1. | Control Board                                                 | . 124 |

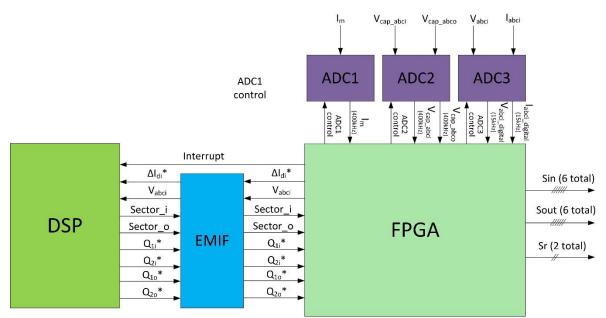

| 8     | .4.2. | Data Processing                                               | . 125 |

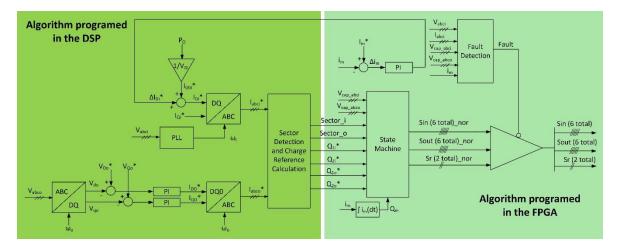

| 8     | .4.3. | Algorithms                                                    | . 127 |

| 8     | .4.4. | State Machine                                                 | . 128 |

| 8     | .4.5. | State Transition Considering the Common Emitter               |       |

|       |       | Inductance Effect                                             | . 130 |

| 8.5.  | Fai   | ult Protection                                                | . 133 |

| 8     | .5.1. | Hardware Protection                                           | . 134 |

| 8     | .5.2. | Software Protection                                           | . 134 |

| 8.6.  | Co    | nclusions                                                     | . 135 |

| СНАРТ | 'ER 9 | : HIGH-FREQUENCY TRANSFORMER DESIGN                           | . 136 |

| 9.1.  | Int   | roduction                                                     | . 136 |

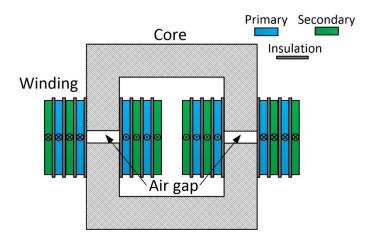

| 9.2.  | Tra   | ansformer Design with Magnetics                               | . 136 |

| 9     | .2.1. | Magnetic Core                                                 | . 136 |

| 9     | .2.2. | Winding Design                                                | . 137 |

| 9     | .2.3. | Leakage Inductance                                            | . 138 |

| 9     | .2.4. | Design Procedure                                              | . 138 |

| 9.3.  | Tra   | ansformer Characterization                                    | . 143 |

| 9.4.  | Hy    | brid Transformer Design with Pre-Biased Flux                  | . 146 |

| 9.4     | 4.1. Theory Background                            | 146 |

|---------|---------------------------------------------------|-----|

| 9.4     | 4.2. Proposed Hybrid Transformer Design           | 151 |

| 9.5.    | Conclusions                                       | 158 |

| СНАРТЕ  | ER 10: SIMULATION AND EXPERIMENTAL                |     |

| VALIDA  | TION                                              | 159 |

| 10.1.   | Introduction                                      | 159 |

| 10.2.   | Simulation Results for the S4T                    | 159 |

| 10.3.   | Fabricated S4T Unit                               | 163 |

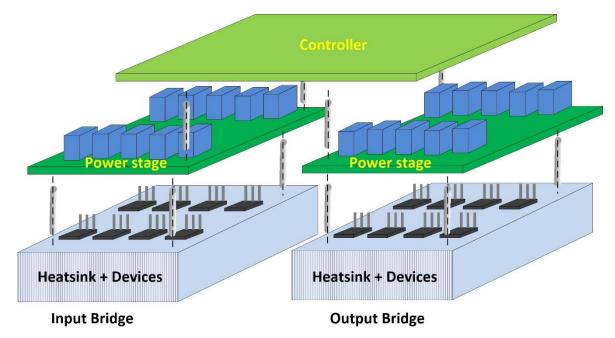

| 10      | 0.3.1. Power Stage of the Converter               | 163 |

| 10      | 0.3.2. Assembled Unit                             | 168 |

| 10.4.   | System for Testing the Unit                       | 170 |

| 10.5.   | Experimental Results for the S4T                  | 170 |

| 10      | 0.5.1. Power-Circulating Test                     | 170 |

| 10      | 0.5.2. Test with Resistive Loads                  | 174 |

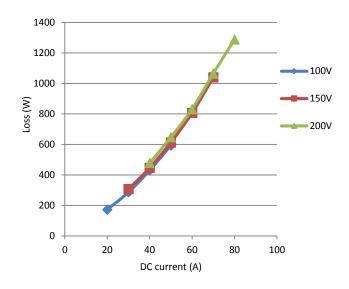

| 10.6.   | Loss Measurement and Comparison                   | 175 |

| 10.7.   | A Unique Application as a Dynamic VAr Compensator | 176 |

| 10.8.   | Conclusions                                       | 181 |

| СНАРТЕ  | ER 11: S4T OPERATION UNDER LOAD STEP-CHANGES,     |     |

| START-U | UP, SHUT-DOWN, AND FAULT CONDITIONS               | 183 |

| 11.1.   | Introduction                                      | 183 |

| 11.2.   | Load Step-Changes                                 | 183 |

| 11      | .2.1. Load Step-Down                              |     |

| 11      | .2.2. Load Step-Up                                | 185 |

| 11.3.   | Converter Start-Up                                | 186 |

| 11.4.   | Converter Shut-Down                               | 190 |

| 11.5.   | Operation under Fault Conditions                  | 192 |

| 11.6.   | Conclusions                                       | 193 |

| СНАРТЕ  | ER 12: SCALING TO MEDIUM VOLTAGE                  | 194 |

| 12.1.   | Introduction                                      | 194 |

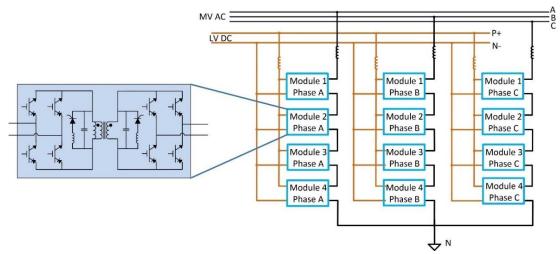

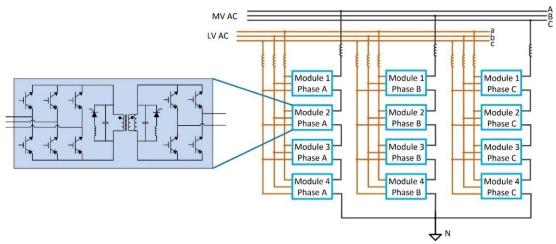

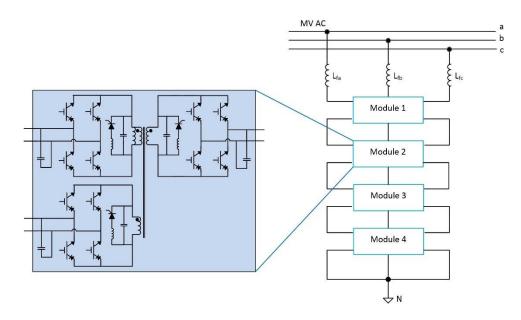

| 12.2.   | Stacking to Medium Voltage and High Power         | 194 |

| 12.3.   | Modular Soft-Switching Dynamic VAr Compensator    | 197 |

| 12     | .3.1. Topology of the Single Module Soft-Switching Dynamic    |     |

|--------|---------------------------------------------------------------|-----|

|        | VAr Compensator                                               | 197 |

| 12     | .3.2. Operating Principle of the Single Module Soft-Switching |     |

|        | Dynamic VAr Compensator                                       | 198 |

| 12     | .3.3. Analysis of the Single Module Soft-Switching Dynamic    |     |

|        | VAr Compensator                                               |     |

| 12     | .3.4. Control of the Single Module Soft-Switching Dynamic VAr |     |

|        | Compensator                                                   |     |

| 12     | .3.5. Simulation Results of the Single-Module Soft-Switching  |     |

|        | Dynamic VAr Compensator                                       |     |

| 12.4.  | Stability Issue of Converter Series Stacking                  |     |

| 12.5.  | Control Strategy for Series Stacking Converters               |     |

| 12     | .5.1. Inner Control Loop                                      |     |

| 12     | .5.2. Outer Control Loop                                      |     |

| 12     | .5.3. Complete Controller for the Stacked Converter           |     |

| 12.6.  | Simulation Results                                            |     |

| 12.7.  | Conclusions                                                   |     |

| CHAPTE | <b>CR 13: CONCLUSIONS AND RECOMMENDATIONS FOR</b>             |     |

| FUTURE | WORK                                                          | 222 |

| 13.1.  | Conclusions                                                   |     |

| 13.2.  | Summary of Contributions                                      |     |

| 13.3.  | Recommendations for Future Work                               |     |

| 13     | .3.1. Experimental Demonstration on a High-Power Level        |     |

| 13     | .3.2. Design with Reverse-Blocking IGBTs                      |     |

| 13     | .3.3. Low-Cost High-Frequency Transformer Design              |     |

| 13     | .3.4. Functional Demonstration for DC, Single-Phase AC, and   |     |

|        | Multi-Port                                                    |     |

| 13     | .3.5. Motor Drive Application                                 |     |

| 13     | .3.6. Demonstration of Medium-Voltage Operation               |     |

| APPEND | IX A: BILL OF MATERIAL FOR THE S4T CONVERTER                  |     |

| APPEND | IX B: PUBLICATIONS AND PATENTS                                |     |

| REFERENCES |  |

|------------|--|

| VITA       |  |

# LIST OF TABLES

| Table 2.1: Topologies with various circuit configurations showing possible  |    |

|-----------------------------------------------------------------------------|----|

| conversion functions                                                        |    |

| Table 2.2: Topologies functional capabilities and device rating for SSTs    |    |

| with three-phase ac/ac input/output                                         |    |

| Table 5.1: Parameters of the simulated zero-current-switching solid state   |    |

| transformer                                                                 | 78 |

| Table 8.1: Device comparison on the conducting voltage drop for SiC         |    |

| MOSFET C2M0025120D and Si IGBT NGTB50N120FL2WG                              |    |

| Table 9.1: Characteristics of high-frequency magnetic materials [111]-[114] |    |

|                                                                             |    |

| Table 9.2: Characteristics of various permanent magnets                     |    |

| Table 10.1: Simulation parameters of the S4T                                |    |

| Table 10.2: Comparison of S4T, conventional DAB based multi-stage SST,      |    |

| and low-frequency transformer with a rectifier and an inverter when         |    |

| implementing a three-phase 480 V/50 kVA solid state transformer with a      |    |

| switching frequency of 15 kHz                                               |    |

# LIST OF FIGURES

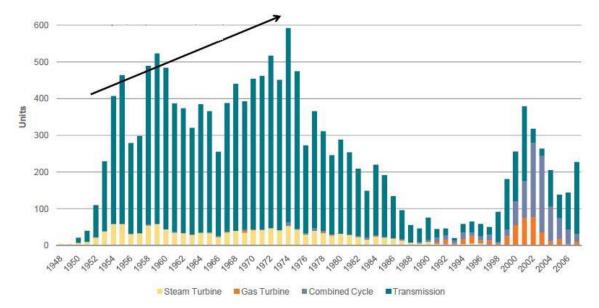

| Fig. 1.1: Yearly installment of large power transformers in the United States     |

|-----------------------------------------------------------------------------------|

| from 1948 to 2006 [1]1                                                            |

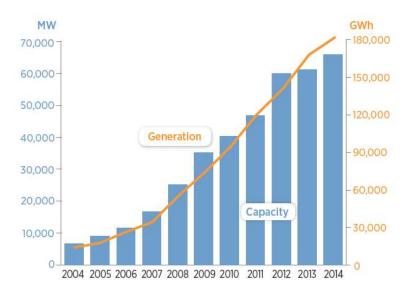

| Fig. 1.2: U.S. total installed wind electricity capacity and generation [2]       |

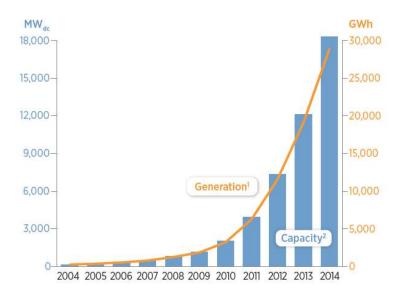

| Fig. 1.3: U.S. PV electricity installed capacity and generation [2]               |

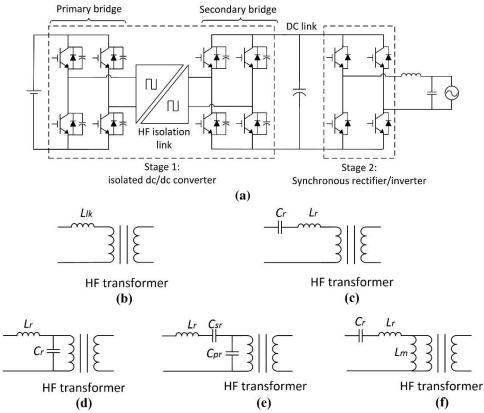

| Fig. 2.1: High-frequency isolation links of (a) type I; (b) type II; (c) type III |

|                                                                                   |

| Fig. 2.2: Two-stage isolated bidirectional dc to single-phase ac converter        |

| and the high-frequency isolation links: (a) converter structure; (b) DAB          |

| isolation link; (c) series resonant link; (d) parallel resonant link; (e) hybrid  |

| series-parallel resonant link; (f) LLC resonant link 10                           |

| Fig. 2.3: Conceptualized waveforms for the DAB converter                          |

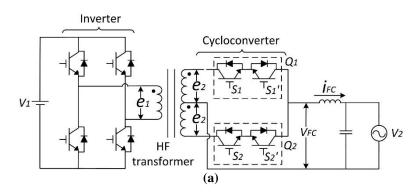

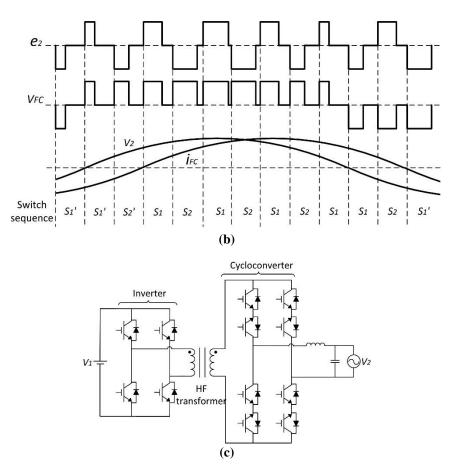

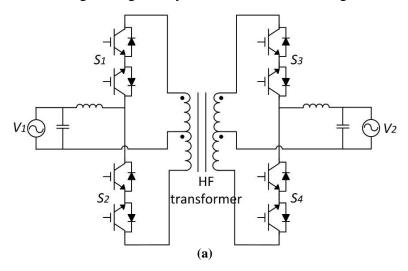

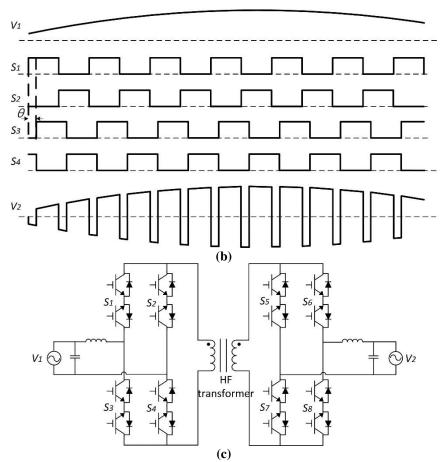

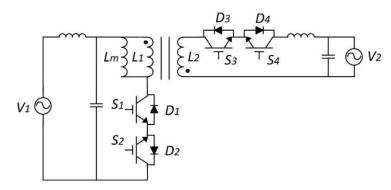

| Fig. 2.4: DC to single-phase ac cycloconverter: (a) half-bridge version; (b)      |

| switching sequence; (c) full-bridge version                                       |

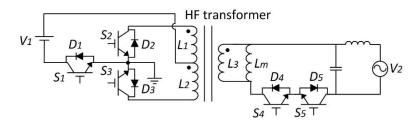

| Fig. 2.5: DC to single-phase ac flyback converter                                 |

| Fig. 2.6: DC to single-phase ac DAB converter                                     |

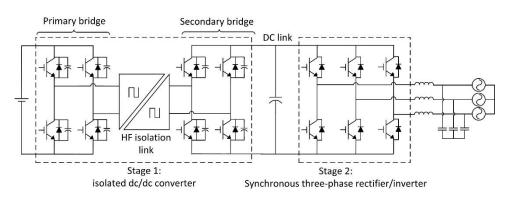

| Fig. 2.7: Multi-stage isolated bidirectional dc to three-phase ac converter       |

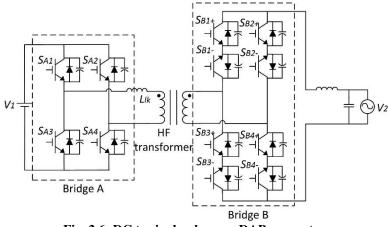

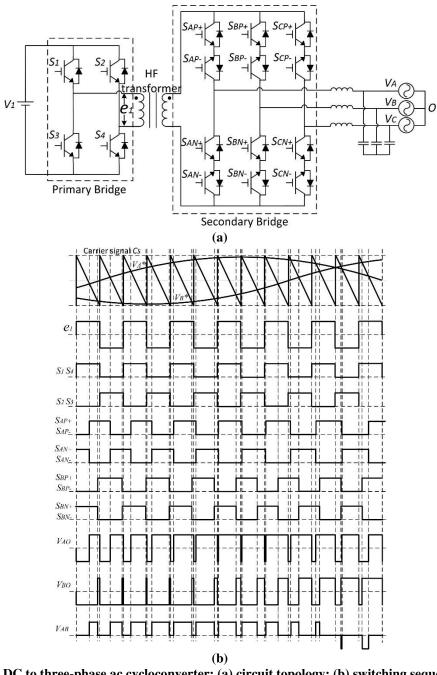

| Fig. 2.8: DC to three-phase ac cycloconverter: (a) circuit topology; (b)          |

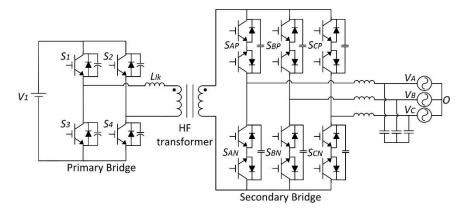

| switching sequence and waveforms 17                                               |

| Fig. 2.9: DC to three-phase ac DAB converter                                      |

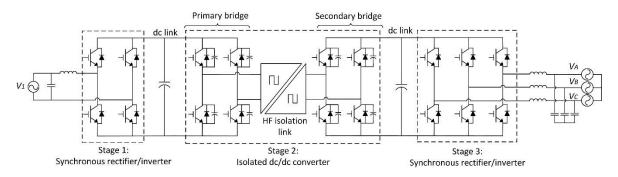

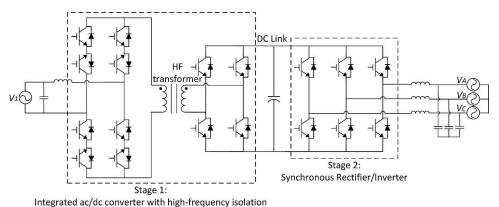

| Fig. 2.10: Multi-stage isolated bidirectional single-phase ac to three-phase      |

| ac converter                                                                      |

| Fig. 2.11: Reduced-stage single-phase ac to three-phase ac converter              |

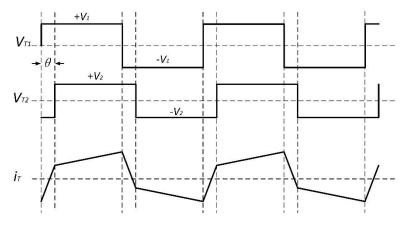

| Fig. 2.12: Single-phase ac to ac cycloconverter: (a) half bridge topology;        |

| (b) switching sequence and waveforms; (c) full bridge topology 22                 |

| Fig. 2.13: Single-phase ac to ac flyback converter                                |

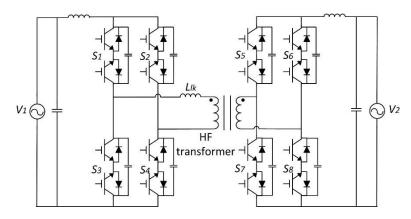

| Fig. 2.14: Single-phase ac to ac DAB converter                                                                                                                        |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

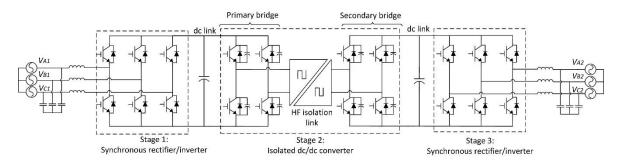

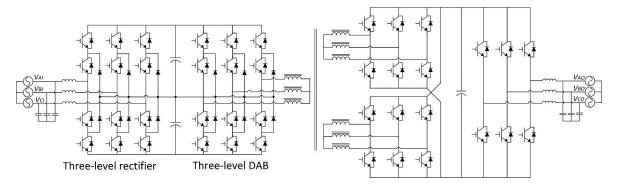

| Fig. 2.15: Multi-stage isolated bidirectional three-phase ac to three-phase ac converter                                                                              |    |

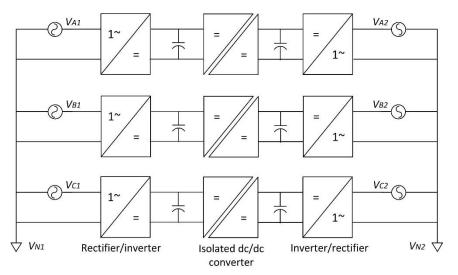

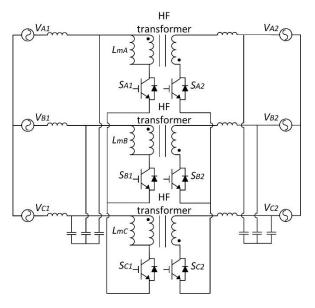

| Fig. 2.16: Three-phase ac/ac topology using single-phase ac/ac converter modules                                                                                      |    |

| Fig. 2.17: Singe-stage three-phase ac/ac isolated direct matrix converter                                                                                             |    |

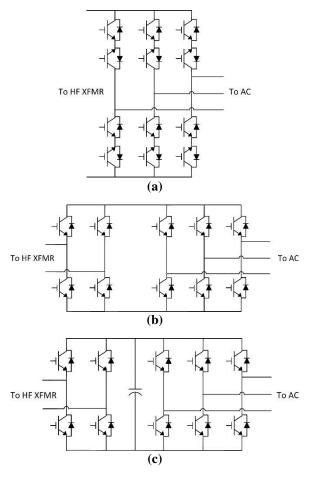

| <ul><li>Fig. 2.18: Three types of bridge configuration: a) direct matrix converter;</li><li>b) indirect matrix converter; c) back-to-back dc link converter</li></ul> |    |

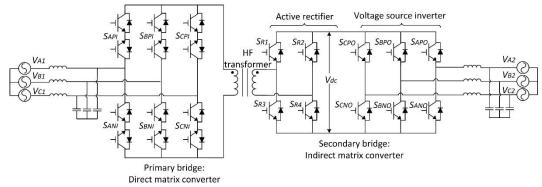

| Fig. 2.19: Three-phase ac/ac converter: a direct matrix converter with an indirect matrix converter                                                                   |    |

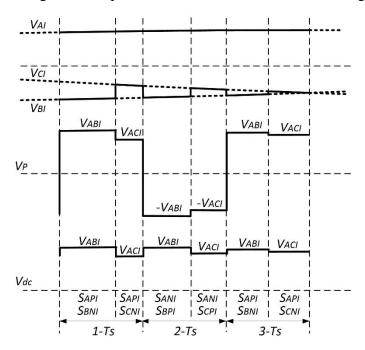

| Fig. 2.20: Conceptualized waveforms for single-stage three-phase ac/ac isolated direct matrix converter                                                               |    |

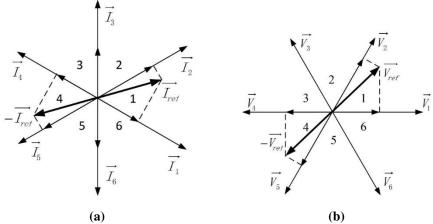

| Fig. 2.21: Space vector modulation for single-stage three-phase ac/ac direct matrix converter: a) current space vector for primary bridge; b) voltage                 |    |

| space vector for secondary bridge                                                                                                                                     |    |

| Fig. 2.22: Three-phase ac/ac flyback converter                                                                                                                        |    |

| Fig. 2.23: AC-Link converter: a) converter topology; b) relative waveforms and switching sequences                                                                    |    |

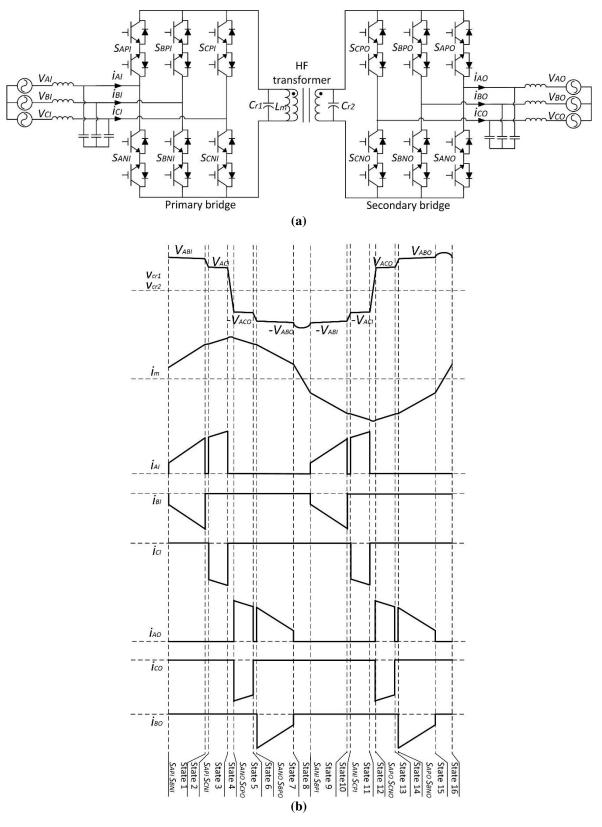

| Fig. 2.24: Partial resonant ac-link converter: a) converter topology; b) relative waveforms and switching sequences; c) equivalent circuits of three                  |    |

| basic modes; d) varied topology with reduced switch count                                                                                                             |    |

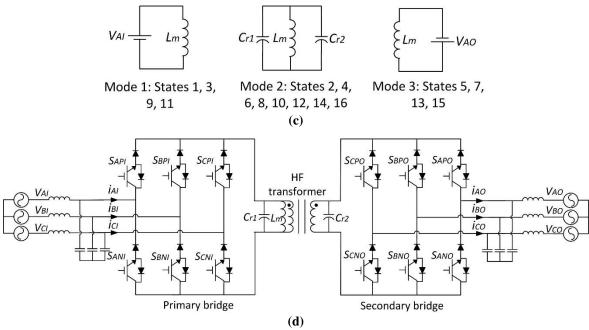

| Fig. 2.25: Tri-port configuration of the partial resonant ac link converter                                                                                           | 36 |

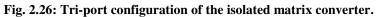

| Fig. 2.26: Tri-port configuration of the isolated matrix converter                                                                                                    |    |

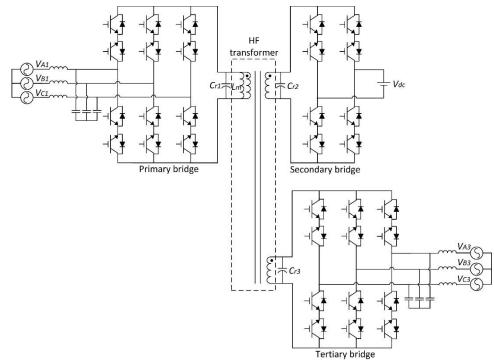

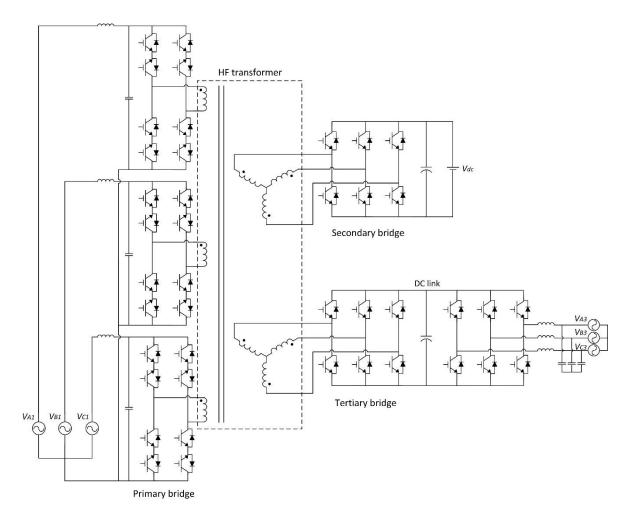

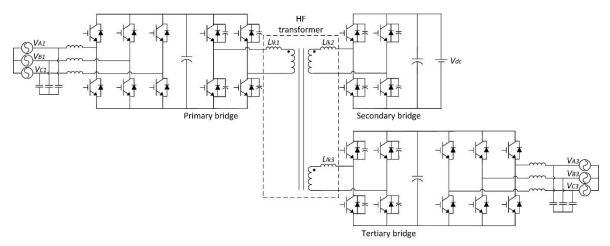

| Fig. 2.27: Tri-port configuration of the DAB converter                                                                                                                |    |

| Fig. 2.28: Equivalent circuit of the tri-port DAB converter                                                                                                           | 38 |

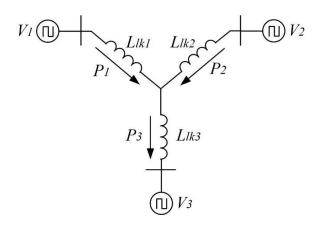

| Fig. 2.29: Scaling to high voltage using modular converters                                                                                                           | 39 |

| Fig. 2.30: Scaling to high voltage using a diode-clamped converter                                                                                                    |    |

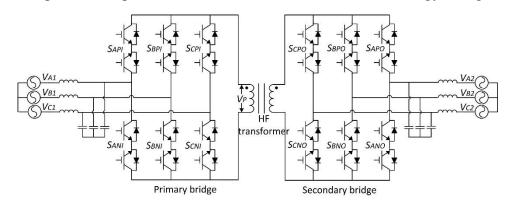

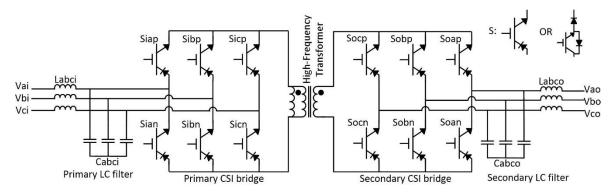

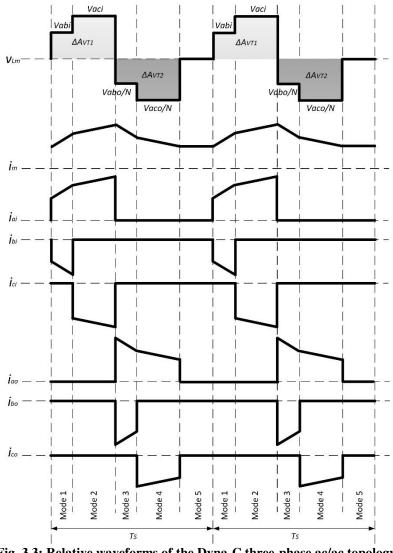

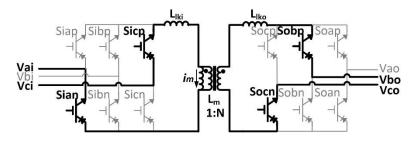

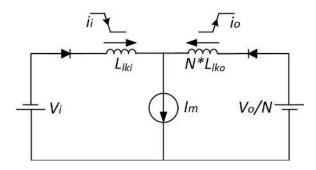

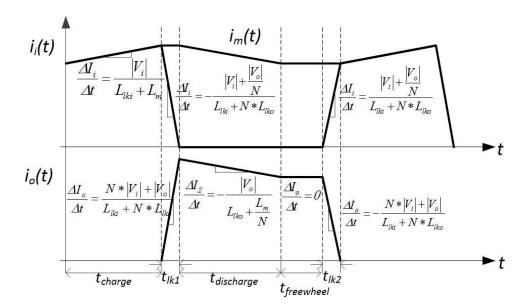

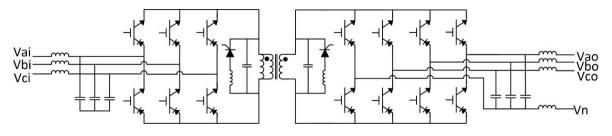

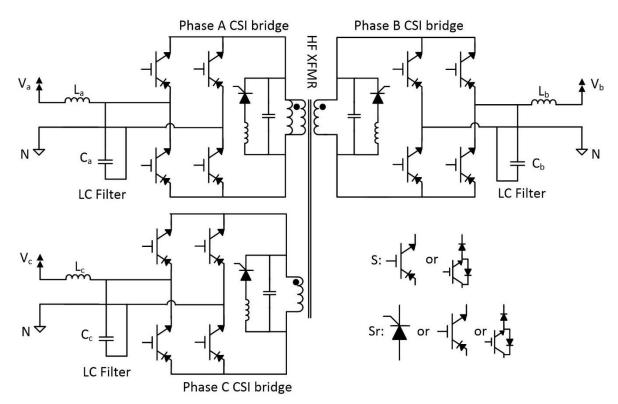

| Fig. 3.1: Dyna-C three-phase ac/ac topology                                      | 45 |

|----------------------------------------------------------------------------------|----|

| Fig. 3.2: Operation modes over one switching cycle for the Dyna-C three-         |    |

| phase ac/ac topology: a) mode 1: charging cycle with 1st input L-L voltage;      |    |

| b) mode 2: charging cycle with 2nd input L-L voltage; c) mode 3:                 |    |

| discharging cycle with 1st output L-L voltage; d) mode 4: discharging cycle      |    |

| with 2nd output L-L voltage; and e) mode 5: free-wheeling                        | 47 |

| Fig. 3.3: Relative waveforms of the Dyna-C three-phase ac/ac topology            | 47 |

| Fig. 3.4: Leakage management mode for the transition from the input bridge       |    |

| to the output bridge                                                             | 50 |

| Fig. 3.5: Simplified equivalent circuit for the leakage management mode          | 50 |

| Fig. 3.6: Conceptualized waveforms of the primary and secondary winding          |    |

| currents during leakage management                                               | 52 |

| Fig. 3.7: Device stress at phase-leg transition: a) equivalent circuit; and b)   |    |

| conceptualized voltage waveforms across $S_1$ at the transition                  | 53 |

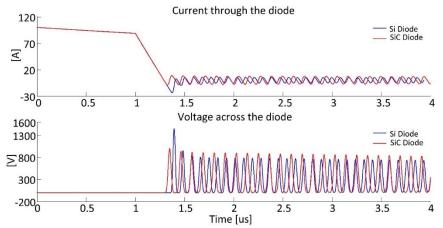

| Fig. 3.8: Simulated current and voltage waveforms at the leakage                 |    |

| management transition for a Si diode APTDF200H120G and a SiC diode               |    |

| GDP60Z120E                                                                       | 54 |

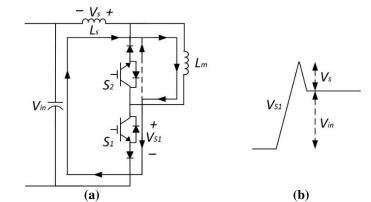

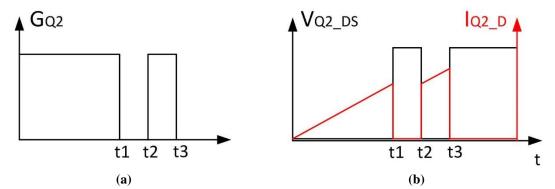

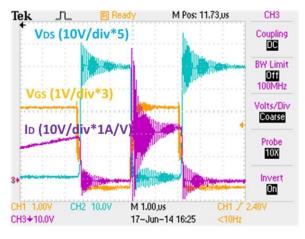

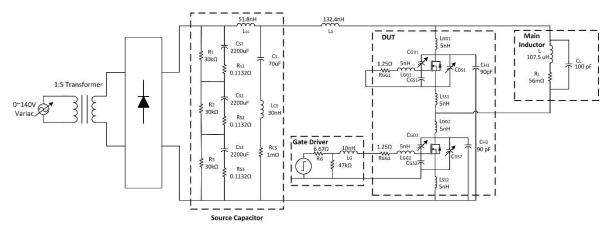

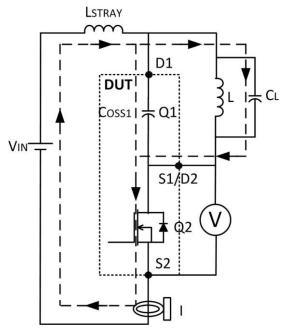

| Fig. 4.1: Circuit diagram of the double-pulse test fixture                       | 58 |

| Fig. 4.2: Theoretical waveforms: (a) $Q2$ gate signal (b) $Q2$ theoretical       |    |

| current, voltage waveforms                                                       | 58 |

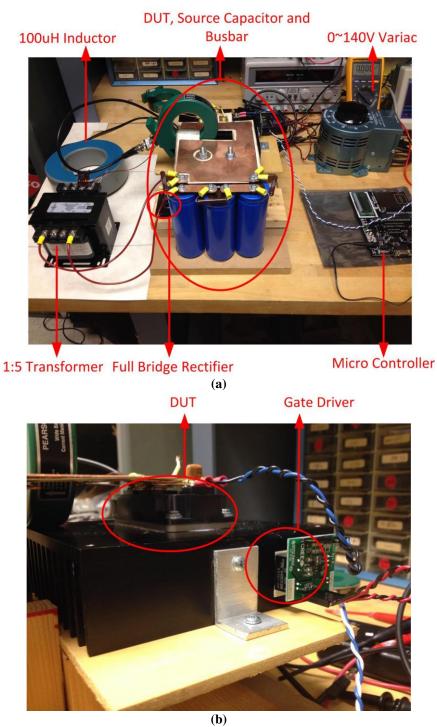

| Fig. 4.3: Photograph of the double-pulse test fixture: (a) test fixture; and (b) |    |

| DUT and gate driver                                                              | 59 |

| Fig. 4.4: Experimental switching waveforms from the double-pulse test            |    |

| fixture                                                                          | 60 |

| Fig. 4.5: Detailed circuit model with parasitic elements                         | 61 |

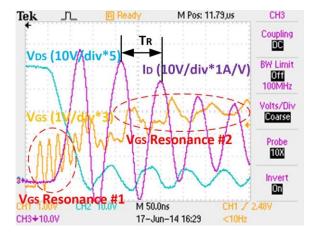

| Fig. 4.6: Zoomed in $Q_2$ turn-on waveforms                                      | 62 |

| Fig. 4.7: Resonant path during $Q_2$ turn-on                                     | 62 |

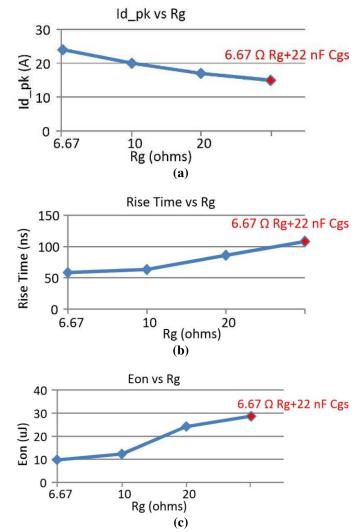

| Fig. 4.8: Effects of different gate resistances and gate-source capacitance         |    |

|-------------------------------------------------------------------------------------|----|

| on: a) drain current spike $I_{d_pk}$ ; b) rise time; and c) turn-on loss $E_{on}$  | 63 |

| Fig. 4.9: Resonant path of $V_{GS}$ resonance type #1                               | 65 |

| Fig. 4.10: Resonant path of $V_{GS}$ resonance type #2                              | 65 |

| Fig. 4.11: Mechanism of causing cross talk during: a) $Q_2$ turn-on; b) $Q_2$ turn- |    |

| off                                                                                 | 67 |

| Fig. 4.12: $Q_1$ gate-source voltage during $Q_2$ switching                         | 67 |

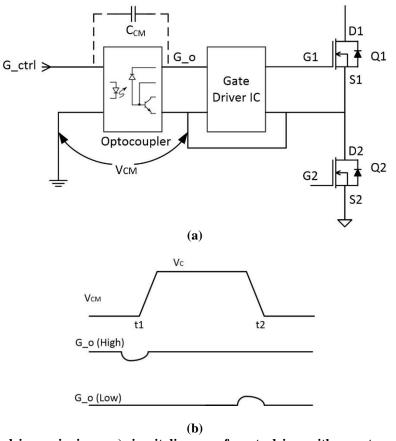

| Fig. 4.13: Gate driver noise issue: a) circuit diagram of a gate driver with        |    |

| an opto-coupler; and b) conceptualized waveforms during the switching               |    |

| transition                                                                          | 68 |

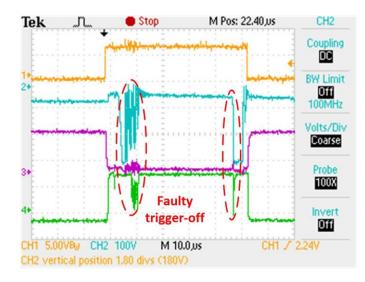

| Fig. 4.14: Experimental waveforms of the gate driver noise issue: CH1 (2.5          |    |

| V/div)-control signal $G_{ctrl}$ ; CH2 (50 V/div)-common mode noise $V_{CM}$ ;      |    |

| CH3 (10 V/div)-opto-coupler output $G_o$ ; CH4 (10 V/div)-gate signal $V_{GS1}$     |    |

|                                                                                     | 69 |

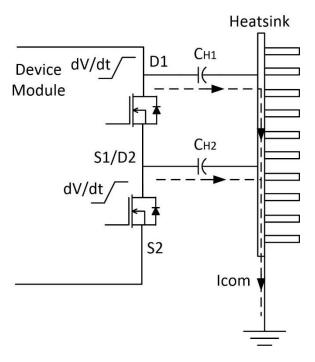

| Fig. 4.15: Common mode current flowing path                                         | 70 |

| Fig. 4.16: Internal layout of CAS100H12AM1                                          | 71 |

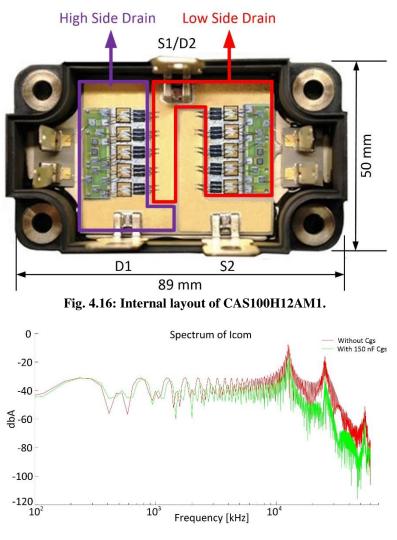

| Fig. 4.17: Spectrum of common mode current <i>I</i> <sub>com</sub>                  | 71 |

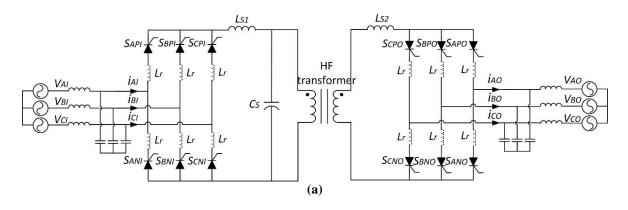

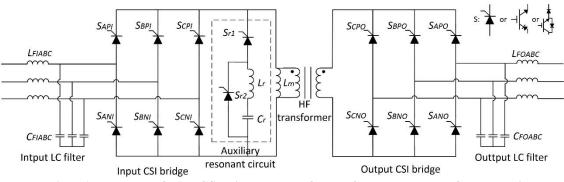

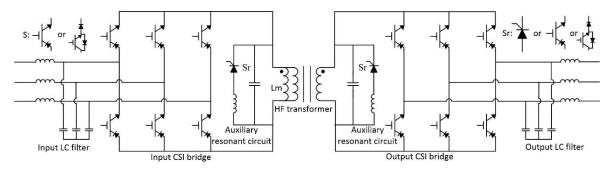

| Fig. 5.1: Topology of the ZCS solid state transformer for three-phase ac/ac         |    |

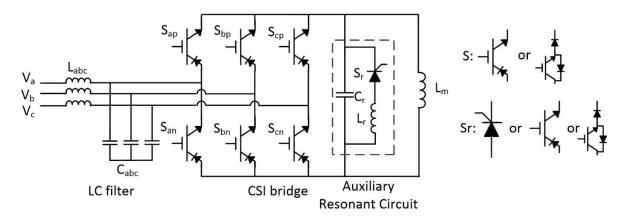

| conversion                                                                          | 74 |

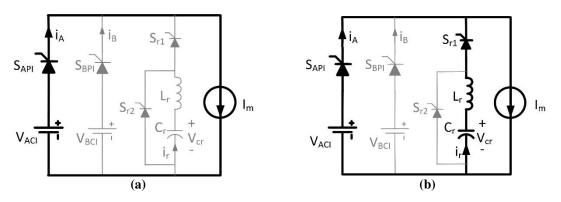

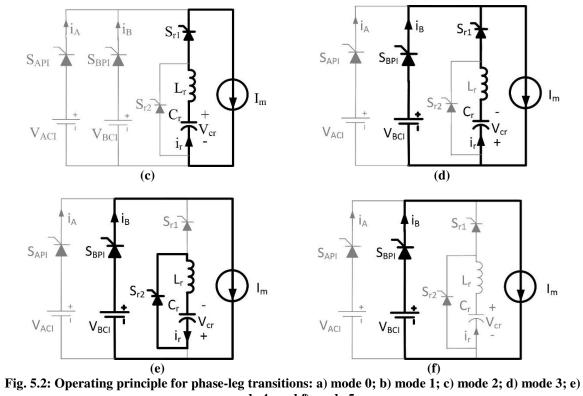

| Fig. 5.2: Operating principle for phase-leg transitions: a) mode 0; b) mode         |    |

| 1; c) mode 2; d) mode 3; e) mode 4; and f) mode 5                                   | 77 |

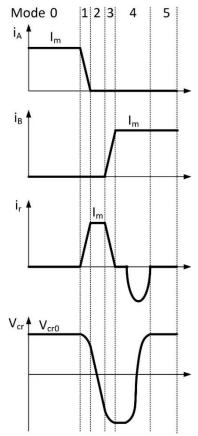

| Fig. 5.3: Relative waveforms at the transition                                      | 77 |

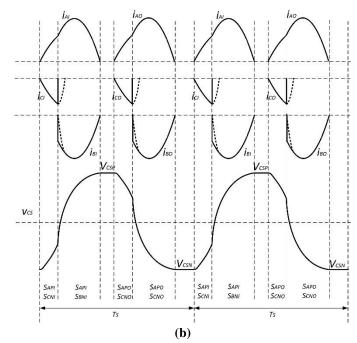

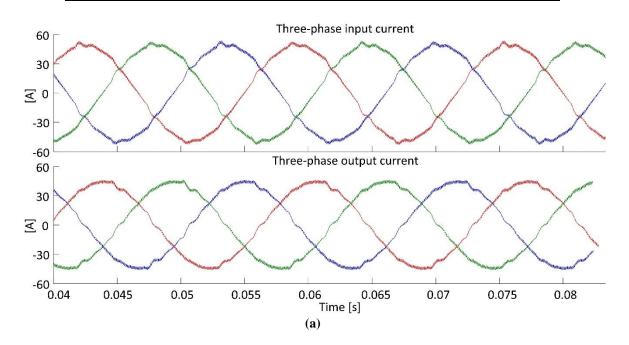

| Fig. 5.4: Simulation waveforms of the ZCS solid state transformer: a) three-        |    |

| phase input and output currents; and b) high-frequency transformer                  |    |

| magnetizing current, voltage and current of the resonant capacitor                  | 79 |

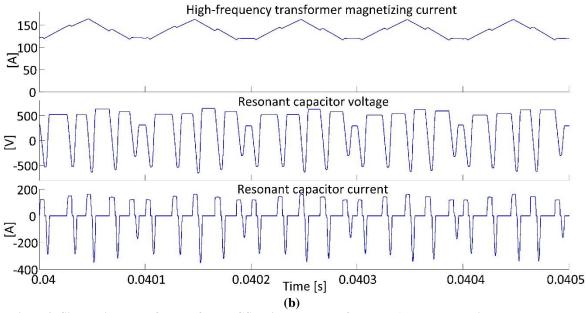

| Fig. 6.1: ZVS switching for the voltage source converter: a) an extra               |    |

| capacitor connected in parallel with the device; and b) equivalent circuit          |    |

| during each switching transition                                                    |    |

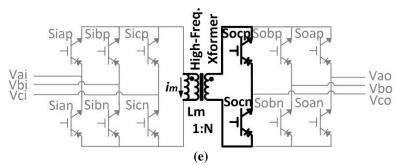

| Fig. 6.2: ZVS switching for the current source converter: a) equivalent                                          |    |

|------------------------------------------------------------------------------------------------------------------|----|

| circuit during each switching transition, and b) conceptualized waveform of                                      |    |

| <i>V</i> <sub>cr</sub>                                                                                           |    |

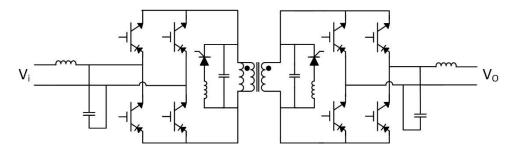

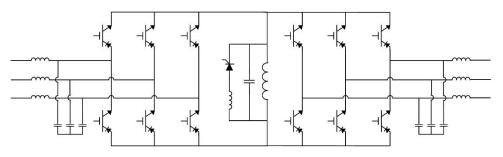

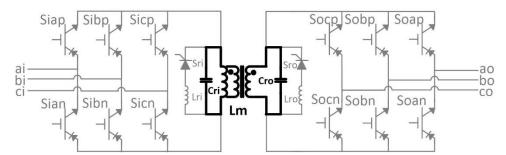

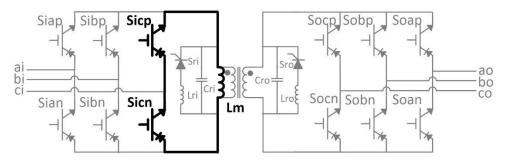

| Fig. 6.3: Topology for the three-phase soft-switching solid state transformer (S4T)                              | 84 |

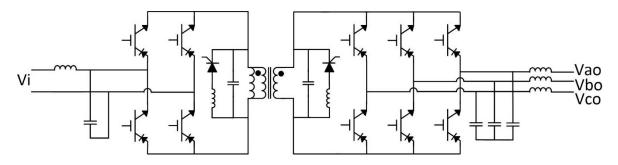

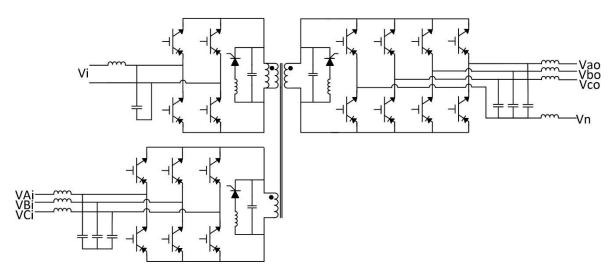

| Fig. 6.4: Topology for dc or single-phase ac to dc or single-phase ac (excluding single-phase ac/ac conversion). | 85 |

| Fig. 6.5: Topology for dc or single-phase ac to three-phase ac                                                   | 86 |

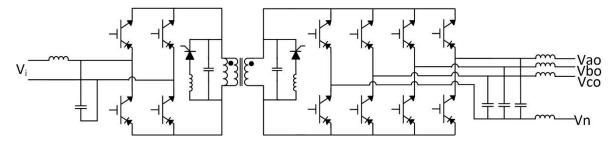

| Fig. 6.6: Topology for dc or single-phase ac to three-phase four-wire ac                                         | 86 |

| Fig. 6.7: Topology for three-phase three-wire ac to three-phase four-wire ac                                     | 86 |

| Fig. 6.8: Tri-port topology 1                                                                                    |    |

| Fig. 6.9: Tri-port topology 2                                                                                    | 87 |

| Fig. 6.10: Non-isolated topology for three-phase ac/ac                                                           | 87 |

| Fig. 6.11: Simplified circuit configuration for unidirectional power flow                                        | 87 |

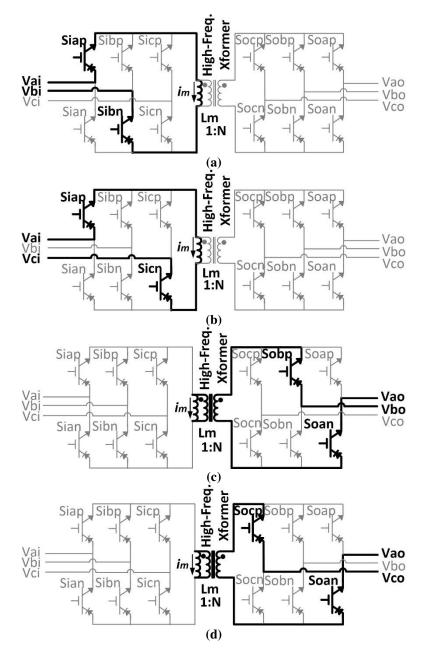

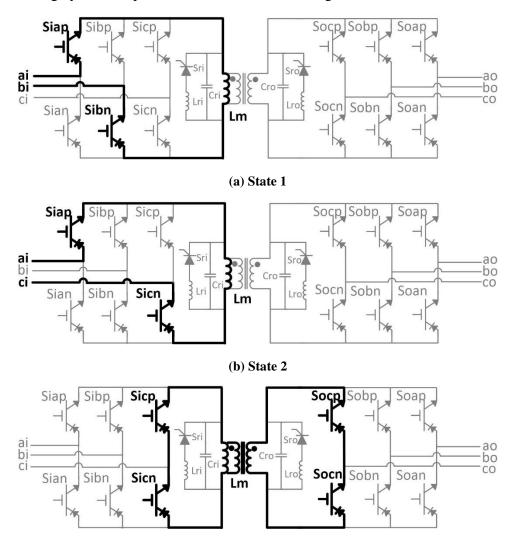

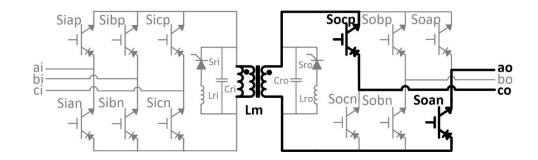

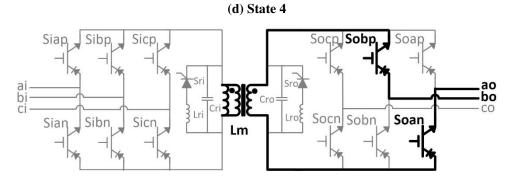

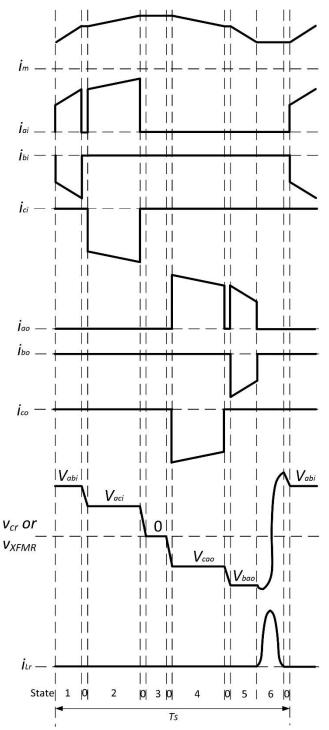

| Fig. 6.12: Operating states over one switching cycle: (a) state 1 – charging                                     |    |

| the magnetizing inductance with the 1 <sup>st</sup> line-to-line input voltage; (b) state                        |    |

| $2$ – charging the magnetizing inductance with the $2^{nd}$ line-to-line input                                   |    |

| voltage; (c) state 3 – freewheeling; (d) state 4 – discharging the magnetizing                                   |    |

| inductance with the 1 <sup>st</sup> line-to-line output voltage; (e) state 5 – discharging                       |    |

| the magnetizing inductance with the $2^{nd}$ line-to-line output voltage ((a) – (e)                              |    |

| are the five active states); (f) state $0 - ZVS$ transition state; and (g) state 6                               |    |

| – resonant state                                                                                                 |    |

| Fig. 6.13: Conceptualized waveforms (states $1 - 5$ correspond to Fig. 6.12                                      |    |

| (a) $-$ (e); state 0 corresponds to Fig. 6.12 (f); and state 6 corresponds to Fig.                               |    |

| 6.12 (g))                                                                                                        |    |

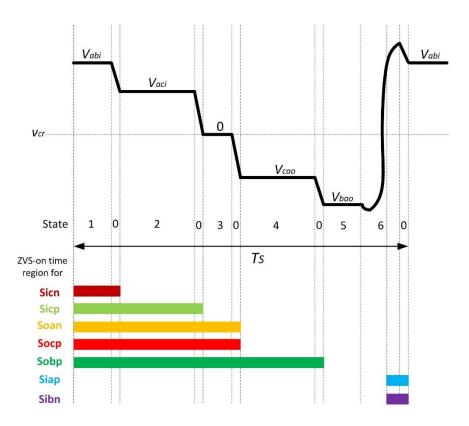

| Fig. 6.14: Allowed ZVS turning-on time region for each device                                                    |    |

| corresponding to the example switching cycle of Fig. 6.13                                                        |    |

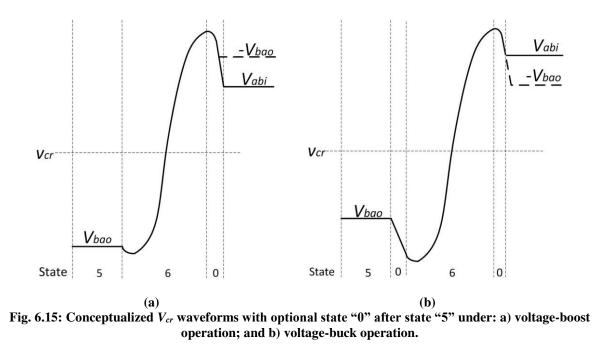

| Fig. 6.15: Conceptualized $V_{cr}$ waveforms with optional state "0" after state     |

|--------------------------------------------------------------------------------------|

| "5" under: a) voltage-boost operation; and b) voltage-buck operation                 |

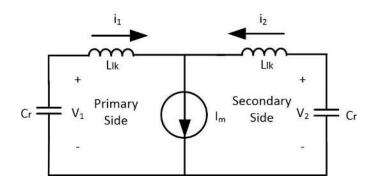

| Fig. 7.1: Equivalent circuit at the ZVS transition 105                               |

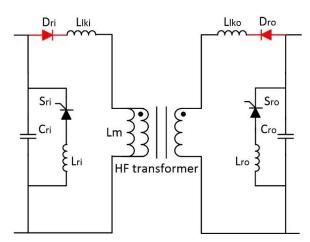

| Fig. 7.2: Two diodes to manage the resonance if leakage inductance is large          |

|                                                                                      |

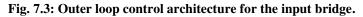

| Fig. 7.3: Outer loop control architecture for the input bridge 108                   |

| Fig. 7.4: Outer loop control architecture for the output bridge 109                  |

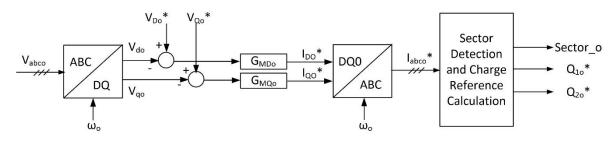

| Fig. 7.5: Inner control loop 110                                                     |

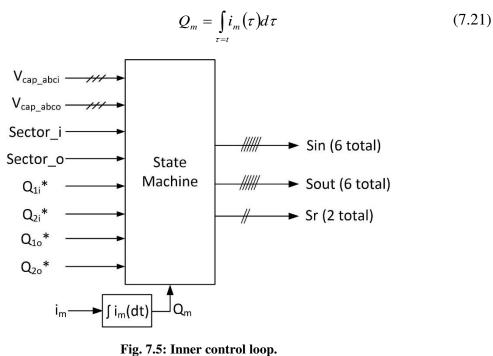

| Fig. 8.1: LC filter with a damping resistor                                          |

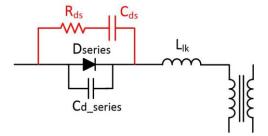

| Fig. 8.2: Resonant circuit and snubber for the auxiliary device                      |

| Fig. 8.3: Diode in series with the transformer and its snubber 117                   |

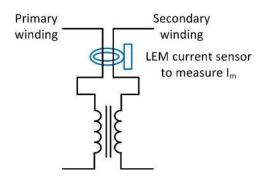

| Fig. 8.4: LEM current sensor to measure the transformer magnetizing                  |

| current                                                                              |

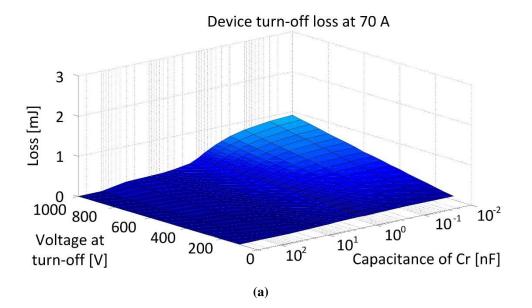

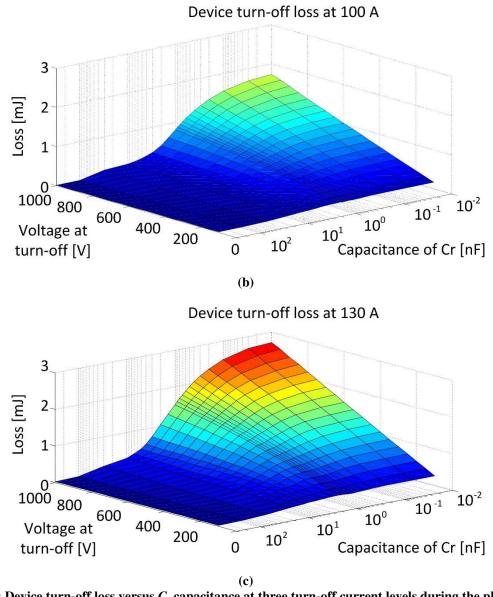

| Fig. 8.5: Device turn-off loss versus $C_r$ capacitance at three turn-off current    |

| levels during the phase-leg transition                                               |

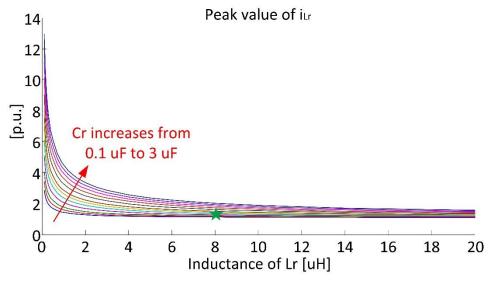

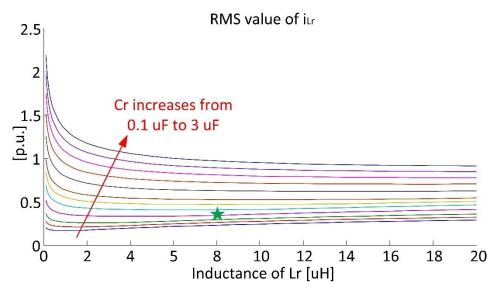

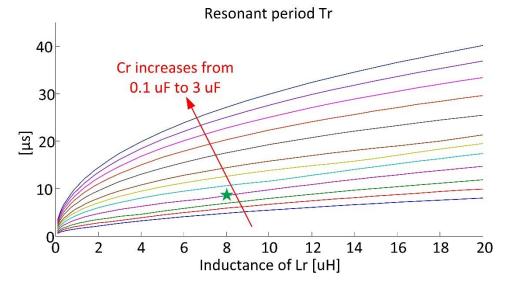

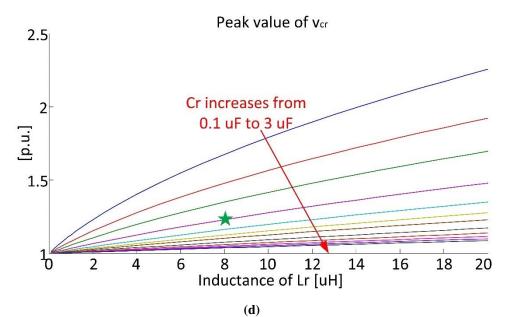

| Fig. 8.6: Peak value, RMS value of $i_{Lr}$ , resonant period $T_r$ , and peak value |

| of $v_{cr}$ versus different $L_r$ and $C_r$ values                                  |

| Fig. 8.7: FPGA-DSP based customized control board for controlling the                |

| S4T                                                                                  |

| Fig. 8.8: Data exchange among ADCs, the DSP, and the FPGA 126                        |

| Fig. 8.9: Control algorithm to be programmed in the DSP and the FPGA 127             |

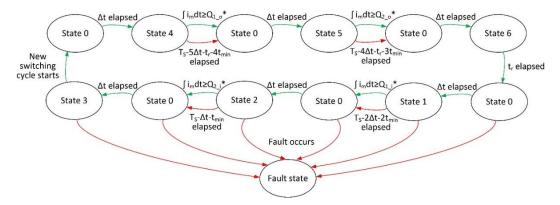

| Fig. 8.10: State machine programmed in the FPGA to control the converter.            |

|                                                                                      |

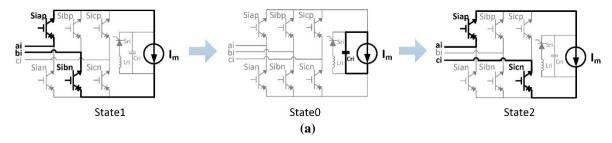

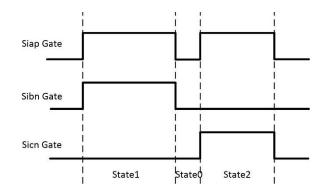

| Fig. 8.11: Transition from state 1 to state 0 and then to state 2: a) circuit        |

| states during the transition; and b) relative device gate signals                    |

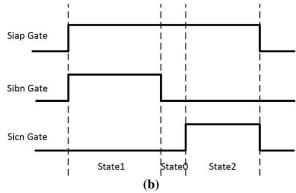

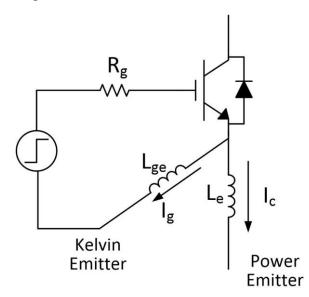

| Fig. 8.12: A device with a common emitter parasitic inductance                       |

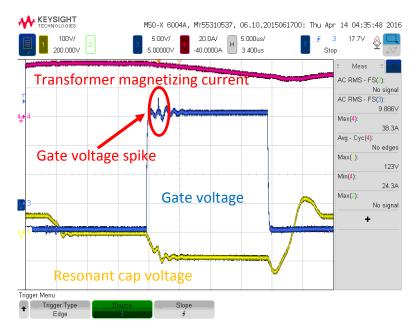

| Fig. 8.13: Experimental waveform of the gate voltage spike                           |

| Fig. 8.14: Modified device gate signals when considering the common                                                                                                                                                                 |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| emitter inductance issue                                                                                                                                                                                                            |     |

| Fig. 8.15: Device with a Kelvin Emitter connection                                                                                                                                                                                  |     |

| Fig. 9.1: Transformer winding mechanism                                                                                                                                                                                             |     |

| Fig. 9.2: Photograph of the fabricated high-frequency transformer for the S4T                                                                                                                                                       |     |

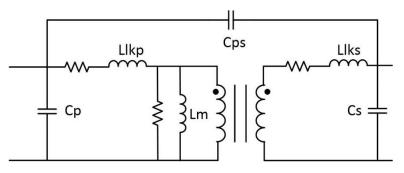

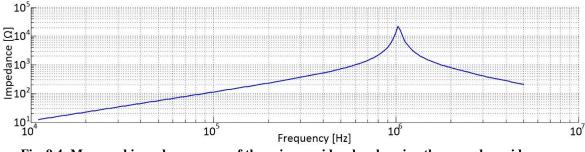

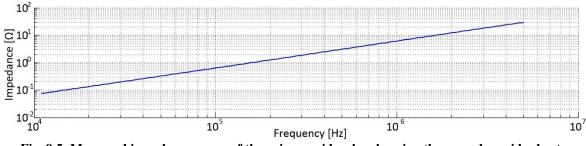

| Fig. 9.3: Equivalent circuit of the transformer considering various parasitic elements                                                                                                                                              |     |

| Fig. 9.4: Measured impedance curve of the primary side when keeping the secondary side open                                                                                                                                         | 144 |

| Fig. 9.5: Measured impedance curve of the primary side when keeping the secondary side short                                                                                                                                        | 144 |

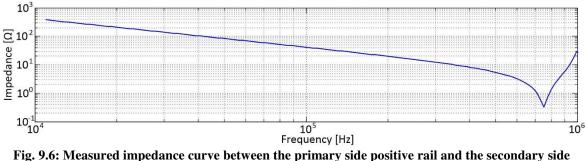

| Fig. 9.6: Measured impedance curve between the primary side positive rail<br>and the secondary side positive rail with both primary and secondary<br>windings shorted                                                               |     |

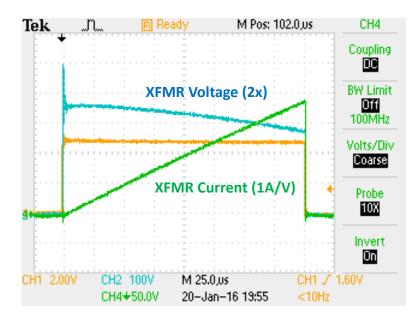

| Fig. 9.7: Experimental waveforms of evaluating transformer's energy storage capability (Blue curve: voltage applied to the transformer with a scaling factor of two; Green curve: current through the transformer with a            |     |

| ratio of 1 volt/ampere)                                                                                                                                                                                                             |     |

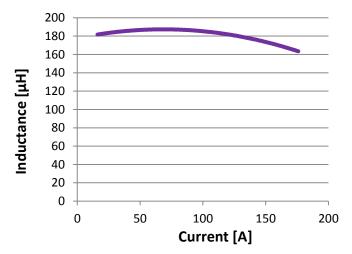

| Fig. 9.8: Calculated magnetizing inductance versus current curve based on the result of Fig. 10.7                                                                                                                                   |     |

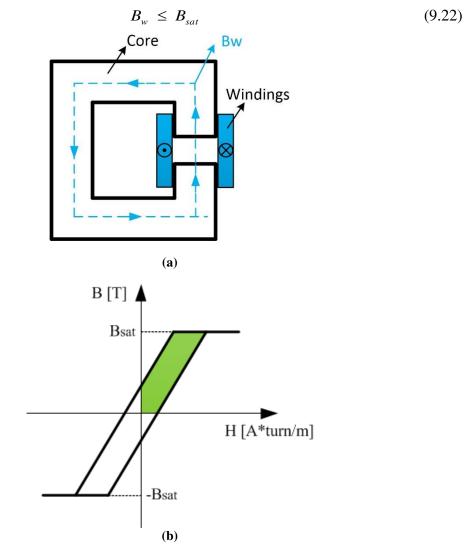

| Fig. 9.9: Transformer design with magnetic core only: a) windings with dc current excites core to cause flux to flow in one direction only; and b) corresponding B-H curve shows that only the 1 <sup>st</sup> quadrant is utilized |     |

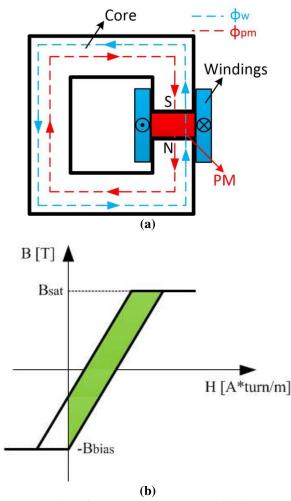

| Fig. 9.10: Hybrid transformer design with permanent magnets inside the magnetic core's air gap: a) flux generated by windings and permanent                                                                                         |     |

| magnets; and b) usable B-H curve extended to the 3 <sup>st</sup> quadrant                                                                                                                                                           |     |

| Fig. 9.11: <i>B-H</i> characteristic of permanent magnet materials [100]                                                                                                                                                            |     |

| Fig. 9.12: Equivalent magnetic circuit for the hybrid transformer design       |     |

|--------------------------------------------------------------------------------|-----|

| when inserting the permanent magnet into the air gap                           |     |

| Fig. 9.13: Proposed hybrid transformer design                                  | 152 |

| Fig. 9.14: Finite element analysis simulation for the two transformer designs: |     |

| a) conventional transformer design with magnetics only; and b) hybrid          |     |

| transformer design with magnetics and permanent magnets                        | 153 |

| Fig. 9.15: Fabricated hybrid transformer: a) core and permanent magnets;       |     |

| and b) final fabricated hybrid transformer                                     | 155 |

| Fig. 9.16: Experimental current and voltage waveforms of testing the two       |     |

| transformers: a) conventional transformer with magnetic cores only; and b)     |     |

| hybrid transformer with magnetic cores and permanent magnets                   | 156 |

| Fig. 9.17: Calculated magnetizing inductance versus current curves based       |     |

| on the results of Fig. 10.16: a) conventional transformer with magnetic cores  |     |

| only; and b) hybrid transformer with magnetic cores and permanent              |     |

| magnets                                                                        | 157 |

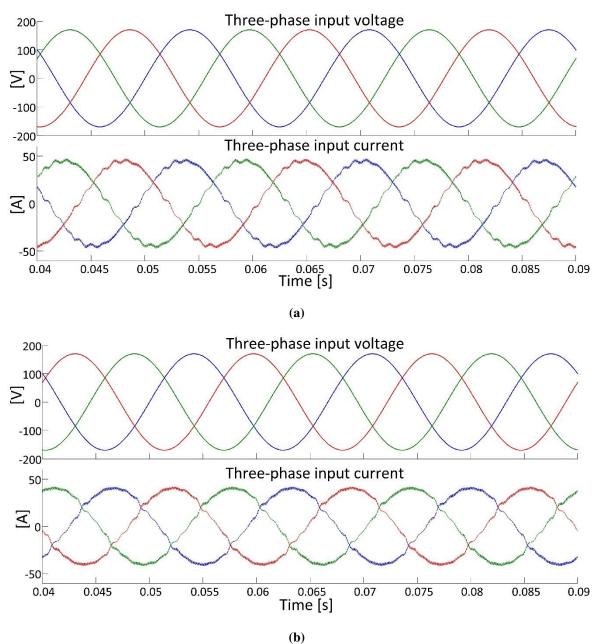

| Fig. 10.1: Simulation waveforms for the S4T of: (a) three-phase input and      |     |

| output currents; and (b) high-frequency transformer magnetizing current,       |     |

| resonant capacitor voltage, and resonant inductor current                      |     |

| Fig. 10.2: Simulation waveforms of the three-phase voltage and current on      |     |

| the input side for the S4T when: (a) power flows in forward direction; and     |     |

| (b) power flows in reverse direction                                           |     |

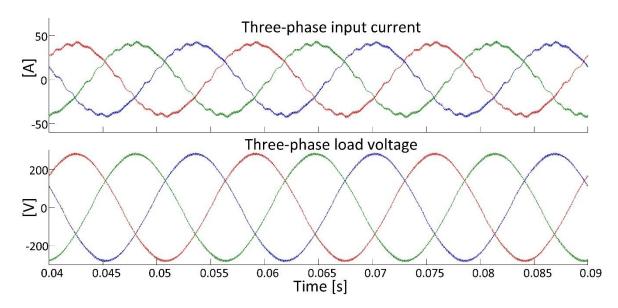

| Fig. 10.3: Simulation waveforms of the three-phase input current and output    |     |

| voltage when a 10 kW resistive load is connected to the S4T output side        |     |

| Fig. 10.4: Simulation waveforms of the two winding currents showing the        |     |

| leakage energy transfer                                                        |     |

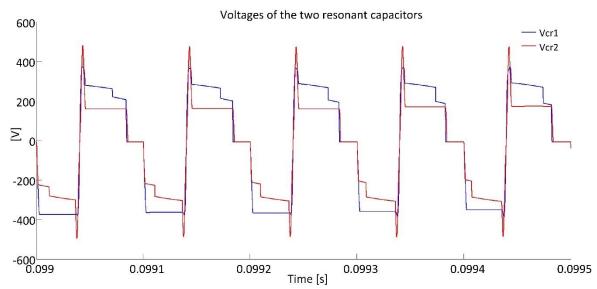

| Fig. 10.5: Simulation voltage waveforms of the two resonant capacitors         |     |

| when considering transformer leakage inductance with diodes connected in       |     |

| series with the transformer                                                    |     |

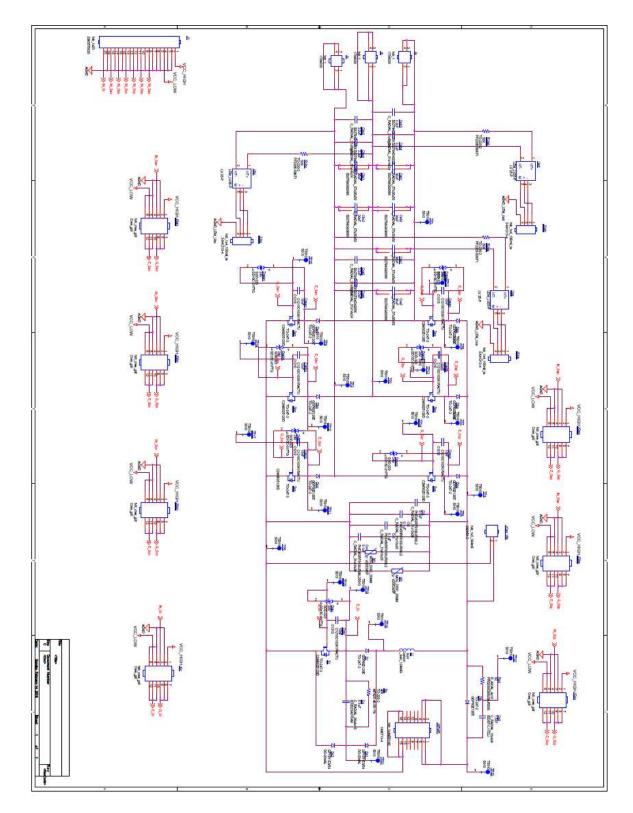

| Fig. 10.6: Schematic of the board                                                                                                                                                                                        | 165  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

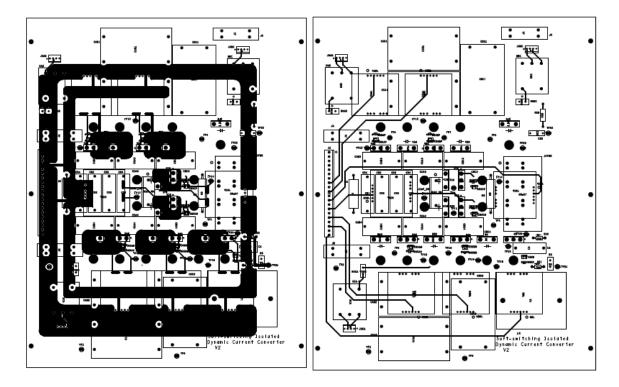

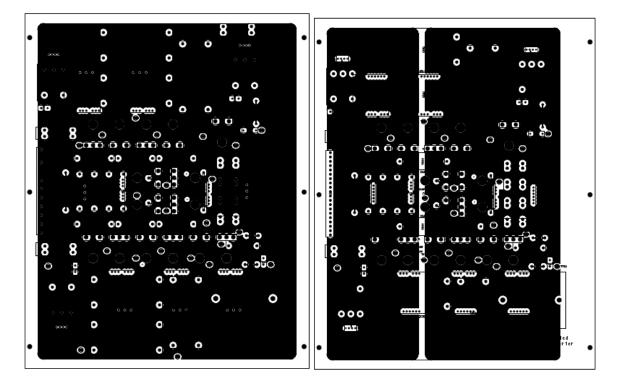

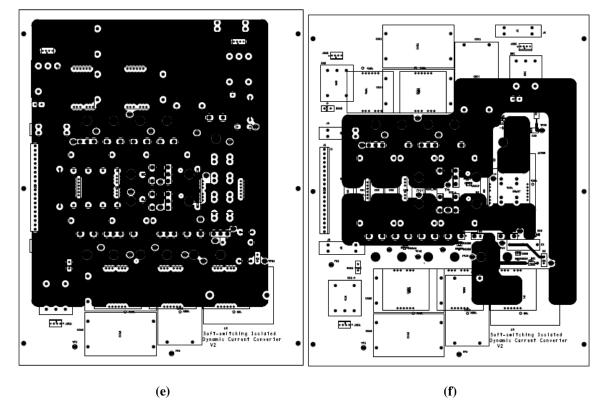

| Fig. 10.7: PCB layout for the S4T converter: a) 1 <sup>st</sup> layer; b) 2 <sup>nd</sup> layer; c) 3 <sup>rd</sup> layer; d) 4 <sup>th</sup> layer; e) 5 <sup>th</sup> layer; and f) 6 <sup>th</sup> layer              | 167  |

| Fig. 10.8: Conceptualized unit assembling for the S4T converter                                                                                                                                                          | 168  |

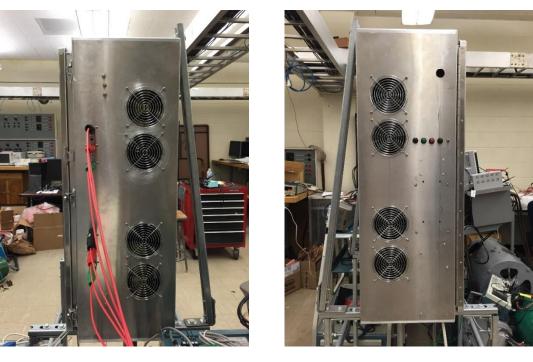

| Fig. 10.9: Final assembled S4T unit: a) unit mounted into an aluminum enclosure; b) power connections for the three-phase input and output on one side; and c) push-buttons and switches on the other side for converter |      |

| control                                                                                                                                                                                                                  | 169  |

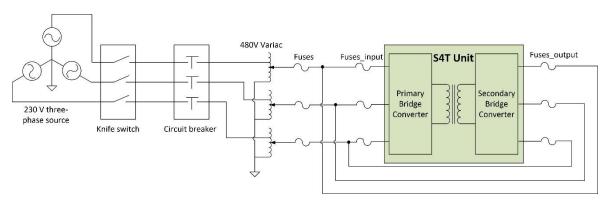

| Fig. 10.10: System schematic for testing the S4T unit                                                                                                                                                                    | 170  |

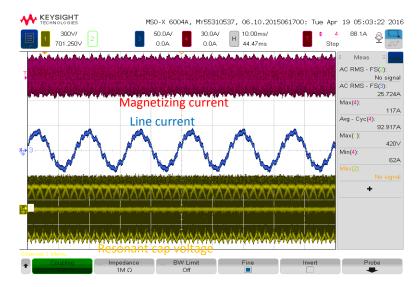

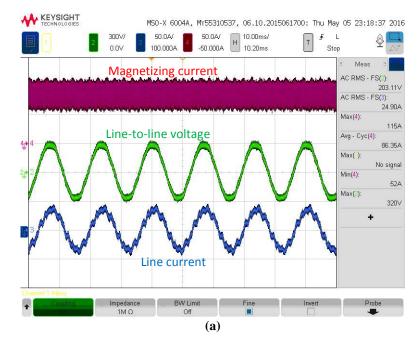

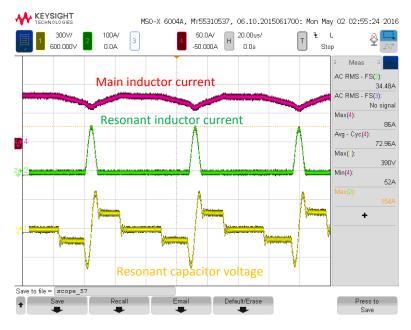

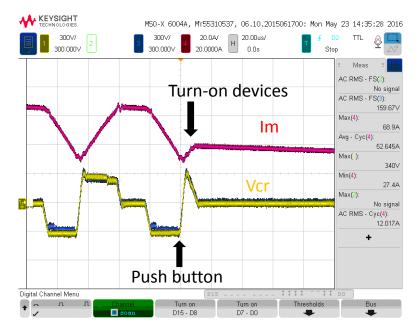

| Fig. 10.11: Experimental waveforms of transformer magnetizing current (CH4, 30 A/div), line current (CH3, 50 A/div), and resonant capacitor                                                                              |      |

| voltage (CH1, 300V/div)                                                                                                                                                                                                  | 171  |

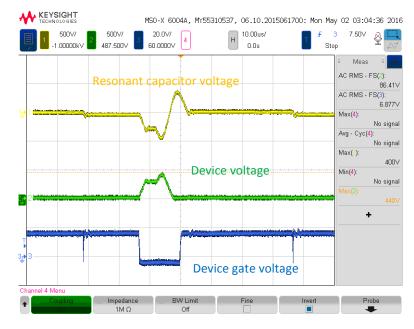

| Fig. 10.12: Experimental waveforms of resonant capacitor voltage (CH1, 300 V/div) and device voltage (CH2, 300 V/div)                                                                                                    | 172  |

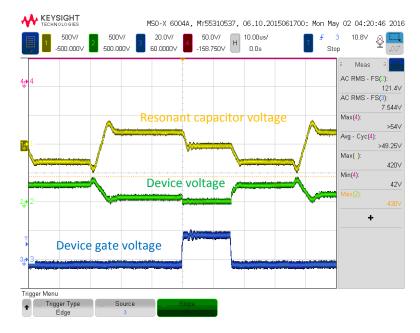

| Fig. 10.13: Zoomed-in cycle-to-cycle waveforms for magnetizing current (CH4, 30 A/div), resonant capacitor voltage (CH1, 300 V/div), and resonant inductor current (CH2, 100 A/div)                                      | 172  |

| Fig. 10.14: One ZVS switching transient waveforms of resonant capacitor voltage (CH1, 500 V/div), device voltage (CH2, 500 V/div), and device gate voltage (CH3, 20 V/div)                                               | 173  |

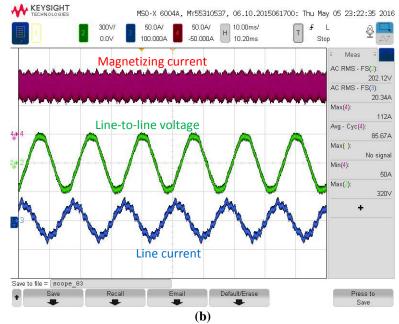

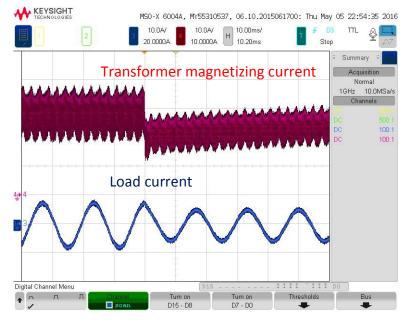

| Fig. 10.15: Experimental waveforms of transformer magnetizing current (CH4, 50 A/div), line-to-line voltage (CH2, 300 V/div), and line current (CH3, 50 A/div) for two power flow directions: a) forward power flow; and | 15.4 |

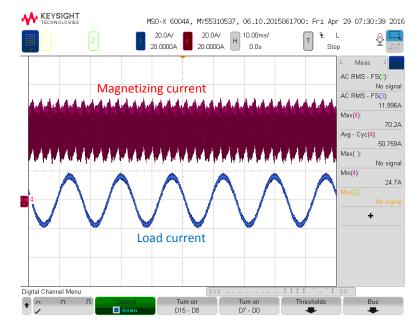

| <ul><li>b) reverse power flow)</li><li>Fig. 10.16: Experimental waveforms of resistive loads test: transformer magnetizing current (CH4, 20 A/div) and current through the resistive load (CH3, 20 A/div)</li></ul>      |      |

| Fig. 10.17: Measured converter loss with different dc currents and line voltages                                                                                                                                                      | 176 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 10.18: Topology of the low-voltage soft-switching dynamic VAr compensator                                                                                                                                                        | 177 |

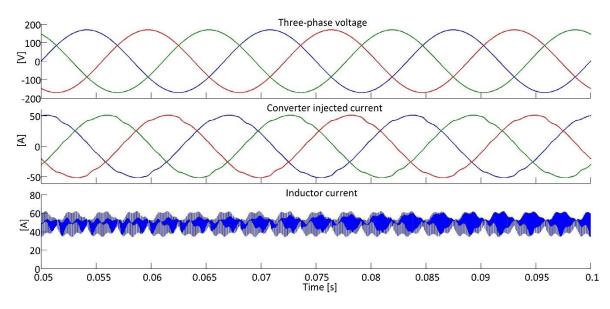

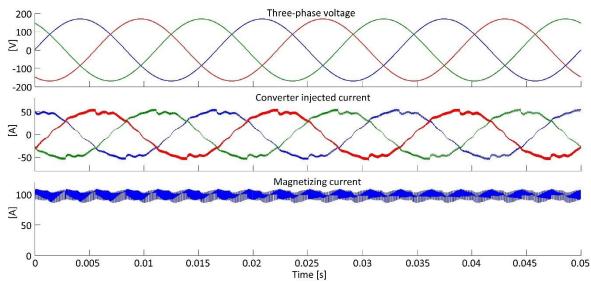

| Fig. 10.19: Simulation results of the three-phase voltage, converter injected current, and inductor current for the low-voltage soft-switching dynamic                                                                                |     |

| VAr compensator                                                                                                                                                                                                                       | 178 |

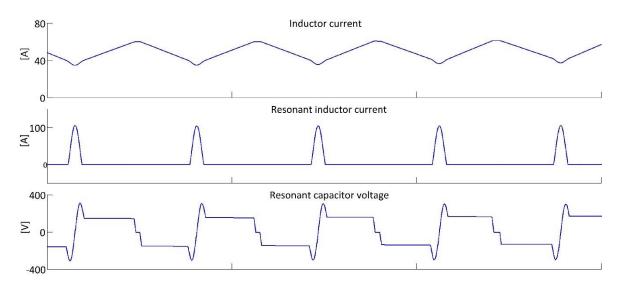

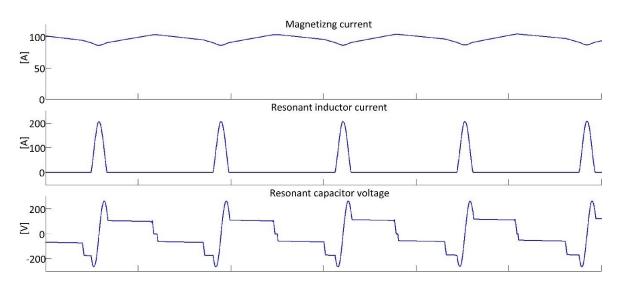

| Fig. 10.20: Cycle-by-cycle waveforms of the inductor current, resonant inductor current, and resonant capacitor voltage for the low-voltage soft-                                                                                     |     |

| switching dynamic VAr compensator                                                                                                                                                                                                     | 178 |

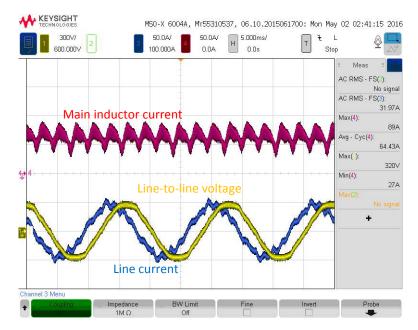

| Fig. 10.21: Experimental waveforms of the inductor current (CH4, 50 A/div), the injected current to phase a (CH3, 50 A/div), and line-to-line voltage Vab (CH1, 300 V/div) for the low-voltage soft-switching dynamic VAr compensator |     |

| Fig. 10.22: Experimental waveforms of the voltage across a device (CH2, 300 V/div) and resonant capacitor voltage (CH1, 300 V/div) for the low-voltage soft-switching dynamic VAr compensator                                         | 180 |

| Fig. 10.23: Experimental waveforms of the inductor current (CH4, 50 A/div), resonant inductor current (CH2, 100 A/div), and resonant capacitor voltage (CH1, 300 V/div) for the low-voltage soft-switching dynamic VAr                |     |

| compensator                                                                                                                                                                                                                           |     |

| Fig. 10.24: Experimental waveforms of one ZVS transient: resonant capacitor voltage (CH1, 500 V/div), device voltage (CH2, 500 V/div), and gate voltage (CH3, 20 V/div) for the low-voltage soft-switching dynamic                    |     |

| VAr compensator                                                                                                                                                                                                                       |     |

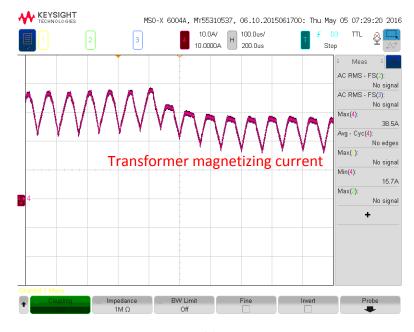

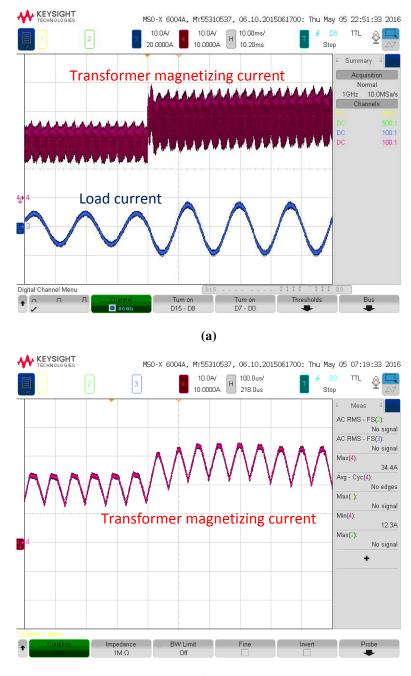

| Fig. 11.1: Transient performance under load step-down change: a) transformer magnetizing current (CH4, 10 A/div) and load current (CH3, 10 A/div); and b) zoomed-in waveforms of the transformer magnetizing                          |     |

| current (CH4, 10 A/div)                                                                                                                                                                                                               |     |

| Fig. 11.2: Transient performance under load step-up change: a) transformer                 |     |

|--------------------------------------------------------------------------------------------|-----|

| magnetizing current (CH4, 10 A/div) and load current (CH3, 10 A/div); and                  |     |

| b) zoomed-in waveforms of the transformer magnetizing current (CH4, 10                     |     |

| A/div)                                                                                     |     |

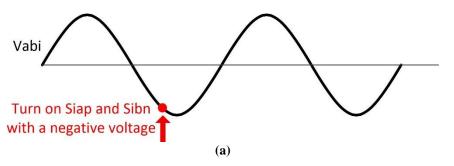

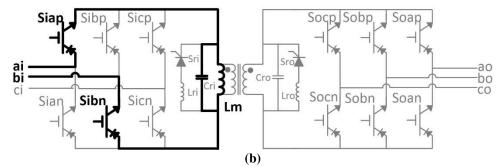

| Fig. 11.3: Charging the resonant capacitors during start-up: a) input line-to-             |     |

| line voltage $V_{abi}$ ; and b) turn-on $S_{iap}$ and $S_{ibn}$ when $V_{abi}$ is negative |     |

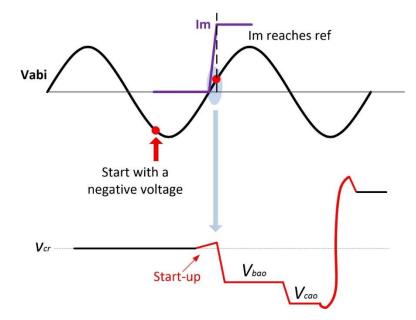

| Fig. 11.4: Conceptualized start-up waveforms of input line-to-line voltage                 |     |

| $V_{abi}$ , the magnetizing current $I_m$ , and the resonant capacitor voltage $V_{cr}$ of |     |

| the first switching cycle after the start-up                                               |     |

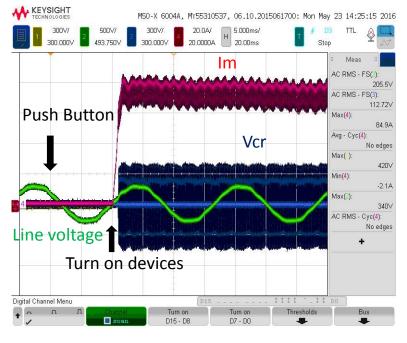

| Fig. 11.5: Start-up experimental waveforms of: a) input line-to-line voltage               |     |

| (CH2, 500 V/div), magnetizing current (CH4, 20 A/div), and resonant                        |     |

| capacitor voltage (CH3, 300 V/div); and b) zoomed-in waveforms of the                      |     |

| magnetizing current (CH4, 20 A/div) and two resonant capacitor voltages                    |     |

| Vcr1 (CH1, 300 V/div) and Vcr2 (CH3, 300 V/div)                                            | 190 |

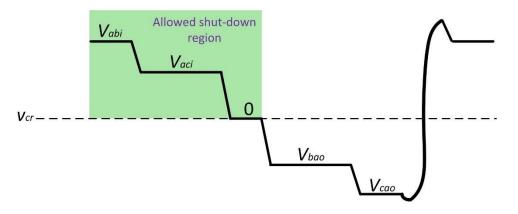

| Fig. 11.6: Converter shut-down by turning on devices $S_{icp}$ and $S_{icn}$               |     |

| Fig. 11.7: Allowed shut-down region with respect to the resonant capacitor                 |     |

| voltage                                                                                    |     |

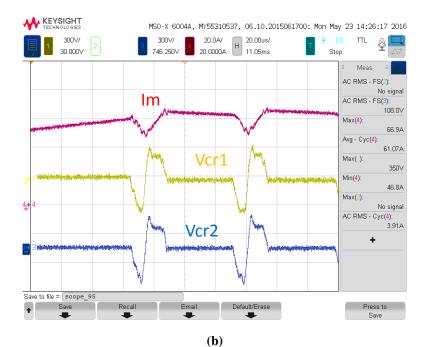

| Fig. 11.8: Shut-down experimental waveforms of: magnetizing current                        |     |

| (CH4, 20 A/div) and two resonant capacitor voltages Vcr1 (CH1, 300                         |     |

| V/div) and Vcr2 (CH3, 300 V/div)                                                           |     |

| Fig. 12.1: Stacked dc to three-phase ac converter using dc to single-phase                 |     |

| ac converter modules                                                                       |     |

| Fig. 12.2: : Stacked three-phase ac to ac converter using three-phase ac to                |     |

| single-phase ac converter modules                                                          |     |

| Fig. 12.3: Stacked dynamic VAr compensator modules                                         | 196 |

| Fig. 12.4: Topology of the modular soft-switching Dynamic VAr                              |     |

| Compensator for high-voltage applications                                                  |     |

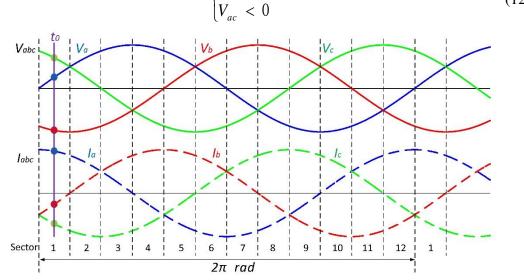

| Fig. 12.5: Three-phase voltage and current waveforms with current leading voltage by 90°                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

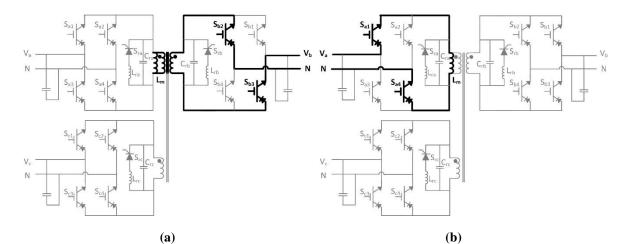

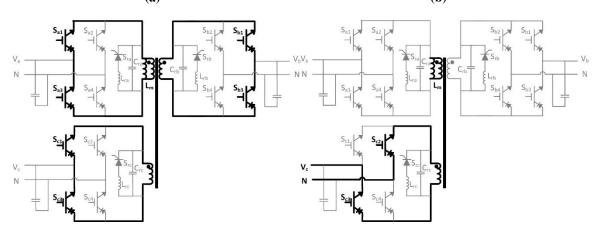

| Fig. 12.6: Operating states over one switching cycle: (a) state $1 - \text{charging}$ the magnetizing inductance with the highest line-to-neutral voltage; (b) state $2 - \text{charging}$ the magnetizing inductance with the second line-to- |

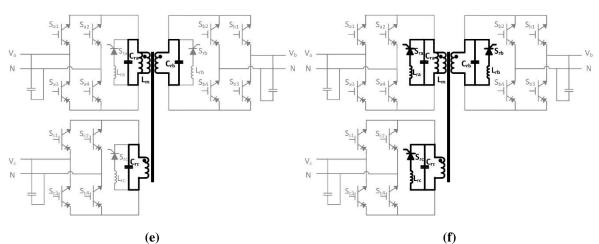

| neutral voltage; c) state 3 –freewheeling; (d) state 4 – discharging the magnetizing inductance with the negative line-to-neutral voltage; (e) state $0 - ZVS$ transition state; and (f) state 5 – resonant state                              |

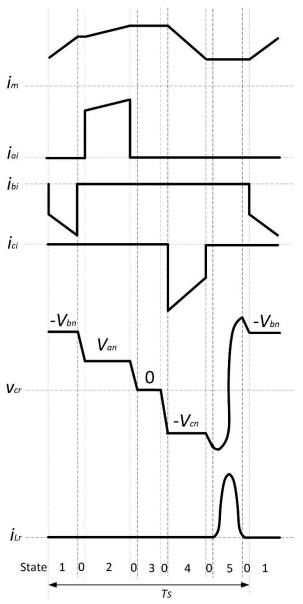

| Fig. 12.7: Conceptualized waveforms (states $1 - 4$ correspond to Fig. 12.6 (a) – (d); state 0 corresponds to Fig. 12.6 (e); and state 5 corresponds to Fig.                                                                                   |

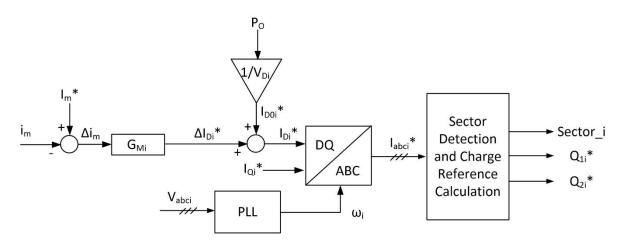

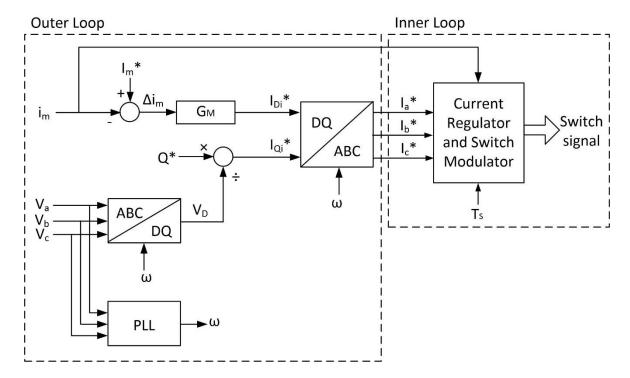

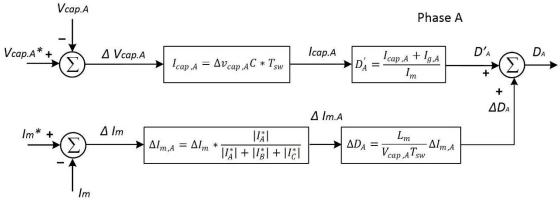

| 12.6 (f))202Fig. 12.8: Control architecture for the single-module soft-switchingdynamic VAr compensator205                                                                                                                                     |

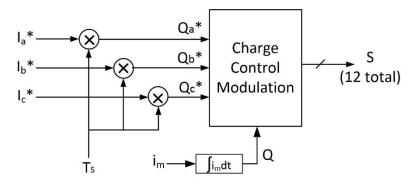

| Fig. 12.9: Inner control loop for the modular soft-switching dynamic VAr compensator                                                                                                                                                           |

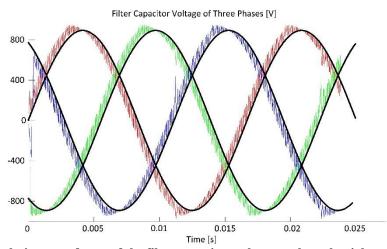

| Fig. 12.10: Simulation results of the three-phase voltage, converter-injected current, and magnetizing current for the single-module soft-switching dynamic VAr compensator                                                                    |

| Fig. 12.11: Cycle-by-cycle waveforms of the magnetizing current, resonant inductor current, and resonant capacitor voltage for the single-module soft-switching dynamic VAr compensator                                                        |

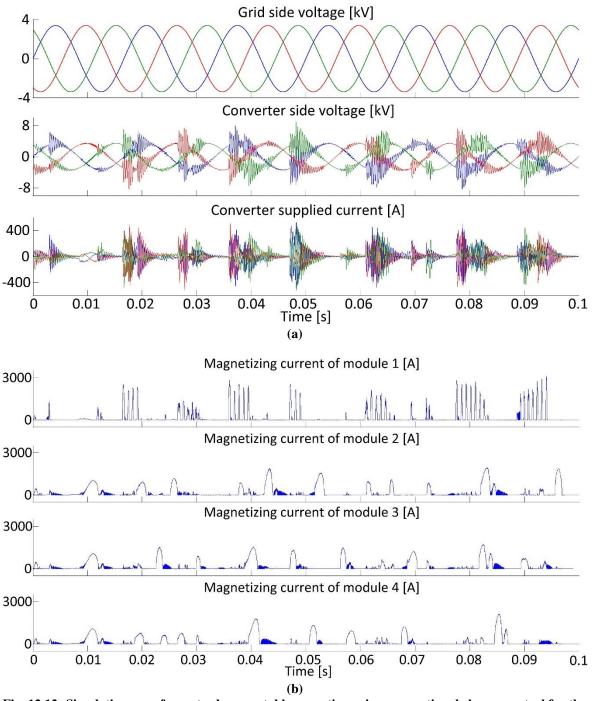

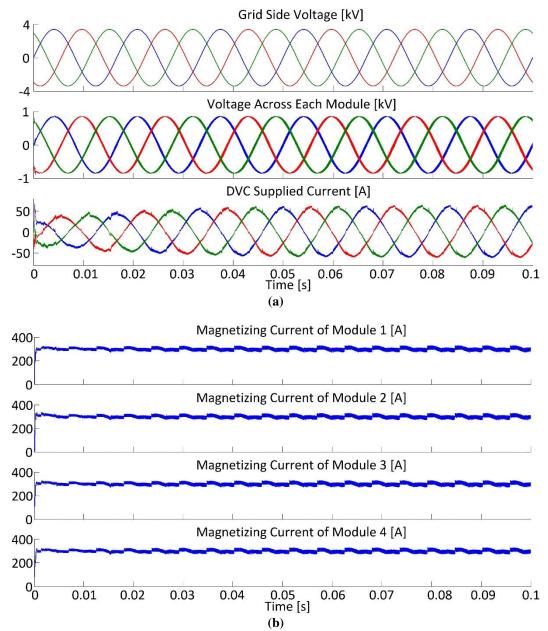

| Fig. 12.12: Simulation waveforms to show unstable operation using conventional charge control for the stacked dynamic VAr compensator: a) waveforms of grid side voltage, converter side voltage, and converter                                |

| supplied current, and (b) magnetizing current of four modules                                                                                                                                                                                  |

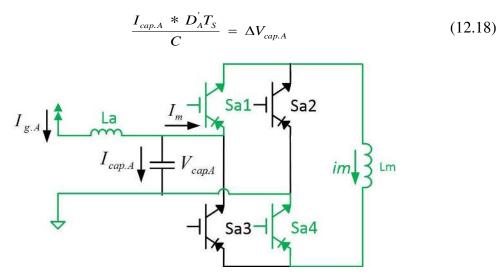

| Fig. 12.13: Simplified phase A bridge configuration                                                                                                                                                                                            |

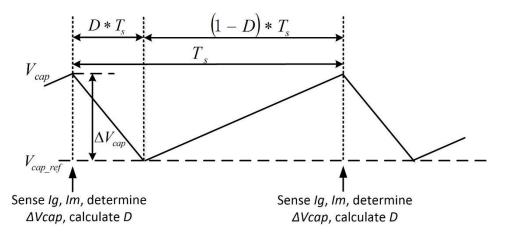

| Fig. 12.14: Principle of controlling the filter capacitor voltage                                                                                                                                                                              |

| Fig. 12.15: Simulation waveforms of the filter capacitor voltage to show the                                                                                                                                                                   |

| tight voltage regulation                                                                                                                                                                                                                       |

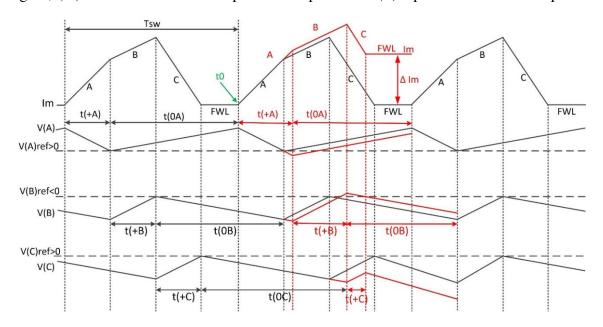

| Fig. 12.16: Principle of increasing the magnetizing current within one        |     |

|-------------------------------------------------------------------------------|-----|

| switching cycle                                                               |     |

| Fig. 12.17: Inner control loop for the series-stacked converter               |     |

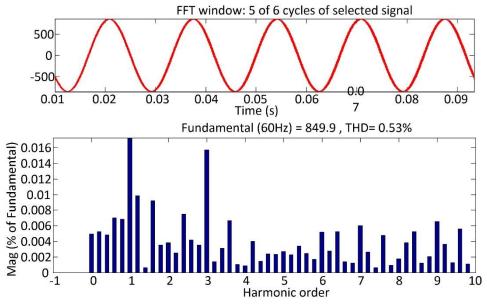

| Fig. 12.18: Harmonics spectrum of the filter capacitor voltage when using     |     |

| the proposed deadbeat control strategy                                        |     |

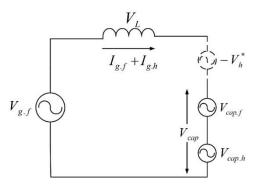

| Fig. 12.19: Equivalent circuit for each phase on the ac side                  |     |

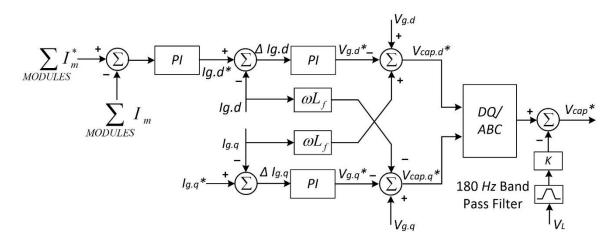

| Fig. 12.20: Outer control loop for the series-stacked converter               |     |

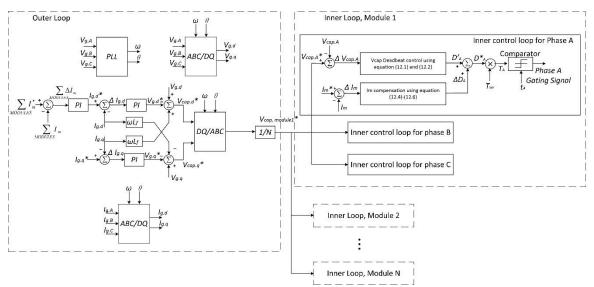

| Fig. 12.21: Complete control diagram for the series-stacked converter         |     |

| Fig. 12.22: Simulation waveforms to show stable operation using the           |     |

| proposed control strategy for the stacked converter: a) waveforms of grid     |     |

| side voltage, converter side voltage, and converter supplied current, and (b) |     |

| magnetizing current of four modules                                           | 220 |

#### SUMMARY

Galvanic isolation is widely used in power supply networks to provide fault isolation and electric energy transfer between circuits at different potentials without a direct conduction path. Compared to the conventional 50 or 60 Hz low-frequency transformers, a power electronics converter with medium- to high-frequency isolation, which is commonly referred as a solid state transformer (SST), significantly reduces the weight and size by reducing the amount of high-volume magnetic core materials. In addition, the SST provides intelligence of: 1) bi-directional power flow control; 2) reactive power compensation; 3) harmonics isolation and elimination; 4) dc or multi-port interfacing; 5) voltage regulation and sag correction; and 6) fault isolations.

Most of the existing SST topologies are isolated voltage source converters, which have the issues of complex multi-stage structures, large component count, high system loss, and high failure rate of bulky energy storage elements. Advanced topologies for implementing the SST have simple circuit structures with lower component count. However, most of them involve either a complicated control strategy, or severe device loss and stress due to hard-switching conditions and inevitable circuit parasitic elements. Low efficiency and poor reliability are the main issues that hinder replacing the conventional utility transformers by the SSTs. Using emerging wide-band-gap devices such as Silicon Carbide (SiC) devices can lead to faster switching speed and higher efficiency. However, the spikes and resonances caused by parasitic elements are exacerbated due to the high *dv/dt* and *di/dt*.

This dissertation presents a novel soft-switching solid state transformer (S4T) topology, which has the features of:

1) minimal two-stage conversion with low device count;

2) soft-switching features for all devices at full range;

3) four-quadrant operation with voltage buck and boost capabilities;

4) arbitrary power factors and frequencies for the input and the output;

5) eliminating the dc energy storage capacitors to avoid inrush current and improve reliability;

6) fast dynamic response to transients;

7) ease of control to achieve soft-switching operation;

8) flexible configurations for two- or multi-terminal dc, single- and multi-phase ac systems such that acting as a universal converter;

9) modular design to scale to medium voltage and high power levels through series and/or parallel stacking the converter modules.

This dissertation presents the topology and the operating principle. Unique attributes, converter analysis, control, and design considerations of the S4T are also provided.

Various topologies can be derived from the proposed S4T, with the same major operating principles. In this dissertation, two soft-switching dynamic VAr compensators are also presented, one with a three-phase converter bridge structure and the other one with a modular structure. Both topologies achieve full-range soft-switching conditions for all main devices.

The high-frequency transformer is the key element of the SST, which acts as an energy transferring element with high-frequency galvanic isolation. Proper design of the high-frequency transformer is crucial to achieve compact size, low loss, low leakage, and high enough dielectric insulation. As part of the dissertation, the transformer design is presented in detail. For the proposed S4T, a constant dc current is maintained in the transformer

magnetizing inductance, resulting in a dc-biased magnetic flux in the high-frequency transformer. This dissertation also presents a hybrid transformer design technique of using high-frequency magnetic cores and permanent magnets to significantly reduce core volume.

The proposed S4T, which has a modular topology, can also be series and/or parallel stacked. This allows using fractionally-rated devices for high-voltage and high-power applications. Even though stacking of voltage source modular converters has been widely investigated in the past, the research of balance control for series stacking current source converters has not been initiated. The low inertial and strong coupling effect properties of the proposed converter impose more severe challenges for stable operation of the series-stacked converter. As part of the research, a robust multi-loop control strategy is developed to realize voltage and power balance for the series-stacked converter system.

A three-phase 208 V / 10 kVA three-phase S4T is designed and fabricated to experimentally verify the functionality of the proposed topology.

The S4T can find a wide range of applications such as dc energy storage interface, uninterruptible power supply (UPS) systems, electrified transportation, space and weight critical applications, smart distribution systems, flexible AC transmission systems (FACTs), and high voltage direct current systems (HVDC).

### **CHAPTER 1: INTRODUCTION AND RESEARCH OBJECTIVES**

### 1.1. Galvanic Isolation in the Electric Grid

Galvanic isolation has been widely used in power supply networks to provide fault isolation as well as electric energy transfer between circuits at different potentials without a direct current flowing path. In the electric grid, power transformers of 50 or 60 Hz frequency are deployed to step up the voltage at generation for efficient, long distant electricity transmission and to step it down at the distribution system for customer use. In 2010, the U.S. demand for large power transformers, which are rated above 60 MVA, was 127,309 MVA, valued at more than \$ 1 billion [1]. Fig. 1.1 represents the historical annual installment of large power transformers in the United States, not including replacement demand [1]. It can be seen from the figure that the need for large power transformers has been growing steadily since 1999, after a low investment period in 1990s.

The low-frequency transformer deployed in the grid, although proven reliable, efficient, and cost effective, has a high volume of steel that makes the transformer very bulky. The large dimensions and heavy weight pose unique requirements for safe transportation. In addition, the lack of intelligence makes dynamic control of the grid more challenging. The distributed and renewable energy sources, which nowadays have a high penetration level, require additional power converters with proper galvanic isolation when connecting to the grid. Fig. 1.2 and Fig. 1.3 shows the U.S. total installed capacity and generation for wind and solar respectively [2].

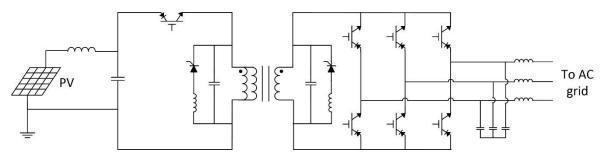

Fig. 1.2: U.S. total installed wind electricity capacity and generation [2].

Fig. 1.3: U.S. PV electricity installed capacity and generation [2].

### 1.2. Solid State Transformer

The idea of a solid state transformer (SST) has attracted tremendous interest for almost five decades, ever since the principles of power conversion were first understood. The SST is a combination of a high-frequency transformer link and solid state switching circuits. High-frequency isolation allows for the saving of significant volume and weight of magnetic materials. In addition, the SST introduces features that include, but are not limited to: 1) bidirectional power flow control, 2) reactive power compensation, 3) harmonic isolation and elimination, 4) dc or multi-terminal interfacing, 5) voltage regulation and sag correction, and 6) fault isolation. The promise of replacing numerous existing 60 hertz transformers, with a power-electronics-based device that is smaller, controllable, and more flexible, has an undeniable appeal. However, the reality has been much more challenging. It has proven difficult to match the low cost (\$25/kVA), high efficiency (>97%), and long life (40 years) of the 60 hertz grid-connected transformer. Further, the practical challenges posed by fault current coordination (>10 kA) with downstream switchgear, and, for transformers connected directly to the 13 kV grid (or higher), the need for 120 kV (or higher) basic insulation level, seem well beyond the capability of cost-effective state of the art power conversion technology.

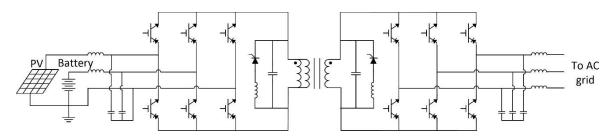

In more specific applications, the potential for SST's is real. Unidirectional ac/dc converters with high-frequency isolation are really switched mode power supplies, and should not be included in the family of solid state transformers. An SST should convert ac (or dc) voltage to another ac (or dc) voltage with galvanic isolation between the input and output, possibly at a different voltage level and/or frequency, and should inherently be able to provide bidirectional control of real and/or reactive power flows. Applications include locomotives, light rail, EV fast chargers, PV inverters, and battery energy storage systems – many of them emerging fields. It could also include specialized bidirectional drives where 60 hertz isolation transformers are often used to manage noise and transient injection into long cables or motors, along with converters to condition the voltage applied to the motor. With all the above potential applications, the global SST market is expected to be valued at more than \$200 million by 2020 [3].

#### **1.3. Problem Statement**

Significant work has been done on implementing SSTs. These can typically be classified as single-stage with ac switches on the input and output, connected with a high-frequency transformer, two-stage with an ac/dc converter followed by an inverter, and three-stage based on ac/dc-dc/dc (including isolation)-dc/ac converters in cascade. It has been concluded that the three-stage converter, including a dual-active-bridge (DAB) soft-switched dc/dc converter, offers perhaps the best performance and controllability. Scaling the SST for higher power and higher voltages required for traction and direct grid connected applications, is also seen to be challenging, and has been addressed in many papers.

One of the major restrictions of direct ac/ac types of conversion comes from the leakage inductance of the transformer. At higher frequencies, this becomes the limiting element in the ability to transfer power across the isolation barrier. Factors such as diode reverse recovery can result in energy trapped in the leakage inductance, which in turn causes excessive stress on the components and limits operating range and efficiency. The DAB converter is considered attractive because it handles all real device and transformer parasitic elements, and still allows zero-voltage-switching (ZVS), albeit over a narrow range of voltage transfer ratios. Even for the three-stage SST, assuming that the DAB converter always operates under ZVS conditions, the rectifier and inverter have to operate in hard switching mode and incur high switching losses. Efforts have been spent to address these issues, for instance with resonant switching to reduce losses, or simpler minimal topologies to reduce complexity, but the efforts have always fallen short of addressing the myriad of issues that can limit solid state transformer performance.

## 1.4. Research Scope and Objectives

This paper presents a new topology for a soft-switching solid-state transformer (S4T), which has a simple and symmetrical architecture, minimal device and component count in the power flow path, with small-rated auxiliary components that enable the soft switching

property. Unlike the DAB converter, the S4T realizes soft switching for all its main devices over the entire load range, and features controlled dv/dt and di/dt rates. Further, it can realize dc, single- or multi-phase ac on the input/output at arbitrary frequencies and power factors with sinusoidal voltages and low electromagnetic interference (EMI). It shows simple control and benign shut down under fault and failure modes, and is relatively insensitive to key parameters such as transformer leakage inductance. By eliminating components such as electrolytic capacitors, it can also realize higher power density and longer life. Finally, it holds the promise of achieving high efficiency, particularly as it scales up in voltage and power. It provides the simplicity of single-stage SSTs, with the control attributes of the threestage SSTs, with higher efficiency, lower dv/dt rate, and an ability to scale that seems unique.

Two soft-switching dynamic VAr compensators, which are derived from the proposed S4T using the same soft-switching operating principle, are also presented, one with a three-phase converter bridge structure and the other one with a modular structure. Both topologies achieve full-range soft-switching conditions for all the main devices.

The high-frequency transformer is the key element of the SST, which has to be properly designed to meet the objectives of achieving compact size, low loss, low leakage, and high enough dielectric insulation. As part of the dissertation, the transformer design is presented in detail. Apart from conventional transformer design methodology, this dissertation also presents a hybrid transformer design technique of using high-frequency magnetic cores and permanent magnets to significantly reduce the core volume.

The proposed S4T has a modular structure, allowing it to be scaled to high voltage through series stacking. However, the low-inertial and strong coupling properties of the proposed converter impose more severe challenges for stable operation of the series-stacked converters. As part of the research, a robust multi-loop control strategy is developed to realize voltage and power balance for the series-stacked converter system.

#### **1.5.** Outline of Chapters

Chapter 2 provides an overview of existing solutions for implementing the SST. It first summarizes the high-frequency isolation links for various topologies based on the functional difference. Then it gives a review of topologies for all types of conversion, including dc to single-phase ac, dc to three-phase ac, single-phase to single-phase ac, single-phase to three-phase ac, three-phase to three-phase ac, and multi-port power conversion. Comparisons for various topologies are also presented in this chapter.

Chapter 3 introduces the topology and operating principle of the Dyna-C, which is a minimal topology for implementing the three-phase SST. Various issues associated with hard-switching conditions are discussed.

Using wide-band-gap devices such as SiC is becoming prevalent in the design of efficient power converters. It seems to be able to address several issues of the hard-switching Dyna-C, and meanwhile makes it feasible to design the converter for medium voltage. However, many issues will arise due to the extreme high di/dt and dv/dt rates. Chapter 4 discusses and analyzes all these issues, and presents the necessity of designing the converter with soft-switching techniques.

Chapter 5 presents the proposed topology of the zero-current-switching solid state transformer. Principles of operation, simulation results, and some discussions are provided.

Chapter 6 proposes the topology of the zero-voltage-switching solid state transformer, named as S4T. A ZVS auxiliary resonant circuit is first proposed to achieve ZVS operation for current source converters, and then the ZVS SST topology is presented. Compared to the ZCS one, it shows more attactive benefits, and thus a prototype will be developed based on this topology. Various topology variations are also presented. Principle of operation and unique attributes are discussed.

Chapter 7 gives the analysis and control strategy for the S4T. Chapters 8 and 9 discuss the converter design and the high-frequency transformer design for the S4T, respectively. Chapter 10 presents the simulation and experimental validation from a 208 V/ 10 kVA S4T

unit. The unit design and the testing system are discussed, and experimental results are presented. As an extended application, the S4T is also operated as a low-voltage three-phase dynamic VAr compensator, whose operation is demonstrated with the fabricated S4T unit. Chapter 11 presents the converter operating principle under load transients, start-up, shut-down, and fault conditions.

Chapter 12 discusses the scaling to medium voltage through series stacking the converter modules, by using the example of the modular soft-switching dynamic VAr compensator. The converter shows low inertia and strong coupling properties, which impose challenges on stabilizing the series-stacked system. A robust multi-loop control strategy is presented in this chapter to address these issues.

Chapter 13 summarizes the research contribution, and presents recommendations for future work.

# **CHAPTER 2: REVIEW OF LITERATURE AND PREVIOUS WORK**

## 2.1. Introduction

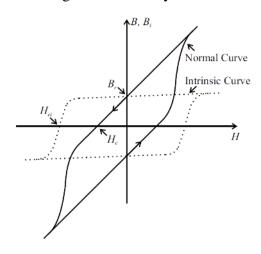

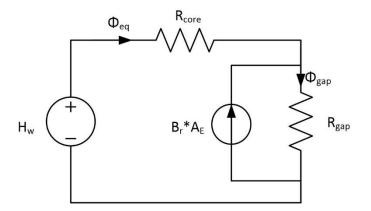

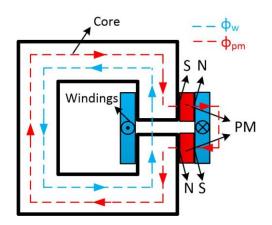

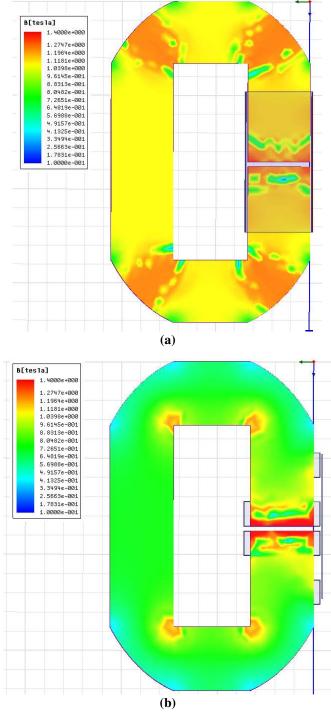

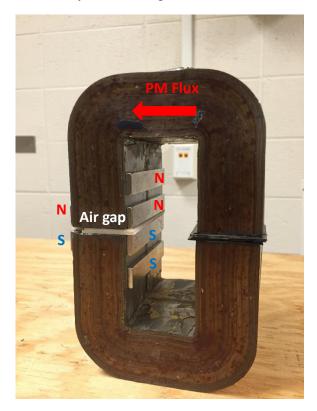

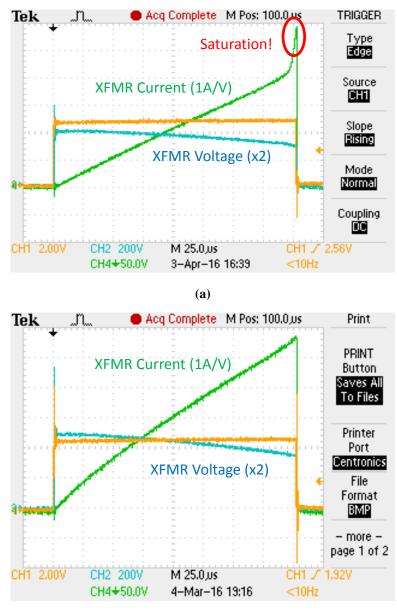

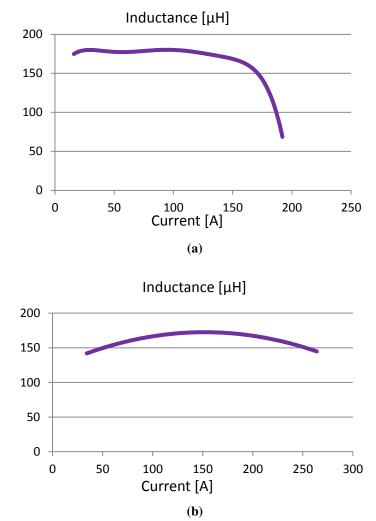

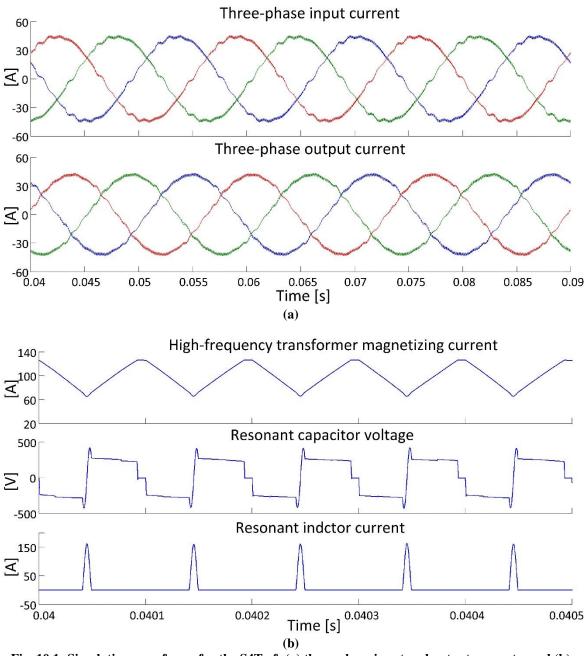

Since the first SST topology was introduced in 1968 as a single-phase ac/ac isolated matrix converter [4], various alternative topologies have been proposed to implement the SST. These include a multi-stage structure that uses an isolated dc/dc converter to provide high-frequency galvanic isolation, as well as an advanced integrated structure with reduced-stage that performs direct isolated ac/ac power conversion. The high-frequency transformer within these SST topologies works under distinct principles.