## **UC Irvine**

#### **UC Irvine Electronic Theses and Dissertations**

#### Title

Software Assists to On-chip Memory Hierarchy of Manycore Embedded Systems

#### **Permalink**

https://escholarship.org/uc/item/8bx2m2hw

#### **Author**

Namaki Shoushtari, Abdolmajid

#### **Publication Date**

2018

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

# $\begin{array}{c} \text{UNIVERSITY OF CALIFORNIA,} \\ \text{IRVINE} \end{array}$

# Software Assists to On-chip Memory Hierarchy of Manycore Embedded Systems DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Majid Namaki Shoushtari

Dissertation Committee: Professor Nikil Dutt, Chair Professor Alex Nicolau Professor Elaheh Bozorgzadeh

Portion of Chapter 2 © 2017 IEEE

Portion of Chapter 2 © 2018 ACM

Portion of Chapter 3 © 2015 IEEE

Portion of Chapter 3 © 2017 IEEE

All other materials © 2018 Majid Namaki Shoushtari

# **DEDICATION**

In memory of my dear aunt Shahnaz, and my beloved grandmothers.

# TABLE OF CONTENTS

|                           |      |                                                                                                           | Page      |

|---------------------------|------|-----------------------------------------------------------------------------------------------------------|-----------|

| LI                        | ST ( | OF FIGURES                                                                                                | vii       |

| LI                        | ST ( | OF TABLES                                                                                                 | xi        |

| $\mathbf{A}^{\mathbf{c}}$ | CKN  | OWLEDGMENTS                                                                                               | xii       |

| $\mathbf{C}^{\gamma}$     | URR  | ICULUM VITAE                                                                                              | xiii      |

| $\mathbf{A}$              | BST  | RACT OF THE DISSERTATION                                                                                  | xvi       |

| 1                         | Intr | roduction                                                                                                 | 1         |

|                           | 1.1  | Technology Implications                                                                                   | 1         |

|                           |      | 1.1.1 Emerging Manycore Architectures                                                                     | 1         |

|                           | 1.0  | 1.1.2 Memory Subsystem of Manycores                                                                       | 3<br>5    |

|                           | 1.2  | Workload Implications                                                                                     |           |

|                           |      | 1.2.1 Data-intensive Workloads and Variation in their Memory Requirement  1.2.2 Error-Resilient Workloads | .s 5<br>6 |

|                           | 1.3  | Thesis Contributions and Organization                                                                     | 7         |

|                           |      |                                                                                                           | ·         |

| 2                         |      | ware-Programmable On-chip Memory Hierarchy                                                                | 10        |

|                           | 2.1  | Introduction                                                                                              | 10        |

|                           | 2.2  | Prior Work on SPMs in Multicores and Manycores                                                            | 14        |

|                           | 2.3  | Target System Architecture Template                                                                       | 16        |

|                           |      | 2.3.1 SPM Programming Model                                                                               | 17        |

|                           |      | 2.3.2 Architecture Model                                                                                  | 20        |

|                           |      | 2.3.3 Execution Model                                                                                     | 21        |

|                           |      | 2.3.4 Coherence Issues                                                                                    | 22        |

|                           | 2.4  | 2.3.5 OS/Runtime Support                                                                                  | 23        |

|                           | 2.4  | Motivational Example                                                                                      | 24        |

|                           | 2.5  | ShaVe-ICE Details                                                                                         | 27        |

|                           |      | 2.5.1 SPM Allocator                                                                                       | 28        |

|                           |      | 2.5.2 Allocation Policies                                                                                 | 28        |

|                           |      | 2.5.2.1 Non-preemptive Allocation Heuristics                                                              | 29<br>29  |

|                           |      | 2.5.2.1.1 Local Allocator(LA)                                                                             |           |

|   |     |         | 2.5.2.1.3 Closest Neighborhood Allocator (CNA)                       | 30 |

|---|-----|---------|----------------------------------------------------------------------|----|

|   |     |         | 2.5.2.2 Preemptive Allocation Heuristics                             | 3  |

|   |     |         | 2.5.2.2.1 Closest Neighborhood with Guaranteed Local Share           |    |

|   |     |         | Allocator (CNGLSA)                                                   | 3  |

|   |     | 2.5.3   | Hardware Support                                                     | 33 |

|   |     | 2.0.0   | 2.5.3.1 Distributed Memory Management Units                          | 33 |

|   |     |         | 2.5.3.2 Network Protocol                                             | 34 |

|   |     | 2.5.4   | Data Movements in ShaVe-ICE                                          | 35 |

|   |     | 2.5.4   |                                                                      |    |

|   |     |         | 1                                                                    | 35 |

|   |     |         |                                                                      | 35 |

|   | 0.0 | CDM C   | 2.5.4.3 Data Migration                                               | 36 |

|   | 2.6 |         | Sharing Evaluations                                                  | 37 |

|   |     | 2.6.1   | Experimental Setup                                                   | 37 |

|   |     | 2.6.2   | Remote vs. Off-chip Access Latencies                                 | 37 |

|   |     | 2.6.3   | Memory Microbenchmark                                                | 36 |

|   |     | 2.6.4   | Performance Comparisons: ShaVe-ICE vs. Software Cache                | 4  |

|   |     | 2.6.5   | Performance Comparisons: ShaVe-ICE Policies                          | 42 |

|   |     |         | 2.6.5.1 Scenario 1: Core Underutilization                            | 44 |

|   |     |         | 2.6.5.2 Scenario 2: Variation in Memory Working Set Size             | 46 |

|   |     |         | 2.6.5.3 Scenario 3: Reducing Network Traffic                         | 47 |

|   |     |         | 2.6.5.4 Scenario 4: Guaranteeing SPM Share for Locally-pinned Thread | 48 |

|   |     | 2.6.6   | Energy Comparisons: ShaVe-ICE Policies                               | 50 |

|   |     | 2.6.7   | Experiments with Real Workload Mixes                                 | 5  |

|   | 2.7 | Discus  | sion on Overheads                                                    | 54 |

|   | 2.8 | Cache-  | +SPM and Shared Data Support Evaluations                             | 56 |

|   |     | 2.8.1   | Experiment 1: Coherence Overhead Due to False Sharing                | 57 |

|   |     | 2.8.2   | Experiment 2: Coherence Overhead Due to Shared Data                  | 58 |

|   |     | 2.8.3   | Experiment 3: Dynamic Partitioning of Local Memory                   | 59 |

|   |     | 2.8.4   | Experiment 4: Sharing SPMs Between Cores                             | 60 |

|   |     |         |                                                                      |    |

| 3 | App | oroxim  | ate On-chip Data Storage                                             | 62 |

|   | 3.1 | Introd  | uction                                                               | 62 |

|   | 3.2 | Prior V | Work on Memory Approximation                                         | 64 |

|   |     | 3.2.1   | Taxonomy of Prior Research on Approximate Memory Management .        | 64 |

|   |     | 3.2.2   | Overview of Prior Research and Practices                             | 69 |

|   | 3.3 | Partia  | lly-Forgetful Memories                                               | 80 |

|   | 3.4 |         | ed Cache                                                             | 82 |

|   |     | 3.4.1   | Introduction                                                         | 82 |

|   |     | 3.4.2   | Motivation                                                           | 84 |

|   |     | 3.4.3   | Hardware Support                                                     | 86 |

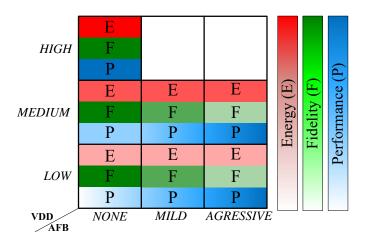

|   |     | 0.2.0   | 3.4.3.1 Tuning Relaxed Ways Based on Architectural Knobs             | 87 |

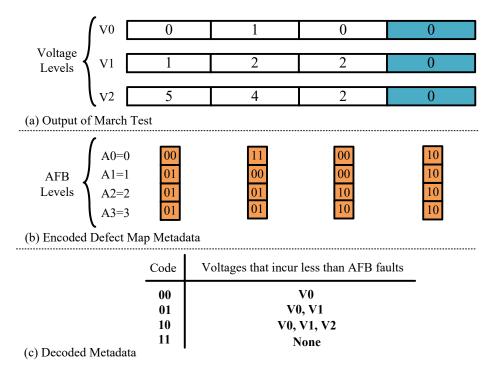

|   |     |         | 3.4.3.2 Defect Map Generation and Storage                            | 88 |

|   |     |         | 3.4.3.3 Non-Criticality Table                                        | 90 |

|   |     |         | 3.4.3.4 Making Cache Controller Aware of Block's Tag                 | 9: |

|   |     | 3.4.4   | Software Support                                                     | 9  |

|   |     | 0.4.4   | porting are purport                                                  | J. |

|     |       | 3.4.4.1 Programmer-Driven Application Modifications  | 91  |

|-----|-------|------------------------------------------------------|-----|

|     |       | 3.4.4.1.1 Data Criticality Declaration               | 91  |

|     |       | 3.4.4.1.2 Cache Configuration                        |     |

|     |       | 3.4.4.2 Runtime System                               |     |

|     | 3.4.5 | Evaluations                                          | 95  |

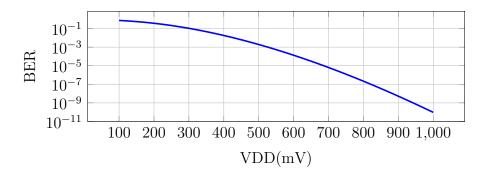

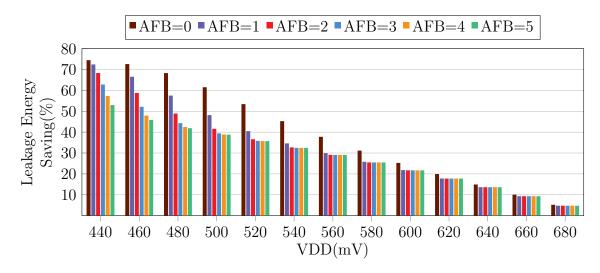

|     |       | 3.4.5.1 Experimental Setup                           |     |

|     |       | 3.4.5.2 Benchmarks                                   |     |

|     |       | 3.4.5.3 Experimental Results                         | 97  |

|     |       | 3.4.5.3.1 Leakage Energy Savings                     |     |

|     |       | 3.4.5.3.2 Fidelity Analysis                          |     |

|     |       | 3.4.5.3.3 Performance Analysis                       |     |

| 3.5 | QuAF  | RK Cache                                             | 101 |

|     | 3.5.1 | Introduction                                         | 101 |

|     | 3.5.2 | STT-MRAM Reliability/Energy Trade-off Knobs          | 103 |

|     |       | 3.5.2.1 STT-MRAM Basics                              | 103 |

|     |       | 3.5.2.2 Reliability-Energy Knobs                     | 104 |

|     | 3.5.3 | The QuARK Approach                                   | 105 |

|     |       | 3.5.3.1 Software Support                             | 106 |

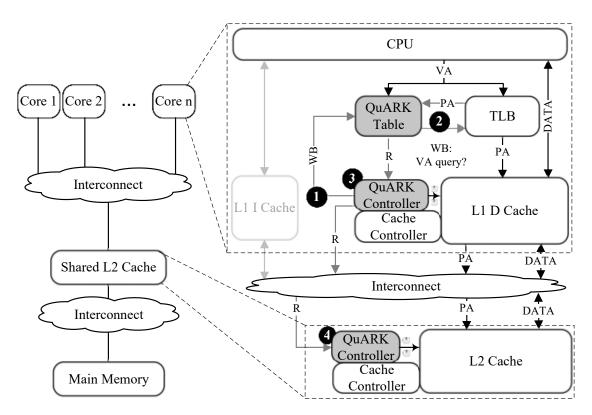

|     |       | 3.5.3.2 Hardware Support                             | 107 |

|     |       | 3.5.3.2.1 QuARK Cache Approximation Table            | 108 |

|     |       | 3.5.3.2.2 QuARK Cache Controller                     | 109 |

|     |       | 3.5.3.2.3 Support for Cache Fillings and Write-backs | 109 |

|     | 3.5.4 | Evaluations                                          | 111 |

|     |       | 3.5.4.1 Experimental Setup                           |     |

|     |       | 3.5.4.2 Benchmarks                                   | 112 |

|     |       | 3.5.4.3 Experimental Results                         |     |

| 3.6 | Write | Skip SPM                                             | 116 |

|     | 3.6.1 | Introduction                                         |     |

|     | 3.6.2 | The Write-Skip Approach                              |     |

|     |       | 3.6.2.1 Read-Before-Write                            |     |

|     |       | 3.6.2.2 Approximate Equality                         |     |

|     | 3.6.3 | Evaluations                                          |     |

|     |       | 3.6.3.1 Approximate Value Locality                   |     |

|     |       | 3.6.3.2 Output Fidelities                            |     |

|     |       | 3.6.3.3 Energy Consumption in On-chip Memory         |     |

| 3.7 |       | rolled Memory Approximation                          |     |

|     | 3.7.1 | Introduction                                         |     |

|     | 3.7.2 | Problem Modeling                                     |     |

|     |       | 3.7.2.1 Application Class                            |     |

|     |       | 3.7.2.2 Monitoring Quality at Runtime                |     |

|     |       | 3.7.2.3 Memory Approximation Knob(s)                 |     |

|     | 3.7.3 | Quality Control with Feedback Control Theory         |     |

|     | 3.7.4 | Case Study: Video Edge Detection                     |     |

|     |       | 3.7.4.1 Application Description and Error Metric     |     |

|     |       | 3.7.4.2 Memory Approximation Knob                    | 129 |

|         | 3.7.5  | System 1    | Identification            | . 129 |

|---------|--------|-------------|---------------------------|-------|

|         |        | 3.7.5.1     | Controller                | . 131 |

|         |        | 3.7.5.2     | Fault Injection Mechanism | . 132 |

|         |        | 3.7.5.3     | Input Dependency          | . 133 |

|         |        | 3.7.5.4     | QoS Tracking              | . 133 |

|         |        | 3.7.5.5     | Comparison                | . 133 |

| 4 Con   | clusio | ns and F    | Suture Directions         | 137   |

| 4.1     | Techni | ical Contr  | ributions                 | . 137 |

| 4.2     | Future | e Direction | ns                        | . 138 |

| Bibliog | graphy |             |                           | 140   |

# LIST OF FIGURES

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

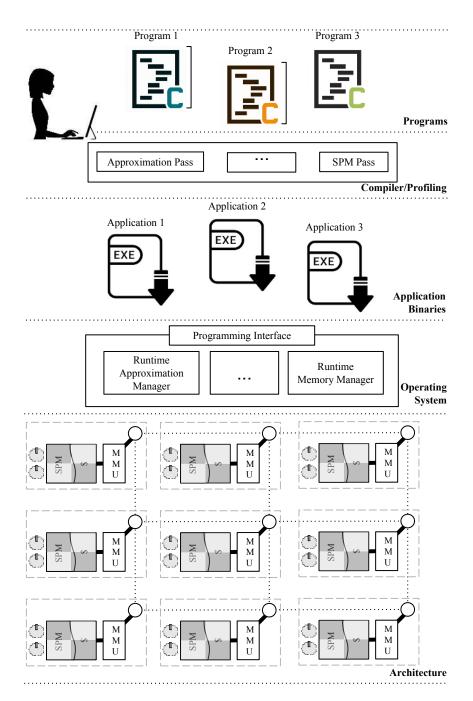

| 1.1  | High-level overeview of the proposed software assisted memory hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8        |

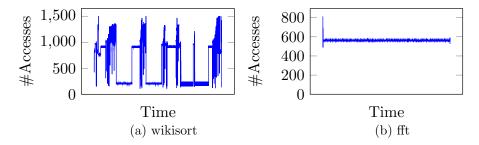

| 2.1  | Number of memory accesses measured periodically for the execution of the wikisort and fft benchmarks: utilization of memory resources changes within a thread and between threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12       |

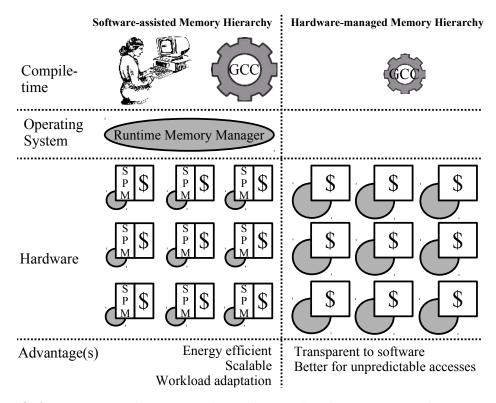

| 2.2  | Software-assisted memory hierarchy vs. hardware-managed memory hierarchy. Relative size of gray components shows their contribution in managing memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.0      |

| 2.2  | hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13       |

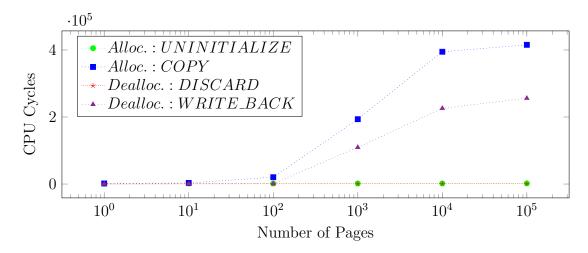

| 2.3  | Number of CPU cycles that a thread has to be stalled for an SPM API to be handled by the OS/HW. SPM page size is assumed to be 64 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19       |

| 2.4  | A code snippet using SPM APIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19       |

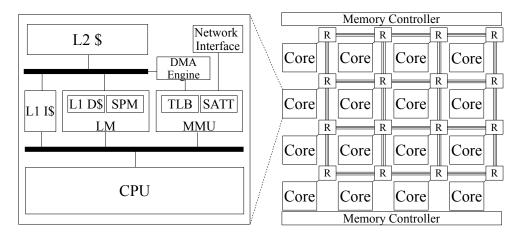

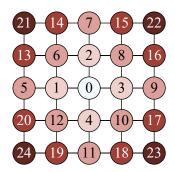

| 2.5  | A 4X4 example of target manycore architecture with software-assisted memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

|      | hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20       |

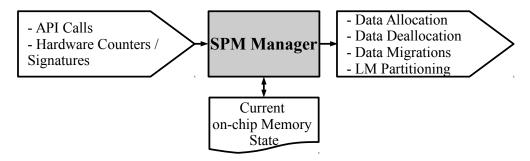

| 2.6  | SPM manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23       |

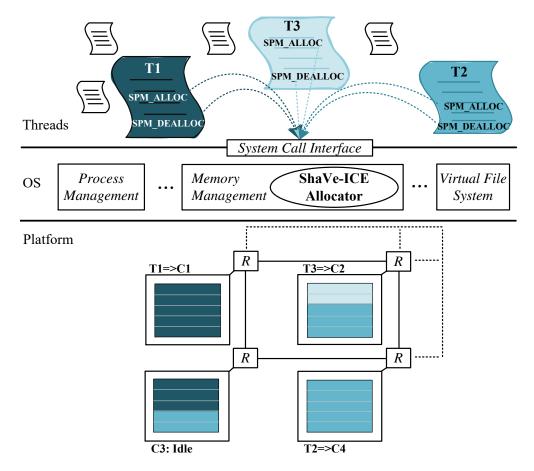

| 2.7  | ShaVe-ICE allocator is invoked when a thread Ti mapped on core Cj calls any of the SPM APIs. It virtualizes and ultimately shares the entire distributed SPM space between all the concurrently running threads. Dedicated hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

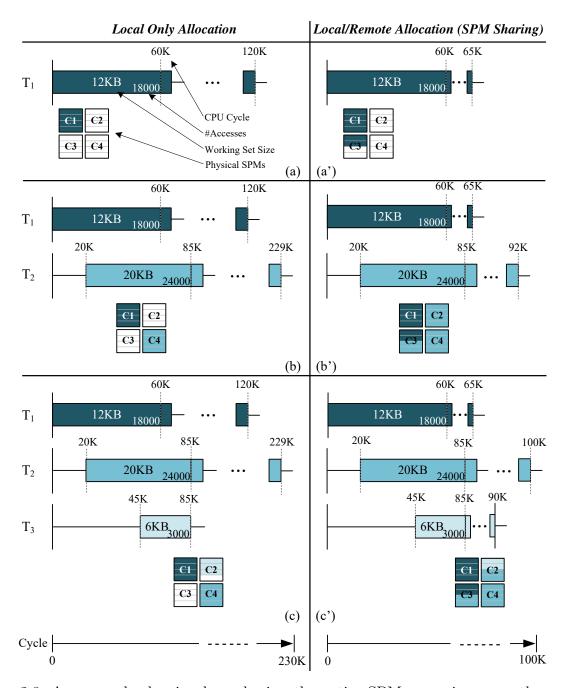

| 2.8  | assist enables remote allocations and remote memory accesses An example showing how sharing the entire SPM space improves the overall performance of a 2X2 system with 3 thread running on it. The left-hand side column shows the state of SPM allocations when allocations are limited to the local SPM only; and right-hand side column shows the same scenario when remote allocations are also possible in addition to local allocations. (a)&(a'): only thread T1 is running, (b)&(b'): thread T2 starts execution after 20K cycles while T1 is still running, (c)&(c'): thread T3 starts execution after 25K cycles while both T1 and T2 are still running. Average and maximum execution times among all three threads are improved by about 2X and 2.9X | 25       |

| 2.9  | respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26<br>31 |

|      | SATT entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33       |

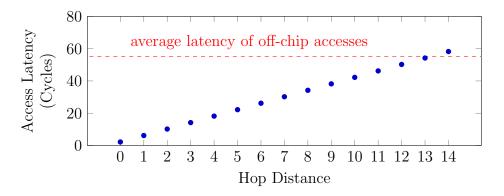

| 2.11 | Average access latency for various hop distances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38       |

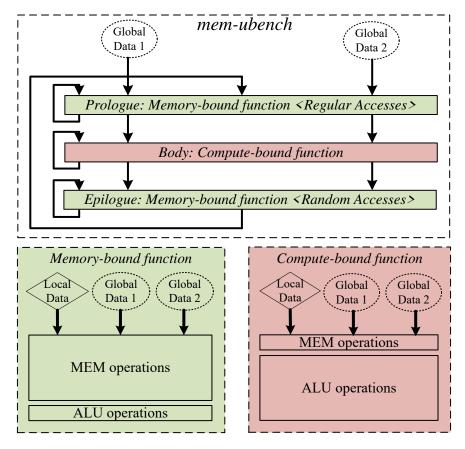

| 2.12 | Overall flow of mem-ubench execution: each phase (prologue, body, epilogue) is either memory or compute intensive to a configurable degree. Operations are |      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | performed on three data arrays of configurable size with both regular (strided)                                                                            |      |

|      | and randomized access patterns. The number of executions of each phase as                                                                                  |      |

|      | well as the entire 3-phase loop are configurable                                                                                                           | 40   |

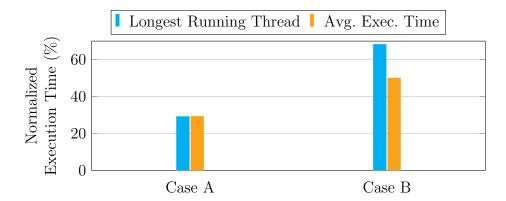

| 2.13 | ShaVe-ICE vs. software cache – Case A: thread's working-set is smaller than                                                                                |      |

|      | software cache and SPM, Case B: thread's working-set is larger than software                                                                               |      |

|      | cache and SPM. Lower values are better                                                                                                                     | 42   |

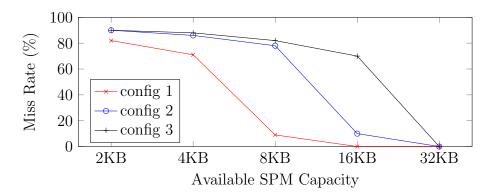

| 2.14 | Miss rate of various mem-ubench configurations for different available SPM                                                                                 |      |

|      | capacities. Miss rate does not have a linear relationship with SPM capacity                                                                                |      |

|      | since not all the data is of the same importance                                                                                                           | 43   |

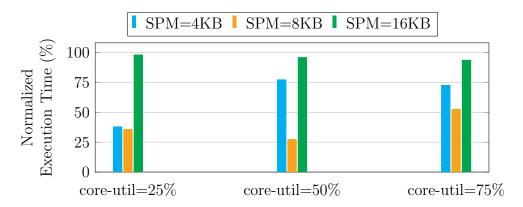

| 2.15 | Scenario 1: Average execution time among all threads in an 8x8 system - RRA                                                                                |      |

|      | normalized to LA. Core underutilization provides the opportunity to RRA to                                                                                 |      |

|      | allocate more SPM space for the threads that have large working set size                                                                                   | 45   |

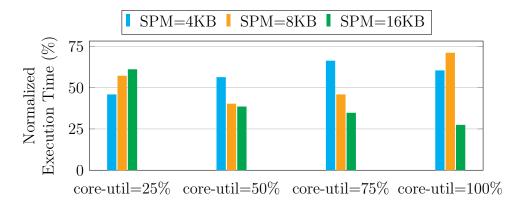

| 2.16 | Scenario 2: Average execution time among all threads in an 8x8 system - RRA                                                                                |      |

|      | normalized to LA: Threads with small working set size provide the opportunity                                                                              |      |

|      | to RRA to utilize the SPM space unused by the locally-pinned thread in order                                                                               |      |

|      | to allocate more SPM space for the threads that have large working set size.                                                                               | 46   |

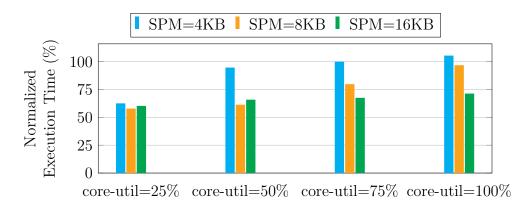

| 2.17 | Scenario 3: Average execution time among all threads in an 8x8 system -                                                                                    |      |

|      | CNA normalized to RRA: CNA allocates remote pages as close as possible to                                                                                  |      |

|      | the owner core resulting in reduced network traffic, faster access latency and                                                                             |      |

|      | ultimately better overall performance compared to RRA                                                                                                      | 48   |

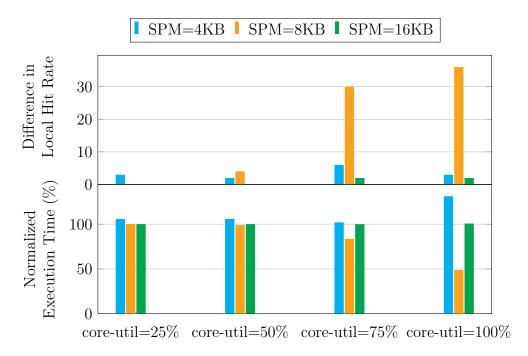

| 2.18 | Scenario 4: Difference in the local hit ratio - CNGLSA-CNA and average                                                                                     |      |

|      | execution time among all threads in an 8x8 system - CNGLSA normalized                                                                                      |      |

|      | to CNA: CNGLSA returns the remotely allocated SPM space to the                                                                                             |      |

|      | locally-pinned thread should that thread needs it. In some cases, this results                                                                             |      |

|      | in improved local hit ratio and decreased average memory access latency                                                                                    |      |

|      | compared to CNA                                                                                                                                            | 49   |

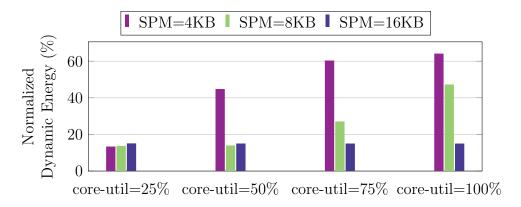

|      | Dynamic energy in memory subsystem and network: CNA normalized to LA.                                                                                      | 50   |

| 2.20 | Dynamic energy in memory subsystem and network: CNGLSA normalized to                                                                                       |      |

|      | CNA                                                                                                                                                        | 50   |

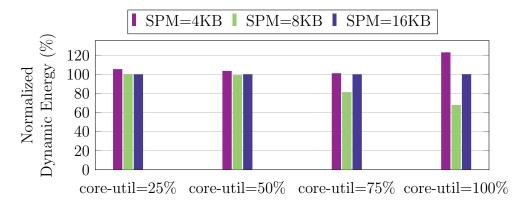

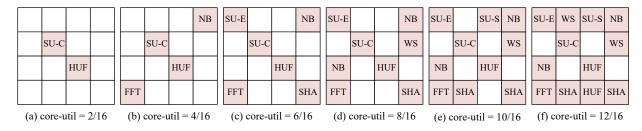

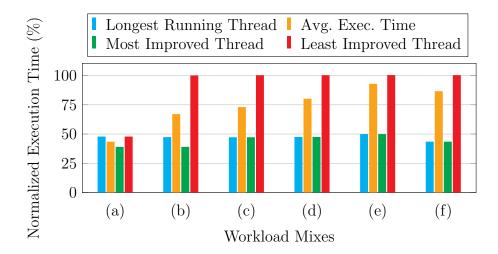

|      | Workload mixes with various core utilizations in a 4X4 platform                                                                                            | 52   |

| 2.22 | Execution time comparison for various workload mixes as shown in Figure 2.21:                                                                              | ۲.   |

| 0.00 | CNGLSA normalized to LA. Lower values are better.                                                                                                          | 53   |

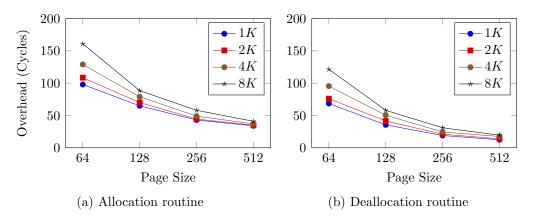

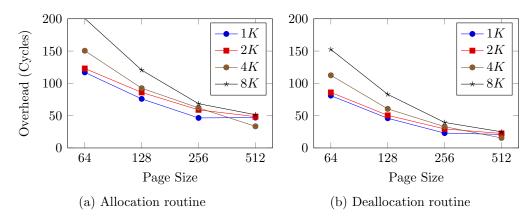

| 2.23 | Runtime overhead of SPM allocator for different combinations of allocation                                                                                 |      |

| 0.04 | size and page size: local policy (simplest policy)                                                                                                         | 55   |

| 2.24 | Runtime overhead of SPM allocator for different combinations of allocation                                                                                 |      |

|      | size and page size: closest neighborhood with local reservation policy (most                                                                               | T G  |

| 2 25 | complex policy)                                                                                                                                            | 56   |

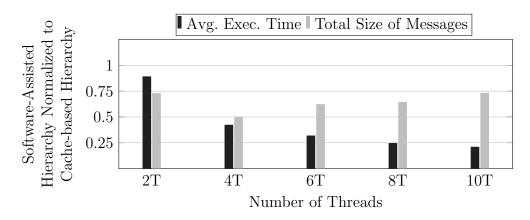

| 2.23 | Comparing software-assisted memory hierarchy with cache-based hierarchy                                                                                    | F 75 |

| 2 26 | implementing MESI protocol when false data sharing exists                                                                                                  | 57   |

| 2.20 | Comparing software-assisted memory hierarchy with cache-based hierarchy                                                                                    | 58   |

| 2 27 | implementing MESI protocol when true data sharing exists                                                                                                   | 96   |

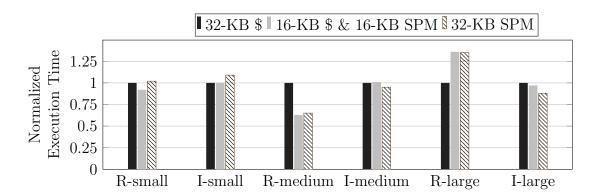

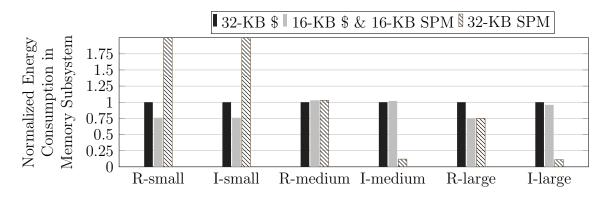

| 4.41 | memory: cache only, SPM and cache, SPM only. Lower is better                                                                                               | 59   |

|      | momory, cache omy, or we and cache, or we only, bower is belief                                                                                            | 00   |

| 2.28            | Comparison of energy consumption with different configurations of a fixed size local memory: cache only, SPM and cache, SPM only. Lower is better                                                                                | 59         |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

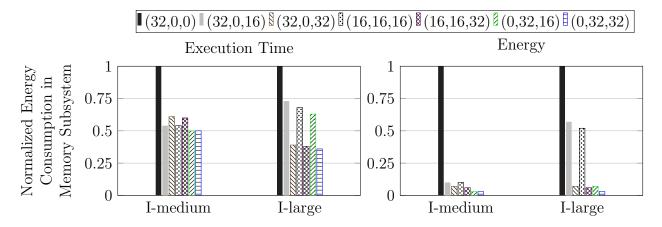

| 2.29            | Comparison of execution time and energy consumption when remote SPMs are available for allocation. Legends are shown as: (local cache, local SPM,                                                                                |            |

|                 | remote SPM at hop distance 1). Lower is better                                                                                                                                                                                   | 60         |

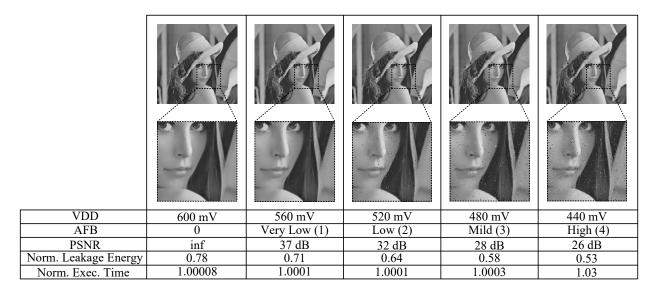

| 3.1             | Exploring performance-energy-fidelity space for Image Smoothing benchmark by adjusting Relaxed Cache controlling knobs (leakage energies and execution times are normalized to a baseline that Uses 700 mV for SRAM array supply |            |

|                 | voltage)                                                                                                                                                                                                                         | 84         |

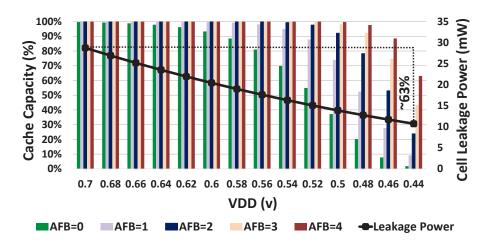

| 3.2             | Trade-off between cache capacity, VDD, AFB and bit-cell leakage power (cache block size=64-byte, technology=45nm)                                                                                                                | 85         |

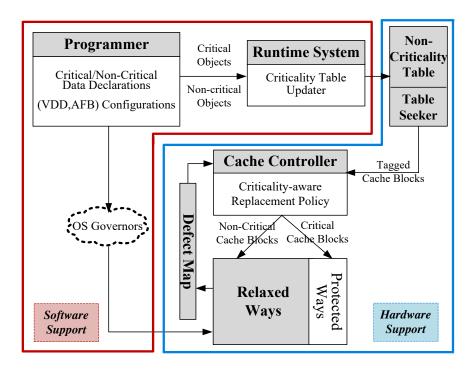

| 3.3             | High-level diagram showing HW/SW components of Relaxed Cache and their                                                                                                                                                           |            |

|                 | interactions                                                                                                                                                                                                                     | 86         |

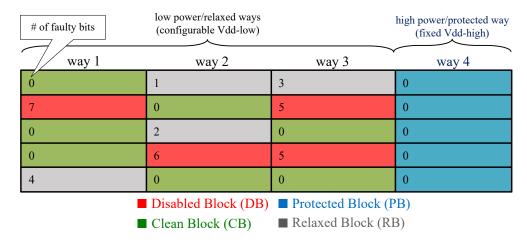

| 3.4             | A Sample 4-way Cache with VDD=580mV and AFB=4                                                                                                                                                                                    | 88         |

| 3.5             | Encoding and decoding defect map info in Relaxed Cache                                                                                                                                                                           | 86         |

| 3.6             | Abstracting Relaxed Cache knobs up to metrics familiar to a software                                                                                                                                                             |            |

|                 | programmer (i.e., performance, fidelity, and energy consumption). Note that                                                                                                                                                      |            |

|                 | (VDD = High, AFB = Mild) and (VDD = High, AFB = Aggressive)                                                                                                                                                                      | 0.6        |

| 2.7             | combinations are sub-optimal, hence not applicable                                                                                                                                                                               | 93         |

| 3.7             | A sample code showing programmer's data criticality declarations and cache                                                                                                                                                       | 0.         |

| 20              | configurations for Relaxed Cache                                                                                                                                                                                                 | 94         |

| 3.8<br>3.9      | SRAM BER for 45nm using models and data from [149] Leakage energy savings for a 4-Way L1 cache with 3 relaxed ways (energy                                                                                                       | 96         |

| 5.9             | savings are normalized to a baseline cache that uses 700mV)                                                                                                                                                                      | 98         |

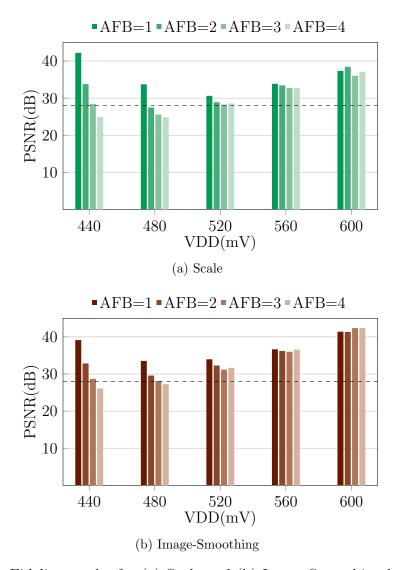

| 3.10            | Fidelity results for (a) Scale and (b) Image-Smoothing benchmarks                                                                                                                                                                | 99         |

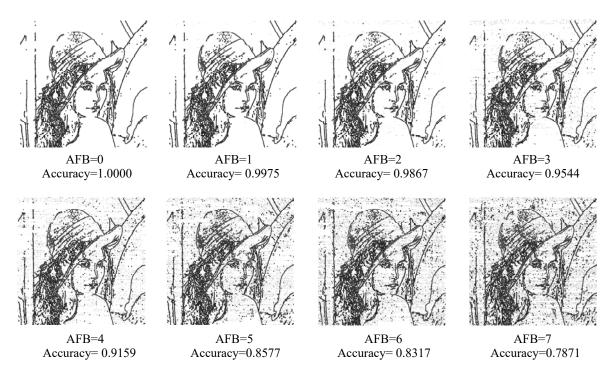

| 3.11            | Fidelity results for Edge-Detection benchmark (VDD=480mV)                                                                                                                                                                        | 100        |

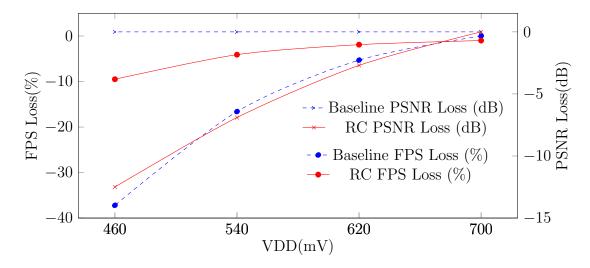

|                 | FPS-PSNR trade-offs with and without Relaxed Cache scheme (AFB=4)                                                                                                                                                                | 10         |

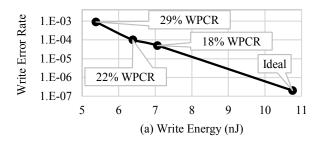

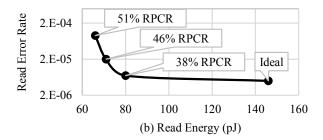

|                 | STT-MRAM knobs for reliability-energy trade-off in 1MB cache. (a) Write Pulse Current Reduction (WPCR), and (b) Read Pulse Current Reduction                                                                                     |            |

|                 | (RPCR)                                                                                                                                                                                                                           | 105        |

| 3.14            | A pseudo-code example showing how QuARK Cache APIs can be used in a                                                                                                                                                              |            |

|                 | face detection application                                                                                                                                                                                                       | 107        |

| 3.15            | Integrating QuARK Cache into the architecture. Required changes are                                                                                                                                                              |            |

|                 | highlighted in gray.                                                                                                                                                                                                             | 108        |

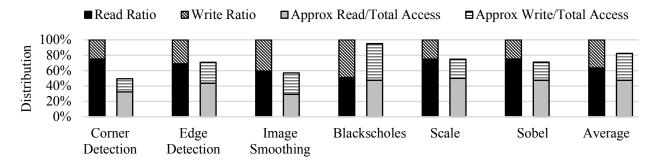

| 3.16            | Distribution of overall and approximation read and write accesses in L2 cache                                                                                                                                                    |            |

| 0.4             | for the selected benchmarks                                                                                                                                                                                                      | 113        |

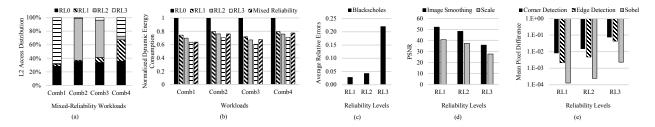

| 3.17            | QuARK Cache evaluation results: (a) Distribution of accesses in                                                                                                                                                                  |            |

|                 | mixed-reliability workloads, (b) Energy savings (normalized to fully-protected                                                                                                                                                   |            |

|                 | STT-MRAM L2 cache), (c) Average relative error for blackscholes benchmark,                                                                                                                                                       |            |

|                 | (d) PSNR for Scale and Image Smoothing benchmarks, and (e) Mean pixel                                                                                                                                                            | 114        |

| 2 10            | difference for Corner Detection, Edge Detection and Sobel benchmarks Percentage of approximately-equal writes in image-smoothing                                                                                                 | 116<br>119 |

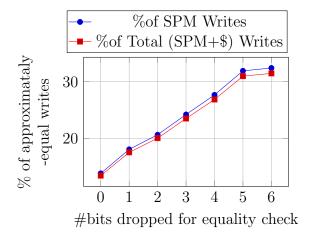

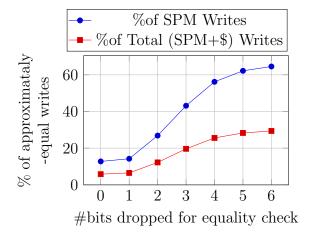

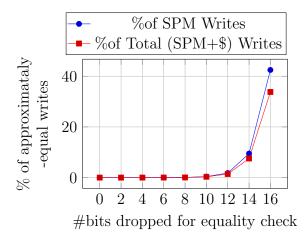

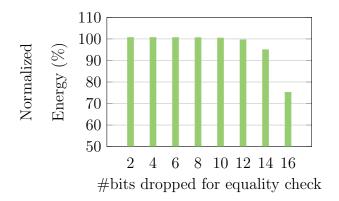

|                 | Percentage of approximately-equal writes in sobel                                                                                                                                                                                | 119        |

|                 | Percentage of approximately-equal writes in k-means                                                                                                                                                                              | 119        |

| $\cup$ . $\cup$ | I OF COLLOWS OF APPEARITMOUTLY CHARLES WITHOUT III IN THICAID.                                                                                                                                                                   | т т с      |

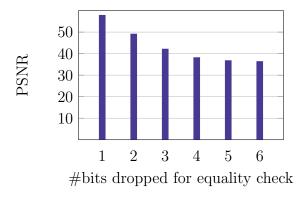

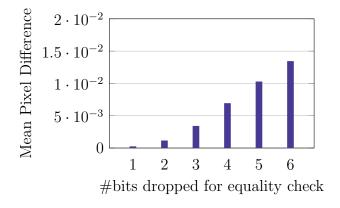

| 3.21 | Output fidelity for image-smoothing                                               | 120  |

|------|-----------------------------------------------------------------------------------|------|

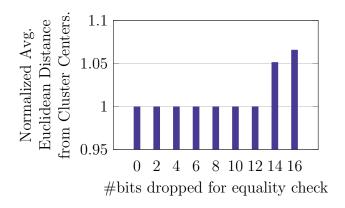

|      | Output fidelity for sobel                                                         | 120  |

|      | Output fidelity for k-means                                                       | 121  |

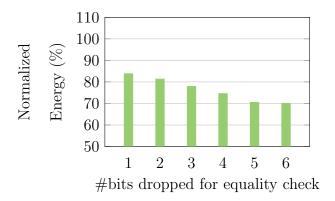

| 3.24 | Energy consumption in on-chip memory for image-smoothing normalized to            |      |

|      | the baseline where none of the write operations are skipped                       | 122  |

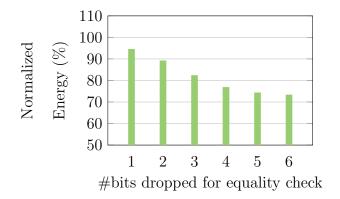

| 3.25 | Energy consumption in on-chip memory for sobel normalized to the baseline         |      |

|      | where none of the write operations are skipped                                    | 122  |

| 3.26 | Energy consumption in on-chip memory for k-means normalized to the baseline       |      |

|      | where none of the write operations are skipped                                    | 122  |

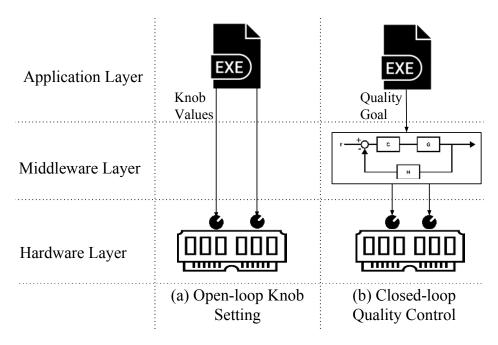

| 3.27 | Open-loop knob settings (prior works) vs. closed-loop quality control (this work) | .123 |

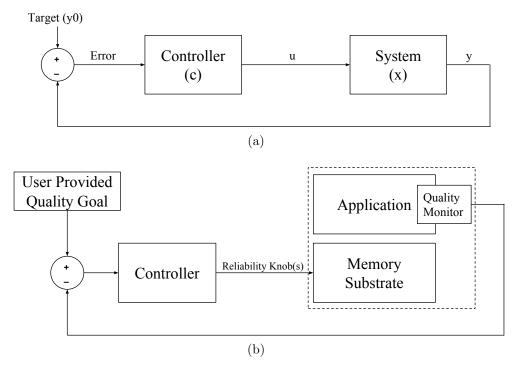

| 3.28 | Closed loop approach (this work) for tuning memory approximation knob(s).         | 128  |

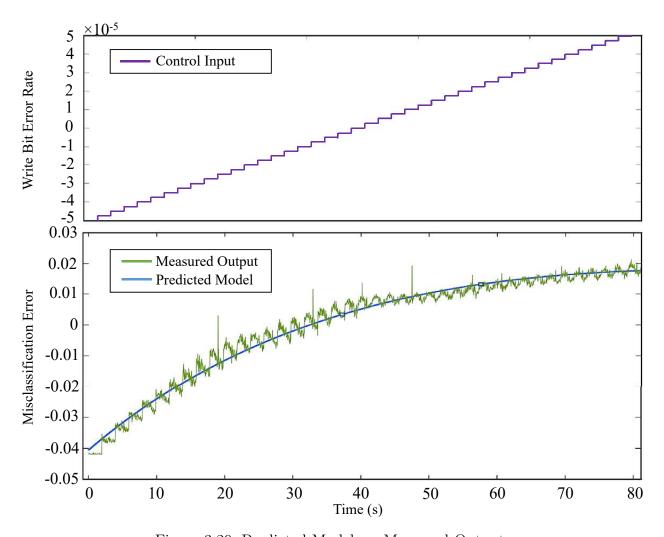

| 3.29 | Predicted Model vs. Measured Output                                               | 131  |

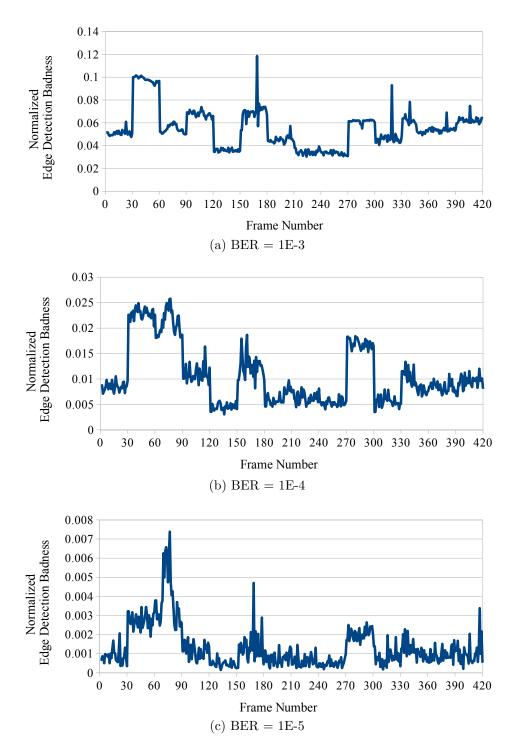

| 3.30 | Variation of the quality of the edge detection in various video scenes when the   |      |

|      | bit error rate is constant                                                        | 134  |

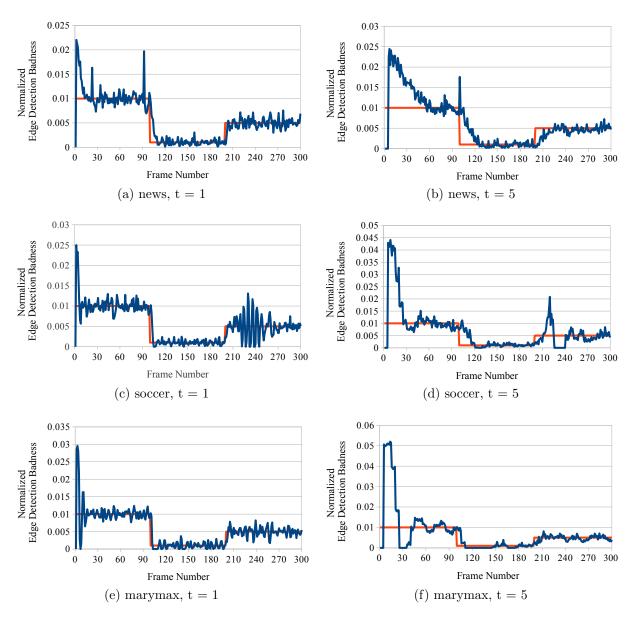

| 3.31 | Quality tracking results. Red curve shows the acceptable error and the blue       |      |

|      | curve shows the error achieved by the controller                                  | 135  |

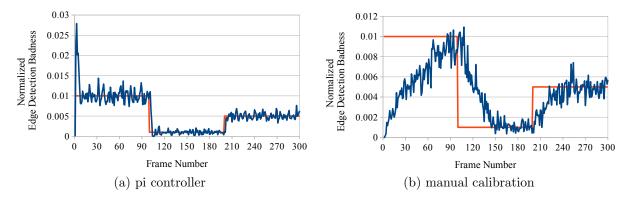

| 3.32 | Comparing PI controller with manual step-wise re-calibration similar to [16].     | 136  |

| 3.33 | Canny edge detection applied to different images with various write bit error     |      |

|      | rates resulting in different quality metrics                                      | 136  |

## LIST OF TABLES

|      |                                                                                                 | Page |

|------|-------------------------------------------------------------------------------------------------|------|

| 1.1  | ITRS mobile devices trend [71]                                                                  | 3    |

| 2.1  | ShaVe-ICE APIs                                                                                  | 17   |

| 2.2  | Details of threads in the motivational example of Figure 2.8                                    | 25   |

| 2.3  | SPM-related network messages in ShaVe-ICE                                                       | 34   |

| 2.4  | List of benchmarks for ShaVe-ICE experiments                                                    | 51   |

| 2.5  | List of microbenchmarks                                                                         | 56   |

| 3.1  | Prior research In approximate memory management classified based on abstraction levels involved | 65   |

| 3.2  | Prior research In approximate memory management classified based on approximation objective     | 66   |

| 3.3  | Prior research In approximate memory management classified based on the memory component        | 67   |

| 3.4  | Prior research In approximate memory management classified based on the memory technology       | 67   |

| 3.5  | Prior research In approximate memory management classified based on the approximation strategy  | 68   |

| 3.6  | A sample criticality table for Relaxed Cache                                                    | 90   |

| 3.7  | gem5 settings for Relaxed Cache experiments                                                     | 96   |

| 3.8  | Relation between PSNR and perceptual quality in image processing domain .                       | 97   |

| 3.9  | QuARK Cache APIs                                                                                | 106  |

| 3.10 | · ·                                                                                             | 111  |

|      | Accuracy-energy transducer map for 1MB QuARK Cache-enabled                                      |      |

|      | STT-MRAM cache. Energy consumptions are reported for a 64-byte                                  |      |

|      | cache line                                                                                      | 112  |

| 3.12 | List of approximate applications for QuARK Cache experiments                                    | 112  |

| 3.13 | List of workload mixes for QuARK Cache experiments                                              | 113  |

| 3.14 | List of approximate applications for Write-Skip experiments                                     | 118  |

### ACKNOWLEDGMENTS

I would like to express my utmost gratitude to my adviser, Professor Nikil Dutt. His mentorship has helped me grow as a person and learn the necessary social skills to grow as a successful individual in the society. I thank him for having faith in me, through my initial struggles, and standing by me in my times of need.

I would like to thank the rest of my dissertation committee members Professor Alex Nicolau and Professor Eli Bozorgzadeh for their time, support and invaluable advice.

I thank my friends and colleagues at UCI, who made a great impact on my life. In particular, I thank Dr Hossein Tajik, Dr Abbas Banaiyan, Bryan Donyanavard, Hamid Nejatollahi, Sajjad Taheri, Dr Jurngyu Park, Dr Amir Rahmani, Tiago Muck, Roger Hsieh, Kasra Moazzami, Dr Luis (Danny) Bathen, Santanu Sarma, Hirak Kashyap, Amir Mahdi Hosseini Monazzah, Maral Amir, Zhi Chen and Dr Nga Dang for their friendship, feedback, guidance, and collaborations.

I thank Dr Abbas Rahimi for mentoring me at the initial stages of my PhD.

I must thank my dear friends Amirali Ghofrani, Farshad Yazdi, Morteza Kayyalha, Aida Ebrahimi, Mehrdad Biglarbegian, and Somayeh Sadeghi for their support and the good memories we have created together.

I would like to thank UC Irvine graduate division, NSF Variability Expedition (Grant Number CCF-1029783) and the school of ICS for providing funding opportunities during my PhD program.

I am also very grateful to Professor Alex Nicolau who provided me with many teaching opportunities and mentored me to be a better instructor.

I thank Melanie Sanders, Holly Byrnes, Kris Bolcer, Grace Wu and Melanie Kilian for making ICS and CECS such enjoyable places to work and for all their help and advice on so many different subjects.

I also thank ACM and IEEE for permissions to include parts of chapters 2 and 3 of my dissertation, which were originally published in IEEE Embedded System Letters, ACM Transaction on Embedded Computing Systems, ACM/IEEE International Symposium on Low Power Electronics and Design.

I am deeply thankful to my family for their love, continued support, and sacrifices; especially my brother Omid for setting high bars for educational and intellectual achievement.

### **CURRICULUM VITAE**

## Majid Namaki Shoushtari

#### **EDUCATION**

Doctor of Philosophy in Computer Science2018University Of California, IrvineIrvine, CAMaster of Science in Computer Engineering2012University Of TehranTehran, IranBachelor of Science in Computer Engineering2009University Of TehranTehran, Iran

#### RESEARCH EXPERIENCE

Graduate Student Researcher2012–2017University of California, IrvineIrvine, CaliforniaGraduate Research Assistant2009–2012University Of TehranTehran, Iran

#### TEACHING EXPERIENCE

Teaching Assistant2014–2018University of California, IrvineIrvine, CATeaching Assistant2009–2012University of TehranTehran, Iran

#### WORK EXPERIENCE

Software Engineering Intern

NVIDIA Corp.

Software Engineering Intern

Rambus Inc.

Software Engineering Intern

Rambus Inc.

Sunnyvale, CA

Sunnyvale, CA

Sunnyvale, CA

Light Sept. 2015

Sunnyvale, CA

Sunnyvale, CA

Karaj, Iran

| REFEREED JOURNAL PUBLICATIONS                                                                                                                                     |                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Exploiting Partially-Forgetful Memories for Approximate Computing IEEE Embedded Systems Letters                                                                   | 2015             |

| Automatic Management of Software Programmable<br>Memories in Many-core Architectures<br>IET Computers & Digital Techniques                                        | 2016             |

| SAM: Software-Assisted Memory Hierarchy for Scalable<br>Manycore Embedded Systems<br>IEEE Embedded Systems Letters                                                | 2017             |

| ShaVe-ICE: Sharing Distributed Virtualized SPMs In Many-Core Embedded Systems ACM Transactions on Embedded Computing Systems                                      | 2018             |

| REFEREED CONFERENCE PUBLICATIONS                                                                                                                                  |                  |

| ARGO: Aging-aware GPGPU Register File Allocation International Conference on Hardware/Software Codesign and System Synthe (CODES+ISSS)                            | <b>2013</b> esis |

| Multi-layer Memory Resiliency Design Automation Conference (DAC)                                                                                                  | 2014             |

| Cross-layer Virtual/physical Sensing and Actuation for<br>Resilient Heterogeneous Many-core SoCs<br>Asia and South Pacific Design Automation Conference (ASP-DAC) | 2016             |

xiv

Cache by Fine-grained Tuning of

International Symposium on Low Power Electronics and Design (ISLPED)

Approximate

2017

Quality-configurable

QuARK:

STT-MRAM

Reliability-Energy Knobs

#### TECHNICAL REPORTS

A Survey of Techniques for Approximate Memory Sept. 2017 Management

UC Irvine, Center for Embedded and Cyber-physical Systems, CECS TR 17-03

SPM-vSharE: Memory Management in SPM-based Nov. 2016 Many-core Embedded Systems

UC Irvine, Center for Embedded and Cyber-physical Systems, CECS TR 16-08

Relaxing Manufacturing Guard-bands in Memories for Aug. 2014 Energy Saving

UC Irvine, Center for Embedded and Cyber-physical Systems, CECS TR 14-04

#### **SOFTWARE**

pin-memapprox https://github.com/mjshoushtari/pin-memapprox A PIN-based fault injector tool to simulate annotated approximate programs.

## ABSTRACT OF THE DISSERTATION

Software Assists to On-chip Memory Hierarchy of Manycore Embedded Systems

By

Majid Namaki Shoushtari

Doctor of Philosophy in Computer Science

University of California, Irvine, 2018

Professor Nikil Dutt, Chair

The growing computing demands of emerging application domains such as Recognition/Mining/Synthesis (RMS), visual computing, wearable devices and the Internet of Things (IoT) has driven the move towards manycore architectures to better manage tradeoffs among performance, energy efficiency, and reliability.

The memory hierarchy of manycore architectures has a major impact on their overall performance, energy efficiency and reliability. We identify three major problems that make traditional memory hierarchies unattractive for manycore architectures and their data-intensive workloads: (1) they are power hungry and not a good fit for manycores in face of dark silicon, (2) they are not adaptable to the workload's requirements and memory behavior, and (3) they are not scalable due to coherence overheads.

This thesis argues that many of these inefficiencies are the result of software-agnostic hardware-managed memory hierarchies. Application semantics and behavior captured in software can be exploited to more efficiently manage the memory hierarchy. This thesis exploits some of this information and proposes a number of techniques to mitigate the aforementioned inefficiencies in two broad contexts: (1) explicit management of hybrid cache-SPM memory hierarchies, and (2) exploiting approximate computing for energy efficiency.

We first present the required hardware and software support for a software-assisted memory hierarchy that is composed of distributed memories which can be partitioned between caches and software-programmable memories (SPMs) at runtime. This memory hierarchy supports local and remote allocations and data movements between SPM and cache and also between two physical SPMs. The distributed SPM space is shared between a mix of threads where each thread explicitly requests SPM space throughout its execution. The runtime component of this hierarchy shares the entire distributed SPM space between contending threads based on an allocation policy. Unlike traditional memory hierarchies, we incorporate no coherence logic in this hierarchy. The program explicitly allocates the shared data on the distributed SPM space. For all threads of that program, the accesses to shared data are forwarded to the same physical copy.

Next, we augment caches and SPMs in this hierarchy with approximation support in order to improve the energy efficiency of the memory subsystem when running approximate programs. We present approximation techniques for major building blocks of our hybrid cache-SPM memory hierarchy. We introduce Relaxed Cache as an approximate private L1 SRAM cache where the quality, capacity, and energy consumption of this cache are controlled through two architectural knobs (i.e., voltage and the number of acceptable faulty bits per cache block). We then present QuARK Cache, an approximate shared L2 STT-MRAM cache. The read and write current amplitude provide two knobs to make a tradeoff between the accuracy of memory operations and the dynamic energy consumption. We then introduce Write-Skip, a technique that skips write operations in STT-MRAM data SPMs if the previous value and the new value are approximately equal. Finally, we discuss a quality-configurable memory approximation strategy using formal control theory that adjusts the level of approximation at runtime depending on the desired quality for the program's output.

We implemented all software and hardware components of the proposed software-assisted memory hierarchy in the gem5 architectural simulator. Our simulations on a mix of RMS and microbenchmarks show that our proposed techniques achieve better performance, energy, and scalability for manycore systems over traditional hardware-managed memory hierarchies.

# Chapter 1

# Introduction

# 1.1 Technology Implications

## 1.1.1 Emerging Manycore Architectures

Up to early 2000s, the principal approach to improve the performance of processors was to simply scale down the manufacturing technology, add more transistor and increase the clock frequency. This was being fueled by the Moore's law and Dennard Scaling. This was the trend for from 1980s to 2000s until the processors started hitting physical limitations in terms of their clock frequency and how effectively they could be cooled and still maintain accuracy.

Essentially, three primary factors led to the design of multicore processor:

- 1. The memory wall: the increasing gap between processor and memory speeds. This, in effect, pushes for cache sizes to be larger in order to mask the latency of memory. This helps only to the extent that memory bandwidth is not the bottleneck in performance.

- 2. The instruction-level parallelism (ILP) wall: the increasing difficulty of finding enough

parallelism in a single instruction stream to keep a high-performance single-core processor busy.

3. The power wall: the trend of consuming exponentially increasing power with each factorial increase of operating frequency. The power wall poses manufacturing, system design and deployment problems that have not been justified in the face of the diminished gains in performance due to the memory wall and ILP wall.

Multicores usually use a bus-based communication infrastructures, which may not scale beyond dozens of cores. As opposed to multicores, a manycore architecture consists of a network-like interconnect, and hundreds or even thousands of processing cores with their own local memories (SRAM/non-volatile caches and scratchpad memories). At the heart of these systems is the network-like communication infrastructure, which has been designed to scale well beyond the dozens of cores. Multicore processors, are usually designed to efficiently run both parallel and serial code, and therefore place more emphasis on high single thread performance (e.g., devoting more silicon to out of order execution, deeper pipelines, more superscalar execution units, and larger, more general caches), and shared memory. Manycore processors are distinct from multicore processors in that: they are optimized from the outset for a higher degree of explicit parallelism, and for higher throughput (or lower power consumption) at the expense of latency and lower single thread performance.

The manycore revolution is also driven by the demand from new softwares such as media rich applications (e.g., streaming content from the cloud), resulting in complex software stacks that require new ways to improve system performance to cope with the increasingly complex software stacks.

Examples of such manycore architectures are Intel SCC [100], Kalray MPPA-256 [44], Tilera TILE64 [27], Adapteva Epiphany [4], Kalray MPPA2-256 [75], IBM Blue Gene/Q [65].

Although manycore architectures have not been deployed yet for widespread use, one clear

trend exists in the mobile computing domain. In recent years, mobile devices, notably smartphones, have shown significant expansion of computing capabilities. ITRS [71] predicts that the number of cores for Application Processors (AP) will moderately increase by 4x in the time horizon. On the other hand, the number of cores in Graphics Processing Units (GPU) will increase by 50x in this time horizon. This increase in GPU processing capacity is necessary to keep up with the increasingly growing number of megapixel offered by the displays. It is expected that the traffic between AP and memory will have to correspondingly increase more than 2x.

Table 1.1: ITRS mobile devices trend [71]

| Year                                       | 2015 | 2017 | 2019 | 2021 | 2023 | 2025 |

|--------------------------------------------|------|------|------|------|------|------|

| Number of AP cores                         | 4    | 9    | 18   | 18   | 28   | 36   |

| Number of GPU cores                        | 6    | 19   | 49   | 69   | 141  | 247  |

| Number of GPU cores Max frequency          | 2.7  | 2.9  | 3.2  | 3.4  | 3.7  | 1    |

| of any Component in System (GHz)           | 2.1  | 2.9  | 3.2  | 3.4  | 3.1  | 4    |

| Number of Mega pixels in Display           | 2.1  | 2.1  | 3.7  | 8.8  | 8.8  | 33.2 |

| Number of Mega pixels in Display Bandwidth | 25.6 | 34.8 | 52.6 | 57.3 | 61.9 | 61.9 |

| between AP and Main memory (Gb/s)          | 25.0 | 34.8 | 52.0 | 31.3 | 01.9 | 01.9 |

Manycore technology has been viewed as a way to improve performance at the processor level, but its profound implications on the energy efficiency and reliability of future embedded systems with 100s or 1000s of cores has not been studied in depth. Facing the challenges brought by dark silicon [50], it is more important than ever to deploy energy-efficient mechanisms to continue supporting the growing high performance requirements of future embedded systems.

## 1.1.2 Memory Subsystem of Manycores

The advent of manycore computing platforms exacerbates the classical processor-memory performance bottleneck. As we scale to manycore systems, it becomes increasingly challenging to scale the traditional cache-based memory hierarchies [125]. One important reason is because the overhead of coherence logic increases rapidly with the number of cores. As we scale the

number of cores on a cache coherent system, "cost" in "time and memory" grows to a point beyond which the additional cores are not useful in a single parallel program. This is called Coherency Wall. Some processors have already tried to alleviate this problem by removing hardware cache coherence from processors either partially or completely, e.g. Intel SCC [100], Kalray MPPA-256 [44]. In these architectures, the coherence – whenever needed by the application/system – must be implemented in software. However in these systems, caching – without coherence – is still implemented in hardware. The fact that hardware caching in manycore architectures becomes power-hungry due to the complexity of caching logic is another challenge hardware implemented caches are facing in scaling to manycore architectures.

An alternative mechanism is to deploy software caching mechanisms for smart data management, using the raw memories in the processor. Here the data movement between the close-to-processor memory and the main memory has to be done explicitly in software, typically done through the use of Direct Memory Access (DMA) instructions. We refer to the raw memories in such processors as Software Programmable Memories (SPM). IBM Cell [69], Tilera TILE64 [27], Adapteva Epiphany [4] use SPMs in their on-chip memory hierarchy.

SPMs offer many advantages over caches. When application designers have deep understanding of the data requirements of their applications – especially in embedded systems – the use of SPMs allows developers to exploit application semantics effectively to achieve efficient execution. SPMs offer many other advantages over caches. The first is power efficiency by eliminating the hardware overhead of traditional caching. The second is predictability, a critical factor for real-time systems. Third, there is potential for performance improvement by orchestrating the management of data transfers explicitly in software.

The need for more energy efficient memories and denser memory space to accommodate for emerging data-intensive applications in the embedded domain has led designers to design Non-Volatile Memories (NVMs) as alternatives to SRAM for on-chip memories. Typically, NVMs (e.g., Spin-Transfer Torque (STT) Memories, Phase-Change Memory (PCM)) offer high densities, low leakage power, comparable read latencies and dynamic read power with respect to traditional embedded memories (SRAM/eDRAM). One major drawback across NVMs is the expensive write operation (high latencies and dynamic energy per access) and wearout constraints overtime.

One of the potential benefits of using SPMs is the ability to explicitly manage data accesses for thermal and wearout constraints, particularly for NVMs.

## 1.2 Workload Implications

# 1.2.1 Data-intensive Workloads and Variation in their Memory Requirements

One of the most critical challenges for today's and future data-intensive and big-data problems (ranging from economics and business activities to public administration, from national security to many scientific research areas) is data storage and analysis. The primary goal is to increase the understanding of processes by extracting highly useful values hidden in the huge volumes of data. The increase of the data size has already surpassed the capabilities of today's computation architectures which suffer from the limited bandwidth, due to communication and memory-access bottlenecks.

Data-centric nature of several emerging media-rich applications in the embedded domain creates demand for denser memories. Memories are likely to dominate energy as well as reliability concerns [112] for computing systems.

While memory resources are becoming more vital to embedded computing platforms, because of the nature of the emerging applications running on them, their importance could vary over time and at a time between concurrently running applications. Tajik et al. [143, 142] have shown the variation in memory requirements between concurrently running threads and within a thread during its course of execution.

#### 1.2.2 Error-Resilient Workloads

Inherent application resilience is the property of an application to produce acceptable outputs despite some of its underlying computations being incorrect or approximate. It is prevalent in a broad spectrum of applications such as digital signal processing, image, audio, and video processing, graphics, wireless communications, web search, and data analytics. Emerging application domains such as Recognition, Mining and Synthesis (RMS) [49], which are expected to drive future computing platforms, also exhibit this property in abundance. The inherent resilience of these applications can be attributed to several factors: (1) significant redundancy is present in large, real-world data sets that they process, (2) they employ computation patterns (such as statistical aggregation and iterative refinement) that intrinsically attenuate or correct errors due to approximations, and (3) a range of outputs are equivalent (i.e., no unique golden output exists), or small deviations in the output cannot be perceived by users.

The distributed memory subsystem is one of the fundamental performance and energy bottlenecks in emerging manycore systems and is likely to dominate energy as well as reliability concerns for those systems. This error resilience can be exploited to build more efficient computing systems, more specifically to improve the energy efficiency of the memory subsystem in emerging manycore architectures.

## 1.3 Thesis Contributions and Organization

Any strategy for memory management of manycores should address a number of challenges: (1) adaptation to the workload with varying memory requirements (in terms of working-set size, access pattern, reliability of accesses) (2) energy efficiency, and (3) scalable coherence management.

This thesis takes the stand that many of these challenges cannot be addressed by today's software-agnostic hardware-managed memory hierarchies. We argue that these challenges could be overcome by using more sophisticated memory hierarchy management techniques that receive some form of software-assist (e.g., information about a program's semantics, memory access patterns, memory phases, etc). Figure 1.1 shows an overview of our contributions in this thesis towards achieving this software assisted memory hierarchy.

Chapter 2 presents a software-assisted memory hierarchy for manycore embedded systems along with the details of its hardware and software support. This hierarchy is composed of distributed memories that can be partitioned between caches and SPMs at runtime. The distributed SPM space is shared between a mix of unknown threads where each thread explicitly requests SPM space for its most accessed data objects throughout its execution. The runtime component of this hierarchy shares the entire SPM space between contending threads based on their requirements and a choice of allocation policy. It also decides about how local memories are partitioned between SPM and cache. Unlike traditional memory hierarchies, we incorporate no coherence logic in this hierarchy. The program explicitly allocates the shared data on the distributed SPM space. For all threads of that program, the accesses to shared data are forwarded to the same physical copy. This memory hierarchy supports local and remote allocations and data movements between SPM and cache and also between two physical SPMs.

Chapter 3 augments caches and SPMs in this hierarchy with approximation support in

Figure 1.1: High-level overeview of the proposed software assisted memory hierarchy.

order to improve the energy efficiency of the memory subsystem. We present approximation techniques for major components of the memory hierarchy introduced in Chapter 2. We introduce Relaxed Cache as an approximate private L1 SRAM cache where the quality, capacity, and energy consumption of this cache are controlled through two architectural

knobs. We then present QuARK Cache, an approximate shared L2 STT-MRAM cache. The read and write current amplitude provide two knobs to to make a tradeoff between the accuracy of memory operations and the dynamic energy consumption. We then introduce Write-skip for STT-MRAM data SPMs. Finally, we discuss a strategy to control the level of memory approximation at runtime depending on the desired output quality.

In Chapter 4 we conclude this thesis and address future directions for this research.

# Chapter 2

# Software-Programmable On-chip

# Memory Hierarchy

## 2.1 Introduction

Future embedded systems are expected to use 10s to 100s of simple processing cores, forming Manycore Embedded System (MES) platforms that hold the promise of increasing performance through parallel execution.

However, these systems cannot rely on traditional approaches for system integration. Most notably: (1) The bus-based communication architecture is not a scalable solution for these systems – adopting Network-on-Chip (NoC) communication allows the system to reach a high level of parallelism and scalability. (2) The traditional cache-based memory hierarchy imposes a huge inefficiency in power consumption, due to the complexity of caching logic, and also in performance, due to the network traffic generated by coherence protocols.

The traditional hardware-managed memory hierarchy needs to be revisited to: (1) address

shortcomings (e.g., coherence overhead) of current techniques when cores are replicated beyond certain numbers, and (2) adapt the memory subsystem to a diverse workload, with variable memory requirements, running on a MES.

Traditionally, cache-coherent memory hierarchies have been the default choice for the memory subsystem of embedded systems, mainly because they hide the memory hierarchy from software and don't require any software intervention. Unfortunately, the overhead of purely hardware-managed memory hierarchy grows very fast as the number of cores increases. This overhead manifests itself in the exacerbated power consumption of the memory subsystem and the cache coherence logic and also the coherence traffic in the NoC. On the other hand, hardware is generally oblivious to the variable requirements of individual threads in a workload. Tuning allocation of memory resources to threads in order to improve the overall performance of the entire workload proves challenging for purely hardware-managed hierarchies.

Software-Programmable Memories (SPM, also known as scratchpad memories) are a promising alternative to hardware-managed caches. For equivalent data capacity, SPMs are around 30% smaller, slightly faster, yet consume about 30% less power than cache [22]. Additionally, no coherence management is required due to their software-programmable nature. However, SPMs require explicit software management. Researchers have previously proposed methods to ease this burden [115, 95, 137, 20, 78, 17].

Most previous efforts have assumed a single thread running on a core with a private SPM in isolation of other threads running concurrently or entering the system at a later time, or they assumed the workload mix is known ahead of time. The shortcomings are twofold:

(1) They do not utilize memory resources that are local to idle cores – these idle memory resources present an opportunity for more efficient use of on-chip memory to boost the overall system efficiency. (2) The variation in the memory intensity level as well as working set size between concurrently running threads in emerging diverse workloads is neglected – this

Figure 2.1: Number of memory accesses measured periodically for the execution of the wikisort and fft benchmarks: utilization of memory resources changes within a thread and between threads.

variation causes on-chip memory resources to be more valuable for some threads over others. The utilization of data memory can vary not only between threads in a workload, but also within a single thread over the course of its execution. Figure 2.1 illustrates the variation in temporal memory access patterns both between and within two different benchmarks.

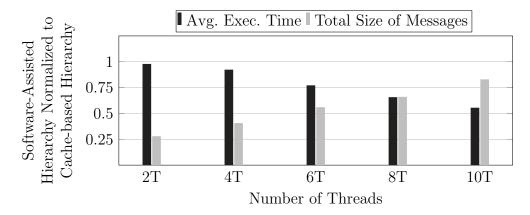

Here we outline an alternative hierarchy organization for MES that employs a Software-Assisted Memory (SAM) hierarchy composed of both cache and SPM guided by static analysis as well as a holistic runtime support. SAM alleviates the aforementioned drawbacks of cache-only hierarchies. Figure 2.2 compares the SAM hierarchy with a purely hardware-managed hierarchy. SAM hierarchy requires less hardware management and relies on the software components of a system (i.e., application, compiler and operating system) to manage memory resources allowing it to be more adaptable to workload's needs and consume less power.