# Postprint

This is the accepted version of a paper published in *IEEE Communications Surveys and Tutorials*. This paper has been peer-reviewed but does not include the final publisher proof-corrections or journal pagination.

Citation for the original published paper (version of record):

Roozbeh, A., Soares, J., Maguire Jr., G Q., Wuhib, F., Padala, C. et al. (2018) Software-Defined "Hardware" Infrastructures: A Survey on Enabling Technologies and Open Research Directions

$\it IEEE\ Communications\ Surveys\ and\ Tutorials,\ 20(3):\ 2454-2485$

https://doi.org/10.1109/COMST.2018.2834731

Access to the published version may require subscription.

N.B. When citing this work, cite the original published paper.

Permanent link to this version:

http://urn.kb.se/resolve?urn=urn:nbn:se:kth:diva-235270

# Software-Defined "Hardware" Infrastructures: A Survey on Enabling Technologies and Open Research Directions

Amir Roozbeh, João Soares, Gerald Q. Maguire Jr., Fetahi Wuhib, Chakri Padala, Mozhgan Mahloo, Daniel Turull, Vinay Yadhav, Dejan Kostić

Abstract— This provides overview of paper an Software-Defined "Hardware" Infrastructures (SDHI). SDHI builds upon the concept of hardware (HW) resource disaggregation. HW resource disaggregation breaks today's physical server-oriented model where the use of a physical resource (e.g., processor or memory) is constrained to a physical server's chassis. SDHI extends the definition of Software-Defined Infrastructures (SDI) and brings greater modularity, flexibility, and extensibility to cloud infrastructures, thus allowing cloud operators to employ resources more efficiently and allowing applications not to be bounded by the physical infrastructure's layout. This paper aims to be an initial introduction to SDHI and its associated technological advancements. The paper starts with an overview of the cloud domain and puts into perspective some of the most prominent efforts in the area. Then, it presents a set of differentiating use-cases that SDHI enables. Next, we state the fundamentals behind SDI and SDHI, and elaborate why SDHI is of great interest today. Moreover, it provides an overview of the functional architecture of a cloud built on SDHI, exploring how the impact of this transformation goes far beyond the cloud infrastructure level in its impact on platforms, execution environments, and applications. Finally, an in-depth assessment is made of the technologies behind SDHI, the impact of these technologies, and the associated challenges and potential future directions of SDHI.

Index Terms—CR-Software-Defined Infrastructure, Resource Disaggregation, Cloud Infrastructure, Rack-scale, Hyperscale Computing, Disaggregated DC

# I. INTRODUCTION

Cloud computing continues to be an emerging field that accelerates digital transformation and innovations in many other technology fields, such as mobile communication [1–7], robotics [8], and Internet of Things (IoT) [9]. Over the years, the information technology (IT) industry has been continuously searching for ways to improve the efficiency of cloud infrastructures (specifically data centers (DCs)), regardless of their size). By improved efficiency we mean, among other aspects, reducing resource wastage and faster infrastructure adaptation. Examples of such improvements are the introduction of server virtualization technologies, such as hypervisor & container technologies [10] and the move towards Software-Defined Infrastructures (SDI). With SDI the entire DC's infrastructure is abstracted, becoming software-defined and dynamically programmable [11].

The abstraction introduced by SDI enabled workloads to be transparently moved within and across cloud infrastructures. For example, this allows applications to quickly scale up/down when they could not do so in the particular infrastructure node where they were initially running. Additionally, these technologies allow infrastructure operators to optimize the infrastructure's efficiency (e.g., reducing resource wastage and energy consumption) and facilitating maintenance (e.g., replacement of servers) by moving workloads around.

In the effort to continue increasing application and infrastructure efficiency, additional approaches, such as microservices [12] and serverless computing [13] have been introduced. Microservices increase modularity by decomposing today's traditional applications into smaller service units, allowing more fine-grained control. In serverless computing, server management and capacity planning aspects are abstracted away and completely hidden from the developer or DC operator. The function-as-a-Service concept [14] is one way to achieve a serverless architecture, while bringing an increased level of granularity and providing more fine-grained control. All of these technologies are primarily based on software mechanisms deployed and running on top of the cloud infrastructure in order to hide and deal with the limitations of this infrastructure.

Current cloud infrastructure architectures build upon a server-oriented model, hence they are constrained by server boundaries and the servers' physical hardware configuration. While SDI and other software approaches continue to improve the efficiency of such infrastructures, industry has realized that to achieve further improvements in efficiency requires changes in some of the today's primary infrastructure principles. This has led to the concept of hardware (HW) resource disaggregation and Software-Defined "Hardware" Infrastructures (SDHI). Here the term "hardware" is used to emphasize the fact that the concept is not simply applying traditional virtualization or other types of software approaches on top of legacy infrastructures.

SDHI requires the cloud infrastructure to be re-architected in fundamental ways. SDHI changes this model by introducing resource disaggregation into the infrastructure. Resource disaggregation breaks the current physical server boundaries and considers physical resources as individual and modular components. These resources are then controlled through software, allowing the composition of a logical server that replaces a motherboard. The resulting logical server interconnects a set of different resources over which an operating system (OS) runs on an interconnected set of resources allocated from pools of resources.

This new approach extends the definition of SDI and brings greater modularity, agility, flexibility, and extensibility of the cloud infrastructure. In SDHI a unified software layer controls the (logical) interconnection between different resources that realize logical server systems. While some of the technologies required for SDHI are already in place today [15], there is still a journey ahead to realize the full potential of SDHI.

The contributions of this paper are numerous. One of the key contributions of this survey is to present a consolidated in-depth study of the enabling technologies and ongoing efforts regarding SDHI. Several ad hoc technological advancements in SDHI have already been made, while others are still ongoing. However, there is no introduction to these in the literature. However, there are technology surveys available that look, individually, into technologies that relate to SDHI, such as virtualization technologies [16] or SDN [17]. This paper aims to be the first introduction to SDHI related technology advancements and existing surveys. Moreover, the paper examines how a shift in hardware and the concept of HW resource disaggregation impacts SDI and the entire cloud architecture, from the HW level up to the application level. Furthermore, the paper discusses previously identified challenges, surveys existing works, and identifies some unforeseen challenges and open research directions. Finally, it provides a set of use-cases that SDHI will unlock. We believe our approach makes this paper a valuable resource for both the research community and practitioners seeking to understand the complexities of SDHI and to help them focus on the key challenges of this concept.

The remainder of this paper is organized as follows. Section II briefly describes traditional cloud infrastructure architectures and elaborates the principle of SDI and its current level of maturity. Moreover, it elaborates the SDHI terminology and discusses the drivers that motivated the realization of SDHI. Section III discusses the market demand for SDHI and describes some of the technical use-case opportunities it will unlock. Section IV examines the key architectural and functional components of a cloud infrastructure ecosystem concerning SDHI. Next, Section V gives a technology overview and describes a range of ongoing efforts toward realizing SDHI. Additionally, it identifies technical challenges and open research directions regarding SDHI technology. Section VI briefly discusses related research initiatives, and refers to a set of tools that can be used to further explore the area of SDHI. Finally, Section VII presents a summary of lessons learned and a set of concluding remarks.

#### II. SOFTWARE DEFINED INFRASTRUCTURE BACKGROUND

Today cloud providers are utilizing virtualized and SDI environments to achieve a higher degree of cost reduction, agility, optimization, programmability of the infrastructure, and automation. Despite all these measures, SDI is limited and tightly coupled to the traditional server architecture. Servers in today's cloud infrastructures are pre-defined at the factory where hardware resources are assembled within a chassis and cannot be used directly beyond that chassis. HW resource

disaggregation expands the boundary of SDI by breaking this tight coupling and allowing resources to be handled as independent resources regardless of the physical chassis they are placed in.

# A. Server-based SDI

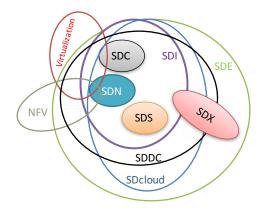

SDI was a response to the demand for greater flexibility, agility, and optimization. As shown in Fig. 1, several other terms with a tight connection and similarity with SDI terminology have also been used in the literature, such as: Software-Defined Environment (SDE), Software-Defined DC (SDDC), and Software-Defined Cloud (SDCloud) (see Table I). By SDI we mean the entire DC's infrastructure is software-defined and dynamically programmable. SDI can be realized by different building blocks including Software-Defined Computing (SDC) and virtualization, Software-Defined Networking (SDN) and virtual network function (VNF), and Software-Defined Storage (SDS) (see Table II).

Fig. 1. Taxonomy of software defined environments.

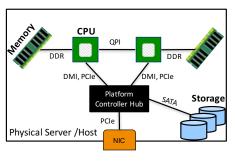

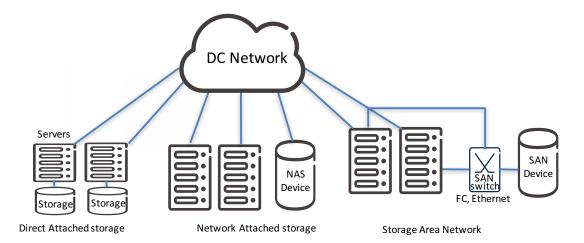

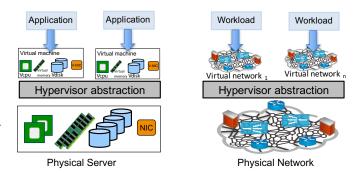

The current cloud infrastructure architecture and SDI are based upon a physical server-oriented model, where the infrastructure (i.e., a DC) is composed of pools of servers. These servers typically consist of a physical circuit board predefined and populated at the factory with specific resources, such as central processing units (CPUs), co-processors, memory, and networking subsystems. As shown in Fig. 2, these resources are interconnected using specialized communication channels, such as Peripheral Component Interconnect Express (PCIe), Double Data

Fig. 2. Simplified physical server component architecture.

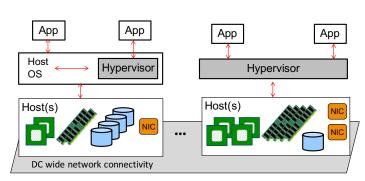

Rate (DDR), SerialAT Attachment (SATA), Quick Path Interconnect (QPI), and Direct Media Interface (DMI). Communication between server components is limited to the server's chassis and has strict requirements on latency and bandwidth to enable the system to work as an integrated system. Table III summarizes these requirements. Servers are interconnected via their network interface (generally referred to as a NIC) via a DC-wide network, as shown in the left side of Fig. 3.

TABLE I

TERMINOLOGIES SIMILAR TO SDI TERMINOLOGY.

| Terminology | Description                                          |  |  |  |  |

|-------------|------------------------------------------------------|--|--|--|--|

| SDE [11]    | All the components in an environment (e.g. IT        |  |  |  |  |

|             | infrastructure, power systems, and cooling systems)  |  |  |  |  |

|             | are software-defined and dynamically programmable.   |  |  |  |  |

| SDI [11]    | The entire DC IT infrastructure is software defined  |  |  |  |  |

|             | and dynamically programmable.                        |  |  |  |  |

| SDCloud     | The process of cloud configuration automated         |  |  |  |  |

| [18, 19]    | by extending virtualization to all of the Cloud      |  |  |  |  |

|             | infrastructure's physical resources in a DC.         |  |  |  |  |

| SDDC [20]   | The software-defined concepts is integrated into all |  |  |  |  |

|             | DC's main blocks, such as network, storage, compute  |  |  |  |  |

|             | and security.                                        |  |  |  |  |

TABLE II

TERMINOLOGIES INVOLVED IN SDI.

| Terminology             | Description                                                                                                                                                                                                                                            |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDN [17]                | Separates the network control planes from data planes and physical network entities to improve programmability, efficiency, and extensibility of network.                                                                                              |

| SDS [21]                | Separates the control planes from the data plane of<br>a storage system enabling heterogeneous storage to<br>respond dynamically to changing workload demands.                                                                                         |

| SDC [11]                | Originated from the computing environment in which<br>the computing functions are virtualized and managed<br>as virtual machines through a central interface as one<br>element.                                                                        |

| Virtualization [16, 17] | A software abstraction layer (i.e., hypervisor) emulates the behavior of physical entities in software. This term has been used in two different contexts in the literature, i.e., network virtualization and server virtualization. See Section V-D2. |

| VNF<br>[22, 23]         | Relocates network functions from dedicated network appliance to commodity servers.                                                                                                                                                                     |

Server oriented SDI

TABLE III

Approximate communication requirements between different resources within a server. These value differ for different hardware [24, 25].

| Communication type | Delay (ns)        | Bandwidth(Gbps) |

|--------------------|-------------------|-----------------|

| CPU - CPU          | ≈ 10              | 500             |

| Memory - CPU       | ≈ 20              | 500             |

| CPU - 10G NIC      | $> 10^3$          | 10              |

| CPU - SSD disk     | > 10 <sup>4</sup> | 5               |

| CPU - HDD disk     | > 10 <sup>6</sup> | 1               |

Until recently, networking technologies were unable to overcome the need to place the different components very close in terms of physical proximity. This resulted in fixed server configurations, making adaptation to workloads extremely difficult. Furthermore, infrastructure lifecycle management is tightly bound to the lifecycle of a server chassis. This causes problems for providers who wish to upgrade part of their infrastructure, especially since the resources that compose a server have different lifecycles. For example, if an infrastructure provider wants to upgrade or increase its compute capacity by adding new memory or processor technology, in most cases this means replacing the entire server.

Another key challenge in today's infrastructures is low resource utilization [26, 27], when the resources the infrastructure operator has paid for are not utilized to their full capacity. One reason for this is resource stranding [28], because of resources left from fragmentation due to the mismatch between application requirements and the fixed configuration of each server. For example, a CPU-intensive application can exhaust a server's computational resources while stranding other resources, such as memory and storage. To cover peak demands infrastructure providers must over-provision. This leads to large aggregated amounts of stranded resources and hence low utilization.

In order to improve resource utilization, infrastructure providers employ advanced resource scheduling techniques, in an attempt to solve what it is in most cases an NP-hard optimization problem. Moreover, they rely upon virtualization technologies, such as containers [29, 30] and hypervisors [31]

SDI based upon a disaggregated architecture

Fig. 3. Server-oriented SDI vs. SDI based upon resource disaggregation

(such as Xen [32], VMware [33], and KVM [34]), to implement server consolidation, multi-tenancy, and resource sharing. These techniques allow infrastructure providers to reduce their costs while providing dynamic scaling to their customers. In general, hypervisor virtualization can be classified into two types: the hypervisor runs directly on the hardware or the hypervisor runs on a host's OS - see the left sides of Fig. 3. However, hypervisor virtualization comes at the cost of extra overhead, as it interleaves execution of the applications and the execution of the hypervisor/host OS. Virtualization adds different amounts of overhead based on the type of virtualization and other competing workloads running on the same physical server [35–37]. In contrast, container-based virtualization has some benefits compared to hypervisor virtualization, especially in terms of performance. However, it is still subject to overheads and is highly dependent on the server's OS.

Despite all these measures, infrastructures still operate at low utilization [27] as today's approaches cannot overcome the physical boundaries of a server's chassis.

#### B. Software-Defined "Hardware" Infrastructure (SDHI)

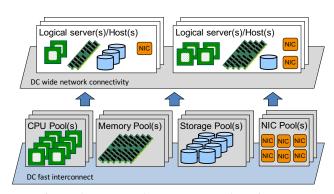

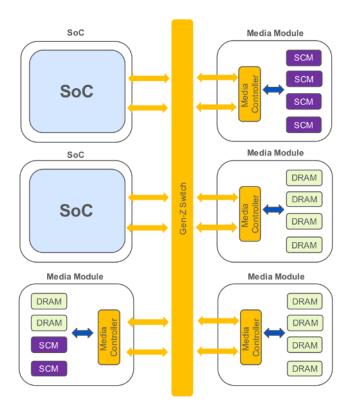

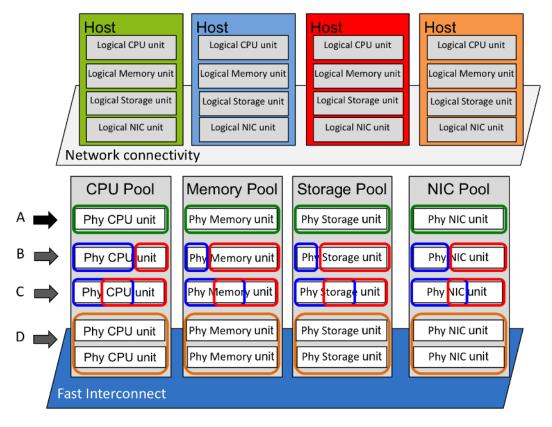

SDHI brings a novel approach to cloud infrastructures by introducing resource disaggregation based on software-defined principles wherein all resources are pooled and managed by software. Resource disaggregation breaks the traditional physical server architecture boundaries and considers hardware resources as individual and modular components. An ultimate disaggregation scenario has each of the different resources organized in independent pools of computing units, memory units, storage units, network interfaces, and other resources (e.g., accelerators, such as Graphics Processing Unit (GPU)).

SDHI breaks the one-to-one mapping between a physical server's chassis and a host by decoupling the software and management components from the underlying hardware. This makes the infrastructure more programmable. When an SDHI is initially deployed, there is no notion of host/server systems, only knowledge of the different hardware components yet to be assigned and programmed. The cloud infrastructure operator then utilizes an application programing interface (API) to create specific host/server systems, i.e., logical servers or logical hosts.

These principles bring a high level of fluidity, modularity, and flexibility to the cloud infrastructure. In this way, it is possible to dynamically establish and adapt the configuration of logical servers to precisely match the needs of particular workloads by on-demand selection and configuration of (physical) resources from different resource pools. This requires the necessary physical resources to be interconnected via high-speed very low latency communication to handle the physical separation between the different physical resources.

The interconnection fabric plays a pivotal role within a SDHI architecture, being both an enabler and blocking factor. Networking can be realized by two separate networks with different requirements: a fast interconnect fabric between individual hardware components and a DC-wide interconnection via NICs. The fast interconnect

fabric interconnects a set of hardware resources from which logical hosts can be realized as an integrated system. As a result, the fast interconnect fabric deals with the traffic within logical hosts. In contrast, in server-based SDI model, this interconnection traffic was restricted to a physical server's motherboard. This fast interconnect fabric should support strict latency and bandwidth requirements [24], while providing substantial resiliency, low cost, and low power consumption. The DC-wide interconnection enables logical hosts to communicate with the external environment (e.g., the Internet or other logical hosts) via the logical host's NICs. This traffic corresponds to the network traffic that exists in today's DC. The right side of Fig. 3 illustrates SDHI realized as a set of resource pools.

Ultimately, with SDHI, each hardware resource can serve multiple hosts, and a single host can consume resources from multiple hardware resources, thus allowing operators to optimize their resources.

Researchers describe somewhat different levels and types of resource disaggregation [38]. In the majority of cases, disaggregation is restricted to a rack (i.e., logical hosts can only be composed within a rack, therefore the term "rack-scale"). This restriction is mostly due to network limitations. However, we believe these limitations will be overcome in the long run. Moreover, in some cases, these systems are composed of microservers (each with a heterogeneous set of resources) interconnected through high-bandwidth low-latency networks. In other cases, they consist of different pools of resources (i.e., each pool having one kind of resource).

The concept of SDHI captured the interest of both industry and research community. One tangible realization is Intel's Rack Scale Design (RSD) [39, 40]. RSD is one of the pillars of the Open Compute Project (OCP) [41], an open source initiative that aims to scale computing infrastructures in the most efficient and economical way. Moreover, RSD is part of the foundation of Ericsson's Hyperscale Data System (HDS) 8000 [15]. Other industrial efforts in the area include Memory-Driven Computing [42], Rack-Scale Computing [43], and others [44–46]. Moreover, research initiatives trying to advance the state-of-the-art are also taking place [47–52]. We further elaborate on these in the following sections.

At this point, it is important to highlight that currently there is not (yet) a fully SDHI environment. Most of the systems only support partial disaggregation (e.g., storage [15, 41]) and are limited to the rack level. Base solutions for the overall system management entities are available (e.g., Intel RSD [39]). However, technology is evolving, and with time further disaggregation will occur (i.e., memory, network interfaces, and others), putting increased and more complex requirements on the management systems.

# III. NEW OPPORTUNITIES AND APPLICATIONS

This section discusses why the market is demanding SDHI, and then elaborate on some of the technical use-case and workload deployment opportunities that are made possible by SDHI. These use cases illustrate the possibility of innovations in the way we run application and workloads in DCs.

# A. Why Now? Market Demand

The rapid digitalization of industries, combined with the concept of IoT [53] and the ongoing transformation of companies through the use of cloud solutions, are just a few of the factors that have driven the increase in IT capacity [54]. In consequence, global spending on DC systems is growing [55] and there have been efforts to move toward SDI driven by economic and pricing theories for cloud resource provisioning, cloud management, and cloud networking [56, 57] in order to achieve sustainable profit, cost reduction, and flexibility. However, because the current ratio between IT capacity and its related cost is still high, it is not easy to deliver the desired capacity by using current SDI technologies simply with increased investment. In addition to financial barriers, the increasing complexity of new services, such as their high dynamicity, brings new challenges for future cloud deployments. These facts have led the IT community to search for ways to scale data center (DC) infrastructures beyond the cost and capacity limitations of today's DC architecture [58]. The first step is to rethink the DC architecture and make it more modular, flexible, and smart. The SDHI concept is driving this architecture change.

SDHI promises to bring new functional and business opportunities by extending the boundary of current SDI. It promises to be a step towards reduced Total Cost of Ownership (TCO) [59, 60]. For example, hardware utilization in current DCs is under 50 percent [61]. Until recently this was acceptable, but that is no longer the case. The market is too aggressive to ignore such wastage of resources. Hence, everything that can significantly affect the operational performance of the cloud infrastructure matters. Consequently, economic efficiency is vital for cloud owners of all sizes. The cost benefits of SDHI can be divided into business opportunities and TCO reduction [62] (as described below).

**Business** opportunities: Combining resource disaggregation and software-defined capabilities makes it less expensive and faster to expand the infrastructure to follow the exponential growth in both data and demand for IT services. Moreover, it offers the possibility to right-size the infrastructure based on the actual market [63] and customer demand, while avoiding over-dimensioning or losing customers due to insufficient capacity. New capacity can be added by either upgrading current components with more powerful ones (e.g., upgrading CPUs to ones with higher clock frequencies or larger core counts) or simply adding new chassis of the specific components which are the bottlenecks (e.g., if there is an increase in the amount of data, expanding the storage tier and memory tier, without needing to purchase new and costly CPUs). Moreover, the inherent flexibility and dynamicity of this type of infrastructure facilitates the adaptation of resources to fit any type of workload or application, further reducing the risk of investments in the infrastructure. Improved efficiency and finer granularity in creating logical servers bring new revenue streams for the cloud infrastructure operator. This makes it possible for these operators to act as a service provider by using these extra resources to offer new services to their customers at low prices.

**TCO reduction:** Low resource utilization is one of the primary reasons for the high cost of computing units [64]. It is widely recognized that cloud infrastructures run at very low levels of resource utilization due to their physical silos, hence resources are being wasted. Resource disaggregation provides a greater degree of sharing, thus enabling higher utilization. Higher utilization means that the same workload can be served with less hardware [65], hence reducing capital expenditures (CAPEX). However, cost savings go beyond CAPEX and can impact operational expenditures (OPEX).

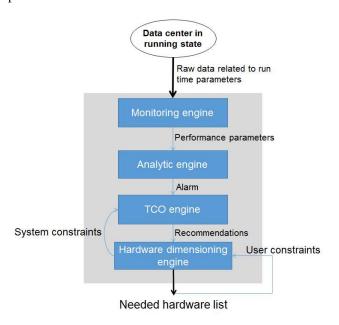

SDHI's TCO related aspects have been thoroughly explored in [60] via a framework to assess the cloud infrastructure's economic efficiency. This work presents a thorough cost comparison of deploying an SDHI architecture versus deploying a server-based SDI architecture in DCs. The study considers all the major cost categories incurred during the DC's lifetime with regard to CAPEX and OPEX (i.e., from the deployment phase, when a huge upfront investment is required, to all costs related to each operational process). Results show that in the presence of heterogeneous workloads, having a DC based on SDHI brings high savings (of more than 40% depending on the applications) compared to server-based SDI. Moreover, lifecycle management cost was one of the main differentiators between SDHI and SDI.

Electricity is one of the limiting factors for deploying DCs. One of the direct consequences of increased resource utilization which comes from SDHI is reduction in the DC's power consumption. As fewer resources have to be turned on for the same workload, the power consumption per unit of workload is lower. Using more energy efficient algorithms for workload placement, which is managed by SDHI, can further reduce energy consumption, leading to a greener DC. Reduction in power consumption, leads to less heat dissipation, hence less cooling power, which contributes to increased power savings compared to DCs operated with server-based SDI [66]. Also, the architecture of the SDHI DCs, including the way cooling system is designed, can have a large impact on the energy consumption of a DC. For example, [67] proposes a novel energy-efficient architecture for software-defined DC infrastructures, were the total power consumption is reduced by 27% in comparison to a DC with a conventional architecture. Moreover, the capabilities of Smart Grids technologies [68–70] should be exploited within DCs based on SDHI to further save energy.

## B. Technical Applications

1) Adaptive Server Realization: Ideally, there should be a perfect match between the workload being executed and the logical server's resources in an SDHI to eliminate resource stranding, thus gaining the most from this new paradigm.

With SDHI, the logical server and the platforms and applications it hosts (the service domain) can interact with the different operational layers (see Section IV) by sending requests and receiving hints and feedback. Tight interaction between the service and operation domains presents an

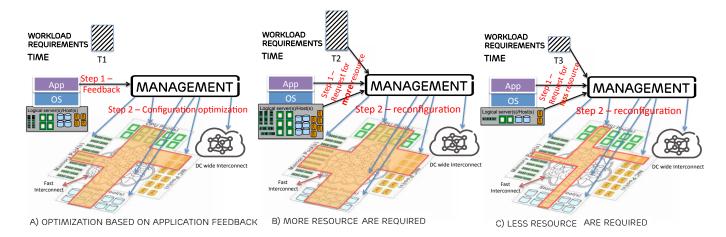

opportunity for dynamic configuration and fine-grain resource (re)scheduling that can increase resource utilization and system efficiency. Fig. 4 illustrates some scenarios where a logical server could benefit from dynamic adaptation.

Fig. 4(a) illustrates a scenario where the execution environment scheduler decides which job (i.e., part of a given workload) will be executed by which CPU, hence this scheduler can provide feedback to the management stack (step 1). This feedback can be used to optimize the configuration of the logical server. For example, the network can be reconfigured such that the part of the known workload will be executed in a particular logical server's CPU and hence will be allocated memory close to this CPU (step 2). Later the operations domain can be notified of either: (1) the logical server requiring more resources - Fig. 4 (b) step 1 or (2) a set of resources may be released - Fig. 4(c) - step 1. In these cases, the operations domain dynamically re-configures the different resources and DC interconnection fabric to adapt the logical server to its new configuration (Fig. 4 (b) and (c) - step 2). Minimizing the time required for realizing these dynamic adaptations is a major factor in achieving high performance and efficiency.

Consistent monitoring of the application and using feedback from the execution layer enables the operations domain to identify deviations in the behavior of a given workload from the predicted behavior. A key question is to identify how frequently reconfiguration and rescheduling should take place in order to increase the efficiency of logical servers while considering the time required for re-configuring and re-scheduling the workload, the network conditions, and the availability of the necessary physical resources.

2) The Big Modular Machine: Today application designers have to deal with the resource limitations of a single server. This is particularly true for those applications that store and handle a large volume of data, thus requiring a large amount of memory. SDHI can solve this problem by forming "very" big machines that are composed by interconnecting a large number of CPUs, memory, and storage.

Applications (such as in-memory databases) that today

rely on being distributed over a set of servers to achieve scale can potentially be deployed on a single big machine provisioned through SDHI. This will reduce the complexity of the application by eliminating the synchronization overheads, load balancing, and failure handling that arise due to scaling by distribution. This approach can also help improve the performance of the application by removing the communication overhead between the servers, as all the data and processing are resident within the single big machine. High-performance Computing (HPC) type of applications, real-time analytics, and in-memory software such as SAP-HANA (which today can be configured to operate on 8 cores and 6 TB of RAM) can potentially be scaled up to operate on a much larger number of CPUs and much larger amounts of memory. This scaling up is needed to cater for large-scale data handling in the future. Legacy applications (such as operations support systems and business support systems (OSS & BSS) were not designed to scale out but need to handle the demands of the future. However, these would benefit from being deployed on logically large machines, thus eliminating the need for scaling up individual processors.

3) Highly Available Server: High Availability (HA) is an important concept in building a robust service. Today ensuring HA of hardware components running a service requires full redundancy of the service on another server(s). In other words, the granularity is that of a server. This is not a cost-effective solution and the recovery time is large. Moreover, the application needs to be aware of the HA setup.

SDHI introduces new failure points, as the boundary of server extends beyond a single physical blade. Thus there are scopes for research in HA and fault resiliency models at HW and software levels. Nevertheless, in SDHI, HA can be provided on a component level rather than a server level. Logical servers composed using SDHI can include redundant components that can quickly take over from components that fail. This means that the failure of a single component in an SDHI composed logical server need not result in the failure of the entire logical server, hence the logical server can continue to function due to the redundant components. Component

Fig. 4. Adaptive and dynamic logical server realization: (a) shows the configuration optimization based on application feedback, (b) shows what happens when a logical server requires more resources, and (c) shows what happens later when the logical server requires fewer resources.

level granularity combined with component health monitoring enables the addition of redundant components only of the type that are failing instead of allocating multiples of an entire redundant server as is done today. An SDHI based logical server can be made robust against failure of CPU, memory, disk, or NICs without incurring a long downtime, resulting in the HA mechanism being transparent to the applications, hence reducing their complexity.

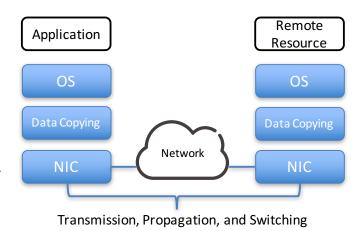

4) In-memory communication and data sharing: A lot of network traffic that traverses network elements (such as switches in a DC) is between applications running on different servers. Today, in order to achieve scale, applications are composed of different components that can be run in a distributed fashion on different servers, but this may lead to an exchange of a large volume of data between the servers within a DC (or even between different DCs).

In an SDHI, logical servers can potentially share a portion of memory and use that memory as a communication channel. This mode of communicating via shared memory can reduce cost by reducing the number or capacity of NICs and switches in the DC (at the cost of using the interconnection fabric). Moreover, it can reduce latency for the communication between applications.

Today big data frameworks (such as Hadoop) need to keep data in a distributed fashion spanning a large number of servers [71]. A single large file can be decomposed into smaller blocks and stored on different servers. Accessing a part of the file from a server might require network communication to fetch the block of that file from a different server, which increases latency and hence negatively impacts performance. The flexibility of SDHI in assigning the resources to logical servers facilitates attaching a block of storage containing the required section of a file to a logical server which wants to operate on the data thus avoiding transfer of the data over the network. Another advantage is the possibility to dynamically compose a logical server for processing data around the storage component which holds the data. In a Map-Reduce use case, logical servers can be composed of storage components which hold the data required for the map operation. Once the map operation is completed and the intermediate data is written to the storage, new logical servers can be composed of those storage components holding the intermediate results for the reduce operation thus reducing the need to shuttle data between servers as it is traditionally done.

# IV. DC ARCHITECTURE BASED ON SDHI

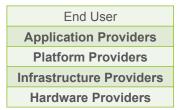

HW disaggregation and the associated concept of SDHI are rather disruptive technologies whose effects are far reaching — from HW design and manufacturing to how applications are developed for disaggregated HW systems. To understand the impact of HW disaggregation on the architecture of DCs, we start with common cloud service models and their associated stakeholders. Fig. 5 shows these stakeholders (in bold) in a generic DC deployment that provides all of the traditional "X" as a Service (XaaS) services. In this deployment, end users consume applications from software providers (i.e., Software as a Service (SaaS)). Application providers develop

Fig. 5. Key stakeholders in a deployment of a cloud-type DC.

(or obtain developed) applications for a software platform that is operated and maintained by platform providers (i.e., Platform as a Service (PaaS)). Platform providers deploy their platform software on the (virtualized) infrastructure provided as a service by infrastructure providers (i.e., Infrastructure as a Service (IaaS)). Infrastructure providers, in turn, consume the services of HW providers (e.g., HW purchasing/leasing, colocation, and other utilities & facilities) to provision the HW infrastructure on which they provide their service.

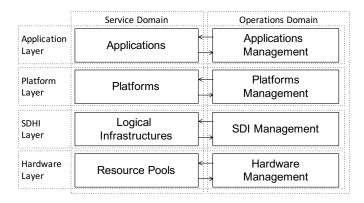

A functional architecture of a DC system built on disaggregated HW resources can be defined with the above stakeholders in mind. Fig. 6 shows one such architecture that has a management layer that corresponds to each stakeholder. In addition to these layers, the functional blocks of the architecture are organized as service-domain functions (on the left) and operations-domain functions (on the right). Service domain functions relate to the "payload" (from the viewpoint of the DC), including the applications that are used by the end users of the cloud, the platform-level software (i.e., OS and supporting services needed to run the application), and HW resources used to execute the software. The operations domain functions, on the other hand, relate to the management functions that make the DC work, starting from those at the hardware level that allow resources to be split and composed into an SDHI, to those at the application level that manage the orchestration and deployment of application components. Management functions implemented by several existing cloud management systems, such as OpenStack [72], Ubuntu Metal as a Service (MaaS) [73], and Kubernetes [74] are examples of operations domain functions at the various layers of the architecture. However, beyond these traditional functions there are new server functions, such as those described in Section

Fig. 6. High-level architecture for a DC built from disaggregated HW resources.

IV-A that are specifically needed to realize SDHI systems.

# A. Hardware Layer

This layer includes the physical resources and their associated interconnects/fabrics from which the SDHI can be realized (in the service domain), as well as the HW-near functions that enable disaggregated HW to be pooled, aggregated, and composed into a software-defined logical infrastructure (in the operations domain). In the service domain, this architecture does not make specific assumptions with regard to the level of HW disaggregation or the specific functionalities available at the HW-level. However, it does assume that the available HW is composable in the sense that it is possible to dynamically compose and recompose logical infrastructures from the HW resources and HW resources are organized into interconnected *resource pools*.

The operations domain functions at this layer include traditional server management functions that are implemented in microcontrollers, such as IPMI [75], HP's ILO [76], and Dell's iDRAC [77]. However, there are a new set of management functions (such as the composability service in Redfish [78] - see section V-C1) which may present an important management overhead when compared to the management of traditional server-based systems.

In the service domain, performance implications need to be taken into account, namely due to additional networking latency between different components within SDHI. These performance implications need to be measured against those present in a non-SDHI system, such as virtualization technologies (e.g., hypervisors or containers), to understand if the benefits of a specific SDHI solution overcome those of a non-SDHI solution.

# B. SDHI Layer

This layer provides the equivalent functionality of a pure SDI and IaaS in today's cloud. It consists of logical infrastructures that are composed of the assigned HW resources. The operations domain for this layer receives requests for logical infrastructures and composes them by making appropriate calls to the HW-layer functions. This layer has a global view of the underlying HW pools and the composed entities, i.e., it has complete knowledge of all HW resources, how they are connected via the interconnects, how the various resources can be sliced and composed with each other to form logical infrastructures, the logical structures that have already been created out of these resources, and so on. However, unlike a traditional IaaS, this layer does not have any view of the software running on top of the composed HW (unlike OpenStack [72] or Amazon EC2 [79] where the Virtual Machine (VM) provisioning process also includes preparation of a virtual disk from whence the VM starts up). Instead, this layer exposes mechanisms, such as network booting and/or disk authoring, that allow the logical infrastructure to boot into a usable state. Furthermore, this layer exposes smart HW functions (e.g., highly available HW, state synchronization, and live state migration) to the software running on the composed infrastructure, whenever these functions are available in the underlying HW.

## C. Platform Layer

This layer handles the software that runs on the composed logical infrastructure to run the application. Examples of open source software platforms include OpenStack, Cloud Foundry [80], Kubernates [74], or a bare Linux OS. In addition to these, there are proprietary platforms, such as [81, 82]. Depending on the platform software, the application may be provided in the form of source code, an executable binary, or even a VM image. A key requirement of this layer is the ability to run multiple platforms at the same time on the same HW infrastructure. This platform layer can be recursive to multiple levels. For example, it should be possible to first deploy an Apache Mesos [83] platform onto a logical infrastructure and then to deploy Apache Yarn [84] and Kubernates on this Mesos platform. This, for example, would allow a MapReduce and containerized applications to execute side by side on the same logical infrastructure. Platform-specific functions, such as auto-scaling of the platform itself, or software libraries that enable the full exploitation of the underlying (disaggregated) HW, are implemented at this level.

# D. Application Layer

The application layer handles the specific applications that provide service to the end-user of the cloud. An application can be a VNF [22, 23] that runs in an OpenStack VM or a 4Quant [85] image analysis tool running on Apache Spark. For each deployed platform we assume an application management interface (e.g., Nova-API in OpenStack or Spark driver in Apache Spark) allows deployment and control of applications for that specific platform. These applications and their management functions come from existing software platforms; therefore, it should be possible to run them unmodified on the logical infrastructure. However, extending these platforms with functionalities stemming from HW disaggregation (see section III ) may be beneficial.

# V. TECHNOLOGIES, CHALLENGES AND FUTURE DIRECTIONS IN SDHI

The direct technological impact of SDHI is confined to the HW and its operation. However, this impact ripples through all the other layers of the architecture. Standardization efforts in the DC technology space expanded with the creation of the open source initiative Open Compute Project (OCP) [41] in 2011. OCP is supported by several industry leaders (IT vendors, network operators, and service providers) and its purpose is to share designs of efficient DC products. Within this initiative, industries have been carrying out extensive collaborative efforts to create new open and flexible standard solutions for future DCs. Among the members of OCP is Intel, who announced in 2013 its hardware disaggregation vision called Rack Scale Architecture (RSA), now called Rack Scale Design (RSD) [40]. RSD is a reference specification for hardware disaggregation and a key component of OCP. RSD's core management and control components (Pooled System Management Engine (PSME), Pod Manager (PODM), and Rack Management Module (RMM)) have been released as open-source software [86]. In early 2016, the Telecom

Infra Project (TIP)) [87] was announced. TIP can be seen as a complement to OCP but is narrowly focused on the development of new telecommunications networking HW. This initiative aims to leverage several OCP efforts, among which are HW disaggregation and composability concepts.

In this section, we present a technology overview and a range of ongoing efforts toward realizing SDHI. These are organized in relation to the different architecture layers presented in section IV. Table IV provides an overview of some of the most relevant efforts. Furthermore, in each section, we present more in-depth efforts and discuss foreseen challenges and future research directions.

# A. HW Layer: resource disaggregation and shift in hardware

HW resource disaggregation is in its early stages. Although storage has been disaggregated [15, 41], challenges remain in how to decouple the remaining server components, such as memory, processors, and NICs. This subsection focuses on the inherent challenges, focusing on three main areas: HW component disaggregation (processor, memory, storage, and NIC), resource control (i.e., slicing, aggregation, and sharing), and the infrastructure interconnection fabric.

1) Processor Aggregation and Slicing: The core of SDHI is independent resource pools that can be dynamically composed into logical infrastructures. Whether it is possible to construct logical servers with an arbitrary number of CPUs without suffering the overheads of hypervisor-based solutions is one of the key questions [151?].

Aggregating CPUs requires a lot of low latency bandwidth for the inter-CPU traffic. Multiprocessor systems based on Intel Xeon processors use QPI [117] for communication between processors. QPI consists of two unidirectional links with a bandwidth of 8-12.8GB/sec and latency of 100-300ns. The upcoming version QPI, called Ultra Path Interconnect (UPI) is designed to run at higher speeds. The big difference of UPI from QPI is that there can be 2-3 UPI per CPU [159]. However, it is hard to realize this bandwidth with low latency over long distances. The common use-case for aggregating CPUs is to build high-capacity servers that are suitable for scale-up scenarios (see Section III-B). However, as current cloud applications are designed to follow the scale-out paradigm, there seems to be little research in this area.

The inverse of aggregating CPUs is slicing a CPU into multiple resources. When the configuration of a server hardware platform is fixed, there is little benefit in slicing the CPU to run different OSs without a hypervisor, as contention exists when accessing hardware resources. However, with resource pooling opportunities exist to exploit CPU slices. Some aspects of this are covered in Section V-D2.

While CPUs are certainly a fundamental element, these are not the only type of processors that are relevant for disaggregation. Acceleration devices, such as GPU and Field Programmable Gate Array (FPGA), are also at the forefront of this technology shift. However, most of the explored approaches purely rely on software and are implemented at

the OS level [147–150]. Moreover, Amazon has a commercial offering for remote acceleration by using OpenGL over Elastic Network Interface (ENI).

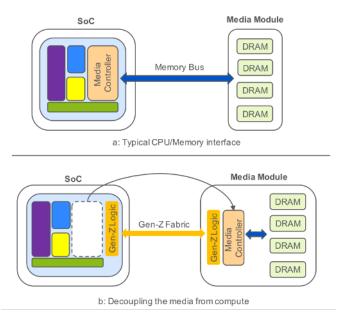

2) Memory Disaggregation and Pooling: The demand for server memory capacity has been increasing along with the increase in the number of cores per socket, the number of VMs running on a server, and the increased memory footprint per VM [88]. The need for increased memory capacities has been further fuelled by the growing number of in-memory applications. These demands are likely to be further exacerbated by the need for in-memory processing and real-time analytics required by the 20-100 billion [160, 161] connected devices. However, a set of studies (e.g., [162, 163]) reveal that the average memory capacity utilization is 50% and the peak memory usage continues to increase. This combination suggests that every large aggregate amounts of memory will be under utilized.

Moreover, Dynamic Random-Access Memory (DRAM) process scaling is becoming costly, imposing limits on how much DRAM can be placed on a server blade. With pin count on processor sockets not increasing dramatically and the number of Dual Inline Memory Modules (DIMMs) per channel decreasing due to increased channel speeds, the growth in the total addressable memory is constrained.

One method that was used earlier to increase memory capacity was Fully Buffered DIMM (FB-DIMM) [89]. FB-DIMM utilizes the high-speed serial interface between the memory controller and an Ambient Memory Buffer (AMB) residing on the DIMMs and uses the store&forward methodology to increase memory capacity. However, increasing the number of DIMMs results in increased latency. Additionally, extending the serial links beyond a single board requires additional store&forward mechanisms which further increases latency. Furthermore, DRAM placed in a compute blade consumes power whether or not it is used, and the FB-DIMM store&forward electronics further increases heat generation. An extension to FB-DIMM has been proposed by the research community, called Optically Connected DIMM (OCDIMM) [90]. OCDIMM uses optical channels to communicate between the AMB and memory controller to increase memory capacity and reduce latency [90]. Simulation results show that OCDIMM can provide higher bandwidth and capacity. However, OCDIMM requires optical connectivity from the CPU, which is not supported in commercially available CPUs.

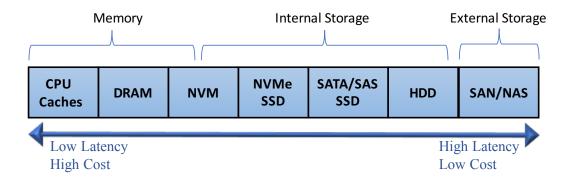

At the same time, there is a variety of storage class memories (SCM) [164, 165] that are being researched. These aim to provide diverse capabilities which promise to be beneficial for different workloads. For example, Non-Volatile Memory (NVM) technologies (e.g., [91, 166, 167]) provide increased memory density at a latency higher than DRAM (see Fig. 7).

However, these different memories are only accessible by a single CPU blade, thus complicating the orchestration of workloads and increasing the potential for underutilization of these memories.

Memory disaggregation could help solve these problems

TABLE IV

TECHNOLOGY OVERVIEW OF SDHI.

| Type                | Area                | References          | Origin                        | Scope                                                                                |

|---------------------|---------------------|---------------------|-------------------------------|--------------------------------------------------------------------------------------|

|                     |                     | [88]                | Research                      | Showing performance benefits of memory disaggregation                                |

|                     | Memory              |                     |                               | in memory constrained environments.                                                  |

|                     |                     | [89, 90]            | Research                      | Increase memory capacity and reduce latency in memory                                |

|                     |                     | [91]                | Industry                      | blade servers.  NVM (e.g., 3D XPoint) technologies to increase memory                |

| Compute<br>Hardware |                     | [>1]                | industry                      | density with a latency higher than DRAM.                                             |

| nardware            |                     | [25, 88, 92–94]     | Research                      | Feasibility of entirely disaggregated memory.                                        |

|                     |                     | [95]                | Research                      | Fast in-memory Key-value store.                                                      |

|                     |                     | [96]                | Research                      | Cost of memory disaggregation.                                                       |

|                     |                     | [97–100]            | Industry<br>Research          | SAS, NAS, and SAN.                                                                   |

|                     | Storage             | [101]               | Research                      | Rack-scale storage fabric. Flash Storage disaggregation.                             |

|                     |                     | [103]               | Research                      | Resiliency aspects of using NVM.                                                     |

|                     |                     | [104, 105]          | Industry                      | Ethernet multi-host technology for rackscale networking.                             |

|                     | NIC                 | [106]               | Research                      | Software architecture for low latency DC communication.                              |

|                     | NIC                 | [107]               | Industry                      | Integrated NIC Architecture.                                                         |

|                     |                     | [108]               | Industry                      | SR-IOV network virtualization.                                                       |

|                     | Interconnection     | [109]               | Industry/Research             | Roadmap on silicon photonics.                                                        |

|                     | Fabric              | [110]               | Research                      | Manycore processor-to-DRAM.                                                          |

| Networking          |                     | [111]               | Research                      | Switching optically-connected memories.                                              |

| Networking          |                     | [112]<br>[113, 114] | Research                      | Optical interconnects for disaggregated resources.  Microsoft rack-scale networking. |

|                     |                     | [115, 114]          | Industry/Research<br>Research | A reconfigurable Rack Network based on SoC switch.                                   |

|                     |                     | [116]               | Research                      | Slim Fly a low diameter network topology.                                            |

|                     |                     | [117]               | Industry                      | QPI.                                                                                 |

|                     | Interconnection     | [118]               | Industry                      | Gen-Z.                                                                               |

|                     | Protocols           | [119]               | Industry                      | OpenCAPI.                                                                            |

|                     |                     | [120]               | Industry                      | CCIX.                                                                                |

| ŀ                   | Network             | [121–129]           | Industry/Research             | SDN.                                                                                 |

|                     | Management          | [130]               | Industry/Research             | SDON.                                                                                |

|                     | S                   | [131, 132]          | Research                      | Control Plane OS.                                                                    |

|                     | Discovery           | [75]                | Industry                      | IPMI.                                                                                |

| Infrastructure      | & Control           | [78, 133]           | Industry                      | Redfish.                                                                             |

| Management          | Scheduling          | [134–136]           | Research                      | Scheduling aspects.                                                                  |

|                     | Cloud               |                     |                               |                                                                                      |

|                     | Management          | [137, 138]          | Industry                      | OpenStack Valence and Ironic/Redfish.                                                |

|                     | -                   | [17]                | Research                      | Survey on network virtualization hypervisors for SDN.                                |

|                     | Network             | [139]               | Industry                      | Cost of network virtualization.                                                      |

|                     | Virtualization      | [16]                | Research                      | Survey on server virtualization.                                                     |

| Platform            | Server              | [140]               | Industry                      | QEMU.                                                                                |

|                     | Virtualization      | [141]               | Research                      | KSM (Kernel Same page Merge).                                                        |

|                     |                     | [142]               | Research                      | Minimal hypervisor by efficient OS implementation.                                   |

|                     |                     | [143]               | Research                      | Hotplug of CPU.                                                                      |

|                     | 0                   | [144]               | Research                      | Hotplug of Memory.                                                                   |

|                     | Operating<br>System | [145]               | Research                      | The operating system is the control plane.                                           |

|                     |                     | [146]               | Industry                      | NVMe interface to provide access to a storage                                        |

|                     |                     | [147–150]           | Research/Industry             | namespace.  Virtualization and Remote Accelerators (DS-CUDA,                         |

|                     |                     | [17/-130]           | rescarentinustry              | gVirtuS, GViM, and rCUDA).                                                           |

|                     |                     | [151, 152]          | Industry                      | ScaleMP and TidalScale.                                                              |

|                     | System              | 1                   | ,                             |                                                                                      |

|                     | Simulator           | [153]               | Industry                      | Simics.                                                                              |

| ŀ                   | Hardware            | F1 5 42             | T 1 .                         | C.F.                                                                                 |

| Dagagrah            | Simulator           | [154]               | Industry                      | CoFluent.                                                                            |

| Research<br>Tools   | Data Center         | [155]               | Research                      | Diablo.                                                                              |

| 10018               | Simulator           | [155]               | Research                      | Diauto.                                                                              |

|                     | Data Center         | [156]               | Research                      | Firesim.                                                                             |

|                     | Simulator           | [100]               |                               | ·                                                                                    |

|                     | Network<br>Emulator | [113]               | Industry/Research             | Maze.                                                                                |

|                     | Emulator            |                     |                               |                                                                                      |

|                     |                     | [41]                | Industry                      | OCP                                                                                  |

| D                   |                     | [87]                | Industry                      | TIP.                                                                                 |

| Projects            | Cross-Area          | [40, 86]            | Industry                      | RSD.                                                                                 |

|                     |                     | [156, 157]          | Research                      | Firebox and dRedBox.                                                                 |

|                     |                     | [158]               | Research                      | M2DC.                                                                                |

Fig. 7. Memory and storage access latency and cost spectrum.

while increasing the memory capacity available for applications, increasing the average utilization of the infrastructure, and reducing total energy consumption (e.g., [168, 169]). However, memory in current commodity architectures has been very tightly coupled to the CPU due to the very high bandwidth and low latency requirements of the CPU-memory bus (see Table III) and the restrictions on the memory types supported by a given CPU. Moreover, the current memory bus cannot be extended to longer distances due to signal integrity issues. Alternatively, converting the parallel-electrical-bus of the memory devices into a serial-optical-bus becomes a very expensive proposition in terms of both cost and energy.

There is little research that considers completely removing memory from the compute sled. Rather, current research approaches attempt to realize partial memory disaggregation by using local DRAM as a cache for remote memory and swapping pages from/to remote memory as required. In these cases, the interface between CPU and memory is usually based on cache line fetches. Moreover, much of the literature focuses on using page sized memory requests similar to disk-based swapping. This is done to exploit data locality and amortize the latency incurred due to delays over the interconnect. Two methods are widely used in the literature: (1) including a PCIe extension to bridge multiple memory domains or (2) use of Remote Direct Memory Access (RDMA) (e.g., Infiniband [170] or Omnipath [171]) or other low latency methods. These approaches have been shown to work well for applications with good data locality [92]. Quite a few papers have evaluated these approaches, some of these evaluations are described in the following paragraphs. Table V summarizes the efforts toward memory disaggregation.

K. Lim, et al. [88] designed a new general-purpose architectural building block - a memory blade - that allows memory to be disaggregated across a system ensemble. This solution can be used for memory capacity expansion to improve performance and for sharing memory across servers. They claim their solution can potentially reduce the cost of provisioning and reduce power consumption. They proposed two new system architecture solutions: (1) a page-swapped remote memory at the virtualization layer and (2) a cache level-access remote memory with support for transparent memory expansion and sharing for commodity-based systems.

Moreover, they explored the implications of these solutions by developing a software-based emulation platform using the Xen hypervisor [93] and compared their results with a disk-based swap mechanism.

Silicon photonics [109] is an evolving technology in which data is transferred optically. This technology is proposed as an interconnect choice for rack-scale systems. Several papers (e.g., [110, 111]) suggest using silicon photonics for CPU-memory interconnects. However, commercial 100 Gbps silicon photonics are insufficient for CPU-memory interfaces, as 1 Tbps connections may be required to fully disaggregate memory. Assuming four memory controllers per CPU (i.e., the norm in X64 Xeon CPUs deployed in clouds), one would need at least 250 Gbps photonic interconnects to meet current requirements. However, this level of performance is expected to be commercially available in a few years when these interfaces are directly integrated into CPUs. However, yet more time will be required for these solutions to be cost effective for broad adoption across the entire infrastructure.

P. X. Gao, et al. [25] demonstrated that current networks are sufficient to do memory disaggregation for a variety of applications. They claim that silicon optics and other future-looking technologies are not required and that current technologies are sufficient to realize memory pooling. One of the main assumptions is that NICs will be embedded into CPUs to reduce latency in a disaggregated memory environment. Their simulation study assumes the use of 40-100Gbps Ethernet connections. Moreover, they ignore software overhead associated with page operations despite the fact that this overhead could be non-negligible if a running process has to do a context switch while waiting for the page swap operation to complete.

Marlin [94] is a PCIe based system where all the memory from multiple blades is aggregated into a global memory. Each machine in the rack is connected to a port of the PCIe switch through a PCIe expansion card and a PCIe cable. On each Non-Transparent Bridged (NTB) port of the Marlin switch is a DMA engine capable of initiating DMA transactions across different physical address ranges. Marlin refers to this Hardware based RDMA (HRDMA) as providing a cross-machine memory copy operation. HRDMA allows data to be copied from one application process address space (running on one machine) to the address space of another

$TABLE\ V$  Summary of individual papers addressing memory disaggregation.

| Ref   | Ref Objective of work                                                                                                                             |                           | Result Summary                                                                                                                                                                 | Interconnection         | Comment                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------|

| [88]  | Evaluate feasibility of memory disaggregation.                                                                                                    | Simulations & Prototype   | Memory disaggregation is feasible and can provide substantial performance benefits (on average 10X) in memory constrained environments.                                        | PCIe                    | OS & hypervisor transparent but requires custom chip. |

| [25]  | Evaluate the feasibility of memory disaggregation with existing system designs and commodity networking technology.                               | Simulation &<br>Emulation | Current network technologies are sufficient<br>to do memory disaggregation for a variety<br>of applications but with some performance<br>degradation.                          | RDMA                    | -                                                     |

| [94]  | Present the design, implementation, and evaluation of a PCIe-based rack area network system for memory disaggregation.                            | Prototype                 | Based on their design, one-way kernel-to-kernel latency is 8.5 $\mu$ sec, and the end-to-end sustainable TCP throughput is 19.6 Gbps.                                          | PCIe<br>&<br>HRDMA      | -                                                     |

| [93]  | Explore software and systems implications of disaggregated memory.                                                                                | Prototype & Emulation     | They develop a software-based prototype by extending the Xen hypervisor to emulate a disaggregated memory design wherein remote pages are swapped into local memory on-demand. | NA                      | -                                                     |

| [92]  | Feasibility of fully disaggregated memory.                                                                                                        | Prototype                 | Memory disaggregation is possible under<br>Spark SQL workload with already available<br>commercial network technology.                                                         | PCIe                    | A case study<br>on Spark<br>SQL.                      |

| [110] | Present a new monolithic silicon photonics technology and its application for manycore processor-to-DRAM networks.                                | Simulation & Prototype    | The focus was on network aspect for communication between CPU and memory based on photonics.                                                                                   | NA                      | -                                                     |

| [111] | Assess feasibility of transferring data across processors by using the optical interconnection fabric.                                            | Simulation                | The performance data demonstrates the effectiveness of switching memory in transparent data sharing and communication within a rack.                                           | NA                      | -                                                     |

| [172] | Design and implementation of a new memory distributed computing platform.                                                                         | Prototype                 | The platform performs well and shows order of magnitude better throughput and latency than main memory systems that use TCP/IP on the same physical network.                   | RDMA<br>over<br>RoCE    | -                                                     |

| [173] | Memory architecture for clusters to enable<br>a distributed non-coherent shared-memory<br>view of the memory resources present in the<br>cluster. | Platform                  | The database that is running in this prototype beats commercial solutions in terms of latency and throughput.                                                                  | HyperTransport<br>[174] | FPGA based solution                                   |

| [175] | Design a system using commodity products that connect multiple nodes and enable resource sharing among these nodes.                               | Prototype                 | The evaluation results indicate that resources can be efficiently shared in many cases.                                                                                        | PCIe SR-IOV             | Software<br>stack<br>extension.                       |

| [176] | Design and implementation of a remote memory paging system for an RDMA network.                                                                   | Prototype.                | Demonstrate the overall memory utilization increases in a cluster of nodes.                                                                                                    | RDMA                    | -                                                     |

| [177] | Assess how can Symmetric Multi-Processing high memory demands take advantage of remote memory.                                                    | Prototype                 | The proposed solution significantly improve<br>the performance of memory intensive<br>workloads                                                                                | RDMA                    | -                                                     |

application process that is running on another machine in the same rack without any software intervention.

There are software solutions that aggregate memory across multiple physical servers and provide access to an aggregated memory, such as [152] and [151]. These solutions target big data applications. However, performance penalties are high when cross-server communication occurs. Moreover, these solutions require adding server boards containing both CPU and memory to increase either of these resources (as the software has to have a CPU to run on to access the physically local memory to make it available remotely).

The design of a memory blade has inherent challenges. As applications become more resource demanding and require larger working sets, several memory pools will be needed on one memory blade to address the increase in required memory bandwidth and to reduce noisy neighbor problems. The rate at which applications need memory, the speed of interconnects,

the memory node characteristics, and the performance of memory controllers are some of the factors determining memory pool capacities and the number of required memory controllers. The location of a memory controller itself presents interesting choices. A memory controller placed close to the memory blade can perform memory bank refreshes locally, thus optimizing the power utilization and logic on the CPU socket. Conversely, the absence of a memory controller on the CPU could present other challenges due to the absence of an on-chip memory arbitration mechanism. A future design could potentially split the roles of the memory controller and realize different roles at different locations.

With memory disaggregation and pooling, different compute nodes and devices can access and share memory blades, thus memory access control mechanisms will be required to prevent unauthorized bare metal servers or devices from accessing memory to which they should not have access. If a hypervisor exists on the compute nodes, it could provide the needed protection. However, in bare metal environments, such access control is required either at the hardware level of the compute node or at the memory blade. Moreover, as multiple applications could attach to the same memory pool, quality of service considerations are required at various points. Additionally, protocols between the compute blade and memory blade need to be agnostic to current memory protocols (e.g., DDR3 and DDR4) to allow the use of different types of memory in the memory blade.