1

Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# Solar PV-fed Multilevel Inverter with Series Compensator for Power Quality Improvement in Grid-Connected Systems

Devalraju Prasad<sup>1</sup>, Graduate Student Member, IEEE, Dhanamjayulu C<sup>1</sup>, Senior Member, IEEE.

<sup>1</sup>School of Electrical Engineering, Vellore Institute of Technology, Vellore, Tamilnadu, India.

Corresponding author: C. Dhanamjayulu (e-mail: dhanamjayulu.c@vit.ac.in)

"This work was supported by Vellore Institute of Technology, Vellore, Tamilnadu, India through the research fund RGEMS under VIT SEED GRANT/12439."

**ABSTRACT** Power quality difficulties arise as a result of Renewable Energy Sources (RES) integrating with the grid. Voltage swell, sag, and harmonic distortion occur on the grid due to power quality issues, which have an impact on customers. An inexpensive series compensator, like the Dynamic Voltage Restorer (DVR), is the best solution for overcoming the aforementioned problems. In this article, a solar PV integrated DVR with a novel multilevel inverter is introduced to address the power quality issues in the grid. The main objective of the proposed work is to develop a DVR integrated with a 23-level multilevel inverter to enhance the power quality. In addition, an improved INC-MPPT technique is designed for the boost converter for maximum energy extraction from the solar PV modules. Despite numerous benefits of multilevel inverters, there exist several reliability challenges such as fewer component counts and reduced THD. The suggested topology can able to generate 23 levels of output voltage with asymmetrical DC sources. The MLI has several advantages such as a reduction in the overall component count, cost and size of the inverter. Additionally, a detailed mathematical analysis is presented for the rotating dq reference frame control. The dynamic performance of the DVR is evaluated with a balanced load and implemented experimentally. Simulation results of the proposed system are carried out using MATLAB/Simulink. The proposed system is implemented using a dSPACE controller with a laboratory hardware prototype and OPAL-RT real-time simulator setup as well. The results show that the design of the proposed system is more effective at compensating for voltage sag and improves the power quality significantly. The THD obtained at the grid side is lower, which is under IEEE standards.

**INDEX TERMS** Enhanced INC MPPT technique, Photovoltaic array, Dynamic voltage restorer, Power quality, multilevel inverter.

| ABBREVIATIO                                                                                  | ONS AND NOMENCLATURE                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VSI<br>NLC                                                                                                                                                                                        | : Voltage Source Inverter<br>: Nearest Level Control                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPD<br>DVR<br>PQ<br>RES<br>INC MPPT<br>EINC<br>MLI<br>THD<br>MV<br>MBV<br>TSV<br>SIMO<br>PSC | <ul> <li>: Custom Power Devices</li> <li>: Dynamic Voltage Restorer</li> <li>: Power Quality</li> <li>: Renewable Energy Sources</li> <li>: Incremental Conductance MPPT</li> <li>: Enhanced Incremental Conductance</li> <li>: Multilevel Inverter</li> <li>: Total Harmonic Distortion</li> <li>: Medium Voltage</li> <li>: Maximum Blocking Voltage</li> <li>: Total Standing Voltage</li> <li>: Single-Input Multi-Output</li> <li>: Pre-Sag Compensation</li> </ul> | $\begin{array}{c} N_{DC} \\ N_{Lev} \\ N_{SW} \\ N_{GDK} \\ V_T \\ \gamma \\ I_o \\ T_c \\ \boldsymbol{\beta} \\ \boldsymbol{G}_n \\ \boldsymbol{\alpha} \\ f_s \\ \boldsymbol{\phi} \end{array}$ | <ul> <li>Number of DC sources</li> <li>Number of Levels</li> <li>Number of Switches</li> <li>Number of Gate Driver Circuits</li> <li>Thermal Voltage</li> <li>Ideality Constant</li> <li>Saturation Current</li> <li>Cell Temperature</li> <li>Coefficient of Temperature</li> <li>Normal Value of Irradiation</li> <li>Duty Ratio</li> <li>switching frequency</li> <li>phase angle</li> </ul> |

In the smart era, microprocessor-controlled devices, or digital, electronic, and non-linear devices, are extensively used in all sectors of the industry. Nearly all of these devices are sensitive to electrical supply disruptions at any minute and cannot be operated properly. Problems that happen because of inadequate power quality are data errors, automatic resets, memory loss, UPS alarms, equipment failure, software corruption, circuit board failure, power supply problems, and overheating of electrical distribution systems. Considering these realities, PQ has become progressively more critical [1]. The use of sensitive loads such as diagnostic apparatus in health centers, educational institutions, detention centers, etc. over several years has been fourfold, which has led to a concern with the quality of power of sensitive loads [2]. The essential power quality issues include voltage swells, sags, harmonics, transients, flickers, fluctuations, and interruptions [3]. The sensitive and critical loads must prevent these issues in terms of power quality and voltage disturbances. In this regard, a wide range of solutions has been introduced, including the best and most efficient solution for the compensation and mitigation of voltage disturbances known as Custom Power Devices (CPDs). The DVR is the best CPD since it has low cost, is small in size, and can respond quickly to voltage disturbances [4], [5].

In grid-connected networks, dynamic voltage restorers (DVR) play a significant role in minimizing voltage disruptions. The grid voltage changes are controlled in grid systems by an energy-efficient photovoltaic (PV)-based DVR with a proportional controller and a new boost converter [6]. Renewable energy sources, as well as DC-DC converters in various topologies accessible today, are very essential for energizing electronics [7]. PV integration helps to generate clean, renewable energy while also lowering pollution levels. It can support important loads in the event of a grid outage, boosting reliability while simultaneously addressing energy issues. Furthermore, integrating PV and DVR while fulfilling energy demands reduces harmonics, voltage dips, and improves power factor.

In many industrial applications, MLIs have found their extensive influence such as UPFC, drives with high power and medium voltage, DSTATCOM, electric vehicles (EV), active power filters, DVR, micro-grid, grid integrated or stand-alone PV systems, and other fields [8]. Half-bridge inverter [9] and H-Bridge (full-Bridge) inverter [10] are familiar inverter topologies in single-phase DVR. Besides that numerous multilevel inverters, matrix converters, and Impedance-fed inverters [11] are used for both single and three-phase DVRs. AC-AC converter-based DVRs [12] are used to enhance the power quality in the absence of a dc-link capacitor. However,

during voltage sag AC-AC converters draw huge current from the grid. Thus, these are not suitable for long-duration voltage sag mitigation in weak grids. For deep voltage sag, Z-source converter-based DVR with less dc-link voltage was presented [13], though it needs storage as well as a risk of shoot-through. Typical three-phase DVR inverter topologies include the fullbridge, four-leg six-switch, and six-switch split capacitor configurations.

However for higher power voltage source inverters with two-level are not suitable because the switches will block large voltage, and more dv/dt creates electromagnetic interference to overcome these problems multilevel inverter (MLI) is the best solution. The benefits of MLIs are lower output voltage step, high power quality, fewer switching losses, minimum harmonics, and better electromagnetic compatibility. Capacitor voltage balancing is difficult when the voltage level increases in the case of diode-clamped MLI, hence these are restricted to three levels. Even though most of the industries are used three-level NPC Inverter. Flying Capacitor MLI requires more dc capacitors for higher voltage levels. However, there is flexibility to set the switching combinations and feasible for DC capacitor voltage balance [14]. Due to its modularity characteristic, CHB MLI topology becomes more reliable and popular. However, each bridge needs an isolated DC source and for higher levels, the requirement for switches also increases [15]. Hybrid topologies, most of which are developed from conventional topologies, have been proposed by researchers as a cost-effective means of addressing power quality issues and achieving high grid code standards [8]. Analysis and comparison of the 49-level modular asymmetrical 49-level inverter were proposed in [16].

The authors in [17] Presented a new DVR topology based on a buck-boost ac/ac converter. It contains an inductor, capacitor, and five switches, and the most prominent characteristic of the topology is the lack of an injection transformer, which allows for a direct connection to the grid without the use of storage devices. As a result, this topology has less physical volume, mass, and cost than traditional topologies. A DVR with a cascaded H-Bridge multilevel converter [15] was connected directly to the MV network without the use of an injection transformer. The voltage restoration is achieved by the capacitors as energy storage using the zero active power compensation technique.

DVR with five-level reduced power components TCHB inverter [18] was used to mitigate the voltage sag using two voltage compensation schemes. In [19] proposed an S4L inverter-based DVR with a single DC power source and reduced switch count, thus it is cost-effective, furthermore, it generates seven levels, which significantly supports in reduction of the system harmonic problem. Interline DVR with CHB multilevel inverter was proposed in [20] to mitigate the voltage sag with better THD. An adjustable dc-link connected MLI-based DVR [21] is suitable for compensation of both long and short period sag. DVR with an open-end winding transformer having reduced inverter loss and lower

harmonics was proposed in [22]. Cascaded OEW transformerbased DVR was reported in [23] with better voltage levels, and reduced THD even though it does not require extra clamping diodes. T- type MLI-based DVR was proposed for medium and high-power applications [24]. A new asymmetrical multilevel inverter that combines an E-type clamped X-type DVR with a reliable fractional-order super-twisting sliding mode control was proposed. In [25] for a definite voltage level, these topologies require a high number of switches thus, the required driver circuits, size, and cost are increased. It was suggested in [26] to use an "odd-nary" cascading asymmetric multi-level inverter, which produces staircase output at higher levels while using fewer switches. To compensate for any voltage disturbances, a novel HCMLI coupled to a photovoltaic power source is proposed as an AC-voltage synthesizer for DVR [27]. A selective harmonic feedback control strategy was proposed in [28] and is implemented in MV DVR to provide voltage harmonic compensation without affecting sag compensation. H infinity voltage controllerbased DVR proposed in [29] is effectively compensated the voltage sags in MV applications.

In this work, asymmetrical 23-level MLI is proposed to overcome all the limitations. The recommended 23-level MLI is implemented in a PV-fed DVR using a rotating dq reference frame controller. From the comparative analysis, the recommended 23-level MLI requires less component count factor and is cost-effective. The proposed PV-fed MLI-DVR efficiently minimizes the voltage sags, and swells and improves the power quality. The following are the most crucial features of the proposed topology:

• The recommended 23-level MLI uses only three DC sources and twelve switches among them seven are unidirectional switches and five bidirectional switches.

- Most switches have reduced voltage stress, allowing them to operate at medium voltages.

- The proposed PV-fed MLI-DVR efficiently minimizes the voltage sags, and swells and improves the power quality.

- The proposed PV-fed MLI-DVR harmonic profile is superior to traditional VSIDVR, and under the IEEE standard.

The remainder of the article is prepared accordingly. Section 2 describes the proposed solar PV integrated MLI-DVR. Section 3 describes the functioning and control of a PVfed MLI-DVR. The proposed solar PV-fed MLI-DVR results were reported in Section 4 and the conclusions were made in Section 5.

### II. Solar PV Fed MLI - DVR Configuration

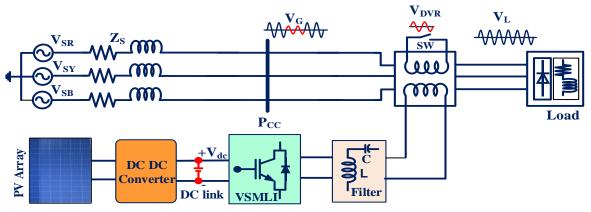

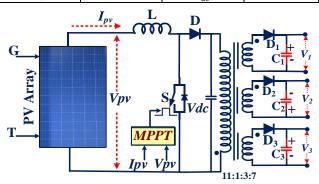

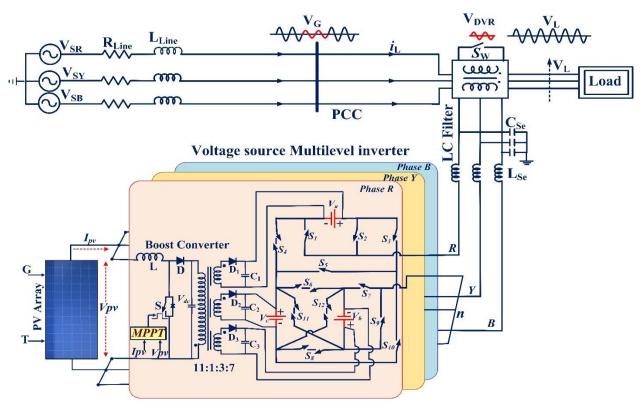

The system is configured using a 3-phase, 3-wire DVR, solar PV, a boost converter, and a load as shown in Figure. 1. DVR is the primary part, made up of a voltage source MLI, a DC link capacitor, an LC filter, and a coupling transformer. The solar PV system is the second part, which includes a PV array, an MPPT controller, and a boost converter.

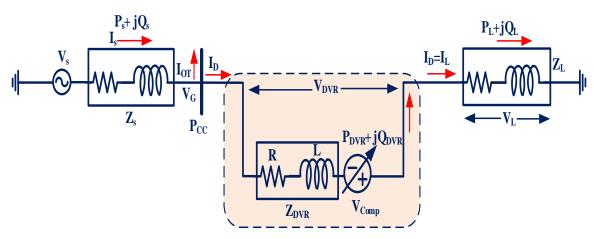

The equivalent circuit of DVR is obtained by connecting a voltage source ( $V_{Comp}$ ) in between source ( $V_S$ ) and load ( $V_L$ ) with their respective impedances,  $Z_S$  and  $Z_L$ , as shown in Figure 2. At the PCC source, current  $I_S$  is divided into  $I_L$  and  $I_{OT}$ . Where  $I_L$  is sensitive load current and  $I_{OT}$  is another load current. The voltage at PCC is represented by  $V_G$  and the voltage compensated by DVR is  $V_{DVR}$ . Resistance R and inductance L are obtained from the impedance Z of the filter and injection transformer, the values of  $R_{DVR}$  and  $X_{DVR}$  are related to  $V_{DVR}$ . The impedance of the source, load, and DVR are  $Z_S$ ,  $Z_L$ , and  $Z_{DVR}$  respectively.

Figure 1. PV fed MLI-DVR configuration

$P_S$  is real power and  $Q_S$  is reactive power of supply.  $P_L$  is real power and  $Q_L$  is the reactive power of the load.  $P_{DVR}$  is real power and  $Q_{DVR}$  is reactive power supplied by the DVR. The voltage across sensitive load  $V_L$  is given by

$$V_{L}(t) = V_{G}(t) + V_{DVR}(t) + Ri_{L}(t) + L\frac{di_{L}}{dt}$$

(1)

For higher power applications, voltage source inverters with two-level are not suitable because the switches will block large voltage, more dv/dt creates electromagnetic interference, and hence recently MLIs are used in DVR configuration. The article proposed a 23-level multilevel inverter supplied by a solar PV array.

Figure 2. Equivalent model of DVR

#### A. Proposed 23-level Inverter

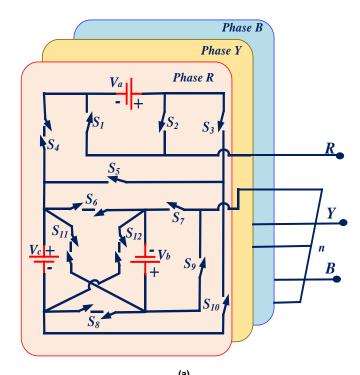

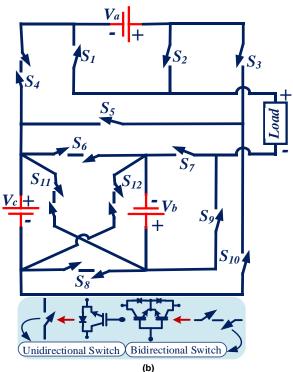

The proposed configuration comprises three dc sources namely  $V_a$ ,  $V_b$ , and  $V_c$ , and seven unidirectional switches and five bidirectional switches. Four bidirectional switches are connected in a crisscross structure [30] as depicted in Figure 3.

For asymmetric operation, the magnitudes of DC voltage sources are fixed as

$$V_a = 1V_{dc}; V_b = 3V_{dc}; V_c = 7V_{dc}$$

(2)

The required DC sources  $N_{DC}$  in terms of levels  $N_{Lev}$  is given by:

$$N_{DC}^{Asym} = \frac{(N_{Lev}-5)}{6} \tag{3}$$

(a) Figure 3. Twenty-three-level MLI topology (a) Three-phase (b) single-phase configuration

The number of switches  $N_{SW}$  required in terms of levels  $N_{Lev}$  is given by:

$$N_{SW}^{Asym} = \frac{(N_{Lev}+1)}{2} \tag{4}$$

The suggested topology uses unidirectional power switches for all of the switches. As a result, the required gate driver circuits  $N_{GDK}$  equals the number of  $N_{SW}$ , and is written as:

$$N_{GDK}^{Asym} = N_{SW}^{Asym} = \frac{(N_{Lev}+1)}{2}$$

(5)

V<sub>L, max</sub> is the maximum voltage output and is given by:

$$V_{L,max}^{Asym} = \frac{(N_{Lev}-1)}{2} \tag{6}$$

The proposed configuration produces an output voltage of 23 levels with magnitudes of zero, positive ( $+V_{dc}$  to  $+11 V_{dc}$ ), and negative ( $-V_{dc}$  to  $-11V_{dc}$ ). TABLE I shows the 23-level MLI switching states in both positive and negative levels.

Total maximum blocking voltage is one of the most important qualitative characteristics, which is referred to as the algebraic sum of the maximum voltage stress on each switch. MBV of particular switches are calculated as follows:

$$MBV_{S7} = MBV_{S9} = V_b = 3V_{dc}$$

$$MBV_{S5} = MBV_{S10} = V_c = 7V_{dc}$$

$$MBV_{S4} = \frac{1}{2}(V_c + V_a) = 4V_{dc}.$$

$$MBV_{S6} = MBV_{S11} = MBV_{S8} = MBV_{S12} = \frac{1}{2}(V_c + V_b) = 5V_{dc}.$$

$$MBV_{S1} = MBV_{S2} = MBV_{S3} = V_a = 1V_{dd}$$

| TABLE I                                      |

|----------------------------------------------|

| SWITCHING CONDITIONS OF THE PROPOSED THE MLI |

|                |                |    |       |                |       |    | 3              | VIIC |             | CON |             | INS OF TH          |    | RUP            | USE |      |       |                |     |                |                |             |     |             |

|----------------|----------------|----|-------|----------------|-------|----|----------------|------|-------------|-----|-------------|--------------------|----|----------------|-----|------|-------|----------------|-----|----------------|----------------|-------------|-----|-------------|

|                |                | Po | sitiv | e lev          | vels  |    |                |      |             |     |             | Output             |    |                | 1   | Nega | ative | e lev          | els |                |                |             |     |             |

| S <sub>1</sub> | S <sub>2</sub> | S₃ | S4    | S <sub>5</sub> | $S_6$ | S7 | S <sub>8</sub> | S9   | <b>S</b> 10 | S11 | <b>S</b> 12 | Voltage<br>(Volts) | S₁ | S <sub>2</sub> | S₃  | S4   | S₅    | S <sub>6</sub> | S7  | S <sub>8</sub> | S <sub>9</sub> | <b>S</b> 10 | S11 | <b>S</b> 12 |

| 0              | 1              | 0  | 1     | 0              | 0     | 1  | 1              | 0    | 0           | 0   | 0           | $11V_{\text{dc}}$  | 1  | 0              | 1   | 0    | 0     | 1              | 0   | 0              | 1              | 1           | 0   | 0           |

| 1              | 0              | 0  | 1     | 0              | 0     | 1  | 1              | 0    | 0           | 0   | 0           | $10V_{dc}$         | 0  | 1              | 1   | 0    | 0     | 1              | 0   | 0              | 1              | 1           | 0   | 0           |

| 1              | 0              | 1  | 0     | 1              | 0     | 1  | 1              | 0    | 0           | 0   | 0           | $9V_{dc}$          | 1  | 0              | 1   | 0    | 1     | 0              | 1   | 1              | 0              | 0           | 0   | 0           |

| 0              | 1              | 0  | 1     | 0              | 0     | 0  | 1              | 1    | 0           | 0   | 0           | $8V_{dc}$          | 1  | 0              | 1   | 0    | 0     | 1              | 1   | 0              | 0              | 1           | 0   | 0           |

| 1              | 0              | 0  | 1     | 0              | 0     | 0  | 1              | 1    | 0           | 0   | 0           | 7V <sub>dc</sub>   | 0  | 1              | 1   | 0    | 0     | 1              | 1   | 0              | 0              | 1           | 0   | 0           |

| 1              | 0              | 1  | 0     | 1              | 0     | 0  | 1              | 1    | 0           | 0   | 0           | $6V_{dc}$          | 1  | 0              | 1   | 0    | 1     | 0              | 0   | 1              | 1              | 0           | 0   | 0           |

| 0              | 1              | 0  | 1     | 0              | 0     | 0  | 0              | 1    | 0           | 0   | 1           | $5V_{dc}$          | 1  | 0              | 1   | 0    | 0     | 0              | 1   | 0              | 0              | 1           | 1   | 0           |

| 0              | 1              | 0  | 1     | 0              | 0     | 1  | 0              | 0    | 0           | 1   | 0           | $4V_{dc}$          | 1  | 0              | 1   | 0    | 1     | 1              | 0   | 0              | 1              | 0           | 0   | 0           |

| 1              | 0              | 0  | 1     | 0              | 0     | 1  | 0              | 0    | 0           | 1   | 0           | $3V_{dc}$          | 1  | 0              | 0   | 1    | 0     | 1              | 0   | 0              | 1              | 0           | 0   | 0           |

| 1              | 0              | 1  | 0     | 1              | 0     | 1  | 0              | 0    | 0           | 1   | 0           | $2V_{dc}$          | 0  | 1              | 0   | 1    | 0     | 1              | 0   | 0              | 1              | 0           | 0   | 0           |

| 0              | 1              | 0  | 1     | 0              | 1     | 1  | 0              | 0    | 0           | 0   | 0           | 1V <sub>dc</sub>   | 1  | 0              | 1   | 0    | 0     | 0              | 0   | 1              | 1              | 1           | 0   | 0           |

| 1              | 0              | 0  | 1     | 0              | 1     | 1  | 0              | 0    | 0           | 0   | 0           | $0V_{dc}$          | 1  | 0              | 0   | 1    | 0     | 1              | 1   | 0              | 0              | 0           | 0   | 0           |

TABLE II SWITCHING CONDITIONS OF THE PROPOSED THE MLI

|                 |                                                                                                                  | ITCHING CONDITION                                  | S OF THE PROPOSED THE MILL                                                                                             |                                   |                  |                              |

|-----------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|------------------------------|

| Levels          | Current conducting path                                                                                          | Active sources                                     | Stress on switches                                                                                                     | Maximum Stress<br>across switches |                  | Output<br>Voltage<br>(Volts) |

| L <sub>1</sub>  | $V_{c}-S_{4}-V_{a}-S_{2}-L-S_{7}-V_{b}-S_{8}-V_{c}$                                                              | $V_c + V_a + V_b$                                  | $S_{1,} S_{6,} S_{9,} S_{11,} S_{12}$                                                                                  | $S_6 = S_{11} = S_{12}$           | $5V_{dc}$        | +11V <sub>dc</sub>           |

| L <sub>2</sub>  | $V_{c}-S_{4}-S_{1}-L-S_{7}-V_{b}-S_{8}-V_{c}$                                                                    | V <sub>c</sub> +V <sub>b</sub>                     | $S_{6}, S_{9}, S_{11}, S_{12}$                                                                                         | $S_6 = S_{11} = S_{12}$           | $5V_{dc}$        | +10V <sub>dc</sub>           |

| L <sub>3</sub>  | $V_{c}$ - $S_{5}$ - $S_{3}$ - $V_{a}$ - $S_{1}$ - $L$ - $S_{7}$ - $V_{b}$ - $S_{8}$ - $V_{c}$                    | V <sub>c</sub> +V <sub>b</sub> -V <sub>a</sub>     | $S_{2,} S_{4,} S_{6,} S_{9,} S_{10,} S_{11,} S_{12}$                                                                   | S <sub>10</sub>                   | 7V <sub>dc</sub> | +9V <sub>dc</sub>            |

| $L_4$           | $V_{c}-S_{4}-V_{a}-S_{2}-L-S_{9}-S_{8}-V_{c}$                                                                    | V <sub>c</sub> +V <sub>a</sub>                     | S <sub>1</sub> , S <sub>11</sub>                                                                                       | S <sub>11</sub>                   | $5V_{dc}$        | +8V <sub>dc</sub>            |

| $L_5$           | $V_{c}-S_{4}-S_{1}-L-S_{9}-S_{8}-V_{c}$                                                                          | Vc                                                 | S <sub>11</sub>                                                                                                        | S <sub>11</sub>                   | $5V_{dc}$        | +7V <sub>dc</sub>            |

| $L_6$           | $V_{c}-S_{5}-S_{3}-V_{a}-S_{1}-L-S_{9}-S_{8}-V_{c}$                                                              | $V_{c}-V_{a}$                                      | S <sub>2</sub> , S <sub>4</sub> , S <sub>10</sub> , S <sub>11</sub> , S <sub>12</sub>                                  | $S_{11} = S_{12}$                 | $5V_{dc}$        | +6V <sub>dc</sub>            |

| L <sub>7</sub>  | $V_{c}-S_{4}-V_{a}-S_{2}-L-S_{9}-V_{b}-S_{12}-V_{c}$                                                             | $V_{c}-V_{b}+V_{a}$                                | S <sub>1</sub> ,S <sub>6</sub> , S <sub>7</sub> , S <sub>8</sub> ,S <sub>11</sub>                                      | $S_6 = S_8 = S_{11}$              | $5V_{dc}$        | $+5V_{dc}$                   |

| L <sub>8</sub>  | V <sub>b</sub> -S <sub>11</sub> -S <sub>4</sub> V <sub>a</sub> -S <sub>2</sub> -L-S <sub>7</sub> -V <sub>b</sub> | $V_b + V_a$                                        | S <sub>1</sub> ,S <sub>6</sub> , S <sub>9</sub>                                                                        | S <sub>9</sub>                    | 3V <sub>dc</sub> | +4V <sub>dc</sub>            |

| L <sub>9</sub>  | $V_{b}$ - $S_{11}$ - $S_{4}$ - $S_{1}$ - $L$ - $S_{7}$ - $V_{b}$                                                 | V <sub>b</sub>                                     | S <sub>6,</sub> S <sub>9</sub>                                                                                         | $S_6 = S_9$                       | 3V <sub>dc</sub> | +3V <sub>dc</sub>            |

| L <sub>10</sub> | $V_{b}$ - $S_{11}$ - $S_{5}$ - $S_{3}$ - $V_{a}$ - $S_{1}$ - $L$ - $S_{7}$ - $V_{b}$                             | $V_{b}$ - $V_{a}$                                  | $S_{2}, S_{4}, S_{6}, S_{9}$                                                                                           | S <sub>9</sub>                    | 3V <sub>dc</sub> | +2V <sub>dc</sub>            |

| L <sub>11</sub> | $V_{a}-S_{2}-L-S_{7}-S_{6}-S_{4}-V_{a}$                                                                          | Va                                                 | S <sub>1</sub>                                                                                                         | S <sub>1</sub>                    | 1V <sub>dc</sub> | +1V <sub>dc</sub>            |

| L <sub>12</sub> | L-S7-S6-S4-S1-L                                                                                                  | -                                                  | -                                                                                                                      | -                                 | 0                | 0V <sub>dc</sub>             |

| L <sub>13</sub> | $V_a$ - $S_3$ - $S_{10}$ - $S_8$ - $S_9$ -L- $S_1$ - $V_a$                                                       | -(Va)                                              | S <sub>2</sub>                                                                                                         | <b>S</b> <sub>2</sub>             | $1V_{dc}$        | -1V <sub>dc</sub>            |

| L <sub>14</sub> | $V_{b}-S_{9}-L-S_{2}-V_{a}-S_{4}-S_{6}-V_{b}$                                                                    | -(V <sub>b</sub> -V <sub>a</sub> )                 | S <sub>1</sub> , S <sub>7</sub>                                                                                        | S <sub>7</sub>                    | 3V <sub>dc</sub> | -2V <sub>dc</sub>            |

| L <sub>15</sub> | $V_{b}-S_{9}-L-S_{1}-S_{4}-S_{6}-V_{b}$                                                                          | -(V <sub>b</sub> )                                 | S <sub>7</sub>                                                                                                         | S <sub>7</sub>                    | 3V <sub>dc</sub> | -3V <sub>dc</sub>            |

| L <sub>16</sub> | $V_{b}-S_{9}-L-S_{1}-V_{a}-S_{3}-S_{5}-S_{6}-V_{b}$                                                              | -(V <sub>b</sub> +V <sub>a</sub> )                 | $S_{2}, S_{4}, S_{7}$                                                                                                  | S <sub>4</sub>                    | 4V <sub>dc</sub> | -4V <sub>dc</sub>            |

| L <sub>17</sub> | $V_c - S_{11} - V_b - S_7 - L - S_1 - V_a - S_3 - S_{10} - V_c$                                                  | -(V <sub>c</sub> -V <sub>b</sub> +V <sub>a</sub> ) | S <sub>2</sub> , S <sub>4</sub> , S <sub>5</sub> , S <sub>6</sub> , S <sub>8</sub> , S <sub>9</sub> , S <sub>12</sub>  | S <sub>5</sub>                    | 7V <sub>dc</sub> | -5V <sub>dc</sub>            |

| L <sub>18</sub> | Va-S3-S5-Vc-S8-S9-L-S1-Va                                                                                        | -(V <sub>c</sub> -V <sub>a</sub> )                 | S <sub>2</sub> , S <sub>4</sub> , S <sub>10</sub>                                                                      | S <sub>10</sub>                   | 7V <sub>dc</sub> | -6V <sub>dc</sub>            |

| L <sub>19</sub> | $V_c$ - $S_6$ - $S_7$ - $L$ - $S_2$ - $S_3$ - $S_{10}$ - $V_c$                                                   | -(V <sub>c</sub> )                                 | S <sub>5,</sub> S <sub>12</sub>                                                                                        | S <sub>5</sub>                    | 7V <sub>dc</sub> | -7V <sub>dc</sub>            |

| L <sub>20</sub> | $V_{c}$ - $S_{6}$ - $S_{7}$ - $L$ - $S_{1}$ - $V_{a}$ - $S_{3}$ - $S_{10}$ - $V_{c}$                             | -(V <sub>c</sub> +V <sub>a</sub> )                 | $S_{2,} S_{4,} S_{5,} S_{12}$                                                                                          | S <sub>5</sub>                    | 7V <sub>dc</sub> | -8V <sub>dc</sub>            |

| L <sub>21</sub> | $V_a$ - $S_3$ - $S_5$ - $V_c$ - $S_8$ - $V_b$ - $S_7$ -L- $S_1$ - $V_a$                                          | -(V <sub>c</sub> -V <sub>a</sub> +V <sub>b</sub> ) | $S_{2,} S_{4,} S_{6,} S_{9,} S_{10,} S_{11,} S_{12}$                                                                   | S <sub>10</sub>                   | 7V <sub>dc</sub> | -9V <sub>dc</sub>            |

| L <sub>22</sub> | $V_{c}$ - $S_{6}$ - $V_{b}$ - $S_{9}$ - $L$ - $S_{2}$ - $S_{3}$ - $S_{10}$ - $V_{c}$                             | $-(V_c+V_b)$                                       | S <sub>5</sub> , S <sub>7</sub> , S <sub>8</sub> ,S <sub>11</sub> , S <sub>12</sub>                                    | S <sub>5</sub>                    | 7V <sub>dc</sub> | -10V <sub>dc</sub>           |

| L <sub>23</sub> | $V_{c}-S_{6}-V_{b}-S_{9}-L-S_{1}-V_{a}-S_{3}-S_{10}-V_{c}$                                                       | -(V <sub>c</sub> +V <sub>b</sub> +V <sub>a</sub> ) | S <sub>2</sub> , S <sub>4</sub> , S <sub>5</sub> , S <sub>7</sub> , S <sub>8</sub> , S <sub>11</sub> , S <sub>12</sub> | S₅                                | 7V <sub>dc</sub> | -11V <sub>dc</sub>           |

The term TSV is stated as the algebraic sum of MBV across individual switches and is expressed in equation 7, equation 8 provides the  $TSV_{PU}$ .

$$TSV = MBV_{S1} + MBV_{S2} + MBV_{S3} + - - + MBV_{Sn}$$

(7)

$$TSV_{PU} = \frac{TSV}{V_{L,max}}$$

(8)

For the proposed topology  $TSV^{Prop}$  is calculated as

$TSV_{PU}^{Prop} = \frac{47V_{dc}}{11V_{dc}} = 4.27$

$$TSV^{Prop} = 4[5V_{dc}] + 2[3V_{dc}] + 2[7V_{dc}] + 3[V_{dc}] + 4V_{dc}$$

$$TSV^{Prop} = 47V_{dc}$$

(9)

And

As a consequence, the recommended MLI topology optimizes the utilization of DC sources with minimum TSV and switches, hence the volume and price will be reduced.

TABLE II shows the current path to the load, as well as the maximum blocking voltage (MBV) and the voltage stress on the switches. It has been found that some operating voltage levels include redundant switches.

A comparison is made between the recommended topology and other recent topologies to evaluate the benefits and capabilities of the recommended 23-level MLI topology. Table III shows a comparison of the required driver circuits, DC sources, switches, component count factor (CCF), the maximum number of conducting devices per level,  $TSV_{PU}$ , and the cost factor [31] for each level.

| <i>Topologies</i> | Qu               | COMPARISONS OF THE PROPOSED 23-LEVEL M<br>Quantitative analysis |                 |                  |     |                  |      | Qualitative analysis |                   |                             |                        |  |  |

|-------------------|------------------|-----------------------------------------------------------------|-----------------|------------------|-----|------------------|------|----------------------|-------------------|-----------------------------|------------------------|--|--|

| Ref               | N <sub>lev</sub> | N <sub>DC</sub>                                                 | N <sub>SW</sub> | N <sub>GDK</sub> | MCD | N <sub>Var</sub> | CCF  | %THD                 | TSV <sub>PU</sub> |                             | N <sub>Lev</sub>       |  |  |

| [32]              | 23               | 6                                                               | 12              | 12               | 6   | 0                | 1.30 | 2.59                 | 5.81              | $\frac{\alpha = 0.3}{1.43}$ | $\alpha = 1.5$<br>1.68 |  |  |

|                   |                  | -                                                               |                 |                  | -   | Ū                |      |                      |                   |                             |                        |  |  |

| [33]              | 23               | 5                                                               | 10              | 10               | 4   | 2                | 1.17 | -                    | 6.09              | 1.39                        | 1.65                   |  |  |

| [34]              | 23               | 5                                                               | 14              | 14               | 7   | 0                | 1.43 | 5.47                 | -                 | -                           | -                      |  |  |

| [35]              | 23               | 5                                                               | 12              | 9                | 3   | 5                | 1.34 | 4.17                 | -                 | -                           | -                      |  |  |

| [36]              | 23               | 5                                                               | 12              | 12               | 4   | 0                | 1.26 | 3.6                  | 4.4               | 1.35                        | 1.54                   |  |  |

| [37]              | 23               | 3                                                               | 12              | 12               | 5   | 0                | 1.17 | -                    | 5.27              | 1.28                        | 1.52                   |  |  |

| Proposed          | 23               | 3                                                               | 12              | 12               | 7   | 0                | 1.17 | 3.23                 | 4.27              | 1.27                        | 1.45                   |  |  |

## TABLE III IPARISONS OF THE PROPOSED 23-LEVEL MLI WITH RECENT TOPOLOG

(10)

#### B. Analysis of Boost Converters for Solar PV.

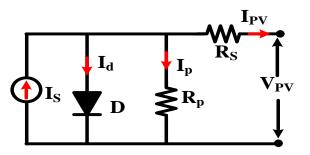

The current and voltage of the PV array are, controlled by temperature, irradiance, and the number of parallel and series strings hence, it is essential to pick the correct PV panel. Trina Solar TSM-200 DC/DA01A panel with 3 parallel and 2 series modules per string is selected. An ideal equivalent model of solar PV is shown in Figure 4. D is the diode and  $R_P$ ,  $R_S$  are the resistances of parallel  $n_p$  and series  $n_s$  connected cells, respectively.

From an ideal PV circuit, the diode current is

$$i_d = I_0 \left( e^{\frac{V_D}{\gamma V_T}} - 1 \right) \tag{11}$$

Where  $\gamma$  is the ideality constant, saturation current is I<sub>o</sub> and thermal voltage V<sub>T</sub> =  $(\frac{kT_c}{q})$  is depends on the charge of electron q, cell temperature T<sub>c</sub>, and Boltzmann's constant k.

Output power  $P_{PV} = V_{PV} * I_{PV}$  (12)

Output current is

$$I_{PV} = I_S - I_d - I_p = I_S - I_0 \left( e^{\frac{V_D}{\gamma V_T}} - 1 \right) - I_p \quad (13)$$

$$I_{PV} = n_p I_s - n_p I_0 \left( e^{\left(\frac{1}{\gamma V_T}\right) \left(\frac{V_{PV} + R_s I_{PV}}{n_s} + \frac{1}{n_p}\right)} - 1 \right) - \frac{n_p}{R_p} \left(\frac{V_{PV}}{n_s} + \frac{R_s I_{PV}}{n_p}\right)$$

(14)

Short circuit current Is

$$I_{s(T)} = I_{s(TR)}[\beta(T - T_R) + 1]$$

(15)

The values of coefficient of temperature  $\beta$ , reference temperature T<sub>R</sub>, and corresponding short circuit current I<sub>S(TR)</sub> are provided in PV datasheets.

Considering the intensity of irradiance then

$$I_{s(G)} = I_{s(Gn)} \frac{G}{G_n} \tag{16}$$

G<sub>n</sub> is the normal value of irradiation

Saturation current  $I_0$  is calculated at  $I_{PV} = 0$ , then  $I_0$  at  $T_R$  is given by

$$I_O = \frac{l_s}{\left(\frac{V_D}{e^{\overline{VV}}T - 1}\right)} \tag{17}$$

VOLUME XX, 2017

Figure 4. Equivalent model of Solar PV

The fundamental problem of employing renewable energy sources to generate electricity is low voltage output. To enhance the voltage level, the RES output is sent to a DC-DC boost converter.

The boost converter output voltage is regulated by the duty cycle of the control switch. Hence, by adjusting the switch-ON time, one can alter the output voltage. The formula used to calculate the average output voltage over the duty cycle ' $\alpha$ ' is

$$V_{dc} = V_{PV} \left(\frac{1}{1-\alpha}\right) \tag{18}$$

The value of inductor and capacitors are calculated using

$$L = \frac{V_{PV}\alpha}{(f_s * \Delta I_L)} \tag{19}$$

$$C = \frac{I_0 \alpha}{(f_s * \Delta V_{dc})} \tag{20}$$

The input current and output voltage ripple factors are  $\Delta I_L$  and  $\Delta V_{dc}$ , respectively, and the switching frequency is  $f_s$ . For a realistic estimation of inductor and capacitor values,  $\Delta I_L$  should be restricted to 30%, and  $\Delta V_{dc}$  is commonly assumed at 5%. TABLE IV lists the features of the solar PV boost converter.

| I ABLE IV                            |

|--------------------------------------|

| SPECIFICATIONS OF PV BOOST CONVERTER |

| OF ECHICATIONS OF T V BOOST CONVERTER |          |                   |         |  |  |  |

|---------------------------------------|----------|-------------------|---------|--|--|--|

| 200W P\                               | / Module | Boost converter.  |         |  |  |  |

| $P_{PV}$                              | 200W     | L                 | 1.28 mH |  |  |  |

| $I_{PV}$                              | 5.32A    | С                 | 1.31µF  |  |  |  |

| $V_{PV}$                              | 37.6V    | $V_{in} = V_{PV}$ | 112.8V  |  |  |  |

| I <sub>sc</sub>                       | 5.60A    | α                 | 0.718   |  |  |  |

| V <sub>oc</sub>                       | 46.0V    | $V_{dc}$          | 400 V   |  |  |  |

Figure 5. SIMO isolated DC-DC converter

Figure 6. Proposed solar PV-fed MLI-DVR configuration

Figure 5 shows a single-input multi-output (SIMO) circuit that receives the output of the DC-DC boost converter [38]. Boost converter output is fed into the primary winding of a transformer and secondary of multi winding transformer gives three output ports with turn's ratio of 11:1:3:7. At the output terminal of each DC-DC converter output port, a diode and a capacitor are connected. The diode is positioned to prevent the capacitor's reverse current from flowing into the transformer windings. The operation of the boost converter is regulated by the MPPT controller depending on inputs such as environmental parameters (solar radiation and temperature), PV array parameters (Voc and Isc), and outputs like DC link voltage. The operational performance of traditional incremental and conductance MPPT algorithms is lower if the operating point is fluctuating around the MPP and under rapidly changing irradiance conditions. To address these issues, an enhanced INC MPPT is employed [39]. The circuit diagram of the PV-fed MLI-DVR connected to the grid is shown in Figure 6.

#### III. Operation and Control of PV-fed MLI-DVR

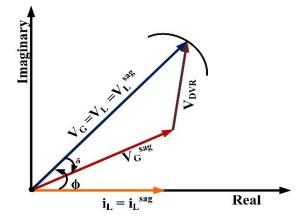

Depending on the type of load and voltage sag, the DVR compensating technique differs. This is because only a few loads respond to fluctuations in voltage magnitude, while others are sensitive to deviations in phase angle, and still, others are sensitive to both. As a result, the load characteristics dictate which control approach to employ. The pre-sag compensation (PSC) method is used to compensate for both the magnitude and phase angle of the voltage sag [40].

In this strategy load voltage is maintained with the presag voltage, therefore no voltage disturbance is sensed by the load because the load voltage is having the same magnitude and phase angle, hence it is also known as the voltage quality optimized technique. The vector representation of PSC is shown in Figure. 7. During sag, the DVR is controlled by adding more real power, which affects the rating of direct energy storage or energy received from the grid hence the requirement of energy source to supply active power will increase apart from reactive power injected by the inverter. It is acceptable for both balanced and unbalanced sensitive loads heaving phase jump or not.

#### Figure 7. Pre sag voltage injection technique for DVR

Equation 21 gives the magnitude of  $V_{DVR}$  and the phase angle of  $V_{DVR}$  is obtained from equation 22.

$$V_{DVR,p} = \sqrt{2} \sqrt{(V_L)^2 + (V_G^{Sag})^2 - (2V_L V_{G,p}^{Sag} \cos(\delta_p))}$$

(21)

Where  $V_{DVR}$  is the DVR injected voltage,  $\phi$  is the phase angle between  $V_L$  and  $I_L$ ,  $V_G^{Sag}$  is the grid voltage at sag,  $\delta$  is the corresponding angle of phase jump to  $V_G^{Sag}$ , p is the corresponding phase of the supply voltage (R, Y, or B).

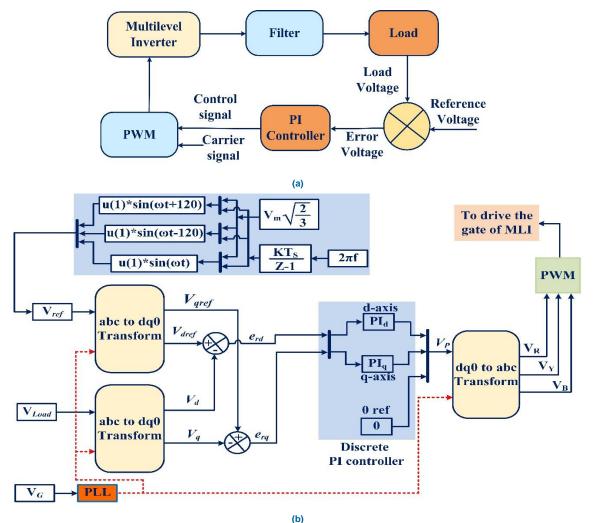

#### A. Control scheme of the DVR

A voltage disturbance duration (both start and end), phase jump, and depth depend on the type of voltage disturbance. Various methods for sensing voltage disturbances are presented in [41]. The Park transformation is utilized to transform the three-phase load voltages  $V_{L\,RYB}$  and reference voltages  $V_{ref, RYB}$  into vectorized dq0 voltage components  $V_{L,dq0}$ , and  $V_{ref,dq0}$ . The following formula is used to compute the three-phase reference voltage:

$$\begin{bmatrix} V_{R ref} \\ V_{Y ref} \\ V_{B ref} \end{bmatrix} = V_{L max} \begin{bmatrix} sin\omega t \\ sin(\omega t - 120^{0}) \\ sin(\omega t + 120^{0}) \end{bmatrix}$$

(23)

Then, using the Park transformation, it is changed from RYB to dq0 components

Once the load and reference voltages change into the dq0 frame, the error signal  $e_r$  will be obtained in terms of magnitude and phase shift of voltage, as shown in figure 8b.

$$\left|e_{r\,dq0}\right| = \sqrt{\left(V_{dref} - V_{di}\right)^{2} + \left(V_{qref} - V_{qi}\right)^{2} + \left(V_{0ref} - V_{0i}\right)^{2}}$$

(25)

The change in the dq0 components will result from variations in magnitude and phase shift of voltage. Changes in the state of the supply are detected and responded to swiftly by the suggested control. In this work, the synchronous reference frame the phase-locked loop (PLL) is used as a synchronization method. It maintains frequency and phase synchronization between the controller output signal and a reference input signal.

The DVR control presented in this article is a PI controller driven by an error signal, resulting in a low level of complexity. The controller function is to reduce the error signal on the distribution grid as much as possible. In the time domain, the contribution signal of the PWM in dq0 frame for the PI controller is Vp, given as

$$V_{P \, dq0} = K_P e_{r \, dq0} + K_i \int_0^1 e_{r \, dq0} dt$$

(26)

Finally, the output of PI control is fed back into abc frame to regulate the PWM that generates the VSI gating pulses, given as

According to Equation (25), the error signals  $e_r$  of dq voltages are given to the PI controller, as

$$e_{rd}(t) = V_{dref} - V_d \tag{28}$$

$$e_{rq}(t) = V_{qref} - V_q \tag{39}$$

The error  $e_{rd}$  signal is fed into the D-axis of the PI controller, whereas the error  $e_{rq}$  is fed into the Q-axis of the PI controller, as shown in Figure 8. The signal provided to the controller is the change in voltage between  $V_{ref}$  and  $V_d$ . The error equation is given as

$$e_r = V_{ref} - V_d \tag{30}$$

Figure 8. DVR PI controller

VOLUME XX, 2017

Figure 8 represents the control strategy of the proposed MLI-based DVR. A rotating dq reference frame controller is used to generate the reference signal shown in Figure 8b. The error signal and error rate drives the PI controller, it analyzes the input and produces controller output. The controller output is given as a reference voltage to the PWM. The pulses generated by the PWM pulse generator control the operation of the multilevel inverter. The systematic procedure of the control system is presented in Figure 8a. The magnitude and phase angle of the reference voltage is produced by using the pre-sag compensation technique and injected through the multilevel inverter. This information is computed by using the synchronous reference frame Phase-Locked Loops (PLL). The parameters of PI controller are obtained as  $K_{pd} = 7.401$ ,  $K_{id} =$ 189.014 in case of D-axis,  $K_{pq} = 69.31$ ,  $K_{iq} = 192.412$  in case of Q-axis.

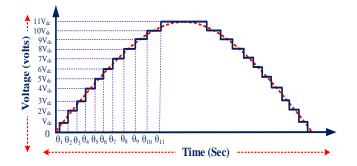

#### B. Pulse width modulation

The nearest level control (NLC) or round method [20] is a low switching frequency control technique used to generate the nearest voltage level by converting it to the desired reference output voltage. Using the switching table, the closest level of voltage to the reference voltage is chosen by selecting the switching combination that corresponds to that level as depicted in Figure 9. The nearest output voltage level for voltage reference  $V_{ref}$  and the modulation index 'm' is

$$V_{ref} = m\left(\frac{N-1}{2}\right) V sin(\omega t) = V_m sin(\omega t)$$

(31)

$$m = \frac{V_m}{\left(\frac{N-1}{2}\right)V} \tag{32}$$

$$V_L = V \ round \ \left(\frac{V_{ref}}{V}\right) \tag{33}$$

The limits of the reference voltage and active switches of the selected voltage level of the NLC technique are represented in Table V. The switching angles are calculated from equation (34) and tabulated in Table VI

$$\theta = \sin^{-1} \left( \frac{x - 0.5}{\frac{N-1}{2}} \right) \tag{34}$$

|                                 |                   | 1 P                                                                                                  | ABLE V                             |                    |                                                                                                       |  |  |  |

|---------------------------------|-------------------|------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| LIMITS OF THE                   | REFERENCE V       | OLTAGE AND ACTIVE SWITCHE                                                                            | S OF THE SELECTED VOLTAGE          | ELEVEL OF PV BO    | DOST CONVERTER                                                                                        |  |  |  |

|                                 | Positive level    | S                                                                                                    | Negative levels                    |                    |                                                                                                       |  |  |  |

| Limits of the reference voltage | Level selected    | Active switches                                                                                      | Limits of the reference<br>voltage | Level<br>selected  | Active switches                                                                                       |  |  |  |

| $0 \le V_{ref} < 0.5$           | $0V_{dc}$         | $S_{2,} S_{3,} S_{6,} S_{8,} S_{9,} S_{11}$                                                          | $-0.5 \le V_{ref} < 0$             | 0V <sub>dc</sub>   | S <sub>1</sub> , S <sub>4</sub> , S <sub>5</sub> , S <sub>7</sub> , S <sub>10</sub> , S <sub>12</sub> |  |  |  |

| $0.5 \leq V_{ref} < 1.5$        | $1V_{dc}$         | S2, S4, S5, S7, S9, S11                                                                              | -1.5 ≤ V <sub>ref</sub> <-0.5      | -1V <sub>dc</sub>  | S1, S3, S6, S8, S10, S12                                                                              |  |  |  |

| $1.5 \leq V_{ref} < 2.5$        | $2V_{dc}$         | S <sub>1</sub> , S <sub>3</sub> , S <sub>6</sub> , S <sub>7</sub> , S <sub>9</sub> , S <sub>11</sub> | $-2.5 \le V_{ref} < -1.5$          | -2V <sub>dc</sub>  | $S_{2,}S_{4,}S_{5,}S_{8,}S_{10,}S_{12}$                                                               |  |  |  |

| $2.5 \leq V_{ref} < 3.5$        | 3V <sub>dc</sub>  | S2, S3, S6, S7, S9, S11                                                                              | $-3.5 \le V_{ref} < -2.5$          | -3V <sub>dc</sub>  | S1, S4, S5, S8, S10, S12                                                                              |  |  |  |

| $3.5 \leq V_{ref} < 4.5$        | 4V <sub>dc</sub>  | S2, S4, S6, S7, S9, S11                                                                              | $-4.5 \le V_{ref} < -3.5$          | -4V <sub>dc</sub>  | S1, S3, S5, S8, S10, S12                                                                              |  |  |  |

| $4.5 \leq V_{ref} < 5.5$        | 5V <sub>dc</sub>  | S2, S4, S5, S8, S9, S12                                                                              | $-5.5 \le V_{ref} < -4.5$          | -5V <sub>dc</sub>  | S1, S3, S6, S7, S10, S11                                                                              |  |  |  |

| $5.5 \le V_{ref} < 6.5$         | 6V <sub>dc</sub>  | $S_{1,} S_{3,} S_{6,} S_{8,} S_{9,} S_{12}$                                                          | $-6.5 \le V_{ref} < -5.5$          | -6V <sub>dc</sub>  | $S_{2,}S_{4,}S_{5,}S_{7,}S_{10,}S_{11}$                                                               |  |  |  |

| $6.5 \leq V_{ref} < 7.5$        | 7V <sub>dc</sub>  | S2, S3, S5, S7, S9, S12                                                                              | $-7.5 \le V_{ref} < -6.5$          | -7V <sub>dc</sub>  | $S_{1}, S_{4}, S_{6}, S_{8}, S_{10}, S_{11}$                                                          |  |  |  |

| $7.5 \le V_{ref} < 8.5$         | 8V <sub>dc</sub>  | S <sub>2</sub> , S <sub>4</sub> , S <sub>5</sub> , S <sub>7</sub> , S <sub>9</sub> , S <sub>12</sub> | $-8.5 \le V_{ref} < -7.5$          | -8V <sub>dc</sub>  | $S_{1,}S_{3,}S_{6,}S_{8,}S_{10,}S_{11}$                                                               |  |  |  |

| $8.5 \le V_{ref} < 9.5$         | 9V <sub>dc</sub>  | S1, S3, S6, S7, S9, S12                                                                              | $-9.5 \le V_{ref} < -8.5$          | -9V <sub>dc</sub>  | S2, S4, S5, S8, S10, S11                                                                              |  |  |  |

| $9.5 \leq V_{ref} < 10.5$       | 10V <sub>dc</sub> | S2, S3, S6, S7, S9, S12                                                                              | $-10.5 \le V_{ref} < -9.5$         | -10V <sub>dc</sub> | $S_{1}, S_{4}, S_{5},  S_{8}, S_{10}, S_{11}$                                                         |  |  |  |

| $10.5 \leq V_{ref}$             | 11V <sub>dc</sub> | S2, S4, S6, S7, S9, S12                                                                              | V <sub>ref</sub> < -10.5           | -11V <sub>dc</sub> | $S_{1,}S_{3,}S_{5,}S_{8,}S_{10,}S_{11}$                                                               |  |  |  |

TABLE V

TABLE VI

SWITCHING ANGLES AND THE CORRESPONDING VOLTAGE LEVELS

| Positive Interval                                                                         | Voltage           | Negative Interval                                                                           |

|-------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|

| $0^0 \le \theta < 2.6^\circ$ , $177.4^\circ \le \theta < 180^\circ$                       | 0V <sub>dc</sub>  | $180^{\circ} \le \theta < 182.6^{\circ}$ , $357.4^{\circ} \le \theta < 360^{\circ}$         |

| $2.6^{\circ} \le \theta < 7.83^{\circ}$ , $172.2^{\circ} \le \theta < 177.4^{\circ}$      | 1V <sub>dc</sub>  | $182.6^{\circ} \le \theta < 187.83^{\circ}$ , $352.17^{\circ} \le \theta < 357.4^{\circ}$   |

| $7.83^{\circ} \le \theta < 13.13^{\circ}$ , $166.87^{\circ} \le \theta < 172.2^{\circ}$   | 2V <sub>dc</sub>  | $187.83^{\circ} \le \theta < 193.13^{\circ}$ , $346.87^{\circ} \le \theta < 352.17^{\circ}$ |

| $13.13^{\circ} \le \theta < 18.55^{\circ}$ , $161.45^{\circ} \le \theta < 166.87^{\circ}$ | 3V <sub>dc</sub>  | $193.13^{\circ} \le \theta < 198.55^{\circ}$ , $341.45^{\circ} \le \theta < 346.87^{\circ}$ |

| $18.55^{\circ} \le \theta < 24.14^{\circ}$ , $155.86^{\circ} \le \theta < 161.45^{\circ}$ | 4V <sub>dc</sub>  | $198.55^{\circ} \le \theta < 204.14^{\circ}$ , $335.86^{\circ} \le \theta < 341.45^{\circ}$ |

| $24.14^{\circ} \le \theta < 30^{\circ}$ , $150^{\circ} \le \theta < 155.86^{\circ}$       | 5V <sub>dc</sub>  | $204.14^{\circ} \le \theta < 210^{\circ}$ , $330^{\circ} \le \theta < 335.86^{\circ}$       |

| $30^{\circ} \le \theta < 36.22^{\circ}$ , $143.78^{\circ} \le \theta < 150^{\circ}$       | 6V <sub>dc</sub>  | $210^{\circ} \le \theta < 216.22^{\circ}$ , $323.78^{\circ} \le \theta < 330^{\circ}$       |

| $36.22^{\circ} \le \theta < 42.98^{\circ}$ , $137^{\circ} \le \theta < 143.78^{\circ}$    | 7V <sub>dc</sub>  | $216.22^{\circ} \le \theta < 223^{\circ}$ , $317^{\circ} \le \theta < 323.78^{\circ}$       |

| $42.98^{\circ} \le \theta < 50.6^{\circ}$ , $129.4^{\circ} \le \theta < 137^{\circ}$      | 8V <sub>dc</sub>  | $223^{\circ} \le \theta < 230.6^{\circ}$ , $309.4^{\circ} \le \theta < 317^{\circ}$         |

| $50.6^{\circ} \le \theta < 59.72^{\circ}$ , $120.8^{\circ} \le \theta < 129.4^{\circ}$    | 9V <sub>dc</sub>  | $230.6^{\circ} \le \theta < 239.72^{\circ}$ , $300.28^{\circ} \le \theta < 309.4^{\circ}$   |

| $59.72^{\circ} \le \theta < 72.65^{\circ}$ , $107.35^{\circ} \le \theta < 120.8^{\circ}$  | 10V <sub>dc</sub> | $239.72^{\circ} \le \theta < 252.65^{\circ}$ , $287.65^{\circ} \le \theta < 300.28^{\circ}$ |

| $72.65^{\circ} \le \theta < 107.35^{\circ}$                                               | $11V_{dc}$        | $252.65^{\circ} \le \theta < 287.65^{\circ}$                                                |

Figure 9. Nearest level control technique waveform of 23 levels

#### **IV. RESULTS AND DISCUSSION**

#### A. Simulation results

The proposed multilevel inverter solar PV fed DVR is evaluated in terms of improving voltage profile. The results

are shown using the MATLAB/Simulink platform. Table VII lists the parameters of DVR.

| IABLE VII                   |                         |  |  |  |  |  |  |

|-----------------------------|-------------------------|--|--|--|--|--|--|

| DVR PARAMETERS AND RATINGS. |                         |  |  |  |  |  |  |

| Source (AC grid)            | 400V, 50 Hz             |  |  |  |  |  |  |

| DC-link voltage             | 400V                    |  |  |  |  |  |  |

| Filter                      | L=5 mH, C=80 μF, R=1.5Ω |  |  |  |  |  |  |

| Switching frequency         | 5kHz                    |  |  |  |  |  |  |

| Transformer ratio           | 1:1                     |  |  |  |  |  |  |

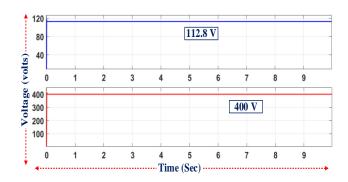

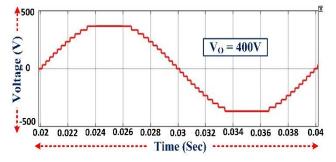

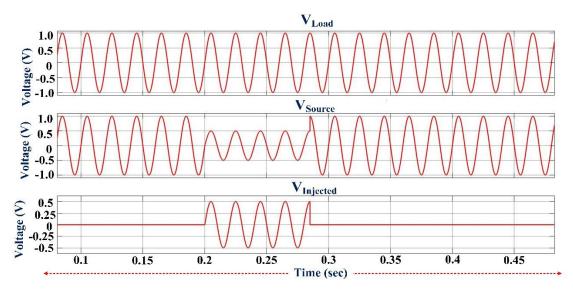

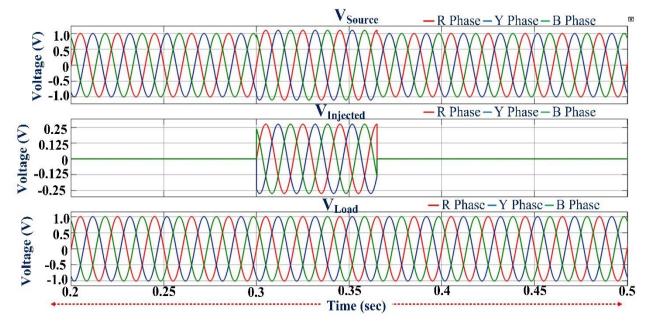

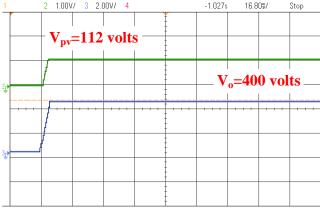

The simulation results of PV and boost converter with EINC MPPT are shown in Figure. 10. PV at MPP generates 112.8 volts and by using a boost converter it is boosted to 400 volts which are appeared at the DC link. Figure 11 represents the R phase voltage waveform of an asymmetrical 23-level MLI. Voltage sag mode is created by applying overload at time intervals ranging from 0.2 sec to 0.285 sec.

#### Figure 10. Simulation results of PV and boost converter

Figure 11. Simulation phase voltage of proposed 23-level MLI topology

Figure 12. Simulation results of Source, Injected, and Load voltages at sag condition.

VOLUME XX, 2017

Figure 13. THD at VLoad with DVR during sag mode

In this test, 0.5pu of sag is applied in comparison to load point reference voltage. The proposed DVR injects the appropriate

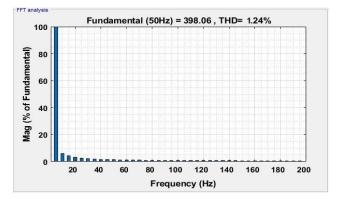

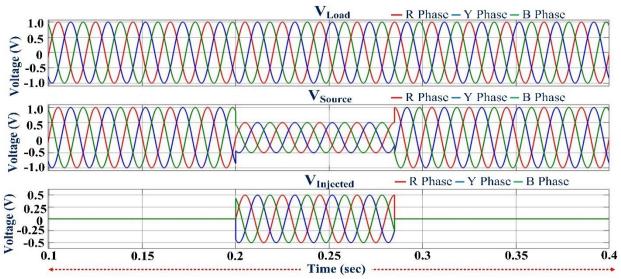

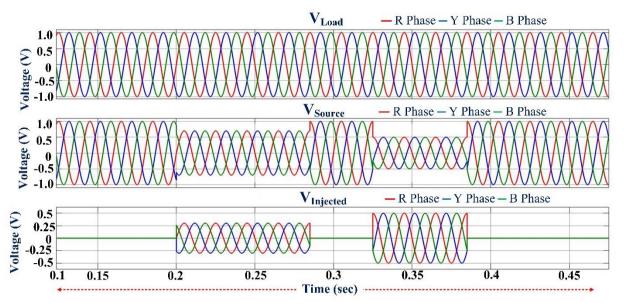

voltage and maintains the load voltage profile, and is shown in Figure 12 and Figure 14. Figure 12 represents the voltage profile of DVR at 0.5pu of sag condition only in one phase, whereas Figure 14 shows a three-phase voltage profile of DVR. Figure 13 depicts the voltage THD at the load side with DVR in sag mode. A double voltage sag mode is created by applying overload at time intervals ranging from 0.2 sec to 0.285 sec with 0.7pu and from 0.315 sec to 0.385 sec with 0.5pu of sag is applied in comparison to load point reference voltage. The proposed DVR injects the appropriate voltages and maintains the load voltage profile, as shown in Figure 15. In this test, a swell mode is created at time intervals from 0.3 sec to 0.365 sec. 1.2 pu of swell is applied in comparison to load point reference voltage. The proposed DVR compensates for the appropriate voltage and maintains the load voltage profile, and is shown in Figure 16.

Figure 14. Simulation results of Source, Injected, and Load voltages at 0.5pu of sag condition.

Figure 15. Simulation results of Source, Injected, and Load voltages at 0.7pu and 0.5pu sag mode

Figure 16. Simulation results of Source, Injected, and Load voltages at 1.2pu swell mode

#### B. Experimental Results

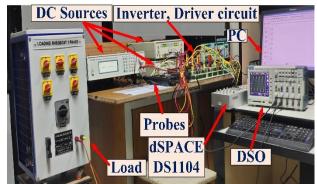

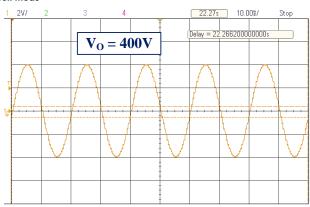

The suggested topology of 23-level MLI is tested using a single-phase prototype built in the lab. A dual dc supply supplies the input dc sources and a 100-ohm resistive load is used. The prototype consists of 12 IGBT switches that are activated by using optocouplers (MCT2E). The real-time controller dSPACE1104 is used to build the switching control system, and DSO is used to monitor the voltage and current waveforms. The experimental setup is shown in Figure 17 and the findings with a resistive load are shown in Figure 18, at steady-state output voltages of 400V (282.84 V<sub>rms</sub>) and the load current of 4A (2.82 I<sub>rms</sub>).

Figure 17. Experimental set-up of 23-level MLI

Figure 18. Experimental output voltage of 23-level MLI

#### C. Real-time Analysis

For high-power applications, it is not feasible to test experimentally the simulation results achieved with MATLAB/Simulink. To verify their accuracy hardware inloop testing (HIL) was developed. This platform scales down testing time, cost and also provides test features in any situation and enables test system change. The setup of the HIL simulator is shown in Figure 19. It consists of an Opal-RT OP5600 simulator, as well as a host computer and a digital storage oscilloscope. It is entirely digital, supported by an FPGA processor, a real-time simulator that runs Simulink in real-time using a fixed-step solver. For viewing and editing the block diagram graphical model in the frontend, it uses MATLAB/Simulink, from which real-time simulation code is generated, updated, and downloaded.

Figure 19. HIL simulator set-up

DS0-X 3014A, MY5431096B: Sun Dec 12 10:50:54 2021

Figure 20. PV and boost converter output in real-time

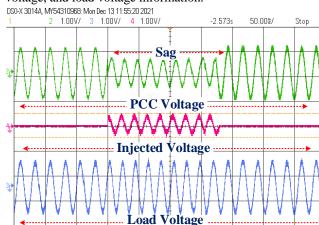

Figure 20 illustrates the performance of an EINC MPPT controlled boost converter using OPAL-RT and Figure 21 shows the output of PV fed MLI-DVR at 0.5pu sag condition of one phase, which includes source voltage, compensation voltage, and load voltage information.

Figure 21. HIL single-phase Voltage profiles at sag condition.

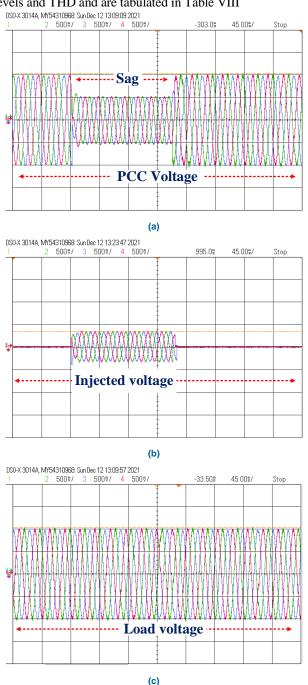

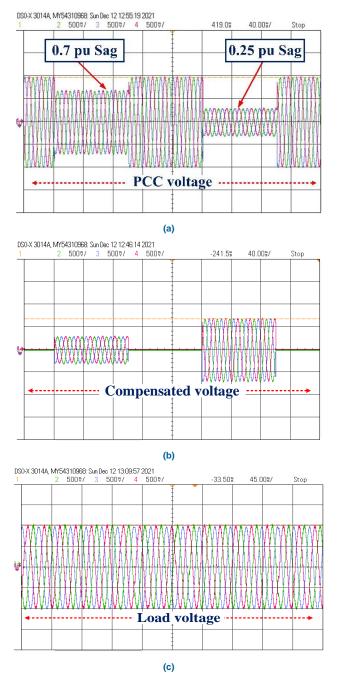

Figure 22 shows the output voltage profile of PV fed MLI-DVR at 0.5pu sag condition, which includes source voltage, compensation voltage, and load voltage information. Figure 23 shows the real-time output details of the proposed DVR source voltage, compensated voltage, and load voltages at 0.7pu and 0.25pu sag conditions.

The THD of the proposed PV-fed DVR is reduced from 17.09 percent (without DVR) to 1.28 percent (with MLI-DVR) at

sag condition and is represented in Figure 24. The proposed DVR architectures are compared with existing MLI DVR architectures in terms of switches required, output voltage levels and THD and are tabulated in Table VIII

Figure 22. HIL three-phase output of (a) Source, (b) Injected, and (c) Load voltages at 0.5pu sag condition.

Figure 25 represents the comparison of the required number of switches per phase to produce expected levels in the output voltage waveform from this the proposed MLI-DVR topology produces higher voltage levels with reduced switches hence the sag voltage is effectively compensated by implementing this topology with lesser THD.

Figure 23. HIL three-phase output of (a) Source, (b) Injected, and (c) Load voltages at 0.7pu and 0.5pu sag conditions.

Figure 24. Real-time load THD at sag condition

| ID   |  |  |  |  |  |  |  |  |

|------|--|--|--|--|--|--|--|--|

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

| 77   |  |  |  |  |  |  |  |  |

| 78   |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

| 23   |  |  |  |  |  |  |  |  |

| 23   |  |  |  |  |  |  |  |  |

| 73   |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

| 8    |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

| 28   |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

| Prop |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

|      |  |  |  |  |  |  |  |  |

TABLE VIII COMPARISON OF PROPOSED MLI-DVR WITH OTHER TOPOLOGIES

Figure 25. Comparison of proposed MLI-DVR with other topologies

#### **VII. CONCLUSION**

A PV-fed MLI-DVR using a rotating dq reference frame controller with an asymmetrical 23-level MLI is proposed in this article. A novel multilevel inverter is designed and implemented experimentally with a laboratory prototype. A synthesized output voltage of the proposed MLI is obtained with a low THD utilizing fewer circuit components. There exits various outstanding features of the proposed MLI such as the TSV<sub>PU</sub> is 2.4 whereas the cost function (CF/L) values for ' $\alpha$ ' are 1.07 and 1.15 respectively, therefore the proposed MLI is cost-effective and superior than the existing topologies. The results of the proposed PV-fed MLI-DVR are verified with the OPAL-RT real time simulator testing platform. The proposed system efficiently minimizes the voltage sag and preserves the DC link voltage to be stable. The maximum power can be extracted from the PV modules using INC MPPT technique. A detailed comparison of the proposed MLI-DVR is presented with the existing topologies and it is found that the proposed system performs efficiently during the compensation of voltage sag. A lower THD of 1.28 % is obtained in the process of compensation of voltage at the grid and satisfies the IEEE standards. The proposed system is significantly performs well henceforth it can be further implemented in HVDC and FACTS devices.

#### ACKNOWLEDGMENT

The authors are grateful to the Vellore Institute of Technology in Vellore, India, for granting a SEED grant to fund this research.

#### REFERENCE

- M. K. Saini and R. Kapoor, "Classification of power quality events - A review," Int. J. Electr. Power Energy Syst., vol. 43, no. 1, pp. 11–19, 2012, doi: 10.1016/j.ijepes.2012.04.045.

- [2] J. Gong, D. Li, T. Wang, W. Pan, and X. Ding, "A comprehensive review of improving power quality using active power filters," Electr. Power Syst. Res., vol. 199, no. June, 2021, doi: 10.1016/j.epsr.2021.107389.

- [3] R. Sepehrzad, A. Mahmoodi, S. Y. Ghalebi, A. R. Moridi, and A. R. Seifi, "Intelligent hierarchical energy and power management to control the voltage and frequency of microgrids based on power uncertainties and communication latency," Electr. Power Syst. Res., vol. 202, no. August 2021, 2022, doi: 10.1016/j.epsr.2021.107567.

- [4] F. Kleber de Araújo Lima, J. M. Guerrero, F. L. Tofoli, C. G. C. Branco, and J. L. Dantas, "Fast and accurate voltage sag detection algorithm," Int. J. Electr. Power Energy Syst., vol. 135, no. August 2021, 2022, doi: 10.1016/j.ijepes.2021.107516.

- [5] Dhanamjayulu, C., and S. Meikandasivam. "Fuzzy controller based design of 125 level asymmetric cascaded multilevel inverter for power quality improvement." *Analog Integrated Circuits and Signal Processing* 101, no. 3 (2019): 533-542.

- [6] M. Bajaj, "Design and Simulation of Hybrid DG System Fed Single-Phase Dynamic Voltage Restorer for Smart Grid Application," Smart Sci., vol. 8, no. 1, pp. 24–38, 2020, doi: 10.1080/23080477.2020.1748928.

- [7] A. B. Kanase-Patil, A. P. Kaldate, S. D. Lokhande, H. Panchal, M. Suresh, and V. Priya, "A review of artificial intelligence-based optimization techniques for the sizing of integrated renewable energy systems in smart cities," Environ. Technol. Rev., vol. 9, no. 1, pp. 111–136, 2020, doi: 10.1080/21622515.2020.1836035.

- [8] P. Kala and S. Arora, "A comprehensive study of classical and hybrid multilevel inverter topologies for renewable energy applications," Renew. Sustain. Energy Rev., vol. 76, no. February, pp. 905–931, 2017, doi: 10.1016/j.rser.2017.02.008.

- [9] S. M. Silva, S. É. da Silveira, A. de Souza Reis, and B. J. Cardoso Filho, "Analysis of a dynamic voltage compensator with reduced switch-count and absence of energy storage system," IEEE Trans. Ind. Appl., vol. 41, no. 5, pp. 1255– 1262, 2005, doi: 10.1109/TIA.2005.853382.

- [10] M. Fang, A. I. Gardiner, A. MacDougall, and G. A. Mathieson, "A novel series dynamic voltage restorer for distribution systems," POWERCON 1998 - 1998 Int. Conf. Power Syst. Technol. Proc., vol. 1, pp. 38–42, 1998, doi: 10.1109/ICPST.1998.728702.

- [11] M. R. Banaei and A. R. Dehghanzadeh, "DVR based cascaded multilevel Z-source inverter," PECon2010 - 2010 IEEE Int. Conf. Power Energy, pp. 51–56, 2010, doi: 10.1109/PECON.2010.5697556.

- [12] S. Jothibasu and M. K. Mishra, "An improved direct AC-AC converter for voltage sag mitigation," IEEE Trans. Ind. Electron., vol. 62, no. 1, pp. 21–29, 2015, doi: 10.1109/TIE.2014.2334668.

- [13] M. Balamurugan, T. S. Sivakumaran, and M. Aishwariya, "Voltage sag/swell compensation using Z-source inverter DVR based on FUZZY controller," 2013 IEEE Int. Conf. Emerg. Trends Comput. Commun. Nanotechnology, ICE-CCN 2013, no. ICECCN, pp. 648–653, 2013, doi: 10.1109/ICE-CCN.2013.6528580.

- [14] Salary, Ebrahim, Mohamad Reza Banaei, and Ali Ajami. "Analysis of Hybrid Multilevel Inverters Using a Reduced Voltage Stress Switch." *Cankaya University Journal of Science and Engineering* 13, no. 2 (2016).

- [15] S. Galeshi and H. Iman-Eini, "Dynamic voltage restorer employing multilevel cascaded H-bridge inverter," IET Power Electron., vol. 9, no. 11, pp. 2196–2204, 2016, doi: 10.1049/iet-pel.2015.0335.

- [16] Salari, Ebrahim, and Ali Darvish Falehi. "A novel 49-level asymmetrical modular multilevel inverter: analysis, comparison and validation." Analog Integrated Circuits and Signal Processing 101, no. 3 (2019): 611-622.

- [17] B. H. Kwon, G. Y. Jeong, S. H. Han, and D. H. Lee, "Novel line conditioner with voltage up/down capability," IEEE Trans. Ind. Electron., vol. 49, no. 5, pp. 1110–1119, 2002, doi: 10.1109/TIE.2002.803236.

- [18] R. J. Satputaley and V. B. Borghate, "Performance analysis of DVR using 'new reduced component' multilevel inverter," Int. Trans. Electr. Energy Syst., vol. 27, no. 4, pp. 1–11, 2017, doi: 10.1002/etep.2288.

- [19] J. Ye, H. B. Gooi, X. Zhang, B. Wang, and J. Pou, "Simplified four-level inverter-based dynamic voltage restorer with single DC power source," IEEE Access, vol. 7, pp. 137461–137471, 2019, doi: 10.1109/ACCESS.2019.2941999.

- [20] M. Shahabadini and H. Iman-Eini, "Improving the Performance of a Cascaded H-Bridge-Based Interline Dynamic Voltage Restorer," IEEE Trans. Power Deliv., vol. 31, no. 3, pp. 1160–1167, 2016, doi: 10.1109/TPWRD.2015.2480967.

- [21] E. Babaei, M. F. Kangarlu, and M. Sabahi, "Dynamic voltage restorer based on multilevel inverter with adjustable dc-link voltage," IET Power Electronics, vol. 7, no. 3. pp. 576–590, 2014, doi: 10.1049/iet-pel.2013.0179.

- [22] G. A. De Almeida Carlos, E. C. Dos Santos, C. B. Jacobina, and J. P. R. A. Mello, "Dynamic Voltage Restorer Based on Three-Phase Inverters Cascaded Through an Open-End Winding Transformer," IEEE Trans. Power Electron., vol. 31, no. 1, pp. 188–199, 2016, doi: 10.1109/TPEL.2015.2404798.

- [23] G. A. De Almeida Carlos, C. B. Jacobina, J. P. R. A. Méllo, and E. C. Dos Santos, "Cascaded Open-End Winding Transformer Based DVR," IEEE Trans. Ind. Appl., vol. 54, no. 2, pp. 1490–1501, 2018, doi: 10.1109/TIA.2017.2768531.

- [24] K. Rajkumar, P. Parthiban, and N. Lokesh, "Real-time implementation of transformerless dynamic voltage restorer based on T-type multilevel inverter with reduced switch count," International Transactions on Electrical Energy

Systems, vol. 30, no. 4. 2020, doi: 10.1002/2050-7038.12301.

- [25] Falehi, Ali Darvish, and Hossein Torkaman. "Promoted supercapacitor control scheme based on robust fractionalorder super-twisting sliding mode control for dynamic voltage restorer to enhance FRT and PQ capabilities of DFIG-based wind turbine." Journal of Energy Storage 42 (2021): 102983.

- [26] Darvish Falehi, Ali. "Half-cascaded multilevel inverter coupled to photovoltaic power source for AC-voltage synthesizer of dynamic voltage restorer to enhance voltage quality." International Journal of Numerical Modelling: Electronic Networks, Devices and Fields 34, no. 5 (2021): e2883.

- [27] Falehi, A. D., and M. Rafiee. "Enhancement of DFIG-wind turbine's LVRT capability using novel DVR based odd-nary cascaded asymmetric multi-level inverter." Engineering science and technology, an international journal 20, no. 3 (2017): 805-824.

- [28] Newman, Michael John, Donald Grahame Holmes, John Godsk Nielsen, and Frede Blaabjerg. "A dynamic voltage restorer (DVR) with selective harmonic compensation at medium voltage level." In 38th IAS Annual Meeting on Conference Record of the Industry Applications Conference, 2003., vol. 2, pp. 1228-1235. IEEE, 2003.

- [29] Li, Yun Wei, D. Mahinda Vilathgamuwa, Frede Blaabjerg, and Poh Chiang Loh. "A robust control scheme for mediumvoltage-level DVR implementation." IEEE Transactions on Industrial Electronics 54, no. 4 (2007): 2249-2261.

- [30] Toupchi Khosroshahi, Mahdi. "Crisscross cascade multilevel inverter with reduction in number of components." IET Power Electronics 7, no. 12 (2014): 2914-2924.

- [31] Devalraju, Prasad, and C. Dhanamjayulu. "A Novel 19-level Asymmetrical Multilevel Inverter for Dynamic Voltage Restorer Applications." In 2021 Innovations in Power and Advanced Computing Technologies (i-PACT), pp. 1-7. IEEE, 2021.

- [32] Thakre, Kishor, Kanungo Barada Mohanty, Aditi Chatterjee, and Vinaya Sagar Kommukuri. "A modified circuit for symmetric and asymmetric multilevel inverter with reduced components count." International Transactions on Electrical Energy Systems 29, no. 6 (2019): e12011.

- [33] Hosseinzadeh, Mohammad Ali, Maryam Sarbanzadeh, Elham Sarbanzadeh, Marco Rivera, and Patrick Wheeler. "New Asymmetric Cascaded Multi-level Converter with Reduced Components." In 2018 IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference (ESARS-ITEC), pp. 1-6. IEEE, 2018.

- [34] Khosroshahi, Mahdi Toopchi, Ali Ajami, Ata Ollah Mokhberdoran, and Mohammadreza Jannati OsKuee. "Multilevel hybrid cascade-stack inverter with substantial reduction in switches number and power losses." Turkish Journal of Electrical Engineering & Computer Sciences 23, no. 4 (2015): 987-1000.

- [35] Thiruvengadam, Annamalai. "An enhanced H-bridge multilevel inverter with reduced THD, conduction, and

switching losses using sinusoidal tracking algorithm." Energies 12, no. 1 (2019): 81

- [36] Meraj, Sheikh Tanzim, Nor Zaihar Yahaya, Kamrul Hasan, and Ammar Masaoud. "A hybrid T-type (HT- type) multilevel inverter with reduced components." Ain Shams Engineering Journal (2021)

- [37] Gupta, K.K. and Jain, S., 2012. Topology for multilevel inverters to attain maximum number of levels from given DC sources. *IET Power Electronics*, *5*(4), pp.435-446.

- [38] S. N. Rao, D. V. A. Kumar, and C. S. Babu, "Grid Connected Distributed Generation System with High Voltage Gain Cascaded DC-DC Converter Fed Asymmetric Multilevel Inverter Topology," Int. J. Electr. Comput. Eng., vol. 8, no. 6, p. 4047, 2018, doi: 10.11591/ijece.v8i6.pp4047-4059.

- [39] A. Belkaid, I. Colak, and O. Isik, "Photovoltaic maximum power point tracking under fast varying of solar radiation," Appl. Energy, vol. 179, pp. 523–530, 2016, doi: 10.1016/j.apenergy.2016.07.034.

- [40] J. G. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump," Conf. Proc. - IEEE Appl. Power Electron. Conf. Expo. - APEC, vol. 2, pp. 1267–1273, 2001, doi: 10.1109/apec.2001.912528.

- [41] P. Boonchiam and N. Mithulananthan, "Diode-clamped Multilevel Voltage Source Converter Based on Medium Voltage DVR," pp. 590–595, 2008.

- [42] B. Wang, G. Venkataramanan, and M. Illindala, "Operation and control of a dynamic voltage restorer using transformer coupled H-Bridge converters," IEEE Trans. Power Electron., vol. 21, no. 4, pp. 1053–1061, 2006, doi: 10.1109/TPEL.2006.876836.

- [43] K. Chandrasekaran and V. K. Ramachandaramurthy, "An improved Dynamic Voltage Restorer for power quality improvement," Int. J. Electr. Power Energy Syst., vol. 82, pp. 354–362, 2016, doi: 10.1016/j.ijepes.2016.02.036.

- [44] M. I. Marei, A. B. Eltantawy, and A. A. El-Sattar, "An energy optimized control scheme for a transformerless DVR," Electr. Power Syst. Res., vol. 83, no. 1, pp. 110–118, 2012, doi: 10.1016/j.epsr.2011.09.015.

- [45] A. J. Visser, J. H. R. Enslin, and H. D. T. Mouton, "Transformerless series sag compensation with a cascaded multilevel inverter," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 824–831, 2002, doi: 10.1109/TIE.2002.801067.

- [46] A. M. Massoud, S. Ahmed, P. N. Enjeti, and B. W. Williams, "Evaluation of a multilevel cascaded-type dynamic voltage restorer employing discontinuous space vector modulation," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2398–2410, 2010, doi: 10.1109/TIE.2010.2041732.