Research Institute for Advanced Computer Science NASA Ames Research Center

p 2015

# **Sparse Distributed Memory and Related Models**

Pentti Kanerva

# **RIACS Technical Report 92.10**

# **April 1992**

| (NASA-CR-190553) SPARSE         | N92-30724 |

|---------------------------------|-----------|

| DISTRIBUTED MEMORY AND RELATED  |           |

| MODELS (Research Inst. for      |           |

| Advanced Computer Science) 55 p | Unclas    |

63/60 0109037

# **Sparse Distributed Memory and Related Models**

Pentti Kanerva

The Research Institute for Advanced Computer Science is operated by Universities Space Research Association (USRA), The American City Building, Suite 311, Columbia, MD 21044, (301)730-2656.

Work reported herein was supported by the National Aeronautics and Space Administration (NASA) under Cooperative Agreement NC2-387 with the Universities Space Research Association (USRA).

# RIACS Technical Report 92.10

# April 1992

# **Sparse Distributed Memory and Related Models**

Pentti Kanerva

Research Institute for Advanced Computer Science Mail Stop T041-5 NASA Ames Research Center Moffett Field, CA 94035 *e-mail:* kanerva@riacs.edu

#### Abstract

This paper describes sparse distributed memory (SDM) as a neural-net associative memory. It is characterized by two weight matrices and by a large internal dimension—the number of hidden units is much larger than the number of input or output units. The first matrix, A, is fixed and possibly random, and the second matrix, C, is modifiable. The paper compares and contrasts SDM to (1) computer memory, (2) correlation-matrix memory, (3) feed-forward artificial neural network, (4) cortex of the cerebellum, (5) Marr and Albus models of the cerebellum, and (6) Albus' cerebellar model arithmetic computer (CMAC). Several variations of the basic SDM design are discussed: the selected-coordinate and hyperplane designs of Jaeckel, the pseudorandom associative neural memory of Hassoun, and SDM with real-valued input variables by Prager and Fallside. SDM research conducted mainly at RIACS in 1986–1991 is highlighted.

iii

INTENTIONALLY BLANK

To appear as Chapter Z in H. M. Hassoun, ed. Associative Neural Memories: Theory and Implementation. New York: Oxford University Press.

# Contents

# 1. Introduction / 1

- 1.1 Sparse Distributed Memory as a Model of Human Long-Term Memory, 1

- 2. SDM as a Random-Access Memory / 2

- 2.1 Random-Access Memory, 3

- 2.2 Sparse Distributed Memory, 3 Construction / Activation / Storage / Retrieval / Random Access Memory as a Special Case / Parallel Realization

# 3. SDM as a Matrix Memory /7

- 3.1 Notation, 7

- 3.2 Memory Parameters, 8

- 3.3 Summary Specification, 10

- 3.4 Relation to Correlation-Matrix Memories, 11

- 3.5 Recall Fidelity ( $\phi$ ), 12

- 3.6 Signal ( $\mu$ ), Noise ( $\sigma$ ), and Probability of Activation (p), 14

- 3.7 Memory Capacity  $(\tau)$ , 15

# 4. SDM as an Artificial Neural Network / 17

#### 5. SDM as a Model of the Cerebellum / 19

- 5.1 Modeling Biology with Artificial Neural Networks, 19

- 5.2 The Cortex of the Cerebellum, 21

# 6. Variations of the Model / 23

- 6.1 Jaeckel's Selected-Coordinate Design, 23

- 6.2 Jaeckel's Hyperplane Design, 24

- 6.3 Hassoun's Pseudorandom Associative Neural Memory, 25

- 6.4 Adaptation to Continuous Variables by Prager and Fallside, 26

# 7. Relation to the Cerebellar Models of Marr and of Albus / 27

- 7.1 Marr's Model of the Cerebellum, 27

- 7.2 Albus' Cerebellar Model Arithmetic Computer (CMAC), 29

#### 8. SDM Research / 31

#### 9. Associative Memory as a Component of a System / 33

10. Summary / 34

Pattern Computing

Acknowledgments / 35

#### References / 36

# 1. Introduction

This chapter describes one basic model of associative memory, called the sparse distributed memory, and relates it to other models and circuits: to ordinary computer memory, to correlation-matrix memories, to feed-forward artificial neural nets, to neural circuits in the brain, and to associative-memory models of the cerebellum. Presenting the various designs within one framework will hopefully help the reader see the similarities and the differences in designs that are often described in different ways.

#### 1.1 Sparse Distributed Memory as a Model of Human Long-Term Memory

Sparse Distributed Memory (SDM) was developed as a mathematical model of human long-term memory (Kanerva 1988). The pursuit of a simple idea led to the discovery of the model, namely, that the distances between concepts in our minds correspond to the distances between points of a high-dimensional space. In what follows, 'high-dimensional' means that the number of dimensions is at least in the hundreds, although smaller numbers of dimensions are often found in examples.

If a concept, or a percept, or a moment of experience, or a piece of information in memory—a point of interest—is represented by a high-dimensional (or "long") vector, the representation need not be exact. This follows from the distribution of points of a high-dimensional space: Any point of the space that might be a point of interest is relatively far from most of the space and from other points of interest. Therefore, a point of interest can be represented with considerable slop before it is confused with other points of interest. In this sense, long vectors are fault-tolerant or robust, and a device based on them can take advantage of the robustness.

This corresponds beautifully to how humans and animals with advanced sensory systems and brains work. The signals received by us at two different times are hardly ever identical, and yet we can identify the source of the signal as a *specific* individual, object, place, scene, thing. The representations used by the brain must allow for such identification, in fact, they must make the identification nearly automatic, and high-dimensional vectors as internal representations of things do that.

Another property of high-dimensional spaces also has to do with the distances between points. If we take two points (of interest) at random, they are relatively far from each other, on the average: they are uncorrelated. However, there are many points between the two that are close to both, in the sense that the amount of space around an intermediate point—in a hypersphere—that contains both of the two original points is very small. This corresponds to the relative ease with which we can find a concept that links two unrelated concepts.

Strictly speaking, a mathematical space need not be a high-dimensional vector

space to have the desired properties; it needs to be a huge space, with an appropriate similarity measure for pairs of points, but the measure need not define a metric on the space.

The important properties of high-dimensional spaces are evident even with the simplest of such spaces—that is, when the dimensions are binary. Therefore, the sparse distributed memory model was developed using long (i.e., high-dimensional) binary vectors or words. The memory is addressed by such words, and such words are stored and retrieved as data.

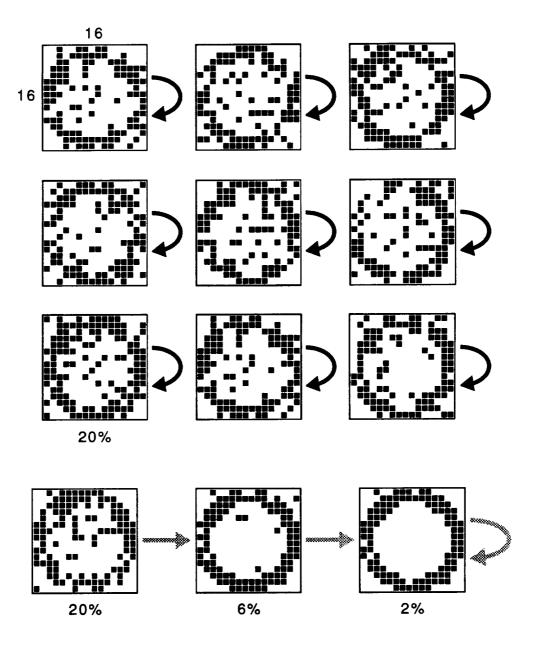

The following two examples demonstrate the memory's robustness in dealing with approximate data. The memory works with 256-bit words: it is addressed by them, and it stores and retrieves them. On top of Figure 2–1 are nine similar (20% noisy) 256-bit words. To help us compare long words, their 256 bits are laid on a 16-by-16 grid, with 1s shown in black. The noise-free prototype word was designed in the shape of a circle within the grid. (This example is confusing in that it might be taken to imply that humans recognize circles based on stored retinal images of circles. No such claim is intended.) The nine noisy words were stored in a sparse distributed memory autoassociatively, meaning that each word was stored with itself as the address. When a tenth noisy word (bottom left), different from the nine, was used as the address, a relatively noise-free 11th word was retrieved (bottom middle), and with that as the address, a nearly noise-free 12th word was retrieved (bottom right), which in turn retrieved itself. This example demonstrates the memory's tendency to construct a prototype from noisy data.

(( FIGURE 2-1. Nine noisy words are stored ... ))

Figure 2–2 demonstrates sequence storage and recall. Six words, shaped as Roman numerals, are stored in a linked list: I is used as the address to store II, II is used as the address to store III, and so forth. Any of the words I–V can then be used to recall the rest of the sequence. For example, III will retrieve IV will retrieve V will retrieve VI. The retrieval cue for the sequence can be noisy, as demonstrated at the bottom of the figure. As the retrieval progresses, a retrieved word, which then serves as the next address, is less and less noisy. This example resembles human ability to find a familiar tune by hearing a piece of it in the middle, and to recall the rest. This kind of recall applies to a multitude of human and animal skills.

(( **FIGURE** 2–2. Recalling a stored sequence ... ))

#### 2. SDM as a Random-Access Memory

Except for the lengths of the address and data words, the memory resembles ordinary computer memory. It is a generalized random-access memory for long words, as will be seen shortly, and its construction and operation can be explained in terms of an ordinary random-access memory. We will start by describing an ordinary random-access memory.

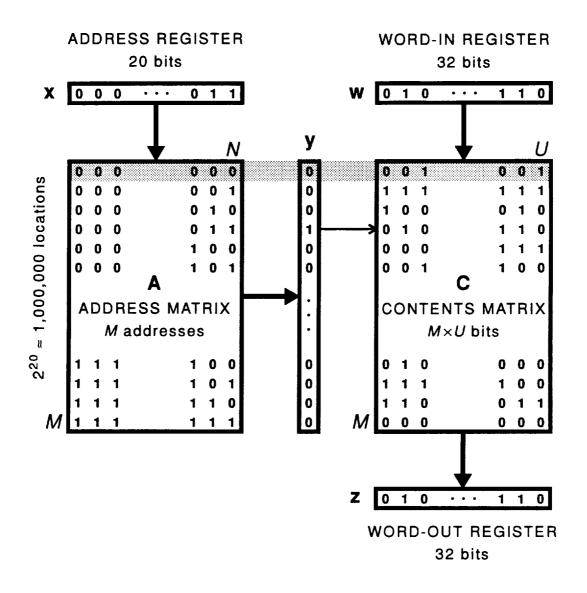

#### 2.1 Random-Access Memory

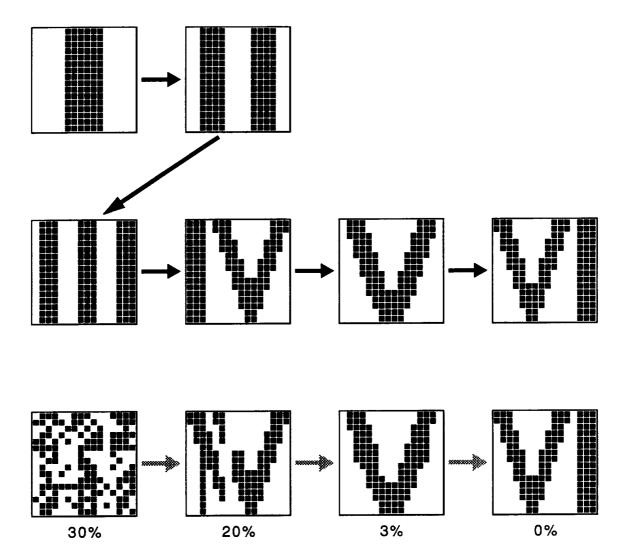

A random-access memory (RAM) is an array of M addressable storage registers or memory locations of fixed capacity. A location's place in the memory array is called the location's *address*, and the value stored in the register is called the location's *contents*. Figure 2-3 represents such a memory, and a horizontal row through the figure represents one memory location. The first location is shown shaded. The addresses of the locations are on the left, in matrix A, and the contents are on the right, in matrix C.

(( FIGURE 2-3. Organization of a random-access memory. ))

A memory with a million locations  $(M = 2^{20})$  is addressed by 20-bit words. The length of the address will be denoted by N (N = 20 in Fig. 2–3). The capacity of a location is referred to as the memory's *word size*, U (U = 32 bits in Fig. 2–3), and the capacity of the entire memory is defined conventionally as the word size multiplied by the number of memory locations (i.e.,  $M \times U$  bits).

Storage and retrieval happen one word at a time through three special registers: the *address register*, for an *N*-bit address into the memory array; the *word-in register*, for a *U*-bit word that is to be stored in memory; and the *word-out register*, for a *U*-bit word retrieved from memory. To store the word w in location x (the location's address is used as a name for the location), x is placed in the address register, w is placed in the word-in register, and a write-into-memory command is issued. Consequently, w replaces the old contents of location x, while all other locations remain unchanged. To retrieve the word w that was last stored in location x, x is placed in the address register and a read-from-memory command is issued. The result w appears in the word-out register. The figure shows (a possible) state of the memory after w = 010...110 has been stored in location x = 000...011 (the word-in register holds w) and then retrieved from the same location (the address register holds x).

Between matrices A and C in the figure is an *activation vector*, y. Its components are 0s except for one 1, which indicates the memory location that is selected for reading or writing (i.e., the location's address matches the address register). In a hardware realization of a random-access memory, a location's activation is determined by an address-decoder circuit, so that the address matrix A is implicit. However, the contents matrix C is an explicit array of  $2^{20} \times 32$  one-bit registers or flip-flops.

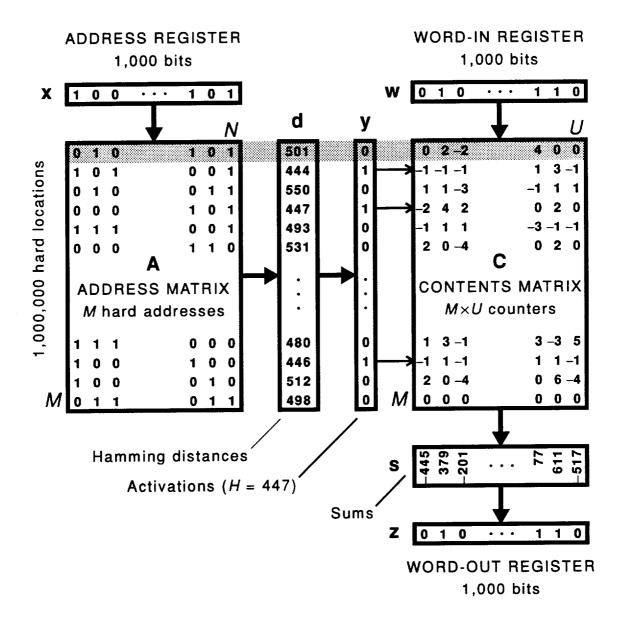

#### 2.2 Sparse Distributed Memory

Figure 2-4 represents a sparse distributed memory. From the outside, it is like a random-access memory: it has the same three special registers—address, word-in, and word-out—and they are used in the same way when words are stored and

retrieved, except that these registers are large (e.g., N = U = 1,000).

(( FIGURE 2-4. Organization of a sparse distributed memory. ))

**Construction.** The internal organization of sparse distributed memory, likewise, is an array of addressable storage locations of fixed capacity. However, since the addresses are long, it is impossible to build a hardware location—a hard location, for short—for each of the  $2^N$  addresses. (Neither is it necessary, considering the enormous capacity that such a memory would have.)

A memory of reasonable size and capacity can be built by taking a reasonably large sample of the  $2^N$  addresses and by building a hard location for each address in the sample. Let *M* be the size of the sample: we want a memory with *M* locations (M = 1,000,000 in Fig. 2-4). The sample can be chosen in many ways, and only some will be considered here.

A good choice of addresses for the hard locations depends on the data to be stored in the memory. The data consist of the words to be stored and of the addresses used in storing them. For simplicity, we assume in the basic model that the data are distributed randomly and uniformly (i.e., bits are independent of each other, and 0s and 1s are equally likely, both in the words being stored and in the addresses used for storing them). Then the *M* hard locations can be picked at random; that is to say, we can take a uniform random sample, of size *M*, of all *N*-bit addresses. Such a choice of locations is shown in Figure 2–4, where the addresses of the locations are given in matrix A and the contents are given in matrix C, and where a row through the figure represents a hard location, just as in Figure 2–3 (row  $A_m$  of matrix A is the *m*th hard address, and  $C_m$  is the contents of location  $A_m$ ; as with RAM, we use  $A_m$  to name the *m*th location).

Activation. In a random-access memory, to store or retrieve a word with x as the address, x is placed in the (20-bit) address register, which activates location x. We say that the address register *points* to location x, and that whatever location the address register points to is activated. This does not work with a sparse distributed memory because its (1,000-bit) address register never—practically never—points to a hard location because the hard locations are so few compared to the number of possible addresses (e.g., 1,000,000 hard addresses vs.  $2^{1,000}$  possible addresses; matrix A is an exceedingly sparse sampling of the address space).

To compensate for the extreme sparseness of the memory, a set of nearby locations is activated at once, for example, all the locations that are within a certain distance from x. Since the addresses are binary, we can use Hamming distance, which is the number of places at which two binary vectors differ. Thus, in a sparse distributed memory, the mth location is activated by x (which is in the address register) if the Hamming distance between x and the location's address  $A_m$  is below or equal to a threshold value H (H stands for a [Hamming] radius of activation). The threshold is chosen so that but a small fraction of the hard locations are activated by any given x. When the hard addresses A are a uniform random sample of the Ndimensional address space, the binomial distribution with parameters N and 1/2 can be used to find the activation radius H that corresponds to a given probability p of activating a location. Notice that, in a random-access memory, a location is activated only if its address matches x, meaning that H = 0.

Vectors **d** and **y** in Figure 2-4 show the activation of locations by address **x**. The distance vector **d** gives the Hamming distances from the address register to each of the hard locations, and the 1s of the activation vector **y** mark the locations that are close enough to **x** to be activated by it:  $\mathbf{y}_m = 1$  if  $\mathbf{d}_m \le H$ , and  $\mathbf{y}_m = 0$  otherwise, where  $\mathbf{d}_m = h(\mathbf{x}, \mathbf{A}_m)$  is the Hamming distance from **x** to location  $\mathbf{A}_m$ . The number of 1s in **y** therefore equals the size of the set activated by **x**.

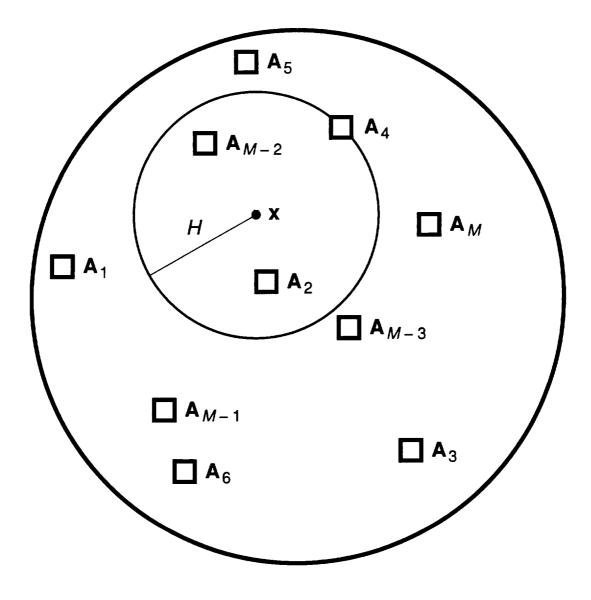

Figure 2-5 is another way of representing the activation of locations. The large circle represents the space of  $2^N$  addresses. Each tiny square is a hard location, and its position within the large circle represents the location's addresses. The small circle around x includes the locations that are within H bits of x and that therefore are activated by x.

(( FIGURE 2-5. Address space, hard locations, and the set ... ))

Storage. To store U-bit words, a hard location has U up-down counters. The range of a counter can be small, for example, the integers from -15 to 15. The U counters for each of the M hard locations constitute the  $M \times U$  contents matrix, C, shown on the right in Figure 2-4, and they correspond to the  $M \times U$  flip-flops of Figure 2-3. We will assume that all counters are initially set to zero.

When x is used as the storage address for the word w, w is stored in each of the locations activated by x. Thus, multiple copies of w are stored; in other words, w is distributed over a (small) number of locations. The word w is stored in, or written into, an active location as follows: Each 1-bit of w increments, and each 0-bit of w decrements, the corresponding counter of the location. This is equivalent to saying that the word w' of -1s and 1s is added (vector addition) to the contents of each active location, where w' is gotten from w by replacing 0s with -1s. Furthermore, the counters in C are not incremented or decremented past their limits (i.e., overflow and underflow are lost).

Figure 2-4 depicts the memory after the word  $\mathbf{w} = 010...110$  (in the word-in register) has been stored with  $\mathbf{x} = 100...101$  as the address (in the address register). Several locations are shown as selected, and the vector  $\mathbf{w}' = (-1, 1, -1, ..., 1, 1, -1)$  has been added to their contents. The figure also shows that many locations have been selected for writing in the past (e.g., the first location has nonzero counters), that the last location appears never to have been selected, and that  $\mathbf{w}$  appears to be the first word written into the selected location near the bottom of the memory (the location contains  $\mathbf{w}'$ ). Notice that a positive value of a counter, +5, say, tells that five more 1s than 0s have been stored in it; similarly, -5 tells that five more 0s than 1s

have been stored (provided that the capacity of the counter has never been exceeded).

**Retrieval.** When x is used as the retrieval address, the locations activated by x are pooled as follows: their contents are accumulated (vector addition) into a vector of U sums, s, and the sums are compared to a threshold value 0 to get an output vector z, which then appears in the word-out register ( $z_u = 1$  iff  $s_u > 0$ ; s and z are below matrix C in Fig. 2-4). This pooling constitutes a majority rule, in the sense that the *u*th output bit is 1 if, and only if, more 1s than 0s have been stored in the *u*th counters of the activated locations; otherwise, the output bit is 0.

In Figure 2-4 the word retrieved, z, is the same as, or very similar to, the word w that was stored, for the following reason: The same x is used as both storage and retrieval address, so that the same set of locations is activated both times. In storing, each active location receives one copy of w', as described above; in retrieving, we get back *all* of them, plus a few copies of many other words that have been stored. This biases the sums, s, in the direction of w', so that w is a likely result after thresholding. This principle holds even when the retrieval address is not exactly x but is close to it. Then we get back *most* of the copies of w'.

The ideas of storing multiple copies of target words in memory, and of retrieving the most likely target word based on the majority rule, are found already in the *redundant hash addressing* method of Kohonen and Reuhkala (1978, Kohonen 1980). The method of realizing these ideas in redundant hash addressing is very different from their realization in a sparse distributed memory.

Retrieval and memory capacity will be analyzed statistically at the end of the next section, after a uniform set of symbols and conventions for the remainder of this chapter has been established. We will note here, however, that the intersections of activation sets play a key role in the analysis, for they appear as weights for the words stored in the memory when the sum vector **s** is evaluated.

**Random-Access Memory as a Special Case.** One more comment about a random-access memory: Proper choice of parameters for a sparse distributed memory yields an ordinary random-access memory. First, the address matrix A must contain all  $2^N$  addresses; second, the activation radius H must be zero; and, third, the capacity of each counter in C must be one bit. The first condition guarantees that every possible address x points to at least one hard location. The second condition guarantees that only a location that is pointed to is activated. The third condition guarantees that when a word is written into a location, it replaces the location's old contents, because overflow and underflow are lost. In memory retrieval, the contents of all active locations are added together; in this case, the sum is over one or more locations with hard address x. Any particular coordinate of the sum is zero if the word last written (with address x) has a 0 in that position; and it is positive if the word has a 1, so that after thresholding we get the word last written

with address x. Therefore, the sparse distributed memory is a generalization of the random-access memory.

**Parallel Realization.** Storing a word, or retrieving a word, in a sparse distributed memory involves massive computation. The contents of the address register are compared to each hard address, to determine which locations to activate. For the model memory with a million locations, this means computing one-million Hamming distances involving 1,000 bits each, and comparing the distances to a threshold. This is very time-consuming if done serially. However, the activations of the hard locations are independent of each other so that they can be computed in parallel; once the address is broadcast to all the locations, million-fold parallelism is possible. The addressing computation that determines the set of active locations corresponds to address decoding by the address-decoder circuit in a random-access memory.

In storing a word, each column of counters in matrix C (see Fig. 2–4) can be updated independently of all other columns, so that there is an opportunity for thousand-fold parallelism when 1,000-bit words are stored. Similarly, in retrieving a 1,000-bit word, there is an opportunity for thousand-fold parallelism. Further parallelism is achieved by updating many locations at once when a word is stored, and by accumulating many partial sums at once when a word is retrieved. It appears that neural circuits in the brain are wired for these kinds of parallelism.

# **3. SDM as a Matrix Memory**

The construction of the memory was described above in terms of vectors and matrices. We will now see that its operation is described naturally in vector-matrix notation. Such description is convenient in relating the sparse distributed memory to the correlation-matrix memories described by Anderson (1968) and Kohonen (1972)—see also Hopfield (1982), Kohonen (1984), Willshaw (1981), and Chapter 1 by Hassoun—and in relating it to many other kinds of artificial neural networks. The notation will also be used for describing variations and generalizations of the basic sparse distributed memory model.

#### 3.1 Notation

In comparing the memory to a random-access memory, it is convenient to express binary addresses and words in 0s and 1s. In comparing it to a matrix memory, however, it is more convenient to express them in -1s and 1s (also called *bipolar* representation). This transformation is already implicit in the storage algorithm described above: a binary word w of 0s and 1s is stored by adding the corresponding word w' of -1s and 1s into (the contents of) the active locations. From here on, we assume that the binary components of A and x (and of w and z) are -1s and 1s, and whether *bit* refers to 0 and 1 or to -1 and 1 will depend on the context.

How is the activation of a location determined after this transformation? In the same way as before, provided that Hamming distance is defined as the number of places at which two vectors differ. However, we can also use the inner product (scalar product, dot product) of the hard address  $A_m$  and the address register x to measure their similarity:  $d = d(\mathbf{A}_m, \mathbf{x}) = \mathbf{A}_m \cdot \mathbf{x}$ . It ranges from -N to N (d = N means that the two addresses are most similar-they are identical), and it relates linearly to the Hamming distance, which ranges from 0 to N (0 means identical). Therefore, Hamming distance  $h(\mathbf{A}_m, \mathbf{x}) \leq H$  if, and only if,  $\mathbf{A}_m \cdot \mathbf{x} \geq N - 2H (=D)$ . In a computer simulation of the memory, however, the exclusive-or (XOR) operation on addresses of 0s and 1s usually results in the most efficient computation of distances and of the activation vector y.

The following typographic conventions will be used:

- italic lowercase for a scalar or a function name. S

- italic uppercase for a scalar upper bound or a threshold. S

- bold lowercase for a (column) vector. v

- ith component of a vector, a scalar. Vj

- Μ bold uppercase for a matrix.

ith row of a matrix, a (column) vector. M;

$\mathbf{M}_{i}$  jth column of a matrix, a (column) vector.

$\mathbf{M}_{i,j}$  $\mathbf{M}^{\mathrm{T}}$ scalar component of a matrix.

transpose of a matrix (or of a vector).

scalar (inner) product of two vectors:  $\mathbf{u} \cdot \mathbf{v} = \mathbf{u}^T \mathbf{v}$ .

matrix (outer) product of two vectors:  $\mathbf{u} \Box \mathbf{v} = \mathbf{u} \mathbf{v}^{\mathrm{T}}$ .

index into the bits of an address.  $n = 1, 2, 3, \dots, N$

u = 1, 2, 3, ..., Uindex into the bits of a word.

index into the data.  $t = 1, 2, 3, \dots, T$

index into the hard locations.  $m = 1, 2, 3, \dots, M$

#### 3.2 Memory Parameters

The sparse distributed memory, as a matrix memory, is described below in terms of its parameters, progressing with the information flow from upper left to lower right in Figure 2-4. Sample memory refers to a memory whose parameter values appear in parentheses in the descriptions below, as in "(e.g., N = 1,000)".

The external dimensions of the memory are given by:

N Address length; dimension of the address space; input dimension (e.g., N =1,000). Small demonstrations can be made with N as small as 25, but N > 100 is recommended, as the properties of high-dimensional spaces will then be evident.

U Word length; the number of bits (-1s and 1s) in the words stored; output dimension (e.g., U = 1,000). The minimum, U = 1, corresponds to classifying the data into two classes. If U = N, it is possible to store words autoassociatively and to store sequences of words as pointer chains, as demonstrated in Figures 2-1 and 2-2.

The data set to be stored—the training set (X, W)—is given by:

T Training-set size; number of elements in the data set (e.g., T = 10,000).

X Data-address matrix; T training addresses;  $T \times N$  -1s and 1s (e.g., uniform random).

W Data-word matrix; T training words;  $T \times U$  -1s and 1s (e.g., uniform random). Autoassociative data (self-addressing) means that X = W, and sequence data means that  $X_t = W_{t-1}$  (t > 1).

The memory's internal parameters are:

*M* Memory size; number of hard locations (e.g., M = 1,000,000). Memory needs to be sufficient for the data being stored and for the amount of noise to be tolerated in retrieval. Memory capacity is low, so that *T* should be 1–5 percent of *M* (*T* is the number of stored patterns; storing many noisy versions of the same pattern [cf. Fig. 2–1] counts as storing one pattern, or as storing few).

A Hard-address matrix; M hard addresses;  $M \times N$  -1s and 1s (e.g., uniform random). This matrix is fixed. Efficient use of memory requires that A correspond to the set of data addresses X (see Sec. 8 on SDM research).

*p* Probability of activation (e.g., p = 0.000445; "ideally," p = 0.000368). This important parameter determines the number of hard locations that are activated, on the average, by an address, which, in turn, determines how well stored words are retrieved. The best *p* maximizes the signal (due to the target word that is being retrieved) relative to the noise (due to all other stored words) in the sum, **s**, and is approximately  $(2MT)^{-1/3}$  (see end of this section, where signal, noise, and memory capacity are discussed).

*H* Radius of activation (e.g., H = 447 bits). The binomial distribution or its normal approximation can be used to find the (Hamming) radius for a given probability. For the sample memory, optimal *p* is 0.000368, so that about 368 locations should be activated at a time. Radius H = 446 captures 354 locations, and H = 447 captures 445 locations, on the average. We choose the latter.

*D* Activation threshold on similarity (e.g., D = 106). This threshold is related to the radius of activation by D = N - 2H, so that D = 108 and D = 106 correspond to the two values of *H* given above.

c Range of a counter in the  $M \times U$  contents matrix C (e.g.,  $c = \{-15, -14, -13, ..., 14, 15\}$ ). If the range is one bit ( $c = \{0, 1\}$ ), the contents of a location are determined wholly by the most-recent word written into the location. An 8-bit byte, an integer variable, and a floating-point variable are convenient counters in computer simulations of the memory.

The following variables describe the memory's state and operation:

**x** Storage or retrieval address; contents of the address register; N - 1s and 1s (e.g.,  $\mathbf{x} = \mathbf{X}_t$ ).

**d** Similarity vector; *M* integers in  $\{-N, -N + 2, -N + 4, ..., N - 2, N\}$ . Since the similarity between the *m*th hard address and the address register is given by their inner product  $\mathbf{A}_m \cdot \mathbf{x}$  (see Sec. 3.1 on Notation), the similarity vector can be expressed as  $\mathbf{d} = \mathbf{A}\mathbf{x}$ .

y Activation vector; M 0s and 1s. The similarity vector **d** is converted into the activation vector **y** by the (nonlinear) threshold function y defined by  $y(\mathbf{d}) = \mathbf{y}$ , where  $\mathbf{y}_m = 1$  if  $\mathbf{d}_m \ge D$ , and  $\mathbf{y}_m = 0$  otherwise. The number of 1s in  $\mathbf{y}$ ,  $|\mathbf{y}|$ , is small compared to the number of 0s ( $|\mathbf{y}| = pM$ ); the activation vector is a very sparse vector in a very-high-dimensional space. Notice that this is the only vector of 0s and 1s; all other binary vectors consist of -1s and 1s.

w Input word; U -1s and 1s (e.g.,  $\mathbf{w} = \mathbf{W}_t$ ).

C Contents matrix;  $U \times M$  up-down counters with range c, initial value usually assumed to be 0. Since the word w is stored in active location  $A_m$  (i.e., when  $y_m = 1$ ) by adding w into the location's contents  $C_m$ , it is stored in all active locations indicated by y by adding the (outer-product) matrix y $\Box$ w (most of whose rows are 0) into C, so that  $C := C + y \Box$ w, where := means substitution, and where addition beyond the range of a counter is ignored. This is known as the outerproduct, or Hebbian, learning rule.

s Sum vector; U sums (each sum has [at most] |y| nonzero terms). Because the sum vector is made up of the contents of the active locations, it can be expressed as  $s = C^{T}y$ . The U sums give us the final output word z, but they also tell us how reliable each of the output bits is. The further a sum is from the threshold, the stronger is the memory's evidence for the corresponding output bit.

z Output word; U -1s and 1s. The sum vector s is converted into the output vector z by the (nonlinear) threshold function z defined by z(s) = z, where  $z_u = 1$  if  $s_u > 0$ , and  $z_u = -1$  otherwise.

In summary, storing the word w into the memory with x as the address can be expressed as

$$\mathbf{C} := \mathbf{C} + y(\mathbf{A}\mathbf{x}) \mathbf{\Box} \mathbf{w}$$

and retrieving the word z corresponding to the address x can be expressed as

$$\mathbf{z} = z(\mathbf{C}^{\mathrm{T}}\mathbf{y}(\mathbf{A}\mathbf{x}))$$

#### 3.3 Summary Specification

The following matrices describe the memory's operation on the data set—the training set (X, W)—as a whole:

**D**  $T \times M$  matrix of similarities corresponding to the data addresses **X**: **D** =  $(\mathbf{A}\mathbf{X}^{T})^{T} = \mathbf{X}\mathbf{A}^{T}$ .

**Y** Corresponding  $T \times M$  matrix of activations: **Y** =  $y(\mathbf{D})$ .

**S**  $T \times U$  matrix of sums for the data set: **S** = **YC**.

**Z** Corresponding  $T \times U$  matrix of output words:  $\mathbf{Z} = z(\mathbf{S}) = z(\mathbf{YC})$ .

If the initial contents of the memory are 0, and if the capacities of the counters are never exceeded, storing the *T*-element data set yields memory contents

$$\mathbf{C} = \sum_{t=1}^{T} \mathbf{Y}_{t} \Box \mathbf{W}_{t} = \sum_{t=1}^{T} y(\mathbf{A}\mathbf{X}_{t}) \Box \mathbf{W}_{t}$$

This expression for C follows from the outer-product learning rule (see C above), as it is the sum of T matrices, each of which represents an item in the data set. However, C can be viewed equivalently as a matrix of  $M \times U$  inner products  $C_{m, u}$ of pairs of vectors of length T. One set of these vectors is the M columns of Y, and the other set is the U columns of W, so that  $C_{m, u} = Y_{\cdot, m} \cdot W_{\cdot, u}$ , and

$$\mathbf{C} = \mathbf{Y}^{\mathrm{T}}\mathbf{W} = y(\mathbf{A}\mathbf{X}^{\mathrm{T}})\mathbf{W}$$

The accuracy of recall of the training set after it has been stored in memory, is then given by

$$Z - W = z(YC) - W$$

$$= z(YYTW) - W$$

This form is convenient in the mathematical analysis of the memory. For example, it is readily seen that if the T rows of Y are orthogonal to one another,  $YY^{T}$  is a diagonal matrix approximately equal to pMI (I is the identity matrix), so that  $z(YY^{T}W) = W$  and recall is perfect. Notice that the rows of Y for the sample memory are nearly orthogonal to one another, and that the purpose of addressing through A is to produce (nearly) orthogonal activation vectors for most pairs of addresses, which is a way of saying that the sets of locations activated by dissimilar addresses overlap as little as possible.

#### 3.4 Relation to Correlation-Matrix Memories

The  $M \times U$  inner products that make up C are correlations of a sort: they are unnormalized correlations that reflect agreement between the M variables represented by the columns of Y, and the U variables represented by the columns of W. If the columns were normalized to zero mean and to unit length, their inner products would equal the correlation coefficients used commonly in statistics. Furthermore, the inner products of activation vectors (i.e., unnormalized correlations)  $Y_t \cdot y$  serve as weights for the training words in memory retrieval, further justifying the term correlation-matrix memory.

The Y-variables are derived from the X-variables (each Y-variable compares the data addresses X to a specific hard address), whereas in the original correlationmatrix memories (Anderson 1968; Kohonen 1972), the X-variables are used directly, and the variables are continuous. Changing from the X-variables to the Y- variables means, mathematically, that the input dimension is blown way up (from a thousand to a million); in practice it means that the memory can be made arbitrarily large, rendering its capacity independent of the input dimension N. The idea of expanding the input dimension goes back at least to Rosenblatt's (1962)  $\alpha$ -perceptron network.

#### **3.5 Recall Fidelity** ( $\phi$ )

We will now look at the retrieval of words stored in memory, that is, how faithfully are the stored words reconstructed by the retrieval procedure. The asymptotic behavior of the memory, as the input dimension N grows without bound, has been analyzed in depth by Chou (1989). Specific dimension N is assumed here, and the analysis is simple but approximate. The analysis follows one given by Jaeckel (1989a) and uses some of the same symbols.

What happens when we use one of the addresses, say, the last data address  $X_T$ , to retrieve a word from memory; how close to the stored word  $W_T$  is the retrieved word  $Z_T$ ? The output word  $Z_T$  is gotten from the sum vector  $S_T$  by comparing its U sums to zero. Therefore, we need to find out how likely will a sum in  $S_T$  be on the correct side of zero. Since the data are uniform random, all columns of C have the same statistics, and all sums in  $S_T$  have the same statistics. So it suffices to look at a single coordinate of the data words, say, the last, and to assume that the last bit of the last data word,  $W_{T, U}$ , is 1. How likely is  $S_{T, U} > 0$  if  $W_{T, U} = 1$ ? This likelihood is called the *fidelity* for a single bit, denoted here by  $\varphi$  (phi for 'fidelity'), and we now proceed to estimate it.

The sum vector  $\mathbf{S}_T$  retrieved by the address  $\mathbf{X}_T$  is a sum over the locations activated by  $\mathbf{X}_T$ . The locations are indicated by the 1s of the activation vector  $\mathbf{Y}_T$ , so that  $\mathbf{S}_T = \mathbf{Y}_T^T \mathbf{C}$ , which equals  $\mathbf{Y}_T^T \mathbf{Y}^T \mathbf{W}$  (that  $\mathbf{C} = \mathbf{Y}^T \mathbf{W}$  was shown above). The last coordinate of the sum vector is then  $\mathbf{S}_{T, U} = \mathbf{Y}_T^T \mathbf{C}_{, U} = \mathbf{Y}_T^T \mathbf{Y}^T \mathbf{W}_{, U} =$  $(\mathbf{Y}\mathbf{Y}_T)^T \mathbf{W}_{, U} = (\mathbf{Y}\mathbf{Y}_T) \cdot \mathbf{W}_{, U}$ , which shows that only the last bits of the data words contribute to it. Thus, the *U*th bit-sum is the (inner) product of two vectors,  $\mathbf{Y}\mathbf{Y}_T$ and  $\mathbf{W}_{, U}$ , where the *T*-vector  $\mathbf{W}_{, U}$  consists of the stored bits (the last bit of each stored word), and the *T* components of  $\mathbf{Y}\mathbf{Y}_T$  act as weights for the stored bits.

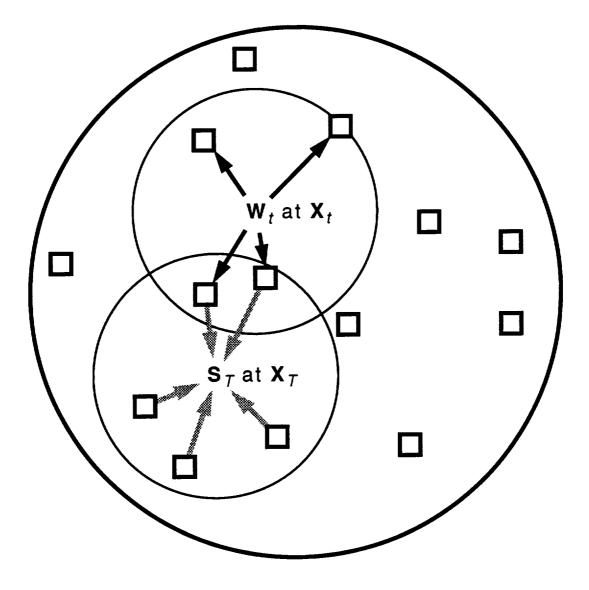

The weights  $\mathbf{Y}\mathbf{Y}_T$  have a clear interpretation in terms of activation sets and their intersections or overlaps: they equal the sizes of the overlaps. This is illustrated in Figure 2-6 (cf. Fig. 2-5). For example, since the 1s of  $\mathbf{Y}_t$  and  $\mathbf{Y}_T$  mark the locations activated by  $\mathbf{X}_t$  and  $\mathbf{X}_T$ , respectively, the weight  $\mathbf{Y}_t \cdot \mathbf{Y}_T$  for the *t*th data word in the sum  $\mathbf{S}_T$  equals the number of locations activated by both  $\mathbf{X}_t$  and  $\mathbf{X}_T$ . Because the addresses are uniform random, this overlap is  $p^2M$  locations on the average, where p is the probability of activating a location, except that for t = T the two activation sets are the same and the overlap is complete, covering pM locations on the average.

(( FIGURE 2-6. Activation overlaps as weights for stored words. ))

In computing fidelity, we will abbreviate notation as follows: Let  $B_t (= \mathbf{W}_{t, U})$ be the last bit of the *t*th data word, let  $L_t = \mathbf{Y}_t \cdot \mathbf{Y}_T$  be its weight in the sum  $\mathbf{S}_{T, U}$ , and let  $\Sigma (= \mathbf{S}_{T, U})$  be the last bit sum. Regard the bits  $B_t$  and their weights  $L_t$  as two sets of *T* random variables, and recall our assumption that addresses and data are uniform random. Then the bits  $B_t$  are independent -1s and 1s with equal probability (i.e., mean  $E\{B_t\} = 0$ ), and they are also independent of the weights. The weights  $L_t$ , being sizes of activation overlaps, are nonnegative integers. When activation is low, as it is in the sample memory (p = 0.000445), the weights resemble independent Poisson variables: the first T - 1 of them have a mean (and variance  $\operatorname{Var}\{L_t\} \approx$ )  $E\{L_t\} = \lambda_t = \lambda = p^2 M$  and the last has a mean (and variance  $\operatorname{Var}\{L_T\} \approx$ )  $E\{L_T\} = \lambda_T = \Lambda = pM$  (i.e., complete overlap). For the sample memory these values are: mean activation  $\Lambda = pM = 445$  locations (out of a million), and mean activation overlap  $\lambda = p^2 M = 0.2$  locations (t < T). We will proceed as if the weights  $L_t$  were independent Poisson variables, and hence our result will be approximate.

We are assuming that the bit we are trying to recover equals 1 (i.e.,  $B_T = \mathbf{W}_{T, U} = 1$ ); by symmetry, the analysis of  $B_T = -1$  is equivalent. The sum  $\Sigma$  is then the sum of T products  $L_t B_t$ , and its mean, or expectation, is

$$\mu = \mathbb{E}\{\Sigma\} = \sum_{t=1}^{T-1} \mathbb{E}\{L_t B_t\} + \mathbb{E}\{L_T \cdot 1\}$$

$$= \mathbb{E}\{L_T\}$$

$$= \Lambda$$

because independence and  $E\{B_t\} = 0$  yield  $E\{L_tB_t\} = 0$  when t < T. The mean sum can be interpreted as follows: it contains all  $\Lambda$  (= 445) copies of the target bit  $B_T$  that have been stored and they reinforce each other, while the other  $(T - 1)\lambda$  (= 2,000) bits in  $\Sigma$  tend to cancel out each other.

Retrieval is correct when the sum  $\Sigma$  is greater than 0. However, random variation can make  $\Sigma \leq 0$ . The likelihood of that happening, depends on the variance  $\sigma^2$  of the sum, which variance we will now estimate. When the terms are approximately independent, their variances are approximately additive, so that

$$\sigma^2 = \operatorname{Var}\{\Sigma\} \approx (T-1)\operatorname{Var}\{L_1B_1\} + \operatorname{Var}\{L_T \cdot 1\}$$

The second variance is simply  $Var\{L_T\} \approx \Lambda$ . The first variance can be rewritten as

$$Var\{L_1B_1\} \equiv E\{L_1^2B_1^2\} - (E\{L_1B_1\})^2$$

$$= E\{L_1^2\}$$

because  $B_1^2 = 1$ , and because  $E\{L_1B_1\} = 0$  as above. It can be rewritten further as

$$\equiv \operatorname{Var}\{L_1\} + (\operatorname{E}\{L_1\})^2$$

$$\approx \lambda + \lambda^2$$

and we get, for the variance of the sum,

$$\sigma^2 \approx (T-1) \, (\lambda + \lambda^2) + \Lambda$$

Substituting  $p^2 M$  for  $\lambda$  and pM for  $\Lambda$ , approximating T - 1 with T, and rearranging finally yields

$$\sigma^2 = \operatorname{Var}\{\Sigma\} \approx pM[1 + pT(1 + p^2M)]$$

We can now estimate the probability of incorrect recall, that is, the probability that  $\Sigma \leq 0$  when  $B_T = 1$ . We will use the fact that if the products  $L_t B_t$  are T independent random variables, their sum  $\Sigma$  tends to the normal (Gaussian) distribution with mean and variance equal to those of  $\Sigma$ . We then get, for the probability of a single-bit failure,

$$\Pr\{\Sigma \le 0 \mid \mu, \sigma\} \approx \Phi(-\mu/\sigma)$$

where  $\Phi$  is the normal distribution function; and for the probability of recalling a bit correctly, or bit-fidelity  $\varphi$ , we get  $1 - \Phi(-\mu/\sigma)$ , which equals  $\Phi(\mu/\sigma)$ .

# **3.6** Signal ( $\mu$ ), Noise ( $\sigma$ ), and Probability of Activation (p)

We can regard the mean value  $\mu (= pM)$  of the sum  $\Sigma$  as signal, and the variance  $\sigma^2$  ( $\approx pM[1 + pT(1 + p^2M)]$ ) of the sum as noise. The standard quantity  $\rho = \mu/\sigma$  is then a signal-to-noise ratio (rho for 'ratio') that can be compared to the normal distribution, to estimate bit-fidelity, as was done above:

$$\varphi = \Pr\{\text{bit recalled correctly}\} \approx \Phi(\rho)$$

The higher the signal-to-noise ration, the more likely are stored words recalled correctly. This points to a way to find good values for the probability p of activating locations and, hence, for the activation radius H: We want p that maximizes  $\rho$ . To find this value of p, it is convenient to start with the expression for  $\rho^2$  and to reduce it to

$$\rho^2 = \mu^2 / \sigma^2 \approx \frac{pM}{1 + pT(1 + p^2M)}$$

Taking the derivative with respect to p, setting it to 0, and solving for p gives

$$p = \frac{1}{\sqrt[3]{2MT}}$$

as the best probability of activation. This value of p was mentioned earlier, and it was used to set parameters for the sample memory.

The probability  $p = (2MT)^{-1/3}$  of activating a location is optimal only when exact storage addresses are used for retrieval. When a retrieval address is approximate (i.e., when it equals a storage address plus some noise), both the signal

and the noise are reduced, and also their ratio is reduced. Analysis of this is more complicated than the one above, and it is not carried out here. The result is that, for maximum recovery of stored words with approximate retrieval addresses, p should be somewhat larger than  $(2MT)^{-1/3}$  (typically, less than twice as large); however, when the data are clustered rather than uniform random, optimum p tends to be smaller than  $(2MT)^{-1/3}$ .

In a case yet more general, the training set is not "clean" but contains many noisy copies of each word to be stored, and the data addresses are noisy (cf. Fig. 2– 1). Then it makes sense to store words within a smaller radius and to retrieve them within a larger. To allow such memories to be analyzed, Avery Wang (unpublished) and Jaeckel (1988) have derived formulas for the size of the overlap of activation sets with different radii of activation. As a rule, the overlap decreases rapidly with increasing distance between the centers of activation.

#### 3.7 Memory Capacity ( $\tau$ )

Storage and retrieval in a standard random-access memory are deterministic. Therefore, its capacity (in words) can be expressed simply as the number of memory locations. In a sparse distributed memory, retrieval of words is statistical. However, its capacity, too, can be defined as a limit on the number T of words that can be stored and retrieved successfully, although the limit depends on what we mean by success.

A simple criterion of success is that a stored bit is retrieved correctly with high probability  $\varphi$  (e.g.,  $0.99 \le \varphi \le 1$ ). Other criteria can be derived from it or are related to it. Specifically, capacity here is the maximum  $T, T_{\text{max}}$ , such that  $\Pr\{\mathbf{Z}_{t, u} = \mathbf{W}_{t, u}\} \ge \varphi$ ; we are assuming that exact storage addresses are used to retrieve the words. It is convenient to relate capacity to memory size M and to define it as  $\tau = T_{\text{max}}/M$ . As fidelity  $\varphi$  approaches 1, capacity  $\tau$  approaches 0, and the values of  $\tau$  that concern us here are smaller than 1. We will now proceed to estimate  $\tau$ .

In Section 3.5 on Recall Fidelity we saw that the bit-recall probability  $\varphi$  is approximated by  $\Phi(\rho)$ , where  $\rho$  is the si2.1-Random-Access Memorygnal-to-noise ratio as defined above. By writing out  $\rho$  and substituting  $\tau M$  for T we get

$$\varphi \approx \Phi(\rho) \approx \Phi\left(\left[\frac{pM}{1+p\tau M(1+p^2M)}\right]^{1/2}\right)$$

which leads to

$$\left[\Phi^{-1}\left(\varphi\right)\right]^{2} \approx \rho^{2} \approx \frac{pM}{1 + p\tau M \left(1 + p^{2}M\right)}$$

where  $\Phi^{-1}$  is the inverse of the normal distribution function. Dividing by pM in the

numerator and the denominator gives

$$\left[\Phi^{-1}\left(\varphi\right)\right]^{2} \approx \frac{1}{\frac{1}{pM} + \tau\left(1 + p^{2}M\right)}$$

The right side goes to  $1/\tau$  as the memory size M grows without bound, giving us a simple expression for the asymptotic capacity:

$$\tau \approx \frac{1}{\left[\Phi^{-1}\left(\phi\right)\right]^2}$$

To verify this limit, we use the optimal probability of activation, taking note that it depends on both M and  $\tau$ :  $p = (2MT)^{-1/3} = (2\tau M^2)^{-1/3}$ . Then, in the expression above,  $1/(pM) = (2\tau/M)^{1/3}$  and goes to zero as M goes to infinity, because  $\tau < 1$ . Similarly,  $\tau(1 + p^2M) = \tau + (\frac{1}{4}\tau/M)^{1/3}$  and goes to  $\tau$ .

To compare this asymptotic capacity to the capacity of a finite memory, consider  $\varphi = 0.999$ , meaning that about one bit in a thousand is retrieved incorrectly. Then the asymptotic capacity is  $\tau \approx 0.105$ , and the capacity of the million-location sample memory is 0.096. Keeler (1988) has shown that the sparse distributed memory and the binary Hopfield net trained with the outer-product leaning rule, which is equivalent to a correlation-matrix memory, have the same capacity per storage element or counter. The 0.15N capacity of the Hopfield net ( $\tau = 0.15$ ) corresponds to fidelity  $\varphi = 0.995$ , meaning that about one bit in 200 is retrieved incorrectly. The practical significance of the sparse distributed memory design is that, by virtue of the hard locations, the number of storage elements is independent of the input and output dimensions. Doubling the hardware doubles the number of words of a given size that can be stored, whereas the capacity of the Hopfield net is limited by the word size.

A very simple notion of capacity has been used here, and it results in capacities of about 10 percent of memory size. However, the assumption has been that exact storage addresses are used in retrieval. If approximate addresses are used, and if less error is tolerated in the words retrieved than in the addresses used for retrieving them, the capacity goes down. The most complete analysis of capacity under such general conditions has been given by Chou (1989). Expressing capacity in absolute terms, for example, as Shannon's information capacity, is perhaps the most satisfying. This approach has been taken by Keeler (1988). Allocating the capacity is then a separate issue: whether to store many words or to correct many errors. A practical guide is that the number of stored words should be from 1 to 5 percent of memory size (the number of hard locations).

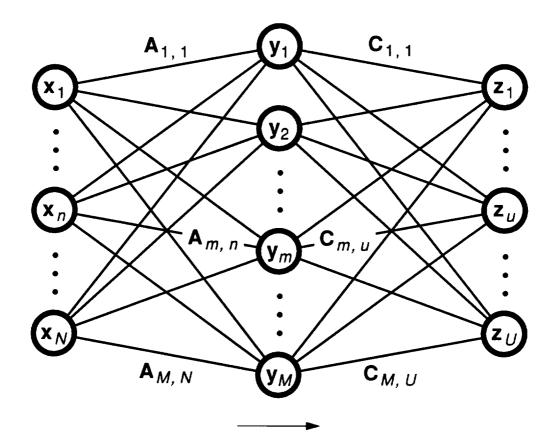

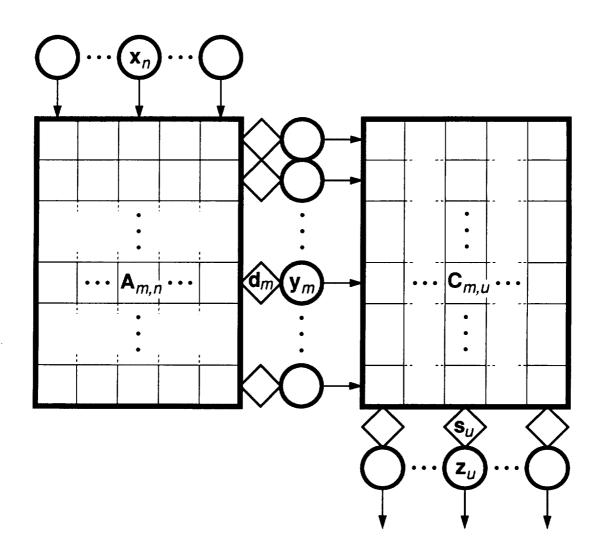

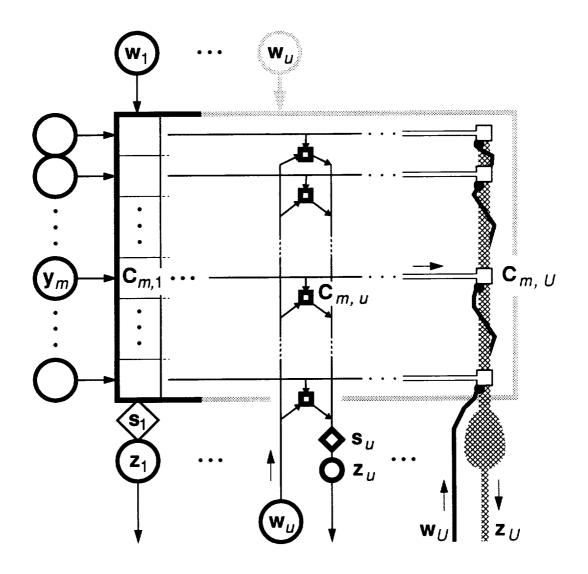

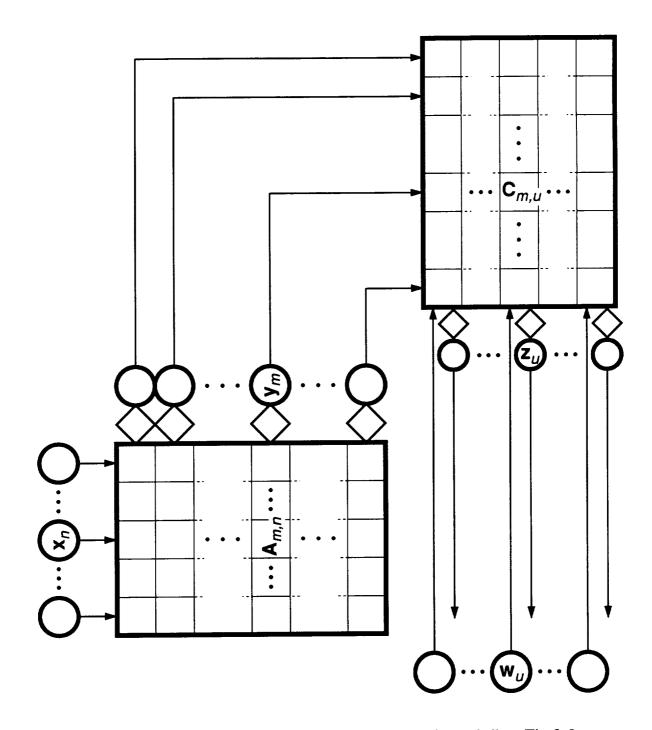

# 4. SDM as an Artificial Neural Network

The sparse distributed memory, as an artificial neural network, is a synchronous, fully connected, three-layer (or two-layer, see below), feed-forward net illustrated by Figure 2–7. The flow of information in the figure is from left to right. The column of N circles on the left is called the *input* layer, the column of M circles in the middle is called the *hidden* layer, and the column of U circles on the right is called the *output* layer, and the columns are called input units, hidden units, and output units, respectively.

(( FIGURE 2-7. Feed-forward artificial neural network. ))

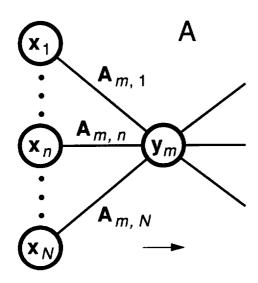

The hidden units and the output units are *bona fide* artificial neurons, so that, in fact, there are only two layers of "neurons." The input units merely represent the outputs of some other neurons. The inputs  $\mathbf{x}_n$  to the hidden units label the input layer, the input coefficients  $\mathbf{A}_{m,n}$  of the hidden units label the lines leading into the hidden units, and the outputs  $\mathbf{y}_m$  of the hidden units label the hidden layer. If y is the activation function of the hidden units (e.g., y(d) = 1 if  $d \ge D$ , and y(d) = 0 otherwise), the output of the *m*th hidden unit is given by

$$\mathbf{y}_m = y\left(\sum_{n=1}^N \mathbf{A}_{m,n} \mathbf{x}_n\right)$$

which, in vector notation, is  $y_m = y(A_m \cdot x)$ , where x is the vector of inputs to, and  $A_m$  is the vector of input coefficients of, the *m*th hidden unit.

A similar description applies to the output units, with the outputs of the hidden units serving as their inputs, so that the output of the *u*th output unit is given by

$$\mathbf{z}_{u} = z \left( \sum_{m=1}^{M} \mathbf{C}_{m, u} \mathbf{y}_{m} \right)$$

or, in vector notation,  $\mathbf{z}_u = z(\mathbf{C}_{\cdot, u} \cdot \mathbf{y})$ . Here,  $\mathbf{C}_{\cdot, u}$  is the vector of input coefficients of the *u*th output unit, and *z* is the activation function.

From the equations above it is clear that the input coefficients of the hidden units form the address matrix **A**, and those of the output units form the contents matrix **C**, of a sparse distributed memory. In the terminology of artificial neural nets, these are the matrices of connection strengths (synaptic strengths) for the two layers. 'Fully connected' means that all elements of these matrices can assume nonzero values. Later we will see sparsely connected variations of the model.

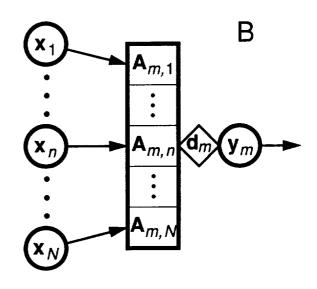

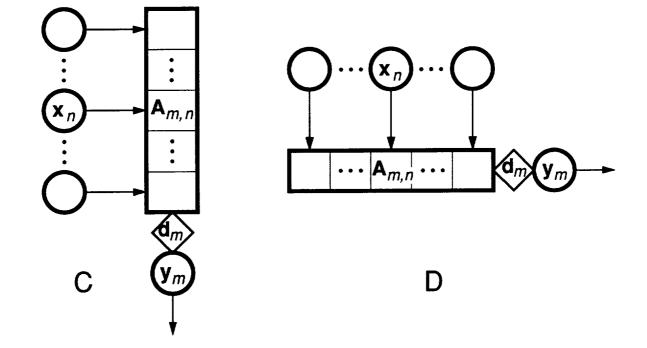

Correspondence between Figures 2–7 and 2–4 is now demonstrated by transforming Figure 2–7 according to Figure 2–8, which shows four ways of drawing artificial neurons. View A shows how they appear in Figure 2–7. View B is laid out similarly, but all labels now appear in boxes and circles. In view C, the

diamond and the circle that represent the inner product and the output, respectively, appear below the column of input coefficients, so that these units are easily stacked side by side. View D is essentially the same as view C, for stacking units on top of each another. We will now redraw Figure 2–7 with units of type D in the hidden layer and with units of type C in the output layer. An input (a circle) that is shared by many units is drawn only once. The result is Figure 2–9. Its correspondence to Figure 2–4 is immediate, the vectors and the matrices implied by Figure 2–7 are explicit, and the cobwebs of Figure 2–7 are gone.

# (( FIGURE 2-8. Four views of an artificial neuron. ))

(( FIGURE 2-9. Sparse distributed memory as an artificial ... ))

In describing the memory, the term 'synchronous' means that all computations are completed in what could be called a machine cycle, after which the network is ready to perform another cycle. The term is superfluous if the net is used as a feedforward net akin to a random-access memory. However, it is meaningful if the network's output is fed back as input: the network is allowed to settle with each input so that a completely updated output is available as the next input.

As a multilayer feed-forward net, the sparse distributed memory is akin to the nets trained with the error back-propagation algorithm (Rumelhart and McClelland 1986). How are the two different? In a broad sense they are not: we try to find matrices A and C, and activation functions y and z, that fit the source of our data. In practice, many things are done differently.

In error back-propagation, the matrices A and C and the activation vector y are usually real-valued, the components of y usually range over the interval [-1, 1] or [0, 1], the activation function y and its inverse are differentiable, and the data are stored using a uniform algorithm to change both A and C. In sparse distributed memory, the address matrix A is usually binary, and various methods are used to choose it, but once a location's address has been set, it is not changed as the data are stored (A is constant); furthermore, the activation function y is a step function that yields an activation vector y that is mostly 0s, with a few 1s. Another major difference is in the size of the hidden layer. In back-propagation nets, the number of hidden units is usually smaller than the number of input units or the number of items in the training set; in a sparse distributed memory, it is much larger.

The differences imply that, relative to back-propagation nets, the training of a sparse distributed memory is fast (it is easy to demonstrate single-trial learning), but applying it to a new problem is less automatic (it requires choosing an appropriate data representation, as discussed in the section on SDM research below).

# 5. SDM as a Model of the Cerebellum

#### 5.1 Modeling Biology with Artificial Neural Networks

Biological neurons are cells that process signals in animals and humans, allowing them to respond rapidly to the environment. To achieve speed, neurons use electrochemical mechanisms to generate a signal (a voltage level or electrical pulses) and to transmit it to nearby and distant sites.

Biological neurons come in many varieties. The peripheral neurons couple the organism to the world. They include the sensory neurons that convert an external stimulus into an electrical signal, the motor neurons whose electrical pulses cause muscle fibers to contract, and other effector neurons that regulate the secretion of glands. However, most neurons in highly evolved animals are interneurons that connect directly to other neurons rather than to sensors or to effectors. Interneurons also come in many varieties and they are organized into a multitude of neural circuits.

A typical interneuron has a cell body and two kinds of arborizations: a dendrite tree that receives signals from other neurons, and an axon tree that transmits the neuron's signal to other neurons. Transmission-contact points between neurons are called synapses. They are either excitatory (positive synaptic weight) or inhibitory (negative synaptic weight) according to whether a signal received through the synapse facilitates or hinders the activation of the receiving neuron. The axon of one neuron can make synaptic contact with the dendrites and cell bodies of many other neurons. Thus, a neuron receives multiple inputs, it integrates them, and it transmits the result to other neurons.

Artificial neural networks are networks of simple, interconnected processing units, called (*artificial*) neurons. The most common artificial neuron in the literature has multiple (N) inputs and one output and is defined by a set of input coefficients— a vector of N reals, standing for the synaptic weights—and a nonlinear scalar activation function. The value of this function is the neuron's output, and it serves as input to other neurons. A linear threshold function is an example of an artificial neuron, and the simplest kind—one with binary inputs and output—is used in the sparse distributed memory.

It may seem strange to model brain activity with binary neurons when real neurons are very complex in comparison. However, the brain is organized in large circuits of neurons working in parallel, and the mathematical study of neural nets is aimed more at understanding the behavior of circuits than of individual neurons. An important fact—perhaps the most important—is that the states of a large circuit can be mapped onto the points of a high-dimensional space, so that although a binary neuron is a grossly simplified model of a biological neuron, a large circuit of binary neurons, by virtue of its high dimension, can be a useful model of a circuit of biological neurons. The sparse distributed memory's connection to biology is made in the standard way. Each row through A, d, y, and C in Figure 2-9—each hidden unit—is an artificial neuron that represents a biological neuron. Vector x represents the N signals coming to these neurons as inputs from N other neurons (along their axons), vector  $A_m$  represents the weights of the synapses through which the input signals enter the *m*th neuron (at its dendrites),  $d_m$  represents the integration of the input signals by the *m*th neuron, and  $y_m$  represents the output signal, which is passed along the neuron's axon to U other neurons through synapses with strengths  $C_m$ .

We will call these (the hidden units) the address-decoder neurons because they are like the address-decoder circuit of a random-access memory: they select locations for reading and writing. The address that the *m*th address-decoder neuron decodes is given by the input coefficients  $A_m$ ; location  $A_m$  is activated by inputs x that equal or are sufficiently similar to  $A_m$ . How similar, depends on the radius of activation *H*. It is interesting that a linear threshold function with *N* inputs, which is perhaps the oldest mathematical model of a neuron, is ideal for address decoding in the sparse distributed memory, and that a proper choice of a single parameter, the threshold, makes it into an address decoder for a location of an ordinary randomaccess memory.

Likewise, in Figure 2–9, each column through C, s, and z is an artificial neuron that represents a biological neuron. Since these U neurons provide the output of the circuit, they are called the output neurons. The synapses made by the axons of the address-decoder neurons with the dendrites of the output neurons are represented by matrix C, and they are modifiable; they are the sites of information storage in the circuit.

We now look at how these synapses are modified; specifically, what neural structures are implied by the memory's storage algorithm (cf. Figs. 2-4 and 2-9). The word  $\mathbf{w}$  is stored by adding it into the counters of the active locations, that is, into the axonal synapses of active address-decoder neurons. This means that if a location is activated for writing, its counters are adjusted upward and downward; if it is not activated, its counters stay unchanged.

Since the output neurons are independent of each other, it suffices to look at just one of them, say, the *u*th output neuron. See Figure 2-10 center. The *u*th output neuron produces the *u*th output bit, which is affected only by the *u*th bits of the words that have been stored in the memory. Let us assume that we are storing the word w. Its *u*th bit is  $w_u$ . To add  $w_u$  into all the active synapses in the *u*th column of C, it must be made physically present at the active synaptic sites of the column. Since different sites in a column are active at different times, it must be made present at all synaptic sites of the column. A neuron's way of presenting a signal is by passing it along the axon. This suggests that the *u*th bit  $w_u$  of the word-in register should be represented by a neuron that corresponds to the *u*th output neuron  $z_u$ , and that its output signal should be available at each synapse in column u, although it is "captured" only by synapses that have just been activated by address-decoder neurons y. Such an arrangement is shown in Figure 2–10. It suggests that word-in neurons are paired with output neurons, with the axon tree of a word-in neuron possibly meshing with the dendrite tree of the corresponding output neuron, as that would help carry the signal to all synaptic sites of a column. This kind of pairing, when found in a brain circuit, can help us interpret the circuit (Fig. 2-10, on the right).

(( FIGURE 2–10. Connections to an output neuron. ))

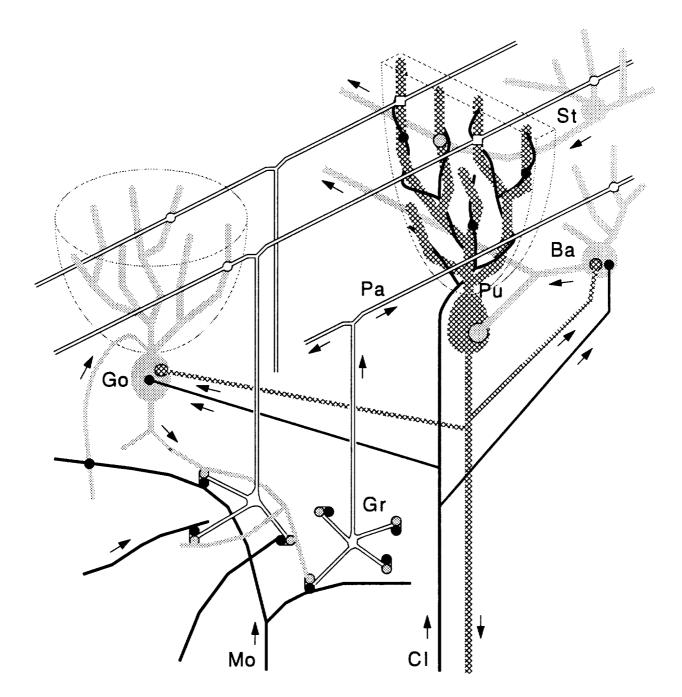

#### 5.2 The Cortex of the Cerebellum

Of the neural circuits in the brain, the cortex of the cerebellum resembles the sparse distributed memory the most. The cerebellar cortex of mammals is a fairly large and highly regular structure with an enormous number of neurons of only six major kinds. Its morphology has been studied extensively since early 1900s, its role in fine motor control has been established, and its physiology is still studied intensively (Ito 1984).

The cortex of the cerebellum is sketched in Figure 2–11 after Llinás (1975). Figure 2–12 is Figure 2–9 redrawn in an orientation that corresponds to the sketch of the cerebellar cortex.

(( FIGURE 2–11. Sketch of the cortex of the cerebellum. ))

(( FIGURE 2-12. Sparse distributed memory's resemblance ... ))

Within the cortex are the cell bodies of five kinds of neurons: the granule cells, the Golgi cells, the stellate cells, the basket cells, and the Purkinje cells. Figure 2–11 shows the climbing fibers and the mossy fibers entering and the axons of the Purkinje cells leaving the cortex. This agrees with the two inputs into and the one output from a sparse distributed memory. The correspondence goes deeper: The Purkinje cells that provide the output, are paired with the climbing fibers that provide input. A climbing fiber, which is an axon of an olivary cell that resides in the interior of the cerebellum, could thus have the same role in the cerebellum as the line from a word-in cell through a column of counters has in a sparse distributed memory (see Fig. 2–10), namely, to make a bit of a data word available at a bit-storage site when words are stored.

The other set of inputs enters along the mossy fibers, which are axons of cells outside the cerebellum. They would then be like an address into a sparse distributed memory. The mossy fibers feed into the granule cells, which thus would correspond to the hidden units of Figure 2–12 (they appear as rows across Fig. 2–9) and would perform address decoding. The firing of a granule cell would constitute activating a location for reading or writing. Therefore, the counters of a location would be found

among the synapses of a granule cell's axon; these axons are called parallel fibers. A parallel fiber makes synapses with Golgi cells, stellate cells, basket cells, and Purkinje cells. Since the Purkinje cells provide the output, it is natural to assume that their synapses with the parallel fibers are the storage sites or the memory's counters.

In addition to the "circuit diagram," other things suggest that the cortex of the cerebellum is an associative memory reminiscent of the sparse distributed memory. The numbers are reasonable. The numbers quoted below were compiled by Loebner (1989) in a review of the literature and they refer to the cerebellum of the cat. Several million mossy fibers enter the cerebellum, suggesting that the dimension of the address space is several million. The granule cells are the most numerous—in the billions—implying a memory with billions of hard locations, and only a small fraction of them is active at once, which agrees with the model. Each parallel fiber intersects the flat dendritic trees of several hundred Purkinje cells, implying that a hard location has several hundred counters. The number of parallel fibers that pass through the dendritic tree of a single Purkinje cell is around a hundred-thousand, implying that a single "bit" of output is computed from about a hundred-thousand counters (only few of which are active at once). The number of Purkinje cells is around a million, implying that the dimension of the data words is around a million. However, a single olivary cell sends about ten climbing fibers to that many Purkinje cells, and if, indeed, the climbing fibers train the Purkinje cells, the output dimension is more like a hundred-thousand than a million. All these numbers mean, of course, that the cerebellar cortex is far from fully connected: every granule cell does not reach every Purkinje cell (nor does every mossy fiber reach every granule cell; more on that below).

This interpretation of the cortex of the cerebellum as an associative memory, akin to the sparse distributed memory, is but an outline, and it contains discrepancies that are evident even at the level of cell morphology. According to the model, an address decoder (a hidden unit) should receive all address bits, but a granule cell receives input from three to five mossy fibers only, and for a granule cell to fire, most or all of its inputs must be firing (the number of active inputs required for firing appears to be controlled by the Golgi cells that provide the other major input to the granule cells; the Golgi cells could control the number of locations that are active at once). The very small number of inputs to a granule cell means that activation is not based on Hamming distance from an address but on certain address bits being on in the address register. Activation of locations of a sparse distributed memory under such conditions has been treated specifically by Jaeckel, and the idea is present already in the cerebellar models of Marr and of Albus. These will be discussed in the next two sections.

Many details of the cerebellar circuit are not addressed by this comparison to the

22

sparse distributed memory. The basket cells connect to the Purkinje cells in a special way, the stellate cells make synapses with the Purkinje cells, and signals from the Purkinje cells and climbing fibers go to the basket cells and Golgi cells. The nature of synapses and signals—the neurophysiology of the cerebellum—has not been considered. Some of these things are addressed by the mathematical models of Marr and of Albus. The point here has been to demonstrate some of the variety in a real neural circuit, to show how a mathematical model can be used to interpret such a circuit, and to suggest that the cortex of the cerebellum constitutes an associative memory. Because its mossy-fiber input comes from all over the cerebral cortex—from many sensory areas—the cerebellum is well located for correlating action that it regulates, with information about the environment.

# 6. Variations of the Model

The basic sparse distributed memory model is fully connected. This means that every input unit (address bit) is seen by every hidden unit (hard location), and that every hidden unit is seen by every output unit. Furthermore, all addresses and words are binary. If -1 and 1 are used as the binary components, 'fully connected' means that none of the elements of the address and contents matrices A and C is (identically) zero. Partially—and sparsely—connected models have zeros in one or both of the matrices, as a missing connection is marked by a weight that is zero.

Jaeckel has studied designs with sparse address matrices and binary data. In the selected-coordinate design (1989a), -1s and 1s are assumed to be equally likely in the data addresses; in the hyperplane design (1989b), the data-address bits are assumed to be mostly (e.g., 90%) -1s. This section is based on these two papers. The papers are written in terms of binary 0s and 1s, but here we will use -1s and 1s, and will let 0 stand for a missing connection or a "don't care"-bit (for which Jaeckel uses the value 1/2). Jaeckel uses one-million-location memories (M = 1,000,000) with a 1,000-dimensional address space (N = 1,000) to demonstrate the designs.

#### 6.1 Jaeckel's Selected-Coordinate Design

In the selected- coordinate design, the hard-address matrix A has a million rows with ten -1s and 1s (k = 10) in each row. The -1s and 1s are chosen with probability 1/2 and they are placed randomly within the row and independently of other rows; the remaining 990 coordinates of a row are 0s. This is equivalent to taking a uniform random A of -1s and 1s and setting a random 990 coordinates in each row to zero (different 990 for different rows). A location is activated if the values of all ten of its selected coordinates match the address register x:  $y_m = 1$  iff  $A_m \cdot x = k$ . The probability of activating a hard location is related to the number of nonzero coordinates in a hard address by  $p = 0.5^k$ . Here, k = 10 and p = 0.001.

#### 6.2 Jaeckel's Hyperplane Design

The hyperplane design deals with data where the addresses are skewed (e.g., 100 1s and 900 -1s). Each row of the hard-address matrix A has three 1s (k = 3), placed at random, and the remaining 997 places have 0s (there are no -1s). A location is activated if the address register has 1s at those same three places:  $y_m = 1$  iff  $A_m \cdot x = k$ . The probability of activating a location is related to the number of 1s in its address by  $p = (L/N)^k$ , where L is the number of 1s in the data addresses x. Here, N = 1,000, L = 100, k = 3, and  $p \approx 0.001$ .

Jaeckel has shown that both of these designs are better than the basic design in recovering previously stored words, as judged by signal-to-noise ratios. They are also easier to realize physically—in hardware—because they require far fewer connections and much less computation in the address-decoder unit that determines the set of active locations.

The region of the address space that activates a hard location in the three designs can be interpreted geometrically as follows: A location of the basic sparse distributed memory is activated by all addresses that are within H Hamming units of the location's address, so that the exciting part of the address space is a hypersphere around the hard address. In the selected coordinate design, a hard location is activated by all addresses in a subspace of the address space defined by the k selected coordinates—that is, by the vertices of an (N - k)-dimensional hypercube. In the hyperplane design, the address space is a hyperplane defined by the number of 1s in an address, L (which is constant over all data addresses), and a hard location is activated by the intersection of the address space with the (N - k)dimensional hypercube defined by the k 1s of the hard address.

The regions have a spherical interpretation also in the latter two designs, as suggested by the activation condition  $A_m \cdot x = k$  (same formula for both designs; see above). It tells that the exciting points of the address space lie on the surface of a hypersphere in Euclidean N-space, with center coordinates  $A_m$  (the hard address) and with Euclidean radius  $(N - k)^{1/2}$  (no points of the address space lie inside the sphere). This gives rise to *intermediate designs*, as suggested by Jaeckel (1989b): let the hard addresses be defined in -1s, 0s, and 1s as above, and let the *m*th hard location be activated by all addresses x within a suitably large hypersphere centered at the hard address. Specifically,  $y_m = 1$  if, and only if,  $A_m \cdot x \ge G$ . The parameters G and k (and L) have to be chosen so that the probability of activating a location is reasonable.

The optimum probability of activation p for the various sparse distributed memory designs is about the same—it is in the vicinity of  $(2MT)^{-1/3}$ —and the reason is that, in all these designs, the sets of locations activated by two addresses, x and x', overlap minimally unless x and x' are very similar to each other. The sets behave in the manner of random sets of approximately pM hard locations each, with two such sets overlapping by  $p^2M$  locations, on the average (unless x and x' are very similar to each other). This is a consequence of the high dimension of the address space.

In the preceding section on the cerebellum we saw that the hard-address matrix A, as implied by the few inputs (3–5 mossy fibers) to each granule cell, is very sparse, and that the number of active inputs required for a granule cell to fire, can be modulated by the Golgi cells. This means that the activation of granule cells in the cerebellum resembles the activation of locations in an intermediate design that is close to the hyperplane design.

Not only are the mossy-fiber connections to a granule cell few (3-5 out of several million), but also the granule-cell connections to a Purkinje cell are few (hundred thousand out of billions), so that also the contents matrix C is very sparse. This aspect of the cerebellum has not been modeled mathematically.

#### 6.3 Hassoun's Pseudorandom Associative Neural Memory

Independently of the above developments, Hassoun (1988) has proposed a model with a random, fixed address matrix A and variable contents matrix C. This model allows us to extend the concepts of this chapter to data with short addresses (e.g., N = 4 bits), and it introduces ideas about storing the data (i.e., training) that can be applied to associative memories at large.

The data addresses X and words W in Hassoun's examples are binary vectors in 0s and 1s. The elements of the hard-address matrix A are small integers; they are chosen at uniform random from the symmetric interval  $\{-L, -L + 1, -L + 2, ..., L\}$ , where L is a small positive integer (e.g., L = 3). Each hard location has its own activation threshold  $D_m$ , which is chosen so that approximately half of all possible N-bit addresses x activate the location:  $y_m = 1$  if  $A_m \cdot x \ge D_m$ , and  $y_m = 0$  otherwise. The effect of such addressing through A is to convert the matrix X of N-bit data addresses into the matrix Y of M-bit activation vectors, where  $M \gg N$  and where each activation vector  $y_m$  is about half 0s and half 1s (probability of activation p is around 0.5).

Geometric interpretation of addressing through A is as follows. The space of hard addresses is an N-dimensional hypercube with sides of length 2L + 1. The unit cubes or cells of this space are potential hard locations. The M hard addresses  $A_m$ are chosen at uniform random from within this space. The space of data addresses is an N-cube with sides of length 2; it is at the center of the hard-address space, with the cell 000...0 at the very center. The data addresses that activate the location  $A_m$ are the ones closest to  $A_m$  and they can be visualized as follows: A straight line is drawn from  $A_m$  through 000...0. Each setting of the threshold  $D_m$  then corresponds to an N - 1-dimensional hyperplane perpendicular to this line, at some distance from  $A_m$ . The cells x of the data-address space that are on the  $A_m$  side of the plane will activate location  $A_m$ . The threshold  $D_m$  is chosen so that the plane cuts the dataaddresses space into two nearly equal parts.

The hard addresses  $A_m$  correspond naturally to points (and subspaces)  $A'_m$  of the data-address space  $\{0, 1\}^N$  gotten by replacing the negative components of  $A_m$  by 0s, the positive components by 1s, and the 0s by either (a "don't care"). The absolute values of the components of  $A_m$  then serve as weights, and the *m*th location is activated by **x** if the *weighted* distance between  $A'_m$  and **x** is below a threshold (cf. Kanerva 1988, pp. 46-48).