Received 1 August 2018; revised 4 October 2018; accepted 7 October 2018. Date of publication 12 October 2018; date of current version 1 March 2019. The review of this paper was arranged by Editor C. C. McAndrew.

Digital Object Identifier 10.1109/JEDS.2018.2875627

# SPICE Modeling of Insulator Metal Transition: Model of the Critical Temperature

SHERIF AMER<sup>®</sup> (Student Member, IEEE), MD SAKIB HASAN<sup>®</sup> (Member, IEEE), MD MUSABBIR ADNAN (Student Member, IEEE), AND GARRETT S. ROSE<sup>®</sup> (Member, IEEE)

Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville, TN 37996, USA

CORRESPONDING AUTHOR: S. AMER (e-mail: samer1@vols.utk.edu)

This work was supported in part by the Air Force Research Laboratory under Agreement FA8750-16-1-0065, and in part by the Air Force Office of Scientific Research under Award FA9550-16-1-0301.

**ABSTRACT** This paper proposes a compact SPICE phenomenological model for insulator metal transition (IMT) devices. The proposed model captures the interplay of electric field and Joule heating to effect a transition from a high resistance insulating state to a low resistance metallic state. The model is corroborated against experimental results and electrothermal simulations available in the literature. The proposed model is implemented in Verilog-A and is fully compatible with commercial SPICE simulators such as Spectre from Cadence, used in this paper. An IMT-based artificial neuron is then designed and simulated using the proposed IMT compact model and design expressions for the operation of the proposed neuron are derived. The simulation results agree with the expected neuron behavior as well as the simulation results of other similar neurons proposed in the literature. This paper will enable circuit designers to design and simulate IMT-based systems and help them explore the full potential of such novel devices.

INDEX TERMS Insulator metal transition, IMT, compact model, SPICE model, neuron, Mott transition.

## I. INTRODUCTION

Insulator Metal Transition (IMT) devices have recently spurred significant interest in the research community [1], [2]. Their switching characteristics have shown to be ideal in applications such as crossbar memory arrays and neuromorphic circuits. For example, in crossbar arrays, IMTs show promising selector characteristics such as high ON/OFF ratio which circumvents sneak path currents and, more importantly, provide Back-End-Of-Line (BEOL) compatibility which helps achieve the ideal  $4F^2$  density of crossbar arrays [3], [4]. On the neuromorphic front, researchers have shown that IMTs can be leveraged in building Integrate-And-Fire (IAF) neurons without the need for complex CMOS circuitry owing to their inherent switching dynamics, thus, providing a significant density advantage [5], [6].

Several works have presented experimental studies on IMT devices attempting to unravel the underlying switching mechanisms contributing to phase transition. Several studies have shown that temperature is the prime cause of phase transition such as the work in [7] and [8] while others have attributed the transition to the electric field [9] with temperature playing a secondary role. A more in depth study about the switching mechanism is presented in [10] and [11] which show that Joule heating may not be sufficient for phase transition and an electric field assisted transition is more plausible. Yang *et al.* [10] hypothesize that a certain threshold voltage is required to effect a phase transition which decreases with increasing temperature. Lin *et al.* [12] have classified IMT devices into two categories: Electronic IMT (E-IMT) and Thermally-driven IMT (T-IMT) and the characteristics of each type have been studied.

The lack of a physics-based compact model, however, has hindered circuit designers from exploring the full potential of IMTs in circuit applications. In particular, understanding the interplay between temperature and electric field has been the main stumbling block to the development of such a compact model [12]. In [5], an electro-thermal model was developed for IMT devices which leverages the positive electro-thermal feedback to effect a phase transition of the device. The model was compared to vanadium oxide  $(VO_2)$  experimental data and could reproduce the data with sufficient accuracy. In [13], a similar model was developed based on the Mott insulator theory and provides a device simulation framework for modeling IMT devices.

On the neuromorphic front, researchers found that the intrinsic dynamics of IMT devices can be leveraged in the design of artificial neurons. In [6] and [14], an IMT-based neuron was proposed. This work, however, did not include the temperature dynamics in the IMT model nor did it study their effect on the IMT-based neuron. In [15] and [16], an IMT-based neuron coupled with a temperature-based model for the IMT device was proposed. However, the model proposed in that work is complex and may not be readily integrated in SPICE simulators nor can it be easily used to derive simple design expressions to facilitate the design process for IMT neurons. Also, the neurons proposed in these works are studied in a larger system.

In this work, a SPICE compatible IMT compact model is developed and implemented in Verilog-A. The proposed model describes the IMT device as a memristive system wherein the state variable is the local temperature of the device. The model is simulated using Spectre from Cadence and shows a close match to experimental results and electrothermal simulations based on the models in [5] and [13]. Using the proposed model, an IMT based artificial neuron is designed and simulated using Spectre from Cadence. Design expressions and oscillation conditions for the proposed design are derived based on the proposed model. Background about previous modeling efforts for IMT devices is described in Section II. Section III describes the proposed compact model. Section IV validates the model against experimental data and electrothermal simulations available in the literature. The IMT-based artificial neuron is described in Section V and the proposed design is presented in Section VI. Section VII provides discussions and future prospects about IMT fabrication and device requirements and Section VIII presents the conclusions.

# **II. BACKGROUND**

Two IMT device models were proposed in [5] and [13]. In [5], a device model that captures the positive feedback between the temperature and electric field was presented. In this model, however, the relationship between the device resistance and the device temperature was implemented using a look up table. This method, while it might be favorable in a device simulation framework, is not compatible with SPICE simulators which require closed form compact models for efficient circuit simulation.

A more refined device model was developed in [13] based on band theory. The IMT device is modeled as a low bandgap semiconductor. Increasing the device temperature results in decreasing the bandgap. This decrease in the bandgap results in an increase of the carrier concentration which ultimately results in decreasing the device resistance. A model is also presented which captures the change in the thermal conductivity with temperature. The bandgap model and the thermal conductivity model are then solved in a self consistent manner to effect a phase transition as a function of temperature. The model in [13] was implemented in Sentaurus TCAD simulator wherein the built-in electrothermal models and finite element drift-diffusion model where leveraged. This model, similar to the previous one, is best used in a TCAD simulation flow and not SPICE level simulators.

The proposed compact model, presented in the next section, builds upon both electrothemal models wherein simplifications such as using lumped element thermal model and proposing a phenomenological relationship between the device temperature and resistance were employed to arrive at a closed form model suitable for integration in commercial SPICE simulators.

### **III. THE PROPOSED IMT SPICE MODEL**

The switching dynamics of IMT devices have been attributed to the interaction of electric field and Joule heating as alluded to before. As the current flows through the device, the device temperature rises until it hits a critical temperature at which point the device transitions from a high resistance insulating phase to a low resistance metallic phase. As the device cools down, the resistance relaxes back to its initial high resistance state.

Here we leverage the memristor theory [17]–[19] to describe the IMT device. The memristive dynamics of the IMT device can be described as follows [20]:

$$I = G(x).V,\tag{1}$$

$$\frac{dx}{dt} = g(x, V), \tag{2}$$

where (1) and (2) describe the output and state equations, respectively, with x being the state variable. The proposed model has two main governing equations: (I) the resistance change equation which corresponds to the output equation (here we used the resistance rather than conductance for modeling convenience) and (II) the temperature evolution equation which corresponds to the state equation, with the temperature being the state variable such that x = T(t).

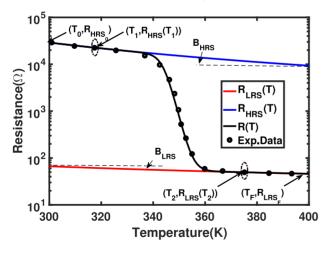

The behavior of the resistance change versus temperature can be captured by two thermistor states for the high resistance and low resistance states and a sigmoid function for the transition from a high resistance state to a low resistance state. Since the thermistance behavior depicts a linear relationship between the resistance and the temperature in the Log-Linear plot, one can simply model the two thermistor states as exponential functions of the temperature such that  $R_{LRS} = R_{LRSF}e^{-B_{LRS}(T(t)-T_F)}$  and  $R_{HRS} = R_{HRS_0}e^{-B_{HRS}(T(t)-T_0)}$ .  $R_{LRSF}$  is the low resistance state defined at temperature  $T_F$  (a reference temperature) and  $R_{HRS_0}$  is the high resistance state defined at the ambient temperature  $T_0$ .  $B_{LRS}$  and  $B_{HRS}$  are the temperature coefficients which are extracted from the slope of the thermistance vs. temperature plot and the negative sign describes Negative Temperature Coefficient (NTC) thermistors. This implementation, however, requires clipping of the  $R_{LRS}$  and  $R_{HRS}$  at some minimum and maximum values to avoid any unphysical behavior during circuit simulation. Clipping, however, requires the use of conditionals which hampers the "smoothness" of the model yielding potential convergence difficulties during circuit simulation. Hence, we reformulate the model equations such that  $R_{LRS}$  and  $R_{HRS}$  smoothly plateau to  $R_{LRSF}$ and  $R_{HRS0}$  at high and low temperatures, respectively.

This relationship between the temperature and the resistance can be expressed as follows:

$$R_{LRS} = R_{LRS_F} (1 + K_{LRS}^A)^{\frac{1}{A}}, \qquad (3a)$$

$$R_{HRS} = R_{HRS_0} \left( \frac{\kappa_{HRS}}{\left(1 + \kappa_{HRS}^A\right)^{\frac{1}{A}}} \right), \tag{3b}$$

$$R_{IMT} = R_{LRS} + \frac{(R_{HRS} - R_{LRS})}{1 + e^{\frac{T(t) - T_c}{T_x}}},$$

(3c)

where  $K_{LRS} = e^{-B_{LRS}(T(t)-T_F)}$  and  $K_{HRS} = e^{-B_{HRS}(T(t)-T_0)}$ .  $T_x$  is a fitting parameter that captures the sharpness of the resistive transition.  $T_c$  is the critical temperature which is around 340K in the case of VO<sub>2</sub> devices [6].  $R_{LRS}$  and  $R_{HRS}$  are the Low Resistance State and High Resistance State, respectively. *A* is a control parameter which governs how the two thermistor states approach the asymptotes [21]. In this work,  $A = 10^4$  is used. However, this parameter can be varied by the user as needed. While the model might seem complicated at first glance, the principal equations are simple exponential functions as aforementioned. This formulation is only employed to abide by compact modeling practices as suggested in [21] and [22]. Appendix A provides a more thorough explanation for (3) and describes the parameter extraction procedure.

The temperature evolution dynamics are described by the compact thermal model in [23] as shown in (4):

$$C_{th}\frac{dT(t)}{dt} = V_{IMT}I_{IMT} - \frac{(T(t) - T_0)}{R_{th}},$$

(4)

where  $V_{IMT}I_{IMT}$  is the Joule heating,  $C_{th}$  and  $R_{th}$  are the effective thermal capacitance and the effective thermal resistance, respectively, and  $T_0$  is the ambient temperature. This model assumes that the device stays at an effective temperature T(t) and exchanges heat with the ambient environment at an ambient temperature  $T_0$ .

Listing 1 depicts Verilog-A code snippet of the core model equations. Suggested good practices for writing compact models are considered based on the work in [24] and [25]. Note that (3a) and (3b) are each split into two equations in the VerilogA implementation. This formulation is to avoid numerical overflow as the values for  $K_{LRS}$  and  $K_{HRS}$  become large; see [21] for more detailed explanation. However, one can readily show that the expressions in each conditional are mathematically identical and, hence, the use of conditionals will not introduce any discontinuities.

```

Iwr = I(p, n);

V(p,n) <+ Iwr*Rm;

K HRS=exp(-B HRS*(tem-T 0));

K\_LRS=exp(-B\_LRS*(tem-T\_F));

(tem>T_F) begin

LRS=LRSF*pow((1+pow(K_LRS,A)),1/A);

end

else begin

LRS=LRSF*K_LRS*pow((1+pow(K_LRS,-A)),1/A);

end

if (tem>T_0) begin

HRS=HRS0*K_HRS/(pow((1+pow(K_HRS,A)),1/A));

end

else begin

HRS=HRS0/(pow((1+pow(K_HRS,-A)),1/A));

end

Rm= LRS + (HRS-LRS) / (1+exp((tem-Tc)/Tx));

Pwr(temp) <+ ddt(Temp(temp));</pre>

Pwr(temp) <+ -pow(Iwr,2) *Rm/Cth;</pre>

Pwr(temp) <+ (Temp(temp) -T0) / (Rth*Cth);</pre>

```

Listing 1. Verilog-A code snippet.

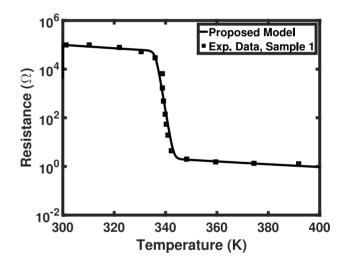

Fig. 1. Model fitting against experimental data.

## IV. MODEL VALIDATION AGAINST EXPERIMENTAL RESULTS AND ELECTRO-THERMAL SIMULATIONS

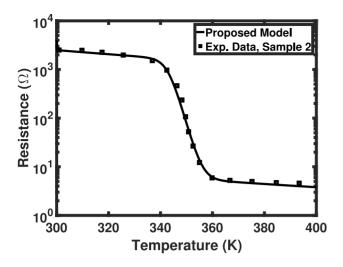

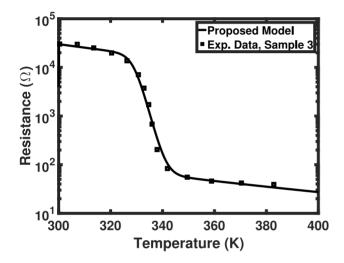

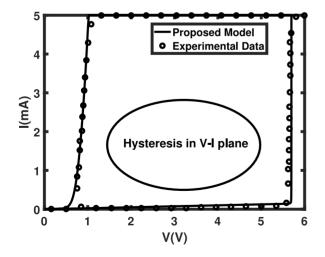

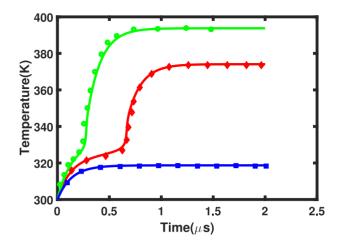

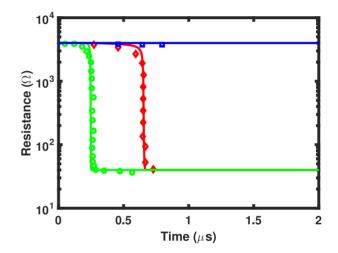

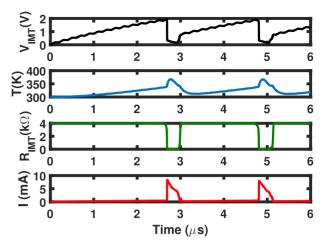

The proposed model is validated against the results in [5]. The proposed model closely matches the experimental results as well as electro-thermal simulation as shown in Figs. 1, 2, 3, 4, 5 and 6. Fig. 1, 2 and 3 depict the resistive transition about the critical temperature which is about 340*K* in VO<sub>2</sub> devices fitted against experimental data from [5]. Fig. 4 depicts the hysteresis in the V-I plane (a fingerprint of memristive systems) exhibited by the IMT device as shown in [5] and [6] and fitted against the experimental data from [5]. Figures 5 and 6 depict the time dependence of temperature and resistance evolution, respectively, fitted against electrothermal simulations from [5]. Three voltage

Fig. 2. Model fitting against experimental data.

Fig. 3. Model fitting against experimental data.

Fig. 4. Demonstration of device Hysteresis in the V-I plane which demonstrates the memristive dynamics of the IMT device.

levels, based on the values used from [5], were applied across the device: 1.4V, 1.6V and 1.8V. One can readily observe in Fig. 5 that the local temperature of the device saturates

Fig. 5. Model (solid line) fitting against electro-thermal simulations (markers). Plotting the Device local temperature against time for three applied voltage values.

Fig. 6. Model (solid line) fitting against elector-thermal simulations (markers). Plotting the Device resistance against time for three applied voltage values.

at a higher temperature value for higher voltages due to increased Joule heating. In Fig. 6, higher voltages result in faster transition time due to faster rate of joule heating.

## **V. SIMULATION OF AN ARTIFICIAL NEURON USING IMT**

This section showcases the utility of the proposed model in a SPICE level simulation framework. The proposed neuron circuit in [5] is simulated in Cadence environment using Spectre circuit simulator with the IMT model implemented in VerilogA.

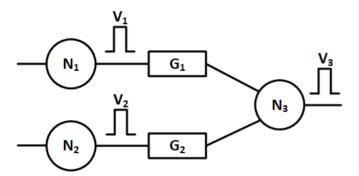

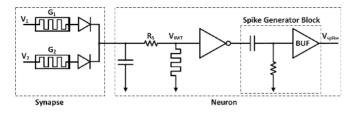

A typical neuromorphic system consists of synapses and neurons. First, inputs to the synapse network are multiplied by their corresponding weights. In memristive neuromorphic systems, the weights are often represented by the conductance of a nonvolatile memristive device (typically, a transition metal oxide in most of state-of-the-art architectures), the inputs are the voltages across the device and the output, result of the multiplication, is the current flowing through the device such that Ohm's law is leveraged for multiplication without the need for additional complex circuitry. The current through the synapses are then summed and fed to the neuron input. The neuron compares the inputs to a threshold and fires if the input signal exceeds the threshold. The neuron then remains idle for a period of time known as the refractory period wherein no fires can take place. A schematic of a neuromorphic system is presented in Fig. 7.

Fig. 7. Schematic of a neuromorphic system.

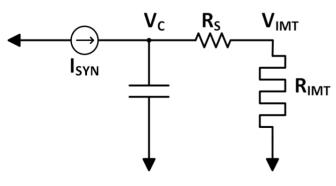

Here, since the aim is to validate the utility of the proposed IMT SPICE model, we replicate the circuit presented in [5]. The accumulated sum through the synaptic weight is represented by a current source feeding into a capacitor such that:

$$\Sigma I_{SYNAPSE} = \Sigma V_i G_i, \tag{5}$$

where  $V_i$  is the voltage spike generated by the *ith* input neuron and  $G_i$  is the conductance (weight) of the *ith* synaptic element. The core of the neuron is the IMT device which switches from  $R_{HRS}$  to  $R_{LRS}$  once the temperature exceeds  $T_c$ . Unlike conventional CMOS neurons, here the neuron's threshold is the device temperature, not a specified voltage value. Fig. 8 depicts the circuit under study.

Fig. 8. Schematic of an IMT neuron Circuit.

Fig. 9 depicts the SPICE simulation of the circuit in Fig. 8. Current pulses were supplied through the capacitor to model voltage spikes multiplied by their corresponding weights. As time evolves, the voltage across the IMT  $V_{IMT}$  increases as well as the device temperature T(t) due to Joule heating. Once the temperature hits  $T_c$ , the resistance of the IMT

Fig. 9. Simulation of an IMT neuron using the proposed mode [5].

$R_{IMT}$  switches to  $R_{LRS}$  and a current spike is generated. The system then remains idle for a period of time equal to the refractory period as shown in Fig. 9 where the capacitor does not accumulate voltage as long as the IMT is at  $R_{LRS}$ . After the device cools down, the resistance relaxes back to  $R_{HRS}$  and the capacitor starts to accumulate voltage while the device starts to heat up again. The obtained SPICE simulation results capture the neuron behavior shown in [5]. Table 1 depicts the device parameters used in the simulation of the circuit in Fig. 9.  $R_{LRS/HRS}$  were extracted from the device geometry and resistivity based on  $R = \rho . L/A$ .

| Parameter              | Symbol             | Value           |

|------------------------|--------------------|-----------------|

| Thermal Resistance     | $R_{th}(K/W)$      | $41.6X10^{3}$   |

| Thermal Capacitance    | $C_{th}(J/K)$      | $3.17X10^{-12}$ |

| High Resistivity State | $\rho_h(\Omega.m)$ | $1X10^{-3}$     |

| Low Resistivity State  | $\rho_l(\Omega.m)$ | $1X10^{-5}$     |

| Area                   | $A(m^2)$           | $5X10^{-13}$    |

| Width                  | W(m)               | $2.5X10^{-6}$   |

| Length                 | L(m)               | $2X10^{-6}$     |

| Ambient Temperature    | $T_0(K)$           | 300             |

| Series Resistance      | $R_S(\Omega)$      | 200             |

TABLE 1. IMT VerilogA model parameters for neuron circuit simulation.

#### VI. PROPOSED IMT-BASED IAF NEURON

The proposed neuron builds off the proposed circuit in [5]. First, the current source is replaced by a synaptic network. Second, an output stage is added in order to provide signal restoration as well as convert the current spike into voltage spike as the output of the neuron serves as an input to the following stages. Fig. 10 depicts the proposed design. Input pulses are fed into the synaptic network wherein each synaptic element is comprised of a nonvolatile memristive device to store the synaptic weight and a diode (a rectifying device) to prevent any back current. The proposed design functions in much the same way as the circuit in Fig. 8 until the current spike is generated. The current spike is then fed

Fig. 10. Schematic of the proposed neuron circuit.

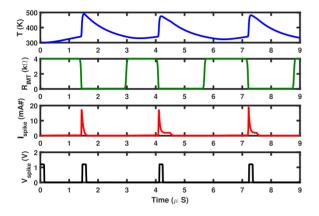

to an inverter to generate a voltage pulse. A spike generation circuit is then added to produce an output voltage spike with a pulse width controlled by the RC time constant of the RC network preceding the output buffer. Fig. 11 depicts the simulation of the proposed design.

## Fig. 11. Simulation of the proposed neuron.

It is important to understand the impact of the design parameters on the operation of the proposed neuron. The essence of neuron oscillation rests in the IMT device alternating between  $R_{HRS}$  and  $R_{LRS}$ . At  $R_{HRS}$ , the steady state temperature exceeds the critical temperature and, accordingly, the neuron fires. At  $R_{LRS}$ , the steady state temperature drops below the critical temperature, the neuron resets and the process is repeated for the next inputs.

At steady state  $\left(\frac{dT}{dt} = 0\right)$ , the solution to the differential equation in (4) can be expressed as follows:

$$T_{ss} = T_0 + R_{th} I_{IMT}^2 R_{IMT}, ag{6}$$

where  $T_{ss}$  is the steady state temperature of the IMT device. Hence, according to the aforementioned explanation, the oscillation condition can be expressed as follows:

$$R_{th} I_{IMT}^2 R_{LRS} < T_c - T_0 < R_{th} I_{IMT}^2 R_{HRS},$$

(7)

Inequality (7) establishes the oscillation condition for the IMT-based neuron as a function of device parameters such as  $R_{th}$ ,  $R_{LRS}$ ,  $R_{HRS}$  and  $T_c$  and circuit variables such as  $I_{IMT}$  which is a function of the amplitude of the voltage spike and the series resistance with the IMT device including the synapse resistance, diode ON resistance and the IMT series resistance. This oscillation is the essence of operation of the IAF neuron as shown in [6]. The relaxation oscillator is a typical circuit that exhibits oscillation which can be found in Appendix B.

The neuron typically operates in three phases: (I) accumulation wherein the inputs from the synapse networks are summed, (II) firing when the accumulated value reaches the neuron's threshold and (III) refractory period wherein the neuron is idle.

In CMOS neurons, an OPAMP is required for accumulation (Integrator) and another is required for comparison against the threshold (comparator). Also, a feedback circuitry is often needed to implement the refractory period. These OPAMPS, besides entailing all the complexities of analog design, are also area consuming and power hungry. For example, extra capacitors are often needed for stability purposes which usually consume significant area.

On the other hand, the IMT device can provide the accumulation function through the heating of the device, fire through device transition and a refractory period during device cooling should the device be placed in such configuration. One can readily see the advantages provided by the IMT device. A typical CMOS neuron, such as the work in [26], requires more than 20 transistors while the proposed IMT-based neuron only requires 7 transistors.

# **VII. DISCUSSIONS AND FUTURE PROSPECTS**

Here the values used for  $R_{HRS}$  and  $R_{LRS}$  are both relatively low which also agree with the experimental results in [5]. It should be noted, however, that this represents a limitation on the fabrication of such devices. Higher  $R_{HRS}$  values might require a significantly long period of time until the device hits the  $T_c$  which might be practically unfeasible. This problem can be overcome, however, via increasing the value of the applied voltage. Yet, another limitation is that the applied voltage should remain within the practical bounds of standard CMOS processes.

These values may not be suitable, however, for memory application. In memory arrays, IMT devices are typically used as selector devices to circumvent sneak path currents. Hence, low  $R_{HRS}$  values might not effectively suppress those unwanted leakage currents. This prospect shows that  $R_{HRS}/R_{LRS}$  values might vary depending on the application.

Finally, as alluded to before, understanding the exact switching dynamics of IMT devices is still subject to further research and, accordingly, the models might require constant refinements. The compact model developed in this work is based on the most established understanding of the switching mechanism of IMT devices available in the literature. Also, the developed compact model was fitted against device models (TCAD-like models) wherein the same physical switching mechanism was considered but with simpler formulation to arrive at closed form expression which can be easily implemented in SPICE simulators. However, further studies of IMT switching dynamics might reveal new switching mechanisms and physics which will require adjustments to the models.

## **VIII. CONCLUSION**

This work presented a SPICE compatible compact model for Insulator Metal Transition devices validated against experimental data and electrothermal simulations from the literature. The proposed model describes the IMT device as a memristive system and captures the role of temperature and electric field in the resistive transition of the device. Using the proposed model, a simple neuron was designed and simulated in Spectre. Design expressions for the neuron's oscillation where derived. The results agree with the expected neuron behavior and published experimental data. Impact of device parameters on the system performance were also discussed and device requirements for efficient circuit operation were projected.

# APPENDIX A IMT MODEL PARAMETER EXTRACTION

In this section, we develop the parameter extraction procedure of the proposed model. We primarily focus on the resistance model and show how  $B_{HRS}$  and  $B_{LRS}$  are extracted. First, the simplified form of equation (3) is used in the extraction procedure, described in Section III, which can be expressed in the following form:

$$ln(R_{LRS}) = ln(R_{LRS_F}) - B_{LRS}(T(t) - T_F), \qquad (8)$$

$$ln(R_{HRS}) = ln(R_{HRS_0}) - B_{HRS}(T(t) - T_0),$$

(9)

four data points are then used to extract the thermal coefficients ( $B_{HRS}$  and  $B_{LRS}$ ) as shown in Fig. 12. The thermal coefficients can be expressed as follows:

$$B_{LRS} = \frac{ln(R_{LRS_F}) - ln(R_{LRS})}{T_2 - T_F},$$

(10)

$$B_{HRS} = \frac{ln(R_{HRS_0}) - ln(R_{HRS})}{T_1 - T_0},$$

(11)

Fig. 12. Thermal coefficients extraction.

As alluded to before, the value chosen for A in this work is  $A = 10^4$ . The higher the value of A, the faster  $R_{HRS}$  and  $R_{LRS}$  saturate to  $R_{HRS_0}$  and  $R_{LRS_0}$  beyond  $T_0$  and  $T_F$ , respectively.

## **APPENDIX B**

#### **RELAXATION OSCILLATOR DESIGN**

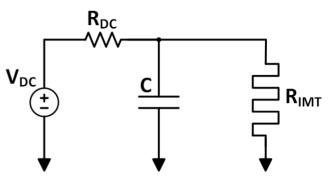

Here we analyze an IMT-based relaxation oscillator and derive the Oscillation conditions. The relaxation oscillator is a simpler circuit than the proposed neuron with the same operation principle. Thus, analyzing this simple circuit may aid with the understanding of the proposed neuron circuit. Fig. 13 depicts the IMT-based relaxation oscillator proposed in [16].

Fig. 13. Schematic of the relaxation oscillator.

A DC voltage is applied at the circuit's input. At steady state  $\left(\frac{dT}{dt} = 0\right)$ , the solution to the differential equation in (4) can be expressed as follows:

$$T_{ss} = T_0 + R_{th} I_{IMT}^2 R_{IMT}, \qquad (12)$$

where the current through the IMT device (at steady state) can be expressed as follows:

$$I_{IMT} = \frac{V_{DC}}{R_{DC} + R_{IMT}},\tag{13}$$

To ensure oscillation:

$$T_{ss}(R_{LRS}) < T_c < T_{ss}(R_{HRS}), \tag{14}$$

Substituting (12) and (13) in (14):

$$\frac{R_{th}R_{LRS}V_{DC}^2}{(R_{LRS} + R_{DC})^2} < T_c - T_0 < \frac{R_{th}R_{HRS}V_{DC}^2}{(R_{HRS} + R_{DC})^2},$$

(15)

Hence, one can readily see that given an IMT device with some arbitrary thermal resistance, high resistance state and low resistance state, circuit variables such as the applied DC voltage and the series resistance can impact the oscillation condition and, thus, should be carefully chosen.

# ACKNOWLEDGMENT

The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the United States Air Force.

## REFERENCES

- A. Pergament, G. Stefanovich, and A. Velichko, "Oxide electronics and vanadium dioxide perspective: A review," *J. Selected Topics Nano Electron. Comput.*, vol. 1, no. 1, pp. 24–43, 2013, doi: 10.15393/j8.art.2013.3002.

- [2] Y. Zhou and S. Ramanathan, "Mott memory and neuromorphic devices," *Proc. IEEE*, vol. 103, no. 8, pp. 1289–1310, Aug. 2015, doi: 10.1109/JPROC.2015.2431914.

- [3] M. Son *et al.*, "Excellent selector characteristics of nanoscale VO<sub>2</sub> for high-density bipolar ReRAM applications," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1579–1581, Nov. 2011, doi: 10.1109/LED.2011.2163697.

- [4] L. Gao, K. E. Holbert, and S. Yu, "Total ionizing dose effects of gamma-ray radiation on NbO<sub>x</sub>-based selector devices for crossbar array memory," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 6, pp. 1535–1539, Jun. 2017, doi: 10.1109/TNS.2017.2700434.

- [5] J. Lin et al., "Low-voltage artificial neuron using feedback engineered insulator-to-metal-transition devices," in Proc. IEEE Int. Electron Devices Meeting (IEDM), 2016, pp. 1–4, doi: 10.1109/IEDM.2016.7838541.

- [6] P.-Y. Chen, J.-S. Seo, Y. Cao, and S. Yu, "Compact oscillation neuron exploiting metal-insulator-transition for neuromorphic computing," in *Proc. ACM Int. Conf. Comput.-Aided Design*, 2016, pp. 1–6, doi: 10.1145/2966986.2967015.

- [7] D. Ruzmetov, S. D. Senanayake, V. Narayanamurti, and S. Ramanathan, "Correlation between metal-insulator transition characteristics and electronic structure changes in vanadium oxide thin films," *Phys. Rev. B, Condens. Matter*, vol. 77, no. 19, 2008, Art. no. 195442, doi: 10.1103/PhysRevB.77.195442.

- [8] E. Freeman *et al.*, "Characterization and modeling of metal-insulator transition (MIT) based tunnel junctions," in *Proc. 70th Annu. Device Res. Conf. (DRC)*, 2012, pp. 243–244.

- [9] D. Ruzmetov, G. Gopalakrishnan, J. Deng, V. Narayanamurti, and S. Ramanathan, "Electrical triggering of metal-insulator transition in nanoscale vanadium oxide junctions," *J. Appl. Phys.*, vol. 106, no. 8, 2009, Art. no. 083702, doi: 10.1063/1.3245338.

- [10] Z. Yang, S. Hart, C. Ko, A. Yacoby, and S. Ramanathan, "Studies on electric triggering of the metal-insulator transition in VO<sub>2</sub> thin films between 77 k and 300 k," *J. Appl. Phys.*, vol. 110, no. 3, 2011, Art. no. 033725, doi: 10.1063/1.3619806.

- [11] G. Gopalakrishnan, D. Ruzmetov, and S. Ramanathan, "On the triggering mechanism for the metal–insulator transition in thin film VO<sub>2</sub> devices: Electric field versus thermal effects," *J. Mater. Sci.*, vol. 44, no. 19, pp. 5345–5353, 2009, doi: 10.1007/s10853-009-3442-7.

- [12] J. Lin et al., "Physics and technology of electronic insulatorto-metal transition (E-IMT) for record high on/off ratio and low voltage in device applications," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2017, pp. 1–4, doi: 10.1109/IEDM.2017.8268446.

- [13] K. Karda, C. Mouli, S. Ramanathan, and M. A. Alam, "A selfconsistent, semiclassical electrothermal modeling framework for Mott devices," *IEEE Trans. Electron Devices*, vol. 65, no. 5, pp. 1672–1678, May 2018, doi: 10.1109/TED.2018.2817604.

- [14] L. Gao, P.-Y. Chen, and S. Yu, "Exploiting NbO<sub>x</sub> metal-insulatortransition device as oscillation neuron for neuro-inspired computing," in *Proc. IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, 2017, pp. 152–153.

- [15] M. D. Pickett, G. Medeiros-Ribeiro, and R. S. Williams, "A scalable neuristor built with Mott memristors," *Nat. Mater.*, vol. 12, no. 2, pp. 114–117, 2013.

- [16] M. D. Pickett and R. S. Williams, "Sub-100 fj and sub-nanosecond thermally driven threshold switching in niobium oxide crosspoint nanodevices," *Nanotechnology*, vol. 23, no. 21, 2012, Art. no. 215202.

- [17] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 7191, pp. 80–83, 2008, doi: 10.1038/nature06932.

- [18] L. Chua, "Memristor-the missing circuit element," *IEEE Trans. Circuit Theory*, vol. CT-18, no. 5, pp. 507–519, Sep. 1971, doi: 10.1109/TCT.1971.1083337.

- [19] L. O. Chua and S. M. Kang, "Memristive devices and systems," *Proc. IEEE*, vol. 64, no. 2, pp. 209–223, Feb. 1976, doi: 10.1109/PROC.1976.10092.

- [20] C. Leon, "Everything you wish to know about memristors but are afraid to ask," *Radioengineering*, vol. 24, no. 2, p. 319, 2015.

- [21] Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor. New York, NY, USA: Oxford Univ. Press, 2011.

- [22] C. C. McAndrew *et al.*, "Best practices for compact modeling in Verilog-A," *IEEE J. Electron Devices Soc.*, vol. 3, no. 5, pp. 383–396, Sep. 2015.

- [23] P.-Y. Chen and S. Yu, "Compact modeling of RRAM devices and its applications in 1T1R and 1S1R array design," *IEEE Trans. Electron Devices*, vol. 62, no. 12, pp. 4022–4028, Dec. 2015, doi: 10.1109/TED.2015.2492421.

- [24] T. Wang and J. Roychowdhury, "Well-posed models of memristive devices," arXiv preprint arXiv:1605.04897, 2016.

- [25] T. Wang, "Modelling multistability and hysteresis in ESD clamps, memristors and other devices," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, 2017, pp. 1–10, doi: 10.1109/CICC.2017.7993681.

- [26] G. Chakma et al., "Memristive mixed-signal neuromorphic systems: Energy-efficient learning at the circuit-level," *IEEE J. Emerg. Sel. Topics Circuits Syst.*, vol. 8, no. 1, pp. 125–136, Mar. 2018.

**SHERIF AMER** received the B.S. and M.S. degrees in electronics and communications engineering from the American University in Cairo, Cairo, Egypt, in 2014 and 2016, respectively. He is currently pursuing the Ph.D. degree in electrical engineering with the University of Tennessee, Knoxville.

His research interests include nanoelectronic device modeling and circuit design.

**MD SAKIB HASAN** received the B.Sc. degree in electrical and electronic engineering from the Bangladesh University of Engineering and Technology, Dhaka, Bangladesh in 2009 and the Ph.D. degree in electrical engineering from the University of Tennessee, Knoxville, in 2017 with the dissertation on modeling and circuit implementation of SOI four gate transistors. He is currently a Post-Doctoral Research Associate with the Department of Electrical Engineering and Computer Science, University of Tennessee. His

research interests include semiconductor device modeling, VLSI circuit design, secure nanoelectronic circuit design, and neuromorphic computing.

**MD MUSABBIR ADNAN** received the B.Sc. degree in electrical and electronic engineering from the Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, in 2015. He is currently pursuing the Ph.D. degree in computer engineering with the University of Tennessee, Knoxville, where he is a member of SENECA Research Group. His research interests include neuromorphic computing, VLSI design of nano-electronic circuits, and emerging devices.

**GARRETT S. ROSE** (S'98-M'06) received the B.S. degree in computer engineering from Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, in 2001 and the M.S. and Ph.D. degrees in electrical engineering from the University of Virginia, Charlottesville, in 2003 and 2006, respectively with the dissertation on the topic of circuit design methodologies for molecular electronic circuits and computing architectures.

From 2011 to 2014, he was with the Air Force Research Laboratory, Information Directorate, Rome, NY, USA. From 2006 to 2011, he was an Assistant Professor with the Department of Electrical and Computer Engineering, Polytechnic Institute of New York University, Brooklyn, NY, USA. From 2004 to 2005, he was with the MITRE Corporation, McLean, VA, USA, involved in the design and simulation of nanoscale circuits and systems. He is currently an Associate Professor with the Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville, where his research is focused in the areas of nanoelectronic circuit design, neuromorphic computing, and hardware security. His research interests include low-power circuits, system-on-chip design, trusted hardware, and developing VLSI design methodologies for novel nanoelectronic technologies.

Dr. Rose serves and has served on Technical Program Committees for several IEEE conferences, including ISVLSI, GLSVLSI, and NANOARCH, and workshops in the area of VLSI design. In 2010, he was a Guest Editor for a special issue of the ACM Journal of Emerging Technologies in Computing Systems that presented key papers from the IEEE/ACM International Symposium on Nanoscale Architectures. From 2014 to 2017, he was an Associate Editor of the IEEE TRANSACTIONS ON NANOTECHNOLOGY. He is a member of the Association of Computing Machinery, IEEE Circuits and Systems Society, and IEEE Computer Society.