# **SPIRAL: Extreme Performance Portability**

This paper provides an end-to-end discussion of the SPIRAL system, its domain-specific languages, and code generation techniques.

By Franz Franchetti<sup>®</sup>, Senior Member IEEE, Tze Meng Low, Member IEEE, Doru Thom Popovici, Student Member IEEE, Richard M. Veras, Member IEEE, Daniele G. Spampinato, Member IEEE, Jeremy R. Johnson, Senior Member IEEE, Markus Püschel, Senior Member IEEE, James C. Hoe, Fellow IEEE, and José M. F. Moura<sup>®</sup>, Fellow IEEE

ABSTRACT | In this paper, we address the question of how to automatically map computational kernels to highly efficient code for a wide range of computing platforms and establish the correctness of the synthesized code. More specifically, we focus on two fundamental problems that software developers are faced with: performance portability across the ever-changing landscape of parallel platforms and correctness guarantees for sophisticated floating-point code. The problem is approached as follows: We develop a formal framework to capture computational algorithms, computing platforms, and program transformations of interest, using a unifying mathematical formalism we call operator language (OL). Then we cast the problem of synthesizing highly optimized computa-

tional kernels for a given machine as a strongly constrained optimization problem that is solved by search and a multistage rewriting system. Since all rewrite steps are semantics preserving, our approach establishes equivalence between the kernel specification and the synthesized program. This approach is implemented in the SPIRAL system, and we demonstrate it with a selection of computational kernels from the signal and image processing domain, software-defined radio, and robotic vehicle control. Our target platforms range from mobile devices, desktops, and server multicore processors to large-scale high-performance and supercomputing systems, and we demonstrate performance comparable to expertly hand-tuned code across kernels and platforms.

**KEYWORDS** | Automatic performance tuning; performance engineering; program generation; program synthesis; SPIRAL

Manuscript received May 24, 2018; revised September 18, 2018; accepted September 19, 2018. Date of current version October 25, 2018. This material is based on research sponsored by DARPA under Agreements FA8750-12-2-0291, FA8750-16-2-0033, HR0011- 13-2-0007, DOI Grant NBCH1050009, and ARO Grant W911NF0710416. This work was supported by the National Science Foundation (NSF) under Awards 0325687, 0702386, and 0931987; by the U.S. Office of Naval Research (ONR) under Grant N000141110112; and by Intel. Nvidia, and Mercury. This work was supported in part by the Department of Defense under Contract FA8702-15-D-0002 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center [DM17-0413]. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of DARPA or the U.S. Government. (Corresponding author: Franz Franchetti.)

F. Franchetti, T. M. Low, D. T. Popovici, D. G. Spampinato, J. C. Hoe, and J. M. F. Moura are with the Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA 15213 USA (e-mail: franzf@ece.cmu.edu).

- **R. M. Veras** is with the Center for Computation and Technology, Louisiana State University, Baton Rouge, LA 70803 USA.

- **J. R. Johnson** is with the College of Computer and Informatics, Drexel University, Philadelphia, PA 19104-2875 USA.

- M. Püschel is with the Department of Computer Science, ETH Zürich, 8092 Zürich, Switzerland.

Digital Object Identifier 10.1109/JPROC.2018.2873289

# I. INTRODUCTION

Computer architects are experimenting with ever more complex systems containing manycore processors, graphics processors, field-programmable gate arrays (FPGAs), and a range of speculation techniques to keep Moore's law on track and to keep systems within their power envelope. This enormous growth of computing power is a boon to scientists; however, it comes at a high cost: the development of efficient and correct computing applications has become increasingly more difficult and complex. Already on a single central processing unit (CPU), the performance of an inefficient implementation can be 10–100 times slower than the fastest code written by an expert. Thus, significant effort has to be invested by highly sophisticated programmers to attain the desired performance on modern platforms that include multiple CPUs or accelerators.

0018-9219 © 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

At the heart of this effort is the inherent tension between performance, software abstraction, and code maintainability as programmers have to constantly develop for the latest release of the newest platform.

Current tools such as advanced compiler frameworks and automatic performance tuning (autotuning) systems allow portability across a wide range of platforms and algorithms while also attaining reasonable performance. However, automatically achieving near-optimal performance for performance-relevant mathematical operations has been shown to be difficult. Part of the reason for this difficulty is that programs do not exactly capture the desired input—output behavior. They are often over-specified either due to language requirements or programmer decisions while writing code. As such, the expert programmer often has to hand-code their highly optimized implementation with low-level machine-specific instructions (assembly) in order to attain appropriate high performance when high-performance library code is not available.

In this paper, we present a complete overview of the Spiral system. Spiral is a program and library generation/synthesis and autotuning system that translates rule-encoded high-level specifications of mathematical algorithms into highly optimized/library-grade implementations for a large set of computational kernels and platforms. The system has been developed over the last 20 years and is freely available as open source under a BSD-style license. Spiral formalizes a selection of computational kernels from the signal and image processing domain, software-defined radio (SDR), numerical solution of partial differential equations, graph algorithms, and robotic vehicle control, among others. Spiral targets platforms spanning from mobile devices, to desktop and server multicore processors, and to large high-performance and supercomputing systems, and it has demonstrated performance comparable to expertly hand-tuned code across a variety of kernels and diversity of platforms. To maximize portability and to leverage the work of backend compiler developers, when producing software SPIRAL usually targets vendor compilers such as the Intel C compiler or IBM's XL C compiler, or widely available compilers such as the GNU C compiler or LLVM, and only rarely generates assembly code directly.

#### A. Contributions

This paper presents an end-to-end description of the current status of the Spiral system and its underlying program generation methodology. We detail:

- the formal framework to describe computational kernels:

- the machine model used to target both known and novel, yet-unknown machines;

- the constraint solving system that derives a search space of candidate programs for a given platform and computational kernel;

- the autotuning approach that yields high performance;

- correctness guarantees and applied verification methods;

- results across a range of platforms for a range of computational kernels.

High-level algorithm representation of linear signal transforms using the signal processing language (SPL) and rule trees, aspects of SIMD vectorization for SSE and SMP parallelization using OpenMP, search and autotuning, as well as performance modeling are discussed in the previous SPIRAL overview paper [1], but will be discussed as necessary to make this paper self-contained.

# **B.** Synopsis

Section II describes the high level and conceptual aspects of Spiral. Section III introduces hardware, algorithm, and program transformation abstractions in a unified framework. Section IV discusses how term rewriting, constraint solving, and domain-specific language (DSL) compilers interact to synthesize optimized software implementations and hardware designs, as well as co-optimize combined hardware/software systems. Section V demonstrates with select results the quality of Spiral generated software and hardware. Section VI describes current work aiming at extending its capabilities and how to obtain the newly released open-source version of Spiral. Finally, Section VII offers a summary and conclusion.

#### II. OVERVIEW

The key observation in the SPIRAL system is that the mathematics underlying computational kernels changes slowly and provides a well-developed language to describe algorithms, while target computer platforms change frequently. Consider some of the basic mathematical and physical concepts that underlie commonly used computational kernels: geometry (Euclid, 300 BC [2]), Gaussian Elimination (unknown Chinese scholars, 179 AD [3]), equations of motion (Newton, 1687 [4]), and the fast Fourier transform (FFT, Gauss, 1805 [5]). Further, consider how FFTs have evolved since Gauss: rediscovered in 1965 by Cooley and Tukey [6], further FFT variants in subsequent years, formalized in matrix form extended and popularized in 1992 by Van Loan [7].

In contrast, consider the release timeline of classes of processors that have been targeted by Spiral: single core x86 CPU with cache in personal computers (mid-1990s), multicore CPU (Pentium D, 2005), GPGPU (GeForce 8800, 2006), manycore CPU (Xeon Phi, 2011). Even if we were to restrict the discussion to Intel CPUs, the rate at which new versions and microarchitectures are released is staggering [8]. Moreover, the range of platforms successfully targeted by Spiral spans orders of magnitude in peak performance: mobile and embedded devices (ARM CPUs and multicores), desktop and server class CPUs (up to tens of cores and gigabytes to terabytes of shared memory), accelerators (graphics processors, Xeon PHI, FPGAs), and large parallel machines such as BlueGene/L/P/Q and the K computer with up to almost 800,000 cores.

# A. Goal and Approach

1) Goal: The goal of SPIRAL is to provide performance portability for well-defined, ubiquitously needed computational kernels across a wide range of continuously changing computational devices. Specifically, SPIRAL aims to automatically generate an implementation that satisfies the functional specification of a given problem on a given platform. The implementation should rival the performance that the best human expert programmer can achieve. Further, SPIRAL aims to provide evidence of correctness for this generated implementation. This problem statement addresses questions of programmability, performance portability, and rapid prototyping. SPIRAL builds on Johnson *et al.*, methodology that connected the mathematics of fast Fourier transforms to programs and computer architectures [9]–[11].

2) Approach: The SPIRAL solution is as follows: 1) develop a formal framework to capture computational algorithms, computing platforms, and program transformations of interest through a unifying mathematical formalism we call *operator language* (OL); and 2) cast the problem of synthesizing highly optimized computational kernels for a given machine as a tightly constrained optimization problem that is solved by a multistage rewriting system that uses semantics-preserving operations. This approach allows us to formally prove the equivalence between the kernel specification and the synthesized program.

The formal system has three main components.

- · Algorithms such as the famous Cooley-Tukey FFT algorithm are captured in OL, which encompasses a family of DSLs that capture various aspects and refinements of specifications and algorithms for computational kernels. The top level DSL (called tagged OL, tOL) captures the input-output behavior of kernels (i.e., their semantics). A midlevel DSL (called operator language, OL, which extends SPL) captures the computation as data flow graph. At an even lower level, a DSL called  $\Sigma$ -OL (pronounced Sigma-OL) captures folded data flow graphs and can be interpreted as providing loop abstractions. Finally, a DSL called icode (an abstract internal code representation) captures a small subset of C in the form of abstract syntax trees (ASTs) and can be given pure functional semantics for a relevant subset of programs.

- Hardware such as a multicore CPU, FPGA, or GPU is modeled through OL expressions that can be implemented efficiently on the given hardware. The idea is that algorithms that can be composed exclusively (or mainly) from these expressions can be mapped efficiently to the associated hardware.

- Program transformations such as loop tiling, fission, and fusion are captured as rewriting rules coupled with a tagging mechanism. Rewriting rules transform  $OL/\Sigma$ -OL expressions into more efficient expressions

that can be composed from the hardware-based OL expressions. The tagging mechanism facilitates the introduction of higher level program transformations such as parallelism.

These three components of the system are used to construct a space of suitable programs for a given OL specification that can be mapped efficiently to Spiral's machine model of a given hardware instance. Conceptually, this is done by intersecting a space of programs that run efficiently on the given hardware with a space of algorithms that implement the desired computational specification, subject to applicable program transformations. The result is a search space in which every point is an algorithm for the given specification that runs efficiently on the given hardware. Finally, an autotuning system traverses this search space and uses a DSL compiler to translate the points in the search space into high-performance implementations.

This approach of mapping a specification to highly optimized implementations across a wide range of machines solves the forward problem: mapping computations to architectures. The inverse problem of finding the best architecture for a given specification, i.e., algorithm/hardware co-optimization can be solved by iteratively solving multiple forward problems while traversing the architecture space.

3) Success: The Spiral approach and associated systems have been developed over the last two decades. The initial focus was on linear transform algorithms including the FFT. The first basic approach of mapping a mathematical DSL to efficient C or Fortran code using a search mechanism for optimization was presented in [12]–[14]. The approach was then expanded to include a larger set of linear transforms and range of computing platforms [1], [15], thus offering a program generation solution for what is later identified as the spectral dwarf in Berkeley's 7 dwarfs/11 motifs classification [16]. The focus of this paper is the work of the last decade in which we expanded the Spiral approach to a much larger scope of computational kernels, while earlier work before 2005 is discussed in [1].

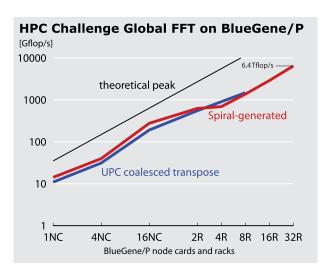

Using the systematic rewriting approach, SPIRAL has demonstrated, over the last two decades, the automatic generation of expert-level performance code across a wide range of microarchitectures. Specifically, SPIRAL has successfully targeted modern CPUs with multilevel caches [1], [12], [13], [17], [18], multiple cores [19], [20], SIMD vector instructions [21]–[29], and multisocket systems with large main memory [30], fixed-point arithmetic [31], fused multiply–add instructions [32], modulo arithmetic [33]), GPUs [34]–[36], DSPs [37], the Cell BE [34], [38], Larrabee and Xeon PHI [39], FPGAs [39]–[45], clusters [47], up to 128k cores on BlueGene/L/P/Q [47]–[49], the K computer, and in presilicon settings (IBM Cell BE [38], BlueGene/L, Intel AVX and Xeon Phi [39]).

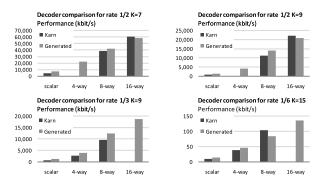

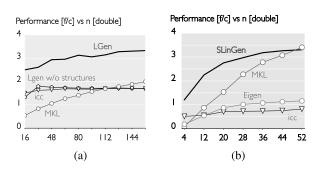

The original focus of SPIRAL was linear transforms [1], [15] such as the discrete Fourier transform [20], [51], linear filters [52], and the discrete wavelet transform [53], and is described in detail in [1]. Since then, the approach and the associated DSLs have been expanded to a range of kernels [54], [55] including the image formation algorithm in SAR [56], components of JPEG 2000 [57], Viterbi decoders [58], SDR [58], [59], matrix multiplication [54], and quantum chemistry kernels [61]. An entire generator devoted to small-scale linear algebra applications was built in [28], [62], and [63]. Support for some multigrid applications [64] and Poisson [61] solvers was also introduced, and we synthesized sensor fusion and control code kernels [65].

Rewriting in Spiral handles the basic mapping to a given target platform, but leaves a space of candidate alternatives for further tuning. To navigate this space, Spiral uses various search methods [1], models [66], but also machine learning approaches [65]–[68].

SPIRAL can be used as a low-level backend code generation tool and kernel generator for polyhedral compiler infrastructures [71], [72] and as a programming tool for special purpose hardware [73]. The formal framework of Spiral lends itself to mathematical correctness arguments [65], [74]. SPIRAL was used to produce parts of Intel's MKL and IPP libraries (it generated 1 million lines of code for IPP's IPPgen module) [75], [76], codelets for the BlueGene/L/P/Q fastest Fourier transform in the west (FFTW) version [48], [77], and Mercury's Scientific Algorithms Library (SAL) [78]. A more principled design and implementation of Spiral using modern language features including pattern matching, staging, and embedded DSLs was studied in [79] and [80] and provides a Spiral prototype implemented in Scala. An experimental Haskell version was also developed in this context [81]. Current work includes extending SPIRAL to support graphs and sparse matrices algorithms, as well as proving the correctness of Spiral's program generation toolchain within the Coq system.

4) Limitations: Generating code that is competitive with the best human-written code across a wide range of platforms is inherently a difficult task. This task is made even more complex when one requires the system to be extensible. Within SPIRAL, we simplify this task by restricting the problem domain to domains and algorithms that can be described in terms of recursive specifications. In addition, possible variations and developer choices must be extracted as free parameters. The specification needs to be encoded as a rewrite rule in a term rewriting system in a DSL with mathematical semantics, and all relevant algorithmic and parametric degrees of freedom need to be expressed. Developing such a specification can be a hard research problem, even for well-understood mathematical kernels, as evidenced by the development time line of Spiral's FFT capabilities [15]. As listed above, we have shown that it is possible to capture other domains

beyond FFTs, but the effort in each case was considerable. Furthermore, adding a new hardware feature computational paradigm (such as vector instructions or multiple cores as they appeared), or program transformation, also requires encoding this knowledge in Spiral's formal system. Surprisingly, this tends to be an easier task than adding a new kernel.

While the Spiral developers have strived for complete coverage of the supported architecture and kernel/application space, a number of the results detailed above were demonstrated as one-off solutions. At one end of the spectrum, the FFT is most completely supported across all platforms targeted by Spiral. At the other end of the spectrum, some coding and communication kernels are only prototypically supported for a single platform [57].

SPIRAL's internal languages are DSLs with mathematical semantics. A mathematics-style notation lends itself to capturing algorithm and program optimization rules concisely, e.g., as done in a book. However, the mathematical notation and its implementation in the dated computer algebra system it was built on still poses a considerable hurdle to adoption. Therefore, we often wrapped up a part of Spiral's capabilities in easy-to-use parameterized generators (e.g., on the web at www.spiral.net) or as a command line tool in a compiler tool chain [71], [72]. We have also exposed part of Spiral's Spi/OL language as a MATLAB tensor library with high-dimensional map, reduce, reshape, and rotate operations in the style of hierarchically tiled arrays (HTAs) [82], [83].

Writing OL specifications is complicated. The specification needs to capture the exact semantics of the computational kernel without introducing superfluous information that may obscure the mathematical specification. Machine abstractions need to be structurally accurate, and standard program transformations need to be recoded as OL rewrite rules. Spiral's implementation in GAP (groups, algorithms, and programming, version 3) [84] adds to the complexity of writing specifications. At this writing, we have had success with web interfaces that expose only part of Spiral's capabilities and with an experimental MATLAB frontend that implements a subset of OL and a C library frontend that extends the FFTW interface [85]. Building Spiral and its DSLs within a powerful multiparadigm language such as Scala can increase maintainability and extensibility [79], [80]. Further, we are pursuing efforts to enable Spiral as a just-in-time (JIT) compiler. We hope that these advancements will make Spiral more accessible to general programmers.

#### B. Related Work

We now discuss the most important approaches and projects of the various technologies that are related to the Spiral project.

1) Performance Libraries: Mathematical performance libraries provide a uniform interface to key functionality across multiple platforms, but have been optimized

by hand for each target platform to obtain performance. Prominent examples include the Intel Math Kernel Library (MKL) [75] and Integrated Performance Primitives (IPP) [76], AMD's Core Math Library (ACML) [86], Cray's Scientific Library (SciLib) [87], IBM's Engineering and Scientific Subroutines Library (ESSL) [88], Mercury Computing's Scientific Algorithms Library (SAL), the Basic Linear Algebra Subroutines (BLAS) [87]–[90], and LAPACK [93]. The BLAS-like Library Instantiation Software (BLIS) [94] is a framework for instantiating a set of functions larger than BLAS from a set of microkernels. Spiral originated as a tool to help automate FFT kernels for some of these libraries, and Spiral-generated kernels can be found in the Intel MKL, IPP, and Mercury's SAL.

2) Compilers: Polyhedral compiler frameworks such as PetaBricks [95], CHiLL [96], R-Stream [97], PLuTo and PTile [98], Polly [99], [100], and the Polyhedral Parallel Code Generator (PPCG) [101] have their strength in regular and dense computations on standard parallel machines and accelerators, and extensions to sparse polyhedral computations have been investigated. Other approaches include annotation-based compilation [102] and the concept of telescoping languages [103].

Many HPC high-level languages follow the partitioned global address space (PGAS) paradigm to provide portability across distributed memory machines. The historically most important examples are HPF and FortranD [104], [105]. Chapel [106], X10 [107], UPC [108], and Co-Array Fortran [109] are other example of languages in this space. Systems such as PEAK [110], PetaBricks [95], Sequoia [111], CHiLL [96], the polyhedral infrastructures Pluto [98], Primetile [112], CLooG [113], as well as the GNU C interactive compilation interface (GCC ICI) and Milepost GCC [114] use autotuning and machine learning. Spiral captures many of the program transformation techniques used by these languages and systems, and its internal representation allows for extracting and capturing information that usually has to be derived by analysis or provided via annotations.

LIVM, Open64, and the GNU compiler suite are open compilers designed to be retargeted to a wide range of instruction set architectures (ISAs). These compilers have backends that can accept new ISAs and that can support novel instructions. Spiral is leveraging the intrinsics interface and vector data type abstractions provided by these open compilers as well as commercial compilers such as the Intel C++ compiler and IBM's XL C compiler to provide portable code generation across a wide range of SIMD vector extensions of CPU ISAs such as x86, POWER, and ARM.

3) Language Extensions: OpenCL, CUDA, OpenMP, and OpenACC extend C or FORTRAN with language constructs and/or pragmas to annotate the source code with information and instructions for the parallelizing/offload compiler. These language extensions require powerful high-level optimizing compilers to generate highly efficient code.

SPIRAL utilizes them as backend compilers to abstract hardware details and attain better portability, but performs all necessary high-level transformations itself.

- 4) High-Level Synthesis: Vivado HLS and BlueSpec [115] translate higher-level language programs into hardware blocks (IP blocks) for FPGAs so that users are freed from some of the tedious work required when directly specifying hardware in Verilog or VHDL. Spiral directly targets Verilog and experimentally targets Vivado HLS to enable quick porting to novel FPGA architectures.

- 5) Code Generators and Autotuners: The autotuning community is the home of a number of influential projects that include code generators and/or autotuning systems for numerical software. Important autotuning projects include the adaptive FFT library FFTW [116], [117], the dense numerical linear algebra project ATLAS [118], [119], the sparse matrix–vector multiplication library OSKI [120], [121], and the quantum chemistry tensor contraction system TCE [122]. SPIRAL is firmly rooted in this community. General autotuning infrastructures that can be used independently of the optimization target include ActiveHarmony [123], Orio [124], and ppOpen-AT [125].

- 6) Generative Programming for Performance: Generative programming has gained considerable interest [126,127,128,129,130]. The basic goal is to reduce the development, maintenance, and analysis of software. Among the key tools, DSLs provide a compact representation that raises the level of abstraction for specific problems and hence enables the manipulation of programs [129]–[132]. C++, Haskell, MetaOCaml, and Scala are often used as host languages to embed DSLs [135]. The SEJITS [136] specializer specializes kernels to low-level implementations. The Delite [137] framework offers a set of optimized parallel patterns to DSLs that can be implemented on top of it. Other approaches are based on multistaging frameworks such as lightweight modular staging (LMS) [79], [137], [138] and Terra [139].

Other examples of DSL-based approaches are query compilers [140], [141] based on a stack of DSLs with progressive lowering of abstractions. Stencil code generators include [71], and Lift [142], which combines a high-level functional data parallel language with a system of rewrite rules that encodes algorithmic and hardware-specific optimization choices.

7) DSLs for HPC Libraries: The build-to-order (BTO) BLAS [143], [144] is a domain-specific compiler for matrix computations. BTO focuses on memory-bound computations (BLAS 1 and 2 operations) and relies on a compiler for vectorization. Cl1ck [145], [146] implements the formal linear algebra methods environment (FLAME) [147] methodology for automatically deriving algorithms for higher-level linear algebra functions [148] given as mathematical equations. The supported functions are mostly those covered by the LAPACK library and the generated

algorithms rely on the availability of a BLAS library. DxTer [149] transforms blocked algorithms such as those generated by Cl1ck and applies transformations and refinements to output high-performance, distributed-memory implementations. The CLAK compiler [150] finds efficient mappings of matrix equations onto building blocks from high-performance libraries such as BLAS and LAPACK.

8) DSLs for Matrix and Stencil Optimization: Another generative approach is adopted by Eigen [151], uBLAS [152], the Matrix Template Library (MTL) [153], STELLA [154], Halide [155], [156], and the Tensor Algebra Compiler (TACO) [157], among others. They use C++ expression templates to optimize the code at compile time. Optimizations include loop fusion, unrolling, and SIMD vectorization. The HTAS [82], [83], which offer data types with the ability to dynamically partition matrices and vectors, automatically handle situations of overlapping areas. HTAs' goal is to improve programmability by reducing the amount of code required to handle tiling and data distribution in parallel programs, leaving any optimization to the programmer (or program generator).

9) Frameworks and Computer Algebra Systems: Systems such as Sketch [158] and Paraglide [159] automatically synthesize software according to a specification. Rewriting systems are reviewed in [160]. Logic programming is discussed in [161]. An overview of functional programming can be found in [162]. Spiral does not employ SAT solvers but solves a specialized constraint programming problem through term rewriting.

Python, R, Julia, MATLAB, Java, and C++, and frameworks such as Caffe [163], Theano [164], and TensorFlow [165] are commonly used by data scientists to express graph analytics and machine learning algorithms. Computer algebra systems such as Maple [166], YACAS [167], and Mathematica [168], interactive numerical systems such as MATLAB [169], as well as interactive theorem proving systems based on higher order logic [170] and the R system for statistical computing [171] provide interactive capabilities to solve complex problems in engineering, mathematics, logic, and statistics. Spiral is built on top of the computer algebra system GAP and uses many of these concepts.

# III. ALGORITHM AND HARDWARE ABSTRACTION

We now discuss the different OL abstractions within SPIRAL that we use to capture specifications, algorithms, algorithmic degrees of freedom, hardware capabilities, and program transformations. The key idea is to capture this information into a single formal system that combines multiple rewriting systems with constraint solving and automatic performance tuning. Algorithms are captured symbolically as data flow graphs that are expanded recursively by identity rules. The target hardware is modeled by the set of all data flow graph fragments it can execute efficiently and a grammar that describes all programs that

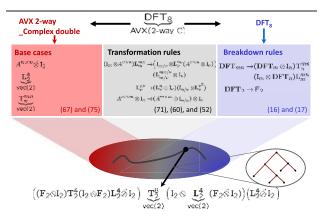

Model: common abstraction = spaces of matching formulas

Fig. 1. SPIRAL's approach: The architecture space (red circle, left), the algorithm space (blue circle, right), and program transformations (shown as space in between) are abstracted in a joint formal framework.

can be built from these fragments. Rewriting rules are essentially program transformations that map an algorithm to more efficient algorithms while preserving correctness.

The overall approach is shown in Fig. 1. The architecture space (red circle, left), the algorithm space (blue circle, right), and program transformations (shown as space in between) are abstracted in a joint formal framework. Abstracting the three components in a compatible way allows Spiral to impose architecture requirements on algorithms and utilize the necessary program transformations.

In this section, we first discuss the algorithm abstraction, followed by the formalization of data layout and program transformations, and finally the hardware abstraction. In the next section (Section IV), we will discuss how these abstractions interact to implement rewriting, constraint solving, and autotuning in SPIRAL's code synthesis process.

# A. Algorithm Abstraction

1) Specification: In SPIRAL, the top-level objects are specifications of computational kernels. A kernel is a function that performs a mathematical operation on its input data to produce its output. Kernels are modeled as parameterizable mathematical operators that map vectors to vectors. SPIRAL operators are stateless (any state would have to be an explicit parameter and matching result value). Higher-dimensional data are linearized and sparsity is abstracted as discussed below. In general, operators can take multiple-input vectors and produce multiple-output vectors. We allow a range of mathematical base types for the vectors, including fields ( $\mathbb{R}$ ,  $\mathbb{C}$ ,  $\mathrm{GF}(k)$ ), rings ( $\mathbb{Z}$ ,  $\mathbb{Z}_n$  with n not prime), and semi-rings (e.g., min/sum semiring, etc. [172]). Operators act as problem specifications in our formal system.

For instance, the scalar product/dot product is mathematically a bilinear operator and defined in Spiral as

$$\langle .,. \rangle_n : \mathbb{R}^n \times \mathbb{R}^n \to \mathbb{R}; (x,y) \mapsto x \cdot y.$$

(1)

Note that we annotate the operator symbol by its vector length n, which will allow us to more concisely describe algorithms and transformations. A specification such as (1) explains unambiguously the input—output behavior of the operator (its semantics) but does not describe how the operator application is to be computed. Digital signal processing examples of operators defined in Spiral are the discrete Fourier transform (DFT)

$$DFT_n: \mathbb{C}^n \to \mathbb{C}^n; x \mapsto \left[\omega_n^{ij}\right]_{i,i} x$$

(2)

with  $\omega_n = \sqrt[n]{-1}$  a primitive *n*th root of 1. Spiral defines more than 50 linear digital signal processing transforms [1] and a number of bilinear and nonlinear transforms [54].

Beyond linear transforms, SPIRAL defines numerical linear algebra operations such as the circular convolution [54]

$$\operatorname{Conv}_{n}: \mathbb{C}^{n} \times \mathbb{C}^{n} \to \mathbb{C}^{n}; (x, y) \mapsto x \circledast y = \sum_{i=0}^{n-1} x_{i} y_{(n-i) \bmod n}$$

(3)

and matrix-matrix multiply [54]

$$\mathrm{MMM}_{k,m,n}: \mathbb{R}^{m \times k} \times \mathbb{R}^{k \times n} \to \mathbb{R}^{m \times n}; (A,B) \mapsto AB$$

(4)

which are bilinear as the scalar product. In Spiral, we implicitly use the isomorphism  $\mathbb{R}^{m\times n}\cong\mathbb{R}^{mn}$  to abstract away tensor rank and convert all higher rank objects to vectors.

Examples of nonlinear operators defined in Spiral include polynomial evaluation and infinity norm

$$P_n: \mathbb{R}^{n+1} \times \mathbb{R} \to \mathbb{R}; (a, x) \mapsto \sum_{i=0}^{n} a_i x^i,$$

(5)

$$\|.\|_{\infty}^{n}: \mathbb{R}^{n} \to \mathbb{R}; x \mapsto \|x\|_{\infty} \tag{6}$$

and checking if a point  $x \in \mathbb{R}^n$  is inside a polytope given by a matrix A of polytope face normal vectors and a vector b of polytope face displacements

Inside<sub>A,b</sub><sup>n</sup>:

$$\mathbb{R}^n \to \mathbb{Z}_2$$

;  $x \mapsto Ax - b < (0, ..., 0)$ . (7)

Equation (7) can be used to implement geofencing for unmanned aerial vehicles (UAVs) [74]. A more complicated nonlinear example is the statistical *z*-test, given by

$$\operatorname{zTest}_{\mu,\alpha}^n : \mathbb{R}^n \to \mathbb{R}; x \mapsto \frac{\bar{x} - \mu}{\sigma(x)/\sqrt{n}} < \Phi^{-1}(1 - \alpha/2)$$

(8)

where  $\mu$  is the population mean,  $\bar{x}$  is the sample mean,  $\sigma(x)$  is the sample standard deviation, and  $\Phi^{-1}$  is the inverse error function.

Beyond the kernels shown in (1)–(8) we have modeled many more kernels as OL operators: the Viterbi decoder [58], polar formatting synthetic aperture radar (SAR) [56], Euler integration, statistical tests [65], wavelet transforms and JPEG2000 image compression [53], [57], the multigrid V cycle [64], quantum chemistry kernels used in ONETEP [61], the operations needed in the physical layer of SDR [60], a range of dense linear algebra kernels [63], and others.

Unambiguously declaring the input-output behavior of a kernel as function of all parameters is the first step required for program generation with Spiral, and developing the exact specification of a kernel is often a hard research problem in particular for higher-level operations such as SAR imaging, Viterbi decoders, and the multigrid V cycle, which require many algorithm and implementation choices. Top level operators often require a number of helper operators to be defined to express algorithms cleanly through breakdown rules, as discussed next.

2) Algorithms: In SPIRAL, algorithms describe how an operation given by a specification is turned into a computation directly or through other operators. For instance, an FFT is an algorithm to compute the DFT (which is a specification), usually through smaller DFTs. Similarly, computing a circular convolution via DFT and pointwise multiplication in the frequency domain or evaluating a polynomial via the Horner scheme are considered algorithms.

More formally, algorithms break down operators into (usually smaller) other operators in the divide-and-conquer style or iterative algorithms. Such algorithmic decompositions are modeled as breakdown rules in Spiral-RAL's rewriting system and may expose algorithmic degrees of freedom. Recursive application of breakdown rules yields a fully specified algorithm that is expressed as a rule tree. The rules explain how a rule tree is translated into a flat data flow graph. The DSL OL is used to capture these data flow graphs. OL programs may contain iterators (similar to map and reduce/fold in functional languages).

3) Operator Language: SPIRAL uses the OL to represent algorithmic breakdown rules and data flow graphs. We often refer to OL programs as OL formulas. OL consists of atomic operators such as (1)–(8) and others including auxiliary ones. Higher-order functions (operations) construct operator expressions, i.e., new operators from others.

Linear operators play an important role in Spiral. Originally, Spiral's language was called signal processing language (SPL) [13] and focused on linear operators, composition, and the Kronecker product to describe linear signal transforms and their algorithms (like the FFT) [1]. OL generalizes SPL to allow for multiple inputs and operator nonlinearity. In OL, matrices are interpreted as linear operators, and matrix multiplication is interpreted as

composition of linear operators. Thus, OL is a generalization of SPL and any SPL expression can be cast in OL.

Important linear operators in SPIRAL include the identity matrix  $I_m$  and the stride permutation matrix  $L_n^{mn}$ , which permutes the elements of the input vector as  $in+j\mapsto jm+i,\ 0\le i< m,\ 0\le j< n.$  If the vector x is viewed as an  $n\times m$  matrix, stored in row-major order, then  $L_m^{mn}$  performs a transposition of this matrix. Also important are diagonal matrices, e.g., to describe the twiddle matrix  $T_n^{mn}$  needed in the most commonly used FFTs.

Higher-order functions create new OL operators from existing OL operators. Important higher-order functions included within Spiral include function composition  $\circ$ , the Cartesian product  $\times$ , the direct sum  $\oplus$ , and the Kronecker product or tensor product  $\otimes$

$$(A \circ B)(x) = A(B(x)), \tag{9}$$

$$(A \times B)(x,y) = A(x) \times B(y), \tag{10}$$

$$(A \oplus B)(x \oplus y) = A(x) \oplus B(y), \text{ and}$$

(11)

$$(A \otimes B)(x \otimes y) = A(x) \otimes B(y). \tag{12}$$

The Kronecker product of matrices A and B is defined as

$$A \otimes B = [a_{k,\ell}B], \quad \text{for } A = [a_{k,\ell}]. \tag{13}$$

It replaces every entry  $a_{k,\ell}$  of A by the matrix  $a_{k,\ell}B$ . The Kronecker product binds weaker than matrix product but stronger than matrix addition. For scalar operations such as +,-,-,-,-,-,-,-,-,-,-, etc., we define the infix operations

$$(A \diamond B)(x) = A(x) \diamond B(x)$$

for  $\diamond \in \{+ - \cdot /, <, \ldots\}$ . (14)

In (9)–(14), we assume that the operators A and B are of arity (1,1), i.e., that they have one input and one output vector. Generalization to higher arities (multiple input or output vectors) is technically complex but conceptually straightforward [54]. Spiral applies the isomorphism between  $\mathbb{R}^{m+n}$  and the direct sum and Cartesian product of  $\mathbb{R}^m$  and  $\mathbb{R}^n$

$$\mathbb{R}^m \times \mathbb{R}^n \cong \mathbb{R}^m \oplus \mathbb{R}^n \cong \mathbb{R}^{m+n}$$

as needed in type unification to simplify handling of higher arities.

More recently, an additional class of OL operators that model functional programming constructs such as map and fold [65], [74] was introduced (into SPIRAL) in OL

$$\operatorname{Map}_{f_i(.)}^n : \mathbb{R}^n \to \mathbb{R}^n; \bigoplus_{i=0}^{n-1} x_i \mapsto \bigoplus_{i=0}^{n-1} f_i(x_i),$$

(15)

$$\operatorname{Fold}_{f_i(\ldots),z}^n:\mathbb{R}^n\to\mathbb{R};x_0\oplus x_r$$

$$\mapsto \begin{cases} f_0(x_0, z), & n = 1\\ f_0(x_0, & \text{Fold}_{f_{i+1}(x_0), z}^{n-1}(x_r)). \end{cases}$$

(16)

This additional class of operators is introduced so that Spiral-generated code can be formally verified using standard techniques common to proving the correctness of functional languages.

4) Breakdown Rules: Algorithms and their degrees of freedom are expressed in SPIRAL as breakdown rules. A breakdown rule is a rewriting rule that matches an OL operator (e.g., specifying a problem) and replaces the matched expression with a more complicated expression made up of simpler/smaller OL operators. The pattern matching performed by the rule encodes possible constraints on the kernel (e.g., a subset of input sizes to which it is applicable). For instance, the general radix Cooley–Tukey FFT algorithm is expressed as breakdown rule [1], [7]

$$DFT_{mn} \to (DFT_m \otimes I_n)T_n^{mn}(I_m \otimes DFT_n)L_m^{mn}.$$

(17)

In (17),  $\mathrm{DFT}_{mn}$  is the nonterminal and is translated into a right-hand side that consists of an  $\mathrm{SPL/OL}$  expression that contains new nonterminals  $\mathrm{DFT}_m$  and  $\mathrm{DFT}_n$ . The left-hand side  $\mathrm{DFT}_{mn}$  encodes the constraint that the size of the DFT be a composite number and therefore can be factored into m and n. Further, the new DFT nonterminals created by (17) are of smaller size than the original nonterminal. Thus recursive application of (17) will terminate and we need to provide a terminal rule that translates  $\mathrm{DFT}_2$  into an atomic  $\mathrm{SPL/OL}$  operator (the butterfly)

$$DFT_2 \rightarrow F_2$$

with  $F_2 = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$ . (18)

*k*-dimensional multi-dimensional DFTs (MDFTs) are broken down into lower dimensional DFTs through tensor products. For instance, a complete decomposition into one-dimensional DFTs is

$$DFT_{m_1 \times \cdots \times m_k} \to DFT_{m_1} \otimes \ldots \otimes DFT_{m_k}.$$

(19)

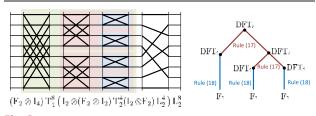

As an example, a DFT $_8$  operator can be fully expanded into an SPL/OL formula by applying (17) twice and (18) thrice to get

$$\label{eq:definition} DFT_8 \rightarrow (F_2 \otimes I_4) T_4^8 \big(I_2 \otimes (F_2 \otimes I_2) T_2^4 (I_2 \otimes F_2) L_2^4 \big) L_2^8.$$

(20)

Fig. 2. Data flow graph, OL formula, and rule tree for DFT $_8$  as expanded in (116) (see Fig. 7).

**Table 1** Spiral OL Breakdown Rules for a Multigrid Solver MGSolvePDE $n,\omega,r,m$  for an  $n \times n$  Discretized 2-D Poisson Equation With Dirichlet Boundary Conditions and Parameters  $\omega$ , r, and m. The Solver Uses a Richardson Smoother With Parameter  $\omega$  and r Iterations and Injection as Restriction Operator. It Performs m Multigrid Cycles [64].

$$\begin{split} & \operatorname{MGSolvePDE}_{n,\omega,r,m} \to [\operatorname{I}_{n^2} \mid 0_{n^2}] \cdot \left( \prod_{i=0}^{m-1} \operatorname{MGCycle}_{n,\omega,r} \right) \cdot \begin{bmatrix} 0_{n^2} \\ \operatorname{I}_{n^2} \end{bmatrix} & (21) \\ & \operatorname{MGCycle}_{n,\omega,r} \to \operatorname{CGC}_{n,\omega,r} \cdot \operatorname{Richardson}_{n,\omega,r} & (22) \\ & \operatorname{CGC}_{n,\omega,r} \to \begin{bmatrix} \operatorname{CoarseError}_{n,\omega,r} \\ 0_{n^2} \mid \operatorname{I}_{n^2} \end{bmatrix} & (23) \\ & \operatorname{CoarseError}_{n,\omega,r} \to \operatorname{Interpolate}_n \cdot \operatorname{Scatter}_n \cdot \operatorname{Solve}_{n,\omega,r} \cdot \operatorname{Gather}_n \cdot \operatorname{Residual}_n & (24) \\ & \operatorname{Interpolate}_n \to \operatorname{Tridiag}_n \left( \sqrt{2}/2, \sqrt{2}, \sqrt{2}/2 \right) \otimes \operatorname{Tridiag}_n \left( \sqrt{2}/2, \sqrt{2}, \sqrt{2}/2 \right) & (25) \\ & \operatorname{Scatter}_n \to \operatorname{S}_{\mathbb{I}_{(n-1)/2} \to \mathbb{I}_n; \ i \mapsto 2i+1} \otimes \operatorname{S}_{\mathbb{I}_{(n-1)/2} \to \mathbb{I}_n; \ i \mapsto 2i+1} & (26) \\ & \operatorname{Solve}_{n,\omega,r} \to \begin{cases} \frac{1}{4} \operatorname{II}, & n=1 \\ \left[ \operatorname{I}_{((n-1)/2)^2} \mid 0_{((n-1)/2)^2} \right] \cdot \operatorname{MGCycle}_{(n-1)/2,\omega,r} \cdot \begin{bmatrix} 0_{((n-1)/2)^2} \\ \operatorname{I}_{((n-1)/2)^2} \end{bmatrix}, & n>1 \\ & \operatorname{Gather}_n \to \operatorname{G}_{\mathbb{I}_{(n-1)/2} \to \mathbb{I}_n; \ i \mapsto 2i+1} \otimes \operatorname{G}_{\mathbb{I}_{(n-1)/2} \to \mathbb{I}_n; \ i \mapsto 2i+1} & (28) \\ \operatorname{Residual}_n \to \left[ (\operatorname{Tridiag}_n(1,-2,1) \otimes \operatorname{In}_n) + (\operatorname{In} \otimes \operatorname{Tridiag}_n(1,-2,1)) \mid \operatorname{In}_n^2 \right] & (29) \\ \operatorname{Richardson}_{n,\omega,r} \to \prod_{i=0}^{r-1} \begin{bmatrix} \operatorname{ResidueLaplace}_{n,\omega} & \omega \operatorname{In}_n^2 \\ 0_{n^2} & \operatorname{In}_n^2 \end{bmatrix} & (30) \\ \operatorname{ResidueLaplace}_{n,\omega} \to (\operatorname{Tridiag}_n(\omega,1/2-2\omega,\omega) \otimes \operatorname{In}_n) + (\operatorname{In} \otimes \operatorname{Tridiag}_n(\omega,1/2-2\omega,\omega)) & (31) \end{cases} \end{split}$$

Table 2 OL Breakdown Rules for Polar Formatting Synthetic Aperture Radar (SAR) [27], [51], [56], Formalizing Algorithms From [173] and [174].

$$\begin{array}{c}

\operatorname{PDFT}_{N}^{\sigma} \to \operatorname{DFT}_{N} S_{\sigma} & (32) \\

\operatorname{PDFT}_{kmn}^{\sigma \otimes km} \to (\operatorname{DFT}_{m} \otimes \operatorname{I}_{kn}) \operatorname{T}_{n}^{mn} \operatorname{L}_{m}^{kmn} (\operatorname{PDFT}_{kn}^{\sigma \otimes k} \otimes \operatorname{I}_{m}) & (33) \\

\operatorname{SAR}_{s,\alpha} \to \operatorname{DFT}_{m_{2} \times n_{2}} \operatorname{2D-Intp}_{(k,r,m,n,\alpha_{r},\alpha_{a})}^{m_{1} \times n_{1} \to m_{2} \times n_{2}} & (34) \\

\operatorname{2D-Intp}_{(k,r,m,n,\alpha_{r},\alpha_{a})}^{m_{1} \times n_{1} \to m_{2} \times n_{2}} \to \left(\operatorname{Intp}_{(k,r,m,n,\alpha_{a}(i))}^{n_{1} \to n_{2}} \otimes_{i} \operatorname{I}_{m_{2}}\right) \left(\operatorname{I}_{n_{1}} \otimes_{i} \operatorname{Intp}_{(k,r,m,n,\alpha_{r}(i))}^{m_{1} \to m_{2}} & (35) \\

\operatorname{Intp}_{(k,r,m,n,w)}^{u \to v} \to \left(\operatorname{I}_{\ell} \otimes_{j} \operatorname{Intp}_{(k,w(j))}^{m \to n}\right) \left(\operatorname{I}_{\ell} \otimes^{r} \operatorname{I}_{m}\right) & (36) \\

\operatorname{Intp}_{(k,(b,s))}^{m \to n} \to \operatorname{G}_{(b,s)}^{km \to n} \operatorname{iDFT}_{km} \operatorname{S}_{(0,k-1) \otimes (m/2)} \operatorname{DFT}_{m} & (37) \\

\operatorname{iDFT}_{km} \operatorname{S}_{(0,k-1) \otimes (m/2)} \to \operatorname{iPDFT}_{km}^{(0,k-1) \otimes (m/2)} & (38)

\end{array}$$

The first application of (17) allows for a choice of (m,n)=(4,2) or (m,n)=(2,4), and for larger sizes requiring multiple rule applications there is a considerable degree of freedom to expand  $\mathrm{DFT}_N$  into a fully expanded SPL/OL formula. The dataflow that is represented by the formula is shown in Fig. 2(left). Such algorithmic degrees of freedom are one source of the optimization space that is leveraged by Spiral. Spiral defines more than 50 linear transform nonterminals such as the DFT and more than 200 breakdown rules such as (17) [1].

Tables 1 and 2 show breakdown rule sets for more complex algorithms. Table 1 shows the set of OL breakdown rules for a multigrid solver  $\mathrm{MGSolvePDE}_{n,\omega,r,m}$  for an  $n \times n$  discretized 2-D Poisson equation with Dirichlet boundary conditions and parameters  $\omega$ , r, and m. The solver uses a Richardson smoother with parameter  $\omega$  and r iterations and injection as restriction operator. It performs m multigrid cycles [64]. Note the interconnected set of auxiliary operators needed.

Table 2 shows the OL breakdown rule set for polar-formatting synthetic aperture radar (SAR [51], [56]), formalizing the algorithms from [173] and [174].

5) Nonlinear OL Breakdowns: The step from linear operators to non-linear operators requires the use of OL constructs in breakdown rules. For instance, matrix–matrix multiplication (MMM) as defined in (4) is a bilinear operator. Optimized MMM implementations utilize multilevel cache and register blocking [91], and blocking of MMM can be described as

$$MMM_{k,m,n} \to MMM_{k/b_1,m/b_2,n/b_3} \otimes MMM_{b_1,b_2,b_3}$$

. (39)

In (39), the multilinear tensor product captures the recursiveness of MMM in the same fashion that (17) captures the recursiveness of the DFT and (19) captures the higher dimensional structure of the MDFT.

Functional programming-style operators are equally decomposed by rewrite rules that express them as para-

Fig. 3. Data flow graph, OL formula, and rule tree for  $d_{\infty}(.,.)$  as expanded in (43).

meterized OL expressions. For instance, the Chebyshev distance (distance induced by the infinity norm)

$$d_{\infty}(u,v) = \|u - v\|_{\infty}, \quad u, v \in \mathbb{R}^n$$

(40)

is captured by the rules

$$d_{\infty}^{n}(.,.) \to \|.\|_{\infty}^{n} \circ \operatorname{Map}_{(x,y)\mapsto x-y}^{n\times n\to n}$$

$$\tag{41}$$

$$\|.\|_{\infty}^n \to \operatorname{Fold}_{(x,y)\mapsto \max(x,y),0}^n \circ \operatorname{Map}_{x\mapsto |x|}^n.$$

(42)

Note that we annotated the OL definition of  $d_{\infty}(u,v)$  with dimensionality n, leading to the OL nonterminal  $d_{\infty}^n(u,v)$  for the Chebyshev distance. The nonterminal  $d_{\infty}^8(.,.)$  can be fully expanded into an SPL/OL expression (a functional style formula) by applying (41) followed by (42), leading to

$$d_{\infty}^{8}(.,.) \to \operatorname{Fold}_{(x,y)\mapsto \max(x,y),0}^{8} \circ \operatorname{Map}_{x\mapsto |x|}^{8} \circ \operatorname{Map}_{(x,y)\mapsto x-y}^{8\times 8\to 8}$$

(43)

Fig. 3 shows the corresponding data flow graph and rule tree.

Similarly, polynomial evaluation (5) is expressed as the breakdown rule

$$P_n(.,.) \rightarrow <.,.>_n \circ \left(I_{n+1} \times \left(\operatorname{Map}_{x \mapsto x^i}^{n+1} \circ \begin{bmatrix} 1 & \cdots & 1 \end{bmatrix}^T\right)\right).$$

(44)

$P_n(.,.)$  is an arity (2,1) operator. The cross product  $\times$  passes the first argument to the identity matrix and the second argument to the Map construct. The linear operator  $\left[1\cdots 1\right]^T$  takes the second input of  $P_n(a,x)$  (the scalar x) and replicates it for n+1 times to form a vector. Then  $\operatorname{Map}_{x\mapsto x^i}^{n+1}$  computes all exponents of x from 0 to n, yielding the vector  $(1,x,x^2,\ldots,x^n)$ . Note that the map function  $f_i(x)=x^i,i=0,\ldots,n$  depends on the index of the mapped element. Furthermore,  $I_{n+1}$  forwards the coefficient vector  $a=(a_n,\ldots,a_0)$  [the first input of  $P_n(.,.)$ ] to the scalar product  $<\cdot,\cdot>_n$ , which performs the pointwise multiplications  $a_ix^i$  for  $i=0,\ldots,n$  and then performs the final sum, yielding the result  $P_n(a,x)=\sum_{i=0}^n a_ix^i$ .

The scalar product is a special case of MMM

$$\langle .,. \rangle_n \to \text{MMM}_{n,1,1}$$

(45)

and thus can be decomposed via (39). The check for being inside a polytope (7) [74] is expressed as an OL breakdown rule by

$$\operatorname{Inside}_{A,b}^{n}(.) \to \operatorname{Fold}_{(x,y)\mapsto (x<0)\wedge y, \operatorname{true}}^{n} \circ \operatorname{Map}_{x\mapsto x-b}^{n} \circ \operatorname{MMM}_{n,1,n}(A,.).$$

(46)

Inside (46) the matrix–vector product Ax required by (7) is expressed as degenerate partially evaluated MMM  $\mathrm{MMM}_{n,1,n}(A,.)$ . The operator  $\mathrm{Map}_{x\mapsto x-b}^n$  subtracts the right-hand side b from the result, and  $\mathrm{Fold}_{(x,y)\mapsto (x<0)\wedge y,\mathrm{true}}^n$  checks that all entries of the resulting vector are negative. Finally, the OL rule set for the z-test (8) for a sample size of n at  $\alpha$  confidence interval is shown in Table 3.

Note that all breakdown rules are point-free: operators are expressed through other operators but the input and output is not part of the expression. This property is important for data flow optimization (discussed next) and program generation.

### B. Program Transformations as Data Flows

In the previous section, we discussed how specifications are expanded into fully expanded (terminated) OL expressions that represent data flow graphs of the algorithm. In this section, we discuss how Spiral performs data flow optimizations that change the geometry and thus locality and shape of parallelism in the data flow graph.

1) Approach: A human developer typically starts from a given algorithm/data flow graph, and then modifies it to better match the underlying hardware. Spiral takes a different approach: The data flow graph is made to fit the targeted hardware while it is derived recursively. This is achieved by a two-pronged approach: 1) program/data flow transformations are also cast as breakdown rules and are treated equivalently to algorithmic breakdown rules; and 2) hardware properties are encoded as constraints on these breakdown rules.

In this section, we discuss how program transformations are encoded as breakdown rules. Section III-C discusses how hardware is modeled through breakdown rules and

**Table 3** The Statistical *z*-Test Represented as a Set of OL Breakdown Rules [74].

$$\operatorname{Mean}_{n} \to \operatorname{Map}_{x \mapsto x/n}^{1} \circ \operatorname{Fold}_{(a,b) \mapsto (a+b),0}^{n}$$

$$\operatorname{Variance}_{n} \to \left( \operatorname{Fold}_{(a,b) \mapsto (a+b),0}^{n} \circ \operatorname{Map}_{x \mapsto x^{2}}^{n} \right)$$

$$- \left( \operatorname{Map}_{x \mapsto x^{2}}^{1} \circ \operatorname{Mean}_{n} \right)$$

$$\operatorname{zTest}_{n,\alpha} \to \left( \operatorname{Mean}_{n} / \operatorname{Map}_{x \mapsto \sqrt{x}}^{1} \circ \operatorname{Variance}_{n} / n \right) < \Phi^{-1}(1 - \alpha/2),$$

$$(49)$$

constraints on them, and Section IV discusses how the resulting constraint problem is solved.

2) Memory Abstraction: Many performance-relevant hardware constraints translate into the requirement that certain contiguous data blocks are held in a certain class of memory, and these data are moved in contiguous blocks of certain sizes. Recall that operators map vectors to vectors. Vectors impose a natural neighborhood relation: for a vector x the component  $x_i$  is neighbor of components  $x_{i-1}$  and  $x_{i+1}$ . A subvector  $(x_i, \ldots, x_{i+k-1})^T$  of length k is contiguous and thus naturally provides the concept of a block.

Therefore, we impose the interpretation of vectors that OL formulas operate on as being mapped to physical storage contiguously, i.e., the memory for a vector is viewed as array (in C notation)  $vector_t X[n]$ , and  $x_i$  is mapped to X[i]. Any different data layout needs to be made explicit through permutation operators as part of the OL formula, not by informally interpreting the vector data layout differently. For example, block cyclic data distribution becomes an explicit permutation in an OL formula.

Partitioning a vector into equally-sized blocks treats the vector as vector of vectors. Blocking may happen recursively (blocks of blocks). For constant block size at each recursion level, this interpretation implies that data vectors are seen as linearized tensors (high-dimensional matrices), which explains the importance of the tensor product and Kronecker product in Spiral's formal framework. This implies that blocking higher-dimensional objects (e.g., matrices) introduces explicit permutations, since subblocks of higher-dimensional blocks contiguous in memory are themselves not contiguous any more. We use this approach to model structural hardware features that require data locality for performance or correctness reasons, as discussed in Section III-C.

3) The Role of Permutations: Spiral's memory abstraction implies that data required to compute an operator  $A_n(.)$  are in the local memory (if there are multiple address spaces) or in the smallest level of the memory hierarchy (e.g., in the L1 cache for standard CPUs). If n is too large (i.e., the memory is too small to hold the necessary data), then the operator needs to be recursively decomposed until this condition holds. In this respect, Spiral's memory model is related to the idea of cache oblivious algorithms [175]. Spiral implies that a data access that crosses memory regions that are contiguous needs to be explicitly marked in the OL data flow abstraction.

Permutations are used to capture both data reordering and communication. They are expressed as permutation matrices that are parameterized by the actual permutation (function). The most prominent example in Spiral is the stride permutation  $\mathcal{L}_n^{mn}$  introduced in Section III-A.

4) Data Flow Representation: With the above convention of how vectors are mapped to memory we can now

describe locality enhancing optimizations as breakdown rules for OL expressions.

First we discuss the meaning of tensor/Kronecker products with identity matrices in the context of data flow graphs. For a linear operator  $A_m \in \mathbb{R}^{m \times m}$  and  $B_n \in \mathbb{R}^{n \times n}$  the Kronecker product  $A_m \otimes B_n$  defined in (13) is a matrix of size  $mn \times mn$ . For  $A_m = I_m$  the tensor product becomes a block-diagonal matrix

$$I_m \otimes B_n = \begin{bmatrix} B_n & & & \\ & \ddots & & \\ & & B_n \end{bmatrix}. \tag{50}$$

The operator  $I_m \otimes B_n$  applies the same operator  $B_n$  on contiguous subvectors of length n, i.e.,

$$(\mathbf{I}_m \otimes B_n)(x_0 \oplus \ldots \oplus x_{m-1}) = (B_n x_0) \oplus \ldots \oplus (B_n x_{m-1})$$

and can be seen as a "parallel operation." The "flipped" tensor product is a block matrix where each block is a constant-diagonal matrix

$$A_m \otimes I_n = \begin{bmatrix} a_{0,0}I_n & \dots & a_{0,m-1}I_n \\ \vdots & \ddots & \vdots \\ a_{m-1,0}I_n & \dots & a_{m-1,m-1}I_n \end{bmatrix}.$$

(51)

Equation (51) applies the operator  $A_m$  to subvectors of length n and can be seen as a "vector operation." A common interpretation is that for a linearized  $m \times n$  input matrix  $x \in \mathbb{R}^{mn}$  the operation  $(I_m \otimes B_n)x$  applies the operator  $B_n$  to the "rows" of x while  $(A_m \otimes I_n)x$  applies the operator  $A_m$  to the "columns" of x. The tensor product is separable: it can be factorized into a "row pass" and "column pass" in two ways, written as breakdown rule

$$A_m \otimes B_n \to \begin{cases} (A_m \otimes I_n)(I_m \otimes B_n) \\ (I_m \otimes B_n)(A_m \otimes I_n) \end{cases} . \tag{52}$$

For instance, (19) together with (52) captures a large class of multidimensional FFT algorithms including the row-column algorithm, as well as the slab and pencil decomposition. Further, the identity matrix is the tensor product of identity matrices

$$I_{mn} \to I_m \otimes I_n$$

(53)

which can be used to represent loop tiling. The following breakdown rule describes the use of (53) to tile the mn iterations of applying the operator A into m iterations of n computations of A:

$$I_{mn} \otimes A \to I_m \otimes (I_n \otimes A).$$

A generalization that allows the blocks  $B_n$  to be different in the occurring entries (but not in size) is expressed

$$I_m \otimes_i B_n^{(i)} = \bigoplus_{i=0}^{m-1} B_n^{(i)}.$$

(54)

The definitions in this section generalize to rectangular matrices  $A_{k \times \ell} \in \mathbb{R}^{k \times \ell}$  and  $B_{m \times n} \in \mathbb{R}^{m \times n}$ .

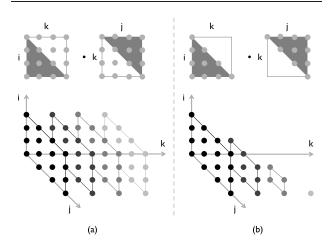

5) Data Layout Transformations: The most important permutation operator in SPIRAL's framework is the stride permutation  ${\cal L}_m^{mn}.$  As discussed in Section III-A, it can be viewed as transposing a linearized matrix: it blocks a vector of length mn into m vectors of length n, treats the vector-of-vectors as a matrix of size  $m \times n$ , transposes the matrix (new size is  $n \times m$ ), reinterprets the matrix as nvectors of length m, and finally linearizes the vector-ofvectors into a single vector of length mn. Note that the reshaping steps are virtual: under Spiral's matrix/tensor linearization rules the data flow graph of a matrix transposition and of a stride permutation are the same.

The stride operation derives its importance from the fact that it commutes the tensor product and thus enables formal derivation of loop transformations such as tiling, blocking, loop interchange, and loop merging/fusion/fission. Written as breakdown rule

$$A_m \otimes B_n \to L_m^{mn}(B_n \otimes A_m)L_n^{mn}.$$

(55)

Furthermore, matrix transposition can be blocked into a transposition of blocks followed by or preceded by a transposition of the blocks [9]

$$\mathbf{L}_{km}^{k^2mn} = \left(\mathbf{I}_k \otimes \mathbf{L}_m^{kmn}\right) \left(\mathbf{L}_k^{k^2} \otimes \mathbf{I}_{mn}\right) \left(\mathbf{I}_k \otimes \mathbf{L}_k^{kn} \otimes \mathbf{I}_m\right). \tag{56}$$

Stride permutations have multiplicative and transposition/inversion properties, which yield the identities

$$\left(\mathbf{L}_{m}^{mn}\right)^{T} \to \mathbf{L}_{n}^{mn} \tag{57}$$

$$\left(\mathbf{L}_{m}^{mn}\right)^{-1} \to \mathbf{L}_{n}^{mn} \tag{58}$$

$$L_{km}^{kmn} \to L_{k}^{kmn} L_{m}^{kmn}$$

$$L_{n}^{kmn} \to L_{kn}^{kmn} L_{mn}^{kmn}$$

$$(60)$$

$$L_n^{kmn} \to L_{kn}^{kmn} L_{mn}^{kmn} \tag{60}$$

$$L_n^{kmn} \to (L_n^{kn} \otimes I_m) (I_k \otimes L_n^{mn})$$

(61)

$$L_{km}^{kmn} \to (I_k \otimes L_m^{mn}) (L_k^{kn} \otimes I_m). \tag{62}$$

Tensor products of stride permutations with identity matrices can be seen as block transpositions, transposition of blocks, or tensor rotations. For instance,  $I_k \otimes L_m^{mn}$  is a block diagonal matrix of size  $kmn \times kmn$  with blocks of size  $mn \times mn$ . Similarly, the operation  $L_m^{mn} \otimes I_k$  is expressing the reordering of packets of size k. Both tensor products can be seen as rotations of a linearized rank-3 tensor in the xy or yz plane. As an aside, the tensor product of two stride permutations is rotating a linearized rank-4 tensor

simultaneously in the xy and zu plane that also can be seen as an operation for a block matrix that simultaneously performs a transposition of blocks and transposition within blocks.

6) Nonlinear and Higher-Arity Data Flows: So far, we have only discussed the tensor product of linear operators. The generalization to multilinear is standard in the field of multilinear algebra and tensor calculus, and we use the standard definitions. For instance, (39) describes recursive blocking of MMM as tensor decomposition of the operator  $MMM_{k,m,n}$ . Generalizations of rules (52)–(62) exist for the multilinear tensor product and generalize to the iterative sum (54).

Spiral also defines a generalization of (50) and (51) for a tensor product of an identity matrix and a nonlinear operator [54]. For the simple case of  $B_n: \mathbb{R}^n \to \mathbb{R}^n$ the generalization is straightforward: the operator ( $I_m \otimes$  $B_n(.)(.)$  applies the operator  $B_n(.)$  on contiguous subvectors of length n, i.e.,

$$(\mathbf{I}_m \otimes B_n(.))(x_0 \oplus \ldots \oplus x_{m-1}) = B_n(x_0) \oplus \ldots \oplus B_n(x_{m-1}).$$

(63)

Using (63) we can break down (15) and (16) to capture program transformations for the Map and Fold operators

$$\operatorname{Map}_{f_i(.)}^{mn} \to \operatorname{I}_m \otimes_j \operatorname{Map}_{f_{in+i}(.)}^n, \quad \text{and}$$

(64)

$$\operatorname{Fold}_{f_i(.,.),z}^{mn} \to \operatorname{Fold}_{f_{in}(.,.),z}^{m} \circ \left( \operatorname{I}_m \otimes_j \operatorname{Fold}_{f_{in+i}(.,.),z}^{n} \right). \tag{65}$$

For more general situations and arities beyond (1,1) these definitions and breakdown rules become unwieldy and for brevity we will not introduce them in this paper.

The relatively small set of identities and breakdown rules introduced in this section gives rise to a large possible space of data layout and blocking transformations that can be exploited in locality optimizations and work handin-hand with algorithmic breakdown rules. Together with hardware parameters (discussed next) they are powerful enough to enable SPIRAL to derive efficient data flow graphs for a wide range of problems and platforms.

# C. Hardware Abstraction

We now discuss how hardware is abstracted in Spiral's formal framework.

1) Approach: The framework is designed to capture the major current architectural and microarchitectural features that require data flow optimizations for performance, including 1) SIMD vector instruction sets, SIMT, and VLIW architectures [22], [25]; 2) cache memories (multiple cache levels and various topologies) [20]; 3) scratch pads (explicitly managed local storage) and multiple address spaces (CPU/device memory) [38]; 4) shared memory parallelism (multicore, manycore, and hyperthreading) [19], [20]; 5) distributed memory parallelism (message passing) [47], [49]; and 6) streaming parallelism (processor arrays and FPGAs) [40], [45], [46]. We expect that also most future hardware paradigms are composed from these features. SPIRAL's hardware model provides a formal way to enumerate "good programs" for a target platform. This is achieved by modeling the hardware in SPIRAL's rewrite system through constrained terminal rules (the rule tree expansion stops), or as constraints on OL breakdown rules. SPIRAL does not use a detailed predictive model (as, e.g., [176] for MMM) but captures structurally which kind of computations work or do not work well. Further autotuning search (or learning) is then used to select which program runs fastest.

Hardware or architecture features that do not require direct changes to the data flow but may influence its parameters are not modeled at the formal level but handled in the backend compiler (see Section IV-B). These features include ISA details such as fused multiply-add instructions, special data type support (floating-point, double-double, fixed-point, finite field arithmetic), and microarchitectural features such as the number of physical and named registers, topology of execution pipelines, and others.

2) Tags: A hardware constraint on an OL operator is captured by a tag. Tags are symbolic annotations that are used in rewrite rules to control pattern matching. Tags carry parameters that provide high-level structural information of the hardware feature they describe. Operators or operator expressions can be tagged. For instance

$$\underbrace{\mathrm{I}_n \otimes A_n}_{\mathrm{vec}(\nu)}, \quad \underbrace{\mathrm{DFT}_n}_{\mathrm{smp}(2)\,\mathrm{vec}(4)}, \quad \text{and} \quad \underbrace{\mathrm{MMM}_{k,m,n}}_{\mathrm{mpi}(16)\,\mathrm{vec}(\mathrm{avx-double})}$$

specify a general operator expression  $I_n \otimes A_n$  to be  $\nu$ -way SIMD vectorized, a DFT $_n$  to be 2-way parallelized for shared memory and 4-way SIMD vectorized, and an  $MMM_{k,m,n}$  to be parallelized for 16 MPI processes and vectorized for the double-precision AVX instruction set, respectively. These examples show that an operator can be tagged with multiple tags (order matters: e.g., smp(2) smp(4) captures a different nested parallelization from smp(4) smp(2)), and that tags can be generic (4-way SIMD vectorization) or specific (SIMD vectorization for AVX double-precision). Specific tags imply generic tags (AVX double precision implies 4-way SIMD vectorization, and 16 MPI processes imply 16-way distributed memory parallelism). Other hardware features are also captured by tags: for instance, a tag for  $\nu$ -way streaming on FPGAs used below is given by  $fpga(\nu)$ .

3) Tagged Breakdown Rules: Tagged breakdown rules propagate tags and constrain algorithmic or data flow optimization breakdown rules so that they become compatible with the target hardware. For instance, the propagation

rule

$$\underbrace{A \circ B}_{\text{tag}} \to \underbrace{A}_{\text{tag}} \circ \underbrace{B}_{\text{tag}} \quad \text{for tag} \in \{\text{par}(.), \text{vec}(.), \ldots\} \quad (66)$$

states that tagging and function composition commutes for certain tags (to parallelize a sequence of operators, parallelize each operator independently and have barriers at the end of each parallel operator).

An example of a parallelization rule that expresses that the outermost loop should be parallelized is given by

$$\underbrace{\mathbf{I}_{p} \otimes A_{n}}_{\text{tag}} \to \mathbf{I}_{p} \otimes_{\text{tag}} A_{n} \quad \text{for tag} \in \{\text{smp}(p), \, \text{mpi}(p), \, \text{fpga}(n)\}.$$

(67)

The rule states that a loop of p iterations with loop body  $A_n(.)$  can be perfectly parallelized across p processors by running one instance of  $A_n(.)$  on each processor. Similarly, on an FPGA a block implementing  $A_n(.)$  as a combinational data path can be invoked every cycle with a new input vector. Thus,  $I_p \otimes A_n$  is executed over p cycles as a pipelined IP block of streaming width n.

The symbol  $\otimes_{tag}$  is a tagged OL operation that carries the information that the loop resulting from this tensor product is parallel to the further stages in the rewriting system. Rule (67) "drops" the tag, i.e., there is no tagged OL object left on in the right-hand side of the rule—only a tagged OL operation. The removal of the tags and replacing them with a specific tagged OL operations restricts the applicable breakdown rules to a smaller, possibly more optimized, subset of breakdown rules that simplifies the implementation of the generator. Note that rule (53) may need to be applied first to make (67) applicable.

An example of a vectorization or streaming rule is given by

$$\underbrace{A_n \otimes \mathcal{I}_{\nu}}_{\text{tag}} \to A_n \otimes_{\text{tag}} \mathcal{I}_{\nu} \quad \text{for tag} \in \{ \text{vec}(\nu), \, \text{fpga}(\nu) \}. \tag{68}$$

It states that for any  $A_n$ , the construct  $A_n \otimes I_{\nu}$  can be implemented using vector instructions by promoting any scalar operations in  $A_n$  to  $\nu$ -way vector operations. For example, the scalar operation a+b is replaced by  $\text{vec\_add}(a,b)$ . SSE code for  $F_2 \otimes_{\text{vec}(4)} I_4$  is given by the following code snippet:

Similarly, on an FPGA for a pipelined block  $A_n$  of streaming width w=1 (i.e., which takes one input per cycle over n cycles),  $A_n \otimes I_{\nu}$  can be implemented with streaming width  $w=\nu$  (consuming  $\nu$  inputs per cycle) by replicating the logic for  $A_n$  for  $\nu$  times.

Table 4 Advanced Vectorization and Parallelization Rules [19], [20], [22], [25].

$$\underbrace{\left(\underbrace{L_{m}^{mn}}_{\text{vec}(\nu)} \to \underbrace{\left(\underbrace{L_{m}^{mn/\nu} \otimes I_{\nu}\right)\left(I_{mn/\nu^{2}} \otimes L_{\nu}^{\nu^{2}}\right)\left(\left(I_{n/\nu} \otimes L_{m/\nu}^{m}\right) \otimes I_{\nu}\right)}_{\text{vec}(\nu)}, \quad \nu \mid m, n \right)}_{\text{vec}(\nu)} + \underbrace{\left(\underbrace{I_{m} \otimes A^{n \times n}\right) L_{m}^{mn}}_{\text{vec}(\nu)} \to \underbrace{\left(\underbrace{I_{m/\nu} \otimes \left(L_{\nu}^{n\nu} (A^{n \times n} \otimes I_{\nu})\right)\right)\left(L_{m/\nu}^{mn/\nu} \otimes I_{\nu}\right)}_{\text{vec}(\nu)}, \quad \nu \mid m \right)}_{\text{vec}(\nu)} + \underbrace{\left(\underbrace{I_{k} \otimes \left(\left(I_{m} \otimes A^{n \times n}\right) L_{m}^{kn}\right)\right) L_{k}^{kmn}}_{\text{vec}(\nu)} \to \underbrace{\left(\underbrace{L_{k}^{km} \otimes I_{n}\right)\left(I_{m} \otimes \left(\left(I_{k} \otimes A^{n \times n}\right) L_{k}^{kn}\right)\right)\left(L_{m}^{mn} \otimes I_{k}\right), \quad \nu \mid k, n \right)}_{\text{vec}(\nu)} + \underbrace{\left(\underbrace{L_{m}^{mn} \to \left(I_{p} \otimes L_{m/p}^{mn/p}\right)\left(L_{p}^{p^{2}} \otimes I_{mn/p^{2}}\right)\left(I_{p} \otimes \left(L_{p}^{n} \otimes I_{m/p}\right)\right), \quad p \mid m, n \right)}_{\text{mpi}(p)} + \underbrace{\left(\underbrace{L_{m}^{mp} \otimes I_{n/p}\right)\left(I_{p} \otimes \left(A_{m} \otimes I_{n/p}\right)\right)\left(L_{p}^{mp} \otimes I_{n/p}\right), \quad \mu \mid n/p \right)}_{\text{smp}(p,\mu)}$$

$$(75)$$

Often, a tag is "pushed down" recursively

$$\underbrace{\mathbf{I}_m \otimes A_n}_{\operatorname{vec}(\nu)} \to \mathbf{I}_m \otimes \underbrace{A_n}_{\operatorname{vec}(\nu)} \tag{69}$$

which states that if the kernel  $A_n$  can be vectorized, then just loop over it. A shorthand notation for parallel tags is  $\otimes_{\parallel}$  and for vector tags is  $\otimes$ .

4) Architecture-Aware Tiling: Rules (61) and (62) are stride permutation factorizations that capture tilings of matrix transposition. They break the transposition into two passes: one pass that transposes blocks and one pass that transposes within blocks. To model the target platform, the size constraints of the architecture are imposed on the factorizations. For instance, the rule

$$\underbrace{\mathbf{L}_{n}^{n\nu}}_{\text{vec}(\nu)} \to \left(\mathbf{I}_{n/\nu} \otimes \underbrace{\mathbf{L}_{\nu}^{\nu^{2}}}_{\text{vec}(\nu)}\right) \left(\mathbf{L}_{n/\nu}^{n} \otimes \mathbf{I}_{\nu}\right) \tag{70}$$

describes how stride permutations are performed efficiently on SIMD vector architectures such as Intel's SSE and AVX or the AltiVec and VSX extensions supported by PowerPC and POWER: it breaks the stride permutation into one stage that is performed solely with vector operations (captured by the tagged operation  $\otimes$ ) and one stage that performs small in-register transpositions (explained below).

More involved vectorization data flow transformations are captured by rules such as (71)–(73) in Table 4, which all ensure that data are accessed in SIMD vectors of size  $\nu$  and the only intravector operation is  $L_{\nu}^{\nu^2}$ , which will be handled below.

Parallelization for shared memory and message passing systems is captured by rules such as (74) and (75). Rule (74) factorizes a parallel transpose into local transposes and a big all-to-all communication with maximum packet size, while (75) performs a loop tiling transformation that

ensures that packets of size  $\mu$  are transferred between p processors, which avoids false sharing.

While the above discussion focused on SIMD vectors and parallelism on shared memory and message passing architectures, the underlying concepts can be generalized. Any hardware that requires coalesced access at a packet level is modeled similar to SIMD vectors, and any explicit or implicit messaging is modeled similar to the MPI rules. The focus in this section was on the stride permutation since it plays a central role in reshaping linearized high-dimensional data structures. However, other permutation families such as permutations that are linear on mixed-radix digits exhibit similar internal structures and can be handled analogously.

5) Architecture-Specific Templates: Rules such as (68) and (75) explain generically (for all operators A) how to vectorize or parallelize the respective data flow pattern. However, these rules may introduce irreducible operators such as  $L_{\nu}^{\nu^2}$  in case of (70) and  $L_{r}^{rs} \otimes I_u$  in case of (74). Spiral contains a template library for such constructs that explains how to implement them for each supported platform. Specifically, for SIMD vector architectures, Spiral requires code fragments that implement

$$L_{\nu}^{\nu^{2}}, L_{2}^{2\nu}, L_{\nu}^{2\nu}, L_{\nu/2}^{\nu^{2}/4} \otimes I_{2}, I_{\nu/2} \otimes \begin{bmatrix} a & b \\ -b & a \end{bmatrix}$$

(76)

for vectors of primitive data types such as reals and integers. These constructs are parameterized by the vector length  $\nu$ , abstract the details of the particular architecture, and provide support for data shuffling and complex arithmetic, e.g., required by  $\mathbf{T}_n^{mn}$ . Code for (76) is stored in Spiral's internal representation (icode, discussed in Section IV-B) and inserted upon program generation. The code templates can be written by hand but also, in certain cases, be generated automatically from the ISA as explained below. Fig. 4 shows a code example for  $\mathbf{L}_4^{16}$  implemented in Intel SSE 4-way float.

```

void L_16_4_SSE4x32f(__m128 *Y, __m128 *X) {

__m128 t3, t2, t1, t0;

t0 = _mm_unpacklo_ps(X[0], X[1]);

t2 = _mm_unpacklo_ps(X[2], X[3]);

t1 = _mm_unpackli_ps(X[0], X[1]);

t3 = _mm_unpackli_ps(X[2], X[3]);

Y[0] = _mm_movell_ps(t0, t2);

Y[1] = _mm_movell_ps(t2, t0);

Y[2] = _mm_movell_ps(t1, t3);

Y[3] = _mm_movell_ps(t3, t1);

}

```

Fig. 4. Code example for  ${\cal L}_4^{16}$  implemented in Intel SSE 4-way float.

The rule system ensures that as long as constructs (76) can be implemented efficiently, the whole data flow graph will be implemented efficiently. Sometimes algorithms require additional irreducible OL operators to be supported, and then users need to supply the necessary templates for the targeted architectures. Examples include the cyclic shift permutation that rotates vector components and the reduction operator that sums up all vector components. Once such a new operator template is provided, it is usable for any algorithm.

For distributed memory systems with message passing, the construct

$$P \otimes I_{\mu}$$

(77)