# SPLIT ARRAY AND SCALAR DATA CACHES: A COMPREHENSIVE STUDY

## OF DATA CACHE ORGANIZATION

Afrin Naz, B.Sc., M.S.

Dissertation Prepared for the Degree of

## DOCTOR OF PHILOSOPHY

## UNIVERSITY OF NORTH TEXAS

August 2007

APPROVED:

Krishna Kavi, Major Professor and Chair of the Department of Computer Science and Engineering Phil Sweany, Minor Professor Robert Brazile, Committee Member Stephen Tate, Committee Member Oscar Garcia, Dean of College of Engineering Sandra L. Terrell, Dean of the Robert B. Toulouse School of Graduate Studies Naz, Afrin. <u>Split array and scalar data cache: A comprehensive study of data</u> <u>cache organization.</u> Doctor of Philosophy (Computer Science) August 2007, 142 pp, 16 tables, 50 figures, references, 84 titles.

Existing cache organization suffers from the inability to distinguish different types of localities, and non-selectively cache all data rather than making any attempt to take special advantage of the locality type. This causes unnecessary movement of data among the levels of the memory hierarchy and increases in miss ratio. In this dissertation I propose a split data cache architecture that will group memory accesses as scalar or array references according to their inherent locality and will subsequently map each group to a dedicated cache partition. In this system, because scalar and array references will no longer negatively affect each other, cache-interference is diminished, delivering better performance. Further improvement is achieved by the introduction of victim cache, prefetching, data flattening and reconfigurability to tune the array and scalar caches for specific application.

The most significant contribution of my work is the introduction of novel cache architecture for embedded microprocessor platforms. My proposed cache architecture uses reconfigurability coupled with split data caches to reduce area and power consumed by cache memories while retaining performance gains. My results show excellent reductions in both memory size and memory access times, translating into reduced power consumption. Since there was a huge reduction in miss rates at L-1 caches, further power reduction is achieved by partially or completely shutting down L-2 data or L-2 instruction

caches. The saving in cache sizes resulting from these designs can be used for other processor activities including instruction and data prefetching, branch-prediction buffers. The potential benefits of such techniques for embedded applications have been evaluated in my work.

I also explore how my cache organization performs for non-numeric data structures. I propose a novel idea called "Data flattening" which is a profile based memory allocation technique to compress sparsely scattered pointer data into regular contiguous memory locations and explore the potentials of my proposed Spit cache organization for data treated with data flattening method. Copyright 2007

by

Afrin Naz

#### ACKNOWLEDGEMENTS

My gratitude and thank, first and foremost, belongs to Almighty Allah Subhanatala, who has given me this life, wisdom and strength.

There are a number of people who have been important in the completion of my dissertation, both academically and personally. This work would not have been possible without them. I owe them a great deal.

I thank my Prophet Muhammad (Peace be upon him.), Hazrat Abu Bakar Siddiq, Khwaja Bahauddin Naqshband, Shaykh Abd Allah al-Faiz ad-Daghestani, Shaykh Nazim Haqqani and finally my Shaykh Hisham Kabbani to enlighten my heart with their blessings.

Dr. K. Kavi has been my faculty advisor during my doctoral research in University of North Texas. He has taught me more about Computer Science than anyone else. His professional and personal standards would be an example to any student. It has been a privilege to work with him. My very best thanks to him, whom I owe a depth of gratitude. I am indebted to Dr. P. Sweany and his wife Dr. M.F. Sweany for all of their support and encouragement. Without their help I would not be able to finish writing of this dissertation. I also give my thanks to Dr. R. Brazile, Dr. S. Tate and Dr. M. Rezaei for devoting their time and support. I would like to thank the staff of Computer Science and Engineering Department of UNT for all the times they patiently took care of administrative matters of my PhD.

iii

I would like to thank my husband, Shahed, for his love, support, patience that he has given me for last ten years. He is the one who made me believe that I can finish my Ph.D. degree, he took care of my children when I needed to work, he gave me encouragement when I lost my hope, he finished the editing of this dissertation when I fall into sleep. I also want to thank my son Nazim and daughter Ameera for all the sacrifice they had made since they are born. I used to keep Nazim in my laboratory since he was three weeks old. Today, Ameera's birthday is not being celebrated only because I need to submit my dissertation tomorrow.

Today I am so happy that I have fulfilled the promise I made to my mom, Prof Razia Begum eleven years ago that someday I will attain a PhD degree like my dad, Dr. Manzural Hosain. I know both of my parents are happy for me. I also like to thank my brother, Dr. Nazmul Hosain and other relatives to provide support during this five and half years journey.

My Ph.D. is dedicated to my spiritual leader Shaykh Muhammad Hisham Kabbani.

May this work be a glory to Almighty Allah Subhanatala.

iv

# TABLE OF CONTENTS

|             |        |         | Page                                                               |

|-------------|--------|---------|--------------------------------------------------------------------|

| ACKNOWLE    | EDGEM  | ENTS.   | iii                                                                |

| LIST OF TAI | BLES   |         | ix                                                                 |

| LIST OF FIG | URES . | •••••   | x                                                                  |

| Chapter     |        |         |                                                                    |

| 1.          | INTRO  | ODUCT   | TION                                                               |

|             | 1.1    | Propos  | sed Cache Organization                                             |

|             |        | 1.1.1   | Scalar Cache and Array Cache                                       |

|             |        | 1.1.2   | Integration of Split Caches with Victim Cache and Stream<br>Buffer |

|             |        | 1.1.3   | Reconfigurability                                                  |

|             |        | 1.1.4   | Data Flattening5                                                   |

|             |        | 1.1.5   | Final Scheme5                                                      |

|             | 1.2    | Differe | ent Application Domains6                                           |

|             |        | 1.2.1   | Desktop Applications                                               |

|             |        | 1.2.2   | Embedded Applications                                              |

|             |        | 1.2.3   | Pointer-intensive Applications10                                   |

| 2.          |        |         | D DEFICIENCIES OF CONVENTIONAL CACHE                               |

|             | 2.1    | Cache   | and Locality of Reference                                          |

|             | 2.2    | Defici  | encies of Conventional Cache Designs14                             |

|             | 2.3    | Conve   | ntional Approaches to Improve Cache Design                         |

|             |        | 2.3.1   | Increasing Block Size and Cache Size15                             |

|             |        | 2.3.2   | Increasing Associativity16                                         |

|             |        | 2.3.3   | Probe Caches or Modified Set-associative Caches16                  |

|             |        | 2.3.4   | Supplementing Cache with Victim Cache17                            |

|    |      | 2.3.5 General Prefetching                                                      | 18 |

|----|------|--------------------------------------------------------------------------------|----|

|    |      | 2.3.6 Multilevel Caches                                                        | 19 |

|    | 2.4  | Comprehensive Evaluation                                                       | 19 |

|    | 2.5  | Issues in Designing Caches for Embedded Systems                                | 19 |

| 3. | RELA | TED WORK                                                                       | 21 |

|    | 3.1  | Cache in Desktop Applications 21 3.1.1 Related Work in Data<br>Cache Splitting | 21 |

|    |      | 3.1.2 Related Work with Victim Cache and Stream Buffer                         | 25 |

|    | 3.2  | Caches for Embedded Systems                                                    | 27 |

|    | 3.3  | Reconfigurable Caches                                                          | 29 |

|    | 3.4  | Data Flattening                                                                | 29 |

| 4. | EXPE | RIMENTAL ENVIRONMENT                                                           | 32 |

|    | 4.1  | Performance Metrics                                                            | 32 |

|    |      | 4.1.1 Cache Miss Rate                                                          | 32 |

|    |      | 4.1.2 Cache Access Time                                                        | 32 |

|    |      | 4.1.3 Area Analysis                                                            | 34 |

|    |      | 4.1.4 Static and Dynamic Power Consumption                                     | 34 |

|    |      | 4.1.5 Execution Cycles                                                         | 36 |

|    | 4.2  | Influence of Different Parameters                                              | 36 |

|    |      | 4.2.1 Interaction among Area, Performance and Power<br>Consumption             | 37 |

|    |      | 4.2.2 Influence of Associativity                                               | 40 |

|    | 4.3  | Benchmarks                                                                     | 40 |

|    |      | 4.3.1 Scientific Applications: SPEC Floating Point Benchmark                   |    |

|    |      | 4.3.2 Embedded Applications: Mi-bench Benchmarks                               | 42 |

|    |      | 4.3.3 Pointer-intensive Applications: Olden Benchmarks                         | 43 |

|    | 4.4  | Simulation                                                                     | 43 |

|    |      | 4.4.1 Simulation with ATOM Tools                                               | 44 |

|    |      | 4.4.2 Simplescalar Simulator                                                   | 45 |

| 5. |      | T DATA CACHE: AN APPROACH FOR SCIENTIFIC<br>ICATIONS                           | 46 |

|    | 5.1  | Introduction                                                                   | 46 |

|    |      |                                                                                |    |

|    | 5.2 | Desig                                                                                                    | n of Split Data Caches                                                             | 48 |

|----|-----|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----|

|    | 5.3 | Related Work4                                                                                            |                                                                                    |    |

|    | 5.4 | Experimental Methods                                                                                     |                                                                                    |    |

|    | 5.5 | Initial Evaluation of Split Data Caches                                                                  |                                                                                    |    |

|    |     | 5.5.1                                                                                                    | Finding Optimum Associativity, Block Size and Cache                                |    |

|    |     | 5.5.2                                                                                                    | Empirical Results with Split Data Caches                                           | 54 |

|    | 5.6 | Split Data Caches Integrated with Victim Cache and Stream<br>Buffer: An Approach for Further Improvement |                                                                                    |    |

|    |     | 5.6.1                                                                                                    | Victim Cache, Stream Buffer and the Integrated Approx                              |    |

|    |     | 5.6.2                                                                                                    | Empirical Results with Integrated Approach                                         | 62 |

|    | 5.7 | Conclu                                                                                                   | usions                                                                             | 66 |

| 6. |     | -                                                                                                        | VE OF PROPOSED CACHE IN THE ARENA OF<br>SYSTEMS                                    | 67 |

|    | 6.1 | Introduction                                                                                             |                                                                                    |    |

|    | 6.2 | Proposed Cache Organizations                                                                             |                                                                                    |    |

|    |     | 6.2.1                                                                                                    | Evaluation of Split Data Caches for Embedded Systems                               |    |

|    |     | 6.2.2                                                                                                    | Generalization of Split Caches with Victim Cache and Stream Buffer                 | 71 |

|    | 6.3 | Relate                                                                                                   | d Work                                                                             | 71 |

|    | 6.4 | Experimental Methods71                                                                                   |                                                                                    |    |

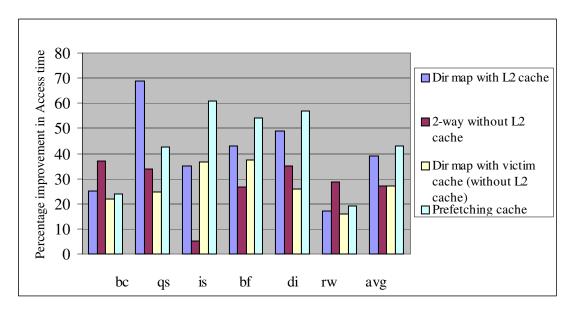

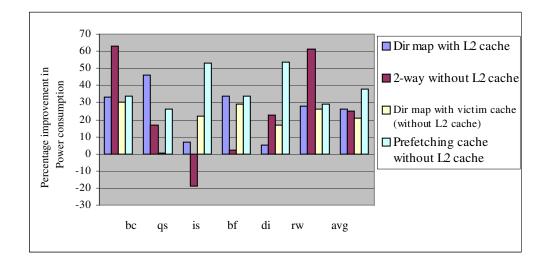

|    | 6.5 | Empirical Results                                                                                        |                                                                                    | 72 |

|    |     | 6.5.1                                                                                                    | Results with Split Data Caches for Embedded Systems                                | 72 |

|    |     | 6.5.2                                                                                                    | Results with Generalization of Split Caches with Victir<br>Cache and Stream Buffer |    |

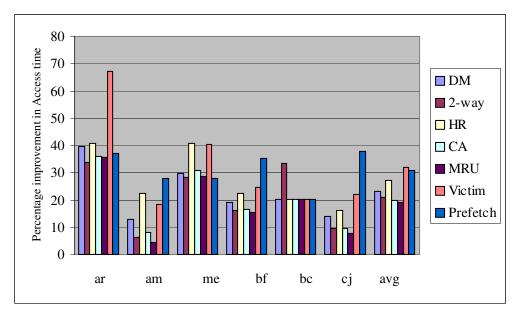

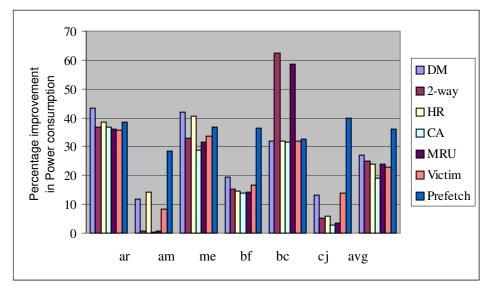

|    | 6.6 | Comprehensive Evaluation of Proposed Caches                                                              |                                                                                    | 78 |

|    | 6.7 | Conclu                                                                                                   | usions                                                                             | 83 |

| 7. |     |                                                                                                          | JRABLE SPLIT DATA CACHE: AN APPROACH FOR<br>APPLICATION                            |    |

|    | 7.1 | Introd                                                                                                   | uction                                                                             | 86 |

|    | 7.2 | Archit                                                                                                   | ectural Design of Reconfigurable Split Caches                                      | 89 |

|    |     | 7.2.1                                                                                                    | Segmentation of Tag and Data Arrays                                                | 90 |

|    |     |                                                                                                          |                                                                                    |    |

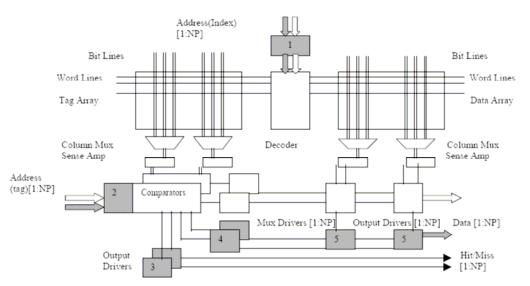

|    |      | 7.2.2  | Hardware Organization                                          | 91      |

|----|------|--------|----------------------------------------------------------------|---------|

|    |      | 7.2.3  | Reconfigurable Split Cache Organization                        |         |

|    | 7.3  | Relate | d Work                                                         | 94      |

|    | 7.4  | Exper  | imental Methods                                                | 96      |

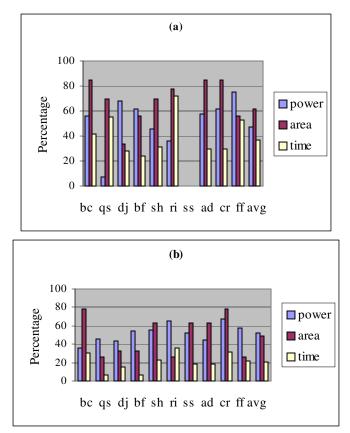

|    | 7.5  | Evalua | ation of Reconfigurable Split Data Caches                      |         |

|    |      | 7.5.1  | Results with Holding One Parameter Fixed                       |         |

|    |      | 7.5.2  | Results with L-1 and L-2 Instruction and Data Ca               | ches101 |

|    | 7.6  |        | ving Further Improvement with Reconfigurable Sp                |         |

|    |      | 7.6.1  | Utilization of the Unused Areas                                |         |

|    |      | 7.6.2  | Shut Down Portions of L-2 Instruction and Data                 |         |

|    | 7.7  |        | s after Achieving Further Improvement with Reco<br>Data Caches | -       |

|    |      | 7.7.1  | Results with Utilization of the Unused Areas                   | 109     |

|    |      | 7.7.2  | Results with Shut Down of L-2 Instruction and D<br>Caches      |         |

|    | 7.8  | Concl  | usions                                                         | 113     |

| 8. |      |        | TENING: AN APPROACH FOR POINTER INTI<br>ON                     |         |

|    | 8.1  | Introd | uction                                                         | 115     |

|    | 8.2  | Propos | sed Design                                                     | 116     |

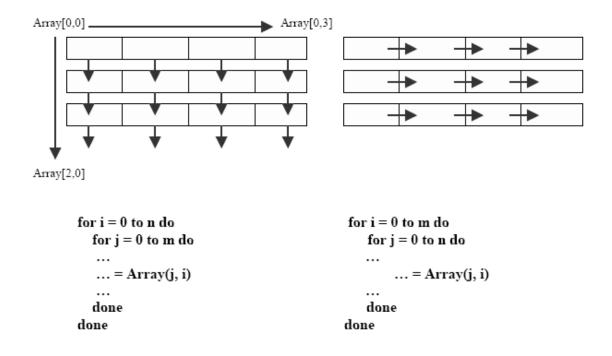

|    |      | 8.2.1  | Array vs. Pointers                                             | 116     |

|    |      | 8.2.2  | Different Data Placement Techniques                            | 118     |

|    |      | 8.2.3  | Data Flattening Method                                         |         |

|    | 8.3  | Relate | d Work                                                         |         |

|    | 8.4  | Exper  | imental Methods                                                |         |

|    | 8.5  | Empir  | ical Results with Data Flattening                              |         |

|    | 8.6  | Concl  | usions                                                         |         |

| 9. | CONC | CLUSIC | DNS                                                            | 131     |

# LIST OF TABLES

| 4.1 | Timing Equations Used to Compare Performance                                                                                                                            |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2 | Power Consumption Equations Used to Compare Performance                                                                                                                 |

| 4.3 | Definition of Terms Used in Timing and Power Consumption Equations                                                                                                      |

| 4.4 | Descriptions of SPEC Floating Point Benchmarks41                                                                                                                        |

| 4.5 | Descriptions of Mi-bench Benchmarks42                                                                                                                                   |

| 4.6 | Descriptions of Pointer-intensive Benchmarks                                                                                                                            |

| 5.1 | Configurations of Memory Hierarchy for Array, Scalar, Victim Caches and<br>Stream Buffer                                                                                |

| 5.2 | Comparison of Miss Rates of Direct-mapped Scalar Cache without Victim Cache,<br>2-way Set-associative Scalar Cache, and Direct-mapped Scalar Cache with Victim<br>Cache |

| 5.3 | Comparison of Miss Rate of a 4 Kilobytes Array Cache without Stream Buffer<br>and a 4 Kilobytes Array Cache with Stream Buffer                                          |

| 6.1 | Memory Configurations for Different Cache Designs Used in Comprehensive<br>Evaluation                                                                                   |

| 6.2 | Comparison of the Miss Rate of Split Cache with Traditional Cache Architecture                                                                                          |

| 6.3 | Comparison of the Miss Rate of Split Cache with Traditional Cache Architectures                                                                                         |

| 7.1 | Additional Multiplexors to Implement Reconfigurability                                                                                                                  |

| 7.2 | Simulation Configurations of Simplescalar                                                                                                                               |

| 7.3 | Cache Configurations Yielding Lowest Power, Area and Cache Access Time97                                                                                                |

| 8.1 | Simulation Configurations of Simplescalar                                                                                                                               |

# LIST OF FIGURES

| 1.1  | CPU-Memory Speed Gap1                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------|

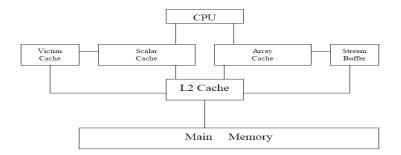

| 1.2  | Proposed Cache Organization                                                                                                 |

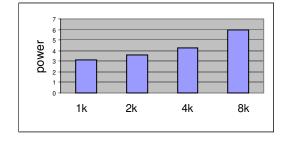

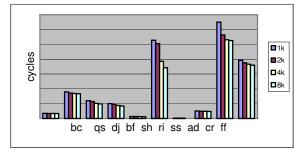

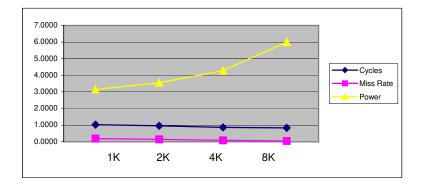

| 4.1  | Increase in Power Consumption as Cache Size Increases                                                                       |

| 4.2  | Decrease in Number of Cycles as Cache Size Increases                                                                        |

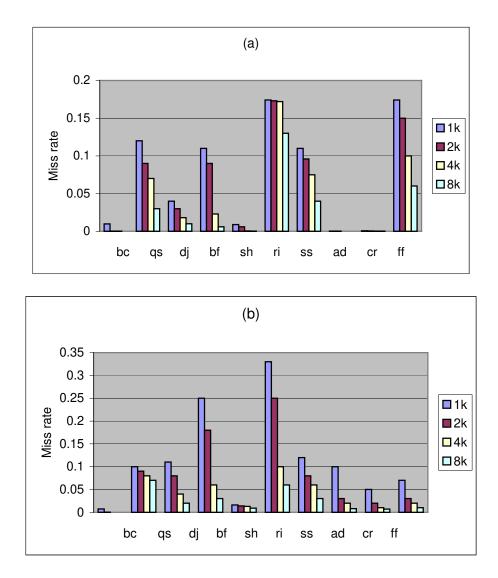

| 4.3  | Instruction (a) and Data (b) Cache Miss Rates for Increasing Cache Size                                                     |

| 4.4  | Changes in Power Consumption, Average Execution Cycles (in 100 millions.) and<br>Miss Rate as Cache Size Increases          |

| 5.1  | Split Data Cache Organization48                                                                                             |

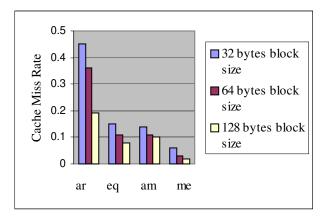

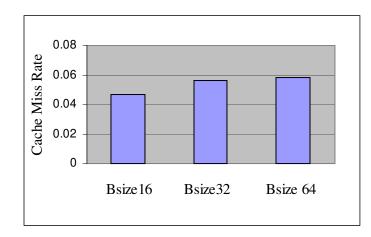

| 5.2  | Decrease in Cache Miss Rate with Increase in Block Size of 4 Kilobytes Array<br>Cache                                       |

| 5.3  | Increase in Cache Miss Rate with Increase in Block Size of Scalar Cache for<br>Benchmark 177 Mesa                           |

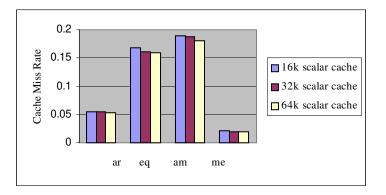

| 5.4  | Changes in Cache Miss Rate with Increase in Cache Size of Scalar Cache                                                      |

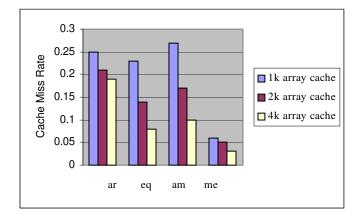

| 5.5  | Changes in Cache Miss Rate with Increase in Cache Size of Array Cache57                                                     |

| 5.6  | Changes in Cache Miss Rate for Array Cache with Different Associativity58                                                   |

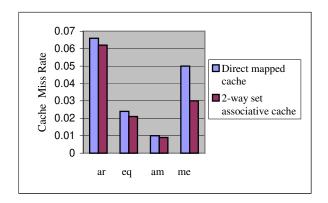

| 5.7  | Changes in Cache Miss Rate for Scalar Cache with Different Associativity58                                                  |

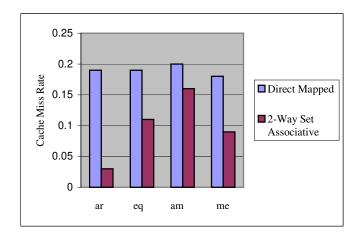

| 5.8  | Reduction in Effective Miss Rate with Split Array and Scalar Caches                                                         |

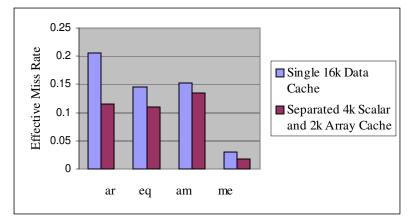

| 5.9  | Percentage Reduction in Access Time by Switching from 2-way Set-associative to Direct-mapped Scalar Cache with Victim Cache |

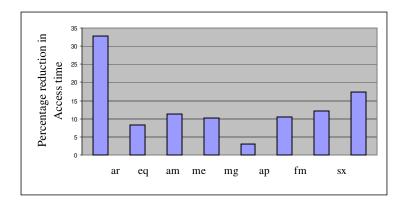

| 5.10 | Percentage Reduction in Access Time by Addition of Stream Buffers65                                                         |

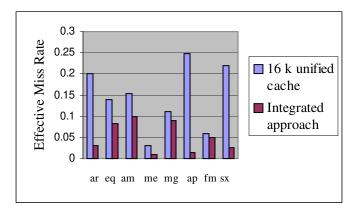

| 5.11 | Reduction in Effective Miss Rate with Integrated Approach65                                                                 |

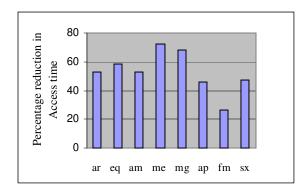

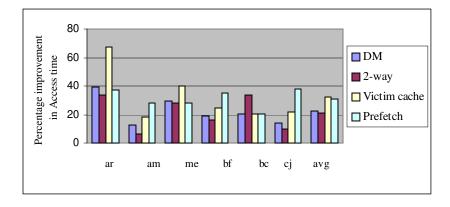

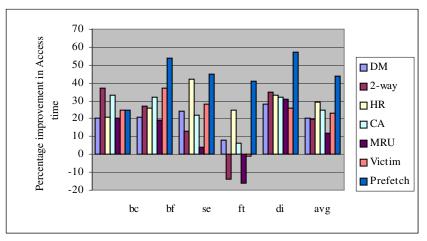

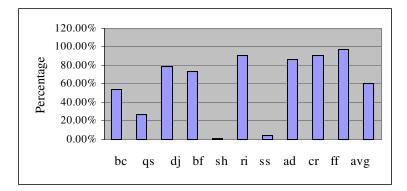

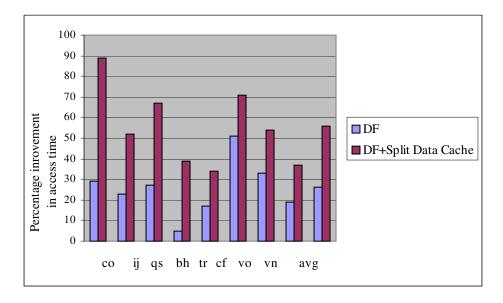

| 6.1  | Percentage Improvement in Access Time by Using the Split Data Caches73                                                      |

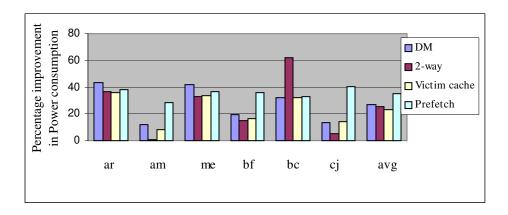

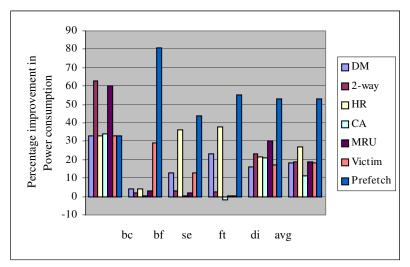

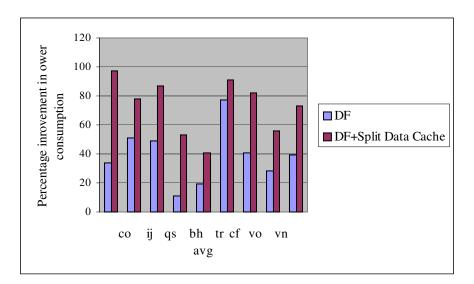

| 6.2  | Percentage Improvement in Power Consumption by Using the Split Data Caches                                                                                                                                                                                                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

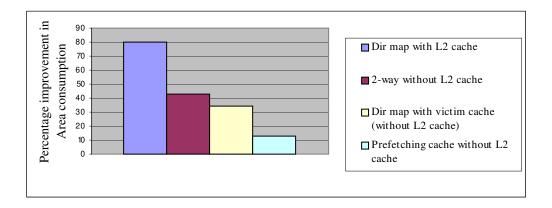

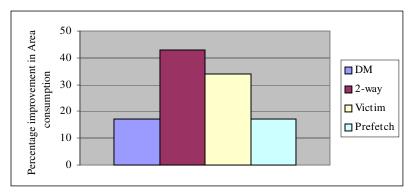

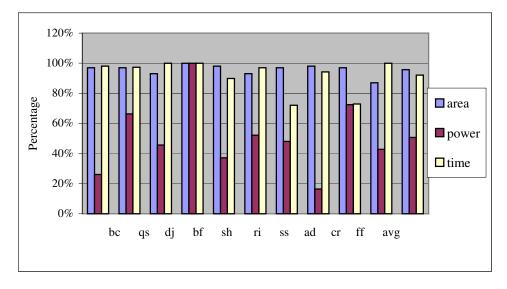

| 6.3  | Percentage Improvement in Area Consumption by Using the Integrated Approach<br>                                                                                                                                                                                              |

| 6.4  | Percentage Improvement in Access Time by Using the Integrated Approach76                                                                                                                                                                                                     |

| 6.5  | Percentage Improvement in Power Consumption by Using the Integrated<br>Approach                                                                                                                                                                                              |

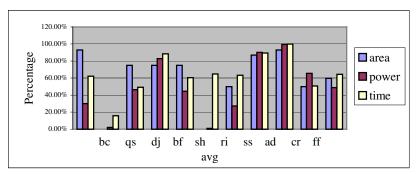

| 6.6  | Percentage Improvement in Access Time by Using the Data Split Cache                                                                                                                                                                                                          |

| 6.7  | Percentage Improvement in Power Consumption by Using the Data Split Cache                                                                                                                                                                                                    |

| 6.8  | Percentage Improvement in Area Consumption by Using the Integrated Approach                                                                                                                                                                                                  |

| 6.9  | Percentage Improvement in Access Time by Using the Integrated Approach82                                                                                                                                                                                                     |

| 7.0  | Percentage Improvement in Power Consumption by Using Integrated Approach                                                                                                                                                                                                     |

| 7.1  | Reconfigurable Split Cache Organization90                                                                                                                                                                                                                                    |

| 7.2  | Additional Logic for Reconfigurable Cache92                                                                                                                                                                                                                                  |

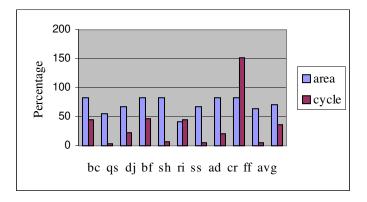

| 7.3  | Percentage of Area and Cycle Reduction                                                                                                                                                                                                                                       |

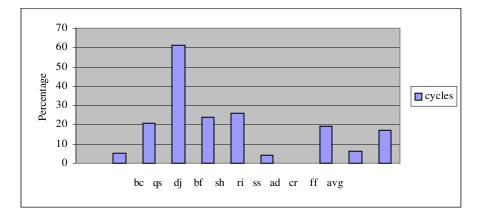

| 7.4  | Percentage of Cycle Reduction without Increased Area100                                                                                                                                                                                                                      |

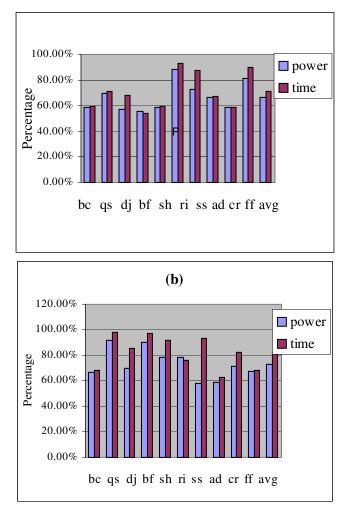

| 7.5  | Percentage Reduction of Power, Area and Cache Access time for L-1 (a)<br>Instruction and (b) Data Caches                                                                                                                                                                     |

| 7.6  | Percentage Reduction of Number of Access in L-2 Caches104                                                                                                                                                                                                                    |

| 7.7  | <ul> <li>(a) Percentage Reduction of Area, Power and Cache Access Time for L- 2</li> <li>Instruction Caches; (b) Percentage Reduction of Area, Power and Cache Access</li> <li>Time for L-2 Data Caches 105 7.8 Percentage Reduction of Execution Cycles</li> <li></li></ul> |

| 7.8  | Percentage Reduction of Execution Cycles                                                                                                                                                                                                                                     |

| 7.9  | Percentage of Power and Access Time Reduction with Prefetching for (a)<br>Instruction and (b) Data Caches                                                                                                                                                                    |

| 7.10 | Percentage Reduction of Execution Cycle after Implementing Prefetching111                                                                                                                                                                                                    |

| 7.11 | Percentage Reduction of Execution Cycle after Implementing Branch Prediction112                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.12 | Percentage of Dynamic and Static Power Reduction without and with Prefetching<br>for (a) Instruction and (b) Data Caches                                      |

| 8.1  | An Example of "Restructuring Computation" Approach119                                                                                                         |

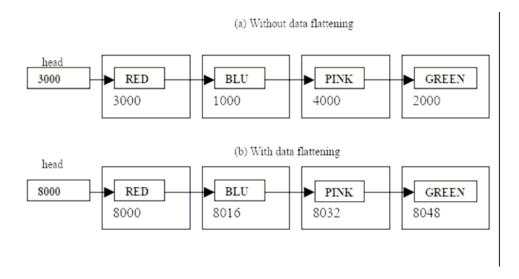

| 8.2  | Locations of Different Nodes in Memory of a List without Data Flattening (a) and with Data Flattening (b) 121 8.3 Percentage Improvement in Cache Access Time |

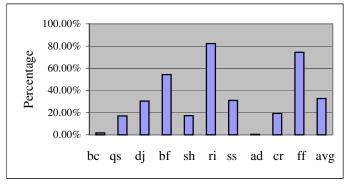

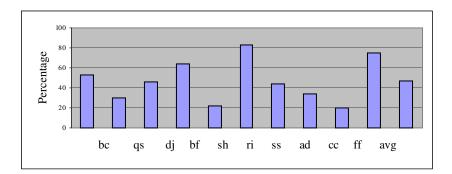

| 8.3  | Percentage Improvement in Cache Access Time127                                                                                                                |

| 8.4  | Percentage Improvement in Cache Power Consumption128                                                                                                          |

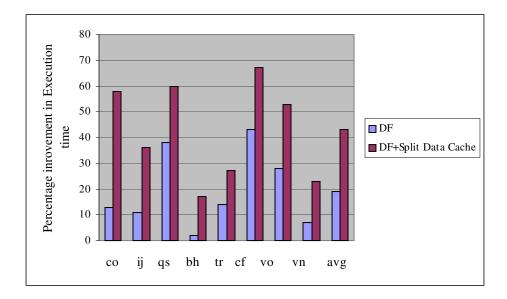

| 8.5  | Percentage Reduction of Execution Cycles                                                                                                                      |

## CHAPTER 1

## INTRODUCTION

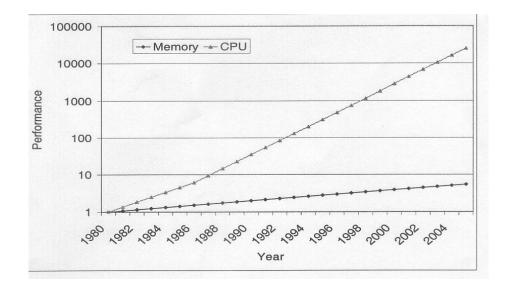

Although caching dates back to Von Neumanns' classic 1946 paper that laid the foundation for modern practical computing, it became vital to the performance of a processor since the beginning of 1990's, as the gap between the processor cycle and memory latency times increased dramatically. Figure 1.1 shows this famous "memory wall" problem; how fast Central Processing Unit (CPU) can process data is no longer a

Figure 1.1 CPU-Memory Speed Gap (Note that the y axis is log scaled.) [31]

problem, rather the main issue of concern in todays' computer system is how fast data can be provided to CPU. The problem is even more complicated in pointer intensive applications, which do not have regularity in data stream as scientific applications and for embedded applications, which place requirements along a number of dimensions including tighter constraints on functionality and on implementation.

As the CPU speed has outstripped the rest of the system by many orders of magnitude, more advanced techniques are needed to improve the performance of cache. This makes cache design one of the most important research topic in computer architecture field. According to Hennessy et al. [31] a bibliographic search for the years 1989-2001 revealed more than 5000 research papers on the subject of caches. Like most of these works, my research is also motivated by the "memory wall" problem. While searching for solutions, I have noticed a major drawback in conventional cache designs. Conventional caches imply no separation of data based on the nature of the characteristics (locality) exhibited by different data references and try to compromise between these data by sending them all to a unified data cache. I believe, that while transistors are plentiful in current Very-Large-Scale Integration (VLSI) designs, it is useful to allocate more resources to allow intelligent control over memory latency reducing techniques and that it is better to implement multiple smaller dedicated caches because these can be accessed relatively quickly. Being inspired by this realization, I propose "Split data caches." In my framework, the compiler will separate data references according to their inherent locality type and send them to appropriate cache. In this study I also show that when carefully designed, combination of different cache optimization techniques (Viz., prefetching, victim caching, data flattening and reconfigurability.) overcomes each other's deficiency and allows each to provide optimum benefit.

In this dissertation I show that even very small data caches, when split to serve data streams exhibiting temporal and spatial localities and augmented with smarter techniques like prefetching, victim caching, data flattening and reconfigurability, can improve performance of scientific, embedded and pointer intensive applications without consuming excessive silicon real estate or power.

#### 1.1 Proposed Cache Organization

First I describe my proposed cache organization in a step by step manner followed by the presentation of my final cache design.

#### 1.1.1 Scalar Cache and Array Cache

Programs exhibit two types of localities, temporal and spatial. Temporal locality implies that, once an instruction or datum is accessed, a high probability exists that it will be accessed again in the near future, and less likely to do so as the time passes. Scalar data items exhibit this behavior. Spatial locality implies that when an instruction or datum is accessed, nearby instructions or data will likely be accessed in the near future. Array data items have spatial locality. I propose a split cache architecture that will group memory accesses as scalar or array references according to their inherent locality and each group will be subsequently mapped to a dedicated cache partition. The "array cache" is a direct mapped cache with larger block sizes to exploit spatial localities more aggressively by prefetching multiple neighboring small blocks on a cache miss. The "scalar cache" is a set associative cache with smaller block sizes to exploit temporal locality.

#### 1.1.2 Integration of Split Caches with Victim Cache and Stream Buffer

Next I propose the inclusion of a victim cache and a stream buffer together with my split cache architecture to further improve my cache designs. Victim caches are based on the fact that reducing the cache misses due to line conflicts for data exhibiting temporal

locality provides an effective way to improve cache performance. Thus Victim caches can augment a direct mapped scalar cache without having to use a set associative cache. Stream buffers tend to eliminate cold misses and prefetch data exhibiting spatial locality. Thus stream buffers can improve array cache performance.

## 1.1.3 Reconfigurability

Then I try to reduce unnecessary area, power and time consumption by introducing reconfigurability. Reconfigurability is a design alternative that provides flexibility in the system so that resource constraints like area, power and performance can be balanced based on application needs. Ideally, the split cache organization should be dynamically reconfigurable to meet the application requirements. Depending upon the types of locality of data my system can partially shutdown a specific portion of the system. For example if the application has more scalar data then prefetch buffers and even the entire array cache may be shut-down to save power. Or the array cache can be dynamically reconfigured to increase the size of the scalar cache. When the unused cache areas are sufficiently large, these areas may be utilized for other processor activities such as larger branch prediction tables or prefetch buffers. By setting a few bits in a configuration register, the cache can be configured in software for optimum sizes for each of my array and scalar caches in Level one (L-1) and Level two (L-2) levels to utilize the unused area for other processor activities or to shut down. For both cases, the reconfiguration leads to only a small overhead in terms of time, power, silicon area and hardware complexity.

#### 1.1.4 Data Flattening

Finally I try to explore how my proposed cache organization performs for non numeric data or non-array data structures. I propose a novel idea called "data flattening" which is a profile based memory allocation technique to compress sparsely scattered pointer data into regular contiguous memory locations (Like array data.). Then I explore the potentials of my proposed spit cache organization for pointer data treated with data flattening method.

## 1.1.5 Final Scheme

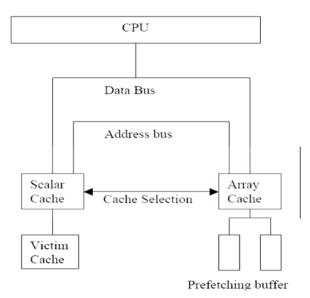

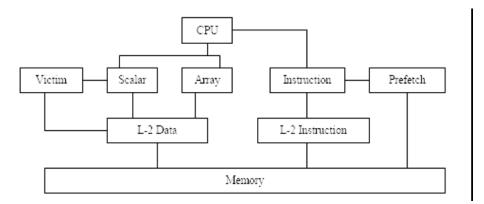

In Figure 1.2 I show the design of my final scheme.

Figure 1.2: Proposed Cache Organization

While other research groups reported on some aspects of cache organizations used in my research, the clear benefits of the combined approach to aggressively improve cache utilization for scientific, pointer intensive and embedded applications by combining split caching, victim caching, prefetching, data flattening and reconfigurability have, to my knowledge, not been studied in the literature.

## 1.2 Different Application Domains

In order to fully explore the problems in different application fields and describe my solutions, I first study existing cache memories for two classes of application domains: "desktop applications" and "embedded applications." The problems with desktop applications are more general as they are also applicable to embedded applications. Whereas for embedded applications the situation is more complicated because on top of these general problems (Inherited from desktop applications.), they have their own set of constraints. Finally I explore "pointer intensive applications" because both "desktop applications" and "embedded applications" utilize pointer based variables in their codes. Hence the problems with pointer intensive applications are present in any member of either desktop or embedded applications which have intensive non-numeric (pointer) data.

## 1.2.1 Desktop Applications

The success of cache memories has been explained by the property of *locality of reference* [74]. Caches exploit locality to shorten the effective access time to data, thereby reducing the cost of accessing main memory. To improve cache performance, modern processors rely on split cache architecture, at least on the first cache level, with separate instruction and data caches, since instruction and data streams exhibit different types of localities. The locality within the data address stream is also not uniform. However it is not common to see a separation of data caches based on access localities

exhibited. Since not all data items exhibit both spatial and temporal localities, using a common data cache is inefficient at adapting to spatial and temporal localities. This traditional method of using a single data cache causes unnecessary movement of data among the levels of the memory hierarchy, causing significant interference between unrelated data inside the cache, causing cache pollution (Viz., untimely removal of needed data.) and unnecessary increases in miss ratio, memory access time and memory bandwidth.

Hence it seems worthwhile to explore separate caches to deal with the two types of localities in data intensive applications. In this work, I have simulated a direct mapped array cache with large block sizes for stream and array references exhibiting spatial locality in order to permit prefetching and reduce compulsory misses. I use a set associative scalar cache with more numbers of smaller blocks to overcome high conflict misses. I have experimentally studied the impacts of split data caches using Standard Performance Evaluation Corporation (SPEC) floating point 2000 benchmarks. My results have shown that the split cache organization achieves lower miss rates and shorter average access times even when the combined size of array and scalar caches is roughly one quarter the size of a unified data cache.

This success has encouraged me to extend my research to explore other ideas for further improvement. I have investigated the interaction between three established methods, split caches, victim cache and stream buffer for improving hit rates in the first level of memory hierarchy. In my proposed cache organization, victim cache nicely complements the direct mapped scalar cache in terms of minimizing conflict misses, while stream buffers add to my array cache with prefetching capabilities. I show that the inclusion of a victim cache and a stream buffer together with partitioned cache architectures provides an effective solution for alleviating existing problems in cache designs and enhancing the effective cache memory space for a given cache size and cost.

## 1.2.2 Embedded Applications

Challenges to the design of processing elements for embedded applications are more stringent than those for desktop applications. Desktop systems afford greater design flexibility for cache memories in terms of cache sizes, associativities, block sizes and multi-level caches. Where as, the limitations on the physical size, real-time predictability, energy budget have made caches less common for embedded systems [35]. Because, caches have demonstrated their usefulness in a wide-range of applications, I feel that it is worthwhile investigating new cache organizations to address both performance and power requirements for embedded applications. While performing design space explorations of embedded systems, I have made four key observations.

Observation 1: Extreme cost sensitivity requires that designers of embedded systems pay more attention to physical size and energy requirements than to performance requirements. For almost all battery-operated systems, reducing total energy consumed is critical. Studies have shown that on-chip caches are responsible for 50% of an embedded processor's total power dissipation [82, 83] and, thus, savings in cache memory power can be significant in overall power savings.

Observation 2: For desktop systems, designers typically emphasize speed or throughput, based on average-case behaviors. In contrast, designers of real-time embedded systems

emphasize system's accuracy, predictability, and reliability, all related to the system's worst-case behavior. When a real-time embedded system controls critical equipment, execution time variability becomes completely unacceptable. Traditional hardware-managed caches prove unsuitable for embedded systems because they cannot accurately predict the access times to data.

Observation 3: Traditionally, designers of embedded systems have viewed complementing direct-mapped cache with a victim cache as an inappropriate choice [84], because fully associative victim caches consume additional energy and silicon area. For similar reasons, prefetching is considered ill suited for embedded systems [35]. Other performance optimization techniques such as instruction reuse (Using trace caches.), branch predictions are also not implemented in embedded systems as they require additional hardware for implementing look-up tables, which lead to increased area and power requirements.

Observation 4: The manufacturer typically selects a fixed cache architecture as a compromise across several applications. For embedded systems, since each architectural feature must be customized for each application, this "one-size-fits-all" fixed cache design philosophy is not adequate, as this will lead to suboptimal performance and/or power consumption profiles. Thus it is necessary to provide for reconfigurable caches whereby the size of array and scalar caches, their block-sizes, associativities, as well as the sizes of prefetch buffers and victim caches can be chosen for each application.

9

I claim that my approach that brings together various cache alternatives addresses the challenges faced by embedded system designers. Since my design reduces the effective memory access times, they can be useful even in real-time systems with strict-deadlines. At the same time, because my split cache design leads to smaller cache sizes (To achieve the same level of performance as a unified data cache.), with reconfigurability, one can either shut down portions of cache to save energy, or use the space to improve system performance by converting the unused portions of caches into trace caches (For instruction reuse or data predictions.) or branch prediction buffers.

## 1.2.3 Pointer-intensive Applications

It is very obvious that my proposed split cache organization will perform better for numeric applications that utilize arrays and streams. But I wanted to explore the benefits of my proposed cache organization for non-numeric applications with pointer data. Pointer data structures contain dynamically allocated data elements that are linked together. In many applications such structures provide for elegant algorithms since the number of elements can grow without a predetermined limit. However, the dynamic allocation cannot assure that consecutive nodes occupy consecutive areas in memory, thus making it difficult to prefetch linked data elements. The lack of (spatial) localities also makes traditional cache designs ineffective. This led computer system designers to investigate new ways for tolerating memory latencies in accessing linked data elements. In my research, I propose to "flatten" the linked data structures into a linear data structure similar to arrays and streams so that I can take advantage of my split data caches described earlier. Data placement is the method to pack sparsely scattered data into adjacent memory locations to take advantage of spatial locality and prefetching. Other researchers have proposed innovative data placement techniques to improve localities of non-numeric (Or non-array.) data [15, 22]. However they have been proposed in the context of a conventional data cache design and not in the context of a reconfigurable split data cache design. In my context "data flattening" is a profile based memory allocation technique which compresses sparsely scattered pointer data into regular contiguous memory locations (Like array data.). I believe since the non-numeric pointer data will exhibit similar pattern after being flattened into a linear structure my cache organization will prove to be useful for a wide-variety of scientific, non-scientific and embedded applications.

The rest of the dissertation is organized as follows:

In Chapter 2 I present a description of designs and deficiencies of conventional cache memories. I provide a survey on related work on Chapter 3. In Chapter 4 I describe the experimental environment used in my study, including performance metrics, benchmarks and tools used in my study. I begin Chapter 5 with the initial evaluation of split array and scalar data caches and show their uniform superiority over the conventional unified data cache design across all of the benchmarks. For example, a 4 kilobytes 32 bytes block sized scalar cache and 2 kilobytes 128 bytes block sized array cache show 43.41%, 24.14%, 11.76% and 43.33% improvements over a 16 kilobytes 64 bytes block sized unified scalar cache for ar, eq, am and me benchmarks respectively. Then I demonstrate how three inherently different approaches, split cache, victim cache and stream buffer

could be combined and make to work together to further improve data access times. For example a 4 kilobytes scalar cache (With 256 bytes victim cache.) and 4 kilobytes array cache (With 512 bytes stream buffer.) on average show 55% improvement over a 16 kilobytes unified data cache for the benchmark set. In Chapter 6 I explore how to design small caches (Including prefetching and victim caching.) that achieve high performance for embedded applications. I also performed a comprehensive evaluation of my proposed methods by comparing with a variety of techniques that have traditionally been applied to improve cache systems. My cache architecture reduced the overall cache size by 43%, access time by 37% and energy consumption by 63% when compared with a unified 2way set associative cache. In Chapter 7 I explore how reconfigurability can be used to design caches for embedded applications. My cache architecture reduces the cache area by as much as 78%, access times by as much as 36% and power consumption by as much as 67% respectively when compared with an 8 kilobytes L-1 unified data caches. Then I explored how unused cache portions can be used for different optimization methods or how power reduction can be achieved by partial/complete shutdown of L-2 caches. I evaluate my novel "data flattening" method in Chapter 8. My split data caches with flattened data provide excellent improvement for all of the benchmarks; on average 56%, 73% and 43% reduction in access time, power consumption and performance respectively, when compared with original code (Without data flattening.) using unified data cache. Finally in Chapter 9 I draw my conclusion with a brief synopsis of future work.

### CHAPTER 2

#### DESIGN AND DEFICIENCIES OF CONVENTIONAL CACHE MEMORY

I begin this chapter with a description of design and deficiencies of conventional cache memories. Next I present the traditional cache optimization techniques used for desktop applications, followed by a brief description of comprehensive evaluation of my proposed design, which includes all of these traditional techniques. Finally I point out the challenges involved with cache designing for embedded microprocessors.

## 2.1 Cache and Locality of Reference

In modern systems cache has become the basic and inevitable mechanism for effectively reducing memory access latencies and for improving overall system performance. Caches are typically placed between a large, relatively slow and inexpensive source of information (The lower level of memory.) and a much faster consumer of that information, the processor. The success of cache memories has been explained by the property of locality of reference [74], which is a property exhibited by most programs. The property of locality has two aspects: temporal and spatial. Temporal locality implies that, once a location is referenced, there is a high probability that it will be referenced again soon, and less likely to do so as the time passes; spatial locality implies that when an instruction or datum is accessed it is very likely that nearby instructions or data will be accessed soon. Since cache buffers recently used segments of information, the property of locality implies that needed information is also likely to be found in the cache. A cache exploits this property to improve the effective access time to data and reducing the cost of accessing main memory.

### 2.2 Deficiencies of Conventional Cache Designs

As the Central Processing Unit (CPU) speed has outstripped the rest of the system by many orders of magnitude and the memory latency problem has continued to grow, some deficiencies of conventional caching have become evident. Conventional caches imply no separation of data based on the nature of the locality exhibited by different data references. As a result all memory references are handled in a uniform manner whenever a reference misses, a new block is brought into cache at the expense of replacing another block. Because not all data items exhibit both spatial and temporal localities, this simple-minded treatment to the references makes the data cache inefficient at adapting to the two types of localities. Generally, caches exploit temporal locality by retaining recently referenced data for a long time, and spatial locality by fetching multiple neighboring words as a cache block on a cache miss. If a data item exhibits no temporal locality, bringing it into the cache is useless. Likewise if no spatial locality is exhibited by data items, bringing an entire cache block leads to wastage. Thus traditional treatment of cache misses not only causes unnecessary movement of data between the various levels of the memory hierarchy, it may lead to premature displacement of blocks that are likely to be re-referenced (A phenomenon known as cache pollution.). This can become costly if the newly loaded data tends to be non-temporal. In any case, an unnecessary increase in miss ratios, memory access times and wasted memory bandwidths occur.

References can be easily divided into two groups according to the types of localities exhibited by the program – the scalar and array (stream) references. Conventional cache techniques perform acceptably for general-purpose scalar references with high temporal

locality. But such is not true for array references, which do not reuse data soon or often enough to derive much benefit from caching. Because arrays and streams exhibit only spatial localities and the data sizes are often very large for caches, computations with streams and array access patterns cause mostly compulsory misses (Rather than conflict misses.) and perform extremely poorly in terms of cache behavior.

#### 2.3 Conventional Approaches to Improve Cache Design

For two decades computer architects have proposed smart cache-control mechanisms and novel cache architectures that detect program access patterns and fine-tune cache policies to improve both overall cache use and data localities for desktop applications. Major cache optimization techniques (To improve either or both miss rate and miss penalty.) are generally categorized as: (1) increasing block size and cache size, (2) increasing associativity, (3) cache probing, (4) supplementing the regular cache with victim cache, (5) prefetching data, or (6) including additional cache hierarchy.

## 2.3.1 Increasing Block Size and Cache Size

The simplest way to reduce miss rate is to use large block sizes; large blocks reduce cold misses and aid in data prefetching. Unfortunately, larger blocks increase miss penalty, which may outweigh the benefits of reduced miss rates. Actually, increasing block size without increasing the total cache size increases other types of misses because increasing only block size (Not cache size.) reduces the number of lines, leading to an increase in conflict and capacity misses [31]. Current desktop computers have used larger caches with larger block sizes for off-chip caches. Some of these caches are as large as the main memories of a decade ago [31].

#### 2.3.2 Increasing Associativity

Another common technique for reducing miss rates is increasing associativity. Caches with higher associativity (4- to 8-way associativity.) have become common in both desktop and server systems. Unfortunately, the design of a first-level cache always involves fundamental tradeoffs between miss rates and access times. Direct-mapped caches have proven to be simpler, easier to design and require less silicon area than caches with higher associativities. The main disadvantage of a direct-mapped cache is the high conflict miss rate—conflict misses typically account for 40% of all direct-mapped cache misses [39]. Conversely for caches with higher associativity, the main advantage becomes lower miss rate, but such caches have higher access times as they require associative searches of sets and multiplexing of the appropriate data words to the processor.

#### 2.3.3 Probe Caches or Modified Set-associative Caches

Recently researchers have proposed Probe caches (Modified 2 way set-associative cache.) that result in miss rates like a 2-way set associative cache, but hit-times like a direct mapped cache [1, 2, 14, 17, 75]. These "sequential search" of set associative caches or probe caches are based on the key observation that associativity is needed only for conflicting blocks and should not be provided at the expense of higher hit latencies for all accesses. In most of these schemes, a traditional direct-mapped cache is conceptually partitioned into sets with 2 blocks per set. Cache access is sequential; first one block is probed, and if the tag doesn't match the second block in the set is probed. In order to achieve fast access different probe caches use different data structures, ranging

from simple hash/mru bit, to complicated way prediction mechanisms [1, 2, 14, 17, 75]. The examples of probe cache include Hash rehash cache [1], Column associative cache [2], MRU cache [17, 75]. Hash rehash cache (HR cache) uses fixed probe order with different hash functions to search the cache [1]. The Column associative cache (CA cache) improves on Hash rehash cache by associating rehash information with each block and improving the replacement algorithm, which reduces the number of second probes required [2]. MRU cache uses a dynamic probe ordering based on most recently used information [17, 75].

2.3.4 Supplementing Cache with Victim Cache

A Victim cache is a fully associative cache, with typically 4 to 16 cache lines that reside between a direct-mapped Level one (L-1) cache and the next level of memory [39]. On a main cache miss, the victim cache is checked before going to the next level of memory. If the address hits in the victim cache the desired data is returned to the CPU and swapped (Or promoted.) with the data currently occupying the primary cache. Upon a miss in victim cache, the next level of memory is accessed and the arriving data is placed in the primary cache, moving the current data to victim cache. In this case an element from victim caches has to be removed (Or written back to next level of memory.) to make room for the newly victimized data.

While set-associative caches, with fewer conflict misses, offer lower miss rates than direct-mapped caches, they cost more and incur longer access times on a hit. Victim caches, in contrast, reduce conflict misses of direct-mapped caches without affecting its fast hit access times. Because victim caches are fully associative (Albeit small.), they can

hold many blocks simultaneously that might otherwise conflict in direct-mapped cache. If most of the conflicting blocks can fit in victim cache, both the miss rates and the average access times improve.

## 2.3.5 General Prefetching

As another technique to improve efficiency, prefetching or exploiting the overlap of processor computations with data access has proven to be effective in tolerating large memory latencies in desktop systems [8, 52]. Although increasing line size presents the simplest way of prefetching, line sizes cannot be made arbitrarily large without both increasing miss rates and greatly increasing the amount of data transferred on cache misses (Thus increasing miss penalties.) [31]. Prefetching can be either hardware or software based [8], [52]. Hardware-based prefetching [8] requires additional hardware connected to the cache. Software prefetching [52] relies on compiler technology to insert explicit prefetch instructions. Typically, on a miss the processor fetches additional blocks along with the requested block. The processor places the requested block in the primary cache and places the prefetched blocks either in the primary cache or in an external buffer. On a future reference, if the processor locates the requested block in the buffer, the original cache request to next level of memory is cancelled, the processor reads the block from buffer and issues the next prefetch request. For data with spatial locality, prefetching is beneficial.

Stream buffer is a fully associative, First In First Out (FIFO) buffer with 4 or 5 entries specially designed to support direct-mapped cache through hardware based prefetching [39]. A miss induces fetching of the missed block along with successive blocks stored in

the buffer rather than the cache. My intent is to use the stream buffer for prefetched blocks and avoid cache pollution.

#### 2.3.6 Multilevel Caches

Inclusion of additional cache hierarchy provides a common technique to improve performance of desktop applications. Adding a second level of cache between the original cache and the main memory improves access times. The L-1 cache can remain small enough to match the clock cycle time of fast CPU, while the L-2 cache can become large enough to capture most accesses, thereby lessening the access time. Some recent architectures contain a third level cache, whereby an even larger cache is placed between the L-2 cache and the main memory.

#### 2.4 Comprehensive Evaluation

I have provided a survey of most popular traditional approaches (Described in section 2.3.) that have been used to improve the cache performance of desktop applications and have selected one or more representatives of each technique. In this research I employed a simulation environment representing each of these traditional techniques and performed a comprehensive evaluation of my proposed methods by comparing them with each of these traditional cache organizations. Results of this comprehensive evaluation are described in chapter 6.

#### 2.5 Issues in Designing Caches for Embedded Systems

Unfortunately the optimization methods described in section 2.3 (Which work well for desktop application.) are not suitable for embedded applications. For desktop applications, the simplest way to improve performance is to increase the cache size and

block size. Whereas, embedded systems cannot include large caches or arbitrarily large block sizes because of the physical size and power constraints. Caches with higher (Or modified.) associativity remain unpopular for embedded systems mostly because higher associativity leads to high power consumption [67, 82]. Thus most cache design efforts have concentrated on optimizing direct-mapped cache organizations. Although victim caches commonly appear in desktop computing, designers have viewed supplementing direct-mapped cache with a victim cache as an inappropriate choice for embedded systems [84], because fully associative victim caches require additional energy and silicon area. Similarly, although successful prefetching can reduce miss rates, any unnecessary prefetching not only wastes the embedded system's valuable power but may also cause cache pollution which leads to additional misses and wasted energy. Additional level of cache hierarchy is also not popular in embedded applications [35]. Because the requirements of cache design in embedded systems differs from that in desktops, I propose reconfigurable split data caches for embedded applications, which will be described in later chapters.

## CHAPTER 3

#### RELATED WORK

In this chapter I provide a survey of related work. In later chapters (Chapter 5-8.) when I describe different stages of my work, I try to distinguish my work from the related work described here.

3.1 Cache in Desktop Applications

I divide this chapter in to two sections. First I describe the related work with data cache splitting, which is followed by the description of the related work with victim cache and stream buffer.

## 3.1.1 Related Work in Data Cache Splitting

Supplementing the cache with a small extra module to exploit temporal and spatial localities was first proposed by Jouppi [39]. Subsequent to Jouppi's work, two approaches emerged; the first approach retains Jouppi's original idea and supplements the regular cache with a small buffer for prefetching all data items regardless of the nature of locality exhibited by the data; the second approach is real cache partitioning to exploit data localities exhibited by different data types. Partitioning of the cache can be either static or dynamic.

The most extensive and prominent work belonging to the first trend is done by Mckee *et al.* [54]. They designed a stream memory controller (SMC), a combination of a small buffer and an intelligent scheduling unit for supporting the regular cache. When the program enters a loop that accesses one or more streams, compiler-generated code provides the scheduling unit with the base addresses, the number of elements, and the

strides for any streams accessed in the loop body. A Memory Scheduling Unit (MSU) uses this information to reorder the requests so that even though the processor still issues requests to the Stream Buffer Unit (SBU) in the natural order, the order in which associated requests are made to memory will maximize the use of its bandwidth. Because the stream accesses no longer affects the cache, the cache can be designed more optimally for the remaining requests.

Sanchez *et al.* [71] propose a dual data cache, composed of two modules. The temporal module is a fully associative buffer, built to exploit just temporal locality and spatial module, is a direct mapped cache targeted to exploit spatial locality. The temporal module has only 16 short blocks (Each 8 bytes.) and the spatial module has larger blocks (32 bytes per block.). At compile time, memory instructions are tagged as *bypass* (Data that do not exhibit any type of locality.), spatial, or temporal. On a miss both modules are checked in parallel to find the required data. References tagged as bypass are sent to directly to the Central Processing Unit (CPU) rather than bringing them into cache. If the reference receives a spatial or temporal tag, a new block is brought into the module indicated by the tag. Previously they proposed a similar architecture [28], where rather than using compile time annotations, they tagged memory references at execution time using an additional hardware unit called *locality prediction table*.

Tomasko *et al.* [78] reported on a preliminary experimental evaluation of architecture with separate array and scalar caches to exploit the potential benefits to a cache organization based on a specific type of locality. In their experiment they assumed a model where the tagging of data as array or scalar to be allocated in one or the other

caches would be done statically by compiler and the model does not assume any extensive analysis of references to determine the nature of the locality of access; rather it allocates the data only on the basis of the data type declaration.

Split Temporal/Spatial (STS) cache proposed by Milutinovic *et al.* [56] differs slightly from other proposed split caches I have already discussed. Because for "temporal" data hierarchy is needed (To reduce miss penalty for subsequent misses.) but fetching the entire block is unnecessary, the temporal part is organized as a two level hierarchy with one word block size. The spatial part is one-level with four 32-bit words with a hardware implemented prefetching mechanism. The STS cache contains four variants STS1, STS2, STS4a STS4b, each with same sized temporal module but larger spatial modules. Spatial and non spatial modules are 4-way set associative with Least Recently Used (LRU) replacement. Initially all data blocks are regarded as "spatial," a data block may be changed to "temporal" and re-allocated through optimization of relevant parameters (Using different counters to detect locality.) during profiling or during runtime by means of a monitoring hardware unit.

In order to avoid the problem of determining counter thresholds present in STS method and also the problem of complicated memory hierarchies for each module, Milutinovic *et al.* [57] proposed a simple method of detecting useful spatial locality which is tested by incorporating it into a new split cache design, called the Split Spatial/Non-Spatial (SS/NS) cache. For detecting different types of locality the design used a flag-based method, requiring fewer cache bits than counter implementation of STS. For exploiting the locality the system has two separate modules with same associativity and equal hierarchy. Prefetching is used if spatial locality is too large to be exploited by larger cache block.

The Hewlett Packard-7200 Assist cache [46, 68] design tries to avoid both cache conflict and cache pollution due to prefetching. The primary direct-mapped cache is coupled with a small fully associative buffer (the Assist buffer), with a one-cycle lookup in both units. The direct-mapped primary cache and the buffer units are designed with equal sized blocks. Until a block is identified as temporal, if it is requested either by a cache miss or a prefetch, the block is first loaded into the Assist buffer. It is promoted into the direct-mapped unit only when it exhibits temporal reuse. Spatial-only data, especially array data, may bypass the direct-mapped cache entirely, moving back to memory in First In First Out (FIFO) fashion from the Assist buffer. In this system dynamic associativity is provided by allowing up to N+1 conflicting blocks, which belong to the same direct-mapped set, to co-exist in the cache simultaneously, where N is the number of block entries in the Assist buffer. Since only a uni-directional communication exists between the direct-mapped unit and the Assist buffer no swapping between the two units is allowed.

The Non-Temporal Streaming (NTS) cache proposed by Rivers and Davidson [69] dynamically detects temporal (T) and non-temporal (NT) data and cache them separately. The NTS cache consists of a Data Storing Unit (DSU) which is a conventional direct mapped cache supplemented with a small fully-associative buffer (NT buffer) and a Non-Temporal Detection Unit (NTDU), which is a hardware bit-map structure attached to the main cache in order to monitor the reuse behavior of the blocks. Cache block size is

uniform across the direct-mapped cache primary cache, the buffer units and the next level of memory. The strategies adopted in the NTS cache for detecting and caching temporal and non-temporal references are very similar to those implemented in Hewlett Packard - 7200 Assist cache [46, 68].

Lee *et al.* [49] have proposed a cache system called Selective Temporal and Aggressive Spatial (STAS) cache. Although they claimed to have two separate caches for temporal and spatial references with different block sizes, the module for spatial locality is actually a buffer rather than a cache. In this system, on every memory access, both modules are accessed simultaneously. If a miss occurs at both places the block is brought to the spatial buffer. However a write back of dirty block in spatial buffer cannot occur directly - the dirty block is always placed in the direct mapped cache before being replaced. Later Lee *et al.* [50] extended the STAS cache into another cache structure Selective Mode Intelligent (SMI) cache which consists of three parts: a direct-mapped cache with a small block size, a fully associative spatial buffer with large block size and a hardware prefetching unit.

### 3.1.2 Related Work with Victim Cache and Stream Buffer

Albera and Bahar [4] combined software code placement and associative-buffer solutions for high performance processors and showed that the buffer can improve performance even more after code layout optimization is applied than when used without the code optimization. In a later study Bahr *et al.* compared the use of victim caches to more traditional techniques and showed that use of a victim cache is usually a better choice for both power and performance [9].

Espasa and Valero [25] considered the usefulness of adding a victim cache next to the register level of a vector processor and show that such placement can provide speedups by allowing a good tolerance of large memory latencies. Hormdee *et al.* proposed an architecture of a self-timed victim cache with a forwarding mechanism suitable for use within an asynchronous environment [33].

Except for the addition of the non-swapping option, no other extension to Jouppi's original victim cache [39] was implemented by any of these above-mentioned studies. Bahar *et al.* [9] tried to add some extra flavor in their "penalty buffer" but failed to gain much improvement. Only one group, Stiliadis *et al.* proposed an improvement of victim caching called "selective victim caching" [77]. In this method a prediction scheme based on each block's past history of utilization is used to selectively place a block either in the main cache or victim cache on a cache miss in either cache and to decide whether to perform swap or not in the case of victim hit.

As described in section 3.1.1, the most extensive and prominent work with stream buffers is that of McKee *et al.* [54]. Their designed SMC is a combination of a stream buffer and an intelligent scheduling unit for supporting regular cache. Palacharla and Kessler [65] have proposed the use of multiple stream buffers to replace big secondary cache.

To date, no study has combined the implementation of victim cache and stream buffer with separated data cache approach. Johnson *et al.* [37] proposed a method where a single 4–way set associative buffer is used to serve the function of both victim cache and stream buffer on groups of data that have been differentiated based upon the reuse behavior. Johnson et al. [37] presented a method to improve the efficiency of cache by bypassing data that is expected to have little reuse in cache and allowing more frequently accessed data to remain cached longer. The bypassing choices are made by a Memory Address Table (MAT), which analyzes the usage patterns of the memory locations accessed. In order to characterize memory locations they introduce the notion of macro-block, which is a group of statically defined blocks of memory with uniform size (1 kilobytes). They used a direct mapped 16 kilobytes Level one (L-1) data cache and 256 kilobytes Level two (L-2) data cache with fully associative buffers of 8 and 256 entries respectively, which hold bypassing data and are accessed in the same manner as a victim cache. Since fetching the entire cache block for bypassed data with little spatial locality will cause cache pollution and extra traffic, they used small lines (Equal to the element size.) for the buffers and optionally filled in consecutive blocks when spatial locality is detected. As we can see they are using a single buffer to serve the purpose of both a victim cache (For scalar data.) and a prefetch buffer (For stream data.). In a later study [38] they extended their scheme by adding an extra structure Spatial Locality Detection Table (SLDT) and extra counter for each MAT entry to detect spatial locality so that the system can adapt to varying spatial locality by dynamically adjusting the amount of data fetched on a cache miss.

#### 3.2 Caches for Embedded Systems

Exploitation of various cache parameters such as associativity and block sizes offer the most common approaches to improve cache performance for desktop systems [74]. Following this approach, Givargis, *et al.* explored the effects of cache size, block size and