# Statistical Estimation of Leakage Current Considering Inter- and Intra-Die Process Variation

Rajeev Rao

Ashish Srivastava

**David Blaauw**

Dennis Sylvester

University of Michigan, EECS Department, Ann Arbor, MI 48109

{rrrao,ansrivas,blaauw,dennis}@eecs.umich.edu

**Abstract** – We develop a method to estimate the variation of leakage current due to both intra-die and inter-die gate length process variability. We derive an analytical expression to estimate the probability density function (PDF) of the leakage current for stacked devices found in CMOS gates. These distributions of individual gate leakage currents are then combined to obtain the mean and variance of the leakage current for an entire circuit. We also present an approach to account for both the inter- and intra-die gate length variations to ensure that the circuit leakage PDF correctly models both types of variation. The proposed methods were implemented and tested on a number of benchmark circuits. Comparison to Monte-Carlo simulation validates the accuracy of the proposed method and demonstrates the efficiency of the proposed analysis method. Comparison with traditional deterministic leakage current analysis demonstrates the need for statistical methods for leakage current analysis.

## **Categories & Subject Descriptors:**

C.4 [Performance of Systems] - modeling techniques

General Terms: Reliability, experimentation

**Keywords:** Leakage current, Monte Carlo, variability

## 1 Introduction

The prominence of leakage currents in modern integrated circuits (ICs) has been spurred by the continued scaling of both supply voltage ( $V_{dd}$ ) and threshold voltage ( $V_{th}$ ). The exponential relationship between  $V_{th}$  and leakage current ( $I_{off}$ ) is central to this problem since  $V_{th}$  must be reduced to maintain good device switching speeds at low supply voltages [1]. With the proliferation of portable applications that spend significant time in standby mode, large  $I_{off}$  values become a critical roadblock to improved battery lifetimes. For example, static power is estimated to account for 15-20% of the total power budget in high-performance ICs at the 130nm technology node [2] and a number of methods for leakage reduction have been proposed for standby mode and during run time [3-8].

In addition to the rapid growth of  $I_{off}$  with each technology generation due to its exponential dependency on  $V_{th}$ , the potential also exists for large fluctuations of  $I_{off}$  from die to die or even gate to gate within a die. This is particularly true since controlling  $V_{th}$  is made more difficult in nanometer scale MOSFETs by drain-induced barrier lowering (DIBL) and discrete dopant effects [9]. While DIBL has been a problem since channel lengths first reached submicron

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

ISLPED '03, August 25–27, 2003, Seoul, Korea. Copyright 2003 ACM 1-58113-682-X/03/0008...\$5.00.

dimensions, it is exacerbated in sub-100nm devices by fundamental scaling limitations on oxide thickness ( $T_{ox}$ ).

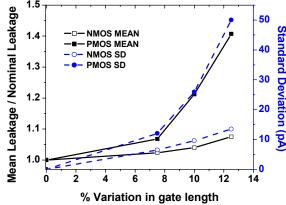

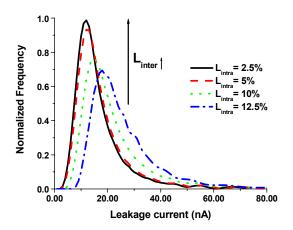

With the growing uncertainty in threshold voltage, estimation of  $I_{off}$  for a device becomes difficult, making the use of traditional delay-oriented corner models for leakage analysis impractical [10]. Worst-case model files can easily exhibit 10-100X larger  $I_{off}$  than a nominal device, which leads to excessive guardbanding and overly conservative design practices. However, ignoring  $I_{\it off}$  variability altogether is also not an option: Consider a circuit block in which a small number of very leaky devices easily dominate the total static power consumption. Figure 1 shows that the average leakage can be much larger (~30% for PMOS with L  $3\sigma$ = 12.5%) than the nominal leakage due to the exponential dependence of current on the gate length. This observation also invalidates the use of nominal device model files for even typical dies. The results also show that the degradation of PMOS leakage current with variations in the gate length is much worse than an NMOS counterpart with the same degree of gate length variation. This arises since DIBL effects in PMOS devices are typically worse than in NMOS devices [11].

The above discussion points towards the statistical modeling of leakage current as a key unexplored area in future high-performance IC design. Monte-Carlo simulations provide a method to analyze the effect of process variation, but are very expensive in terms of time complexity. An analytical approach to leakage current estimation is therefore needed to enable the prediction of leakage power in a design before it has been fabricated [12].

A statistical leakage analysis method was previously proposed in [13] for modeling the impact of gate length variations, gate oxide thickness variations, and doping fluctuations on leakage. The analysis, however, was limited to stacks of single transistors and the extension to multi-transistor stacks is not straightforward. Also, the inter- and intra-die component of process variation was not accounted for. In this paper, we therefore propose a new analytical approach for statistical leakage estimation that can be applied to general circuit topologies and accounts for both inter- and intra-die variations.

Figure 1. Dependence of mean and standard deviation of leakage current on 3 variation in gate length.

As found in [13], the variation in gate length has the strongest impact among the process parameters affecting the leakage current. Gate oxide thickness is extremely well controlled by modern processes and the effect of the channel doping on the leakage current is fairly small. Hence, in this paper we only consider variation of the gate length. The dependence of the gate oxide thickness and channel doping can be expressed in the same form as the dependence on drawn gate length, and hence the same approach can be adapted to include variability in these process parameters as well.

## 2 Analytical Approach to Leakage Variability

Our goal is to obtain an analytical model that allows efficient computation of the PDF of leakage currents for a circuit block or chip across the manufactured die. Using this model, we avoid the high computational costs of Monte Carlo based simulations that are impractical for analysis during the design process.

The objective is to find the PDF of the subthreshold leakage current I for a circuit block or chip, given the PDF of the drawn channel length L. We perform this task in three phases. First, we compute the leakage current distribution of individual gates in the circuit using the method described in Sections 2.1. Due to the exponential dependence of leakage current on gate length, the distribution of gate leakage for an individual gate has a lognormal shape. Secondly, based on the mean and variance of the leakage current distribution of individual gates, the total leakage of a circuit block is computed based on approximations for sums of lognormal distributions, as described in Section 2.2. In the third phase, the impact of inter-die gate length variation is accounted for using a discrete PDF of the inter-die component of gate length variation. As described in Section 2.3, the distribution of the leakage current due to intra-die variability is repeatedly computed, each time centered at a gate length that is shifted from the nominal value due to inter-die variation. We then take a weighted sum of this set of intra-die leakage distributions using numerical convolution to obtain the total leakage distribution accounting for both inter- and intra-die gate length variations. Since the number of discretizations of the inter-die gate length PDF is typically small, the runtime of the third phase of the analysis remains small.

## 2.1 Leakage Distribution of Individual Gates

We begin by describing our method for computing an analytical expression for the PDF of gate leakage of an individual gate. First, the dependence of I on L is characterized by the function h such that I = h(L). We then determine the inverse function g(I), that expresses L as a function of I:  $L = h^{-1}(I) = g(I)$ . In order to compute the PDF of the leakage, it is essential that: (1) the function g is a closed-form expression and (2) the function h is differentiable over the given range of currents. Unfortunately, the complexity of the relationship between leakage current and channel length (i.e., the function h(L)) does not allow for the derivation of g(I) such that it satisfies these two conditions. Therefore, as will be explained in Sections 2.1 and 2.2, we propose an approximate fit for the function h(L), such that the required inverse function can be computed while maintaining good accuracy.

Given the closed form expression of g(I) and the PDF of  $L = f_x(L)$ , we can express the PDF of I using the above expressions [14]:

$$PDF(I) = f_{y}(I) = \frac{f_{x}(g(I))}{h'(L)}$$

(1)

In our analysis, we assume that the drawn gate length has a

Gaussian distribution with a fixed mean  $\mu$  and standard deviation  $\sigma$ . Using these facts we can write the PDF of I as follows:

$$PDF(I) = f_y(I) = \left(\frac{1}{h'(L)}\right) \left(\frac{1}{\sigma\sqrt{2\pi}}\right) \exp\left(\frac{-(g(I) - \mu)^2}{2\sigma^2}\right)$$

(2)

Finally, to calculate the mean and standard deviation of the leakage current distribution of the gate, we perform numerical integration of  $f_v(I)$  over the given range of leakage currents.

$$E(I) = \sum_{I} I.f_{y}(I)$$

(3)

$$SD(I) = \sqrt{\left(\sum_{I} I^{2} f_{y}(I) - \left(\sum_{I} I f_{y}(I)\right)^{2}\right)}$$

(4)

Below, we explain the proposed method for computing  $f_y(I)$  in more detail for a single device. We initially discuss the approach for a single device and then extend the analysis for a stack of two or more transistors.

Single Transistor Stacks (Inverters)

Based on the BSIM3 device model, the subthreshold current through a device can be expressed as [15]

$$I = I_0 \exp((V_{gs} - V_{th}) / nV_T) (1 - \exp(-V_{ds} / V_T))$$

(5)

Here  $V_T=kT/q$  and  $I_0=\mu_0C_{ox}(W_{eff}/L_{eff})V_T^2\exp(1.8)$ . The term  $(1-\exp(-V_{ds}/V_T))$  can be neglected for an inverter since  $V_{ds}=V_{dd}$  is much greater than the thermal voltage  $V_T$ . We also set  $V_{gs}=0$  since the source nodes of either device in an inverter are tied directly to a supply rail and do not vary.  $V_{th}$  is the threshold voltage and is given by:

$$V_{th} = V_{fb} + |2\phi_P| + \frac{\lambda_b}{C_{ox}} \sqrt{2qN\varepsilon_S(|2\phi_P + V_{sb}|)} - \lambda_d V_{ds}$$

(6)

where  $\lambda_b$  is the body-effect factor and  $\lambda_d$  is the DIBL co-efficient. Expressions for  $\lambda_b$  and  $\lambda_d$  are given as in [15], [16].

$$\lambda_b = 1 - \left( \sqrt{1 + \frac{2W_{sd}}{X_j}} - 1 \right) \frac{X_j}{L_{eff}}$$

(7)

$$\lambda_d = \left[ \frac{L_{eff}}{2.2\mu m^{-2} (T_{ox} + 0.012\mu m)(W_{sd} + 0.15\mu m)(X_j + 2.9\mu m)} \right]^{-2.7}$$

(8)

These equations in principle enable us to calculate these parameters using the device model files for a given technology. However, analytical expressions for leakage current based on these parameters were found to fit very poorly for 0.18µm technologies. In particular, nebulous definitions for the values for technology constants such as  $N_{sub}$  and  $x_j$  produce large errors in the analytical current expressions. Further, Equation 7 and particularly Equation 8 are inadequate in modeling  $\lambda_b$  and  $\lambda_d$  [12] and produce unrealistically small values for these parameters resulting in large errors in the values for leakage current.

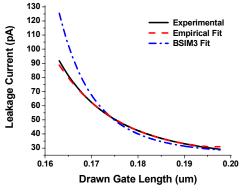

The actual BSIM3 model used to compute leakage current in SPICE simulations is much more complex than the simplified expressions presented in Equations 5–8. Additionally, the constraints placed on functions g and h necessitates the use of further simplifications to derive a suitable analytical expression for current in terms of drawn gate length. From Figure 2 we see that a simplified BSIM3 model vastly overestimates the leakage current for devices with gate lengths that deviate by more than 5% from the nominal value. Since these conditions correspond to the devices that contribute a large portion of leakage current, the resulting PDF

will be skewed to the right, rendering the BSIM3 fit unacceptable.

We therefore propose a new mathematical model to express leakage current *I* as a function of L.

$$I = q_1 \exp(q_2 L + q_3 L^2) = h(L)$$

(9)

This expression circumvents the use of  $V_{th}$  as an intermediate variable in expressing the current as a function of the gate length. However, it maintains the general form of the BSIM3 model and has the following properties:

- (1) It preserves the exponential dependency of I on L.

- (2) It is easily invertible (as shown below).

- (3) It yields closed form expressions for both I and L.

- (4) It accurately fits currents for both individual NMOS/PMOS as well as transistor stacks.

Figure 2 shows the comparison between the values for leakage current obtained from SPICE simulations and the values obtained from both the BSIM3 fit and our empirical fit for a single stacked device with 10% variation in gate length. From the plot we can see that the empirical model provides a better fit over a wide range of channel lengths.

Equation 9 is a simple exponential quadratic equation that can be inverted to obtain an analytical expression for *L* as follows:

$$L = \left(\frac{1}{2q_3}\right) \left(-q_2 + \sqrt{q_2^2 - 4q_3 \ln\left(\frac{q_1}{I}\right)}\right) = g(I)$$

(10)

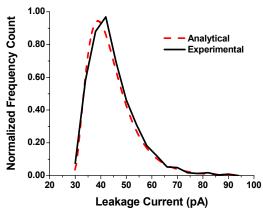

Using the expressions from Equations 2–4 with the functions g, h as specified by Equations 9–10, we can obtain the PDF of I. Figure 3 presents the comparison between the PDF obtained from SPICE simulations and the PDF obtained analytically for a single stacked device with 10%  $3\sigma$  variation in gate length. The plots of the PDFs, including the tail portion, match well and have a lognormal shape.

Figure 2. Comparison of the BSIM3 fit and analytical fit for h(L) with results from SPICE.

### Series-Connected Devices (Stacks)

In the case of a stack of transistors, the gate length variation impacts the leakage current of the bottom transistor in the stack in two ways: 1) Gate length variation of the bottom transistor directly modulates its threshold voltage. 2) Gate length variation of the top transistor indirectly affects the leakage of the bottom transistor by altering the voltage drop across the top transistors of the stack. Hence, the analytical expression of current as a function of gate length is more complex for stacks of multiple transistors. Since the devices in a stack are placed close together the layout, we make the

simplifying assumption that their gate length variations in are perfectly correlated. Also, we derive the analysis for stacks of two and three transistors, the method can be extended to stacks of arbitrary length in a straightforward manner.

In an inverter we ignored the term  $(1-\exp(-V_{ds}/V_T))$  in Equation 5 since the drain-source voltage  $V_{ds}$  in the leaking device is much greater than the thermal voltage  $V_T$ . For a device with stacked structures of two or three transistors, the value of the intermediate node voltage  $(V_{ds2})$  and  $V_{ds3}$  is much lower. In [17], the authors present a model to compute the drain-source voltage of transistors in stacks of arbitrary length. However, the complexity of these analytical expressions makes the derivation for a suitable equation for g (as in Equation 1) very difficult.

On the other hand, our empirical model is sufficiently robust to provide the leakage currents in these stacked circuits using the same general form of Equation 9. The current is once again empirically modeled as:

$$I = q_1 \exp(q_2 L + q_3 L^2) = h(L)$$

(11)

The constants  $q_1$ ',  $q_2$ ' and  $q_3$ ' are a new set of fitting parameters. Naturally, this set of constants will vary for different stack depths and also for NMOS vs. PMOS since the drain-source voltages will differ. Equation 10 is then solved again using the suitable coefficients in the quadratic expression to obtain the value of channel length as a function of I and similarly the PDF can be determined.

A simplifying assumption generally made is treating ON transistors in a stack as short circuits [17]. This is a reasonable assumption when the ON device is not the top device in an NMOS stack or the bottom device in a PMOS stack. In these cases the ON devices lead to  $V_{th}$  drops from the nominal voltages, leading to an overall lower leakage current. We consider this effect by estimating the leakage current under the assumption that the  $V_{th}$  drop is a constant value that corresponds to the nominal  $V_{th}$  of the device. This allows us to use the same models for stacks of transistors with an effectively reduced power supply voltage.

Figure 3. Comparison of the SPICE PDF with the analytical PDF found from Equation 2.

#### 2.2 Leakage Distribution of Circuit Blocks

In this section, we extend the approach developed to estimate the leakage current distribution for individual gate to the circuit level. Since the distribution of the leakage currents of a single gate is close to lognormal, we approximate the leakage current for the circuit as a whole as the sum of lognormals. Thus, to find the distribution of the total leakage current, given k lognormal random

variables (RVs) we need to find the distribution of the sum S given as:

$$S = X_1 + X_2 + \dots + X_k = e^{Y_1} + e^{Y_2} + \dots + e^{Y_k}$$

(12)

Sums of lognormals, assuming independence, can be well approximated by another lognormal RV [18]. Various approaches are known to estimate the parameters of the final lognormal. As shown in [18] a simpler Wilkinson approximation [19] is more accurate as compared to other complex approaches for our range of interest in the cumulative probability of leakage current. In Wilkinson's approach the sum of the mean and variance of the individual gate leakage current distributions,  $X_1, X_2, ..., X_k$  is matched with the first two moments of S:

$$E(S) = \mu_1 + \mu_2 + \mu_3 + \mu_4 + \dots$$

(13)

$$Var(S) = \sigma_1^2 + \sigma_2^2 + \sigma_3^2 + \sigma_4^2 + \dots$$

(14)

where the  $\mu$ 's and  $\sigma$ 's are the mean and standard deviation of the leakage currents of the individual gates. The PDF of a lognormal is given by,

$$f(x) = \left(\frac{1}{x\sqrt{2\pi}\beta}\right) \exp\left(\frac{-\left(\ln(x) - \alpha\right)^2}{2\beta^2}\right)$$

(15)

where  $\alpha$  and  $\beta$  are the parameters of the lognormal distribution. If  $Y(\mu,\sigma)$  is a Gaussian random variable then the corresponding lognormal X is related to Y as  $X=\exp(Y)$  and since the parameters of the lognormal are the mean and variance of the corresponding Gaussian distribution, we need to compute these based on the mean and variance of the lognormal:

$$E(X) = \exp(\alpha + \beta^2 / 2)$$

(16)  $Var(X) = \exp[2(\alpha + \beta^2)] - \exp(2\alpha + \beta^2)$

(17)

These values can be used to obtain the parameters of the Gaussian in terms of the mean and variance of the lognormal as given below:

$$\alpha = \left(\frac{1}{2}\right) \log \left(\frac{E^4(X)}{E^2(X) + Var(X)}\right)$$

(18)

$$\beta^2 = \log \left( \frac{Var(X) + E^2(X)}{E^2(X)} \right)$$

(19)

The parameters of the lognormal are then obtained using Equations 18 and 19, which completely determines the PDF of the leakage current of the circuit block. Note that for large circuit blocks the leakage current distribution will approach a Gaussian due to the Central Limit Theorem [14]. As shown in [20], both S (in Equation 12) as well as  $log\ S$  can be approximated by a Gaussian for large k. Thus, for large k, the lognormal distribution will tend towards the shape of a Gaussian distribution, and using a lognormal distribution to approximate sums of lognormals is justified.

## 2.3 Accounting for Inter- and Intra-Die Variations

Process variation can be classified into inter-die variation and intra-die variations. Intra-die variation refers to variation within a particular circuit block or chip. Inter-die variation occurs from one die to the next, meaning that the same device in the design has different features among different die. We consider the total drawn gate length of device i to be the algebraic sum of the nominal gate length  $L_{nominal}$ , the intra-die variation  $\Delta L_{intra}$  and the inter-die

variation  $\Delta L_{inter}$ . Consequently, the total variance is a sum of the inter- and intra-die variances.

$$L_{total\ i} = L_{nominal} + \Delta L_{inter} + \Delta L_{intra.i}$$

(20)

$$\sigma_{total}^2 = \sigma_{inter}^2 + \sigma_{intra}^2 \tag{21}$$

Note that in the above equation, the random variable  $\Delta L_{inter}$  is shared by all devices in a design (creating correlation between their leakage currents), where as the random variables  $\Delta L_{intra}$  assigned to each device are independent (reducing correlation of their leakage currents).  $\Delta L_{inter}$  can also be interpreted as the distribution of the chip-mean gate length, where as  $\Delta L_{intra}$  represents deviation in gate length of individual devices from this chip mean.

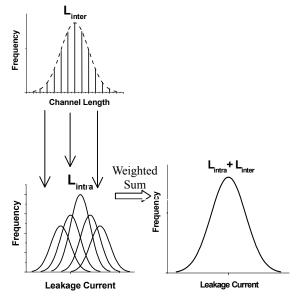

To compute the total leakage, accounting for both types of gate length variation, we first discretize the PDF of  $L_{inter}$  as shown in Figure 4(a). For each discrete point  $L_{inter,j}$  on the PDF of  $L_{inter}$ , we consider the intra-die variation of the channel length as a normally distributed PDF, whose mean is  $L_{inter,j}$  and standard deviation is  $\sigma_{intra}$ . Corresponding to this channel length, we obtain a PDF of the leakage current for the circuit using the approach outlined in the Sections 2.1 and 2.2.

Thus we obtain a family of the PDFs of leakage current as shown in Figure 4(b), where each PDF is associated with a conditional probability that corresponds to the PDF value of  $L_{inter,i}$  on the PDF of  $L_{inter,i}$ . To obtain the PDF of leakage current considering both variations we form a weighted sum of the family of PDF's. This can be expressed as:

$$P(I < i < I + \Delta I) = \sum_{i=1}^{n} P_{intra,j} (I < i < I + \Delta I) * P_{inter} (L_{inter,j})$$

(22)

where  $P_{inter}(L_{inter,j})$  is the probability of occurrence of  $j^{th}$  point from the set of 'n' discrete points selected.  $P_{intra}$  is calculated based on the lognormal distribution of the leakage current corresponding to the  $j^{th}$  point,  $L_{inter,j}$  on the  $L_{inter}$  PDF.

Figure 4. PDFs for (a) Channel length considering only  $L_{inter}$  (b) Leakage current corresponding to each point in (a) considering  $L_{intra}$  (c) Leakage current considering both  $L_{inter}$  and  $L_{intra}$

#### 3 Results

In this section we first compare the results obtained from the analytical approach outlined in the previous section and Monte Carlo simulations for individual gates and circuit blocks assuming only intra-die variation. We then present the comparison between SPICE simulations and our analytical approach for the ISCAS benchmark circuits considering both inter- and intra-die variation. We also show the difference between deterministic analysis and statistical analysis for various circuit blocks. In the analysis that follows we only compare the mean and variance of the two approaches.

Table 1 compares the analytical approach to Monte-Carlo simulations for a single gate. The drawn gate length is assumed to be normally distributed, with the  $3\sigma$  variation being 10% of the mean, the mean being 0.18µm. The table shows that the error in estimating the mean leakage current varies from 0-6% but is typically < 4%. The estimate in standard deviation shows higher error for one of the cases, but in all other cases it is small. The leakage current can be seen to drop significantly while going from a 1-stack to a 2-stack which is due to the well known "stack effect". The stack effect shows an even larger reduction for standard deviation when going from stacks of depth one to two. For the NMOS stacks, the mean reduces by a factor of 5 while the standard deviation reduces by a factor of 9.

Table 1. Comparison of the analytical approach with Monte-Carlo simulations for NMOS/PMOS stacks.

| 3σ Var = 10% |      |           |      |        |         |      |        |  |

|--------------|------|-----------|------|--------|---------|------|--------|--|

|              |      | Mean (pA) |      |        | SD (pA) |      |        |  |

|              |      | Exp       | Ana  | %Error | Exp     | Ana  | %Error |  |

| 1-Stack      | PMOS | 32.3      | 34.1 | 5.6    | 25.9    | 28.9 | 11.6   |  |

|              | NMOS | 44.1      | 44.4 | 0.7    | 9.6     | 10.0 | 4.2    |  |

| 2-Stack      | PMOS | 4.7       | 4.7  | 0.0    | 0.3     | 0.3  | 0.0    |  |

|              | NMOS | 9.1       | 9.1  | 0.4    | 1.0     | 1.0  | 3.1    |  |

| 3-Stack      | PMOS | 3.6       | 3.6  | 0.0    | 0.1     | 0.1  | 0.0    |  |

|              | NMOS | 5.8       | 6.0  | 3.1    | 0.6     | 0.6  | 3.4    |  |

Table 2 shows the results of the comparison of the analytical approach to Monte-Carlo simulation for nine ISCAS85 benchmark circuits [21]. The  $3\sigma$  variation in the drawn gate length is set at The experimental mean and standard deviation are calculated for a random set of input vectors for each circuit. The table shows that the average error in estimating the mean over all circuits is 3.5% with a maximum error of 8.3%. The average error in the standard deviation is 13.7% with a maximum error of 17.9%. In our experiments considering both inter and intra-die variation, we assume the total standard deviation to be equal to 15% of the mean. Table 3 compares the results of the analytical approach to Monte-Carlo simulation considering both intra- and inter-die variation. The table lists the data for the case where intra-die and inter-die process standard deviation have been assumed to be 10% and 11% of mean, respectively, which make up a total standard deviation of 15% based on Equation 21. As can be seen, the error in the estimated mean is always within 6.1% and that for the standard deviation within 21%.

We compare the new analytical approach to a traditional deterministic approach, where all gates lengths are assumed to be perfectly correlated and hence have the same length. Table 4 compares the median and the 95<sup>th</sup>/99<sup>th</sup> percentile points estimated using the traditional approach to the new statistical approach. As can be seen, the traditional approach significantly overestimates the

leakage for higher confidence points since all the devices are assumed to be operating at the pessimistic corner point. Since the relationship between the gate length and leakage current is monotonic, we find the median point as estimated by a traditional analysis to be very close to the nominal leakage current.

Table 2. Comparison of the analytical approach with Monte-Carlo simulations for a circuit considering only intra-die variation.

|         |                 | Mean (nA) |       |        | SD (pA) |        |        |

|---------|-----------------|-----------|-------|--------|---------|--------|--------|

| Circuit | Size<br>(Gates) | Exp       | Ana   | Err(%) | Exp     | Ana    | Err(%) |

| c17     | 6               | 0.2       | 0.3   | 8.3    | 36.0    | 37.0   | 2.8    |

| c432    | 159             | 7.1       | 7.2   | 1.4    | 190.0   | 210.0  | 10.5   |

| c499    | 519             | 19.0      | 20.0  | 5.3    | 280.0   | 330.0  | 17.9   |

| c880    | 364             | 17.0      | 17.0  | 0.0    | 280.0   | 330.0  | 17.9   |

| c1355   | 528             | 21.0      | 22.0  | 4.8    | 320.0   | 370.0  | 15.6   |

| c1908   | 432             | 16.0      | 17.0  | 6.3    | 260.0   | 300.0  | 15.4   |

| c2670   | 825             | 32.0      | 33.0  | 3.1    | 350.0   | 410.0  | 17.1   |

| c3540   | 940             | 39.0      | 40.0  | 2.6    | 420.0   | 480.0  | 14.3   |

| c6288   | 2470            | 120.0     | 120.0 | 0.0    | 900.0   | 1010.0 | 12.2   |

Table 3. Comparison of the analytical approach with Monte-Carlo simulations for a circuit considering both intraand inter-die variation.

| and inter-die variation. |       |           |        |         |       |        |  |

|--------------------------|-------|-----------|--------|---------|-------|--------|--|

| Circuit                  | M     | lean (nA) |        | SD (nA) |       |        |  |

|                          | Exp   | Ana       | Err(%) | Exp     | Ana   | Err(%) |  |

| c17                      | 0.4   | 0.4       | 0.0    | 0.5     | 0.4   | 20.0   |  |

| c432                     | 10.0  | 10.0      | 0.0    | 9.2     | 7.6   | 17.4   |  |

| c499                     | 28.0  | 27.0      | 3.6    | 24.1    | 19.5  | 19.1   |  |

| c880                     | 24.6  | 23.9      | 2.8    | 21.2    | 17.4  | 17.9   |  |

| c1355                    | 32.2  | 30.6      | 5.0    | 30.2    | 23.9  | 20.9   |  |

| c1908                    | 23.6  | 23.3      | 1.3    | 21.9    | 17.5  | 20.1   |  |

| c2670                    | 48.2  | 45.4      | 5.8    | 41.3    | 33.7  | 18.4   |  |

| c3540                    | 57.5  | 54.5      | 5.2    | 47.4    | 38.2  | 19.4   |  |

| c6288                    | 186.7 | 175.4     | 6.1    | 183.5   | 152.0 | 17.2   |  |

Table 4. Traditional analysis estimates the median values accurately but the higher percentiles are vastly overestimated.

|         | Leakage Current (nA) |       |        |                                           |              |              |  |  |

|---------|----------------------|-------|--------|-------------------------------------------|--------------|--------------|--|--|

| Circuit | Traditional Analysis |       |        | Statistical Analysis (Analytical) / Ratio |              |              |  |  |

|         | 50%                  | 95%   | 99%    | 50%                                       | 95%          | 99%          |  |  |

| c17     | 0.2                  | 0.8   | 2.1    | 0.2 / 1.0                                 | 0.3 / 2.67   | 0.5 / 4.2    |  |  |

| c432    | 6.7                  | 21.2  | 49.8   | 6.7 / .96                                 | 11.6 / 1.83  | 26.2 / 1.90  |  |  |

| c499    | 18.2                 | 57.2  | 134.6  | 19 / .96                                  | 34.3 / 1.67  | 78.5 / 1.71  |  |  |

| c880    | 16.1                 | 50.2  | 116.8  | 16.8 / .96                                | 34.1 / 1.47  | 77.4 / 1.51  |  |  |

| c1355   | 20.0                 | 67.0  | 162.7  | 20.7 / .97                                | 51.2 / 1.31  | 113.2 / 1.43 |  |  |

| c1908   | 15.5                 | 48.3  | 112.5  | 16.2 / .96                                | 37.8 / 1.28  | 80.4 / 1.40  |  |  |

| c2670   | 30.7                 | 96.9  | 227.3  | 31.3 / .98                                | 72.3 / 1.34  | 160.8 / 1.41 |  |  |

| c3540   | 37.3                 | 112.9 | 258.9  | 38.4 / .97                                | 86 / 1.31    | 179.7 / 1.44 |  |  |

| c6288   | 111.1                | 402.1 | 1010.0 | 115.2 / .96                               | 306.2 / 1.31 | 710.4 / 1.42 |  |  |

Figure 5. PDFs of leakage current for different contributions of inter and inter-die process variation. The total variation is 15%.

Figure 5 shows the impact of varying the distribution of inter-die process variation on the PDF of the leakage current while keeping the standard deviation of the total gate length  $\sigma_{total}$ =15% of the mean. The figure shows that when inter-die process variation is increased (and consequently the intra-die variation is decreased), the PDF tends to a lognormal shape. Note that for the case of no intra-die process variation, all gate lengths on a single die will be at their nominal values. Hence the PDF of this leakage current due to inter-die process variation alone should be similar to the PDF of the leakage current of a single gate which, as we know, can be closely approximated by a lognormal.

The figure suggests that, since leakage current is well characterized in terms of the  $I_{DDQ}$  values across die, the shape of this leakage current PDF can be a useful way to estimate the contribution of the inter-die or intra-die component to the total process variation.

## 4 Conclusions

In this work we have presented a method to estimate distributions of leakage current in the presence of both inter- and intra-die process variations. We developed a model to predict leakage currents as a function of drawn gate length and have shown it to be fairly accurate over the range of values of interest. We then developed a new approach to estimate leakage currents PDF's in circuit blocks considering both inter- and intra-die process variation. We compared this approach to Monte-Carlo simulations and have showed it to be accurate in estimating the overall mean and standard deviation of the leakage current in circuit blocks. We have shown that using the analytical approach we can significantly reduce the pessimism introduced by deterministic analysis while saving on the computational effort required for a Monte-Carlo analysis. We have also highlighted the difference in the impact of inter and intra-die process variation on the PDF of leakage current.

#### Acknowledgements

We would like to acknowledge the helpful discussions with Sani Nassif from IBM ARL, Austin, TX. This research was supported by NSF, MARCO/DARPA and SRC grants.

#### 5 References

- C. Hu, "Device and technology impact on low power electronics," *Low Power Design Methodologies*, ed. Jan Rabaey, Kluwer, pp. 21-35, 1996.

- [2] http://developer.intel.com/design/mobile/datashts

- [3] S. Sirichotiyakul, T. Edwards, C. Oh, J. Zuo, A. Dharchoudhury, R. Panda, and D. Blaauw, "Standby power minimization through simultaneous threshold voltage and circuit sizing," *Proc. DAC*, pp. 436-441, 1999.

- [4] Y. Ye, S. Borkar, and V. De, "A new technique for standby leakage reduction in high-performance circuits," *Proc.* Symposium on VLSI Circuits, pp. 40-41, 1998.

- [5] J. Halter and F. Najm, "A gate-level leakage power reduction method for ultra-low-power CMOS circuits," *Proc. CICC*, pp. 475-478, 1997.

- [6] S. Mutoh, T. Douseki, Y. Matsuya, T. Aoki, S. Shigematsu, and J. Yamada, "1-V power supply high-speed digital circuit technology with multithreshold voltage CMOS," *IEEE Journal of Solid-State Circuits*, vol. 30, pp. 847-854, Aug. 1995.

- [7] R.K. Krishnamurthy, A. Alvandpour, V. De, and S. Borkar, "High-performance and low-power challenges for sub-70nm microprocessor circuits," *Proc. CICC*, pp. 125-128, 2002.

- [8] P. Pant, V. De, and A. Chatterjee, "Device-circuit optimization for minimal energy and power consumption in CMOS random logic networks," *Proc. DAC*, pp. 403-408, 1997.

- [9] International Technology Roadmap for Semiconductors, 2001.

- [10] S. Narendra, V. De, S. Borkar, and A. Chandrakasan, "Full chip sub-threshold leakage power prediction model for sub-0.18um CMOS," *Proc. ISLPED*, pp.19-23, 2002.

- [11] S. Tyagi et al, "A 130nm generation logic technology featuring 70nm transistors, dual Vt transistors and 6 layers of Cu interconnect," *Proc. IEDM*, pp. 567-570, 2000.

- [12] J. Kao, S. Narendra, and A. Chandrakasan, "Subthreshold leakage modeling and reduction techniques," *Proc. ICCAD*, pp. 141-148, Nov. 2002.

- [13] A. Srivastava, R. Bai, D. Blaauw, and D. Sylvester, "Modeling and analysis of leakage power considering within-die process variations," *Proc. ISLPED*, pp. 64-67, 2002.

- [14] A. Papoulis, Probability, Random Variables, and Stochastic Processes, McGraw-Hill Inc, New York, 1991.

- [15] A. Chandrakasan, W.J. Bowhill, and F. Fox, Design of high-performance microprocessor circuits, IEEE Press, 2001.

- [16] K.K. Ng, S.A. Eshraghi, and T.D. Stanik, "An improved generalized guide for MOSFET scaling," *IEEE TED*, vol.40, pp. 1893-1895, 1993.

- [17] Z. Chen, M. Johnson, L. Wei, and K. Roy, "Estimation of standby leakage power in CMOS circuits considering accurate modeling of transistor stacks," *Proc. ISLPED*, pp. 239-244, 1998.

- [18] N.C. Beaulieu, A.A. Abu-Dayya, and, P.J.McLane. "Comparison of methods of computing lognormal sum distributions and outages for digital wireless applications," *IEEE International Conference on Communications*, vol.3 pp.1270-1275,1994.

- [19] S.C. Schwartz and Y.S. Yeh, "On the distribution function and moments of power sums with lognormal components," *Bell Systems Technical Journal*, vol.61, pp.1441-1462, Sept. 1982.

- [20] N. Marlow, "A normal limit theorem for power sums of independent random variables," *Bell Systems Technical Journal*, vol.46, pp.2081-2090, Nov. 1967.

- [21] F. Brglez and H. Fujiwara, "A neutral netlist of 10 combinational benchmark circuits and a target translator in Fortran," *Proc. International Symposium on Circuits and Systems*, pp. 695-698, May 1989.