Foundations and Trends<sup>®</sup> in Electronic Design Automation Vol. 1, No. 4 (2006) 331–480 © 2007 X. Li, J. Le and L. T. Pileggi DOI: 10.1561/100000008

### Statistical Performance Modeling and Optimization

## Xin Li<sup>1</sup>, Jiayong Le<sup>2</sup> and Lawrence T. Pileggi<sup>3</sup>

- <sup>1</sup> Department of ECE, Carnegie Mellon University, Pittsburgh, PA 15213, USA, xinli@ece.cmu.edu

- <sup>2</sup> Extreme DA, 165 University Avenue, Palo Alto, CA 94301, USA, kelvin@extreme-da.com

- <sup>3</sup> Department of ECE, Carnegie Mellon University, Pittsburgh, PA 15213, USA, pileggi@ece.cmu.edu

#### Abstract

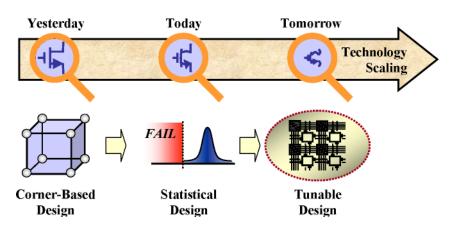

As IC technologies scale to finer feature sizes, it becomes increasingly difficult to control the relative process variations. The increasing fluctuations in manufacturing processes have introduced unavoidable and significant uncertainty in circuit performance; hence ensuring manufacturability has been identified as one of the top priorities of today's IC design problems. In this paper, we review various statistical methodologies that have been recently developed to model, analyze, and optimize performance variations at both transistor level and system level. The following topics will be discussed in detail: sources of process variations, variation characterization and modeling, Monte Carlo analysis, response surface modeling, statistical timing and leakage analysis, probability distribution extraction, parametric yield estimation and robust IC optimization. These techniques provide the necessary CAD infrastructure that facilitates the bold move from deterministic, corner-based IC design toward statistical and probabilistic design.

# 1 Introduction

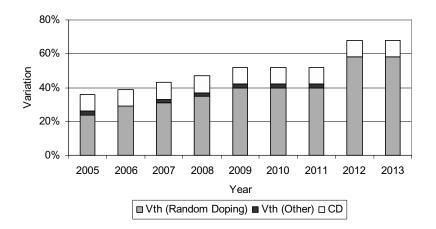

As integrated circuit (IC) technologies continue shrinking to nanoscale, there is increasing uncertainty in manufacturing process which makes it continually more challenging to create a reliable, robust design that will work properly under all manufacturing fluctuations. Large-scale process variations have already become critical and can significantly impact circuit performance even for today's technologies [14, 72, 73, 100]. Figure 1.1 shows the relative process variations ( $3\sigma$ /mean) predicted by the International Technology Roadmap for Semiconductors (ITRS) [100]. These large-scale variations introduce numerous uncertainties in circuit behavior and make it more difficult than ever to achieve a robust IC design.

In addition, when we consider some of the promising new device structures (e.g., carbon nano-tube [8, 34], FinFET [20], etc.) that have been recently proposed to maintain the aggressive pace of IC technology scaling, it is apparent that applying them to high-volume production will be a challenging problem due to the manufacturing uncertainty, or even their likelihood of failure. While it has already become extremely difficult to reliably manufacture nano-scale devices and achieve high product *yield* (defined as the proportion of the manufactured chips

Fig. 1.1 Relative process variations  $(3\sigma/\text{mean})$  predicted by [100].

that function correctly) with today's technologies, it would be almost impossible to do so affordably with tomorrow's technologies using existing deterministic design methodologies. For this reason, a paradigm shift in IC design is required to simultaneously improve circuit performance and product yield when using manufacturing technologies that present significant uncertainty.

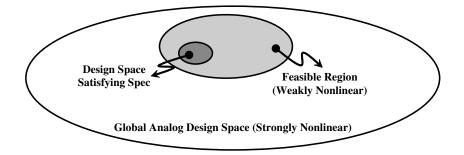

The yield loss in a manufacturing process can be classified into two broad categories: *catastrophic* (due to physical and structural defects, e.g., open, short, etc.) and *parametric* (due to parametric variations in process parameters, e.g.,  $V_{\rm TH}$ ,  $T_{\rm OX}$ , etc.). As process variations become relatively large due to technology scaling, parametric yield loss is becoming increasingly significant at 90 nm technologies and beyond. Therefore, we focus on the parametric yield problem in this paper. We will review a number of recently-developed techniques that handle large-scale process variations at both transistor and system levels to facilitate affordable statistical integrated circuit design. Especially, we will focus on the following two questions:

• When should process variations be considered? Ideally, we want to take into account process variations in the earliest design stage. However, this strategy may not be necessary and/or efficient in practice. During early-stage system-level

#### 334 Introduction

design, many simplified models must be used to make the large-scale design problem tractable. The errors of these system-level models may be comparable to, or even larger than, the uncertainties caused by process variations. In such cases, it is not meaningful to model and analyze process variations at system level. As the design moves from system level down to circuit level, more accurate circuit-level models become available. We should start to consider process variations at the stage where circuit models are sufficiently accurate and process variations become the dominant uncertainties that impact performance.

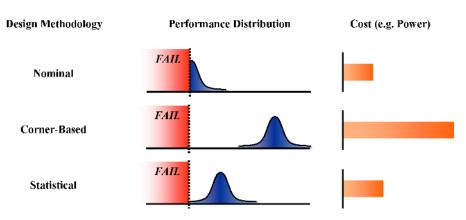

• *How should process variations be considered?* For example, the simplest way to model process variations is to define a number of process corners. That is, every process parameter is assigned with a lower bound and an upper bound, and the best-case and worst-case circuit performances are computed by enumerating all possible combinations of the extreme values of process parameters. The aforementioned corner model is simple; however, such a corner-based approach may result in large error, since it completely ignores the correlation among different process parameters. In addition, it is not guaranteed that the best/worst-case performance always occurs at one of these corners. An alternative approach to model process variations is to use statistical device models where process parameters are modeled as random variables. (More details on statistical device models can be found in Chapter 2.) The statistical device model is much more accurate, but also expensive, than the traditional corner model.

One of the major objectives of this paper is to review and compare different statistical IC analysis and optimization techniques, and analyze their trade-offs for practical industrial applications. The following topics will be covered in this paper:

• Sources of process variations and their models. We will briefly review both front-end of line (FEOL) variations and back-end of line (BEOL) variations in Chapter 2. Several

techniques for variation characterization and modeling will be presented for both device-level and chip-level applications.

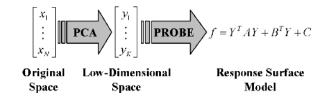

- Transistor-level statistical methodologies. In Chapter 3, we will discuss and compare a number of transistorlevel statistical modeling, analysis and optimization techniques. In particular, the following topics will be covered: Monte Carlo analysis, response surface modeling, probability distribution extraction, parametric yield estimation, and robust transistor-level optimization. Several recentlydeveloped methodologies, including projection-based performance modeling (PROBE) and asymptotic probability extraction (APEX), will be described in detail.

- System-level statistical methodologies. Most system-level statistical analysis and optimization techniques utilize a hierarchical flow to partition the entire system into multiple small blocks such that the large-size problem becomes tractable. In Chapter 4, we will discuss a number of system-level statistical methodologies that have been recently proposed. In particular, we will focus on the statistical timing and leakage problems for large-scale digital systems.

Finally, we will conclude and propose several possible areas for future research in Chapter 5.

## 2

## **Process Variations**

Process variations are the deviations from the intended or designed values for the structural or electrical parameters of concern. In this paper, we focus on the *parametric variations* due to the continuously varying structural or electrical parameters. For modern semiconductor manufacturing processes, transistors and other active devices are first fabricated on top of semiconductor substrate. After that, metal layers are deposited to connect transistors and supply power. Based on the manufacturing steps, parametric variations can be classified into two broad categories: front-end of line (FEOL) variations for devices and back-end of line (BEOL) variations for interconnects. In this chapter, we briefly review the sources of these variations and their models.

#### 2.1 Front-End of Line (FEOL) Variations

FEOL variations mainly refer to the variations at device level. The major sources of FOEL variations consist of transistor gate length and gate width variations, gate oxide thickness variations, doping-related variations, etc. After transistors are fabricated, these variations can be observed by measuring the corresponding device characteristics, including drain-source current  $(I_{\rm DS})$ , threshold voltage  $(V_{\rm TH})$ , gate leakage current  $(I_{\rm Gate})$ , etc. For example, poly critical dimension (CD) variations can change  $I_{\rm DS}$ , and gate oxide thickness variations and doping-related variations can change  $V_{\rm TH}$ .

In nano-scale IC technologies, transistor gate length, or poly critical dimension, can significantly vary due to its small feature size. The sources of CD variations typically include exposure system variations, mask errors, and resist effects. Exposure system variations may have optical, mechanical or illuminative explanations [108]. Optical performance (e.g., flare) can introduce non-uniform exposure dose. Mechanical performance (e.g., vibrations during reticle scanning and/or wafer scanning) can cause focus variations. Illumination performance is mainly related to the polarization control of the laser.

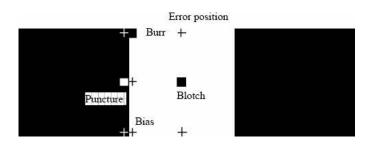

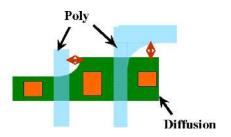

As shown in Figure 2.1, mask errors can be puncture, burr, blotch, mask bias, etc. [118] Since mask errors affect all the dies within the same mask, the variations caused by mask errors are systematic. Furthermore, regions within a design with relatively low aerial-image contrast will be subject to larger amplification of mask errors.

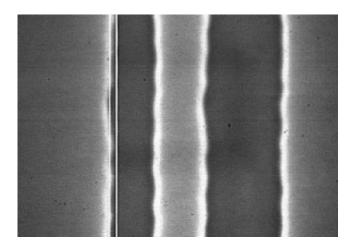

Resist effects result in line edge roughness (LER) [7], as shown in Figure 2.2. LER has caused little worry in the past since the critical dimensions of MOSFETs were orders of magnitude larger than the roughness. However, as the aggressive technology scaling moves into nanometer regime, LER does not scale accordingly and becomes an increasingly large fraction of the gate length.

Along with gate length, gate width also shows substantial variations. Since many transistors in a practical design typically have much

Fig. 2.1 Examples of mask error (showing puncture, burr, blotch, and mask bias).

Fig. 2.2 A typical LER effect on poly.

bigger gate widths than their gate lengths, gate width variations are not as dominant as gate length variations. However, for minimal-width transistors, gate width variations can significantly impact transistor performance.

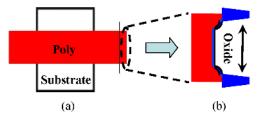

Part of the transistor gate width variations comes from shallow trench isolation (STI) polish [35]. STI is a method used for electrical isolation of microstructures during IC manufacturing. It is a replacement of the old Local Oxidation of Silicon (LOCOS) for technologies beyond  $0.35\,\mu$ m. STI uses a nitride mask to protect transistor regions and expose isolation regions. It etches trenches into a wafer, and then fills the trenches with oxide. Afterwards, it uses chemical mechanical polishing (CMP) to polish away any excess oxide. During the etching and filling step, some parts of the device area might be consumed (as shown in Figure 2.3) and, therefore, the effective width of the poly becomes smaller. This effect is especially significant for narrow-width transistors.

Another source of gate width variations is from the rounding effect due to patterning limitations, as shown in Figure 2.4. Rounding affects both transistor gate length and gate width. In Figure 2.4, the effective gate width for the left-most transistor is increased by the rounding

Fig. 2.3 Top view of shallow trench isolation. (a) Top view of the drawn poly. (b) Right edge of the ploy where part of its area is consumed by the etching and filling step.

Fig. 2.4 Example of rounding effect.

effect at diffusion. Meanwhile, the effective gate length is increased by the rounding effect at poly for the right-most transistor. To mitigate the problem, strict design rules must be applied so that the rounding effect can be minimized.

Threshold voltage is another important device parameter that exhibits significant variations. Threshold voltage variations consist of two major components: (1) die-to-die variations and (2) random withindie variations. The die-to-die variations mainly come from waferlevel non-uniformity (e.g., non-uniform temperature distribution during thermal oxidation). On the other hand, the random within-die variations are mainly caused by random channel dopant fluctuations and poly dopant fluctuations. In today's leading-edge manufacturing technologies, there are only about 500 dopant atoms in one MOSFET channel. The fluctuation of the number of dopant atoms affects the threshold voltage of each device independently, and the resulting threshold voltage variation can be approximated as a zero-mean Normal distribution whose standard deviation is inversely proportional to the square root

of the effective gate width and the effective gate length [65, 84, 111]:

$$\sigma\left(\Delta V_{\rm TH}^{\rm Random}\right) \sim \frac{1}{\sqrt{W_{\rm Eff} \cdot L_{\rm Eff}}},$$

(2.1)

where  $W_{\text{Eff}}$  and  $L_{\text{Eff}}$  are the effective gate width and length, respectively.

#### 2.2 Back-End of Line (BEOL) Variations

BEOL variations refer to the variations of metal interconnects. For example, metal width, metal thickness, and inter layer dielectric can have both systematic and random variations. Subsequently, the electrical parameters of interconnects including both resistance and capacitance exhibit corresponding variability.

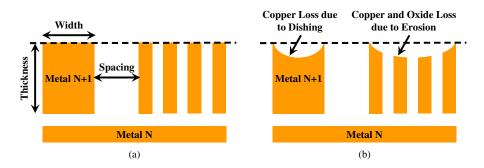

At 90 nm technology node, metal thickness variations can be up to  $30\%\sim40\%$  of the nominal thickness. Such large-scale variations can significantly impact the resistance and capacitance of a wire and lead to severe timing and/or signal integrity issues. Metal thickness variations depend on wire width and metal density, and have short range interactions [82]. Thickness variations are influenced by process maturity, location of the metal layer in process stack and other process operating conditions. One important source of metal thickness variations is the copper loss during chemical mechanical polishing (CMP). Such copper loss is a function of metal pattern density (erosion) and metal width (dishing) as shown in Figure 2.5.

Fig. 2.5 Metal thickness variations due to chemical mechanical polishing. (a) Ideal case after copper CMP. (b) Realistic case after copper CMP.

#### 2.2 Back-End of Line (BEOL) Variations 341

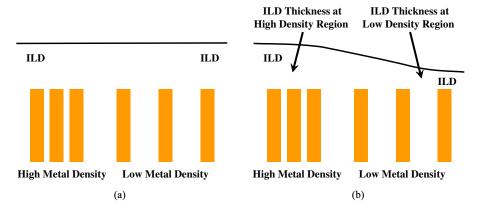

Fig. 2.6 ILD thickness variations due to chemical mechanical polishing. (a) ILD thickness after oxide deposition but before oxide CMP. (b) ILD thickness after oxide CMP.

In addition to metal thickness, inter-layer dielectric (ILD) thickness is another important process parameter that varies significantly in nano-scale technologies. ILD is the dielectric that separates two adjacent metal layers and it strongly impacts the parasitic capacitance of metal interconnects. ILD thickness variations come from the fluctuations of the oxide CMP polishing rate that are influenced by the lower-layer metal density [110]. It can be modeled as a function of the underlying metal pattern density and the pad planarization length, as shown in Figure 2.6.

The third major component of BEOL variations is the metal width/spacing variation. Metal width/spacing variations are primarily due to lithography effects. The width variation of a critical wire segment (also known as selective process biasing) is primarily determined by the metal width and the spacing to its neighbors. Process engineers typically measure width variations in silicon and create a two-dimensional table to model width variations as a function of metal width and spacing. This table is typically incorporated into the process-technology file that can be further used by the capacitanceand-resistance extraction engine to account for the effect of width variations.

#### 2.3 Variation Characterization

Modern IC manufacturing typically involves hundreds of, or even thousands of, steps, and, therefore, the true causes of manufacturing variations are highly complicated. For example, they can be caused by fluctuations in equipment conditions, fluctuations in wafers, consumable material characteristics, layout and topography interactions with the process, and their combinations. Generally, process variations manifest themselves in both temporal and spatial manner. In this chapter, we classify process variations into different categories based on their statistical or geometrical properties. We also briefly describe the test structures for variation characterization. Due to the difference in their underlying nature, variations in different categories typically require different test structures to characterize them.

#### 2.3.1 Statistical Categorization

From statistical point of view, process variations can be classified into two broad categories: *systematic variations* and *random variations*. Systematic variations refer to the variation components that can be attributed to a specific deterministic cause. It is usually dependent on the component position in the die and its surrounding properties such as metal density. For example, gate length and width variations contain systematic components that mainly come from the fluctuations of focus and exposure of the lithography system for different layout patterns. Part of metal thickness variations is caused by CMP and, therefore, is systematic.

Systematic variations are deterministic and can be predicted by process simulations (e.g., lithograph simulation). However, accurately predicting systematic variations may not be feasible for many practical designs because of the following two reasons. First, accurate process simulations can be extremely expensive and may not be applicable to large-size circuits. Second, a lot of design information may not be available at the earlier design stages, further limiting the accuracy of process simulation. For example, placement and routing information is not available at schematic design phase and, therefore, it is difficult to predict systematic variations for schematic design. From this point of view, systematic variations can be viewed as the repeatable but unpredictable modeling error due to the lack of computational resource and/or design information.

On the other hand, random variations refer to the variation components that correspond to unrepeatable uncertainties due to insufficient process control and intrinsic fluctuations. An important example here is the threshold voltage variation caused by doping fluctuation. In modern IC technologies, there are only about a few hundred dopant atoms in one MOSFET channel. It would be extremely difficult, if not impossible, to precisely count the dopant atoms during manufacturing. Therefore, the fluctuations of the number of dopant atoms introduce random threshold voltage variations for MOSFETs.

As IC technologies are scaled to smaller feature sizes in the future, both systematic and random variations may further increase. To reduce systematic variations, IC designers start to utilize restricted layout patterns for both digital circuits [48, 86] and analog circuits [121, 123]. Random mismatches, however, can hardly be controlled by circuit layout. As feature sizes become smaller and each transistor contains fewer atoms in its gate channel, random mismatches are expected to become the dominant variation component in 65 nm technologies and beyond.

#### 2.3.2 Geometrical Categorization

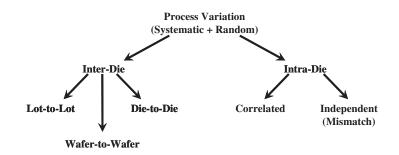

According to the spatial scale of their manifestation, process variations can be classified into four different levels: lot-to-lot, wafer-to-wafer (within-lot), die-to-die (within-wafer), and within-die [109]. The first three variations are also called the *inter-die variations*: they model the common/average variations across the die. The within-die variations are also called the *intra-die variations* or *on-chip variations*: they model the individual, but spatially correlated, local variations within the same die. Intra-die variations further consist of two different components: correlated variations and *independent mismatches*. The spatial correlation of intra-die variations is distance-dependent. Such a spatial correlation occurs mainly because systematic variations are modeled as random variables [109]. Figure 2.7 summarizes the geometrical categorization of process variations.

Fig. 2.7 Categorization of process variations according to geometrical scale.

#### 2.3.3 Test Structures for Variation Characterization

Device parameters (e.g., gate length, gate width, etc.) can be directly measured from the chip. However, such measurement is typically expensive and sometimes even impossible. To avoid directly physical/mechanical measurement, various test structures are designed for process characterization. These test structures can translate the device parameters of interest to a set of electrical characteristics (e.g., ring oscillator frequency, I–V curve) that are easy to measure.

Ring oscillator is an important test structure that has been widely used to characterize inter-die variations and long-range correlated intradie variations [11, 77, 79, 80]. The performance of interest of a ring oscillator is its oscillation frequency. The digital output of a ring oscillator can be easily delivered out of chip and its frequency can be accurately measured without any distortion. For this reason, ring oscillators can be easily distributed at both wafer level and die level. The frequency information of different ring oscillators is then collected to extract the spatial map of process variations.

Most ring oscillators, however, are not sensitive to random mismatches, since the random per-transistor variations can be averaged out when cascading a large number of inverter blocks to create a ring oscillator. Recently, transistor array has been proposed as a promising approach for mismatch characterization [75]. The basic idea here is to have a great number of regular transistors and measure the I–V curve for each of them. A major design challenge for transistor array is to build high-performance analog circuit to accurately deliver analog voltage and current signals out of chip for measurement through a limited number of I/O pins.

#### 2.4 Variation Modeling

To facilitate statistical analysis and optimization of integrated circuits, variation models must be carefully created to abstract and approximate the physical phenomenon during IC manufacturing. The accuracy of these models directly impact the quality of the final statistical analysis and optimization results at chip level. In this chapter, we briefly review the statistical models at both device level and chip level. We do not explicitly distinguish systematic and random variations and statistically model both of them as random variables. It should be noted, however, that systematic variations are not truly random. They are modeled statistically, because accurately predicting their exact values is not feasible due to the lack of computational resource and/or design information.

#### 2.4.1 Device-Level Variation Modeling

Commercial IC foundries started to incorporate manufacturing variation information into their device models long time ago. The early variation-aware device models are mostly corner-based. Namely, in addition to offering device models for nominal process conditions, additional models are provided for a number of process corners. Basic process corners, for example, include FF (fast PMOS and fast NMOS), FS (fast PMOS and slow NMOS), SF (slow PMOS and fast NMOS), and SS (slow PMOS and slow NMOS).

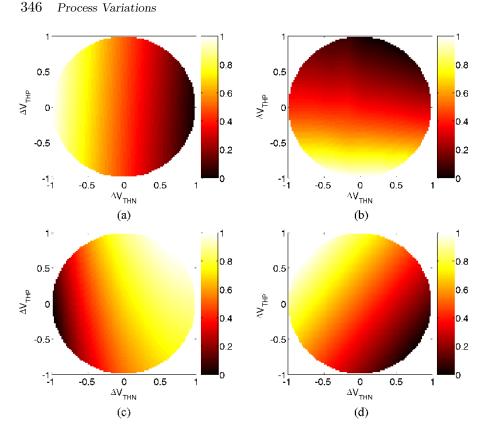

While corner models have been widely used in the past, they suffer from a few major limitations that become increasingly critical in nanoscale technologies [71]. First, it is not guaranteed that the worst-case performance always occurs at one of these corners. Different circuits with different topologies and performance metrics typically show different sensitivities with respect to process variations and, therefore, reach the worst case at different process corners. In other words, the "realistic" worst-case corner should be topology-dependent and performancedependent. Figure 2.8 shows the relative performance variations for an

Fig. 2.8 Performance variations (normalized to [0, 1]) of an industrial voltage-controlled oscillator design in a commercial  $0.13 \,\mu$ m CMOS process. (a) Center frequency. (b) Gain. (c) Output voltage swing. (d) Power.

industrial voltage-controlled oscillator design in a commercial  $0.13 \,\mu$ m CMOS process. The color maps in Figure 2.8 indicate the performance sensitivities with respect to inter-die  $V_{\text{THP}}$  (threshold voltage of PMOS) and  $V_{\text{THN}}$  (threshold voltage of NMOS) variations. Studying Figure 2.8, one would notice that the performance gradients are completely different for the four performance metrics of interest.

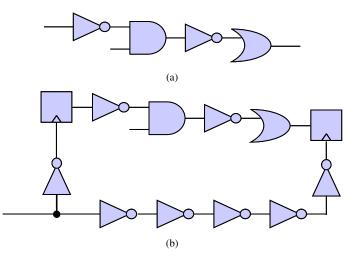

Second, corner models are typically created for inter-die variations only. Ignoring intra-die variations can result in either pessimistic or erroneous results, depending on the circuit topology and performance metric of interest. Figure 2.9(a) shows a simple digital path that consists of several logic gates. Corner models assume that all gate delays in this path are fully correlated and they reach the worst case

Fig. 2.9 Ignoring intra-die variations can result in either pessimistic or erroneous results. (a) A simple digital path (pessimistic results). (b) A simple sequential digital circuit with D flip-flops (erroneous results).

simultaneously, thereby yielding pessimistic results. Such pessimistic results may lead to unnecessary over-design which implies large chip area and/or high power consumption for digital circuits.

While Figure 2.9(a) gives an example of pessimism, Figure 2.9(b) shows another practical case where corner models yield erroneous results if they are not correctly used. In this example, the clock path delay  $(D_{\text{CLK}})$  must be greater than the data path delay  $(D_{\text{DATA}})$  to avoid setup timing failure. Since  $D_{\text{CLK}}$  and  $D_{\text{DATA}}$  are not fully correlated due to intra-die variations, simulating both  $D_{\text{CLK}}$  and  $D_{\text{DATA}}$  at the same corner (e.g., FF or SS) incorrectly assumes that  $D_{\text{CLK}}$  and  $D_{\text{DATA}}$  perfectly track each other (i.e., simultaneously increase or decrease), thereby yielding erroneous results. In this example, the true worst case occurs when the clock path is fast and the data path is slow.

In addition to the digital circuit examples in Figure 2.9, intra-die variations are even more important for analog circuits. Many basic analog building blocks (e.g., differential pair, current mirror, switchedcapacitor amplifier, etc.) rely on device matching to achieve the correct analog functionality. In other words, these circuits are designed to be robust to inter-die variations, but they are extremely sensitive to

intra-die variations (particularly, device mismatches). In these cases, intra-die variations must be carefully considered for worst-case performance analysis.

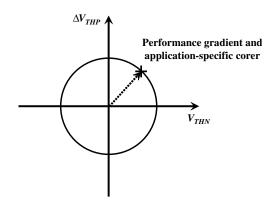

There have been various ways to improve corner models, e.g., replacing manufacturer-defined corners by application-specific corners [101] (also called user-defined corners). The basic idea here is to look at the performance change with respect to process variations to determine the specific location in the random variation space that yields the worstcase performance value, as shown in Figure 2.10. In this case, intra-die variations can also be incorporated to determine the worst-case corner. Considering intra-die variations for corner extraction, however, will increase the problem complexity, as additional random variables must be utilized to model intra-die variations, thereby resulting in a higher-dimensional variation space.

Given a fixed circuit topology and a number of pre-defined performance metrics, the aforementioned application-specific corners are not fixed; instead, they depend on the design variable values of the circuit (e.g., transistor sizes, bias current, etc.). In practice, a great number of corners may be required to capture the worst-case performance over a reasonable range of design variable values. For example, it is not uncommon to end up with more than 1000 application-specific corners for an industrial mixed-signal design in 65 nm technologies. Such

Fig. 2.10 Extract application-specific worst-case corner based on performance gradient.

```

vary \varepsilon_1 dist = gauss std = 1

vary \varepsilon_2 dist = gauss std = 1

model NMOS b~4

+ type = n

+ tox = 4e-9 + 1e-10*\varepsilon_1 - 1.3e-10*\varepsilon_2 + ...

+ vth0 = 0.6 + 0.24*\varepsilon_1 + 0.3*\varepsilon_2 + ...

+ ...

```

Fig. 2.11 A simple example of statistical device model where  $\varepsilon_1$  and  $\varepsilon_2$  are used to model inter-die variations.

a large number of corners can result in expensive simulation cost during verification.

To address the fundamental limitations of corner models, many commercial IC foundries start to provide statistical device models [104]. In these models, a number of random variables are defined to capture both inter-die and intra-die variations and the device model parameters are represented as functions of these random variables. Taking Figure 2.11 as an example, two independent random variables  $\varepsilon_1$  and  $\varepsilon_2$  are extracted by principal component analysis (more details in Section 2.4.3) to model the correlated inter-die variations of  $T_{\text{OX}}$  and  $V_{\text{TH}}$ . It should be noted that an industrial statistical device model can be much more complicated than the simple example in Figure 2.11, as a great number of pre-defined random variables must be utilized to capture all process variations with spatial correlation.

#### 2.4.2 Chip-Level Correlation Modeling

As shown in Figure 2.7, process variations consist of three major components: inter-die variations, on-chip long-range correlated variations, and independent device mismatches. Good statistical device models should accurately capture all these three components. At chip level, the long-range correlated variations are most difficult to model. The challenging problem here is how to use the silicon data measured by test structures to accurately extract the spatial correlation for the entire chip that consists of millions of transistors. To solve this problem, the following two questions must be properly addressed: (1) What is the

correct correlation function that is distance-dependent? (2) How can we efficiently and robustly handle the large problem size?

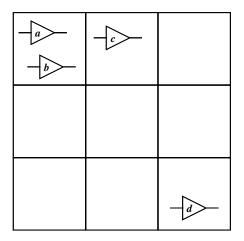

One useful approach for modeling correlated intra-die variations is to partition the entire die into a number of grids [18], as shown in Figure 2.12. The intra-die variations in the same grid are fully correlated, while those in close (far-away) grids are strongly (weakly) correlated. Taking Figure 2.12 as an example, the gates a and b are in the same grid and, therefore, their process parameters are fully correlated. The gates a and c lie in two neighboring grids and their process parameters are strongly correlated. The gates a and d sit far away from each other and their process parameters are weekly correlated.

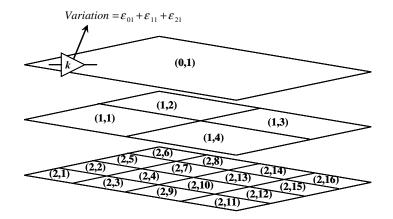

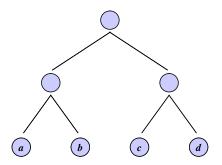

The authors in [2] proposed another hierarchical approach for modeling correlated intra-die variations. The key idea is to hierarchically divide the entire chip into a number of regions using a multi-level quadtree partition, as shown in Figure 2.13. At each level *i*, the die area is partitioned into  $2^i$  by  $2^i$  rectangles. The 0th level, for example, contains one rectangle only that covers the entire chip. An independent random variable  $\varepsilon_{ij}$  is assigned to each region (i, j) to model a portion of the total intra-die variations. The overall variation of a gate *k* is expressed as the sum of the individual components  $\varepsilon_{ij}$

Fig. 2.12 Grid-based model for spatial correlation.

Fig. 2.13 Hierarchical model for spatial correlation.

over all levels of the regions that overlap with the location of the gate k.

The techniques proposed in [2] and [18] have been successfully applied to many practical problems. Since both techniques rely on partition, the trade-off between model accuracy and model complexity can be easily controlled by the number of total partitions. However, such partition-based approaches suffer from one major limitation: the approximated correlation function is not continuous in distance. Discontinuity will appear at the boundary of every individual region.

Most recently, several techniques have been proposed to address the aforementioned discontinuity problem. The authors in [119] proposed an efficient numerical algorithm to extract the spatial correlation function based on measurement data. The correlation extraction is formulated as a nonlinear optimization problem that can be robustly and efficiently solved by a projection-based algorithm. Bhardwaj et al. proposed an alternative algorithm to address the similar problem [10]. The algorithm proposed in [10] is based on the Karhunen–Loève expansion borrowed from stochastic process theory. It attempts to find a compact set of nonlinear basis functions to approximate the two-dimensional spatial correlation.

#### 2.4.3 Principal Component Analysis

While many physical variations (e.g.,  $\Delta T_{\text{OX}}$ ,  $\Delta V_{\text{TH}}$ , etc.) are correlated, most statistical analysis algorithms can handle independent random variations much more easily than correlated variations. For example, it is easy to draw independent sampling points from a random number generator for Monte Carlo analysis (more details in Chapter 3). If one wants to create correlated random samples, the computational cost will be significantly increased [92]. For this reason, there is a need to mathematically represent correlated physical variations by a set of independent random variables. Principal component analysis (PCA) [98] is a statistical method that finds a compact set of independent factors to represent a *multivariate Normal distribution*. The random variables from a multivariate Normal distribution are also called *jointly Normal*.

Given N process parameters  $X = [x_1, x_2, ..., x_N]^T$ , the process variation  $\Delta X = X - X_0$ , where  $X_0$  is the mean value of X, is often approximated as a zero-mean multivariate Normal distribution. The correlation of  $\Delta X$  can be represented by a symmetric, positive semidefinite covariance matrix R. PCA decomposes R as

$$R = V \cdot \Sigma \cdot V^T, \tag{2.2}$$

where  $\Sigma = \text{diag}(\lambda_1, \lambda_2, \dots, \lambda_N)$  contains the eigenvalues of R, and  $V = [V_1, V_2, \dots, V_N]$  contains the corresponding eigenvectors that are orthonormal, i.e.,  $V^T V = I$  (I is the identity matrix). Based on  $\Sigma$  and V, PCA defines a set of new random variables:

$$\Delta Y = \Sigma^{-0.5} \cdot V^T \cdot \Delta X. \tag{2.3}$$

These new random variables in  $\Delta Y$  are called the principal components or factors. It is easy to verify that all elements in  $\Delta Y = [\Delta y_1, \Delta y_2, \dots, \Delta y_N]^T$  are uncorrelated and satisfy the standard Normal distribution N(0,1) (i.e., zero mean and unit standard deviation):

$$E\left(\Delta Y \cdot \Delta Y^{T}\right) = E\left(\Sigma^{-0.5} \cdot V^{T} \cdot \Delta X \cdot \Delta X^{T} \cdot V \cdot \Sigma^{-0.5}\right)$$

$$= \Sigma^{-0.5} \cdot V^{T} \cdot E\left(\Delta X \cdot \Delta X^{T}\right) \cdot V \cdot \Sigma^{-0.5}$$

$$= \Sigma^{-0.5} \cdot V^{T} \cdot V \cdot \Sigma \cdot V^{T} \cdot V \cdot \Sigma^{-0.5} = I, \quad (2.4)$$

where  $E(\bullet)$  stands for the expected value operator. In addition, jointly Normal random variables are mutually independent if and only if they are uncorrelated [98]. Therefore, Equation (2.4) also implies that all elements in  $\Delta Y = [\Delta y_1, \Delta y_2, \dots, \Delta y_N]^T$  are mutually independent.

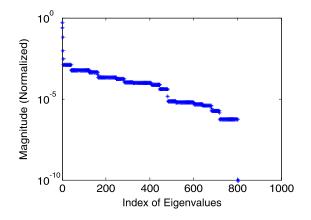

The essence of PCA can be interpreted as a coordinate rotation of the space defined by the original random variables. In addition, if the magnitudes of the eigenvalues  $\{\lambda_i\}$  decrease quickly, it is possible to use a small number of random variables, i.e., a small subset of principal components, to approximate the original *N*-dimensional space. More details of PCA can be found in [98].

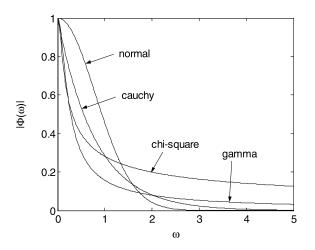

#### 2.4.4 Non-Normal Process Variations

In most practical cases, process parameters are modeled as a multivariate Normal distribution, which allows us to apply many mathematical techniques to simplify the statistical analysis problem. PCA, for example, can decompose correlated jointly Normal variables into independent ones. If the random variables are non-Normal, mutual independence must be checked by high-order moments and, therefore, PCA cannot be applied to such cases.

There are a few cases where process variations are non-Normal, as observed from the measurement data. For example, systematic variations often exhibit non-Normal distributions, since they are not truly random. In these cases, if the non-Normal variations are mutually independent, they can be either directly incorporated into statistical analysis engine (e.g., for Monte Carlo analysis) or converted to Normal distributions by a nonlinear transform. Next, we briefly describe the nonlinear transform that converts independent non-Normal distributions to independent Normal distributions.

Given a set of random variables  $\Delta X = [\Delta x_1, \Delta x_2, \dots, \Delta x_N]^T$ , we assume that all these random variables  $\{\Delta x_i; i = 1, 2, \dots, N\}$  are non-Normal and mutually independent. A set of one-dimensional functions  $\{\Delta y_i = g_i(\Delta x_i); i = 1, 2, \dots, N\}$  can be constructed to convert  $\Delta X$  to  $\Delta Y = [\Delta y_1, \Delta y_2, \dots, \Delta y_N]^T$  such that  $\{\Delta y_i; i = 1, 2, \dots, N\}$  are Normal [98]. The transform function  $g_i(\bullet)$  can be found via the following two steps [98].

First, the random variable  $\Delta x_i$  is converted to a uniform distribution  $\Delta u_i \in [0,1]$  by defining

$$\Delta u_i = \mathrm{cdf}_{\Delta x_i}(\Delta x_i),\tag{2.5}$$

where  $\operatorname{cdf}_{\Delta x_i}(\bullet)$  is the cumulative distribution function of  $\Delta x_i$ . Since any cumulative distribution function is monotonic, we have

$$P\left(\Delta u_{i} \leq t\right) = P\left[\Delta x_{i} \leq \operatorname{cdf}_{\Delta x_{i}}^{-1}\left(t\right)\right],$$

(2.6)

where  $P(\bullet)$  denotes the probability and  $\operatorname{cdf}_{\Delta x_i}^{-1}(\bullet)$  stands for the inverse function of  $\operatorname{cdf}_{\Delta x_i}(\bullet)$ . Therefore, the cumulative distribution function of  $\Delta u_i$  is equal to

$$\operatorname{cdf}_{\Delta u_i}(t) = P(\Delta u_i \le t) = P\left[\Delta x_i \le \operatorname{cdf}_{\Delta x_i}^{-1}(t)\right] = \operatorname{cdf}_{\Delta x_i}\left[\operatorname{cdf}_{\Delta x_i}^{-1}(t)\right] = t$$

(2.7)

Equation (2.7) shows the fact that  $\Delta u_i$  is a uniform distribution.

Second, we convert the uniform distribution  $\Delta u_i$  to a standard Normal distribution  $\Delta y_i$  by defining

$$\Delta y_i = \operatorname{cdf}_{N(0,1)}^{-1}(\Delta u_i), \qquad (2.8)$$

where  $\operatorname{cdf}_{N(0,1)}(\bullet)$  is the cumulative distribution function of standard Normal distribution. Given the uniform distribution  $\Delta u_i$ , the following equation proves why  $\Delta y_i$  defined in (2.8) is a standard Normal distribution

$$\operatorname{cdf}_{\Delta y_i}(t) = P(\Delta y_i \le t) = P\left[\Delta u_i \le \operatorname{cdf}_{N(0,1)}(t)\right] = \operatorname{cdf}_{N(0,1)}(t).$$

(2.9)

Since the random variables  $\{\Delta x_i; i = 1, 2, ..., N\}$  are mutually independent, the random variables  $\{\Delta y_i; i = 1, 2, ..., N\}$  are also mutually independent and their joint probability density function is given by

$$pdf_{\Delta Y}(\Delta y_1, \Delta y_2, \dots, \Delta y_N) = pdf_{\Delta y_1}(\Delta y_1) \cdot pdf_{\Delta y_2}(\Delta y_2) \cdots pdf_{\Delta y_N}(\Delta y_N).$$

(2.10)

It is easy to verify that the random variables in  $\Delta Y$  constitute a multivariate Normal distribution [98].

The aforementioned nonlinear transform approach, however, is not applicable to correlated non-Normal distributions. At first glance, the nonlinear transform approach seems still valid. The one-dimensional nonlinear functions { $\Delta y_i = g_i(\Delta x_i)$ ; i = 1, 2, ..., N} can be constructed to convert each non-Normal random variable  $\Delta x_i$  to a Normal variable  $\Delta y_i$ . Unfortunately, after the nonlinear transform is performed, the random variables { $\Delta y_i$ ; i = 1, 2, ..., N} are *not* mutually independent and their joint probability density function is not equal to the product of the marginal probability density functions, i.e.,

$$pdf_{\Delta Y}(\Delta y_1, \Delta y_2, \dots, \Delta y_N) \neq pdf_{\Delta y_1}(\Delta y_1) \cdot pdf_{\Delta y_2}(\Delta y_2) \cdots pdf_{\Delta y_N}(\Delta y_N).$$

(2.11)

In this case, the random variables  $\{\Delta y_i; i = 1, 2, ..., N\}$  are not guaranteed to be a multivariate Normal distribution. In other words, even if the random variables  $\{\Delta y_i; i = 1, 2, ..., N\}$  are marginally Normal, they might not be jointly Normal [98]. This property can be understood from the following example described in [98].

Consider two random variables  $\Delta y_1$  and  $\Delta y_2$ , and their joint probability density function:

$$pdf_{\Delta Y}(\Delta y_1, \Delta y_2) = pdf_1(\Delta y_1) \cdot pdf_2(\Delta y_2)$$

$$\cdot \{1 + \rho \cdot [2 \cdot cdf_1(\Delta y_1) - 1]$$

$$\cdot [2 \cdot cdf_2(\Delta y_2) - 1]\}, \qquad (2.12)$$

where  $|\rho| < 1$ , and  $pdf_1(\Delta y_1)$  and  $pdf_2(\Delta y_2)$  are two probability density functions with respective cumulative distribution functions  $cdf_1(\Delta y_1)$ and  $cdf_2(\Delta y_2)$ . It is easy to verify that [98]

$$pdf_{\Delta Y}(\Delta y_1, \Delta y_2) \ge 0$$

$$\int_{-\infty}^{+\infty} \int_{-\infty}^{+\infty} pdf_{\Delta Y}(\Delta y_1, \Delta y_2) \cdot d\Delta y_1 \cdot d\Delta y_2 = 1.$$

(2.13)

Equation (2.13) shows that the function in (2.12) is a valid joint probability density function. In addition, directly integrating the joint probability density function yields [98]:

$$\int_{-\infty}^{+\infty} \mathrm{pdf}_{\Delta Y}(\Delta y_1, \Delta y_2) \cdot d\Delta y_2 = \mathrm{pdf}_1(\Delta y_1)$$

$$\int_{-\infty}^{+\infty} \mathrm{pdf}_{\Delta Y}(\Delta y_1, \Delta y_2) \cdot d\Delta y_1 = \mathrm{pdf}_2(\Delta y_2)$$

(2.14)

implying that  $pdf_1(\Delta y_1)$  and  $pdf_2(\Delta y_2)$  in (2.12) are the marginal probability density functions of  $\Delta y_1$  and  $\Delta y_2$ , respectively. In particular, let  $pdf_1(\Delta y_1)$  and  $pdf_2(\Delta y_2)$  be Normal distributions. In this case, both  $\Delta y_1$  and  $\Delta y_2$  are marginally Normal; however, their joint probability density function in (2.12) is not a multivariate Normal distribution.

Correlated non-Normal random variables must be characterized by their joint probability density function, thereby making them extremely difficult to handle in statistical analysis. Even Monte Carlo simulation becomes impractical, if not impossible, in such cases, since it is difficult to draw random samples from a general, multi-dimensional joint probability density function [92, 94]. In addition, using correlated non-Normal distributions also increases the difficulty of process characterization, because extracting the multi-dimensional joint probability density function from silicon testing data is not trivial. For these reasons, how to efficiently model and analyze correlated non-Normal process variations remains an open topic in the IC design community.

#### 2.5 Manufacturing Yield

The large-scale process variations significantly impact circuit performance in nano-scale technologies. From the product point of view, they directly affect the manufacturing yield. *Yield* is defined as the proportion of the manufactured chips that function correctly. As process variations become relatively large in 65 nm technologies and beyond, yield becomes one of the top concerns for today's integrated circuit design. In this sub-section, we briefly review several important concepts related to yield.

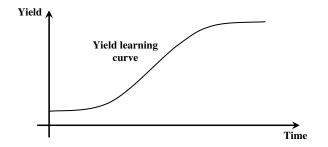

First of all, it is important to note that the yield of a specific product manufactured with a specific technology is *not* static [61]. Yield is typically low when a new process is initially developed. It must be substantially improved before high-volume production is started. Otherwise, the manufacturing cost would be extremely expensive or even unaffordable. The yield improvement could be achieved via various tunings by both design engineers and process engineers. Such a tuning procedure is called *yield learning*, as shown in Figure 2.14.

Fig. 2.14 Yield learning curve for a specific product manufactured with a specific technology.

The *faults* in a manufacturing process can be classified into two broad categories: *catastrophic* faults (due to physical and structural defects such as open, short, etc.) and *parametric* faults (due to parametric variations in process parameters such as  $V_{\rm TH}$ ,  $T_{\rm OX}$ , etc.). Both catastrophic faults and parametric faults play important roles in integrated circuit manufacturing. In general, it is difficult to emphasize one of them while completely ignoring the other. There are several important observations of catastrophic and parametric faults for most commercial manufacturing processes.

First, catastrophic faults are often critical at the initial stage when a new technology node is developed. As the manufacturing technology becomes mature, catastrophic faults can be significantly reduced and parametric faults become increasingly important. Second, catastrophic faults are most important for large-size circuits that consume large silicon areas. For example, digital system-on-chip (SOC) designs and memory circuits significantly suffer from catastrophic faults. Finally, as process variations become relatively large due to technology scaling, parametric faults are becoming increasingly crucial at 90 nm technologies and beyond.

In summary, the relative importance of catastrophic faults and parametric faults varies from time to time as manufacturing technologies become more and more mature. It is also circuit-dependent and processdependent. Therefore, for a specific design, both catastrophic and parametric faults must be carefully studied for yield learning.

| - |    |  |

|---|----|--|

|   |    |  |

| • | ٩. |  |

|   |    |  |

|   |    |  |

## **Transistor-Level Statistical Methodologies**

Transistor-level statistical analysis and optimization techniques focus on a single circuit block consisting of a few hundred devices. A circuit block can be, for example, a standard library cell, an interconnect wire, an analog amplifier, etc. Analyzing these circuit blocks involve transistor-level simulation using SPICE-like engine (e.g., Cadence SPECTRE, Synopsys HSPICE, etc.). For nano-scale IC technologies, even though a circuit block is small, the corresponding statistical analysis and optimization problem is not trivial mainly because of the following reasons:

- Device models are extremely complex at 65 nm technologies and beyond. The state-of-the-art BSIM4 model contains more than 20,000 lines of C code to describe the behavior of a single MOS transistor! It, in turn, results in expensive device model evaluation for transistor-level simulation. In many practical applications, it is not uncommon that more than 50% of the simulation time is consumed by device model evaluation.

- Large-scale process variations must be characterized by complex statistical models. A statistical device model typically

contains a great number of random variables to capture various device-level variations, thereby further increasing device model complexity. For example, a commercial 65 nm CMOS process may contain more than 300 independent random variables to model inter-die variations. If device mismatches are simultaneously considered, it will introduce more than 10 additional random variables for *every* transistor!

• Interconnect models become increasingly sophisticated. As the continuous device scaling pushes operational frequency to GHz region, a physical on-chip interconnect model can consist of hundreds of (or even thousands of) RC elements. In many high-speed applications (e.g., micro-processor package, high-speed data link, RF transceiver, etc.), parasitic inductance starts to play an important role, which further complicates both parasitic extraction and transistor-level simulation.

In this chapter, we review various statistical techniques that address the transistor-level analysis and optimization problem. Several recently-developed methodologies, including projection-based performance modeling (PROBE) and asymptotic probability extraction (APEX), will be discussed in detail.

#### 3.1 Monte Carlo Analysis

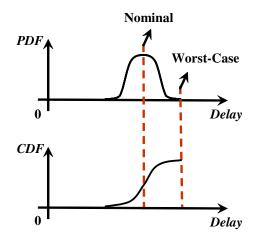

Monte Carlo analysis is an important technique for statistical circuit analysis [92, 94]. It attempts to estimate the probability distribution of the performance of interest (e.g., gain, bandwidth, power, etc.) via three steps: (1) generating a set of random samples for process parameters, (2) running transistor-level simulations and evaluating the performance values at all sampling points, and (3) estimating the performance distribution by bin-based histogram or advanced kernel smoothing methods [102].

The relative cost of the aforementioned three steps is applicationdependent. In general, it is difficult to identify which one of these steps dominates the overall computational time. For transistor-level

#### 360 Transistor-Level Statistical Methodologies

Monte Carlo analysis, the second step is often the most time-consuming part, since it involves a large number of expensive transistor-level simulations.

The accuracy of Monte Carlo analysis depends on the number of random samples. In practice, a huge number of sampling points are required to achieve sufficient accuracy, which is one of the major limitations of Monte Carlo analysis. Next, we will discuss this accuracy issue in detail.

#### 3.1.1 Accuracy of Monte Carlo Analysis

Monte Carlo analysis is a statistical sampling technique. Theoretically, we cannot get identical results from two separate Monte Carlo simulations. It, therefore, implies that Monte Carlo accuracy must be analyzed by statistical methodologies. We will use the following simple example to show such statistical analysis.

Assume that x is a random variable with standard Normal distribution (i.e., zero mean and unit variance) and we attempt to estimate its mean value by Monte Carlo analysis. For this purpose, we randomly pick up M sampling points  $\{x_1, x_2, \ldots, x_M\}$  and estimate the mean value by

$$\mu_x = \frac{1}{M} \cdot \sum_{i=1}^M x_i, \qquad (3.1)$$

where  $\mu_x$  is called a *point estimator* of the mean value [81].

Since  $\{x_1, x_2, \ldots, x_M\}$  are drawn from a random number generator that follows the probability distribution of x, all  $\{x_1, x_2, \ldots, x_M\}$  are standard Normal distributions. In addition, all  $\{x_1, x_2, \ldots, x_M\}$  should be mutually independent, if the random number generator is sufficiently good, i.e., the period of its pseudo-random sequence is sufficiently large. Given these two assumptions, we can theoretically calculate the first two moments of  $\mu_x$

$$E(\mu_x) = E\left(\frac{1}{M} \cdot \sum_{i=1}^{M} x_i\right) = \frac{1}{M} \cdot \sum_{i=1}^{M} E(x_i) = 0$$

(3.2)

3.1 Monte Carlo Analysis 361

$$E(\mu_x^2) = E\left[\frac{1}{M^2} \cdot \left(\sum_{i=1}^M x_i\right)^2\right] = \frac{1}{M^2} \cdot \sum_{i=1}^M E(x_i^2) = \frac{1}{M}.$$

(3.3)

Equation (3.2) demonstrates that the expected value of  $\mu_x$  is exactly equal to the mean value of x. Therefore, the point estimator in (3.1) is called an *unbiased estimator* [81]. The variance value in (3.3) has a twofold meaning. First, given a finite value of M, the estimator  $\mu_x$ does not yield a deterministic value. In other words, we cannot get identical results from two separate Monte Carlo simulations. Second, as M increases, the variance in (3.3) decreases and, therefore, the accuracy of Monte Carlo analysis is improved.

The accuracy of Monte Carlo analysis can be mathematically specified by a confidence interval [92]. The  $\alpha$ -level confidence interval is defined as an interval where the statistical measurement (e.g., the estimator  $\mu_x$  in the aforementioned example) falls corresponding to a given probability  $\alpha$ . For a fixed value of  $\alpha$ , the  $\alpha$ -level confidence interval shrinks (meaning that Monte Carlo analysis becomes increasingly accurate), as the number of random samples increases. However, due to the statistical nature of Monte Carlo analysis, there is always a small probability (i.e.,  $1 - \alpha$ ) that the statistical measurement will fall outside the confidence interval. From this point of view, even if a large number of samples are used, Monte Carlo analysis may still (although unlikely) yield a "wrong" result.

For a given accuracy specification defined by confidence interval, we can calculate the required number of Monte Carlo sampling points (i.e., M). In the aforementioned example, since all  $\{x_1, x_2, \ldots, x_M\}$ are Normal distributions, the estimator  $\mu_x$  in (3.1) is a linear combination of multiple Normal distributions and, therefore, is also Normal [81]. The 99.7%-level confidence interval is corresponding to the  $\pm 3\sigma$  boundary of  $\mu_x$ . If we require the 99.7%-level confidence interval to be [-0.1, 0.1], the required number of sampling points is equal to

$$M \ge \left(\frac{3}{0.1}\right)^2 = 900. \tag{3.4}$$

#### 362 Transistor-Level Statistical Methodologies

If we require the 99.7%-level confidence interval to be [-0.01, 0.01], the required number of sampling points is equal to:

$$M \ge \left(\frac{3}{0.01}\right)^2 = 90,000. \tag{3.5}$$

Studying (3.4) and (3.5), one would notice that Monte Carlo error is only reduced by  $10\times$ , if the number of random sampling points is increased by  $100\times$ . To achieve sufficient accuracy, a great number of sampling points are required, which is one of the major limitations of Monte Carlo analysis. In many practical problems, a typical selection of the number of random samples is around 1,000 ~ 10,000.

One major advantage of Monte Carlo analysis is that its accuracy is independent of the underlying problem dimension (i.e., the number of random variables in the stochastic system) [92, 94]. This property implies that we do not have to increase the number of Monte Carlo sampling points as problem dimension becomes increasingly large, e.g., when both inter-die variations and device mismatches must be simultaneously considered for statistical analysis. For this reason, Monte Carlo analysis can be more attractive than other techniques (e.g., response surface modeling methods) for large-dimension problems. A detailed comparison between Monte Carlo analysis and other techniques will be given in Section 3.2.4.

#### 3.1.2 Latin Hypercube Sampling

As discussed in 3.1.1, Monte Carlo analysis often requires a large number of random sampling points, thereby resulting in expensive computational cost. There are various techniques to control Monte Carlo samples to reduce the overall analysis cost. Instead of directly drawing random samples from a random number generator, these methods attempt to create sampling points from a controlled random sequence such that the estimation accuracy can be improved. *Latin hypercube sampling* (LHS) [64, 83] is one of these fast Monte Carlo techniques that we will discuss in detail in this sub-section.

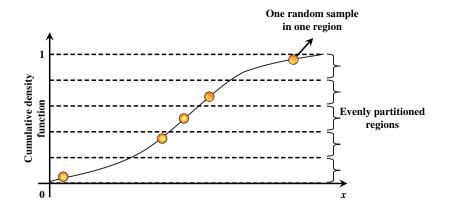

The key idea of Latin hypercube sampling [64, 83] is to make sampling point distribution close to the probability distribution function of the random variable that we try to sample. In the one-dimensional

Fig. 3.1 Five one-dimensional Latin hypercube samples for a single random variable x.

case where we attempt to generate M sampling points for a random variable x, Latin hypercube sampling consists of two steps. First, the cumulative distribution function  $cdf_x(x)$  is evenly partitioned into Mregions. Second, a single sampling point is randomly selected in each region. Figure 3.1 shows a simple example where five Latin hypercube sampling points are created for the random variable x. In this example, Latin hypercube sampling guarantees to select five sampling points from five different regions and, therefore, it eliminates the possibility that many sampling points come from the same small local region. Since Latin hypercube sampling distributes the sampling points all over the random space, it is more efficient than direct random sampling.

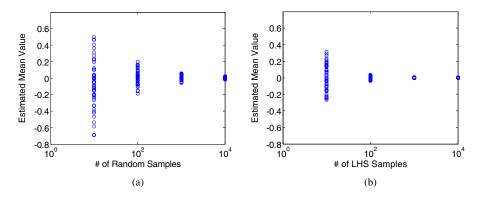

The efficacy of Latin hypercube sampling can be demonstrated by the following simple example. Assume that x is a random variable with standard Normal distribution (i.e., zero mean and unit variance) and we want to estimate its mean value by (3.1) based on Monte Carlo analysis. To compare Latin hypercube sampling with direct random sampling, we estimate the mean value of x by both sampling schemes. A number of experiments are conducted with different number of sampling points (M = 10,100,1,000, and 10,000) such that we can study the convergence rate of the error. In addition, given a fixed number of sampling points (e.g., M = 10), 50 independent Monte Carlo analyses are conducted to predict the probability distribution of the estimation error.

Fig. 3.2 Comparison of direct random sampling and Latin hypercube sampling. (a) Estimated mean values from random samples. (b) Estimated mean values from Latin hypercube samples.

Figure 3.2 shows the Monte Carlo analysis results and provides two important observations. First, both sampling schemes yield smaller error if a larger number of sampling points are utilized. Second, but most importantly, Latin hypercube sampling consistently results in smaller error (measured by the variance of the estimated mean value) than direct random sampling in this example.

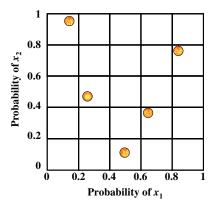

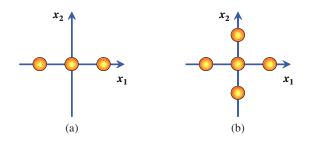

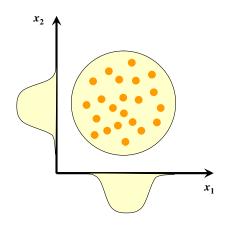

The aforementioned one-dimensional Latin hypercube sampling can be easily extended to two-dimensional cases. Assume that we want to generate M two-dimensional Latin hypercube samples for two independent random variables  $x_1$  and  $x_2$ . (Correlated Normal random variables can be decomposed to independent random variables by principal component analysis.) We first create two independent one-dimensional Latin hypercube sampling sets for  $x_1$  and  $x_2$ , respectively. Each sampling set consists of M samples. Next, we randomly combine the samples in these two sets to create M two-dimensional pairs. Figure 3.3 shows a simple example where five two-dimensional Latin hypercube sampling points are created for the independent random variables  $x_1$ and  $x_2$ . As shown in Figure 3.3, there is only a single grid filled with one sampling point in each row (or column), and the sampling point is randomly selected within that grid. As such, Latin hypercube sampling distributes its samples all over the two-dimensional random space. A high-dimensional Latin hypercube sampling can be similarly constructed [64, 83].

Fig. 3.3 Five two-dimensional Latin hypercube samples for two independent random variables  $x_1$  and  $x_2$ .

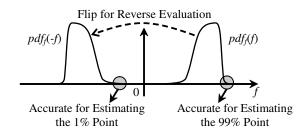

#### 3.1.3 Importance Sampling

Importance sampling is another commonly-used approach to speed-up Monte Carlo analysis [46, 92, 94]. The basic idea is to distort the original probability density function  $pdf_x(x)$  to reduce the variance of the estimator. Mathematically, the expected value of a given performance function f(x) is defined as

$$E(f) = \int_{-\infty}^{+\infty} f(x) \cdot \mathrm{pdf}_x(x) \cdot dx.$$

(3.6)

Direct Monte Carlo analysis estimates E(f) by drawing random sampling points from  $pdf_x(x)$ . Importance sampling, however, attempts to find a distorted probability density function  $pdf_y(y)$  such that choosing random sampling points from  $pdf_y(y)$  yields an estimation of E(f)with smaller variance.

$$E(f) = \int_{-\infty}^{+\infty} f(y) \cdot \frac{\mathrm{pdf}_{y}(y)}{\mathrm{pdf}_{y}(y)} \cdot \mathrm{pdf}_{x}(y) \cdot dy$$

$$= \int_{-\infty}^{+\infty} f(y) \cdot \frac{\mathrm{pdf}_{x}(y)}{\mathrm{pdf}_{y}(y)} \cdot \mathrm{pdf}_{y}(y) \cdot dy.$$

(3.7)

Equation (3.7) implies that if random sampling points are selected from the distorted probability density function  $pdf_y(y)$ , the expected value of  $f(y) \cdot pdf_x(y)/pdf_y(y)$  is exactly equal to E(f). Therefore, E(f) can

#### 366 Transistor-Level Statistical Methodologies

be estimated by the following unbiased estimator:

$$\mu_f = \frac{1}{M} \cdot \sum_{i=1}^M f(y_i) \cdot \frac{\mathrm{pdf}_x(y_i)}{\mathrm{pdf}_y(y_i)} \quad \left[ y_i \sim \mathrm{pdf}_y(y) \right], \tag{3.8}$$

where  $y_i$  is the *i*th random sampling point selected from the probability density function  $pdf_u(y)$ , and M is the total number of random samples.

It can be proven that if the distorted probability density function  $pdf_y(y)$  is proportional to  $f(y) \cdot pdf_x(y)$ , i.e.,

$$\frac{f(y) \cdot \mathrm{pdf}_x(y)}{\mathrm{pdf}_y(y)} = k \; \Rightarrow \; \mathrm{pdf}_y(y) = \frac{1}{k} \cdot f(y) \cdot \mathrm{pdf}_x(y), \qquad (3.9)$$

where k is a constant, the Monte Carlo analysis using importance sampling has minimal error, i.e., the variance of the estimator  $\mu_f$  in (3.8) is minimized [94]. In this "ideal" case, no matter which value is randomly selected for y, the function  $f(y) \cdot \text{pdf}_x(y)/\text{pdf}_y(y)$  is always equal to the constant k and, therefore, the variance of the estimator  $\mu_f$  in (3.8) is equal to 0.

The ideal case in (3.9), however, cannot be easily applied to practical applications. It can be extremely difficult to draw random samples from a general probability density function  $pdf_y(y) = f(y) \cdot pdf_x(y)/k$ , especially if the random variable y is multi-dimensional [92, 94]. Even in the one-dimensional case, selecting random sampling points from  $pdf_y(y)$  requires to know its cumulative distribution function [81, 92]:

$$\operatorname{cdf}_{y}(y) = \int_{-\infty}^{y} \operatorname{pdf}_{y}(y) \cdot dy = \frac{1}{k} \cdot \int_{-\infty}^{y} f(y) \cdot \operatorname{pdf}_{x}(y) \cdot dy \qquad (3.10)$$

implying that the integral in (3.6) must be known in advance and there would hence be no reason to run Monte Carlo analysis at all!

Based on these discussions, a practical selection of the distorted probability density function  $pdf_y(y)$  must satisfy the following two constraints:

• Easy to sample. Random samples must be created from  $pdf_y(y)$  easily.

• Minimizing estimator variance.  $pdf_y(y)$  must be close to  $f(y) \cdot pdf_x(y)/k$  as much as possible so that the estimator variance (i.e., the error) can be minimized.

Finding the optimal probability density function  $pdf_y(y)$  for importance sampling is not trivial in many practical applications. It is often application-dependent and must be constructed by experience, which is one of the key limitations of the importance sampling technique. For integrated circuits, one important application of importance sampling is to estimate the rare failure events of memory circuits, as reported in [46]. In such applications, the optimal probability density function  $pdf_y(y)$  is optimized such that the rare failure events will occur with a much higher probability and, therefore, they can be easily captured by Monte Carlo analysis.

## 3.1.4 Quasi Monte Carlo Analysis

An alternative strategy for better controlling Monte Carlo samples is to use so-called *low-discrepancy* samples which are deterministically chosen to "more uniformly" sample the statistical distribution [92]. The technique is called *Quasi Monte Carlo* (QMC) and is widely used in many application domains. For example, it is a standard method in the computational finance world for evaluating complex financial instruments under various forms of statistical uncertainty. The technique is applicable to the world of scaled semiconductor problems as well: speedups of  $10-50 \times$  have been demonstrated in [105] compared with a direct Monte Carlo simulation.

A number of deterministic sequences can be constructed for Quasi Monte Carlo analysis such that the *divergence* (a measure of Monte Carlo analysis error) decreases in the order of  $O[(\log M)^{N-1}/M]$  [92], where M is the number of random samples and N is the underlying problem dimension (i.e., the number of random variables in the stochastic system). Compared with the direct Monte Carlo analysis that has a divergence rate of O[1/sqrt(M)], Quasi Monte Carlo analysis can offer a substantial gain, when N is small and M is large. However, for high-dimensional problems where N is large, the benefit of using Quasi Monte Carlo analysis may be difficult to justify.

# 3.2 Statistical Performance Modeling

As previously discussed, Monte Carlo analysis requires a huge number of sampling points to achieve sufficient accuracy. In practice, repeatedly running transistor-level simulations for so many times is often time-consuming or even infeasible for large-size circuits. For example, simulating an industrial phase-locked loop (PLL) or analog-to-digital converter (ADC) at one single sampling point may take more than one month on a stand-alone machine!

To overcome this difficulty, response surface modeling (also referred to as performance modeling) has been widely used to reduce the computational cost. The key idea here is to approximate the performance of interest (e.g., delay, power, gain, etc.) as a polynomial function of the process parameters that are modeled as random variables (e.g.,  $V_{\rm TH}$ ,  $T_{\rm OX}$ , etc.). Such a response surface model establishes an analytical dependence between device-level variations and circuit-level performance so that statistical analysis can be further applied to estimate the performance variation efficiently.

# 3.2.1 Response Surface (Performance) Modeling

Given a fixed circuit design, the circuit performance f can be approximated as a linear response surface model of process parameters [69, 73]:

$$f(X) = B^T X + C, (3.11)$$

where  $X = [x_1, x_2, ..., x_N]^T$  represents the random variables to model process variations,  $B \in \mathbb{R}^N$  and  $C \in \mathbb{R}$  stand for the model coefficients, and N is the total number of the random variables of concern.

The linear approximation in (3.11) is efficient and accurate when process variations are sufficiently small. However, the recent advances in IC technologies suggest a need to revisit this assumption. As IC technologies are scaled to finer feature sizes, process variations become relatively larger. As reported in [73], the gate length variation can reach  $\pm 35\%$  at 90 nm technologies and beyond. It, in turn, implies the importance of applying high-order (e.g., quadratic) response surface models to achieve high approximation accuracy [69]. Note that applying quadratic response surface models is especially important for analog circuits, since many analog performances can be strongly nonlinear in the presence of large-scale manufacturing variations. A quadratic response surface model has the form of [69]:

$$f(X) = X^{T}AX + B^{T}X + C,$$

(3.12)

where  $C \in R$  is the constant term,  $B \in R^N$  contains the linear coefficients, and  $A \in R^{N \times N}$  contains the quadratic coefficients.

The unknown model coefficients in (3.11) and (3.12) can be determined by solving the over-determined linear equations at a number of sampling points [69]:

$$B^T X_i + C = \tilde{f}_i \quad (i = 1, 2, \dots, S)$$

(3.13)

$$X_i^T A X_i + B^T X_i + C = \tilde{f}_i \quad (i = 1, 2, \dots, S),$$

(3.14)

where  $X_i$  and  $\tilde{f}_i$  are the value of X and the exact value of f for the *i*th sampling point, respectively, and S is the total number of sampling points.

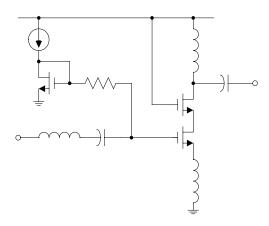

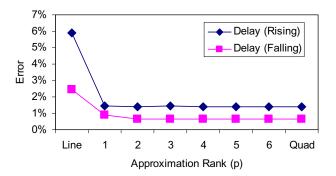

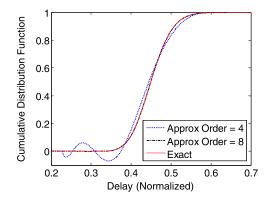

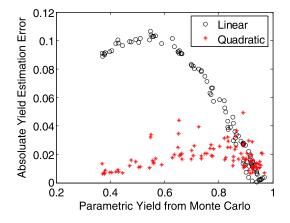

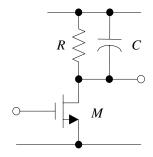

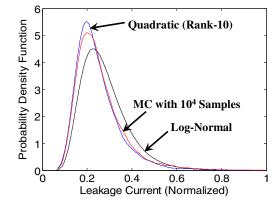

Quadratic response surface model is much more accurate than linear response surface model in many practical applications. Figure 3.4 shows the circuit schematic of a low noise amplifier designed in a commercial

Fig. 3.4 Circuit schematic of a low noise amplifier designed in a commercial  $0.25\,\mu\mathrm{m}$  BiC-MOS process.

$0.25 \,\mu$ m BiCMOS process. For this low noise amplifier, the variations of both MOS transistors and passive components (capacitors and inductors) are modeled. The probability distributions and the correlation information of these variations are provided in the process design kit. After principal component analysis, eight principal factors are identified to capture all process variations. The performance of the low noise amplifier is characterized by eight different performance metrics. We approximate these performance metrics by both linear and quadratic response surface models. Table 3.1 shows the approximation error for both models. In this example, the quadratic modeling error is  $7.5 \times$ smaller than the linear modeling error on average. In addition, it should be noted that the nonlinear terms in the quadratic models are expected to become increasingly important, as process variations become larger in scaled IC technologies.

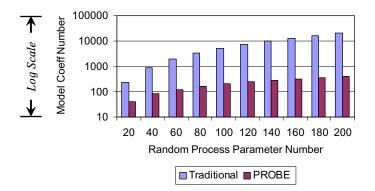

Using quadratic response surface model, however, significantly increases the modeling cost. It is straightforward to verify that the number of unknown coefficients in (3.12) is  $O(N^2)$ , where N is the total number of the random variables to model process variations. If the total number of random variables reaches 100, a quadratic approximation will result in a 100 × 100 quadratic coefficient matrix containing 10,000 coefficients! The overall computational cost of quadratic response surface modeling consists of two portions:

• Simulation cost. i.e., the cost for running a transistor-level simulator to determine the performance value  $\tilde{f}_i$  at every sampling point  $X_i$ . The number of simulation samples should be greater than the number of unknown coefficients in order

| Performance | Linear $(\%)$ | Quadratic (%) |

|-------------|---------------|---------------|

| F0          | 1.76          | 0.14          |

| S11         | 6.40          | 1.32          |

| S12         | 3.44          | 0.61          |

| S21         | 2.94          | 0.34          |

| S22         | 5.56          | 3.47          |

| NF          | 2.38          | 0.23          |

| IIP3        | 4.49          | 0.91          |

| Power       | 3.79          | 0.70          |

Table 3.1 Response surface modeling error for low noise amplifier.

to uniquely solve the linear equations in (3.14). Therefore, at least  $O(N^2)$  sampling points are required to fit the quadratic model in (3.12). In practical applications, the number of samples is generally selected to be significantly larger than the unknown coefficient number to avoid over-fitting. The simulation cost is typically the dominant portion of the overall computational cost, if the transistor-level simulation is expensive for a given circuit.

• Fitting cost. i.e., the cost for solving the over-determined linear equations in (3.14). For the quadratic model in (3.12), the fitting cost is on the order of  $O(N^6)$ .

The high computational cost of quadratic response surface modeling becomes one of the most challenging problems recently, especially because intra-die variations (e.g., device mismatches) play an increasingly important role in nano-scale technologies. These intra-die variations must be modeled by many additional random variables, thereby significantly increasing the number of unknown model coefficients. This makes quadratic response surface modeling much more expensive or even infeasible in many practical nano-scale problems.

There are several techniques available to reduce quadratic response surface modeling cost. *Projection pursuit* is one of the interesting and useful techniques in this domain. The original work on projection pursuit was proposed by mathematicians in the early of 1980's [33]. The idea was recently adapted and tuned by Li et al. [57] to create an efficient projection-based extraction algorithm (PROBE) for quadratic response surface modeling. We will discuss the PROBE algorithm in detail in the next sub-section.

## 3.2.2 Projection-Based Performance Modeling

# 3.2.2.1 Mathematic Formulation

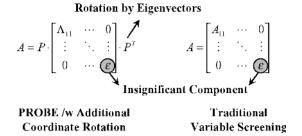

The key disadvantage of the traditional quadratic response surface modeling is the need to compute all elements of the matrix A in (3.12). This matrix is often sparse and rank-deficient in many practical problems. Therefore, instead of finding the full-rank matrix A,

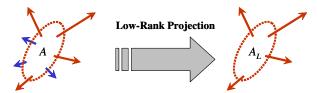

PROBE [57] approximates A by another low-rank matrix  $A_L$ . Such a low-rank approximation problem can be stated as follows: given a matrix A, find another matrix  $A_L$  with rank  $p < \operatorname{rank} (A)$  such that their difference  $||A_L - A||_F$  is minimized. Here,  $|| \bullet ||_F$  denotes the Frobenius norm, which is the square root of the sum of the squares of all matrix elements. Without loss of generality, we assume that A is symmetric in this paper, since any asymmetric quadratic form  $X^T A X$  can be converted to an equivalent symmetric form  $0.5 \cdot X^T (A + A^T) X$  [38].

From matrix theory [38], for any symmetric matrix  $A \in \mathbb{R}^{N \times N}$ , the optimal rank-*p* approximation with the least Frobenius-norm error is:

$$A_L = \sum_{i=1}^p \lambda_i P_i P_i^T, \qquad (3.15)$$

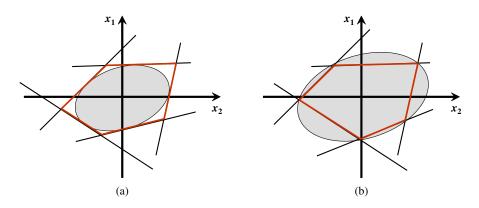

where  $\lambda_i$  is the *i*th dominant eigenvalue and  $P_i \in \mathbb{R}^N$  is the *i*th dominant eigenvector. The eigenvectors in (3.15) define an orthogonal projector  $P_1P_1^T + P_2P_2^T + \cdots + P_pP_p^T$ , and every column in  $A_L$  is the *projection* of every column in A onto the subspace span $\{P_1, P_2, \ldots, P_p\}$ . PROBE uses this orthogonal projector for quadratic response surface modeling, which is intuitively illustrated in Figure 3.5.

The main advantage of the rank-p projection is that, for approximating the matrix  $A \in \mathbb{R}^{N \times N}$  in (3.12), only  $\lambda_i \in \mathbb{R}$  and  $P_i \in \mathbb{R}^N$ (i = 1, 2, ..., p) should be determined, thus reducing the number of problem unknowns to O(pN). In many practical applications, p is significantly less than N and the number of unknown coefficients that PROBE needs to solve is almost a linear function of N. Therefore,

Fig. 3.5 PROBE identifies the most critical directions where process variations significantly impact a given circuit performance and then fits a quadratic response surface model along these directions [57].

compared with the problem size  $O(N^2)$  of the traditional quadratic modeling, PROBE is much more efficient and can be applied to large-size problems.

## 3.2.2.2 Coefficient Fitting via Implicit Power Iteration

Since the matrix A in (3.12) is not known in advance, we cannot use the traditional matrix computation algorithm to compute the dominant eigenvalues  $\lambda_i$  and eigenvectors  $P_i$  that are required for low-rank approximation. One approach for finding the optimal rank-p model is to solve the following optimization problem for the unknown coefficients  $\lambda_i$  and  $P_i$  (i = 1, 2, ..., p) and B, C:

minimize

$$\psi = \sum_{i} \left[ X_i^T \left( \sum_{j=1}^p \lambda_j P_j P_j^T \right) X_i + B^T X_i + C - \tilde{f}_i \right]^2$$

(3.16)

subject to  $||P_j||_2 = 1$  (j = 1, ..., p),

where  $\|\bullet\|_2$  denotes the 2-norm of a vector.

Compared with (3.12), Equation (3.16) approximates the matrix A by  $\lambda_1 P_1 P_1^T + \lambda_2 P_2 P_2^T + \cdots + \lambda_p P_p P_p^T$ . Therefore, we can expect that minimizing the cost function  $\Psi$  in (3.16) will converge  $\lambda_i$  and  $P_i$  to the dominant eigenvalues and eigenvectors of the original matrix A, respectively. Unfortunately,  $\Psi$  in (3.16) is a 6th-order polynomial and may not be convex. In addition, the constraint set in (3.16) is specified by a quadratic equation and is not convex either. Therefore, the optimization in (3.16) is not a convex programming problem and there is no efficient optimization algorithm that can guarantee finding the global optimum for  $\Psi$ .

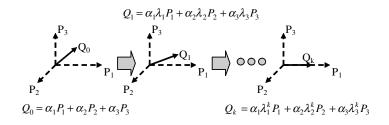

Instead of solving the non-convex optimization problem in (3.16), PROBE utilizes an *implicit power iteration* method to efficiently extract the unknown coefficients  $\lambda_i$  and  $P_i$  (i = 1, 2, ..., p). The implicit power iteration solves a sequence of over-determined linear equations and exhibits robust convergence. In what follows, we first describe the implicit power iteration algorithm for rank-one approximation, and then extend it to rank-p approximation.

## A. Rank-One Implicit Power Iteration

# Algorithm 3.1 rank-one implicit power iteration.

- (1) Start from a set of sampling points  $\{X_i, \tilde{f}_i; i = 1, 2, ..., S\}$ , where S is the total number of sampling points.

- (2) Randomly select an initial vector  $Q_0 \in \mathbb{R}^N$  and set k = 1.

- (3) Compute  $Q_{k-1} = Q_{k-1} / ||Q_{k-1}||_2$ .

- (4) Solve the over-determined linear equations for  $Q_k$ ,  $B_k$ , and  $C_k$ :

$$X_i^T Q_k Q_{k-1}^T X_i + B_k^T X_i + C_k = \tilde{f}_i \quad (i = 1, 2, \dots, S).$$

(3.17)

(5) If the residue:

$$\psi_k(Q_k, B_k, C_k) = \sum_i \left( X_i^T Q_k Q_{k-1}^T X_i + B_k^T X_i + C_k - \tilde{f}_i \right)^2$$

(3.18)

is unchanged, i.e.,

$$|\psi_k(Q_k, B_k, C_k) - \psi_{k-1}(Q_{k-1}, B_{k-1}, C_{k-1})| < \varepsilon,$$

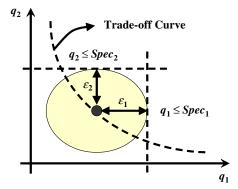

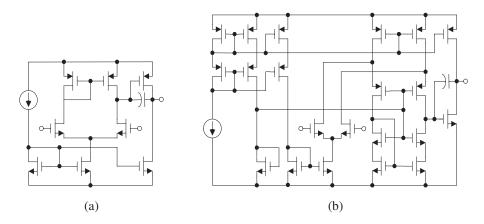

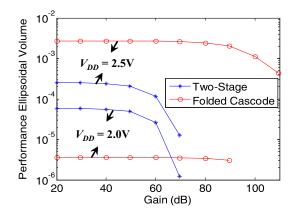

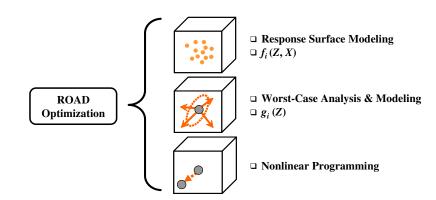

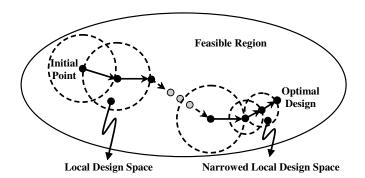

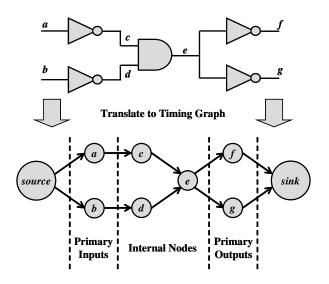

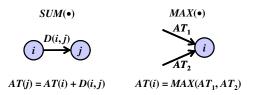

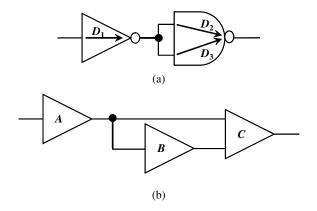

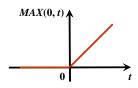

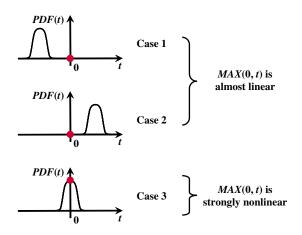

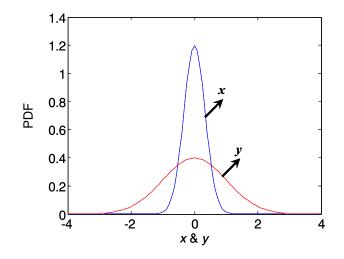

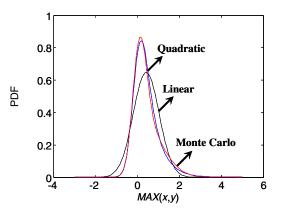

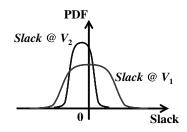

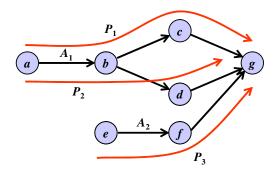

(3.19)