# Structural properties and band offset determination of p-channel mixed As/Sb type-II staggered gap tunnel field-effect transistor structure

Y. Zhu, N. Jain, D. K. Mohata, S. Datta, D. Lubyshev et al.

Citation: Appl. Phys. Lett. 101, 112106 (2012); doi: 10.1063/1.4752115

View online: http://dx.doi.org/10.1063/1.4752115

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v101/i11

Published by the American Institute of Physics.

#### **Related Articles**

Increase of interface and bulk density of states in amorphous-indium-gallium-zinc-oxide thin-film transistors with negative-bias-under-illumination-stress time

Appl. Phys. Lett. 101, 113504 (2012)

Enhancing threshold voltage of AlGaN/GaN high electron mobility transistors by nano rod structure: From depletion mode to enhancement mode Appl. Phys. Lett. 101, 112105 (2012)

Comparative study of solution-processed carbon nanotube network transistors Appl. Phys. Lett. 101, 112104 (2012)

Localized tail state distribution in amorphous oxide transistors deduced from low temperature measurements Appl. Phys. Lett. 101, 113502 (2012)

Influence of the side-Ohmic contact processing on the polarization Coulomb field scattering in AlGaN/AlN/GaN heterostructure field-effect transistors Appl. Phys. Lett. 101, 113501 (2012)

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

### **ADVERTISEMENT**

# Structural properties and band offset determination of p-channel mixed As/Sb type-II staggered gap tunnel field-effect transistor structure

Y. Zhu,  $^1$  N. Jain,  $^1$  D. K. Mohata,  $^2$  S. Datta,  $^2$  D. Lubyshev,  $^3$  J. M. Fastenau,  $^3$  A. K. Liu,  $^3$  and M. K. Hudait  $^{1,a)}$

(Received 3 July 2012; accepted 28 August 2012; published online 12 September 2012)

The structural properties and band offset determination of p-channel staggered gap  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  heterostructure tunnel field-effect transistor (TFET) grown by molecular beam epitaxy (MBE) were investigated. High resolution x-ray diffraction revealed that the active layers are strained with respect to "virtual substrate." Dynamic secondary ion mass spectrometry confirmed an abrupt junction profile at the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  heterointerface and minimal level of intermixing between As and Sb atoms. The valence band offset of  $0.37 \pm 0.05 \, eV$  was extracted from x-ray photoelectron spectroscopy. A staggered band lineup was confirmed at the heterointerface with an effective tunneling barrier height of  $0.13 \, eV$ . Thus, MBE-grown staggered gap  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  TFET structures are a promising p-channel option to provide critical guidance for the future design of mixed As/Sb type-II based complementary logic and low power devices. ©  $2012 \, American \, Institute \, of \, Physics$ . [http://dx.doi.org/10.1063/1.4752115]

Tunnel field-effect transistors (TFETs) have attracted a great deal of attention owing to the gate-controlled band-toband-tunneling (BTBT) transport mechanism, which is expected to achieve subthreshold swing (SS) below the thermal limit of 60 mV/dec at 300 K, enabling transistor operation at voltages below 0.5 V.1-3 TFETs based on III-V materials will achieve higher ON-current (ION) compared to conventional Si TFETs due to the smaller band gap and lower effective carrier mass. 1,4,5 Among them, mixed As/Sb based heterojunction allows a wide range of staggered band alignments depending on the material compositions in source and channel layers. Moreover, an abrupt junction profile at the source/channel heterointerface, minimal intermixing between As and Sb atoms, and well controlled defects at this interface should be maintained. Recently, great efforts have been devoted to boost performance of mixed As/Sb staggered gap TFETs, such as improving  $I_{ON}^{\phantom{ON}4}$  and reducing OFF-state leakage (I<sub>OFF</sub>).<sup>6,7</sup> However, most of the researches were restricted to n-channel TFETs.<sup>6-8</sup> A study of highperformance p-channel TFET within the same material system is equally important, without which the energy efficient complementary logic circuits will not be realized. On the other hand, the band alignment, particularly the valence band offset (VBO), is critical to the performance of p-channel TFETs. 6-9 Proper band alignments at the source/ channel heterointerface would necessary to increase I<sub>ON</sub> without sacrificing I<sub>OFF</sub>. As a result, precise determination of band offset at the source/channel heterointerface will provide an important guidance to design TFET structure for further improvement of device performance at low voltage operation.

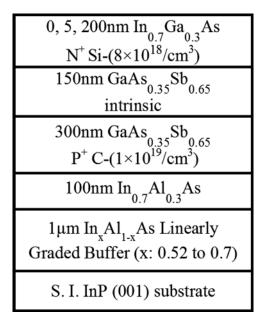

In this Letter, we demonstrate the experimental study of the structural properties and the band offset determination of a p-channel staggered gap In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterostructure TFET. The VBO at the heterointerface was determined from x-ray photoelectron spectroscopy (XPS) measurements. All p-channel TFET structures used for this work were grown by solid source molecular beam epitaxy (MBE), and Fig. 1 shows the schematic of such layer structures. The 5 nm In<sub>0.7</sub>Ga<sub>0.3</sub>As/450 nm GaAs<sub>0.35</sub>Sb<sub>0.65</sub> structure

FIG. 1. Schematic diagram of a p-channel TFET layer structure. 5 nm  $\rm In_{0.7}Ga_{0.3}As/450\,nm~GaAs_{0.35}Sb_{0.65}$  was used for the measurement of binding energy information at the heterointerface, while  $200\,nm~In_{0.7}Ga_{0.3}As/450\,nm~GaAs_{0.35}Sb_{0.65}$  and  $450\,nm~GaAs_{0.35}Sb_{0.65}$  without the top  $\rm In_{0.7}Ga_{0.3}As$  layer were used to measure the binding energy information of bulk  $\rm In_{0.7}Ga_{0.3}As$  and  $\rm GaAs_{0.35}Sb_{0.65}$ , respectively.

<sup>&</sup>lt;sup>1</sup>Bradley Department of Electrical and Computer Engineering, Virginia Tech, Blacksburg, Virginia 24061, USA

<sup>&</sup>lt;sup>2</sup>Electrical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802, USA <sup>3</sup>IQE Inc., Bethlehem, Pennsylvania 18015, USA

a) Author to whom correspondence should be addressed. Electronic mail: mantu.hudait@vt.edu. Tel.: (540) 231-6663. Fax: (540) 231-3362.

was used for the measurement of binding energy information at the heterointerface, while 200 nm  $In_{0.7}Ga_{0.3}As/450$  nm  $GaAs_{0.35}Sb_{0.65}$  and 450 nm  $GaAs_{0.35}Sb_{0.65}$  without the top  $In_{0.7}Ga_{0.3}As$  layer were used to measure the binding energy information of bulk  $In_{0.7}Ga_{0.3}As$  and  $GaAs_{0.35}Sb_{0.65}$ , respectively. XPS measurements were performed on a Phi Quantera Scanning XPS Microprobe instrument using a monochromatic Al  $K\alpha$  (1486.6 eV) x-ray source. A take-off angle of 45° and pass energy of 26 eV was used in all measurements. The binding energy was corrected by adjusting the carbon (C) 1s core level (CL) peak position to 285 eV for each sample surface. Curve fitting was done by the CasaXPS 2.3.14 using a Lorentzian convolution with a Shirley-type background.

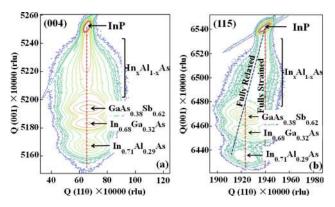

As shown in Fig. 1, due to the lattice constant difference between active layers (In<sub>0.7</sub>Ga<sub>0.3</sub>As and GaAs<sub>0.35</sub>Sb<sub>0.65</sub>) and the InP substrate, a linearly graded In<sub>x</sub>Al<sub>1-x</sub>As buffer was used to accommodate the lattice mismatch induced defects. Reciprocal space maps (RSMs) were obtained using Panalytical X'pert Pro system with Cu  $K\alpha$ -1 line focused x-ray source to determine the amount of strain relaxation and the layer compositions of the p-channel TFET structure. Figures 2(a) and 2(b) show RSMs for (004) and (115) reflections obtained from the structure containing 200 nm In<sub>0.7</sub>Ga<sub>0.3</sub>As, with the projection of incident x-ray beam along [110] direction. All layers with measured compositions were labeled to corresponding reciprocal space points (RLPs) in these figures. Using the out-of-plane and in-plane lattice constants extracted from Figs. 2(a) and 2(b), only 10% strain relaxation with respect to the In<sub>0.7</sub>Al<sub>0.3</sub>As "virtual substrate" was calculated in the In<sub>0.7</sub>Ga<sub>0.3</sub>As and GaAs<sub>0.35</sub>Sb<sub>0.65</sub> layers. The significantly lower strain relaxation value confirms the pseudomorphic nature of these two layers with respect to the In<sub>0.7</sub>Al<sub>0.3</sub>As "virtual substrate."

Engineering an abrupt change from Sb rich to As rich interface is necessary for type-II staggered band alignment. The change of group-V fluxes from Sb to As in the mixed anion GaAsSb to mixed cation InGaAs layers would introduce interface intermixing that leads to uncontrolled layer composition at the interface, resulting in the shift of band alignment. Dynamic secondary ion mass spectrometry (SIMS) was performed to determine the compositional

FIG. 2. Symmetric (004) and asymmetric (115) RSMs of the p-channel TFET structure with the projection of incident x-ray beam along [110] direction. Only 10% strain relaxation values in  $In_{0.7}Ga_{0.3}As$  and  $GaAs_{0.35}Sb_{0.65}$  layers were extracted from RSMs, indicating low defect density in this region.

profile of As, Sb, Ga, In, Si, and C atoms at the interface. SIMS analysis was performed using Cameca IMS-7f GEO with Cs<sup>+</sup> as primary ion beam. Figure 3(a) shows the Ga, In, As, and Sb depth profiles of the p-channel TFET structure. The depth profiles display an abrupt In<sub>0.7</sub>Ga<sub>0.3</sub>As/ GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface. The transition between  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  is less than 10 nm, within the sputter-induced broadening of the ion beam, indicating low value of As and Sb intermixing at the interface. On the other hand, a sharp doping concentration change at the source/ channel interface can reduce the tunneling width and increase the tunneling electric field, thereby improves the I<sub>ON</sub> and SS.<sup>4</sup> Figure 3(b) shows the Si and C doping profiles in the same p-channel TFET structure. It depicts an abrupt junction profile at the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> interface, suggesting a steep junction is formed at the heterointerface.

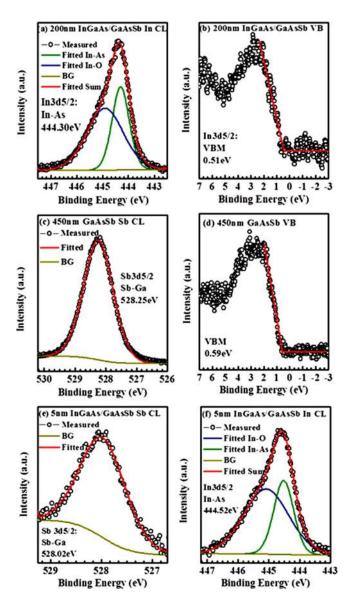

The valence band offset at the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  interface was determined with the method by Kraut *et al.*, <sup>10</sup>

$$\Delta E_{V} = \left(E_{Sb~3d_{5/2}}^{GaAsSb} - E_{VBM}^{GaAsSb}\right) - \left(E_{In~3d_{5/2}}^{InGaAs} - E_{VBM}^{InGaAs}\right) - \Delta E_{CL}(i)$$

$$\tag{1}$$

where  $E_{Sb\ 3d_{5/2}}^{GaAsSb}$  and  $E_{In\ 3d_{5/2}}^{InGaAs}$  are CL binding energies of Sb3d<sub>5/2</sub> and In3d<sub>5/2</sub>;  $E_{VBM}$  is the valence band maxima (VBM) of the corresponding samples.  $E_{VBM}$  was determined by linearly fitting the leading edge of the valence band (VB) spectrum to the base line.  $^{11}$  ( $E_{In\ 3d_{5/2}}^{InGaAs} - E_{VBM}^{InGaAs}$ ) and ( $E_{Sb\ 3d_{5/2}}^{GaAsSb} - E_{VBM}^{GaAsSb}$ ) were measured from 200 nm In<sub>0.7</sub>Ga<sub>0.3</sub> As/450 nm GaAs<sub>0.35</sub>Sb<sub>0.65</sub> and 450 nm GaAs<sub>0.35</sub>Sb<sub>0.65</sub> without the In<sub>0.7</sub>Ga<sub>0.3</sub>As overlayer, respectively.  $\Delta E_{CL}(i) = E_{Sb\ 3d5/2}^{GaAsSb}(i) - E_{In\ 3d5/2}^{InGaAs}(i)$  is the binding energy difference between Sb3d<sub>5/2</sub> and In3d<sub>5/2</sub> CLs measured at the

FIG. 3. (a) Dynamic SIMS depth profiles of Ga, In, As, and Sb of the TFET structure. An abrupt  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  interface with a transition between  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  of less than 10 nm was confirmed, indicating low level of As and Sb intermixing at the interface; (b) doping concentration profiles of Si in the  $n^+$  source and C in the  $p^+$  drain region. An abrupt junction profile at the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  interface suggests a formation of steep junction.

heterointerface from 5 nm In<sub>0.7</sub>Ga<sub>0.3</sub>As/450 nm GaAs<sub>0.35</sub> Sb<sub>0.65</sub> sample. The CL and VB spectra from each sample were shown in Figs. 4(a)-4(f). In order to improve accuracy of the measured binding energy information, high resolution measurements with a step-size of 0.025 eV was performed to resolve the spin-orbit splitting of In and Sb 3d peaks. Curve fitting was done on each CL spectra to separate In-As and Sb-Ga bonds from the In-O and Sb-O bonds. The measured binding energy of In-O and Sb-O bonds was about 444.90 eV and 530 eV, respectively, which were in agreement with the reported values. 12,13 The binding energy difference between Sb-O and Sb-Ga bonds are large enough to resolve the Sb-O bond as a separated peak (not shown in Fig. 4) from Sb-Ga spectrum. As a result, unlike In3d<sub>5/2</sub> CL spectrum, which was a combination of In-As and In-O bonds, the measured Sb3d<sub>5/2</sub> CL peak was Lorentzian shape without curve fitting.

FIG. 4. XPS spectra of (a)  $In3d_{5/2}$  CL and (b) valence band (VB) from  $200\,\mathrm{nm}$   $In_{0.7}Ga_{0.3}As/150\,\mathrm{nm}$   $GaAs_{0.35}Sb_{0.65}$  sample; (c)  $Sb3d_{5/2}$  CL and (d) VB from  $150\,\mathrm{nm}$   $GaAs_{0.35}Sb_{0.65}$  without the top  $In_{0.7}Ga_{0.3}As$  layer; (e)  $Sb3d_{5/2}$  CL and (f)  $In3d_{5/2}$  CL from  $5\,\mathrm{nm}$   $In_{0.7}Ga_{0.3}As/150\,\mathrm{nm}$   $GaAs_{0.35}Sb_{0.65}$  measured at the interface. CL spectra curves were fitted using a Lorentzian convolution with a Shirley-type background. VBM were determined by linear extrapolation of the leading edge of VB spectra to the base line.

All measured binding energy values are summarized in Table. I. The values of  $(E_{In}^{InGaAs} - E_{VBM}^{InGaAs})$  and  $(E_{Sb}^{GaAsSb} - E_{VBM}^{InGaAs})$  and  $(E_{Sb}^{GaAsSb} - E_{VBM}^{InGaAs})$  were found to be 443.79 eV and 527.66 eV, respectively. The VBO of  $In_{0.7}Ga_{0.3}As$  source relative to  $GaAs_{0.35}Sb_{0.65}$  channel from the Eq. (1) is  $\Delta E_v = 0.37 \pm 0.05$  eV. The uncertainty value 0.05 eV is due to the scatter of VB with respect to the fitting in VBM position.

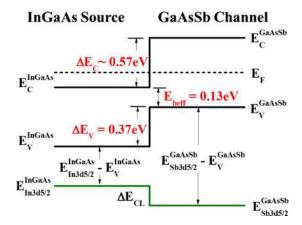

The conduction band offset (CBO) can be calculated from the following equation, <sup>11</sup>

$$\Delta E_C = E_g^{GaAsSb} + \Delta E_V - E_g^{InGaAs}, \tag{2}$$

where,  $E_g^{GaAsSb}$  and  $E_g^{InGaAs}$  are the band gaps of GaAs<sub>0.35</sub> Sb<sub>0.65</sub> and In<sub>0.7</sub>Ga<sub>0.3</sub>As, respectively. The bandgap of intrinsic GaAs<sub>0.35</sub>Sb<sub>0.65</sub> at 300 K was found to be 0.70 eV by the commonly used empirical law. <sup>14</sup> The bandgap of heavily doped In<sub>0.7</sub>Ga<sub>0.3</sub>As was determined to be 0.50 eV using the experimental measured bandgap of intrinsic In<sub>0.7</sub>Ga<sub>0.3</sub>As <sup>15</sup> and by considering the band gap narrowing (BGN) effect caused by heavily Si doping. <sup>16,17</sup> Using these results, the CBO of In<sub>0.7</sub>Ga<sub>0.3</sub>As with respect to GaAs<sub>0.35</sub>Sb<sub>0.65</sub> was calculated to be  $\Delta$ E<sub>C</sub>  $\sim$  0.57 eV.

The strain relaxation of the active layers (In<sub>0.7</sub>Ga<sub>0.3</sub>As/ GaAs<sub>0.35</sub>Sb<sub>0.65</sub>) of the p-channel heterojunction TFET structures is only limited to 10% with respect to the uppermost layer ( $In_{0.7}Al_{0.3}As$ ) of the linearly graded  $In_xAl_{1-x}As$  buffer. These active layers are considered to be strained or near lattice matched with respect to the "virtual substrate." However, the active layers are about 1.1% lattice mismatched to InP substrate and the measured strain relaxation was  $\sim 80\%$  relative to InP substrate. The 1.1% lattice mismatch was mitigated by the linearly graded In<sub>x</sub>Al<sub>1-x</sub>As (x = 0.52 to 0.7) buffer starting with the lattice matched composition of In<sub>0.52</sub>Al<sub>0.48</sub>As to InP and ending with In<sub>0.7</sub> Al<sub>0.3</sub>As, which is closely internal lattice matched to In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers. Growing of such In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> p-channel TFET structure on Si will be lattice mismatched with respect to Si substrate, however, the active layers (In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub>) and the uppermost layer (In<sub>0.7</sub>Al<sub>0.3</sub>As) of In<sub>x</sub>Al<sub>1-x</sub>As graded buffer will also be closely internal lattice matched. Thus, the entire p-channel TFET on Si will be considered as "metamorphic" (fully or partially relaxed) structure and the active layers will be either pseudomorphic (strained) or latticed matched. In the past, the In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well FET has been demonstrated on Si where the entire structure was metamorphic while the active layers were pseudomorphic.<sup>18</sup> Thus, the value of valence band offset will not once the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$ change, p-channel tunnel FET structures are grown on Si.

Figure 5 shows the schematic band alignment based on the band gap energy values determined above and the experimental result of  $\Delta E_V$  measured by XPS. One can find that a type-II band alignment was formed at the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface. An effective tunneling barrier height ( $E_{beff} = E_g^{InGaAs} - \Delta E_V$ ) of 0.13 eV was extracted from the present result. This effective tunneling barrier height plays a significant role on the performance of either n-channel or p-channel TFETs, which not only determines the ON-state BTBT rate but also sets the blocking barrier for

TABLE I. XPS core level spectra results after curve fitting and VBM positions obtained by linear extrapolation of the leading edge to the extended base line of the valence band spectra.

| Sample                                                | States              | Binding<br>Energy (eV) | Bonding |

|-------------------------------------------------------|---------------------|------------------------|---------|

| 200 nm In <sub>0.7</sub> Ga <sub>0.3</sub> As/ 450 nm | In3d <sub>5/2</sub> | 444.30                 | In-As   |

| GaAs <sub>0.35</sub> Sb <sub>0.65</sub>               | In3d <sub>5/2</sub> | 444.90                 | In-O    |

|                                                       | VBM                 | 0.51                   | _       |

| 450 nm GaAs <sub>0.35</sub> Sb <sub>0.65</sub>        | Sb3d <sub>5/2</sub> | 528.25                 | Sb-Ga   |

|                                                       | Sb3d <sub>5/2</sub> | 530                    | Sb-O    |

|                                                       | VBM                 | 0.59                   | _       |

| 5 nm In <sub>0.7</sub> Ga <sub>0.3</sub> As/ 450 nm   | Sb3d <sub>5/2</sub> | 528.02                 | Sb-Ga   |

| GaAs <sub>0.35</sub> Sb <sub>0.65</sub>               | In3d <sub>5/2</sub> | 444.52                 | In-As   |

|                                                       | In3d <sub>5/2</sub> | 445.07                 | In-O    |

FIG. 5. Schematic energy-band diagram of the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  heterointerface of a p-channel TFET structure. A type-II staggered band lineup with an effective barrier height of  $0.13\,eV$  was determined at the heterointerface.

OFF-state leakage. 1,6,7 In order to increase I<sub>ON</sub> and improve the switching efficiency, a reduced energy barrier for tunneling is required.<sup>6,8,9</sup> Large increase in BTBT current has been measured in type-II mixed As/Sb staggered gap TFETs by reducing E<sub>beff.</sub> 6,8 However, if E<sub>beff</sub> is reduced to a negative value, a broken band lineup will be formed at the heterointerface. Although a broken band alignment yields better ONstate performance, the increase in I<sub>OFF</sub> becomes another roadblock for boosting the performance of TFET devices. In that case, an additional gate bias is required to turn off this tunneling mechanism. 19 As a result, the E<sub>beff</sub> value should be well optimized to guarantee high performance operation for both ON and OFF states in a p-channel or n-channel TFET structure. It has been reported that high  $I_{ON}$  of 135  $\mu$ A/ $\mu$ m with high  $I_{ON}/I_{OFF}$  ratio of  $2.7 \times 10^4$  ( $V_{DS} = 0.5 \text{ V}$ , and  $V_{ON} - V_{OFF} = 1.5 \text{ V}$ ) was achieved using the similar device structure for n-channel TFET,6 indicating promising device performance is expected in the structure studied here for complementary p-channel TFET application.

In conclusion, the experimental determination of structural properties and valence band offset of a p-channel

In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterostructure tunnel FET grown by MBE was investigated. Symmetric (004) and asymmetric (115) reciprocal space maps demonstrated the strain relaxation of the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  active layers is limited to only 10% with respect to the upper most layer  $(In_{0.7}Al_{0.3}As)$  of the graded  $In_xAl_{1-x}As$  buffer. Dynamic SIMS measurement confirmed a low level intermixing between As and Sb atoms as well as an abrupt junction profile at the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface. A valence band offset of  $0.37 \pm 0.05 \, \text{eV}$  at In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface was obtained from XPS measurements. The corresponding conduction band offset of ~0.57 eV was calculated using bandgaps of GaAs<sub>0.35</sub>Sb<sub>0.65</sub> and In<sub>0.7</sub>Ga<sub>0.3</sub>As. A type-II band lineup was formed at the heterointerface with an effective tunneling barrier height of 0.13 eV. Knowledge of band alignment parameters, especially the valence band offset and effective tunneling barrier height of In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterojunction, is believed to facilitate the design of mixed As/Sb staggered gap p-channel tunnel FETs for ultra-low power applications.

This work is supported in part by National Science Foundation under Grant No. ECCS-1028494 and Intel Corporation.

<sup>1</sup>J. Knoch and J. Appenzeller, IEEE Electron Device Lett. **31**, 305 (2010).

<sup>2</sup>R. Gandhi, C. Zhixian, N. Singh, K. Banerjee, and L. Sungjoo, IEEE Electron Device Lett. **32**, 437 (2011).

<sup>3</sup>A. M. Ionescu and H. Riel, Nature (London) **479**, 329 (2011).

<sup>4</sup>H. Zhao, Y.-T. Chen, Y. Wang, F. Zhou, F. Xue, and J. C. Lee, Appl. Phys. Lett. **98**, 093501 (2011).

<sup>5</sup>S. Datta, in *Proceedings of 66th IEEE Device Research Conference* (2008), p. 33.

<sup>6</sup>D. K. Mohata, R. Bijesh, Y. Zhu, M. K. Hudait, R. Southwick, Z. Chbili, D. Gundlach, J. Suehle, J. M. Fastenau, D. Loubychev, A. K. Liu, T. S. Mayer, V. Narayanan, and S. Datta, Dig. Tech. Pap—Symp. VLSI Technol. **2012**, 53.

<sup>7</sup>Y. Zhu, N. Jain, S. Vijayaraghavan, D. K. Mohata, S. Datta, D. Lubyshev, J. M. Fastenau, W. K. Liu, N. Monsegue, and M. K. Hudait, J. Appl. Phys. **112**, 024306 (2012).

<sup>8</sup>D. K. Mohata, R. Bijesh, S. Mujumdar, C. Eaton, R. Engel-Herbert, T. Mayer, V. Narayanan, J. M. Fastenau, D. Loubychev, A. K. Liu, and S. Datta, Tech. Dig.—Int. Electron Devices Meet. **2011**, 781.

<sup>9</sup>O. M. Nayfeh, C. N. Chleirigh, J. Hennessy, L. Gomez, J. L. Hoyt, and D. A. Antoniadis, IEEE Electron Device Lett. **29**, 1074 (2008).

<sup>10</sup>E. A. Kraut, R. W. Grant, J. R. Waldrop, and S. P. Kowalczyk, Phys. Rev. Lett. 44, 1620 (1980).

<sup>11</sup>M. Kumar, M. K. Rajpalke, B. Roul, T. N. Bhat, A. T. Kalghatgi, and S. B. Krupanidhi, Phys. Status Solidi B 249, 58 (2012).

<sup>12</sup>A. W. C. Lin, N. R. Armstrong, and T. Kuwana, Anal. Chem. 49, 1228 (1977)

<sup>13</sup>C. D. Wagner, Faraday Discuss. **60**, 291 (1975).

<sup>14</sup>R. E. Nahory, M. A. Pollack, J. C. Dewinter, and K. M. Williams, J. Appl. Phys. 48, 1607 (1977).

<sup>15</sup>M. K. Hudait, Y. Lin, M. N. Palmisiano, and S. A. Ringel, IEEE Electron Device Lett. 24, 538 (2003).

<sup>16</sup>S. C. Jain and D. J. Roulston, Solid State Electron. **34**, 453 (1991).

<sup>17</sup>W.-S. Cho, M. Luisier, D. Mohata, S. Datta, D. Pawlik, S. L. Rommel, and G. Klimeck, Appl. Phys. Lett. **100**, 063504 (2012).

<sup>18</sup>M. K. Hudait, G. Dewey, S. Datta, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, R. Pillarisetty, W. Rachmady, M. Radosavljevic, T. Rakshit, and R. Chau, Tech. Dig.—Int. Electron Devices Meet. 2007, 625.

<sup>19</sup>S. O. Koswatta, S. J. Koester, and W. Haensch, Tech. Dig.—Int. Electron Devices Meet. 2009, 909.