Helsinki University of Technology Department of Signal Processing and Acoustics Espoo 2008

Report 5

# STUDIES ON HIGH-SPEED HARDWARE IMPLEMENTATION OF CRYPTOGRAPHIC ALGORITHMS

Kimmo Järvinen

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Faculty of Electronics, Communications and Automation for public examination and debate in Auditorium S1 at Helsinki University of Technology (Espoo, Finland) on the 21st of November, 2008, at 12 noon.

Helsinki University of Technology Faculty of Electronics, Communications and Automation Department of Signal Processing and Acoustics

Teknillinen korkeakoulu Elektroniikan, tietoliikenteen ja automaation tiedekunta Signaalinkäsittelyn ja akustiikan laitos Distribution: Helsinki University of Technology Department of Signal Processing and Acoustics P.O. Box 3000 FIN-02015 HUT Tel. +358-9-451 3211 Fax. +358-9-452 3614 E-mail: Mirja.Lemetyinen@hut.fi

© Kimmo Järvinen

ISBN 978-951-22-9589-0 (Printed) ISBN 978-951-22-9590-6 (Electronic) ISSN 1797-4267

Multiprint Oy Espoo 2008

| ABSTRACT OF DOCTORAL DISSERTATION                                                                 | HELSINKI UNIVERSITY OF TECHNOLOGY<br>P.O. BOX 1000, FI-02015 TKK<br>http://www.tkk.fi |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Author                                                                                            |                                                                                       |

| Name of the dissertation                                                                          |                                                                                       |

| Manuscript submitted                                                                              | Manuscript revised                                                                    |

| Date of the defence                                                                               |                                                                                       |

| Monograph                                                                                         | Article dissertation (summary + original articles)                                    |

| Faculty<br>Department<br>Field of research<br>Opponent(s)<br>Supervisor<br>Instructor<br>Abstract |                                                                                       |

| Keywords                                                                                          |                                                                                       |

| ISBN (printed)                                                                                    | ISSN (printed)                                                                        |

| ISBN (pdf)                                                                                        | ISSN (pdf)                                                                            |

| Language                                                                                          | Number of pages                                                                       |

| Publisher                                                                                         | !                                                                                     |

| Print distribution                                                                                |                                                                                       |

| The dissertation can be read at http://lib.tkk.fi/Dis                                             | 3S/                                                                                   |

| VÄITÖSKIRJAN TIIVISTELMÄ                                | TEKNILLINEN KORKEAKOULU<br>PL 1000, 02015 TKK<br>http://www.tkk.fi |

|---------------------------------------------------------|--------------------------------------------------------------------|

| Tekijä                                                  |                                                                    |

| Väitöskirjan nimi                                       |                                                                    |

|                                                         |                                                                    |

| Käsikirjoituksen päivämäärä                             | Korjatun käsikirjoituksen päivämäärä                               |

| Väitöstilaisuuden ajankohta                             |                                                                    |

| Monografia                                              | Yhdistelmäväitöskirja (yhteenveto + erillisartikkelit)             |

| Tiedekunta                                              |                                                                    |

| Laitos                                                  |                                                                    |

| Tutkimusala                                             |                                                                    |

| Vastaväittäjä(t)                                        |                                                                    |

| Työn valvoja                                            |                                                                    |

| Työn ohjaaja                                            |                                                                    |

| Tiivistelmä                                             |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

| Asiasanat                                               |                                                                    |

| ISBN (painettu)                                         | ISSN (painettu)                                                    |

| ISBN (pdf)                                              | ISSN (pdf)                                                         |

| Kieli                                                   | Sivumäärä                                                          |

| Julkaisija                                              |                                                                    |

| Painetun väitöskirjan jakelu                            |                                                                    |

| Luettavissa verkossa osoitteessa http://lib.tkk.fi/Diss | s/                                                                 |

### Acknowledgments

THE RESEARCH WORK for this thesis was carried out in the Department of Signal Processing and Acoustics (formerly, Signal Processing Laboratory), Helsinki University of Technology (TKK). First of all, I would like to thank my supervisor, Prof. Jorma Skyttä, for the support he gave me during these years. He always took care of the ever-increasing university bureaucracy and let me concentrate almost 100%-ly to my research work, which I greatly appreciate. Sincere thanks go also to Dr. Matti Tommiska for patient guidance in the early phases of this work.

The pre-examiners of this thesis, Dr. Panu Hämäläinen and Dr. Toomas P. Plaks, are greatly acknowledged for insightful comments which, I believe, helped me to improve the manuscript of this thesis significantly.

I had the privilege of being in the Graduate School of Electronics, Telecommunications and Automation (GETA) from 2004 to 2008. I thank former director of GETA, Prof. Iiro Hartimo, current director, Prof. Ari Sihvola, and coordinator, Marja Leppäharju, for making GETA such an exemplary graduate school. Without GETA's support making of this thesis would have been much more difficult, or perhaps impossible.

Signal Processing Laboratory was always a nice place to work. The thanks for that go to everyone who have worked there over the years, but I would like to thank, especially, Juha Forsten, Antti Hämäläinen, Jaakko Kairus, Esa Korpela, Pekka Korpinen, Keijo Länsikunnas, Dr. Jarno Martikainen, Sampo Ojala, Taneli Riihonen, Dr. Matti Rintamäki, Kati Tenhonen, and Dr. Matti Tommiska. Also, I express my gratitude to the laboratory's former secretary, Anne Jääskeläinen, and secretary, Mirja Lemetyinen, because they never hesitated to help me in various practical problems.

GETA, Prof. Graham Jullien, and Prof. Vassil Dimitrov arranged me an opportunity to visit the ATIPS Lab at the University of Calgary, Canada, for three months period in autumn 2005. It is hard to exaggerate the importance of this visit for my thesis work, and I am therefore most grateful for this wonderful opportunity that I had. Especially, I would like to thank Prof. Dimitrov, Prof. Michael Jacobson, Jr., Dr. Laurent Imbert, Dr. Zhun Huang, and Andy Chan, with whom I had the pleasure of working during my short stay in Calgary.

Since June 2008, I have been affiliated with the Department of Information and Computer Science at TKK. I would like to thank everyone there for warmly welcoming me. In particular, I thank my new boss, Prof. Kaisa Nyberg, for giving me time to finalize this thesis, and Billy Bob Brumley for fruitful cooperation that started already long before I joined the department. He also deserves thanks for commenting the manuscript of this thesis.

The research work was financed by GETA and two projects: GO-SEC (2003–2005), financed by Tekes and several Finnish telecommunication companies, and PLA (2006–2008), financed entirely by Tekes. My doctoral thesis work was financially supported also by the Nokia Foundation, Emil Aaltosen säätiö, Tekniikan edistämissäätiö (TES), and Elektroniikkainsinöörien säätiö, and I greatly appreciate their generosity.

Finally, I would like to thank those who, although without having a direct effect on my research work, have influenced the outcome of this work in many other ways. Therefore, I thank my parents, brothers, and sister for providing me a solid background and always supporting me in everything I have chosen to do in my life. My warmest thanks go to Hanna for love, encouragement, and support she has given me over the years.

Espoo, October 2008

Kimmo Järvinen

# Table of Contents

| A  | ckno                                    | wledgments                                                                                                                                                                                                                                                                                                                                                                  | i                                                                                                                                                         |

|----|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ta | able                                    | of Contents                                                                                                                                                                                                                                                                                                                                                                 | iii                                                                                                                                                       |

| Li | st of                                   | Publications                                                                                                                                                                                                                                                                                                                                                                | vii                                                                                                                                                       |

| Li | st of                                   | Abbreviations                                                                                                                                                                                                                                                                                                                                                               | ix                                                                                                                                                        |

| Li | st of                                   | Symbols                                                                                                                                                                                                                                                                                                                                                                     | xi                                                                                                                                                        |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | roduction         Motivation for the Thesis         Scope of the Thesis         Contributions of the Thesis         Structure of the Thesis         Summary of Publications and Author's Contribution                                                                                                                                                                       | <b>1</b><br>1<br>2<br>3<br>5<br>5                                                                                                                         |

| 2  | <b>Ove</b> 2.1<br>2.2<br>2.3            | Prview of CryptographySecret-key Cryptography2.1.1Data Encryption Standard (DES)2.1.2Advanced Encryption Standard (AES)Public-key Cryptography2.2.1Diffie-Hellman Key Exchange2.2.2RSA Cryptosystems2.2.3ElGamal Cryptosystems2.2.4Digital Signature Algorithm (DSA)2.2.5Elliptic Curve Cryptosystems2.2.6On Difficulties of the Hard ProblemsCryptographic Hash Algorithms | <ol> <li>9</li> <li>11</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>14</li> <li>15</li> <li>15</li> <li>17</li> <li>17</li> </ol> |

| 3  | <b>Har</b><br>3.1                       | rdware Implementation of Cryptographic Algorithms         Implementation Platforms         3.1.1       General-Purpose Processors         3.1.2       Application Specific Integrated Circuits (ASICs)         3.1.3       Low-Cost Environments                                                                                                                            | <b>21</b><br>22<br>23<br>24<br>24                                                                                                                         |

|          | 3.2  | Field Programmable Gate Arrays (FPGAs) 24                                                                                            |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------|

|          |      | 3.2.1 Modern FPGAs and Recent Trends                                                                                                 |

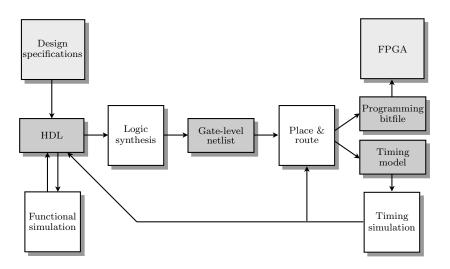

|          |      | 3.2.2 FPGA Design Flow                                                                                                               |

|          |      | 3.2.3 Cryptographic Algorithms in FPGAs                                                                                              |

|          |      | 3.2.4 Comparisons                                                                                                                    |

|          | 3.3  | Metrics for Evaluating Implementations                                                                                               |

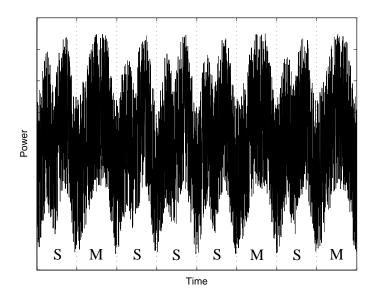

|          | 3.4  | Side-Channel Attacks                                                                                                                 |

|          |      |                                                                                                                                      |

| 4        | Fini | te Fields 35                                                                                                                         |

|          | 4.1  | Preliminaries                                                                                                                        |

|          | 4.2  | Prime Fields                                                                                                                         |

|          | 4.3  | Binary Fields                                                                                                                        |

|          |      | 4.3.1 Polynomial Basis                                                                                                               |

|          |      | 4.3.2 Normal Basis                                                                                                                   |

|          | 4.4  | Inversion                                                                                                                            |

|          | 4.5  | Notes on Implementations                                                                                                             |

|          |      |                                                                                                                                      |

| <b>5</b> | Adv  | vanced Encryption Standard 47                                                                                                        |

|          | 5.1  | Description of AES                                                                                                                   |

|          |      | 5.1.1 Decryption $\dots \dots \dots$ |

|          | 5.2  | Implementation of AES 49                                                                                                             |

|          |      | 5.2.1 Memory-based Implementations                                                                                                   |

|          |      | 5.2.2 Combinatorial Implementations                                                                                                  |

|          | 5.3  | Literature Review of AES Implementations                                                                                             |

|          |      | 5.3.1 ASIC Implementations                                                                                                           |

|          |      | 5.3.2 FPGA Implementations                                                                                                           |

|          |      | 5.3.3 Comparisons                                                                                                                    |

| _        |      |                                                                                                                                      |

| 6        | -    | ptic Curve Cryptography 61                                                                                                           |

|          | 6.1  | Preliminaries                                                                                                                        |

|          | 6.2  | Arithmetic on Elliptic Curves                                                                                                        |

|          |      | 6.2.1 Affine Coordinates                                                                                                             |

|          |      | 6.2.2 Standard Projective Coordinates                                                                                                |

|          |      | 6.2.3 López-Dahab Coordinates                                                                                                        |

|          | 6.3  | Elliptic Curve Point Multiplication                                                                                                  |

|          |      | 6.3.1 Methods with Precomputations                                                                                                   |

|          |      | 6.3.2 Multiple Point Multiplication                                                                                                  |

|          |      | Koblitz Curves                                                                                                                       |

|          | 6.5  | Literature Review of ECC Implementations                                                                                             |

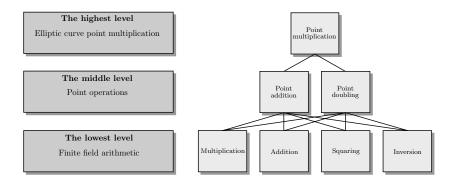

|          |      | 6.5.1 Typical Structure of ECC Processors                                                                                            |

|          |      | 6.5.2 Parallelism in ECC Processors                                                                                                  |

|          |      | 6.5.3 Flexibility of ECC Processors                                                                                                  |

|          |      | 6.5.4 Optimizations for Specific Curves or Algorithms 82                                                                             |

|          |      | 6.5.5 Comparisons                                                                                                                    |

| -        | ъ    |                                                                                                                                      |

| 7        | Res  |                                                                                                                                      |

|          | 7.1  | AES-related Contributions                                                                                                            |

|          |      | 7.1.1 AES Surveys                                                                                                                    |

|          |      | 7.1.2 Fast AES Implementation                                                                                                        |

|          | 7.2  | ECC-related Contributions                                                                                                            |

|                           | 7.2.1      | ECC Implementations for General Curves    | 86  |

|---------------------------|------------|-------------------------------------------|-----|

|                           | 7.2.2      | Utilizing Parallelism with Koblitz Curves | 87  |

|                           | 7.2.3      | Efficient Converters for Koblitz Curves   | 87  |

|                           | 7.2.4      | Adaptation of the DBNS to Koblitz Curves  | 88  |

| 8                         | Conclusion | ns                                        | 89  |

| Bibliography 93           |            |                                           | 93  |

| Errata of Publications 12 |            |                                           | 121 |

### List of Publications

This thesis consists of an overview and of the following publications which are referred to in the text by their Roman numerals.

- I. Kimmo Järvinen, Matti Tommiska and Jorma Skyttä, "Comparative Survey of High-Performance Cryptographic Algorithm Implementations on FPGAs," *IEE Proceedings: Information Security*, vol. 152, no. 1, Oct. 2005, pp. 3–12.

- II. Kimmo U. Järvinen, Matti T. Tommiska and Jorma O. Skyttä, "A Fully Pipelined Memoryless 17.8 Gbps AES-128 Encryptor," in *Proceedings of* the 11th ACM International Symposium on Field-Programmable Gate Arrays, FPGA 2003, Monterey, California, USA, Feb. 23–25, 2003, pp. 207-215.

- III. Kimmo Järvinen, Matti Tommiska and Jorma Skyttä, "A Scalable Architecture for Elliptic Curve Point Multiplication," in *Proceedings of the* 2004 IEEE International Conference on Field-Programmable Technology, FPT 2004, Brisbane, Queensland, Australia, Dec. 6–8, 2004, pp. 303-306.

- IV. Kimmo Järvinen and Jorma Skyttä, "On Parallelization of High-Speed Processors for Elliptic Curve Cryptography," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 16, no. 9, Sep. 2008, pp. 1162–1175.

- V. Kimmo Järvinen, Juha Forsten and Jorma Skyttä, "FPGA Design of Self-certified Signature Verification on Koblitz Curves," in *Proceedings of* the Workshop on Cryptographic Hardware and Embedded Systems, CHES 2007, Vienna, Austria, Sep. 10–13, 2007, Lecture Notes in Computer Science, vol. 4727, Springer, pp. 256-271.

- VI. Kimmo Järvinen and Jorma Skyttä, "Fast Point Multiplication on Koblitz Curves: Parallelization Method and Implementations," *Microprocessors* and *Microsystems*, in press, 11 pages.

- VII. Kimmo U. Järvinen and Jorma O. Skyttä, "High-Speed Elliptic Curve Cryptography Accelerator for Koblitz Curves," in *Proceedings of IEEE*

International Symposium on Field-programmable Custom Computing Machines, FCCM 2008, Stanford, California, USA, Apr. 14–15, 2008, in press, 10 pages.

- VIII. Kimmo Järvinen, Juha Forsten and Jorma Skyttä, "Efficient Circuitry for Computing τ-adic Non-Adjacent Form," in Proceedings of the 13th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2006, Nice, France, Dec. 10–13, 2006, pp. 232-235.

- IX. Billy Bob Brumley and Kimmo Järvinen, "Koblitz Curves and Integer Equivalents of Frobenius Expansions" in *Revised Selected Papers of the* 14th Annual Workshop on Selected Areas in Cryptography, SAC 2007, Ottawa, Ontario, Canada, Aug. 16–17, 2007, Lecture Notes in Computer Science, vol. 4876, Springer, pp. 126-137.

- X. V.S. Dimitrov, K.U. Järvinen, M.J. Jacobson, Jr., W.F. Chan, and Z. Huang, "FPGA Implementation of Point Multiplication on Koblitz Curves Using Kleinian Integers," in *Proceedings of the Workshop on Cryptographic Hardware and Embedded Systems, CHES 2006*, Yokohama, Japan, Oct. 10–13, 2006, Lecture Notes in Computer Science, vol. 4249, Springer, pp. 445-459.

- XI. Vassil S. Dimitrov, Kimmo U. Järvinen, Michael J. Jacobson, Jr., Wai Fong (Andy) Chan and Zhun Huang, "Provably Sublinear Point Multiplication on Koblitz Curves and Its Hardware Implementation," *IEEE Transactions on Computers*, vol. 57, no. 11, Nov. 2008, pp. 1469–1481.

# List of Abbreviations

| 3DES    | Triple-DES                                   |

|---------|----------------------------------------------|

| AES     | Advanced Encryption Standard                 |

| AES-128 | AES with a 128-bit key                       |

| AES-192 | AES with a 192-bit key                       |

| AES-256 | AES with a 256-bit key                       |

| ALM     | Adaptive Logic Module                        |

| ALU     | Arithmetic Logic Unit                        |

| ALUT    | Adaptive Look-Up Table                       |

| ANSI    | American National Standards Institute        |

| ASIC    | Application Specific Integrated Circuit      |

| CBC     | Cipher Block Chaining                        |

| CHES    | Cryptographic Hardware and Embedded Systems  |

| CLB     | Configurable Logic Block                     |

| CMOS    | Complementary Metal Oxide Semiconductor      |

| CPLD    | Complex Programmable Logic Device            |

| CTR     | CounTeR                                      |

| DBNS    | Double-Base Number System                    |

| DES     | Data Encryption Standard                     |

| DLP     | Discrete Logarithm Problem                   |

| DoS     | Denial-of-Service                            |

| DPA     | Differential Power Analysis                  |

| DSA     | Digital Signature Algorithm                  |

| DSP     | Digital Signal Processing / Processor        |

| ECB     | Electronic Code Book                         |

| ECC     | Elliptic Curve Cryptography                  |

| ECDLP   | Elliptic Curve Discrete Logarithm Problem    |

| ECDSA   | Elliptic Curve Digital Signature Algorithm   |

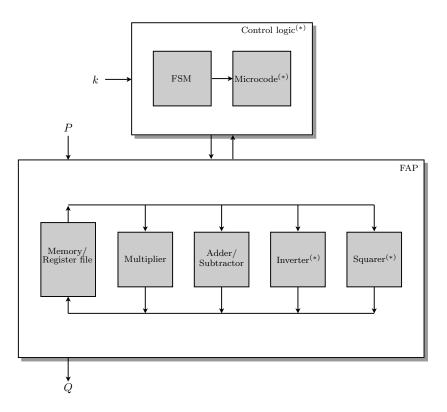

| FAP     | Field Arithmetic Processor                   |

| FCCM    | Field-programmable Custom Computing Machines |

| FIPS    | Federal Information Processing Standard      |

| FPGA    | Field Programmable Gate Array                |

| FSM     | Finite State Machine                         |

| gcd     | Greatest Common Divisor                      |

| GCM     | Galois Counter Mode                          |

| GLV     | Gallant, Lambert, and Vanstone               |

|         |                                              |

- GNB Gaussian Normal Basis Hardware Description Language HDL HECC Hyper-Elliptic Curve Cryptography IDEA International Data Encryption Algorithm IEEE Institute of Electrical and Electronics Engineers IFP Integer Factorization Problem JSF Joint Sparse Form LAB Logic Array Block lsbLeast Significant Bit Look-Up Table LUT MD Message Digest Most Significant Bit msb NAF Non-Adjacent Form  $NAF_w$ Width-w Non-Adjacent Form NBS National Bureau of Standards NIST National Institute of Standards and Technology NSA National Security Agency ONB **Optimal Normal Basis** PAL Programmable Array Logic PLA Packet Level Authentication / Programmable Logic Array RACE Research and development in Advanced Communications technologies in Europe Random Access Memory RAM RFID Radio Frequency IDentification RIPEMD **RACE** Integrity Primitives Evaluation MD RISC Reduced Instruction Set Computer ROM Read-Only Memory RSA Rivest, Shamir, and Adleman Secure Hash Algorithm SHA Simple Power Analysis SPA Substitution-Permutation Network SPN SSL Secure Sockets Layer VHDL Very high speed integrated circuit HDL XOR eXclusive-OR  $\tau JSF$  $\tau$ -adic Joint Sparse Form  $\tau \text{NAF}$  $\tau$ -adic Non-Adjacent Form

- $\tau \operatorname{NAF}_w$  Width- $w \tau$ -adic Non-Adjacent Form

# List of Symbols

| *                                                                              | Binary operation                                                            |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| $\otimes$                                                                      | Bitwise logical and operation (AND)                                         |

| $\oplus$                                                                       | Bitwise logical exclusive-or operation (XOR)                                |

| [.]                                                                            | The largest smaller or equal integer                                        |

| [.]                                                                            | The smallest larger or equal integer                                        |

| $(\cdot)^{-1}$                                                                 | Inverse                                                                     |

| $ \begin{bmatrix} \cdot \\ \cdot \end{bmatrix}^{-1} \\ \langle \cdot \rangle $ | Bit string notation                                                         |

| $\langle \cdot \rangle_x$                                                      | Hexadecimal notation                                                        |

| $a, \ldots, e$                                                                 | Elements of groups, rings, fields, and vector spaces                        |

| $a_1, a_2, a_3, a_4, a_6$                                                      | Curve parameters                                                            |

| $a_1, a_2, a_3, a_4, a_6$<br>$a(x), \ldots, d(x)$                              | Elements of $\mathbb{F}_{2^m}$ with polynomial basis                        |

| $A, \ldots, J$                                                                 | Temporary variables of point operations in $\mathcal{P}$ and $\mathcal{LD}$ |

| A                                                                              | Addition                                                                    |

| $\mathcal{A}$                                                                  | Affine coordinates                                                          |

| $\operatorname{AddRoundKey}(\cdot, \cdot)$                                     | Round key mixing transformation of the AES                                  |

| C                                                                              | Ciphertext                                                                  |

| d                                                                              | Exponent used in decryption                                                 |

| $d_N$                                                                          | Number of ones in a multiplication matrix                                   |

| $d_K(\cdot)$                                                                   | Decryption function with a key $K$                                          |

| D                                                                              | Multiplier digit-size                                                       |

| $D_i$                                                                          | Data after round $i$ in block ciphers                                       |

| $\deg(\cdot)$                                                                  | Degree of                                                                   |

| e                                                                              | Exponent used in encryption                                                 |

| $e_K(\cdot)$                                                                   | Encryption function with a key $K$                                          |

| E                                                                              | Elliptic curve                                                              |

| $E_{a_2}$                                                                      | Koblitz curve $(a_2 \in \{0,1\})$                                           |

| $E(\mathbb{F}_q)$                                                              | Group of points on an elliptic curve $E$ over $\mathbb{F}_q$                |

| $\mathbb{F}$                                                                   | Field                                                                       |

| $\mathbb{F}_q \\ \mathbb{F}_q^*$                                               | Finite field with $q$ elements                                              |

| $\mathbb{F}_{a}^{*}$                                                           | Multiplicative group of $\mathbb{F}_q$                                      |

| $\mathbb{F}_p^*$                                                               | Prime field                                                                 |

| $\mathbb{F}_{2^m}$                                                             | Binary field                                                                |

| $\mathbb{F}_q[x]$                                                              | Ring of polynomials over $\mathbb{F}_q$                                     |

| f                                                                              | Clock frequency                                                             |

|                                                                                |                                                                             |

| f(x)                                | Binary polynomial of $x \in \mathbb{F}$            |

|-------------------------------------|----------------------------------------------------|

| $f(\cdot, \cdot)$                   | Round function of a block cipher                   |

| $F(\cdot, \cdot)$                   | F-function of normal basis multiplication          |

| g                                   | Generator of $\mathbb{F}_q$                        |

| G                                   | Group                                              |

| $gcd(\cdot, \cdot)$                 | Greatest common divisor                            |

| h                                   | Hash                                               |

| $H(\cdot)$                          | Hamming weight, the number of nonzero terms        |

| $H_n(\cdot)$                        | Joint Hamming weight of $n$ expansions             |

| $HASH(\cdot)$                       | Cryptographic hash algorithm                       |

| $i, j, n, r, \ldots, u$             | Positive integers                                  |

| I                                   | Inversion                                          |

| 1                                   | Latency                                            |

| l                                   | Bit length                                         |

| $\hat{k}$                           | Positive (random) integer                          |

| k                                   | An array of binary expansions                      |

| K                                   | Key                                                |

| $K_i$                               | Round key for the <i>i</i> th round                |

| $K_e$                               | Encryption key                                     |

| $K_e$<br>$K_d$                      | Decryption key                                     |

| $\operatorname{KeySCHEDULE}(\cdot)$ | Key schedule of the AES                            |

| $\mathcal{LD}$                      | López-Dahab coordinates                            |

| m                                   | Dimension of an extension field                    |

| M                                   |                                                    |

| M                                   | Message, plain text                                |

|                                     | Multiplication<br>Column transformation of the AES |

| $MIXCOLUMNS(\cdot)$ $Nr$            | Number of rounds                                   |

|                                     |                                                    |

| $\operatorname{ord}(\cdot)$         | Order of<br>The preint at infinite                 |

| 0                                   | The point at infinity                              |

| p                                   | Prime number                                       |

| p                                   | The number of parallel operations                  |

| p(x)                                | Irreducible polynomial                             |

| P                                   | Point on an elliptic curve, the base point         |

| $\mathcal{P}$                       | Projective coordinates                             |

| q                                   | Order of a finite field                            |

| Q                                   | Point on an elliptic curve, the result point       |

| R                                   | Ring                                               |

| RoundKeys                           | Round keys of the AES                              |

| S                                   | Squaring                                           |

| $S(\cdot)$                          | S-box                                              |

| $\operatorname{ShiftRows}(\cdot)$   | Row permutation transformation of the AES          |

| STATE                               | State in the AES                                   |

| $SUBBYTES(\cdot)$                   | Substitution transformation of the AES             |

| t                                   | Computation time                                   |

| Т                                   | Throughput                                         |

| $T_i(\cdot)$                        | T-box $i$                                          |

| $\mathbf{T}_N$                      | Multiplication matrix of normal basis              |

| V                                   | Vector space                                       |

| w                                   | Window size                                        |

| x,y                                 | Coordinates of a point in $\mathcal{A}$            |

| X, Y, Z          | Coordinates of a point in $\mathcal{P}$ or $\mathcal{LD}$ |

|------------------|-----------------------------------------------------------|

| $\alpha$         | Normal element of $\mathbb{F}_{2^m}$                      |

| $\delta, \mu$    | Auxiliary variables for Koblitz curves                    |

| $\Delta$         | Temporary variable of composite field inversion           |

| $\lambda$        | Temporary variable of point operations in $\mathcal{A}$   |

| ξ                | Element of a multiplication matrix $\mathbf{T}_N$         |

| σ                | Field isomorphism                                         |

| au               | Complex root                                              |

| $\varphi(\cdot)$ | Euler's totient function                                  |

| $\phi(\cdot)$    | Frobenius endomorphism                                    |

| $\psi, \omega$   | Coefficients of irreducible polynomials                   |

# Chapter 1

## Introduction

INFORMATION SECURITY is a fundamental requirement for an operational information society. Although issues considered as information security, such as privacy of communication and reliable authentication, have been important throughout history, developments in digital computing and information technology have set new requirements and challenges for them. The importance of information security has grown because new technologies have made accessing and misusing confidential information easier and more profitable. Hence, information security, previously considered mostly by militaries and governments, has become an issue having relevance even for an average person living in a modern information society because of its significance in commerce, telecommunication, *etc*.

Cryptography, the art and science of hiding data, plays a central role in achieving information security. It has become a fundamental part of communication and commercial applications in the Internet as well as in many other digital applications. Cryptography is deployed with cryptographic algorithms, mathematical functions for hiding messages and retrieving hidden messages. This thesis studies and proposes methods to efficiently implement certain cryptographic algorithms.

### 1.1 Motivation for the Thesis

The motivation for this thesis, as perhaps for all engineering, arises from the classic utilitarian view which was well captured by Cilardo *et al.* [67] who stated,

"A mathematical construction with practical applications, such as a cryptographic algorithm, has no real interest, in an engineering sense, as long as methods for feasible implementation are not available."

In other words, efficient implementation techniques for cryptographic algorithms are necessary in order to use them in practice.

Applications using cryptographic algorithms often set very tight requirements for implementations. Low-cost applications, such as mobile hand-held devices, sensor networks, or smart cards, to name a few, often set strict constraints on available resources, such as logic, memory, or power [90]. On the other hand, high-speed applications, such as high-speed network servers, require very high computation speeds in order to prevent cryptography from becoming the bottleneck [105, 126]. Hence, designing implementations fulfilling the requirements is often a challenging task and implementing cryptographic algorithms has been widely studied in academia.

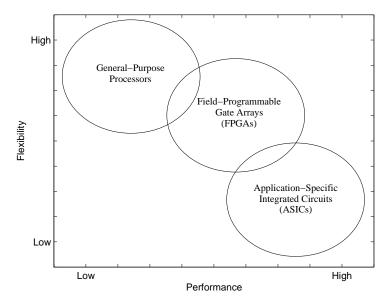

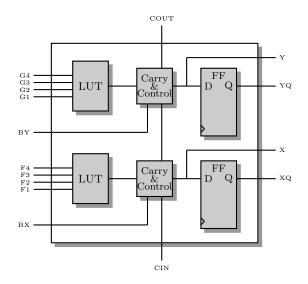

Naturally, general-purpose microprocessors can be used for implementing cryptographic algorithms but, in that case, the execution of computationally demanding cryptographic algorithms easily becomes the limiting factor for overall performance [63]. Hence, dedicated hardware implementations are commonly required to offload cryptographic algorithms away from the microprocessor [63]. Reprogrammable hardware has established itself as one of the most attractive platforms for cryptographic algorithms because of the combination of speed and flexibility [293]. This thesis concentrates on Field Programmable Gate Arrays (FPGAs) which are commonly considered very feasible implementation platforms among implementors of cryptographic algorithms [293]. However, a majority of the ideas and architectures presented in this thesis can be applied also to Application Specific Integrated Circuits (ASICs), and some even for software implementations.

#### 1.2 Scope of the Thesis

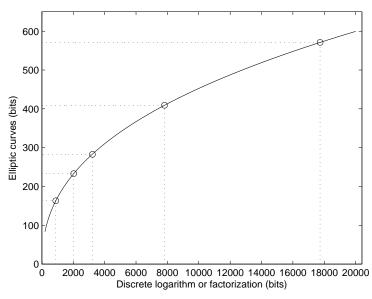

The thesis concentrates on a secret-key cryptographic algorithm, Advanced Encryption Standard (AES) [206], and public-key cryptographic algorithms based on arithmetic on elliptic curves, Elliptic Curve Cryptography (ECC) [146, 194]. AES has become a true *de facto* algorithm for secret-key cryptography and it is used in countless applications worldwide ranging from RFID tags [95] and sensor networks [120] to heavily-loaded servers [105] and optical networks [126]. Because of the very wide use of AES, it is justified to focus this study solely to AES. ECC is in many ways superior to traditional public-key algorithms, such as the widely-used RSA [239], because it offers similar levels of security with considerably shorter keys [32, 164] and faster performance [88, 251]. In the recent years, ECC has gained popularity also in practical systems and it is used, e.g., in Windows Vista [160], OpenSSL [218], and German biometric passports [43, 44], to name a few. The National Security Agency (NSA) of the United States is also strongly promoting the use of ECC [210]. ECC has thus become a mainstream method for public-key cryptography and its use is increasing. Hence, the selection of ECC is justified.

Because this thesis considers both secret-key and public-key cryptographic algorithms, the results also enable designing cryptosystems where a secret key is first shared by two parties with the public-key algorithm, *i.e.*, with ECC, and, then, the actual encryption is performed with the faster secret-key algorithm, *i.e.*, with AES. As mentioned, both AES and ECC are algorithms which are used in numerous practical applications and they are likely to remain popular also in the foreseeable future. Consequently, most of the findings of this thesis can be directly applied in practice.

Requirements for cryptographic implementations are diverse, but the primary requirement considered in this thesis is speed of computation. Before a cryptographic algorithm can be adopted to a practical application, there must exist ways to implement it so that it matches the speed requirements of the application. For instance, if traffic in a high-speed network is encrypted with cryptographic algorithms, the implementations must be able to compute the algorithms with throughputs matching the throughput of the network, or otherwise they become the bottleneck for the entire communication. An example of an application that sets very high requirements for computation speed is the Packet Level Authentication (PLA) communication scheme [46, 47], which was the main target application, especially, for the implementations presented in  $\mathbf{V}$ and **VII**. Other examples include heavily-loaded e-commerce servers [105] and optical network switches [126].

Most publications of this thesis concern ECC. The emphasis is on methods allowing increased use of parallelism in ECC operations, or more specifically in elliptic curve point multiplication, the principal operation of ECC. Point multiplication is recursive in nature and it is thus hard to parallelize. Many of the contributions focus on a class of elliptic curves, called Koblitz curves [148], which offer faster computation, but require certain conversions for integers. Koblitz curves have attained a lot of interest in theoretical cryptography research and they are listed in major ECC standards, such as [52, 205], but, prior to this thesis, they have attained only limited interest in the community implementing cryptographic algorithms in hardware.

The focus of this thesis is on the algorithmic level and in methods allowing efficient implementation. This thesis does not discuss higher level aspects, such as cryptographic protocols. Also lower levels, such as gate or transistor levels, are not discussed in this thesis. All contributions address the problem of achieving fast computation of cryptographic algorithms efficiently. The scope of the thesis can be described as finding answers to the following questions:

- Which algorithms are the most suitable for hardware (or FPGA) implementations and how could they be improved in order to increase their suitability?

- How should these algorithms be implemented in order to provide the best possible results?

Author's other publications on topics related to cryptography, in addition to the publications of this thesis, include an automated design generator for ECC [137], studies of cryptographic hash algorithms, MD5 and SHA-1 [138, 139], and a recent work on fast decompressions in ECC [41].

### **1.3** Contributions of the Thesis

This thesis has contributed to several areas of research in cryptographic implementations. More specifically, the contributions enable faster implementations of AES and ECC than those that were available previously, and they thus provide improvements predominantly to applications requiring high speed implementations. The following lists the main contributions of this thesis. More detailed discussions are given in the publications and in Ch. 7.

The AES-related contributions  $(\mathbf{I}, \mathbf{II})$  include

- a review of existing FPGA-based implementations of widely-used secretkey cryptographic algorithms including AES and hash algorithms (I) and a review complementing and updating this review (Ch. 5),

- a study illuminating the relationship between achieved throughput and consumed area in AES implementations also when they use embedded memory of FPGAs (I), and

- a high-speed implementation of AES which was the fastest FPGA-based implementation at the time of publication (II).

The most significant contributions are those considering ECC (III–XI) and they include

- a review of existing ECC implementations on FPGAs and ASICs (Ch. 6),

- an implementation optimized for the structure of FPGAs (III),

- a study on the effects of parallelism in ECC implementations and tools for evaluating and optimizing parallelism in these implementations (IV),

- a method that splits point multiplications on Koblitz curves for parallel processors and FPGA implementations utilizing this method (**IV**),

- an FPGA design for computing signature verifications, the most demanding operations of the PLA, with very high speed  $(\mathbf{V})$ ,

- improvements to precomputation algorithms used in these signature verifications  $(\mathbf{V})$ ,

- a method utilizing parallelism and interleaved point operations on Koblitz curves (**VI**),

- implementations of the above method (**VI**) and an optimized implementation which further improves on this by utilizing similarity of certain point multiplication algorithms (**VII**); these implementations achieve the fastest point multiplications currently available in the literature,

- hardware-optimized algorithms for integer conversions related to Koblitz curves and their implementations (VIII, IX), and

- an introduction of a new multiple-base expansion to Koblitz curves and its FPGA implementations (X, XI).

These contributions increase knowledge of implementing AES and ECC in hardware, and more specifically in FPGAs. The most substantial results are those that provide methods to implement ECC with increased amounts of parallelism, because they result in very fast FPGA implementations. Especially, the results related to Koblitz curves dramatically improve existing solutions. The contributions of this thesis could be directly applied in various practical systems and, as a consequence, they also have significant practical relevance.

#### 1.4 Structure of the Thesis

This thesis comprises an overview and eleven publications which are appended in the end. The remainder of this overview is structured as follows:

Ch. 2 presents an overview of cryptography.

Ch. 3 discusses implementation platforms of cryptographic algorithms.

Ch. 4 introduces preliminaries of finite fields and their implementations.

Ch. 5 discusses AES and its implementations.

Ch. 6 discusses ECC and its implementations.

Ch. 7 summarizes the results of the thesis.

Ch. 8 draws conclusions.

Ch. 2 and 3 give general descriptions of cryptography and cryptographic hardware, whereas Ch. 4–6 present detailed descriptions of both theory and practice of the algorithms discussed in the publications. Ch. 7 and 8 present the results and conclude their importance for the research field.

### 1.5 Summary of Publications and Author's Contribution

The following provides short summaries of the eleven publications of this thesis. The author had a major role in research and writing in all these publications, and the author's contribution in every particular publication is specified in the end of each summary.

**Publication I** The article presents a comparative survey of cryptographic algorithm implementations on FPGAs. The study concentrates on high-speed implementations of AES, International Data Encryption Algorithm (IDEA), MD5, and SHA-1, but other secret-key algorithms and hash algorithms are studied shortly as well. The survey addressed the well-recognized problem of comparing implementations using embedded memory to memory-free implementations. It was concluded that FPGAs suit well for cryptographic algorithms.

The author is responsible for all research and writing, except for the study of IDEA in Sec. 2.2 which was written by Dr. Matti Tommiska who also made improvement suggestions to the rest of the paper. Prof. Jorma Skyttä supervised the research.

**Publication II** The paper describes an implementation of AES. The implementation provided the highest reported throughput at the time of publication, and the most important contribution of the paper was thus the speed of the implementation. Composite fields were utilized in order to increase the efficiency of the implementation. Xilinx Virtex FPGAs were used for demonstration but the architecture itself is generic and applies to both FPGAs and ASICs.

All hardware designs are due to the author. The author wrote all of the paper; except Secs. 1, 6, and 7. Dr. Matti Tommiska provided extensive support in both research work and writing of the paper. He also introduced the possibility of using composite fields to the author and wrote the above mentioned sections. Prof. Jorma Skyttä supervised the research.

**Publication III** The paper presents an implementation of ECC optimized for the structure of Xilinx Virtex FPGAs. The implementation was designed so that it could be easily generated with an automatic VHDL (Very high speed integrated circuit Hardware Description Language) generator which was presented in [137]. The achieved point multiplication times were among the fastest published results at the time of publication, and even the fastest ones for certain parameters.

The author designed and implemented all hardware architectures. The author also wrote the entire paper while Dr. Matti Tommiska supervised the work and made many observations in both research work and writing of the paper. Prof. Jorma Skyttä supervised the research.

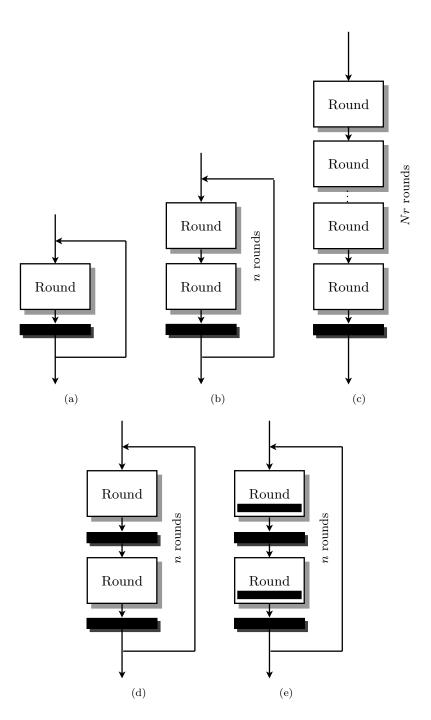

**Publication IV** The article discusses parallelization of ECC processors and describes a generic processor architecture which is used in analyzing effects of parallelism. The article presents a comprehensive study of existing parallelization technique using parallel processors which results in considerable reductions in latency, especially, on Koblitz curves but also on general curves with certain presuppositions. A number of FPGA-based implementations are presented for both general and Koblitz curves.

The author is responsible for all theory, hardware implementations, and the entire writing of the manuscript. Prof. Jorma Skyttä supervised the research and presented comments on the manuscript.

**Publication V** The paper presents an accelerator designed specifically for verifying self-certified signatures on Koblitz curves. This operation acts as the bottleneck in the PLA. It was concluded that up to 166,000 signatures can be verified in second with a single FPGA by using massive parallelism. The paper also presents certain improvements to precomputations involved in verifications. The main contribution of the paper is that it shows that considerable improvements in the number of operations per second are achievable by tolerating slightly longer computation times for single operations.

The author is responsible for everything presented in the paper and he wrote the entire paper. Juha Forsten helped in verifying the designs on an FPGA and he also made certain improvements to the manuscript. Prof. Jorma Skyttä supervised the research.

**Publication VI** The article discusses ECC on Koblitz curves. It introduces a new parallelization method which achieves optimal multiplier utilization by interleaving successive operations. The method has several advantages over the best previously presented methods (the ones presented in **IV**). First, the achievable critical path is shorter; second, the method enables implementing both general and Koblitz curves efficiently in the same hardware; third, the method increases the attractiveness of using Koblitz curves; and, fourth, efficient implementations can be designed by using the method as demonstrated in the paper on FPGAs.

The author is alone responsible for all theory, implementations, and writing. Prof. Jorma Skyttä supervised the research.

**Publication VII** The paper presents an implementation designed specifically for Koblitz curves. The implementation can compute point multiplications and sums of up to three point multiplications and, hence, it supports all ECC operations required in the PLA, confer  $\mathbf{V}$  which supports only verifications. The implementation utilizes the common structure of the algorithms and specific processing units optimized for different parts of the algorithms, especially, the method presented in  $\mathbf{VI}$ . Both fast computation time for single operations and high throughput are achieved with the implementation and, to the author's knowledge, it outperforms all other implementations available in the literature.

The author is responsible for everything presented in the paper and all writing. Prof. Jorma Skyttä supervised the research.

**Publication VIII** The paper describes an architecture for integer conversions related to Koblitz curves. To the author's knowledge, it was (and still is) the only publication presenting such converters. The converter is compact and fast and, hence, it has significance in hardware realization of ECC on Koblitz curves. Prior to the publication of the paper, a general-purpose processor was used for the conversions in all publications. The contributions of the paper include modifications to conversion algorithms, which make them more suitable for hardware, and an efficient converter architecture.

The author is responsible for all research, implementations, and writing in the publication. Juha Forsten helped in testing the converter and gave some comments during the writing of the paper. Prof. Jorma Skyttä supervised the research.

**Publication IX** This paper discusses conversions related to Koblitz curves too, but to the other direction than in **VIII**. Such conversions have significance, *e.g.*, in digital signature algorithms. The benefit compared to conversions discussed in **VIII** is that conversions can be computed in parallel with other operations. The paper also presents efficient hardware implementations of the conversion, and such converters were not presented previously in the literature.

The author designed and implemented the hardware architecture. Theoretical work and ideas are due to Billy Bob Brumley. The author made certain suggestions on how to efficiently compute the conversions and wrote Sec. 4. Brumley wrote the rest of the paper.

**Publication X** The paper presents multiple-base expansions, analogous to the Double-Base Number System (DBNS) [79, 80], and they are useful in ECC on Koblitz curves. Two types of representations, one with two bases and the other with three, were suggested and it was proven that the number of terms in the three-base expansions is sublinear in the bit length of an integer. The same was conjectured for the two-base expansions based on extensive numerical evidence. The practical feasibility of the two-base method was shown by

designing an FPGA implementation. The implementation used the state-of-theart algorithms and achieved high speed with moderate area requirements. The implementation was the fastest published ECC implementation at the time of publication. The suggested expansions were the first multiple-base expansions presented for Koblitz curves which were shown to be feasible in practice.

The author designed and implemented the entire hardware implementation, except the multiple-base expansion converter which was designed and implemented by Dr. Zhun Huang. Theoretical work and ideas on multiple-base expansions are due to Prof. Vassil Dimitrov and Prof. Michael Jacobson, Jr. The software implementation and numerical results were made by Andy Chan. The author is responsible for the writing of Sec. 4, excluding Sec. 4.3, and a part of Sec. 5. The co-authors wrote the rest of the paper.

**Publication XI** The article extends  $\mathbf{X}$ . It discusses multiple-base expansions with more details and provides additional numerical evidence supporting feasibility of the expansions. A new section discussing inherent parallelism available in the expansions is included together with a description of an FPGA implementation utilizing this parallelism.

The most important new part, Sec. 5, was written solely by the author, and the author is alone responsible for all research related to that section. Otherwise, the responsibilities were the same as in  $\mathbf{X}$ .

# Chapter 2

# Overview of Cryptography

CRYPTOGRAPHY, the art and science of keeping messages secure, has a long Chistory which can be traced back to ancient Egypt some 4000 year ago [189]. Undoubtedly, cryptanalysis, the art and science of revealing messages hidden by means of cryptography, has an equally long history. Together cryptography and cryptanalysis are called cryptology. When the history of cryptology is discussed, it must be emphasized that historical cryptology has little common with modern cryptology which started in the 20th century, and which is the topic of this thesis.

First, some fundamental terminology is introduced. The message, which is to be kept in secret, is referred to as plaintext. The process of hiding its content is called encryption and the encrypted message is referred to as ciphertext. The process of receiving the content of plaintext back from ciphertext is decryption. A cryptographic algorithm is the mathematical function used for encrypting and decrypting messages. A modern cryptographic algorithm always includes a key. A cryptographic algorithm, plaintexts, ciphertexts, and keys are referred to as cryptosystem.

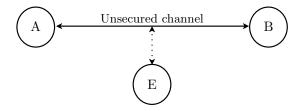

Fig. 2.1 shows the basic communication model where Alice (A) and Bob (B) are communicating over an unsecured channel, and Eve (E) is trying to eavesdrop their communication. In order to prevent Eve from obtaining the content of a message, M, Alice uses a cryptographic algorithm to turn M into

Figure 2.1: Communication model

a ciphertext, C, *i.e.* she performs

$$C = e_K(M) \tag{2.1}$$

where  $e_K(\cdot)$  is the encryption function with the key, K. Alice sends C over the unsecured channel to Bob who performs

$$M = d_K(C) \tag{2.2}$$

where  $d_K(\cdot)$  is the decryption function. Thus, Bob has received M but Eve, who does not have K, is unable to get M from C unless she can break the cryptographic algorithm. [122, 258]

Let  $K_e$  and  $K_d$  be the keys used in encryption and decryption, respectively. Cryptographic algorithms where  $K_e$  can be computed from  $K_d$ , and vice versa, are called secret-key<sup>1</sup> cryptographic algorithms. The secrecy of keys is essential for the security of secret-key cryptographic algorithms because if Eve obtains  $K_e$ , she can easily compute  $K_d$ . Thus, Alice and Bob must exchange keys by using a secured channel which makes key distribution one of the most difficult problems in many applications. The most efficient way to attack a secret-key algorithm should be an exhaustive search through the key space. Even in that case, a secret-key algorithm is weak if it is realistic to assume that it could be possible to build a machine that can perform an exhaustive search in some reasonable time with realistic cost. [258]

Secret-key algorithms were the only option to deploy cryptography until the mid-1970s when Whitfield Diffie and Martin E. Hellman published their landmark paper, "New Directions in Cryptography" [76]. They introduced the concept of public-key cryptography<sup>2</sup> where  $K_e$  can be easily computed from  $K_d$ but  $K_d$  cannot be computed from  $K_e$  (in any reasonable time). Thus,  $K_e$  can be made public. Communication between Alice and Bob operates so that Bob publishes his  $K_e$ . Alice uses it to encrypt M and sends C over the unsecured channel. Only Bob has access to  $K_d$  because it cannot be computed from  $K_e$ , and Bob is thus the only one able to decrypt C. Public-key cryptographic algorithms are based on hard problems where "hard" means that a problem is considered impossible to solve with any computational resources available currently or in the (near) future. In proportion, a problem is "weak" if there are methods for solving the problem with some amount of computational resources available at the time although acquiring such resources might be unreachable for all but the richest governments or corporations. Thus, the hardness of a problem is open to interpretation. [258]

Moreover, the required level of security depends on confidentiality of the data being encrypted. Hence, an adequate level of security may be achieved with weak algorithms. For example, Data Encryption Standard (DES) was used until late-1990s by some corporations although it was commonly considered weak already in the 1980s [164]. As a rule of thumb, if the cost of breaking a cryptosystem exceeds the value of encrypted data, then the cryptosystem can be considered adequately secure [258]. However, cryptography alone does not provide information security, but it is rather a set of techniques [189]. In addition to cryptographic algorithms, security relies also on many other aspects. In

<sup>&</sup>lt;sup>1</sup>Terms such as private-key or symmetric(-key) are also commonly used in the literature. <sup>2</sup>Also called as asymmetric(-key) cryptography.

fact, failures in practical cryptosystems, such as automatic teller machines, are commonly due to implementation and management errors [11]. Hence, in order to make a system secure, all sides of an application must be secured: protocols, algorithms, implementations, *etc.*, [164] and security considerations should be an organic part in designing applications where security is an issue [231]. The above does not diminish the importance of secure cryptographic algorithms because they have an essential role in building a secure system in the first place. Security is always compromised if a severe flaw is found in a cryptographic algorithm.

Secret-key cryptography is considered in more detail in Sec. 2.1 and publickey cryptography is discussed in Sec. 2.2. Cryptographic hash algorithms are one-way functions which have a great significance in many cryptosystems, and they are considered in Sec. 2.3.

### 2.1 Secret-key Cryptography

Secret-key cryptographic algorithms are categorized into either stream ciphers or block ciphers based on how they manipulate data. A stream cipher handles data one symbol, typically a bit, at a time whereas a block cipher encrypts data in fixed-length blocks. Most cryptographic algorithms used today are block ciphers and stream ciphers are used predominately in situations where transmission errors are probable and implementation resources are limited [189], such as mobile communication devices. Stream ciphers are not considered further in this thesis.

Modern block ciphers are usually constructed using a Feistel structure or a Substitution-Permutation Network (SPN), *e.g.*, DES uses a Feistel structure and AES is an SPN. In both cases, encryption and decryption are performed by iteratively applying a round function,  $D_i = f(D_{i-1}, K_i)$ , where  $D_{i-1}$  is the data at iteration i-1 and  $K_i$  is the round key for iteration i. Round keys are derived from the key, K, with a routine called key schedule. The round function,  $f(\cdot, \cdot)$ , includes substitutions performed with the so-called S-boxes which are predefined tables, permutations that rearrange the input data using fixed rules, and round key mixing which is typically performed with an exclusive-or (XOR). [274]

An enormous amount of different block ciphers have been proposed and are in use in different applications. Probably the two most important ones, DES and AES, are discussed in Secs. 2.1.1 and 2.1.2, respectively.

#### 2.1.1 Data Encryption Standard (DES)

In 1972, National Bureau of Standards (NBS) of the United States, nowadays National Institute of Standards and Technology (NIST), initiated a program for computer security which included the development of an encryption standard. After initial problems in finding a candidate that would fulfill the requirements set for the standard, they received a promising candidate called Lucifer from IBM. Lucifer was evaluated and revised by the NSA before its adaptation as a Federal Information Processing Standard (FIPS) in 1976. The standard [203] was published in January 1977. The development process and introduction of DES was perhaps the most important landmark in the history of academic research on cryptosystems. It was the first time in history when a high-security cryptographic algorithm became available to everyone and, hence, it marked the beginning of wide-scale academic research on cryptography. [258]

It had become obvious that the key length of DES was too short to be secure against exhaustive key search and, thus, a strengthened variant called Triple-DES (3DES) was included into the final reaffirmation of the standard in 1999 [204]. DES was withdrawn officially in 2005 and it has been replaced by AES. DES is not considered further in this thesis because of its decreasing importance in contemporary cryptosystems.

#### 2.1.2 Advanced Encryption Standard (AES)

Because it had become obvious that DES had exceeded the end of its reasonable lifetime, NIST began the process to replace DES in January 1997. An open competition was announced for algorithms in September of the same year. The requirements for the algorithm were 128-bit block size, support for keylengths of 128, 192, and 256 bits, and royalty free availability. Altogether 15 candidate algorithms were submitted to the competition. After the first round, five finalist algorithms were selected; namely, Mars, RC6, Rijndael, Serpent, and Twofish. [45, 211]

Criteria for the selection of the winner included security, performance, and algorithm characteristics. All finalists were stated to be secure enough to be selected as AES, and there were no known intellectual property issues for any of the algorithms. Thus, performance was the key issue which finally decided the winner. Performance was evaluated on various platforms including 8-bit embedded processors, 32-bit Pentium processors (the most important), Digital Signal Processors (DSPs), FPGAs, and ASICs. [45, 211]

In October 2000, NIST announced that Rijndael was selected as the new AES algorithm. The reasons why Rijndael was selected were its strong performance on basically all platforms and the ease of hardware implementation [45, 211]. Rijndael was also the most popular choice in straw polls at the final AES conference, and its selection received an approving reception in the community [45]. Rijndael was officially adopted as the AES on December 6, 2001 [206]. Henceforth, AES always refers to Rijndael in this thesis<sup>3</sup>. Details of the algorithm are not considered here because they are discussed thoroughly in Sec. 5.1.

### 2.2 Public-key Cryptography

As mentioned, public-key cryptography was invented by Diffie and Hellman in the mid-1970s. The main idea that they presented in [76] was that different keys  $K_e$  and  $K_d$  could be used for encryption and decryption so that it is easy to derive  $K_e$  from  $K_d$  but it would be infeasible to find  $K_d$  from  $K_e$ . Diffie and Hellman suggested using discrete exponentiation as a method for obtaining  $K_e$ . Because of its fundamental nature, their key exchange method is reviewed in Sec. 2.2.1 and it is followed by short descriptions of certain other public-key algorithms currently used in many practical applications. Only basic versions

$<sup>^{3}</sup>$ To be precise, there is a small difference between AES and Rijndael: Rijndael accepts block sizes of 128, 192, and 256 bits, whereas AES defines only a fixed block size of 128 bits. In this thesis, both terms refer to the official AES unless stated otherwise.

are presented and they may be insecure against certain attacks, such as theman-in-the-middle attack; see [258], for example.

Public-key cryptography is used in key exchange, encryption, and digital signatures. Key exchange and encryption are self-explanatory: Key exchange permits two parties to safely agree a shared secret key over an unsecured channel and encryption allows data to be encrypted without sharing a secret key. Digital signatures can be seen as digital counterparts for handwritten signatures and they provide unforgeable proofs of authorship and authenticity as well as nonrepudiation.