Linköping Studies in Science and Technology Dissertation No. 1999

# Studies on Selected Topics in Radio Frequency Digitalto-Analog Converters

M. Reza Sadeghifar

Linköping Studies in Science and Technology Dissertation No. 1999

### Studies on Selected Topics in Radio Frequency Digital-to-Analog Converters

M. Reza Sadeghifar

Linköping University Department of Electrical Engineering Division of Integrated Circuits and Systems SE-581 83 Linköping, Sweden

Linköping 2019

© 2019 M. Reza Sadeghifar, unless otherwise noted. ISBN 978-91-7685-030-5 ISSN 0345-7524 URL http://urn.kb.se/resolve?urn=urn:nbn:se:liu:diva-160893

Published articles have been reprinted with permission from the respective copyright holder. Printed in Sweden by LiU-Tryck, Linköping 2019 To Hoda

Yesterday I was clever, so I wanted to change the world. Today I am wise, so I am changing myself.

Rumi

#### POPULÄRVETENSKAPLIG SAMMANFATTNING

Tidsfördröjningen genom nätverket i den femte generationens mobilteknik (5G) är bara några få millisekunder vilket är mycket lägre än i 4G-tekniken. Ett öga tar cirka 400 millisekunder på sig att blinka. Den enorma förbättringen tillsammans med högre informationskapacitet inom 5G-tekniken banar väg för framtida innovationer i det smarta, uppkopplade samhället. Det nya nätverket bör byggas på en trådlös infrastruktur där många radiobasstationer kan distribueras tätt och över stort område. Det innebär att samtidigt som radiobasstationen måste möta den tuffa specifikationen i form av storlek, vikt och effektförbrukning måste nätverket optimeras för att kunna bli kommersiellt gångbart.

När antalet antennelement ökar i så kallade MIMO-baserade radio, som 5G, blir det en utmaning att konstruera de multibandssändare i 10-GHz-bandet som krävs. Framförallt krävs integration av de olika komponenterna såsom de digitala integrerade kretsarna (ASIC) och bredbandiga dataomvandlare med hög upplösning. Den här avhandlingen fokuserar på högfrekventa digital-till-analog-omvandlare (RF DAC) och semi-digitala digital-till-analog-omvandlare (SDFIR DAC) samt olika tekniker som används i dessa strukturer för att förbättra deras prestanda.

I RF DAC-delen av avhandlingen presenteras en ny DAC-lösning för radiofrekvenser som kan integreras monolitiskt med digitala ASICs tack vare sin "digitala" arkitektur. En spänningsbaserad omvandlingsmetod används i utgångssteget och i datavägen används en konfigurerbar logik som skapar en högre frekvenslob. Därmed kan utsignalen i den första eller andra Nyquist-zonen användas och således höga signalfrekvenser.

I SDFIR DAC-delen formuleras en ansats att optimera en SDFIR DAC. Storleks- och energimetriker med bland annat variabel koefficientprecision definieras för seriekopplade digitala sigma-delta-modulatorer, halvdigitala FIR-filter samt överföringsfunktionen för DAC-en. En uppsättning analoga kostnadsmått används i formuleringen av optimeringsproblemet. Det visar sig att hårdvarukostnaden för omvandlaren kan minskas avsevärt genom att införa flexibel koefficientprecision utan att överkonstruera omvandlaren. Olika användningsfall används som mål för formuleringarna i optimeringsproblemet för att ta reda på den optimala uppsättningen vikter i det halvdigitala FIR-filtret.

Vidare presenteras en så kallad direkt digital-till-RF-omvandlare (DRFC) där spänningsbaserade RFDAC-celler används som vikter i ett halvdigitalt FIR-filter. Dessa kommer kunna syntetisera spektralt rena signaler vid höga frekvenser. Tack vare sin digitala natur drar DRFC nytta av processskalning och kan integreras i digitala VLSI-system. En fjärde ordningens digital bandpass sigma-delta modulator med enbitars kvantisering används, vilket resulterar i ett högt signal-brusförhållande (SNR). Det spektralt formade kvantiseringsbruset utanför bandet dämpas av det halvdigitala filtret. Utsignalen skapas av en ny typ av konfigurerbar lösning som erbjuder hög linearitet till låg kostnad.

En kompensationsteknik för att häva det kodberoende beroendet av strömmen genom matningen presenteras också i avhandlingen. Metoden simuleras på systemnivå och en modell av omvandlaren samt resultat presenteras för att stödja den analytiska diskussionen.

#### ABSTRACT

The network latency in fifth generation mobile technology (5G) will be around one millisecond which is much lower than in 4G technology. This significantly faster response time together with higher information capacity and ultra-reliable communication in 5G technology will pave the way for future innovations in a smart and connected society. This new 5G network should be built on a reasonable wireless infrastructure and 5G radio base stations that can be vastly deployed. That is, while the electrical specification of a radio base station in 5G should be met in order to have the network functioning, the size, weight and power consumption of the radio system should be optimized to be able to commercially deploy these radios in a huge network.

As the number of antenna elements increases in massive multiple-input multiple-output radios such as in 5G, designing true multi-band transceivers, with efficient physical size, power consumption and cost in emerging cellular bands especially in mid-bands (frequencies up to 10 GHz), is becoming a challenge. This demands a hard integration of radio components; particularly the radio's digital application-specific integrated circuits (ASIC) with high-performance energy-efficient multi-band data converters.

In this dissertation radio frequency digital-to-analog converter (RF DAC) and semi-digital finite-impulse response (FIR) filter digital-to-analog converter has been studied. Different techniques are used in these structures to improve the transmitter's overall performance.

In the RF DAC part, a radio frequency digital-to-analog converter solution is presented, which is capable of monolithic integration into today's digital ASIC due to its digital-innature architecture, while fulfills the stringent requirements of cellular network radio base station linearity and bandwidth. A voltage-mode conversion method is used as output stage, and configurable mixing logic is employed in the data path to create a higher frequency lobe and utilize the output signal in the first or the second Nyquist zone and hence achieving output frequencies up to the sample rate.

In the semi-digital FIR part, optimization problem formulation for semi-digital FIR digitalto-analog converter is investigated. Magnitude and energy metrics with variable coefficient precision are defined for cascaded digital Sigma-Delta modulators, semi-digital FIR filter, and Sinc roll-off frequency response of the DAC. A set of analog metrics as hardware cost is also defined to be included in semi-digital FIR DAC optimization problem formulation. It is shown that hardware cost of the semi-digital FIR DAC, can be reduced by introducing flexible coefficient precision in filter optimization while the semi-digital FIR DAC is not overdesigned either. Different use cases are selected to demonstrate the optimization problem formulations. A combination of magnitude metric, energy metric, coefficient precision and analog metric are used in different use cases of the optimization problem formulation and solved to find out the optimum set of analog FIR taps.

Moreover, a direct digital-to-RF converter (DRFC) is presented in this thesis where a semidigital FIR topology utilizes voltage-mode RF DAC cells to synthesize spectrally clean signals at RF frequencies. Due to its digital-in-nature design, the DRFC benefits from technology scaling and can be monolithically integrated into advance digital VLSI systems. A fourth-order single-bit quantizer bandpass digital Sigma-Delta modulator is used preceding the DRFC, resulting in a high in-band signal-to-noise ratio (SNR). The out-of-band spectrally-shaped quantization noise is attenuated by an embedded semi-digital FIR filter. The RF output frequencies are synthesized by a configurable voltage-mode RF DAC solution with a high linearity performance. A compensation technique to cancel the code-dependent supply current variation in voltagemode RF DAC for radio frequency direct digital frequency synthesizer is also presented in this dissertation and is studied analytically. The voltage-mode RF DAC and the compensation technique are mathematically modeled and system-level simulation is performed to support the analytical discussion.

### Acknowledgments

My PhD studies is divided in two periods; 2010-2014 and 2018-2019. In the first period I was full-time PhD student with Electronic Systems Division in Linköping University. Electronic Systems Division consolidated in 2014 into Integrated Circuits and Systems Division. In the second period (2018-2019), I was conducting my PhD research on spare time in order to finalize my PhD studies; while I was with Ericsson AB in Stockholm, working on radio systems and hardware. That part of my PhD was memorable since it was difficult, challenging and fun all in the same time! It required a lot of effort and many early-mornings and I received a lot of help from people that I would like to thank.

I would like to thank, first and foremost, my supervisor Prof. Jacob Wikner who never stopped supporting me during all these years. Apart from technical aspects, you taught me how to be productive, work efficiently and how to think out-of-the-box. Technical knowledge during PhD studies can be gained in one way or another, but for professional attitudes one needs to have a professional supervisor!

I would like to thank Prof. Atila Alvandpour, head of Integrated Circuits and Systems Division. I should say this journey actually started in 2008 when I started as a fresh SoC Master student in Sweden. I was inspired by your series of Analog CMOS courses (called VLSI at that time) on CMOS circuits design, chip tape-out and measurements. Your passionate and exciting lectures kept me in this business. I would also like to thank Prof. Oscar Gustafsson, head of Computer Engineering Division, for providing me the opportunity to start as a PhD student in Linköping University and for your guidance during this time and in my publications. I would like to thank my former colleagues in Electronic Systems Division during my time in Linköping especially Dr. Nadeem Afzal with whom I shared office - and shared great time as well - for four years. I would also like to thank my colleagues in Integrated Circuits and Systems Division for the occasional visits during the past two years who created a friendly atmosphere especially Martin Nielsen Lönn and Pavel Angelov. Thanks to Eva Zurawski for the help with the administrative issues.

I would like to thank my colleagues in Ericsson Radio Department. Special thanks to my mentor, Dr. Håkan Bengtsson, for helpful discussion and smart ideas, and to Dr. Björn Halvarsson for the proofreading of the thesis, and to my past and current managers Wojciech Mudyna, Martin Schmekel and Kaiyu Liu for their support.

I would like to thank all my friends through out these years for the great time we shared. Special thanks to Kamyar Rasta for the proofreading of the thesis and to Dr. Reza Moosavi for the help with Latex template.

I am blessed to have a family who loves me unconditionally. I would like to thank my parents and my parents-in-law for all your love, encouragement, support and good wishes. Special thanks to my mom and my dad for the time you spent here with us helping with the children, so that I could find some more time to spend on this thesis, and to my two lovely children beautiful Elsa and little Elvin, who have filled my life with your love and sweetness, and to Leila, Soheila, Navid and Milad for being the amazing people that your are.

Last but not least I would like to especially thank my soulmate and my love Hoda. Without all your help, your devotion and patience, I would not be able to complete this work. Therefore, I dedicate this work to you.

> M. Reza Sadeghifar Stockholm, September 2019

## Contents

| $\mathbf{A}$ | bstra | $\operatorname{ct}$                                   | vii  |

|--------------|-------|-------------------------------------------------------|------|

| A            | cknov | wledgments                                            | xii  |

| C            | onter | ıts                                                   | xiii |

| Li           | st of | Figures                                               | xv   |

| Li           | st of | Tables                                                | xix  |

| Li           | st of | Abbreviations                                         | xxii |

| 1            | Intr  | oduction                                              | 1    |

|              | 1.1   | Motivation                                            | 1    |

|              | 1.2   | Background                                            | 2    |

|              | 1.3   | Research Methodology                                  | 3    |

|              | 1.4   | Contributions of the Thesis                           | 6    |

|              | 1.5   | Other Publications                                    | 10   |

| <b>2</b>     | Rad   | lio Frequency Digital-to-Analog Converters            | 13   |

|              | 2.1   | Transmitter Architectures                             | 14   |

|              | 2.2   | Frequency Response of Digital-to-Analog Converters    |      |

|              | 2.3   | High-Speed DAC Implementation Techniques              | 24   |

|              | 2.4   | Current-Steering DAC for High-Speed Operation         | 29   |

| 3            | Volt  | tage-Mode Radio Frequency Digital-to-Analog Converter |      |

|              | 3.1   | Digital Transmitter                                   | 37   |

|              | 3.2   | RF DAC-Based Digital Transmitter                      | 38   |

|              | $3.3 \\ 3.4$                                         | Implementation       Simulation Results                                                               | $\begin{array}{c} 45\\ 46\end{array}$         |

|--------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 4            |                                                      | Supply Current Compensation Technique in Voltage-         de RF DACs for RF DDFS         Introduction | <b>49</b><br>49<br>53<br>56                   |

| 5            | <b>Sen</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | hi-Digital FIR Digital-to-Analog Converter<br>Introduction                                            | <b>61</b><br>64<br>65<br>66<br>69<br>70       |

| 6            |                                                      | Direct DRFC Employing Semi-Digital FIR Voltage-Mode<br>DAC<br>Digital IQ Transmitter Architecture     | <b>79</b><br>79<br>81<br>81<br>86<br>86<br>91 |

| 7            | <b>Cor</b><br>7.1                                    | nclusion<br>Future Direction                                                                          | <b>93</b><br>94                               |

| Bi           | bliog                                                | graphy                                                                                                | 97                                            |

| Pa           | aper                                                 | I                                                                                                     | 115                                           |

| Paper II 12  |                                                      | 127                                                                                                   |                                               |

| Paper III 13 |                                                      |                                                                                                       | 137                                           |

| Paper IV 1   |                                                      |                                                                                                       | 151                                           |

| Paper V      |                                                      |                                                                                                       | 167                                           |

| Pa           | Paper VI                                             |                                                                                                       |                                               |

| Pa           | Paper VII 1                                          |                                                                                                       |                                               |

| Pa           | Paper VIII 18                                        |                                                                                                       |                                               |

# List of Figures

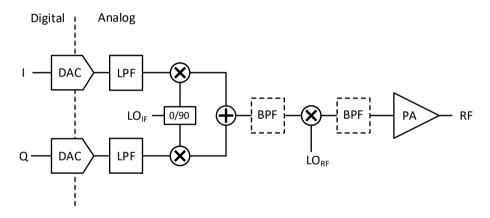

| 2.1  | A simplified block diagram illustration of a superheterodyne trans-   |    |

|------|-----------------------------------------------------------------------|----|

|      | mitter                                                                | 15 |

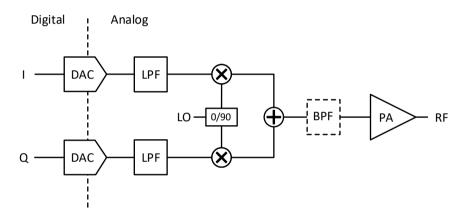

| 2.2  | A simplified block diagram illustration of a direct-conversion trans- |    |

|      | mitter                                                                | 16 |

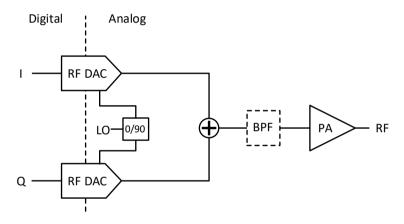

| 2.3  | Direct-digital-to-RF transmitter with analog IQ modulation            | 17 |

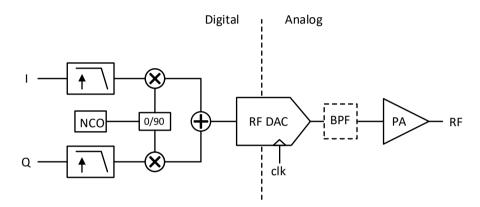

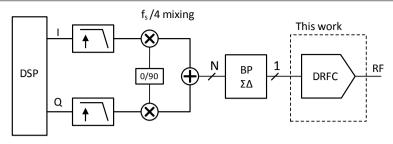

| 2.4  | Direct-digital-to-RF transmitter with digital IQ modulation           | 18 |

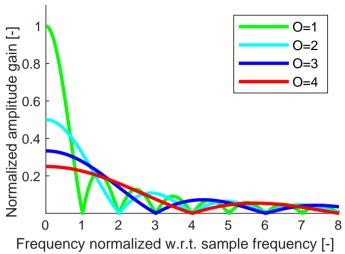

| 2.5  | Frequency characteristics for different PAM pulse duration in         |    |

|      | return-to-zero schemes                                                | 20 |

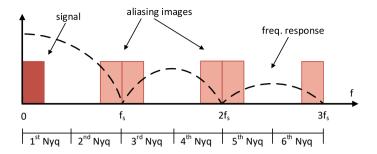

| 2.6  | Frequency response of a conventional DAC using rectangular PAM        |    |

|      | pulse. The higher Nyquist images are attenuated by the frequency      |    |

|      | response                                                              | 21 |

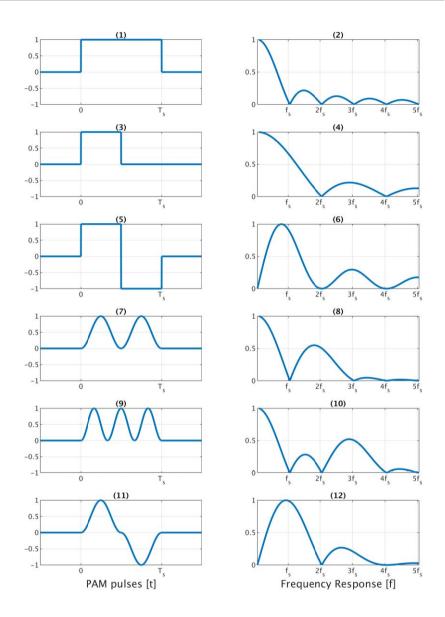

| 2.7  | DAC frequency Response with different PAM pulses                      | 23 |

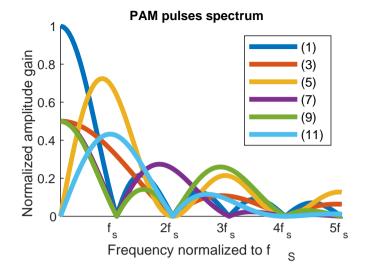

| 2.8  | Different PAM pulses spectrum normalized to the conventional          |    |

|      | rectangular pulse amplitude.                                          | 24 |

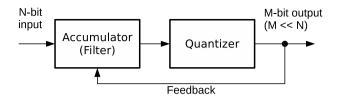

| 2.9  | Simplistic view of a $\Sigma\Delta$ modulator                         | 25 |

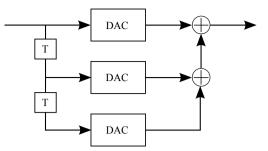

| 2.10 | Example of three time-interleaved DACs                                | 26 |

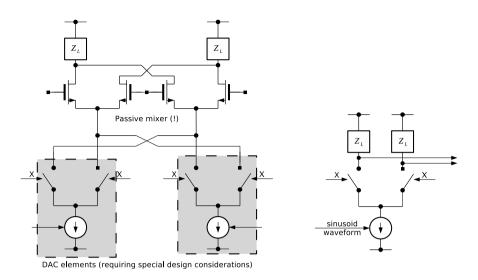

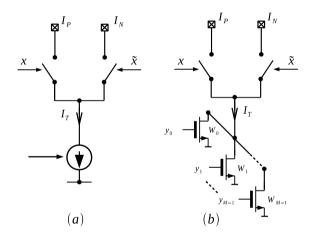

| 2.11 | Two examples of unit DAC element integrated with mixers, one          |    |

|      | with passive mixer on the output (left) and one with active mixer     |    |

|      | on the input (right).                                                 | 27 |

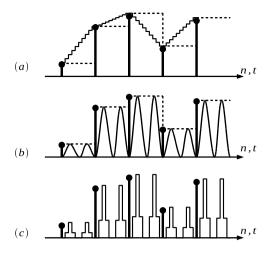

| 2.12 | Illustration of time-domain behavior for (a) linear interpolation,    |    |

|      | (b) sinusoid mixing, (c) quantized microstepping of sinusoid wave-    |    |

|      | form                                                                  | 28 |

| 2.13 | Simplified representation of two approaches to perform up-mixing      |    |

|      | in a current-steering DAC. (a) shows an analog method and (b) a       |    |

|      | mixed-signal method.                                                  | 28 |

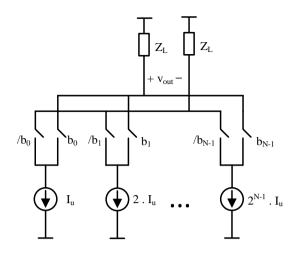

| 2.14 | Simplified block diagram of a binary-weighted current-steering DAC    | 30 |

|      |                                                                       |    |

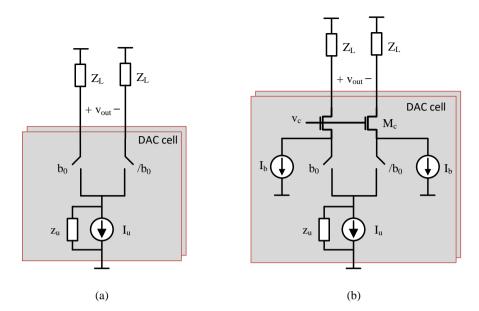

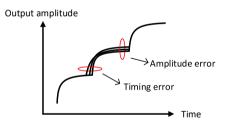

|      | (a) DAC current cell with finite output impedance (b) Bleed-<br>ing current sources added to the DAC cell making the output<br>impedance of the DAC independent of the input code<br>Amplitude and Timing error | 32<br>32        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

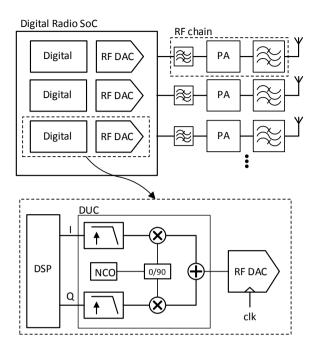

| 3.1  | Block diagram representation of a massive MIMO-based transmit-<br>ter with monolithic integration of data converters into the digital<br>radio System-On-Chip.                                                  | 36              |

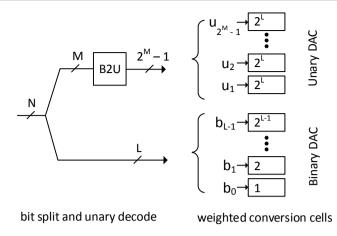

| 3.2  | Top-level functional block diagram of the proposed RF DAC for a digital RF transmitter with an off-chip Balun.                                                                                                  | 38              |

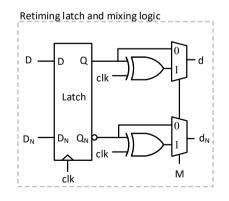

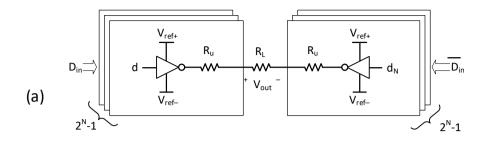

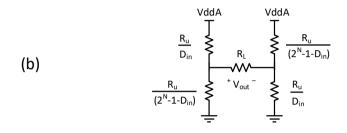

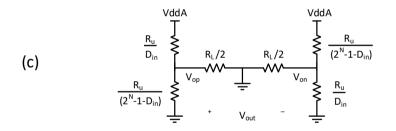

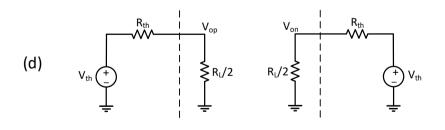

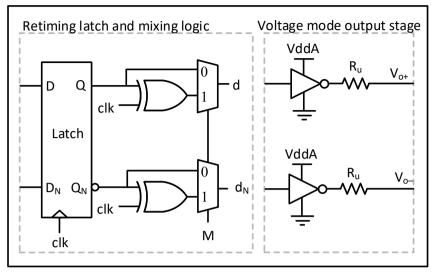

| 3.3  | Retiming latch and mixing logic. The normal-mode operation or mix-mode operation is selected by the signal $M$                                                                                                  | 39              |

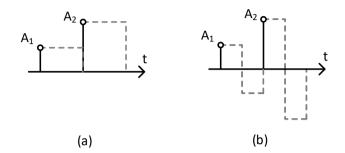

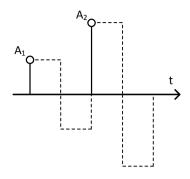

| 3.4  | Time-domain illustration of the pulse amplitude modulation (PAM). (a) Normal-mode operation with rectangular PAM, (b) mix-mode operation with bipolar rectangular PAM.                                          | 40              |

| 3.5  | Step-by-step derivation of the half-differential Thevenin equivalent                                                                                                                                            |                 |

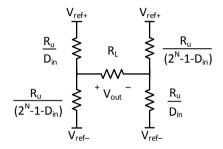

| 3.6  | of the voltage-mode output stage                                                                                                                                                                                | 42<br>44        |

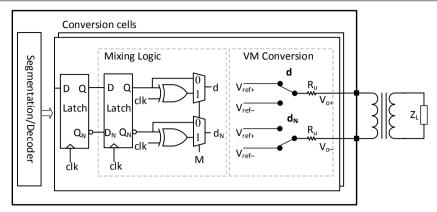

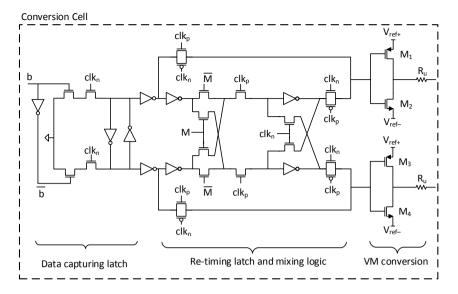

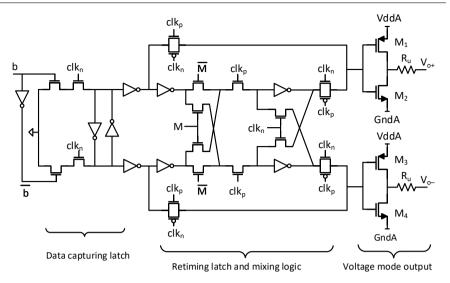

| 3.7  | Complete transistor-level schematic diagram of one conversion unit<br>element cell, including the latches, mixing logic and voltage-mode                                                                        |                 |

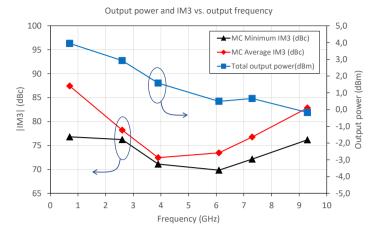

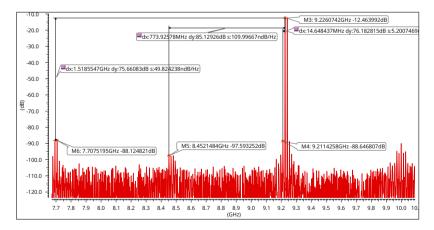

| 3.8  | (VM) conversion $\dots \dots \dots$                                                                             | 45              |

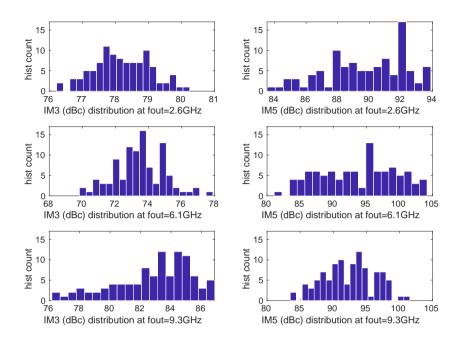

| 3.9  | signals from DC to $f_s$ . The sample frequency is at 10 Gsps<br>IM3 and IM5 distribution of 100 Monte-Carlo points, for three<br>different $f_{out}$ : 2.6, 6.1 and 9.3 GHz. The sample frequency is at        | 46              |

| 3.10 | 10 Gsps                                                                                                                                                                                                         | 48<br>48        |

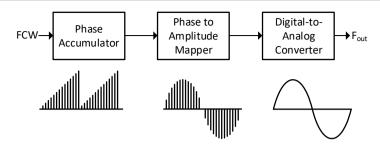

| 4.1  | Block diagram of a direct digital frequency synthesizer.                                                                                                                                                        | 50              |

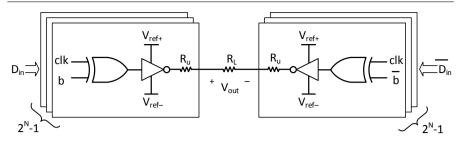

| 4.1  | Voltage-Mode RF DAC conversion unit cell consisting of retiming<br>latch, mixing logic and voltage-mode output stage                                                                                            | 51              |

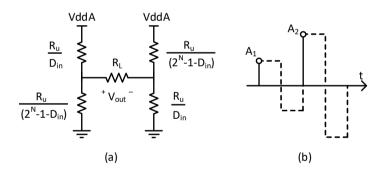

| 4.3  | (a) Simplified equivalent circuit of the output stage at each clock                                                                                                                                             |                 |

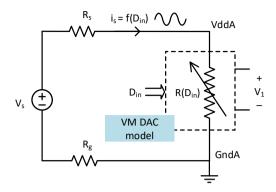

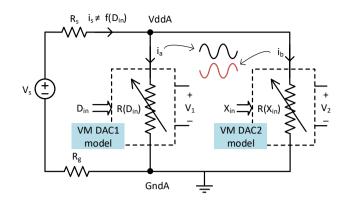

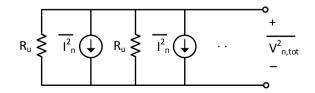

| 4.4  | phase, (b) Bipolar PAM to generate the RF DAC frequency response. Modeling of voltage-mode RF DAC and supply non-idealities                                                                                     | $\frac{51}{52}$ |

| 4.5  | Modeling of voltage-mode DAC and compensating DAC to cancel input code-dependent supply current variation impact.                                                                                               | 54              |

| 4.6  | Complete transistor-level schematic diagram of one conversion unit<br>element cell, including the latches, mixing logic and voltage-mode                                                                        |                 |

|      | conversion                                                                                                                                                                                                      | 56              |

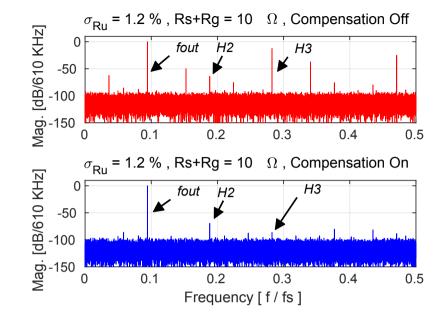

| 4.7                                        | System-level simulation based on the RF DAC model, with $R_u$ sigma of 1.2% and supply resistance of 10 $\Omega$ , with and without             |            |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

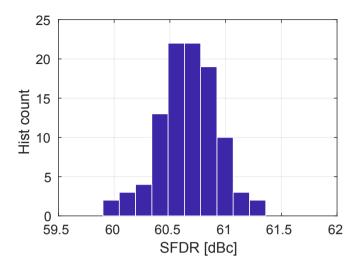

| 4.8                                        | compensation<br>Spurious-Free Dynamic Range (SDFR) within a 5 GHz bandwidth,<br>in a 100-point Monte-Carlo simulation (Latin Hypercube sampling | 57         |

|                                            | method).                                                                                                                                        | 58         |

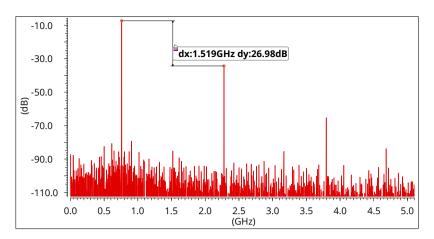

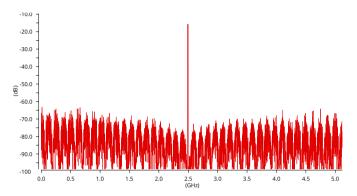

| $\begin{array}{c} 4.9 \\ 4.10 \end{array}$ | Output spectrum without compensation method Output spectrum with compensating method enabled. The worse-                                        | 59         |

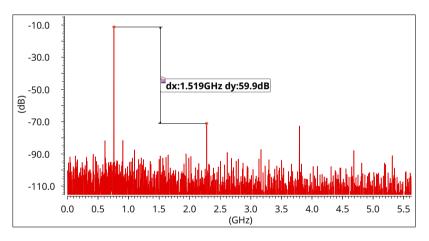

|                                            | case Monte-Carlo simulation shows $\approx 60$ dBc of SFDR                                                                                      | 59         |

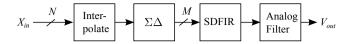

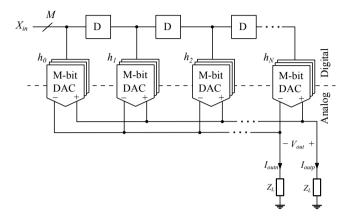

| 5.1                                        | Oversampling $\Sigma\Delta$ semi-digital FIR DAC                                                                                                | 62         |

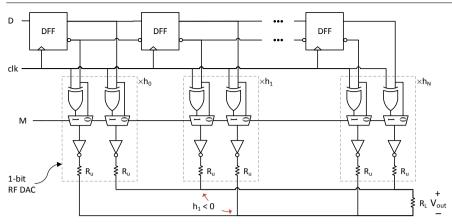

| 5.2                                        | Multi-bit semi-digital FIR filter architecture.                                                                                                 | 62         |

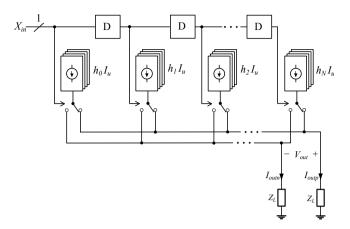

| 5.2                                        | Single-bit semi-digital FIR filter architecture.                                                                                                | 63         |

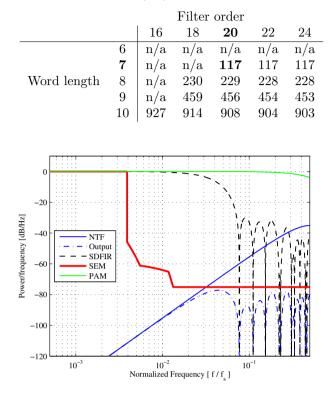

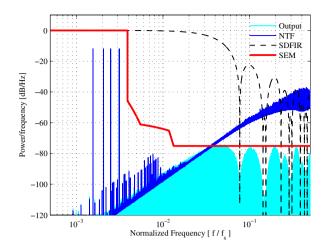

| 5.4                                        | Optimization results from example 1 (based on model). Also shown                                                                                | 00         |

| 0.1                                        | are the $\Sigma\Delta$ modulator noise transfer function (NTF), spectral                                                                        |            |

|                                            | emission mask (SEM), semi-digital FIR filter (SDFIR) response,                                                                                  |            |

|                                            | and DAC <i>Sinc</i> roll-off (PAM).                                                                                                             | 72         |

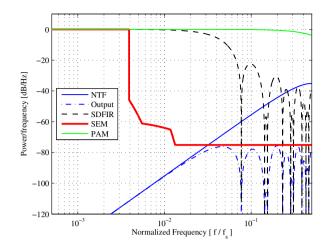

| 5.5                                        | $\Sigma\Delta$ modulator noise transfer function (NTF), spectral emission                                                                       |            |

|                                            | mask (SEM), semi-digital FIR filter (SDFIR), pulse amplitude                                                                                    |            |

|                                            | modulation effect (PAM). Optimization result in example 1 with                                                                                  | <b>H</b> 4 |

| FC                                         | fine-tuning variable $s$ , based on the model                                                                                                   | 74         |

| 5.6                                        | $\Sigma\Delta$ modulator noise transfer function (NTF), spectral emission                                                                       |            |

|                                            | mask (SEM), semi-digital FIR filter (SDFIR). Simulation results                                                                                 | 75         |

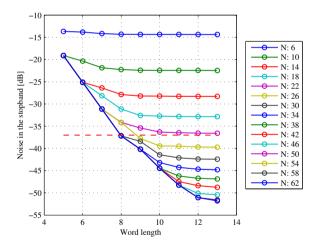

| 5.7                                        | in example 1 with fine-tuning variable $s. \ldots \ldots \ldots \ldots$<br>Noise in the stop-band versus filter order $N$ and word length       | 75<br>75   |

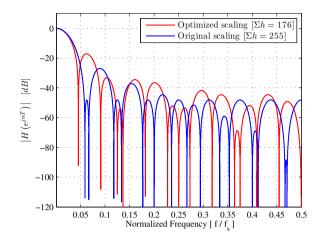

| 5.7<br>5.8                                 | Comparison of SDFIR filter response of the optimized scaling                                                                                    | 15         |

| 0.0                                        | method and the original scaling (Sec. 5.6 and Sec. 5.6).                                                                                        | 76         |

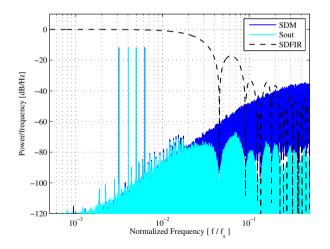

| 5.9                                        | Signal at $\Sigma\Delta$ modulator output (SDM), semi-digital FIR filter                                                                        | 10         |

| 0.5                                        | response, and signal at the output of SDFIR (Sout)                                                                                              | 78         |

|                                            |                                                                                                                                                 | 10         |

| 6.1                                        | Block diagram illustration of a digital IQ transmitter employing a                                                                              |            |

|                                            | BP $\Sigma\Delta$ Modulator and a DRFC                                                                                                          | 80         |

| 6.2                                        | Functional block diagram illustration of direct digital-to-RF con-                                                                              |            |

|                                            | verter employing SDFIR and one-bit voltage-mode differential RF-                                                                                |            |

|                                            | DAC                                                                                                                                             | 82         |

| 6.3                                        | Time-domain illustration of the bipolar pulse amplitude modula-                                                                                 |            |

|                                            | tion (PAM) used in the mixing RF DAC.                                                                                                           | 83         |

| 6.4                                        | Mixing logic operation by XNOR-gating the input bit and the clock.                                                                              | 84         |

| 6.5                                        | Simplified equivalent circuit at each clock phase                                                                                               | 84         |

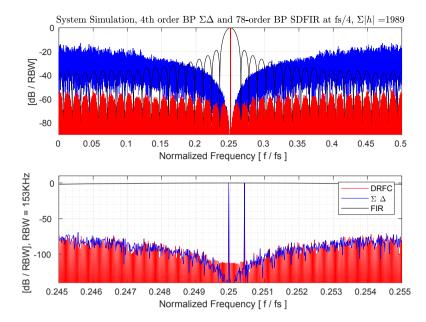

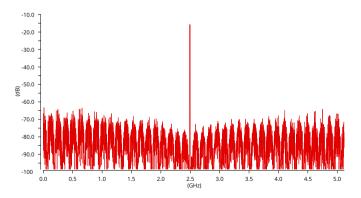

| 6.6                                        | Behavioral-level simulation of the $\Sigma\Delta$ modulator, SDFIR filter re-                                                                   |            |

|                                            | sponse and the DRFC. The first Nyquist zone is illustrated. Wide-                                                                               |            |

|                                            | span spectrum is shown at the top and zoom-in span is shown at                                                                                  |            |

|                                            | the bottom.                                                                                                                                     | 87         |

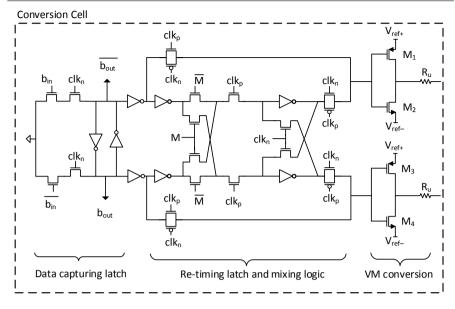

| 6.7                                        | Conversion cell schematic.                                                                                                                      | 88         |

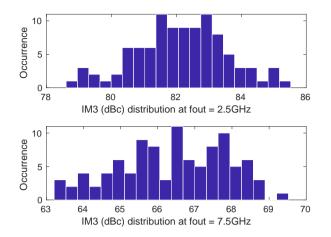

| 6.8  | 6.8 Distribution of 100-point Monte-Carlo IM3 (dBc) simulation for |    |  |

|------|--------------------------------------------------------------------|----|--|

|      | two output frequencies of 2.5 GHz and 7.5 GHz                      | 89 |  |

| 6.9  | Equivalent noise circuit.                                          | 89 |  |

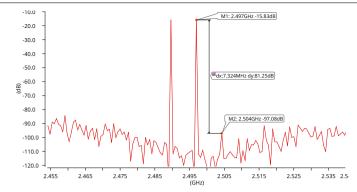

| 6.10 | Linearity performance at 2.5 GHz                                   | 90 |  |

| 6.11 | Linearity performance at 2.5 GHz - far out spectrum                | 90 |  |

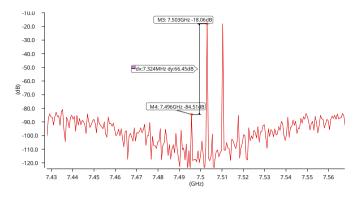

| 6.12 | Linearity performance at 7.5 GHz                                   | 91 |  |

| 6.13 | Linearity performance at 7.5 GHz - far out spectrum                | 92 |  |

### List of Tables

| 3.1 | Mismatch variation of one unit element resistor $R_u$ with nominal value of 10 k $\Omega$ .                       | 43 |

|-----|-------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Mismatch variation of 64 unit element resistors $R_u$ in parallel with<br>nominal value of $10k/64 = 156\Omega$ . | 44 |

| 5.1 | Sum of coefficients $(\Sigma h)$ versus filter order and word length                                              | 72 |

| 5.2 | Sum of the coefficients $(\Sigma h)$ for the variable pass-band gain prob-                                        |    |

|     | lem in example 1                                                                                                  | 73 |

| 5.3 | Optimization results with variable pass-band gain                                                                 | 78 |

| 6.1 | One unit element resistor $R_u$ with nominal value of 10 k $\Omega$                                               | 88 |

| 6.2 | 64 unit element resistors $R_u$ in parallel (example $h_k = 64$ ) with                                            |    |

|     | nominal value of $10k/64 = 156\Omega$ .                                                                           | 89 |

## List of Abbreviations

| 4G             | Fourth generation mobile technology              |

|----------------|--------------------------------------------------|

| 5G             | Fifth generation mobile technology               |

| ADC            | Analog-to-Digital Converter                      |

| ASIC           | Application-specific integrated circuits         |

| BB             | Base Band                                        |

| BPF            | Band Pas Filter                                  |

| $\mathbf{BS}$  | Base Station                                     |

| CAD            | Computer Aided Design                            |

| CMOS           | Complementary Metal–Oxide–Silicon                |

| CORDIC         | Coordinate Rotation Digital Computing            |

| $\mathbf{CW}$  | Continuous Wave                                  |

| DAC            | Digital-to-Analog Converter                      |

| DDFS           | Direct Digital Frequency Synthesizer             |

| DDRM           | Direct-Digital-to-RF Modulator                   |

| DEM            | Dynamic Element Matching                         |

| $\mathbf{DFT}$ | Discrete-Fourier Transform                       |

| $\mathbf{DL}$  | Down-Link: the link from base station to a phone |

| DPD            | Digital Pre-Distortion                           |

| DRFC           | Digital-to-RF Converter                          |

| DSP            | Digital Signal Processing                        |

| DUC            | Digital Up-Converter                             |

| FDD            | Frequency-Division Duplexing                     |

| FDSOI          | Fully Depleted Silicon-On-Insulator              |

| $\mathbf{FFT}$ | Fast-Fourier Transform                           |

| $\mathbf{FIR}$ | Finite-Impulse Response                          |

| FOM            | Figure of Merit                                  |

|                |                                                  |

| HDHarmonic DistortionHPFHigh Pas FilterICTInformation and Communications TechnologyIFIntermediate FrequencyIMInter-modulationIQIn-phase and Quadrature-phaseIoTInternet-of-ThingsLOLocal OscillatorLPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio Frequency Digital-to-Analog ConverterSDFIRSigma-Delta ModulatorSDMSigma-Delta ModulatorSDMSigmal-to-Noise RatioSTFSignal-to-Noise RatioSTFSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSocSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment | FPGA                   | Field Programmable Gate Arrays                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------|

| ICTInformation and Communications TechnologyIFIntermediate FrequencyIMInter-modulationIQIn-phase and Quadrature-phaseIoTInternet-of-ThingsLOLocal OscillatorLPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRFRadio FrequencyRFSigma-Delta ModulatorSDMSigma-Delta ModulatorSDRSignal-to-Noise RatioSTFSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSORSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                   |                        |                                                    |

| IFIntermediate FrequencyIMInter-modulationIQIn-phase and Quadrature-phaseIoTInternet-of-ThingsLOLocal OscillatorLPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                 | HPF                    | High Pas Filter                                    |

| IFIntermediate FrequencyIMInter-modulationIQIn-phase and Quadrature-phaseIoTInternet-of-ThingsLOLocal OscillatorLPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                 | ICT                    | Information and Communications Technology          |

| IMInter-modulationIQIn-phase and Quadrature-phaseIoTInternet-of-ThingsLOLocal OscillatorLPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRFRadio Frequency Digital-to-Analog ConverterSDFIRSigma-Delta ModulatorSDMSigma-Delta ModulatorSDMSignal-to-Noise RatioSTFSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSURSignal-to-Quantization Noise RatioSURSignal-to-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                   | $\mathbf{IF}$          |                                                    |

| IQIn-phase and Quadrature-phaseIoTInternet-of-ThingsLOLocal OscillatorLPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRFRadio FrequencyRFSigma-Delta ModulatorSDFIRSigma-Delta ModulatorSDMSigma-Delta ModulatorSDMSigma-Delta ModulatorSDRSignal-to-Noise RatioSTFSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                       | $\mathbf{IM}$          |                                                    |

| IoTInternet-of-ThingsLOLocal OscillatorLPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRFRadio FrequencyRFSigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSOCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                      | IQ                     | In-phase and Quadrature-phase                      |

| LPFLow Pas FilterLSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSigma-Delta ModulatorSDMSigma-Delta ModulatorSQNRSignal-to-Noise RatioSTFSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                          | IoT                    |                                                    |

| LSBLeast Significant BitLTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRFRadio Frequency Digital-to-Analog ConverterSDFIRSigma-Delta ModulatorSDMSigmal-to-Noise RatioSQMSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSOCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                        | LO                     | Local Oscillator                                   |

| LTELong Term EvolutionMIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRFRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSUMSigmal-to-Noise RatioSUMSignal-to-Noise RatioSTFSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSuffSignal Transfer FunctionSUMSignal-to-OkipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                      | $\mathbf{LPF}$         | Low Pas Filter                                     |

| MIMOMultiple-input multiple-outputMSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio FrequencyRFRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSDMSigmal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                               | $\mathbf{LSB}$         | Least Significant Bit                              |

| MSBMost Significant BitNCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                         | $\mathbf{LTE}$         | Long Term Evolution                                |

| NCONumerically-Controlled OscillatorNSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                | MIMO                   | Multiple-input multiple-output                     |

| NSDNoise Spectral DensityNTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                    | $\mathbf{MSB}$         | Most Significant Bit                               |

| NTFNoise Transfer FunctionNRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                             | NCO                    | Numerically-Controlled Oscillator                  |

| NRNew Radio access technologyOSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{NSD}$         | Noise Spectral Density                             |

| OSROver-Sampling RatioPAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                    | NTF                    | Noise Transfer Function                            |

| PAPower AmplifierPAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\mathbf{NR}$          | New Radio access technology                        |

| PAMPulse-Amplitude ModulationPLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSR                    | Over-Sampling Ratio                                |

| PLLPhase-Locked LoopRBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{PA}$          | Power Amplifier                                    |

| RBSRadio Base StationRFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\mathbf{PAM}$         | Pulse-Amplitude Modulation                         |

| RFRadio FrequencyRF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\mathbf{PLL}$         | Phase-Locked Loop                                  |

| RF DACRadio Frequency Digital-to-Analog ConverterSDFIRSemi-Digital Finite-Impulse ResponseΣΔSigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RBS                    |                                                    |

| SDFIRSemi-Digital Finite-Impulse Response $\Sigma\Delta$ Sigma-Delta ModulatorSDMSigma-Delta ModulatorSNRSignal-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\mathbf{RF}$          | Radio Frequency                                    |

| <ul> <li>ΣΔ Sigma-Delta Modulator</li> <li>SDM Sigma-Delta Modulator</li> <li>SNR Signal-to-Noise Ratio</li> <li>SQNR Signal-to-Quantization Noise Ratio</li> <li>STF Signal Transfer Function</li> <li>SoC System-On-Chip</li> <li>TDD Time-Division Duplexing</li> <li>UE User Equipment</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RF DAC                 | Radio Frequency Digital-to-Analog Converter        |

| SDMSigma-Delta ModulatorSNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        | Semi-Digital Finite-Impulse Response               |

| SNRSignal-to-Noise RatioSQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        | Sigma-Delta Modulator                              |

| SQNRSignal-to-Quantization Noise RatioSTFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{SDM}$         | Sigma-Delta Modulator                              |

| STFSignal Transfer FunctionSoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\mathbf{SNR}$         | •                                                  |

| SoCSystem-On-ChipTDDTime-Division DuplexingUEUser Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\mathbf{SQNR}$        |                                                    |

| <b>TDD</b> Time-Division Duplexing <b>UE</b> User Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\mathbf{STF}$         | •                                                  |

| UE User Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\mathbf{SoC}$         |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{TDD}$         |                                                    |

| <b>UL</b> Up-Link: the link from a phone to the base station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{UE}$          |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{UL}$          | Up-Link: the link from a phone to the base station |

| VCO Voltage-Controlled Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |                                                    |

| <b>VDSL</b> Very high-speed Digital Subscriber Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |                                                    |

| VLSI Very Large Scale Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VLSI                   | Very Large Scale Integration                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{V}\mathbf{M}$ | Voltage-Mode                                       |

| , Los tory harge beare integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\mathbf{V}\mathbf{M}$ | Voltage-Mode                                       |

#### CHAPTER

1

### Introduction

#### 1.1 Motivation

Massive multiple-input, multiple-output (MIMO) wireless technology is a key to achieve higher information transfer capacity by employing spatial multiplexing and beamforming techniques in the fifth-generation cellular network technology (5G). According to the Shannon-Hartley theorem, there are two ways to improve the channel capacity; bandwidth and signal-to-noise ratio,

$$C = B \cdot \log_2\left(1 + \frac{S}{N}\right),\tag{1.1}$$

where C is the communication channel capacity, B is the allocated bandwidth and S/N is the signal to noise and interference ratio (SNR) of the communication signal at the receiver expressed in linear power ratio. Increasing the bandwidth further in the currently crowded spectrum specially below 4GHz can be very costly. Although larger bandwidth is available in millimeter-wave frequency (24-40GHz), the high free space path loss and the outdoor-to-indoor propagation losses in an urban area are challenges to overcome [97].

In order to improve the capacity, different new techniques and features have been employed during the course of time in each generation of communication standards from 2G to 5G. Spatial multiplexing and dynamic beamforming in a multi-user massive-MIMO wireless technology, are effective techniques to increase the capacity beyond what is shown in Eq 1.1, and are used in 5G technology [64]. In fact, multiple users (UEs) are communicating with a base station using different beams on the same frequency-time resources. The available SNR in a communication channel is shared between different spatially separated layers resulting in a linear relation between the capacity and the number of spatial layers. The maximum number of spatial layers is dependent on the number of transmitters and receivers in a MIMO channel so called channel rank. Moreover, by dynamic beamforming the available SNR is also increased and thus it reduces the inter-cell interference and improves the cell-edge performance.

There are several beamforming implementation options for massive MIMO 5G radios: digital, analog and hybrid beamforming. In an analog/hybrid beamforming implementation, the phase adjustments are implemented in the radio, i.e., in the RF chain part of the transceiver and strongly depend on the calibration of the analog components [99]. In a digital beamforming implementation, there are multiple data branches in digital domain and highly focused beams are formed by proper phase shift between the branches in digital domain [127]. There are advantages and disadvantages with each of these beamforming implementations. Digital beamforming comes with high flexibility but also high power and cost [118]. The advantage with analog beamforming is that the interface between the radio unit and the baseband unit has lower load and larger data bandwidth would be possible with this implementation. Thus, this implementation method is adopted in mm-wave massive MIMO radios today [110]. On the other hand, digital beamforming is capable of performing frequency selective scheduling and multi-user scheduling; this is not possible with analog beamforming.

A digital beamforming architecture requires the same number of data converters as the number of antenna elements since the per-element beamforming weights are applied digitally. This means that, for instance, a 64-antenna radio with digital beamforming implementation, should have 64 digital-to-analog converters (DAC) and 64 analog-to-digital converters (ADC). The radio board design will be even much more sophisticated for the radios with 128 or 256 antennas. This demands innovative data converters solutions in order to efficiently implement the 5G radios with respect to cost, size and power dissipation.

#### 1.2 Background

Data converters are key components in the transceiver circuits in telecommunication equipment. Thanks to digitalization, signal processing has become much more capable and reliable and much less expensive in digital realm, while signals need to be physical quantities to be able to be transmitted and received. Therefore, the need for evolution of digital-analog data converters never ends.

As the number of antenna elements increases in a digital beamforming implementation of massive MIMO radios, designing efficient radio base stations covering multiple bands in existing, unlicensed, or emerging frequency bands with efficient size, cost, and power consumption is becoming a challenge. This demands a hard integration of the radio components and specifically the digital application-specific integrated circuit with high-performance data converters.

For instance, in the downlink, monolithic integration of radio frequency digital-to-analog converters (RF DAC) and digital digital application-specific integrated circuit (ASIC) into "one" digital radio System-On-Chip (SoC) results in reduced power consumption as well as a considerable footprint reduction and thus a reduction in radio size.

Depending on the data converters performance in terms of speed and spectral purity, the transceiver architectures have changed during the course of time, from two step heterodyne transceivers to fully digital RF DAC/ADCbased transceivers. In other words, digitalization of electronic systems which started in 1970s and mostly on signal processing part, is progressing towards antenna in transceivers.

This digitalization has been further crucial by introduction of Massive MIMO and 5G technology where the number of transceivers branches and antennas in the same radio equipment is growing exponentially from one or two antennas in 3G/4G up to 256 antennas in 5G [12].

To this end, high performance data converters are highly demanded in order to fulfill the wireless infrastructure requirements with high output bandwidth to cover multiple frequency bands, and in the same time, compatible with digital integration [78, 63, 76, 39, 79, 59].

#### 1.3 Research Methodology