# Study and control of 5-level PWM rectifier-5-level NPC active power filter cascade using feedback control and redundant vectors

Thameur ABDELKRIM<sup>1,\*</sup>, El Madjid BERKOUK<sup>2</sup>, Karima BENAMRANE<sup>1</sup>, Tarak BENSLIMANE<sup>3</sup>

<sup>1</sup>Applied Research Unit on Renewable Energies, Industrial Zone, B.P. 88, Ghardaïa-ALGERIA e-mail: tameur2@yahoo.fr

<sup>2</sup>Laboratory of Process Control, Polytechnic National School, Street Hassen Badi, El Harrach, B.P. 182, Algiers-ALGERIA

<sup>3</sup>University of Msila, BP. 166, Street Ichbilia, 28000 Msila-ALGERIA

Received: 22.12.2010

#### Abstract

The purpose of this paper is to develop a control and regulation method for the input DC voltages of a 5-level neutral point clamping (NPC) active power filter (APF). This APF is applied for the enhancement of medium-voltage network power quality by compensation of harmonic currents produced by an induction motor speed variator. In the first part, the authors present a topology of a 5-level NPC voltage source inverter and its simplified space vector pulse width modulation (SVPWM) control strategy. In the second part, the control strategy of the 5-level pulse width modulation current rectifier is presented. In the third part, to remedy to instability problem of the input DC voltages of the APF, the authors propose the feedback control of the 5-level rectifier associated with a simplified SVPWM with the redundant vectors method for the 5-level APF. After that, the sliding mode regulator used to control the APF is developed. The application of the proposed control algorithm offers the possibility of stabilizing the DC voltages of the APF. The stable DC bus supply associated with the sliding regulator of the APF allows the obtainment of low-harmonic content network currents with unity power factor. The instability problem associated with the use of the multilevel APF is solved. The obtained results are full of promise for the use of the multilevel APF in medium-voltage and high-power applications.

**Key Words:** Active power filter, NPC multilevel converter, space vector pulse width modulation, redundant vectors, feedback control

# 1. Introduction

The increasing use of control systems based on industrial power electronics involves more and more disturbance problems at the level of the electrical power supply networks [1]. Thus, a regular increase in current harmonic

<sup>\*</sup>Corresponding author: Applied Research Unit on Renewable Energies, Industrial Zone, B.P. 88, Ghardaïa-ALGERIA

distortion and unbalance rates can be observed, as well as an important consumption of reactive power. These harmonic currents yield voltage harmonics and unbalances via impedance of the power supply network, which infects the sinusoidal waveform of the electrical power supply voltage. These disturbances of course have bad consequences for electrical equipment, such as strong heating, sudden stopping of the revolving machines, or even the total destruction of such equipment.

Several solutions for reducing harmonic current in electrical power supply networks have been proposed. Active compensators such as the shunt active filter, series active filter, and combined shunt-series active filters satisfy the industrial constraints better than passive compensators [2].

In fact, the main role of active filtering is to constantly control the harmonic distortion in an active way by compensating for the harmonics [3]. European standards CEI 61000-3-4 and CEI 61000-3-6 define the harmonic current limits of low-, medium-, and high-voltage power supply networks [4].

Research on the shunt active filters includes different works concerning harmonic identification methods such as the Fourier transform method [5], the method of synchronous reference frame (d-q) [6], and control strategies such as sliding mode regulators, artificial neural networks, and fuzzy logic controllers [7-9]. The structure of the filters has also undergone an evolution, from 2-level converters [10,11] to multilevel converters [12-14]. In high-power applications, multilevel converters are more adequate, simply because of the low harmonic distortion rate of voltage and current, the low switching frequency, and the ability to be used without a transformer [15-18]. Various topologies have been developed, such as flying capacitor multilevel converters, diode-clamped multilevel converters, neutral point clamping (NPC) multilevel converters, and Hbridge multilevel converters.

The unbalance of the different DC voltage sources of the multilevel (NPC) active power filters (APFs) constitutes the major limitation for the use of these power converters. Several methods have been proposed to suppress the unbalance of neutral point potential. Some of these methods are based on adding a zero sequence or a DC-offset to the output voltage [19,20]. In [21,22], power electronics circuitry was added to redistribute the charges between capacitors. A method based on minimizing a quadratic parameter that depends on capacitor voltages was presented in [23]. This quadratic parameter was positively defined and reached 0 when the 2 capacitors had the same voltage. Some other works have used a converter-inverter cascade [24] and have applied automatic control methods, such as fuzzy logic control [25] or sliding mode control [26], to this cascade. The drawback of these methods is either high costs and system complexity, or the use of an open-loop scheme. In this work, we use a simple closed-loop method based on the continuous measurement of output current and the difference between capacitor voltages to choose the redundant vector.

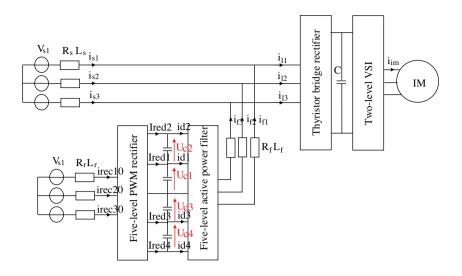

The first part of the paper is dedicated to the presentation of the model of the 3-phase, 5-level NPC voltage source inverter (VSI) with its space vector pulse width modulation (SVPWM) control method. In the second part, the control strategy of the 5-level pulse width modulation (PWM) current rectifier is presented. After that, the multi-DC bus voltage balancing method using feedback control and redundant vectors is detailed. This APF is applied for the enhancement of medium-voltage network power quality by compensation of harmonic currents produced by an induction motor speed variator (Figure 1). At the end, the simulation results of the sliding mode-controlled APF are presented. ABDELKRIM, BERKOUK, BENAMRANE, BENSLIMANE: Study and control of 5-level PWM rectifier-5-level NPC active...,

Figure 1. Synoptic diagram of application of shunt APF on power supply-fed cascaded thyristor bridge rectifier 2-level VSI-induction motor.

# 2. Modeling and control of 5-level NPC VSI

### 2.1. Modeling of 5-level NPC VSI

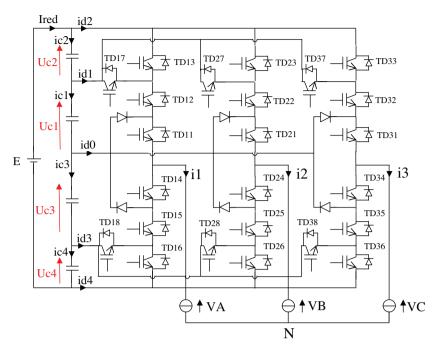

The 3-phase, 5-level NPC VSI comprises 3 legs and 4 DC voltage sources. Every leg has 8 bidirectional switches, 6 in series and 2 in parallel, and 2 diodes to get 0 voltage for  $V_{KM}$  (Figure 2). Every switch is composed of a transistor and a diode in antiparallel [27].

The switch connection function,  $F_{KS}$ , indicates the opened or closed state of the switch,  $T_{KS}$ :

$$F_{KS} = \begin{cases} 1 & \text{if } T_{KS} \text{ closed} \\ 0 & \text{if } T_{KS} \text{ open} \end{cases}$$

(1)

For a leg K of the 3-phase, 5-level NPC VSI, several complementary control laws are possible. The optimal control law that allows the obtaining of a 5-level voltage (Uc1, Uc1+Uc2, 0, -Uc3, -Uc3-Uc4) for each leg of this inverter is:

$$\begin{cases}

F_{K5} = 1 - F_{K1} \\

F_{K4} = 1 - F_{K2} \\

F_{K6} = 1 - F_{K3}l \\

F_{K7} = F_{K1} \cdot F_{K2} \cdot (1 - F_{K3}) \\

F_{K8} = F_{K4} \cdot F_{K5} \cdot (1 - F_{K6})

\end{cases}$$

(2)

Figure 2. Five-level NPC voltage source inverter.

The half-leg connection function  $F^b_{Km}$  is defined as:

$$\begin{cases}

F_{K1}^b = F_{K1}F_{K2}F_{K3} \\

F_{K0}^b = F_{K4}F_{K5}F_{K6}

\end{cases},$$

(3)

where m = 1 for the lower half-leg and m = 0 for the upper half-leg.

The output voltages of the inverter relative to point N of the load using the connection functions are given as follows:

$$\begin{bmatrix} V_A \\ V_B \\ V_C \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \left\{ \begin{bmatrix} F_{17} + F_{11}^b \\ F_{27} + F_{21}^b \\ F_{37} + F_{31}^b \end{bmatrix} U_{c1} + \begin{bmatrix} F_{11}^b \\ F_{21}^b \\ F_{31}^b \end{bmatrix} U_{c2} - \begin{bmatrix} F_{18} + F_{10}^b \\ F_{28} + F_{20}^b \\ F_{38} + F_{30}^b \end{bmatrix} U_{c3} - \begin{bmatrix} F_{10}^b \\ F_{20}^b \\ F_{30}^b \end{bmatrix} U_{c4} \right\}.$$

$$(4)$$

The input currents  $i_{d1}$ ,  $i_{d2}$ ,  $i_{d3}$ ,  $i_{d4}$ , and  $i_{d0}$  of the inverter using the connection functions and load currents  $i_1$ ,  $i_2$ , and  $i_3$  are given as follows:

ABDELKRIM, BERKOUK, BENAMRANE, BENSLIMANE: Study and control of 5-level PWM rectifier-5-level NPC active...,

| Switching |          |                                                                  | C L | Switchir | ıg state | s   |     |     | Output             |  |

|-----------|----------|------------------------------------------------------------------|-----|----------|----------|-----|-----|-----|--------------------|--|

| symbols   | $T_{i1}$ | $T_{i1}  T_{i2}  T_{i3}  T_{i4}  T_{i5}  T_{i6}  T_{i7}  T_{i8}$ |     |          |          |     |     |     |                    |  |

| P2        | ON       | ON                                                               | ON  | OFF      | OFF      | OFF | OFF | OFF | $U_{c1}+U_{c2}$    |  |

| P1        | ON       | ON                                                               | OFF | OFF      | OFF      | ON  | ON  | OFF | $U_{c1}$           |  |

| 0         | ON       | OFF                                                              | OFF | ON       | OFF      | ON  | OFF | OFF | 0                  |  |

| N1        | OFF      | OFF                                                              | ON  | ON       | ON       | OFF | OFF | ON  | $-\mathrm{U}_{c3}$ |  |

| N2        | OFF      | OFF                                                              | OFF | ON       | ON       | ON  | OFF | OFF | $-U_{c3}-U_{c4}$   |  |

Table 1. States of the 5-level inverter.

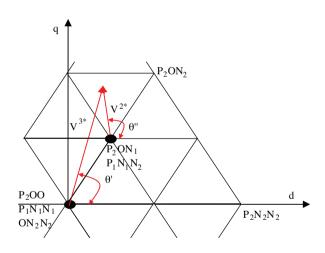

The output voltage vector in the space vector diagram is defined as:

$$Vs = Vd + jVq. ag{6}$$

Vd and Vq are real and imaginary components of Vs in the (d-q) frame.

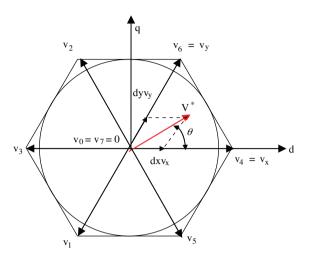

Output voltage vector Vs can take several discrete positions in the (d-q) frame according to the switching states of the inverter legs. These positions are indicated on the space vector diagram given in Figure 3. They are identified by the combination of the switching states of the legs, P2, P1, 0, N1, or N2 (Table 1). Since each leg has 5 possible switching states, the 5-level inverter has  $5^3 = 125$  states.

Some positions of the output voltage vector are synthesized by more than one switching state. In Figure 3 and Table 2, we can find 24 positions with no redundancy (V37 to V60), 18 positions with 2 redundancies (V1 to V18), 12 positions with 3 redundancies (V19 to V30), 6 positions with 4 redundancies (V30 to V36), and 1 position with 5 redundancies (V61).

Figure 3. Space vector diagram of a 5-level inverter.

| Vectors | Re | dundancies | Vectors | Re    | dundancies | Vectors | Re     | dundancies |

|---------|----|------------|---------|-------|------------|---------|--------|------------|

|         | a  | P2N1N1     |         | a     | P200       |         | a      | P2P1P1     |

| V1      | b  | P1N2N2     | V19     | b     | P1N1N1     |         | b      | P100       |

| I I I   | a  | P2ON1      |         | с     | ON2N2      | V31     | с      | ON1N1      |

| V2      | b  | P1N1N2     |         | а     | P2P1O      |         | d      | N1N2N2     |

| 170     | a  | P2P1N1     | V20     | b     | P1ON1      |         | а      | P2P2P1     |

| V3      | b  | P1ON2      |         | с     | ON1N2      | 1700    | b      | P1P1O      |

| V4      | a  | P2P2N1     |         | a     | P2P2O      | V32     | с      | OON1       |

| V4      | b  | P1P1N2     | V21     | b     | P1P1N1     |         | d      | N1N1N2     |

| V5      | a  | P1P2N1     |         | с     | OON2       | a       | P1P2P1 |            |

| v o     | b  | OP1N2      |         | а     | P1P2O      | 1799    | b      | OP1O       |

| V6      | a  | OP2N1      | V22     | b     | OP1N1      | V33     | с      | N1ON1      |

| VO      | b  | N1P1N2     |         | с     | N1ON2      |         | d      | N2N1N2     |

| V7      | a  | N1P2N1     |         | а     | OP2O       |         | a      | P1P2P2     |

| V /     | b  | N2P1N2     | V23     | b     | N1P1N1     | 1794    | b      | OP1P1      |

| V8      | a  | N1P2O      |         | с     | N2ON2      | V34     | с      | N100       |

| vo      | b  | N2P1N1     |         | OP2P1 |            | d       | N2N1N1 |            |

| V9      | a  | N1P2P1     | V24     | b     | N1P1O      | V35     | a      | P1P1P2     |

| V 9     | b  | N2P1O      |         | с     | N2ON1      |         | b      | OOP1       |

| V10     | a  | N1P2P2     |         | а     | OP2P2      |         | с      | N1N1O      |

| V10     | b  | N2P1P1     | V25     | b     | N1P1P1     |         | d      | N2N2N1     |

| V11     | a  | N1P1P2     |         | с     | N2OO       |         | a      | P2P1P2     |

| V I I   | b  | N2OP1      |         | а     | OP1P2      | V36     | b      | P1OP1      |

| V12     | a  | N1OP2      | V26     | b     | N1OP1      | V 30    | с      | ON1O       |

| V 12    | b  | N2N1P1     |         | с     | N2N1O      |         | d      | N1N2N1     |

| V13     | a  | N1N1P2     |         | a     | OOP2       |         |        |            |

| V 15    | b  | N2N2P1     | V27     | b     | N1N1P1     |         |        |            |

| V14     | a  | ON1P2      |         | с     | N2N2O      |         |        |            |

| V 14    | b  | N1N2P1     |         | a     | P1OP2      |         |        |            |

| V15     | a  | P1N1P2     | V28     | b     | ON1P1      |         |        |            |

| V 10    | b  | ON2P1      |         | с     | N1N2O      |         |        |            |

| V16     | a  | P2N1P2     |         | a     | P2OP2      |         |        |            |

| 10      | b  | P1N2P1     | V29     | b     | P1N1P1     |         |        |            |

| V17     | a  | P2N1P1     |         | с     | ON2O       |         |        |            |

| , 11    | b  | P1N2O      |         | a     | P2OP1      |         |        |            |

| V18     | a  | P2N1O      | V30     | b     | P1N1O      |         |        |            |

| , 10    | b  | P1N2N1     |         | с     | ON2N1      |         |        |            |

Table 2. Redundant vectors of a 5-level inverter.

### 2.2. Five-level inverter control

#### 2.2.1. Space vector modulation for 2-level inverter

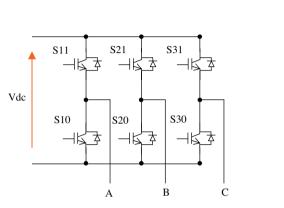

Figure 4 shows the structure of the 2-level inverter. Each of the 3 phases of the inverter has 2 switches and 2 freewheeling diodes. Depending on the values of the switching signals, the 2-level inverter has 8 states, summarized in Table 3, where the output voltage vector produced in each state is also indicated. These output vectors are shown in the space vector diagram of Figure 5. The arbitrary reference vector,  $V^*$ , to be generated by the inverter is also indicated.

Desired voltage vector  $V^*$ , located in a given sector, can be generated by a linear combination of the 2 adjacent base vectors,  $v_x$  and  $v_y$ , which frame the sector, and 1 of the 2 zero vectors,  $v_z$ .

$$V^* = d_x v_x + d_y v_y + d_z v_z \tag{7}$$

Figure 4. Two-level inverter structure.

Figure 5. Space vector diagram of 2-level inverter.

Table 3. States of 2-level inverter.

| State | $\mathbf{F}_{a}$ | $\mathbf{F}_{b}$ | $\mathbf{F}_{c}$ | Voltage vector |

|-------|------------------|------------------|------------------|----------------|

| 0     | 0                | 0                | 0                | $V_0$          |

| 1     | 0                | 0                | 1                | $V_1$          |

| 2     | 0                | 1                | 0                | $V_2$          |

| 3     | 0                | 1                | 1                | $V_3$          |

| 4     | 1                | 0                | 0                | $V_4$          |

| 5     | 1                | 0                | 1                | $V_5$          |

| 6     | 1                | 1                | 0                | $V_6$          |

| 7     | 1                | 1                | 1                | $V_7$          |

$d_x$ ,  $d_y$ , and  $d_z$  denote the so-called duty ratios of states X, Y, and Z of the inverter within the switching interval, respectively. Duty ratios  $d_x$ ,  $d_y$ , and  $d_z$  are calculated as [28,29]:

$$d_{x} = \frac{\left|V^{2*}\right|}{\sqrt{2/3}V_{dc}} \frac{\sin(60 - \theta)}{\sin(60)},$$

$$d_{y} = \frac{\left|V^{2*}\right|}{\sqrt{2/3}V_{dc}} \frac{\sin(\theta)}{\sin(60)},$$

$$d_{z} = 1 - d_{x} - d_{y}.$$

(8)

#### 2.2.2. Simplified SVPWM for 5-level inverter

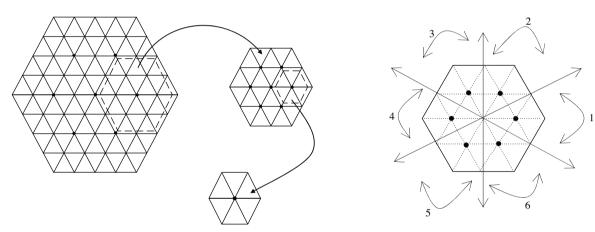

The space vector diagram of a 5-level inverter can be considered to be composed of 6 hexagons that are the space vector diagrams of the 3-level inverters [30-32]. Each of these 6 hexagons, constituting the space vector diagram of a 3-level inverter, centers on the 6 apexes of the medium hexagon, as shown in Figure 6.

Turk J Elec Eng & Comp Sci, Vol.20, No.5, 2012

To simplify to the space vector diagram of a 3-level inverter, 2 steps have to be taken.

First, from the location of a given reference voltage, 1 hexagon has to be selected among the 6 hexagons. There exist some regions that are overlapped by 2 adjacent hexagons. These regions will be equally divided between the 2 hexagons, as shown in Figure 7. Each hexagon is identified by a number, S, defined in Eq. (9).

$$s = \begin{cases} 1 & \text{if } -\pi/6 < \theta < \pi/6 \\ 2 & \text{if } \pi/6 < \theta < \pi/2 \\ 3 & \text{if } \pi/2 < \theta < 5\pi/6 \\ 4 & \text{if } 5\pi/6 < \theta < 7\pi/6 \\ 5 & \text{if } 7\pi/6 < \theta < 3\pi/2 \\ 6 & \text{if } 3\pi/2 < \theta < 11\pi/6 \end{cases}$$

(9)

Second, we translate the origin of the reference voltage vector toward the center of the selected hexagon as indicated in Figure 8. This translation is done by subtracting the center vector of the selected hexagon from the original reference vector. Table 4 gives components d and q of reference voltage  $V^{3*}$  after translation for all 6 hexagons. The index (<sup>5</sup>) or (<sup>3</sup>) above the components indicates 5- or 3-level cases, respectively.

**Figure 6.** Simplification of a 5-level space vector diagram into a 2-level space vector diagram.

Figure 7. Division of overlapped regions.

| Table 4. | Correction | of 5-level | reference | voltage | vector. |

|----------|------------|------------|-----------|---------|---------|

|----------|------------|------------|-----------|---------|---------|

| $\mathbf{S}$ | $v_{d}^{3*}$     | $v_{q}^{3*}$            |

|--------------|------------------|-------------------------|

| 1            | $v_d^{5*} - 1/2$ | $v_{q}^{5*}$            |

| 2            | $v_d^{5*} - 1/4$ | $v_q^{5*} - \sqrt{3}/4$ |

| 3            | $v_d^{5*} + 1/4$ | $v_q^{5*} - \sqrt{3}/4$ |

| 4            | $v_d^{5*} + 1/2$ | $v_{q}^{5*}$            |

| 5            | $v_d^{5*} + 1/4$ | $v_q^{5*} + \sqrt{3}/4$ |

| 6            | $v_d^{5*} - 1/4$ | $v_q^{5*} + \sqrt{3}/4$ |

To simplify to the space vector diagram of a 2-level inverter, we have to take the 2 steps mentioned above. Figure 9 shows the translation of the 3-level reference voltage vector. The correction of its reference voltage vector is presented in Table 5.

Figure 8. Translation of 5-level reference voltage vector.

| s | $v_{d}^{2*}$     | $v_{q}^{2*}$            |

|---|------------------|-------------------------|

| 1 | $v_d^{3*} - 1/4$ | $v_{q}^{3*}$            |

| 2 | $v_d^{3*} - 1/8$ | $v_q^{3*} - \sqrt{3}/8$ |

| 3 | $v_d^{3*} + 1/8$ | $v_q^{3*} - \sqrt{3}/8$ |

| 4 | $v_d^{3*} + 1/4$ | $v_{q}^{3*}$            |

| 5 | $v_d^{3*} + 1/8$ | $v_q^{3*} + \sqrt{3}/8$ |

| 6 | $v_d^{3*} - 1/8$ | $v_a^{3*} + \sqrt{3}/8$ |

Table 5. Correction of 3-level reference voltage vector.

Figure 9. Translation of 3-level reference voltage vector.

# 3. Modeling and control of 5-level PWM current rectifier

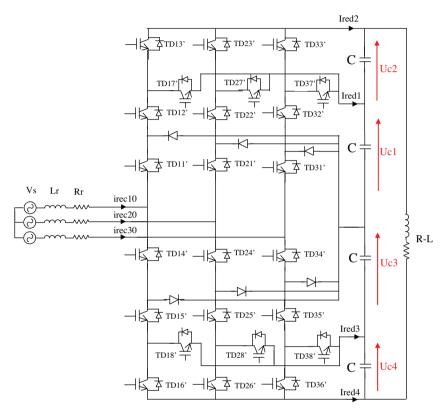

The advantages of 5-level PWM current rectifier topology (Figure 10) are well known and have been applied in medium-voltage and high-power applications in the last years. The reversibility of the 5-level VSI allows it to work as a current rectifier.

Turk J Elec Eng & Comp Sci, Vol.20, No.5, 2012

The rectifier output currents are given as follows:

$$I_{red1} = F'_{17}i_{rec10} + F'_{27}i_{rec20} + F'_{37}i_{rec30}$$

$$I_{red2} = F^{b'}_{11}i_{rec10} + F^{b'}_{21}i_{rec20} + F^{b'}_{31}i_{rec30}$$

$$I_{red3} = F'_{18}i_{rec10} + F'_{28}i_{rec20} + F'_{38}i_{rec30}$$

$$I_{red4} = F^{b'}_{10}i_{rec10} + F^{b'}_{20}i_{rec20} + F^{b'}_{30}i_{rec30}$$

(10)

Figure 10. Five-level PWM current rectifier topology.

The basic principle of the 5-level hysteresis current control is based on the classical hysteresis control applied to conventional 2-level inverters. The 5-level hysteresis control algorithm is given by Eq. (11).

$$\begin{cases} \varepsilon_k > 2 \cdot di \implies B_{i1} = 0, B_{i2} = 0, B_{i3} = 0. \\ di < \varepsilon_k < 2 \cdot di \implies B_{i1} = 0, B_{i2} = 0, B_{i3} = 1. \\ -di < \varepsilon_k < di \implies B_{i1} = 1, B_{i2} = 0, B_{i3} = 0. \\ -2 \cdot di < \varepsilon_k < -di \implies B_{i1} = 1, B_{i2} = 1, B_{i3} = 0. \\ \varepsilon_k < -2 \cdot di \implies B_{i1} = 1, B_{i2} = 1, B_{i3} = 1. \end{cases}$$

(11)

Here,  $\varepsilon_k = i_{reci0} - i_{reci0ref} \cdot \varepsilon_k$  is the difference between reference current  $i_{reci0ref}$  and source current  $i_{reci0}$ , and di is the hysteresis band width.

ABDELKRIM, BERKOUK, BENAMRANE, BENSLIMANE: Study and control of 5-level PWM rectifier-5-level NPC active...,

# 4. Control strategy of multilevel NPC APF

The stabilization of the input DC voltages of a 5-level diode clamped inverter using redundant vectors and feedback control of a 2-level PWM rectifier was treated in [33], and this solution was also applied for a 5-level NPC APF fed by a 3-level PWM rectifier [34].

In this paper, instead of using a 3-level PWM rectifier to feed the APF, we use a 5-level PWM rectifier. The latter improves the quality of the output DC voltage of the rectifier with a reduced switching frequency. Additionally, its input AC voltage and current are less polluted than those of the 3-level rectifier. Furthermore, the 12-kV voltage supported by 4 transistors of 1 leg of the 3-level rectifier will be supported by 8 transistors of 1 leg of the 5-level rectifier, which prolongs the life expectancy of the transistors.

#### 4.1. Redundant vectors algorithm for 5-level APF

To know the impact of each vector on the capacitor voltages, 4 steps must be followed.

The first step consists in defining the equations linking the capacitor currents to load currents for each vector with redundant states. Tables 6-8 present the relationships between the load currents and capacitor currents for all of the redundant vectors of the space vector diagram.

To reduce the size of the control algorithm, the second step consists in forming vector groups that have the same disposition in the table of states D1, D2 and D3. Table 9 shows 6 possible cases of disposition of states D1, D2 and D3. The different groups are listed below.

Group 1: 1, 4, 7, 10, 13, 16 Group 2: 2, 6, 8, 12, 14, 18 Group 3: 3, 5, 9, 11, 15, 17 Group 4: 19, 21, 23, 25, 27, 29 Group 5: 20, 22, 24, 26, 28, 30 Group 6: 31, 32, 33, 34, 35, 36 The third step consists in anal

The third step consists in analyzing the influence of different groups of redundant vectors on capacitor voltages under different conditions of load currents. From Table 9, it can be noted that some vectors depend on D1 (groups 1, 4, and 6) and others depend on D1, D2, and D3 (groups 2, 3, and 5).

For vectors depending on D1, there are 2 possibilities of polarity according to the load currents. Each possibility is associated with the logic function in the following manner:

$$\begin{cases}

P_1 = 1 \text{ if } D1 \ge 0elseP_1 = 0 \\

P_2 = 1 \text{ if } D1 < 0elseP_2 = 0

\end{cases}$$

(12)

For vectors depending on D1, D2, and D3, there are 6 possible combinations according to the load currents, associated with 6 logic functions defined as follows:

$$\begin{cases}

P_{1} = 1 & \text{if} \quad D1 < 0, D2 < 0, D3 \ge 0elseP_{1} = 0 \\

P_{2} = 1 & \text{if} \quad D1 < 0, D2 \ge 0, D3 < 0elseP_{2} = 0 \\

P_{3} = 1 & \text{if} \quad D1 < 0, D2 \ge 0, D3 \ge 0elseP_{3} = 0 \\

P_{4} = 1 & \text{if} \quad D1 \ge 0, D2 < 0, D3 < 0elseP_{4} = 0 \\

P_{5} = 1 & \text{if} \quad D1 \ge 0, D2 < 0, D3 \ge 0elseP_{5} = 0 \\

P_{6} = 1 & \text{if} \quad D1 \ge 0, D2 \ge 0, D3 < 0elseP_{6} = 0

\end{cases}$$

(13)

|       | vec | tors   | $4 i_{c1}$ | $4 i_{c2}$ | $4 i_{c3}$ | $4 i_{c4}$ | D1=      | D2 =         | D3=           |

|-------|-----|--------|------------|------------|------------|------------|----------|--------------|---------------|

| V1 -  | a   | P2N1N1 | D1         | D1         | D1         | -3D1       | -i1      |              |               |

| V I   | b   | P1N2N2 | D1         | 3D1        | D1         | D1         | -11      |              |               |

| V2 -  | a   | P2ON1  | D1         | D1         | D2         | D3         | :1 : :0  | :1 9:0       | 2:1 + :0      |

| V Z   | b   | P1N1N2 | D1         | D3         | D1         | D2         | -i1+i2   | -i1-3i2      | 3i1+i2        |

| V3    | a   | P2P1N1 | D1         | D2         | D1         | D3         | -i1-2i2  | -i1+2i2      | 3i1+2i2       |

| v.5   | b   | P1ON2  | D2         | D3         | D1         | D1         | -11-212  | -11+212      | $311 \pm 212$ |

| V4 -  | a   | P2P2N1 | D1         | D1         | D1         | -3D1       | -(i1+i2) |              |               |

| V 4   | b   | P1P1N2 | D1         | -3D1       | D1         | D1         | -(11+12) |              |               |

| V5 –  | a   | P1P2N1 | D1         | D2         | D1         | D3         | -2i1-i2  | 2i1-i2       | 2i1+3i2       |

| v.5   | b   | OP1N2  | D2         | D3         | D1         | D1         | -211-12  | 211-12       | 211+312       |

| V6 –  | a   | OP2N1  | D1         | D1         | D2         | D3         | i1-i2    | -3i1-i2      | i1+3i2        |

| VO    | b   | N1P1N2 | D1         | D3         | D1         | D2         | 11-12    | -311-12      | $11 \pm 312$  |

| V7 -  | a   | N1P2N1 | D1         | D1         | D1         | -3D1       | -i2      |              |               |

| V 1   | b   | N2P1N2 | D1         | -3D1       | D1         | D1         | -12      |              |               |

| V8 -  | a   | N1P2O  | D1         | D1         | D2         | D3         | -i1-2i2  | 3i1+2i2      | -i1+2i2       |

| VO    | b   | N2P1N1 | D1         | D3         | D1         | D2         | -11-212  | 5117212      | -11-212       |

| V9 -  | a   | N1P2P1 | D1         | D2         | D1         | D3         | 21132    | -2i1-3i2     | -2i1+i2       |

| V 9   | b   | N2P1O  | D2         | D3         | D1         | D1         | 2i1+i2   | -211-512     | -211+12       |

| V10   | a   | N1P2P2 | D1         | D1         | D1         | -3D1       | i1       |              |               |

| V 10  | b   | N2P1P1 | D1         | -3D1       | D1         | D1         | 11       |              |               |

| V11   | a   | N1P1P2 | D1         | D2         | D1         | D3         | i1-i2    | i1+3i2       | -3i1-i2       |

| VII   | b   | N2OP1  | D2         | D3         | D1         | D1         | 11-12    | $11 \pm 012$ | -511-12       |

| V12   | a   | N1OP2  | D1         | D1         | D2         | D3         | i1+2i2   | i1-2i2       | -3i1-2i2      |

| V 12  | b   | N2N1P1 | D1         | D3         | D1         | D2         | 117212   | 11-212       | -011-212      |

| V13 - | a   | N1N1P2 | D1         | D1         | D1         | -3D1       | i1+i2    |              |               |

| V 15  | b   | N2N2P1 | D1         | -3D1       | D1         | D1         | 11 - 12  |              |               |

| V14   | a   | ON1P2  | D1         | D1         | D2         | D3         | 2i1+i2   | -2i1+i2      | -2i1-3i2      |

| VIA   | b   | N1N2P1 | D1         | D3         | D1         | D2         | 211   12 | -211   12    | -211-012      |

| V15 - | a   | P1N1P2 | D1         | D2         | D1         | D3         | -i1+i2   | 3i1+i2       | -i1-3i2       |

| V 10  | b   | ON2P1  | D2         | D3         | D1         | D1         | -11   12 | 011   12     | 11 012        |

| V16   | a   | P2N1P2 | D1         | D1         | D1         | -3D1       | i2       |              |               |

| 10    | b   | P1N2P1 | D1         | -3D1       | D1         | D1         | 12       |              |               |

| V17   | a   | P2N1P1 | D1         | D2         | D1         | D3         | i1+2i2   | -3i1-2i2     | i1-2i2        |

| V I I | b   | P1N2O  | D2         | D3         | D1         | D1         | 11   212 | -011-212     | 11-212        |

| V18 – | a   | P2N1O  | D1         | D1         | D2         | D3         | -2i1-i2  | 2i1+3i2      | 2i1-i2        |

| V 10  | b   | P1N2N1 | D1         | D3         | D1         | D2         | -211-12  | 2117012      | 211-12        |

Table 6. Relationship between load currents and capacitor currents for the vectors with 2 redundant states.

The influence of different groups of redundant vectors on capacitor voltages depends on the logic function  $P_i$ , as shown in Tables 10.1 through 10.6. In these tables, (+) indicates that the redundant vectors of the concerned group charge the capacitor and consequently increase the capacitor voltage. On the other hand, (-) indicates that the redundant vectors of the concerned group discharge the capacitor and consequently decrease its voltage.

|     | Vec | tors   | $4 i_{c1}$ | $4 i_{c2}$ | 4 i <sub>c3</sub> | $4 i_{c4}$ | D1=      | D2=       | D3=      |

|-----|-----|--------|------------|------------|-------------------|------------|----------|-----------|----------|

|     | a   | P2OO   | D1         | D1         | -D1               | -D1        |          |           |          |

| V19 | b   | P1N1N1 | D1         | -D1        | D1                | -D1        | -2i1     |           |          |

|     | с   | ON2N2  | -D1        | -D1        | D1                | D1         |          |           |          |

|     | а   | P2P1O  | D1         | D2         | D3                | D3         |          |           |          |

| V20 | b   | P1ON1  | D2         | D3         | D1                | D3         | -2i1-3i2 | -2i1+i2   | 2i1+i2   |

|     | с   | ON1N2  | D3         | D3         | D2                | D1         |          |           |          |

|     | a   | P2P2O  | D1         | D1         | -D1               | -D1        |          |           |          |

| V21 | b   | P1P1N1 | D1         | -D1        | D1                | -D1        | -2i1-2i2 |           |          |

|     | с   | OON2   | -D1        | -D1        | D1                | D1         |          |           |          |

|     | a   | P1P2O  | D1         | D2         | D3                | D3         |          |           |          |

| V22 | b   | OP1N1  | D2         | D3         | D1                | D3         | -3i1-2i2 | i1-2i2    | i1 + 2i2 |

|     | с   | N1ON2  | D3         | D3         | D2                | D1         |          |           |          |

|     | a   | OP2O   | D1         | D1         | -D1               | -D1        |          |           |          |

| V23 | b   | N1P1N1 | D1         | -D1        | D1                | -D1        | -2i2     |           |          |

|     | с   | N2ON2  | -D1        | -D1        | D1                | D1         |          |           |          |

|     | a   | OP2P1  | D1         | D2         | D3                | D3         |          |           |          |

| V24 | b   | N1P1O  | D2         | D3         | D1                | D3         | 3i1+i2   | -i1-3i2   | -i1+i2   |

|     | с   | N2ON1  | D3         | D3         | D2                | D1         |          |           |          |

|     | a   | OP2P2  | D1         | D1         | -D1               | -D1        |          |           |          |

| V25 | b   | N1P1P1 | D1         | -D1        | D1                | -D1        | 2i1      |           |          |

|     | с   | N2OO   | -D1        | -D1        | D1                | D1         |          |           |          |

|     | а   | OP1P2  | D1         | D2         | D3                | D3         |          |           |          |

| V26 | b   | N1OP1  | D2         | D3         | D1                | D3         | 2i1-i2   | 2i1+3i2   | -2i1-i2  |

|     | с   | N2N1O  | D3         | D3         | D2                | D1         |          |           |          |

|     | а   | OOP2   | D1         | D1         | -D1               | -D1        |          |           |          |

| V27 | b   | N1N1P1 | D1         | -D1        | D1                | -D1        | 2i1+2i2  |           |          |

|     | с   | N2N2O  | -D1        | -D1        | D1                | D1         |          |           |          |

|     | a   | P1OP2  | D1         | D2         | D3                | D3         |          |           |          |

| V28 | b   | ON1P1  | D2         | D3         | D1                | D3         | -i1+2i2  | 3i1 + 2i2 | -i1-2i2  |

|     | с   | N1N2O  | D3         | D3         | D2                | D1         |          |           |          |

|     | a   | P2OP2  | D1         | D1         | -D1               | -D1        |          |           |          |

| V29 | b   | P1N1P1 | D1         | -D1        | D1                | -D1        | 2i2      |           |          |

|     | с   | ON2O   | -D1        | -D1        | D1                | D1         |          |           |          |

|     | a   | P2OP1  | D1         | D2         | D3                | D3         |          |           |          |

| V30 | b   | P1N1O  | D2         | D3         | D1                | D3         | i1+3i2   | -3i1-i2   | i1-i2    |

|     | с   | ON2N1  | D3         | D3         | D2                | D1         | 1        |           |          |

Table 7. Relationship between load currents and capacitor currents for vectors with 3 redundant states.

The fourth step consists in choosing the redundancies. For each case of redundancy, the vector that tends to cancel the unbalance in the capacitor voltages will be selected. In other words, we select the vector that charges the undercharged capacitors and discharges the overcharged ones.

To do so, we must define the different cases of capacitor voltages and their derivations. We get 24 cases. For each selected vector, the redundancy that will decrease the largest capacitor voltage and increase the smallest capacitor voltage is selected (Table 11).

Turk J Elec Eng & Comp Sci, Vol.20, No.5, 2012

|      | Vec | tors   | $4 i_{c1}$ | $4 i_{c2}$ | 4 i <sub>c3</sub> | $4 i_{c4}$ | D1=    | D2= | D3= |

|------|-----|--------|------------|------------|-------------------|------------|--------|-----|-----|

|      | a   | P2P1P1 | D1         | -3D1       | D1                | D1         |        |     |     |

| 1791 | b   | P100   | -3D1       | D1         | D1                | D1         | :1     |     |     |

| V31  | с   | ON1N1  | D1         | D1         | -3D1              | D1         | i1     |     |     |

|      | d   | N1N2N2 | D1         | D1         | D1                | -3D1       |        |     |     |

|      | a   | P2P2P1 | D1         | -3D1       | D1                | D1         |        |     |     |

| V32  | b   | P1P1O  | -3D1       | D1         | D1                | D1         | i1+i2  |     |     |

| V 32 | с   | OON1   | D1         | D1         | -3D1              | D1         | 11+12  |     |     |

|      | d   | N1N1N2 | D1         | D1         | D1                | -3D1       |        |     |     |

|      | a   | P1P2P1 | D1         | -3D1       | D1                | D1         |        |     |     |

| V33  | b   | OP10   | -3D1       | D1         | D1                | D1         | i2     |     |     |

| 100  | с   | N1ON1  | D1         | D1         | -3D1              | D1         | 12     |     |     |

|      | d   | N2N1N2 | D1         | D1         | D1                | -3D1       |        |     |     |

|      | a   | P1P2P2 | D1         | -3D1       | D1                | D1         |        |     |     |

| V34  | b   | OP1P1  | -3D1       | D1         | D1                | D1         | -i1    |     |     |

| V 54 | с   | N100   | D1         | D1         | -3D1              | D1         | -11    |     |     |

|      | d   | N2N1N1 | D1         | D1         | D1                | -3D1       |        |     |     |

|      | a   | P1P1P2 | D1         | -3D1       | D1                | D1         |        |     |     |

| V35  | b   | OOP1   | -3D1       | D1         | D1                | D1         | -i1-i2 |     |     |

| V 55 | с   | N1N1O  | D1         | D1         | -3D1              | D1         | -11-12 |     |     |

|      | d   | N2N2N1 | D1         | D1         | D1                | -3D1       |        |     |     |

|      | а   | P2P1P2 | D1         | -3D1       | D1                | D1         |        |     |     |

| V36  | b   | P10P1  | -3D1       | D1         | D1                | D1         | -i2    |     |     |

| V 30 | с   | ON10   | D1         | D1         | -3D1              | D1         | -12    |     |     |

|      | d   | N1N2N1 | D1         | D1         | D1                | -3D1       |        |     |     |

Table 8. Relationship between load currents and capacitor currents for vectors with 4 redundant states.

Table 9. Disposition of states D1, D2, and D3.

| r           |      |        |           |           |           |           | D4       | D û     | Da            |

|-------------|------|--------|-----------|-----------|-----------|-----------|----------|---------|---------------|

|             | vect | ors    | $4i_{c1}$ | $4i_{c2}$ | $4i_{c3}$ | $4i_{c4}$ | D1       | D2      | D3            |

| V1          | (a)  | P2N1N1 | D1        | D1        | D1        | -3D1      | -i1      |         |               |

| V I         | (b)  | P1N2N2 | D1        | -3D1      | D1        | D1        | -11      |         |               |

| V2          | (a)  | P2ON1  | D1        | D1        | D2        | D3        | -i1+i2   | -i1-3i2 | 3i1+i2        |

| V Z         | (b)  | P1N1N2 | D1        | D3        | D1        | D2        | -11+12   | -11-312 | $311 \pm 12$  |

| V3          | (a)  | P2P1N1 | D1        | D2        | D1        | D3        | -i1-2i2  | -i1+2i2 | 3i1+2i2       |

| v 3         | (b)  | P1ON2  | D2        | D3        | D1        | D1        | -11-212  | -11+212 | $311 \pm 212$ |

|             | (a)  | P2OO   | D1        | D1        | -D1       | -D1       |          |         |               |

| V19         | (b)  | P1N1N1 | D1        | -D1       | D1        | -D1       | -2i1     |         |               |

|             | (c)  | ON2N2  | -D1       | -D1       | D1        | D1        |          |         |               |

|             | (a)  | P2P1O  | D1        | D2        | D3        | D3        |          |         |               |

| V20         | (b)  | P1ON1  | D2        | D3        | D1        | D3        | -2i1-3i2 | -2i1+i2 | 2i1+i2        |

|             | (c)  | ON1N2  | D3        | D3        | D2        | D1        |          |         |               |

|             | (a)  | P2P1P1 | D1        | -3D1      | D1        | D1        |          |         |               |

| <b>W</b> 91 | (b)  | P100   | -3D1      | D1        | D1        | D1        | :1       |         |               |

| V31         | (c)  | ON1N1  | D1        | D1        | -3D1      | D1        | i1       |         |               |

|             | (d)  | N1N2N2 | D1        | D1        | D1        | -3D1      |          |         |               |

|       | R        | edund    | ancy (   | a)       | Redundancy (b) |          |          |          |  |

|-------|----------|----------|----------|----------|----------------|----------|----------|----------|--|

|       | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$       | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ |  |

| $P_1$ | +        | +        | +        | -        | +              | -        | +        | +        |  |

| $P_2$ | -        | -        | -        | +        | -              | +        | -        | -        |  |

Table 10.1. Effect of redundant vectors of group 1 on capacitor voltages.

Table 10.2. Effect of redundant vectors of group 2 on capacitor voltages.

|       | R        | edund    | ancy (   | a)       | Redundancy (b) |          |          |          |  |

|-------|----------|----------|----------|----------|----------------|----------|----------|----------|--|

|       | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$       | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ |  |

| $P_1$ | -        | -        | -        | +        | -              | +        | -        | -        |  |

| $P_2$ | -        | -        | +        | -        | -              | -        | -        | +        |  |

| $P_3$ | -        | -        | +        | +        | -              | +        | -        | +        |  |

| $P_4$ | +        | +        | -        | -        | +              | -        | +        | -        |  |

| $P_5$ | +        | +        | -        | +        | +              | +        | +        | -        |  |

| $P_6$ | +        | +        | +        | -        | +              | -        | +        | +        |  |

Table 10.3. Effect of redundant vectors of group 3 on capacitor voltages.

|       | R        | edund    | ancy (   | R        | edunda   | ancy (   | b)       |          |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|

|       | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ |

| $P_1$ | -        | -        | -        | +        | -        | +        | -        | -        |

| $P_2$ | -        | +        | -        | -        | +        | -        | -        | -        |

| $P_3$ | -        | -        | -        | +        | +        | +        | -        | -        |

| $P_4$ | +        | -        | +        | -        | -        | -        | +        | +        |

| $P_5$ | +        | -        | +        | +        | -        | +        | +        | +        |

| $P_6$ | +        | +        | +        | -        | +        | -        | +        | +        |

Table 10.4. Effect of redundant vectors of group 4 on capacitor voltages.

|       | Redu     | indanc   | y (a)    |          | Redu     | indanc   | y (b)    |          | Redundancy (c) |          |          |          |  |  |  |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------------|----------|----------|----------|--|--|--|

|       | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$       | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ |  |  |  |

| $P_1$ | +        | +        | -        | -        | +        | -        | +        | -        | -              | -        | +        | +        |  |  |  |

| $P_2$ | -        | -        | +        | +        | -        | +        | -        | +        | +              | +        | -        | -        |  |  |  |

Table 10.5. Effect of redundant vectors of group 5 on capacitor voltages.

|       | R        | edund    | ancy (a  | a)       | R        | edunda   | ancy (   | b)       | Redundancy (c) |          |          |          |  |  |  |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------------|----------|----------|----------|--|--|--|

|       | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$       | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ |  |  |  |

| $P_1$ | 1        | -        | +        | +        | -        | +        | 1        | +        | +              | +        | -        | -        |  |  |  |

| $P_2$ | -        | +        | -        | -        | +        | -        | -        | -        | -              | -        | +        | -        |  |  |  |

| $P_3$ | -        | +        | +        | +        | +        | +        | -        | +        | +              | +        | +        | -        |  |  |  |

| $P_4$ | +        | -        | -        | -        | -        | -        | +        | -        | -              | -        | -        | +        |  |  |  |

| $P_5$ | +        | -        | +        | +        | -        | +        | +        | +        | +              | +        | -        | +        |  |  |  |

| $P_6$ | +        | +        | -        | -        | +        | -        | +        | -        | -              | -        | +        | +        |  |  |  |

|       | Redundancy (a) |          |          |          |          | edunda   | ancy (   | b)       | R        | edund    | ancy (   | c)       | Redundancy (d) |          |          |          |  |

|-------|----------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------------|----------|----------|----------|--|

|       | $U_{c1}$       | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$ | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ | $U_{c1}$       | $U_{c2}$ | $U_{c3}$ | $U_{c4}$ |  |

| $P_1$ | +              | -        | +        | +        | -        | +        | +        | +        | +        | +        | -        | +        | +              | +        | +        | -        |  |

| $P_2$ | -              | +        | -        | -        | +        | -        | -        | -        | -        | -        | +        | -        | -              | -        | -        | +        |  |

Table 10.6. Effect of redundant vectors of group 6 on capacitor voltages.

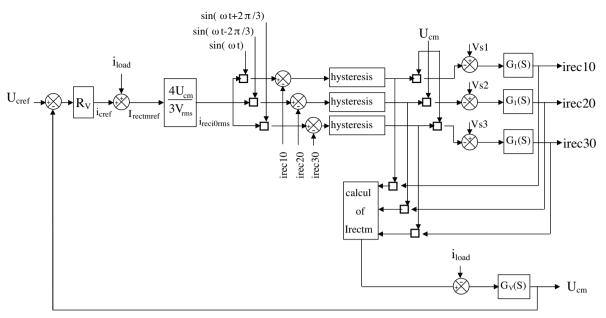

# 4.2. Feedback control of the multilevel rectifier

In this part, enslavement of the output DC voltage of the 5-level PWM current rectifier using a PI-based feedback control is proposed. The synoptic diagram of the 5-level PWM current rectifier control is shown in Figure 11. The transfer functions  $G_I(S)$  and  $G_V(S)$  are expressed as follows:

| Groups                                                                                                                                                                                                                                                                                  | 1  | 1  |    |    | 2  | 2  |    |    |    |    | 1  | 3  |    |    | 4  | 1  | 5  |    |    |    |    |    | 6  |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Possibility<br>Derivation case                                                                                                                                                                                                                                                          | P1 | P2 | P1 | P2 | Р3 | P4 | Р5 | P6 | P1 | P2 | Р3 | P4 | Р5 | P6 | P1 | P2 | P1 | P2 | P3 | P4 | Р5 | P6 | P1 | P2 |

| Uc1 <uc2<uc3<uc4< td=""><td>a</td><td>b</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>b</td><td>b</td><td>а</td><td>а</td><td>а</td><td>a</td><td>с</td><td>с</td><td>b</td><td>с</td><td>а</td><td>с</td><td>а</td><td>d</td><td>b</td></uc2<uc3<uc4<> | a  | b  | b  | a  | b  | а  | b  | а  | b  | b  | b  | а  | а  | а  | a  | с  | с  | b  | с  | а  | с  | а  | d  | b  |

| Uc1 <uc2<uc4<uc3< td=""><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>b</td><td>b</td><td>а</td><td>а</td><td>а</td><td>а</td><td>с</td><td>c</td><td>b</td><td>b</td><td>а</td><td>с</td><td>а</td><td>с</td><td>b</td></uc2<uc4<uc3<> | а  | b  | b  | а  | b  | а  | а  | а  | b  | b  | b  | а  | а  | а  | а  | с  | c  | b  | b  | а  | с  | а  | с  | b  |

| Uc1 <uc3<uc2<uc4< td=""><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>b</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>с</td><td>c</td><td>b</td><td>с</td><td>а</td><td>а</td><td>b</td><td>d</td><td>b</td></uc3<uc2<uc4<> | а  | b  | b  | а  | а  | b  | b  | а  | b  | b  | b  | а  | а  | а  | b  | с  | c  | b  | с  | а  | а  | b  | d  | b  |

| Uc1 <uc3<uc4<uc2< td=""><td>b</td><td>а</td><td>а</td><td>а</td><td>а</td><td>b</td><td>b</td><td>b</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>с</td><td>а</td><td>а</td><td>b</td><td>а</td><td>b</td></uc3<uc4<uc2<> | b  | а  | а  | а  | а  | b  | b  | b  | а  | b  | b  | а  | а  | b  | b  | а  | а  | b  | с  | а  | а  | b  | а  | b  |

| Uc1 <uc4<uc2<uc3< td=""><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>а</td><td>а</td><td>b</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>а</td><td>c</td><td>c</td><td>b</td><td>b</td><td>а</td><td>c</td><td>а</td><td>c</td><td>b</td></uc4<uc2<uc3<> | b  | а  | а  | а  | b  | а  | а  | b  | а  | b  | b  | а  | а  | b  | а  | c  | c  | b  | b  | а  | c  | а  | c  | b  |

| Uc1 <uc4<uc3<uc2< td=""><td>b</td><td>а</td><td>а</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>a</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>а</td><td>b</td></uc4<uc3<uc2<> | b  | а  | а  | b  | a  | b  | а  | b  | a  | b  | b  | а  | а  | b  | b  | а  | а  | b  | b  | а  | а  | b  | а  | b  |

| Uc2 <uc1<uc3<uc4< td=""><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>а</td><td>а</td><td>с</td><td>с</td><td>а</td><td>c</td><td>а</td><td>с</td><td>а</td><td>d</td><td>a</td></uc1<uc3<uc4<> | а  | b  | b  | а  | b  | а  | b  | а  | b  | a  | b  | а  | b  | а  | а  | с  | с  | а  | c  | а  | с  | а  | d  | a  |

| Uc2 <uc1<uc4<uc3< td=""><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>а</td><td>а</td><td>с</td><td>c</td><td>а</td><td>b</td><td>а</td><td>с</td><td>а</td><td>с</td><td>a</td></uc1<uc4<uc3<> | а  | b  | b  | а  | b  | а  | а  | а  | b  | a  | b  | а  | b  | а  | а  | с  | c  | а  | b  | а  | с  | а  | с  | a  |

| Uc2 <uc3<uc1<uc4< td=""><td>a</td><td>b</td><td>b</td><td>a</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>a</td><td>b</td><td>a</td><td>a</td><td>с</td><td>с</td><td>a</td><td>c</td><td>b</td><td>b</td><td>а</td><td>d</td><td>a</td></uc3<uc1<uc4<> | a  | b  | b  | a  | b  | a  | b  | а  | b  | а  | b  | a  | b  | a  | a  | с  | с  | a  | c  | b  | b  | а  | d  | a  |

| Uc2 <uc3<uc4<uc1< td=""><td>a</td><td>b</td><td>b</td><td>a</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>а</td><td>a</td><td>b</td><td>b</td><td>a</td><td>с</td><td>с</td><td>b</td><td>a</td><td>а</td><td>b</td><td>b</td><td>с</td><td>b</td><td>a</td></uc3<uc4<uc1<> | a  | b  | b  | a  | b  | a  | b  | а  | b  | а  | a  | b  | b  | a  | с  | с  | b  | a  | а  | b  | b  | с  | b  | a  |

| Uc2 <uc4<uc1<uc3< td=""><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>c</td><td>c</td><td>а</td><td>c</td><td>a</td></uc4<uc1<uc3<> | а  | b  | b  | а  | b  | а  | а  | а  | b  | а  | а  | b  | b  | а  | а  | b  | b  | а  | b  | c  | c  | а  | c  | a  |

| Uc2 <uc4<uc3<uc1< td=""><td>а</td><td>b</td><td>b</td><td>b</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>с</td><td>b</td><td>b</td><td>а</td><td>а</td><td>c</td><td>b</td><td>c</td><td>b</td><td>a</td></uc4<uc3<uc1<> | а  | b  | b  | b  | b  | а  | а  | а  | b  | а  | а  | b  | b  | а  | с  | b  | b  | а  | а  | c  | b  | c  | b  | a  |

| Uc3 <uc1<uc2<uc4< td=""><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>b</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>c</td><td>c</td><td>с</td><td>с</td><td>b</td><td>а</td><td>b</td><td>d</td><td>c</td></uc1<uc2<uc4<> | а  | b  | b  | а  | а  | b  | b  | а  | b  | b  | b  | а  | а  | а  | b  | c  | c  | с  | с  | b  | а  | b  | d  | c  |

| Uc3 <uc1<uc4<uc2< td=""><td>b</td><td>а</td><td>а</td><td>а</td><td>а</td><td>b</td><td>b</td><td>b</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>с</td><td>с</td><td>b</td><td>а</td><td>b</td><td>а</td><td>c</td></uc1<uc4<uc2<> | b  | а  | а  | а  | а  | b  | b  | b  | а  | b  | b  | а  | а  | b  | b  | а  | а  | с  | с  | b  | а  | b  | а  | c  |

| Uc3 <uc2<uc1<uc4< td=""><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>с</td><td>c</td><td>с</td><td>с</td><td>b</td><td>b</td><td>b</td><td>d</td><td>c</td></uc2<uc1<uc4<> | а  | b  | b  | а  | а  | b  | b  | а  | b  | а  | b  | а  | b  | а  | b  | с  | c  | с  | с  | b  | b  | b  | d  | c  |

| Uc3 <uc2<uc4<uc1< td=""><td>a</td><td>b</td><td>b</td><td>a</td><td>a</td><td>b</td><td>b</td><td>а</td><td>b</td><td>а</td><td>a</td><td>b</td><td>b</td><td>a</td><td>с</td><td>a</td><td>a</td><td>с</td><td>а</td><td>b</td><td>b</td><td>с</td><td>b</td><td>с</td></uc2<uc4<uc1<> | a  | b  | b  | a  | a  | b  | b  | а  | b  | а  | a  | b  | b  | a  | с  | a  | a  | с  | а  | b  | b  | с  | b  | с  |

| Uc3 <uc4<uc1<uc2< td=""><td>b</td><td>a</td><td>a</td><td>a</td><td>a</td><td>b</td><td>b</td><td>b</td><td>а</td><td>b</td><td>a</td><td>b</td><td>a</td><td>b</td><td>с</td><td>a</td><td>a</td><td>с</td><td>а</td><td>b</td><td>a</td><td>с</td><td>a</td><td>с</td></uc4<uc1<uc2<> | b  | a  | a  | a  | a  | b  | b  | b  | а  | b  | a  | b  | a  | b  | с  | a  | a  | с  | а  | b  | a  | с  | a  | с  |

| Uc3 <uc4<uc2<uc1< td=""><td>b</td><td>a</td><td>a</td><td>a</td><td>a</td><td>b</td><td>b</td><td>b</td><td>а</td><td>а</td><td>a</td><td>b</td><td>b</td><td>b</td><td>с</td><td>a</td><td>a</td><td>с</td><td>а</td><td>b</td><td>b</td><td>с</td><td>b</td><td>с</td></uc4<uc2<uc1<> | b  | a  | a  | a  | a  | b  | b  | b  | а  | а  | a  | b  | b  | b  | с  | a  | a  | с  | а  | b  | b  | с  | b  | с  |

| Uc4 <uc1<uc2<uc3< td=""><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>b</td><td>b</td><td>b</td><td>с</td><td>c</td><td>а</td><td>с</td><td>d</td></uc1<uc2<uc3<> | b  | а  | а  | b  | b  | а  | а  | b  | а  | b  | а  | b  | а  | b  | а  | b  | b  | b  | b  | с  | c  | а  | с  | d  |

| Uc4 <uc1<uc3<uc2< td=""><td>b</td><td>а</td><td>а</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>с</td><td>а</td><td>а</td><td>b</td><td>b</td><td>с</td><td>а</td><td>с</td><td>а</td><td>d</td></uc1<uc3<uc2<> | b  | а  | а  | b  | a  | b  | а  | b  | а  | b  | а  | b  | а  | b  | с  | а  | а  | b  | b  | с  | а  | с  | а  | d  |

| Uc4 <uc2<uc1<uc3< td=""><td>b</td><td>а</td><td>а</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>b</td><td>b</td><td>а</td><td>b</td><td>b</td><td>а</td><td>b</td><td>с</td><td>с</td><td>а</td><td>с</td><td>d</td></uc2<uc1<uc3<> | b  | а  | а  | b  | b  | а  | а  | b  | а  | а  | а  | b  | b  | b  | а  | b  | b  | а  | b  | с  | с  | а  | с  | d  |

| Uc4 <uc2<uc3<uc1< td=""><td>b</td><td>а</td><td>a</td><td>b</td><td>b</td><td>а</td><td>а</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>b</td><td>b</td><td>с</td><td>b</td><td>b</td><td>а</td><td>а</td><td>с</td><td>b</td><td>с</td><td>b</td><td>d</td></uc2<uc3<uc1<> | b  | а  | a  | b  | b  | а  | а  | b  | а  | а  | а  | b  | b  | b  | с  | b  | b  | а  | а  | с  | b  | с  | b  | d  |

| Uc4 <uc3<uc1<uc2< td=""><td>b</td><td>а</td><td>а</td><td>b</td><td>a</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>c</td><td>а</td><td>а</td><td>с</td><td>а</td><td>с</td><td>а</td><td>с</td><td>а</td><td>d</td></uc3<uc1<uc2<> | b  | а  | а  | b  | a  | b  | а  | b  | а  | b  | а  | b  | а  | b  | c  | а  | а  | с  | а  | с  | а  | с  | а  | d  |

| Uc4 <uc3<uc2<uc1< td=""><td>b</td><td>а</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>b</td><td>а</td><td>а</td><td>а</td><td>b</td><td>b</td><td>b</td><td>c</td><td>а</td><td>а</td><td>с</td><td>а</td><td>с</td><td>b</td><td>с</td><td>b</td><td>d</td></uc3<uc2<uc1<> | b  | а  | а  | b  | а  | b  | а  | b  | а  | а  | а  | b  | b  | b  | c  | а  | а  | с  | а  | с  | b  | с  | b  | d  |

Table 11. Selection of redundancies.

$$G_I(S) = \frac{(1/R_r)}{1 + (L_r/R_r)S},$$

(14)

$$G_V(S) = \frac{1}{CS}.$$

(15)

The modeling of this loop is based on the instantaneous power conservation principle with no loss hypothesis. This loop imposes the root mean square (rms) value of network current.

Figure 11. Synoptic diagram of 5-level PWM current rectifier control.

Input and output powers are:

$$\begin{cases}

P_{in} = \sum_{i=1}^{3} \left( V_{si} i_{reci0} - R_r i_{reci0}^2 - \frac{L_r}{2} \frac{di_{reci0}^2}{dt} \right) \\

P_{out} = \sum_{i=1}^{4} \left( U_{rci} i_{reci} \right) = 4U_{cm} (i_c + i_{load})

\end{cases}$$

(16)

Different quantities  $i_{load}$ ,  $i_c$ , and  $I_{rectm}$  (Figure 11) are defined as follows:

$$\begin{aligned}

Irectm &= \frac{Ired1 + 2Ired2 - Ired3 - 2Ired4}{4} \\

i_{load} &= \frac{id1 + 2id2 - id3 - 2id4}{4} \\

i_c &= Irectm - i_{load}

\end{aligned}$$

(17)

Using the power conservation principle and neglecting joule loss in resistor  $\mathbf{R}_r$ , and considering a sinusoidal supply network current in phase with corresponding voltage  $\mathbf{V}_{si}$ , it can be written as:

$$3V_{si}i_{reci0} = 4U_{cm}(i_c + i_{load}).$$

<sup>(18)</sup>

### 4.3. Sliding mode control of the multilevel APF

The APF is controlled using a sliding mode regulator [7-9,35,36]. From the model of the active filter associated with the supply network in Eq. (19), and by considering the error between the harmonic current reference and the active filter current as a sliding surface in Eq. (20) and the smooth continuous function as an attractive control function Eq. (21), one gets the control law in Eq. (22).

$$V_{frefK} - V_K = R_f i_{fK} + L_f \frac{di_{fK}}{dt},$$

(19)

with:

$$V_{K} = V_{sK} - R_{s}i_{SK} - L_{s}\frac{di_{sK}}{dt};$$

$$K = 1, 2, and3.$$

$$S = i_{frefK} - i_{fK}$$

(20)

$$U_n = k \cdot \frac{S(x)}{|S(x)| + \lambda} \tag{21}$$

$$V_{frefK} = R_f i_{fK} + L_f \frac{di_{frefK}}{dt} + V_K + k \frac{S}{|S| + \lambda}$$

$$\tag{22}$$

### 5. Simulation results

A medium-voltage electric power source of 5.5 kV and 50 Hz feeds an induction motor speed variator as illustrated in Figure 1.

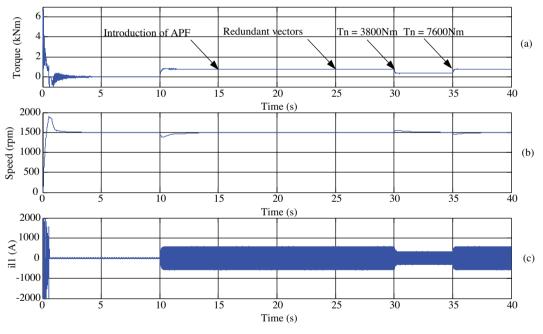

The motor speed and torque are presented in Figures 12a and 12b. At t = 10 s, rated torque (Tn = 7.6 kN m) is applied. It is noted that the speed returns to its reference (1500 rpm) after a slight decrease.

The current drawn by the speed variator is distorted with 97% total harmonic distortion (THD), which is above the tolerated THD standard limit (Figure 12c).

Figure 12. Torque, speed, and load currents.

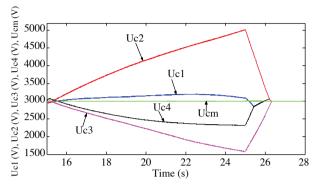

The first part of the simulation was dedicated to investigating the performance of the redundant vectors control algorithm (RVCA). For that, active power filtering was introduced at t = 15 s without application of the RVCA. Capacitor voltages diverge, but the average capacitor voltage mean value (Ucm) remains constant thanks to the feedback control of the 5-level PWM rectifier (Figure 13). Application of the proposed redundant

ABDELKRIM, BERKOUK, BENAMRANE, BENSLIMANE: Study and control of 5-level PWM rectifier-5-level NPC active...,

vectors-based SVPWM algorithm at t = 25 s pushes capacitor voltages toward the reference value of 3 kV, keeping them constant.

Figure 13. DC bus capacitors voltages of 5-level APF.

The second part of the simulation was devoted to testing the performance of the APF.

The instantaneous real and imaginary powers method was used to identify reference harmonic currents [37].

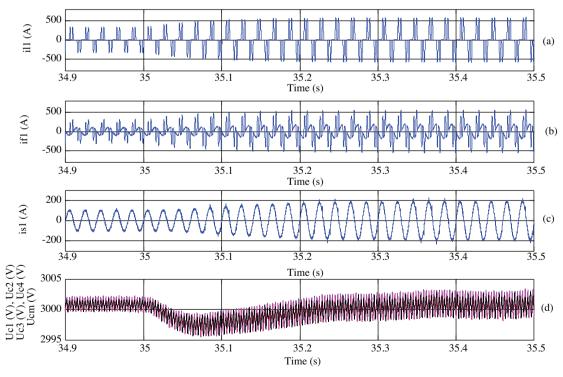

As shown in Figure 12a, at t = 35 s, the torque value changes from 1/2 Tn to Tn (Tn is the rated or the nominal torque). This increase in mechanical load torque implies the increase of the nonlinear load current amplitude (the rectifier feeding the inverter), as depicted in Figure 14a. As a consequence, filter and power supply current amplitudes increase, as well (Figures 14b and 14c). The capacitor voltages return to the reference value after a slight decrease (Figure 14d).

Figure 14. Load current, filter current, power supply current, and capacitor voltages.

#### Turk J Elec Eng & Comp Sci, Vol.20, No.5, 2012

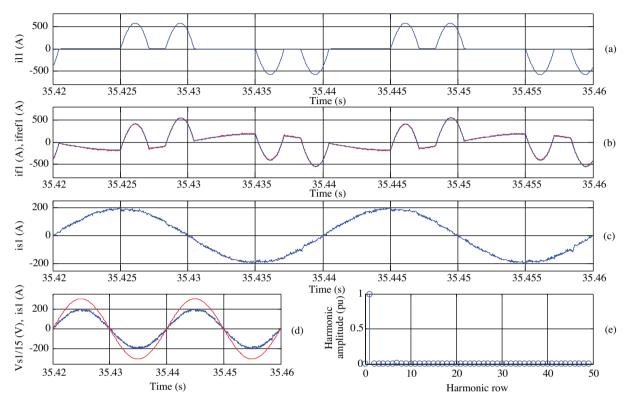

Figures 15a-15e present 2 periods of the load current, the filter current with its reference, and the power supply current and its spectral analysis. One can see that output filter current  $i_{f1}$  is almost superimposed on the reference identified harmonic current,  $i_{fref1}$ , presented in Figure 15b. Figure 15d presents power supply voltage  $V_{s1}$  and current  $i_{s1}$ . Spectral analysis of the power supply current is presented in Figure 15e. It is obvious that the latter is almost sinusoidal, with THD of less than 3% with unity power factor.

Figure 15. Load current, filter current with its reference, and power supply current and its spectral analysis.

### Simulation parameters

Main source:

$V_{(ph-ph)} = 5.5 \text{ kV}, f = 50 \text{ Hz}, R_s = 0.0001 \Omega, L_s = 0.001 \text{ H}.$

Induction motor:

${\rm P}_n \,=\, 1.2~{\rm MW},~\Omega_n \,=\, 1500~{\rm rpm},~{\rm T}_n \,=\, 7.6~{\rm kN}~{\rm m},~{\rm V}_{IM(ph-ph)} = 2300~{\rm V},~{\rm J} = 46~{\rm kg}~{\rm m}^2,~{\rm R}_{st} \,=\, 0.0406$   $\Omega,~{\rm R}_{ro} \,=\, 0.0308~\Omega,~{\rm L}_{ro} \,=\, 0.0591~{\rm H},~{\rm L}_{st} \,=\, 0.0591~{\rm H},~{\rm M} = 0.0581~{\rm H}.$

Active power filter:

$R_f = 0.0001 \ \Omega$ ,  $L_f = 0.0031 \ H$ ,  $C = 0.05 \ F$ ,  $f_c = 1.5 \ kHz$ .

Five-level PWM rectifier:

$\mathbf{U}_{cref}\,=3$  kV,  $\mathbf{L}_{r}\,=0.05$  H ,  $\mathbf{R}_{r}\,=0.0001~\Omega.$

# 6. Conclusion

This study investigated the unbalance of capacitor DC voltages of a 5-level NPC shunt APF, showing that its different input voltages were not stable, which implies a bad harmonic current compensation.

To balance the DC voltages of the APF, the authors propose the application of a feedback control method to the 5-level PWM rectifier feeding the APF controlled by using the redundant vector-based closed-loop method.

The application of the proposed simplified SVPWM based on redundant vector control makes the input multi-DC link voltages stable.

The stable DC bus supply of the sliding mode-controlled 5-level NPC shunt APF allows the obtaining of balanced main source currents with low THD and unity power factor. The results show that the proposed solution allows the use of this topology to compensate for the harmonic current and the reactive power in high-power utilities.

# References

- V.E. Wagner, "Effects of harmonics on equipment", IEEE Transactions on Power Delivery, Vol. 8, pp. 672-680, 1993.

- [2] B. Singh, V. Verma, "An improved hybrid filter for compensation of current and voltage harmonics for varying rectifier loads", International Journal of Electrical Power and Energy Systems, Vol. 29, pp. 312-321, 2007.

- [3] G. Choe, M. Park, "A new injection method for AC harmonic elimination by active power filter", IEEE Transactions on Industry Applications, Vol. 35, pp. 141-147, 1988.

- [4] S.M. Dig, D. Ruşinaru, A.C. Grigorescu, "Aspects concernant la limitation des effets de la circulation des harmoniques dans les reseaux de distribution", Annals of the University of Craiova, Electrical Engineering, Vol. 30, pp. 282-287, 2006.

- [5] J.H. Choi, J.W. Park, S.B. Dewan, "Standby power supply with active power filter ability using digital controller", Proceedings of Applied Power Electronics Conference and Exposition, Vol. 2, pp. 783-789, 1995.

- [6] S. Bhattacharya, D.M. Divan, B.B. Banerjee, "Active filter solutions for utility interface", Proceedings of International Conference on Power Electronics, Drives and Energy Systems for Industrial Growth, Vol. 2, pp. 1-11, 1995.

- [7] S. Saetieo, R. Devaraj, D.A. Torrey, "The design and implementation of a three-phase active power filter based on sliding mode control", IEEE Transactions on Industry Applications, Vol. 31, pp. 993-1000, 1995.

- [8] B.R. Lin, Z.L. Hung, S.C. Tsay, M.S. Liao, "Shunt active filter with sliding mode control", International Conference on Electrical and Electronic Technology, pp. 884-889, 2001.

- [9] T. Abdelkrim, E.M. Berkouk, "Commande non linéaire par mode de glissement d'un filtre actif parallèle à sept niveaux", Conférence Internationale Francophone d'Automatique, 2008.

- [10] E. Özdemir, M. Kale, Ş. Özdemir, "A novel control method for active power filter under non-ideal mains voltage", Proceedings of Conference on Control Applications, Vol. 2, pp. 931-936, 2003.

- [11] N. Mendalek, K. Ai-Haddad, "Modeling and nonlinear control of shunt active power filter in the synchronous reference frame", Ninth International Conference on Harmonics and Quality of Power, Vol. 1, pp. 30-35, 2000.

- [12] R. Gupta, A. Ghosh, A. Joshi, "Control of 3-level shunt active power filter using harmonic selective controller", IEEE Power India Conference, 2006.

- [13] V. Aburto, M. Schneider, L. Moran, F. Dixon, "An active power filter implemented with a three-level NPC voltagesource inverter", 28th Annual IEEE Power Electronics Specialists Conference, Vol. 2, pp. 1121-1126, 1997.

- [14] B.R. Lin, H.K. Chiang, C.H. Huang, "Three-phase three-level active power filter with a clamped capacitor topology", IEE Proceedings - Electric Power Applications, Vol. 153, pp. 513-522, 2006.

- [15] A. Nabae, I. Takahashi, H. Akagi, "A new neutral-point-clamped PWM inverter", IEEE Transactions on Industrial Applications, Vol. 1A, pp. 518-523, 1981.

- [16] J.S. Lai, F.Z. Peng, "Multilevel converters a new breed of power converters", IEEE Transactions on Industry Applications, Vol. 32, pp. 509-517, 1996.

- [17] V.F. Corasaniti, B.M. Barbieri, P.L. Arnera, M.I. Valla, "Comparison of active filters topologies in medium voltage distribution power systems", IEEE Power and Energy Society General Meeting - Conversion and Delivery of Electrical Energy, pp. 1-8, 2008.

- [18] M. Rastogi, P.W. Hammond, S.R. Simms, "Multi-level active filter for medium voltage applications", International Conference on Power Electronics and Drives Systems, pp. 1508-1513, 2005.

- [19] Y.H. Lee, R.Y. Kim, D.S. Hyun, "A novel SVPWM strategy considering DC-link balancing for multi-level voltage source inverter", Fourteenth Annual IEEE Applied Power Electronics Conference and Exposition, Vol. 1, pp. 509-514, 1999.

- [20] C. Newton, M. Summer, "Neutral point control for multi-level inverters: theory, design and operational limitations", IEEE Industry Applications Society Annual Meeting, Vol. 2, pp. 1336-1343, 1997.

- [21] D.H. Lee, S.R. Lee, F.C. Lee, "An analysis of midpoint balance for the neutral-point-clamped three-level VSI", 29th Annual IEEE Power Electronics Specialist Conference, Vol. 1, pp. 193-199, 1998.

- [22] A.V. Jouanne, S. Dai, H. Zhang, "A multilevel inverter approach providing DC-link balancing, ride-through enhancement, and common-mode voltage elimination", IEEE Transactions on Industrial Electronics, Vol. 49, pp. 739-745, 2002.

- [23] J. Pou, R. Pindado, D. Boroyevich, P. Rodriguez, J. Vicente, "Voltage balancing strategies for diode-clamped multilevel converters", 35th Annual IEEE Power Electronics Specialists Conference, Vol. 5, pp. 3988-3993, 2004.

- [24] A. Talha, E.M. Berkouk, M.S. Boucherit, "Study and control of two-level PWM rectifier-clamping bridge-seven-level NPC VSI cascade: application to PMSM speed control", European Transactions on Electrical Power, Vol. 16, pp. 93-107, 2005.

- [25] S. Barkati, E.M. Berkouk, M.S. Boucherit, "Control of the DC-buses of a seven-level diode-clamped inverter using type-2 fuzzy systems", The Mediterranean Journal of Measurement and Control, Vol. 2, pp. 161-168, 2006.

- [26] V. Gazi, B. Fidan, Y.S. Hanay, I. Köksal, "Aggregation, foraging, and formation control of swarms with nonholonomic agents using potential functions and sliding mode techniques", Turkish Journal of Electrical Engineering and Computer Sciences, Vol. 15, pp. 149-168, 2007.

- [27] R.W. Menzies, P. Steimer, J.K. Steinke, "Five-level GTO inverters for large induction motor drives", IEEE Transactions on Industry Applications, Vol. 30, pp. 938-944, 1994.

- [28] H.W. Van Der Broeck, H.C. Skudelny, G.V. Stanke, "Analysis and realization of a pulse width modulation based on voltage space vectors", IEEE Transactions on Industrial Applications, Vol. 24, pp. 142-150, 1988.

- [29] T. Sutikno, A. Jidin, N.R.N. Idris, "New approach FPGA-based implementation of discontinuous SVPWM", Turkish Journal of Electrical Engineering and Computer Sciences, Vol. 18, pp. 499-514, 2010.

- [30] J.H. Seo, C.H. Cho, D.S. Hyun, "A new simplified space-vector PWM method for three-level inverters", IEEE Transactions on Power Electronics, Vol. 16, pp. 545-550, 2001.

- [31] D. Lalili, N. Lourci, E.M. Berkouk, F. Boudjema, J. Petzoldt, M.Y. Dali, "A simplified space vector pulse width modulation algorithm for five level diode clamping inverter", International Symposium on Power Electronics, Electrical Drives, Automation and Motion, pp. 21-26, 2006.

- [32] D. Lalili, E.M. Berkouk, F. Boudjema, N. Lourci, T. Taleb, J. Petzold, "Simplified space vector PWM algorithm for five-level inverter", European Physical Journal - Applied Physics, Vol. 40, pp. 335-342, 2007.

- [33] N. Lourci, E.M. Berkouk, D. Lalili, "Stabilizing and balancing of input DC voltages of five levels diode clamped inverter by combining space vector modulation and sliding mode control", The Mediterranean Journal of Measurement and Control, Vol. 5, pp. 11-21, 2009.

- [34] T. Abdelkrim, E.M. Berkouk, K. Benamrane, T. Benslimane, "Study and control of three-level PWM rectifierfive-level NPC active power filter cascade using feedback control and redundant vectors", International Review of Electrical Engineering, Vol. 5, pp. 820-830, 2010.

- [35] J.J. Slotine, W. Li, Applied Nonlinear Control, New Jersey, Prentice-Hall, 1991.

- [36] V.I. Utkin, "Sliding mode control design principles and application to electric drives", IEEE Transactions on Industrial Electronics, Vol. 40, pp. 23-36, 1993.

- [37] H. Akagi, Y. Kanazawa, A. Nabae, "Generalized theory of the instantaneous reactive power in three-phase circuits", International Power Electronics Conference, Tokyo, Japan, pp. 1375-1386, 1983.