Aalborg Universitet

# Study of Current Density Influence on Bond Wire Degradation Rate in SiC MOSFET Modules

Luo, H.; Iannuzzo, F.; Baker, N.; Blaabjerg, F.; Li, Wuhua; He, Xiangning

Published in: IEEE Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2019.2920715

Publication date: 2020

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Luo, H., lannuzzo, F., Baker, N., Blaabjerg, F., Li, W., & He, X. (2020). Study of Current Density Influence on Bond Wire Degradation Rate in SiC MOSFET Modules. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 8(2), 1622-1632. [8730380]. https://doi.org/10.1109/JESTPE.2019.2920715

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Study of Current Density Influence on Bond Wire Degradation Rate in SiC MOSFET Modules

Haoze Luo, *Member IEEE*, Francesco Iannuzzo, *Senior Member IEEE*, Nick Baker, *Member IEEE*, Frede Blaabjerg, *Fellow IEEE*, Wuhua Li, *Member IEEE*, Xiangning He, *Fellow IEEE*

Abstract - This paper proposes a separated test method for studying the current effect on the ageing process of wire-bonded Silicon Carbide (SiC) MOSFET module under power cycling test (PCT). The separated test method enables to test SiC MOSFET with different load current densities, but under the same temperature swing and average temperature conditions. By analyzing the output characteristics in the linear region, the relations among the gate voltage, on-state voltage and junction temperature are revealed. Then, the one-to-one correspondence between gate voltage and conduction power loss can be used to adjust the current density with the same temperature conditions. Two six-pack SiC modules (1200V/20A) are tested under 12A and 24A conditions to experimentally verify the proposed method. The ageing curves show that the higher current can speed up the ageing rate of bond wires even under the same temperature conditions ( $65^{\circ}C \sim 125^{\circ}C$ ). Moreover, the high current density also has an impact on the solder layer degradation as well as the temperature conditions. Finally, power device analyzer B1506A and Scanning Acoustic Microscopy (SAM) are used to investigate the degradation of electrical parameter and solder layer, respectively. The final summary of analytical results shows that the input current has a non-negligible impact on the degradation process of power module.

*Index Terms* – Silicon carbide MOSFET, power cycling test, separated test, adjustable gate voltage, and package degradation.

# I. INTRODUCTION

High-power Silicon Carbide (SiC) MOSFET modules have begun to enter the market [1], [2]. Since the characteristics of SiC dies are quite different from the Si-based devices in terms of smaller dies, higher temperature tolerance and higher switching frequency, the conventional package techniques developed for Si-based semiconductor inevitably bring new obstacles to SiC dies [3]. With the advantages of mature package techniques and low cost, the conventional wire-bonded packages are usually employed in the existing commercial SiC power modules [4]–[7]. Hence, how to evaluate the reliability level for the combination of emerging SiC dies and the conventional wire-bonded package becomes a real problem.

H. Luo, W. Li, and X. He are with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China.

F. Iannuzzo, N. Baker and F. Blaabjerg are with the Energy Technology Department, Aalborg University, Aalborg East 9220, Denmark. (corresponding author: Francesco Iannuzzo, Email: fia@et.aau.dk.).

Accelerated power cycling test (PCT) is often used for the package-level failure mechanism evaluation of power modules. So far, many PCT works have been done to evaluate the package reliability issues on the conventional wire-bonded power modules and discrete devices [8]–[11]. In the late 90's, the experimental test time (or power cycles) to failure as a function of temperature swing ( $\Delta T_j$ ) and average temperature ( $T_{avg}$ ) under PCT were published in the LESIT Study [12]. It is concluded that the both  $\Delta T_j$  and  $T_{avg}$  dominate for the number of cycles to the end of life. Finally, due to the mismatch of Coefficient of Thermal Expansions (CTE) between different materials, the temperature swing is regarded as the main decisive cause for the package wear-out degradation [13], [14].

However, according to the extensive statistical test results, the correlations between the number of power cycles and the temperature swing are associated with many test conditions [15]–[17]. Apart from the typical  $\Delta T_j$  and  $T_{avg}$ , both the amplitude of load current  $I_{load}$  and pulse duration ton also have a great impact on the final power cycles and lifetime estimation of power modules [15], [18], [19]. In order to investigate the effect of different test conditions on the ageing process, the separate control strategies have been developed for the conventional PCT, such as constant ton, constant power loss methods. In [18], [20], the influence of different  $t_{on}$  duration on the number of power cycles is studied. A similar test idea is performed in AC-based PCT platform [21], where the fundamental frequency effect on the lifetime and failure mechanism of IGBT modules are also studied. However, the aforementioned separation test methods do not take into account the current effect individually in the tests.

Usually, the current effect is mixed with temperature factors for the bond wire degradation evaluation because the temperature swing is adjusted by the load current [8], [22]. In the standard PCT process, both large temperature swing and current are imposed on the module. Since the desired temperature swing is mainly proportional to the input current, the influence of current cannot be separated from  $\Delta T_i$  when using the standard PCT principle. In the case of different load currents, the pulse duration time should be adjusted accordingly for the required temperature swings. If so, the total test time spend on the same number of cycles would be completely different. As a result, the effect of different current densities on the module degradation cannot be compared fairly due to the different test time and power cycles. So far, the PCT standard formulated in IEC 60749-34 specifies the operation rules only with regard to the desired  $\Delta T_i$  and how to avoid thermal runaway failure [23]. The load current is not treated as a quantitative factor in PCT principle, which could cause deviations to the lifetime model and the reliability evaluation.

Manuscript received Oct 8, 2018; revised Feb 02, 2019, revised Mar 04, 2019, and accepted May 18, 2019. This work has been conducted under the CORPE (Center of Reliable Power Electronics) framework – Aalborg University, and funded by The Obel Foundation, Denmark.

To overcome the above problems, a power cycling test method for investigating the current density effect individually on the wire-bonded SiC module is proposed. By controlling the gate voltage  $V_{gs}$ , the conduction loss of SiC MOSFET can be adjusted instead of the load current. Therefore, the SiC module can be tested under the same  $T_j$  requirements ( $\Delta T_j$  and  $T_{avg}$ ) and pulse duration  $t_{on}$ , but with the different load current in PCT. The package reliability evaluation, especially the bond wire and solder layer, can be investigated without the coupling effect of temperature factors ( $\Delta T_j$  and  $T_{avg}$ ).

This paper is organized as follows: In Section II, the problems in the conventional PCT method is introduced firstly, and then the failure mechanisms for bond wires and solder layer are reviewed. In Section III, on the basis of linear region characteristics of SiC MOSFET, an equivalent power loss control method by means of gate voltage adjustment is described. The experimental results confirm the feasibility of the proposed method, and the corresponding analysis and discussion are shown in Section IV and Section V, respectively. Finally, the findings form the conclusion.

# II. CURRENT EFFECT ON WIRE-BONDED PACKAGE DEGRADATION

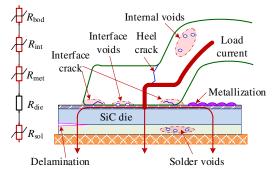

Because of the CTE mismatches among SiC die (2.77 ppm/K), Aluminum wires (23.5 ppm/K), solder material (15~30 ppm/K), wire bond interconnection and die attach solder layer are regarded as the weakest parts in the wire-bonded modules [24]. Extensive research demonstrated that several typical categories of failure mechanisms which are mainly dependent on the locations where the failure occurs [9], [24], [25]. The typical failure and fatigue modes and the corresponding parasitic resistance dependence are depicted in Fig.1.

Accordingly, the parasitic resistance from bond wire to the copper layer consists of bond wire resistance ( $R_{bod}$ ), interconnection resistance ( $R_{int}$ ), Aluminum pad resistance ( $R_{met}$ ), SiC die resistance ( $R_{die}$ ) and die attach solder layer resistance ( $R_{sol}$ ) [26]. Among them,  $R_{die}$  can be treated as constant without taking into account threshold voltage shift.

Due to the accumulative plastic strains caused by the large temperature extrusion, the cracks are most likely to occur at the tail of bond wires [21]. Moreover, the heel parts as well as the body part are also prone to cracks. With the increase of power cycles, the interface cracks could propagate inwards until the bond wire eventually lifts off. When the heel and body part of bond wires suffer from the temperature extrusion, especially from the ohmic self-heating, heel cracks are easy to occur because of the thermal expansion and contraction [27]. Recently, in the case of low  $\Delta T_j$  tests, many interfacial voids and some random voids have been widely observed during both the thermal and power cycling tests [28], [29]. It is studied that the appearance of interfacial voids can be attributed to the oxide debris and particles among the interfaces. Due to the dislocation density of the atoms, these voids continue to develop and expand along with the number of power cycles.

Concerning the fatigue occurring throughout the bond wire body, some of them are far away from the interconnection part. For example, the top part of bond wires are less affected by the temperature swing than the self-heating which are related to the current density. Due to the existence of cracks, voids, and slip bands, an inhomogeneous current density would flow though the bond wires and lead to the uneven self-heating effect on them [30]. This uneven self-heating effects will get worse and worse with the growth of cracks and voids. The bond wire fatigue modes and the related dependences are listed in Table I.

Table I. Fatigue modes and ageing dependences of bond wires.

| Fatigue modes in bond<br>wires             | Stress types                                                                                                      | Major factors                                                                                             |  |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Heel cracks                                | Mean $T_j$ , $T_j$ variation, $t_{on}/t_{off}$                                                                    | Mismatch of CTE at the interface between bond                                                             |  |

| Interface voids                            | Mean $T_j$ , $T_j$ variation, $t_{on}/t_{off}$                                                                    | wire and chip. It mainly                                                                                  |  |

| Interface cracks                           | Mean $T_j$ , $T_j$ variation, $t_{on}/t_{off}$                                                                    | depends on the $\Delta T_j$<br>related CTE mismatch                                                       |  |

| Internal voids far away<br>from interface  | Mean T <sub>j</sub> , T <sub>j</sub> variation, current<br>density induced self-heating and<br>electron migration | Bond wire ohmic self-<br>heating effects. It<br>depends on parasitic<br>resistance and current<br>density |  |

| Internal cracks far away<br>from interface | Mean T <sub>j</sub> , T <sub>j</sub> variation, current<br>density induced self-heating and<br>electron migration |                                                                                                           |  |

As shown in Table I, on the foundation of the physics-of-failure mechanisms, the reliability-related thermomechanical stresses, plastic strain and elastic energy stored in the bonding wire loop can also be affected by the current density and the related electromigration effect [31], [32]. The metal reconstruction is the most typical fatigue mode for the aluminium metallization. The reconstruction of surface would make uneven current distribution to the SiC die cells and also increase both  $R_{int}$  and  $R_{met}$ . Usually, the metallization fatigue is also mainly attributable to the high current density [33]. With regard to the second weakest part, the solder layer degradation rarely cause the notorious open-circuit failure in the tests. As depicted in Fig.1, delamination and voids are the main fatigue modes on the die-attach solder layer, which can also be attributable to both CTE mismatch and the current density effect.

In Table II, the ageing dependences about the die attach solder layer fatigues shown in Fig.1 are listed. The delamination usually starts at the edge and corner of the chip, and then continues to propagate from the outside to the centre of the chip [34], [35]. Theoretically, electromigration is the self-diffusion of metal (e.g. Aluminium) induced by the electric current, which can lead to the generation of voids and interconnect failure on the solder layer [36]–[38]. Recently, the electron migration related reliability issue has been taken into consideration at package-level as well as chip-level [37], [39]–[41].

Table II. Fatigue modes and ageing dependences of die attach solder layer.

| Fatigue modes<br>in solder layer | Stress types                                                                                                                            | Major factors                                                                                                                                                             |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Delamination                     | <i>T</i> <sub>j</sub> variation, <i>t</i> <sub>on</sub> / <i>t</i> <sub>off</sub> ,<br>current density<br>induced electron<br>migration | Mismatch of CTE at the edge and<br>corner of the die attach solder layer;<br>Electron migration effect would<br>accelerate the delamination under high<br>current density |  |  |

| Interface voids                  | t <sub>on</sub> /t <sub>off</sub> duration,<br>current density<br>induced electron<br>migration                                         | Electron migration effect induced self-<br>diffusion of Aluminium metal; <i>T</i> <sub>j</sub><br>variation could accelerate the void<br>expansion                        |  |  |

Generally, the current density and the related electromigration effect have impact for both the degradation of bond wire and solder layer. In traditional PCT, since the temperature variation is proportional to the input current, the effect of current density and the temperature swing related CTE mismatch are coupled together. Hence, it is necessary to separate the current density effect on the failure mechanism of package degradation.

# III. CONSTANT TEMPERATURE SWING CONTROL METHOD WITH DIFFERENT CURRENT CONDITIONS

#### A. Problem statement in conventional DC-based PCT

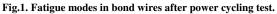

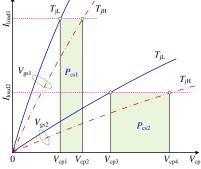

In the conventional PCT methods, the SiC MOSFETs are usually driven with standard gate voltages, +18V or +20V. Then, the  $\Delta T_i$  is obtained by the on-state conduction power losses using second-scale duration. The related temperature variation control method is plotted in Fig.2. To obtain the desired  $\Delta T_i$ , the conduction power loss  $P_{cs}$  usually can be controlled by two control variables, the on-state period  $(t_{on}/t_{off})$  and load current Iload. An external heat plate is used to control the case temperature ( $T_{case}$ ). As long as the PCT system reaches a thermal equilibrium, the minimum junction temperature  $(T_{\min})$  falls back to the case temperature  $T_{\text{case}}$  at the end of  $t_{\text{off}}$  pulse. As shown in Fig.2, the effect of different temperature variation intertwine with the duty cycle and  $I_{load}$ . In the case of fixed  $t_{on}$ , the desired  $\Delta T_{\rm j}$  can only be adjusted by the input  $I_{\rm load}$ . In order to investigate the current density effect on the bond wires independently, the temperature factors  $\Delta T_{\rm j}$  and  $T_{\rm avg}$  should be separated from the load current.

Fig.2. Conduction power loss and junction temperature swing pattern in DC-based tests.

#### B. Proposed test method

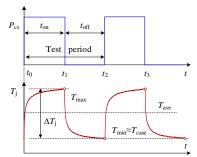

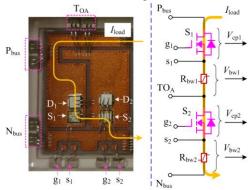

The appearance and equivalent circuits of single SiC MOSFET die are depicted in Fig.3. Thanks to the 4-terminal package with a Kelvin-source terminal (s), the gate loop does not contain the parasitic bond wire resistance  $R_{bw}$ . As a result,

the increase of  $R_{bw}$  has no effect on the gate voltage  $V_{gs}$  during the long-term PCT process.

Fig.3. Commercial 4-terminal MOSFET containing a Kelvin-source terminal.

Unlike conventional test method with the fixed SiC gate voltages (+18V or +20V), a large  $V_{gs}$  adjustment control strategy is proposed to achieve the desired  $\Delta T_j$  under different load current. In DC-based PCT, the power MOSFETs are operated in the linear region with relatively low drain voltage  $V_{DS}$ . Under fixed duty ratio ( $t_{on}/t_{off}$ ) and base plate temperature, the expected  $\Delta T_j$  in Fig.2 is proportional to the conduction loss  $P_{cs}$ , as expressed in

$$\Delta T_j \propto P_{cs} = \int_{t_2}^{t_3} V_{cp} I_{load} dt \qquad (1).$$

Assuming the gate overdrive  $(V_{gs}-V_{th})$  is larger than the Drain-to-source voltage  $V_{DS}$ , the Drain current  $I_D$  can be calculated by

$$I_{load} = I_D = \frac{Z\mu_{in}C_{ax}}{L_{CH}} \left[ \left( \frac{V_{gs}}{V_{gs}} - V_{ih} \right) V_{DS} \right] \text{ for } |V_{DS}| \le V_{gs} - V_{th} \quad (2).$$

Then  $V_{\rm DS}$  can be expressed as

$$V_{DS} = \frac{I_{load}L_{CH}}{Z\mu_{in}C_{ox}}\frac{1}{\left(V_{gs}-V_{th}\right)} \quad \text{for } |V_{DS}| \le V_{gs} - V_{th} \quad (3).$$

Where  $L_{CH}$  is the length of channel, Z is the width of channel,  $C_{ox}$  is the specific capacitance of the gate oxide layer and  $\mu_{in}$  is the electron mobility in the inversion layer. Furthermore, the  $\mu_{in}$ is temperature-dependent parameter, which can be obtained by

$$\mu_{in} = \mu_0 \left( \frac{T_j + 273}{300} \right)^{-\kappa} \tag{4}.$$

Where  $\mu_0$  is constant related to the electron mobility and semiconductor processing and the exponent k varies from 1 to 2.5 [42]. Hence, the die voltage  $V_{cp}$  is a function of gate voltage  $V_{gs}$  and load current  $I_{load}$  under given  $T_j$ , as shown below

$$\Delta T_{j} \propto P_{cs} = \int_{t_{2}}^{t_{3}} \frac{I_{load} L_{CH}}{Z \mu_{in} C_{ox}} \frac{1}{\left(\mathbf{V}_{gs} - V_{th}\right)} I_{load} dt \qquad (5).$$

From (4) and (5), the  $\Delta T_j$  related conduction loss  $P_{cs}$  can be expressed as

$$\Delta T_{j} \propto P_{cs} = \frac{I_{load}^{2} L_{CH}}{Z \mu_{0} C_{ox}} \int_{t_{2}}^{t_{3}} \frac{(T_{j} + 273)^{k}}{(V_{gs} - V_{th})} dt$$

(6).

Assuming  $T_j$  increases from  $t_2$  to  $t_3$ , the desired  $\Delta T_j$  can be adjusted by both  $I_{load}$  and  $V_{gs}$  for the given MOSFET. In order to achieve the same  $\Delta T_j$  under different load current,  $V_{gs}$  should be calculated and adjusted correspondingly. The typical output characteristics of SiC MOSFETs under different  $V_{gs}$  in the linear region are plotted in Fig.4. Besides, the related definitions labeled in Fig.4 are listed in Table III. For the higher load current Iload1, the voltage difference ( $V_{cp2}$ - $V_{cp1}$ ) under desired This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JESTPE.2019.2920715, IEEE Journal of Emerging and Selected Topics in Power Electronics

$\Delta T_j$  ( $T_{jH}$ - $T_{jL}$ ) should be limited in a relatively low value. In the case of fixed ton, the desired  $\Delta T_j$  under different load current can be achieved by the law of equivalent area

$$I_{load1}(V_{cp2} - V_{cp1})\Big|_{V_{gs1}} = I_{load2}(V_{cp4} - V_{cp3})\Big|_{V_{gs2}}$$

(7)

By means of the quantitative  $V_{gs}$  adjustment, the on-state power losses under different  $I_{load}$  can be equal.

Fig.4. SiC MOSFET Output characteristics under different temperatures and gate voltages.

| TABLE III. ELECTRICAL DEFINITIONS UNDER DIFFERENT V <sub>GS</sub> AND |

|-----------------------------------------------------------------------|

| TEMPERATURES                                                          |

| Notification                  | Condition 1   | Condition 2      |

|-------------------------------|---------------|------------------|

| Planned load current          | Iload1        | Iload2           |

| Gate voltage                  | $V_{\rm gs1}$ | V <sub>gs2</sub> |

| Maximum <i>T</i> <sub>j</sub> | $T_{ m jH}$   | $T_{ m jH}$      |

| Minimum T <sub>j</sub>        | $T_{ m jL}$   | $T_{ m jL}$      |

| Conduction power loss         | $P_{cs1}$     | Pcs2             |

#### IV. EXPERIMENTAL PLATFORM AND TEST CONDITIONS

#### A. Module Under Test

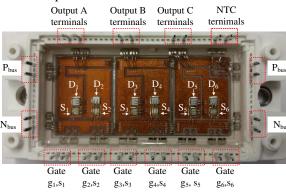

The devices under test are two six-pack modules (CREE CCS020M12CM2). The module consists of three identical half-bridge substrates. The maximum allowable operation  $T_j$  is 150 °C, and the internal layouts of the six SiC dies are depicted in Fig.5. For each SiC die, there are two bond wires used to carry the load current and another two thinner bond wires for the gate driver loop.

Fig.5. Layouts for the module under test (CREE CCS020M12CM2).

The half-bridge schematic and the measurement proposal are depicted in Fig.6. The independent measurement method for the bond wire and die resistances proposed in [43] is applied to the dies under test. Taking the first die  $S_1$  as an example, its bond wire voltage  $V_{bw1}$  can be measured by the gate auxiliary terminal  $s_1$  and the output power terminal  $T_{OA}$ . Meanwhile, the die

voltage  $V_{cp1}$  under constant  $I_{load}$  can be measured by the positive bus terminal  $P_{bus}$  and the gate auxiliary terminal  $s_1$ . During the test, both the die voltage and bond wire voltage are measured and recorded simultaneously, and the increased  $V_{bw1}$  can be attributed to the bond wire  $R_{bw1}$  degradation.

Fig.6. Half-bridge schematic and bond wire voltage measurement.

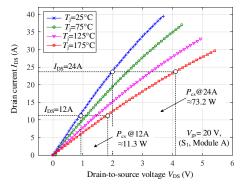

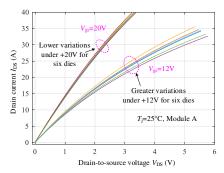

For S<sub>1</sub> in Module A, the output characteristic curves under different junction temperatures are plotted in Fig.7. Since the electron mobility varies inversely with the temperature, the on-state voltage  $V_{DS}$  increases with the increasing  $T_j$  under fixed  $I_{DS}$ . Assuming the desired  $\Delta T_j$  ranges from 25°C to 175°C, the average power loss Pcs under  $I_{DS}$ =24 A is around 73.2W while Pcs equals to 11.3W at 12 A condition. It is also proved that the conduction power loss is proportional to fixed  $I_{DS}$  within the given turn-on duration. In order to get the same  $T_j$  swing under different  $I_{DS}$ , the gate voltage is required to be adjusted accordingly.

Fig.7. Output characteristic curves under different junction temperature.

## B. On-line $T_i$ measurement

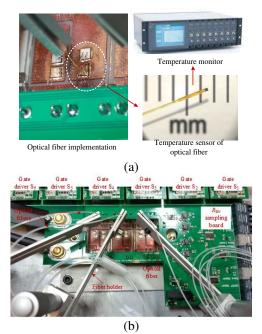

The on-line  $T_j$  measurement without gel removal is achieved by the isolated optical fibers from Opsens and the implementation is depicted in Fig.8. The part number of optical fiber is OTG-F-10 with 5 ms response time, as shown in Fig.8 (a) [44]. In order to hold the optical fiber during operation, a precision manipulator is applied to the optical fiber. It is worth noting that the measured  $T_j$  merely represents the temperature of the contact point. In practice, the sensor of optical fiber is placed at the center of the inspected SiC die. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JESTPE.2019.2920715, IEEE Journal of Emerging and Selected Topics in Power Electronics

Fig.11. Online junction temperature measurement implementation using optical fiber.

# C. Test conditions and experimental results

In order to investigate the current density effects on the bond wires, two SiC modules (labeled Module A and Module B) were tested. The desired  $\Delta T_j$  for both modules are controlled in the range of 65°C to 125°C with the same test conditions except for the Drain current injection. The test conditions for the two SiC-MOSFET modules are listed in Table IV.

| Parameters                    | Module A | Module B |

|-------------------------------|----------|----------|

| Maximum <i>T</i> <sub>j</sub> | 125 °C   | 125 °C   |

| Minimum T <sub>j</sub>        | 65 °C    | 65 °C    |

| $\Delta T_{ m j}$             | 60 °C    | 60 °C    |

| $t_{\rm on}/t_{\rm off}$      | 2s / 4s  | 2s / 4s  |

| Load current                  | 24 A     | 12 A     |

TABLE IV. TEST CONDITIONS FOR CREE MODULES.

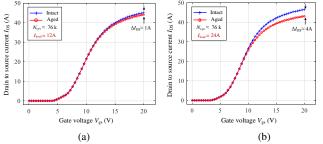

The output characteristics of Module A under different gate voltages are plotted in Fig.9. Because of the discrepancies in the manufacturing process, the six dies present different output characteristics under the same static test conditions. Therefore, six independent gate drivers with adjustable output voltages were used in the tests.

Fig.9. Output characteristic curves for six dies for module A.

In Table V, the practical gate voltages for the constant  $\Delta T_j$  under two load current conditions are recorded.

TABLE V. GATING VOLTAGES FOR CREE MODULES.

| Gate voltage<br>adjustment       | $S_1$  | $S_2$ | <b>S</b> <sub>3</sub> | $S_4$ | <b>S</b> <sub>5</sub> | <b>S</b> <sub>6</sub> |

|----------------------------------|--------|-------|-----------------------|-------|-----------------------|-----------------------|

| Module A:<br>+24A,<br>65°C~125°C | 18.9 V | 19.6V | 21.1V                 | 19.7V | 21.4V                 | 20.6V                 |

| Module B:<br>+12A,<br>65°C~125°C | 7.9 V  | 7.9V  | 8.0V                  | 8.0V  | 8.1V                  | 7.9V                  |

The temperature variations for the high-side three dies of Module A at the beginning of the test are depicted in Fig.10. The measured  $T_i$  swings are in the range of 65°C~125°C.

**Fig.10.** Online junction temperature measurements for high-side three dies of Module A.

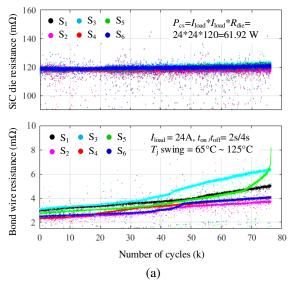

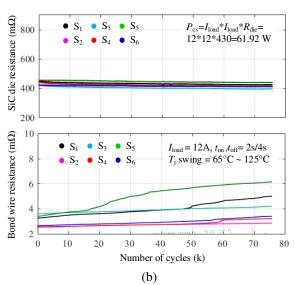

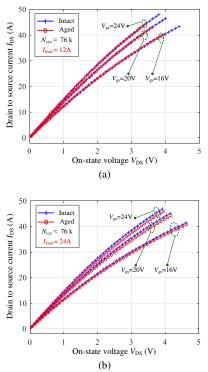

In Fig.11.(a) and (b), the on-line record for SiC die and bond wire resistances under two current conditions are depicted, respectively. Due to the layout differences, the initial bond wire resistances are not the same [45]. In this study, the measured high-side bond wire resistances are higher than the low-side bond wire resistances, which are consistent with the load current path depicted in Fig.6. As shown in Fig.11 (a), the die resistances for six dies of Module A remain around 120 m $\Omega$  throughout the test. The corresponding conduction power loss  $P_{\rm cs}$  is around 61.92W. After 76k power cycles ( $N_{\rm cyc}$ ), the  $R_{\rm bw}$  of S<sub>1</sub> increased by 300% and then the test was stopped. This excess  $R_{\rm bw}$  increase implies the contact area between bond wire and SiC die is dramatically reduced.

Fig.11. Online measurement and record for bond wire and die resistances (a)  $I_{\text{load}}$ =24A and end-of-test  $N_{\text{cyc}} \approx 76$  k. (b)  $I_{\text{load}}$ =12A and end-of-test  $N_{\text{cyc}} \approx 76$  k.

In order to make a better comparison, the Module B is also stopped after 76k cycles' test. The ageing curves for Module B  $(I_{load} = 12A)$  are depicted in Fig.11 (b). It is shown that the average die resistance for the six SiC dies is around 430 m $\Omega$ under lower gate voltages. Even though the load current is 12A, the conduction power loss Pcs could also be kept around 61.92W for the same  $T_i$  swing.

#### V. COMPREHENSIVE ANALYSIS AND DISCUSSION

#### A. Ageing process comparison

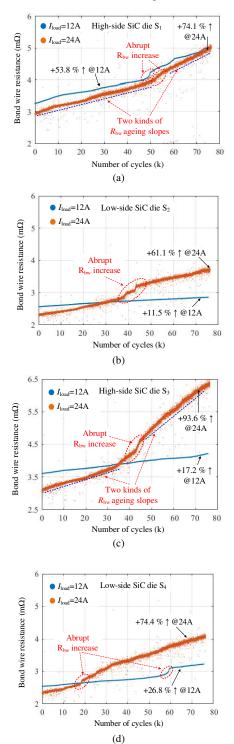

The online bond wire resistance measurements under two current conditions after 76k power cycles are compared individually and plotted in Fig.12. Considering the layout difference among the six dies, the ageing curves are only compared for the dies with the same layout in the module. Fig.12 illustrates two kinds of ageing trend in the test, one is the linear growth with  $N_{\text{cyc}}$  increase, and the other is step  $R_{\text{bw}}$  increase along with a subsequent steeper linear growth.

As can be seen from all the sub figures, there is a linear ageing process under fixed test conditions in the beginning stages. It is shown that the higher the load current, the steeper the ageing slope. The typical linear ageing process can be found in Figs.12 (b), (c) and (f) under  $I_{load}=12A$  condition (see blue curves). These linear ageing processes indicate that the constant temperature stresses ( $\Delta T_j$  and  $T_{avg}$ ) have uniform degradation effect on the bond wire resistance. Before stopping the test of Module B, the measured bond wire resistances for S<sub>2</sub>, S<sub>3</sub>, and S<sub>6</sub> are increased by 11.5%, 17.2% and 28.7%, respectively. In this scenario, the follow-up  $R_{bw}$  increase can be easily estimated by an approximate linear model.

For the second ageing trend, this kind of abrupt  $R_{bw}$  increase is usually present at the end of test. Once the abrupt  $R_{bw}$  increase occurs, the bond wires under test start to get into an accelerated process, and the bond wires would lift off the die within a short period. The increased bond wire resistance under high current could lead to a higher self-heat effect and then accelerate the follow-up bond wire degradation, as demonstrated in Figs.12 (a), (c) and (f). Notably, in the case of  $I_{load}=24A$ , the bond wires continue to keep almost the same ageing pace after the sudden  $R_{bw}$  increase, as shown in Fig.12 (b) and Fig.12 (f). The significant abrupt increases can be attributable to the cracks and sudden delamination, which are related to high current density rather than CTE mismatch. However, in the case of low current density ( $I_{load}=12A$ ), such as Figs.12 (b), (c) and (f) do not show significant sudden  $R_{bw}$  step increase in the tests. Since the two modules experienced the same  $T_j$  conditions and power cycles, Module A has higher ageing speed and more abrupt  $R_{bw}$  increases than Module B due to the higher current density.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JESTPE.2019.2920715, IEEE Journal of Emerging and Selected Topics in Power Electronics

Fig.12. Comparisons of online bond wire resistance measurements under different current conditions after 76k cycles. (a) die S1, (b) die S2 (c) die S3 (d)S4 (e) die S5(f) die S6.

In particular, a variable ageing rate process without any abrupt  $R_{bw}$  increase is shown in Fig.12 (e). In Fig.12 (e), there are three kinds of straight ageing slope under  $I_{load}=24$  A condition. After 38k cycles, the ageing rate starts to increase for the first time. Then, it changes the ageing rate again after 67k cycles. The measured  $R_{bw}$  increases quickly and the bond wire appears lift off behavior within 10k cycles. The ageing curve plotted in Fig.12 (e) implies that the higher current density can change and accelerate the ageing slope even without the sudden  $R_{bw}$  increase.

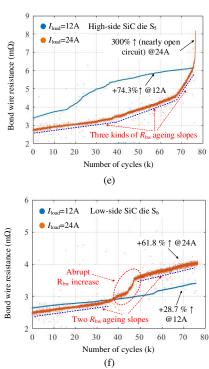

Generally, compared with the ageing processes under low current conditions, the modules under high current tests shown higher ageing rate in terms of abrupt  $R_{bw}$  increase and variable ageing rate. For an overall comparison, the ageing speed can be evaluated by using increase rate  $R_{rate}$

$$R_{rate} = \left(\frac{R_{end}}{R_{ini}} - 1\right) 100\% \tag{8}$$

Where  $R_{end}$  is measured bond wire resistance at the end of test,  $R_{int}$  is the initial measured resistance. The increase rates for the six SiC dies after 76k cycles are summarized in Fig.13. It is shown that all the increase rates under  $I_{load}$ =24A are higher than the increase rates under  $I_{load}$ =12A. In the case of higher current density, the wire bonded packages are subjected to higher self-heating and electro-migration effect. As a result, the bond wires degrade faster even under the same temperature swings.

**Fig.13.** Comparisons of bond wire resistance increase rates for six SiC dies at different current conditions.

#### B. Ageing process comparison

By means of the B1506A power device analyzer, three kinds of electrical parameters are selected and compared: output characteristic, transfer characteristic and on-state resistance. All the static tests are conducted under constant temperature room environment, and the room temperature is around 25  $^{\circ}$ C.

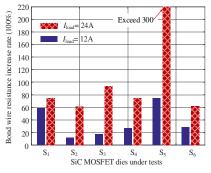

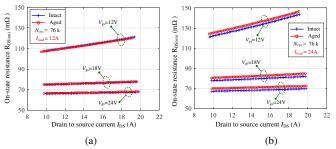

In Fig.14, the measured output characteristic comparisons before and after the tests are depicted. As shown in Fig.14 (a), there is almost no obvious degradation in the output characteristic curves under different gate voltages. In the case of 24A, the slopes of output characteristic curves for the aged die are lower than the initial measurements. This lower slope means that the conduction losses would increase during the ageing process even under the same working conditions. According to the comparisons, the die S<sub>3</sub> shows significant degradation under  $I_{load}$ =24A condition and these results are consistent with the ageing curves plotted in Fig.12 (c).

Fig.14. Output characteristic curve comparisons before and after power cycling tests for S<sub>3</sub>: (a)  $I_{load}$ =12A and  $T_i$ =25°C, (b)  $I_{load}$ =24A and  $T_i$ =25°C.

In Fig.15, the transfer characteristic curves before and after tests are compared and plotted. Theoretically, transfer characteristic curve indicates how drain current increases with gate voltage under a given Drain-to-source voltage  $V_{\rm DS}$ . Moreover, the slope of transfer characteristic curve is the trans-conductance of the device. Compared with the initial curves, both two dies show the evidence of degradation. However, in the case of  $V_{\rm gs}$ =20V, the measured drain current I<sub>DS</sub> under  $I_{\rm load}$ =24A decreased by 4A, which is greater than the results under  $I_{\rm load}$ =12A. The slight negative slopes imply that switching speed would become slower under  $V_{\rm gs}$ =20V after the power cycling tests.

**Fig.15.** Transfer characteristic curve comparisons before and after power cycling tests for S<sub>3</sub>: (a)  $I_{\text{load}}$ =12A and  $T_j$ =25°C, (b)  $I_{\text{load}}$ =24A and  $T_j$ =25°C.

In Fig.16, the measured on-state device resistances before and after the power cycling test are plotted and compared. It is worth noting that the measured on-state resistance  $R_{DS(on)}$  from B1506A is a combination of die resistance and parasitic resistances including bond wire resistance, copper layer resistance and Aluminum pad resistance.

**Fig.16.** Measured on-state resistance comparisons before and after power cycling tests for S<sub>3</sub>: (a) Module A,  $I_{load}$ =12A and  $T_j$ =25°C, (b) Module B,  $I_{load}$ =24A and  $T_j$ =25°C.

Referring to Fig.11 (a), the measured  $R_{\text{DS}(on)}$  do not significantly change after power cycling tests. According to the results in Fig.12 (e), the bond wire increase is less than 1 m $\Omega$ , which can hardly affect  $R_{\text{DS}(on)}$ . However, in the case of  $I_{\text{load}}$ =24A shown in Fig.16.(b), the visible changes about 3.3 m $\Omega$ increase can be detected, and the measured results are consistent with the recorded curve in Fig.12 (e).

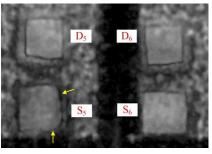

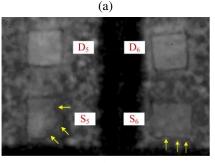

In Fig.17, the Scanning Acoustic Microscopy (SAM) images for die attach solder degradation are shown. The freewheeling diodes  $D_5$  and  $D_6$  have not been tested, so the diode SAM image can be regarded as reference compared with SiC dies. In Fig.17 (a), there are no visible degradations on  $D_5$ ,  $D_6$  and  $S_6$  under  $I_{load}$ =12A conditions. For  $S_5$ , there is a slight delamination on the right side and the bottom-right corner. In general, the die attach solder layer maintain a healthy state of interconnection. However, in the case of  $I_{load}$ =24A shown in

Fig.17 (b), the delamination on  $S_5$  is worse than the die under lower current condition. More significant delamination can be found from the right side and the bottom-right corner. Besides, a slight delamination can be observed on the bottom side on  $S_6$ .

(b)

Fig.17. SAM images of die attach solder layer after 76k temperature cycles (a) Module A,  $I_{\text{load}}$ =12A,  $T_{\text{j}}$ =65 °C~125 °C (b) Module B,  $I_{\text{load}}$ =24A,  $T_{\text{j}}$ =65 °C~125 °C.

It is confirmed that different current conditions have a great impact on the die attach solder layer degradation even under the same  $T_j$  swing conditions. Compared with the typical Si-based semiconductor die (13 mm<sup>2</sup>), the active area of SiC die (4.2 mm<sup>2</sup>) is smaller in the SiC MOSFET modules [46]. In order to alleviate the high current density effect on the package of SiC modules, the number of bond wire needs to be increased from the manufacturing point of view. Moreover, in a real application using SiC modules, the duration time of over-current operation should be limited, which would also accelerate the bond wire degradation in SiC MOSFET power modules.

## VI. CONCLUSION

This paper has presented a separate test method for SiC MOSFET modules in power cycling test. Through adjusting the gate voltage, the on-state die resistance can be adjusted under the given current. Therefore, the conduction losses and related temperature swing can be changed accordingly by using gate voltage rather than load current. The SiC MOSFET modules with wire-bonded package can be tested under different current densities but with the same temperature conditions. Hence, the current density effect can be evaluated separately under the framework of conventional PCT standards. Results shown that different current densities have different impacts on both the bond wire resistance and die-attach solder layer. The module under higher current test condition shown faster ageing speed. Besides, more abrupt degradation can be found in the bond wire resistances in the case of higher current. It is experimentally validated that the package degradation rate is related to the current effect as well as the temperature swing and average temperature. By using a power device analyzer, the static parameters were measured and compared before and after power cycling tests. The analysis and comparisons are consistent with the PCT monitoring measurement results. With the help of scanning acoustic microscopy, a delamination effect can be observed and confirms the involvement of current in the aging effect. Finally, the experimental results and analysis validated the effectiveness of proposed method.

# ACKNOWLEDGEMENT

The authors would like to thank Dr. Sungyoung Song and Prof. Christian Uhrenfeldt from Aalborg University for providing SAM support and fruitful suggestions during the work.

#### REFERENCES

- Q. Zhang, R. Callanan, M. K. Das, S. H. Ryu, A. K. Agarwal, and J. W. Palmour, "SiC Power Devices for Microgrids," IEEE Trans. Power Electron., vol. 25, no. 12, pp. 2889–2896, Dec. 2010.

- [2] A. Bindra, "Wide-Bandgap Power Devices: Adoption Gathers Momentum," IEEE Power Electron. Mag., vol. 5, no. 1, pp. 22–27, Mar. 2018.

- [3] J. Wang, T. Zhao, J. Li, Alex Q. Huang, R. Callanan, F. Husna, A. Agarwal., "Characterization, Modeling, and Application of 10-kV SiC MOSFET," IEEE Trans. Electron Devices, vol. 55, no. 8, pp. 1798–1806, Aug. 2008.

- [4] A. J. Morgan, Y. Xu, D. C. Hopkins, I. Husain, and W. Yu, "Decomposition and electro-physical model creation of the CREE 1200V, 50A 3-Ph SiC module," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), 2016, pp. 2141–2146.

- [5] H. Li, S. Munk-Nielsen, S. Bęczkowski, and X. Wang, "A Novel DBC Layout for Current Imbalance Mitigation in SiC MOSFET Multichip Power Modules," IEEE Trans. Power Electron., vol. 31, no. 12, pp. 8042–8045, Dec. 2016.

- [6] M. Wang, F. Luo, and L. Xu, "A Double-End Sourced Wire-Bonded Multichip SiC MOSFET Power Module With Improved Dynamic Current Sharing," IEEE J. Emerg. Sel. Top. Power Electron., vol. 5, no. 4, pp. 1828–1836, Dec. 2017.

- [7] C. Chen, Y. Chen, Y. Li, Z. Huang, T. Liu, and Y. Kang, "An SiC-Based Half-Bridge Module With an Improved Hybrid Packaging Method for High Power Density Applications," IEEE Trans. Ind. Electron., vol. 64, no. 11, pp. 8980–8991, Nov. 2017.

- [8] C. Durand, M. Klingler, D. Coutellier, and H. Naceur, "Power Cycling Reliability of Power Module: A Survey," IEEE Trans. Device Mater. Reliab., vol. 16, no. 1, pp. 80–97, Mar. 2016.

- [9] V. Smet, F. Forest, J. Huselstein, F. Richardeau, Z. Khatir, S. Lefebvre, M. Berkani., "Ageing and Failure Modes of IGBT Modules in High-Temperature Power Cycling," IEEE Trans. Ind. Electron., vol. 58, no. 10, pp. 4931–4941, Oct. 2011.

- [10] V. Smet, F. Forest, J. J. Huselstein, A. Rashed, and F. Richardeau, "Evaluation of rm ce Monitoring as a Real-Time Method to Estimate Aging of Bond Wire-IGBT Modules Stressed by Power Cycling," IEEE Trans. Ind. Electron., vol. 60, no. 7, pp. 2760–2770, Jul. 2013.

- [11] L. R. GopiReddy, L. M. Tolbert, and B. Ozpineci, "Power Cycle Testing of Power Switches: A Literature Survey," IEEE Trans. Power Electron., vol. 30, no. 5, pp. 2465–2473, May 2015.

- [12] M. Held, P. Jacob, G. Nicoletti, P. Scacco, and M. H. Poech, "Fast power cycling test of IGBT modules in traction application," in Proceedings of Second International Conference on Power Electronics and Drive Systems, 1997, vol. 1, pp. 425–430 vol.1.

- [13] M. Ciappa, "Selected failure mechanisms of modern power modules," Microelectron. Reliab., vol. 42, no. 4, pp. 653–667, Apr. 2002.

- [14] H. Luo, X. Wang, C. Zhu, W. Li, and X. He, "Investigation and Emulation of Junction Temperature for High-Power IGBT Modules Considering Grid Codes," IEEE J. Emerg. Sel. Top. Power Electron., vol. 6, no. 2, pp. 930–940, Jun. 2018.

- [15] R. Bayerer, T. Herrmann, T. Licht, J. Lutz, and M. Feller, "Model for Power Cycling lifetime of IGBT Modules - various factors influencing lifetime," in 5th International Conference on Integrated Power Electronics Systems, 2008, pp. 1–6.

- [16] M. Denk and M. M. Bakran, "Comparison of counting algorithms and empiric lifetime models to analyze the load-profile of an IGBT power module in a hybrid car," in 2013 3rd International Electric Drives Production Conference (EDPC), 2013, pp. 1–6.

- [17] H. Luo, F. Iannuzzo, F. Blaabjerg, W. Li, and X. He, "Separation test method for investigation of current density effects on bond wires of SiC power MOSFET modules," in IECON 2017 - 43rd Annual Conference of the IEEE Industrial Electronics Society, 2017, pp. 1525–1530.

- [18] R. Schmidt and U. Scheuermann, "Separating Failure Modes in Power Cycling Tests," in 2012 7th International Conference on Integrated Power Electronics Systems (CIPS), 2012, pp. 1–6.

- [19] U. Scheuermann and R. Schmidt. "Impact of load pulse duration on power cycling lifetime of Al wire bonds " Microelectron. Reliab., 53 (2013): 1687-1691.

- [20] U. Scheuermann and S. Schuler, "Power cycling results for different control strategies," Microelectron. Reliab., vol. 50, no. 9, pp. 1203–1209, Sep. 2010.

- [21] U. M. Choi, F. Blaabjerg, and S. Jørgensen, "Study on Effect of Junction Temperature Swing Duration on Lifetime of Transfer Molded Power IGBT Modules," IEEE Trans. Power Electron., vol. 32, no. 8, pp. 6434–6443, Aug. 2017.

- [22] L. R. GopiReddy, L. M. Tolbert, and B. Ozpineci, "Power Cycle Testing of Power Switches: A Literature Survey," IEEE Trans. Power Electron., vol. 30, no. 5, pp. 2465–2473, May 2015.

- [23] "IEC 60749-34:2010 | IEC Webstore." [Online]. Available: https://webstore.iec.ch/publication/3381. [Accessed: 17-Mar-2018].

- [24] U. Scheuermann, "Reliability challenges of automotive power electronics," Microelectron. Reliab., vol. 49, no. 9, pp. 1319–1325, Sep. 2009.

- [25] A. Oukaour et al., "Ageing defect detection on IGBT power modules by artificial training methods based on pattern recognition," Microelectron. Reliab., vol. 51, no. 2, pp. 386–391, Feb. 2011.

- [26] S. Dusmez, H. Duran, and B. Akin, "Remaining Useful Lifetime Estimation for Thermally Stressed Power MOSFETs Based on on-State Resistance Variation," IEEE Trans. Ind. Appl., vol. 52, no. 3, pp. 2554–2563, May 2016.

- [27] T. Y. Hung, L. L. Liao, C. C. Wang, W. H. Chi, and K. N. Chiang, "Life Prediction of High-Cycle Fatigue in Aluminum Bonding Wires Under Power Cycling Test," IEEE Trans. Device Mater. Reliab., vol. 14, no. 1, pp. 484–492, Mar. 2014.

- [28] A. Morozumi, K. Yamada, T. Miyasaka, S. Sumi, and Y. Seki, "Reliability of power cycling for IGBT power semiconductor modules," IEEE Trans. Ind. Appl., vol. 39, no. 3, pp. 665–671, May 2003.

[29] K. B. Pedersen and K. Pedersen, "Dynamic Modeling Method of

- [29] K. B. Pedersen and K. Pedersen, "Dynamic Modeling Method of Electro-Thermo-Mechanical Degradation in IGBT Modules," IEEE Trans. Power Electron., vol. 31, no. 2, pp. 975–986, Feb. 2016.

- [30] K. Li, G. Y. Tian, L. Cheng, A. Yin, W. Cao, and S. Crichton, "State Detection of Bond Wires in IGBT Modules Using Eddy Current Pulsed Thermography," IEEE Trans. Power Electron., vol. 29, no. 9, pp. 5000–5009, Sep. 2014.

- [31] C. Bailey, X. Zhu, H. Lu, and C. Yin, "Modelling metal migration for high reliability components when subjected to thermo-mechanical loading," in 2012 IEEE 14th Electronics Packaging Technology Conference (EPTC), 2012, pp. 474–478.

- [32] S. N. S. B. S. Noh, M. F. A. Hamid, and M. N. Tamin, "Mass Migration Damaged Based Model and the Behaviour of Electromigration and Thermomigration in Interconnect," in 2018 IEEE 38th International Electronics Manufacturing Technology Conference (IEMT), 2018, pp. 1–5.

- [33] L. Dupont, S. Lefebvre, M. Bouaroudj, Z. Khatir, J. C. Faugieres, and F. Emorine, "Ageing Test Results of low voltage MOSFET Modules for electrical vehicles," in 2007 European Conference on Power Electronics and Applications, 2007, pp. 1–10.

- [34] M. A. Eleffendi, L. Yang, P. Agyakwa, and C. Mark Johnson, "Quantification of cracked area in thermal path of high-power multi-chip modules using transient thermal impedance measurement," Microelectron. Reliab., vol. 59, pp. 73–83, Apr. 2016.

- [35] L. Feller, S. Hartmann, and D. Schneider, "Lifetime analysis of solder

joints in high power IGBT modules for increasing the reliability for operation at 150°C," Microelectron. Reliab., vol. 48, no. 8, pp. 1161–1166, Aug. 2008.

- [36] C. Tan, G. Zhang, and Z. Gan, "Dynamic study of the physical processes in the intrinsic line electromigration of deep-submicron copper and aluminum interconnects," IEEE Trans. Device Mater. Reliab., vol. 4, no. 3, pp. 450–456, Sep. 2004.

- [37] C. Hau-Riege and Y. Yau, "Electromigration Reliability of Solder Balls," in 2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), 2018, pp. 1–5.

- [38] D. P. Wang et al., "Interconnect Reliability of Low Temperature Solder for Potential Application in Enterprise Computers, Portable, and Automotive Electronics," in 2018 19th International Conference on Electronic Packaging Technology (ICEPT), 2018, pp. 1675–1680.

- [39] T. Parrassin et al., "Statistical electrical and failure analysis of electromigration in advanced CMOS nodes for accurate design rules checker," in 2013 IEEE International Reliability Physics Symposium (IRPS), 2013, pp. 3F.3.1-3F.3.5.

- [40] E. Sancaktar, P. Rajput, and A. Khanolkar, "Correlation of silver migration to the pull out strength of silver wire embedded in an adhesive matrix," IEEE Trans. Compon. Packag. Technol., vol. 28, no. 4, pp. 771–780, Dec. 2005.

- [41] Y. Li, K. Croes, T. Kirimura, Y. K. Siew, and Z. Tökei, "Copper electromigration failure times evaluated over a wide range of voiding phases," in 2012 IEEE International Reliability Physics Symposium (IRPS), 2012, p. EM.1.1-EM.1.4.

- [42] B. J. Baliga, Fundamentals of Power Semiconductor Devices. Springer US, 2008.

- [43] N. Baker, H. Luo, and F. Iannuzzo, "Simultaneous On-State Voltage and Bond-Wire Resistance Monitoring of Silicon Carbide MOSFETs," Energies, vol. 10, no. 3, p. 384, Mar. 2017.

- [44] L.-A. in W. D. Strategies Web Development and Web, "OTG-F fiber optic temperature sensor, probe and transducer," Opsens Industrial. [Online]. Available: https://opsens-solutions.com/products/fiber-optic-temperature-sensors/ otg-f/. [Accessed: 24-Feb-2019].

- [45] U. Choi, I. Vernica, and F. Blaabjerg, "Effect of Asymmetric Layout of IGBT Modules on Reliability of Motor Drive Inverters," IEEE Trans. Power Electron., vol. 34, no. 2, pp. 1765–1772, Feb. 2019.

- [46] A. Castellazzi, T. Funaki, T. Kimoto, and T. Hikihara, "Short-circuit tests on SiC power MOSFETs," in 2013 IEEE 10th International Conference on Power Electronics and Drive Systems (PEDS), 2013, pp. 1297–1300.

**Haoze Luo** (M'15) received the B.S. and M.S. degrees from the Department of Electrical Engineering, Hefei University of Technology, Hefei, China, in 2008 and 2011, respectively. He received the Ph.D. degree from Zhejiang University, Hangzhou, China in 2015. From January to April 2015, he was a visiting researcher at Newcastle University, Newcastle upon Tyne, U.K. From October 2015 to May 2018, he was a Postdoc at the Department of Energy Technology in Aalborg University Denmark. His research interests include

high-power converters and reliability of high-power semiconductor modules.

**Francesco Iannuzzo** (*M'09*) received the M.Sc. degree in Electronic Engineering and the Ph.D. degree in Electronic and Information Engineering from the University of Naples, Italy, in 1997 and 2002, respectively. He is primarily specialized in power device modelling. He is currently a professor in reliable power electronics at the Aalborg University, Denmark, where he is also part of CORPE, the Center of Reliable Power Electronics. His research interests are in the field of reliability of power devices, including mission-profile based life

estimation, condition monitoring, failure modelling and testing up to MW-scale modules under extreme conditions, like overvoltage, overcurrent, over temperature and short circuit. He is author or co-author of more than 190 publications on journals and international conferences, three book chapters and four patents. Besides publication activity, over the past years he has been invited for several technical seminars about reliability at first conferences as ISPSD, EPE, ECCE, PCIM and APEC.

Prof. Iannuzzo is a senior member of the IEEE (Reliability Society, Power Electronic Society, Industrial Electronic Society and Industry Application Society). He currently serves as Associate Editor for Transactions on Industry Applications, and is secretary elect of IAS Power Electronic Devices and Components Committee. He was the general chair of ESREF 2018, the 29<sup>th</sup> European Symposium on Reliability of Electron devices, Failure physics and analysis.

**Nick Baker** received the M.Eng. degree in electrical and electronic engineering from Loughborough University, Leicestershire, U.K., in 2011. In 2013, he started working toward the Ph.D. degree at Aalborg University, Aalborg, Denmark, in temperature measurements of power semiconductor devices using electrical parameters. Mr. Baker received the European Power Electronics Association Young Member Award in 2015.

**Frede Blaabjerg** (S'86 – M'88 – SM'97 – F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. From 2017 he became a Villum Investigator. He is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn Technical University (TTU) in Estonia. His current

research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications. He has received 30 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014 and the Villum Kann Rasmussen Research Award 2014. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he serves a President of IEEE Power Electronics Society. He is Vice-President of the Danish Academy of Technical Sciences too. He is nominated in 2014-2018 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.

**Wuhua Li** (*M'09*) received the B.Sc. and Ph.D. degree in Power Electronics and Electrical Engineering from Zhejiang University, Hangzhou, China, in 2002 and 2008, respectively.

From 2004 to 2005, he was a Research Intern, and from 2007 to 2008, a Research Assistant in GE Global Research Center, Shanghai, China. From 2008 to 2010, he joined the College of Electrical Engineering, Zhejiang University as a Post doctor. In 2010, he was promoted as an Associate Professor. Since 2013, he has been a Full Professor at Zhejiang

University. From 2010 to 2011, he was a Ryerson University Postdoctoral Fellow with the Department of Electrical and Computer Engineering, Ryerson University, Toronto, ON, Canada. His research interests include power devices, converter topologies and advanced controls for renewable energy based power systems. Dr. Li has published more than 200 peer-reviewed technical papers and holds over 30 issued/pending patents. Due to his excellent teaching and research contributions, Dr. Li received the 2012 Distinguished Young Scholar from Zhejiang University, the 2012 Delta Young Scholar from Delta Environmental & Educational Foundation, the 2012 Outstanding Young

Scholar from National Science Foundation of China (NSFC). He received one National Natural Science Award and four Scientific and Technological Achievement Awards from Zhejiang Provincial Government and the State Educational Ministry of China.

**Xiangning He** (*M'95--SM'96--F'10*) received the B.Sc. and M.Sc. degrees from Nanjing University of Aeronautical and Astronautical, Nanjing, China, in 1982 and 1985, respectively, and the Ph.D. degree from Zhejiang University, Hangzhou, China, in 1989.

From 1985 to 1986, he was an Assistant Engineer at the 608 Institute of Aeronautical Industrial General Company, Zhuzhou, China. From 1989 to 1991, he was a Lecturer at Zhejiang University. In 1991, he obtained a Fellowship from the Royal Society of U.K., and conducted research in the Department of

Computing and Electrical Engineering, Heriot-Watt University, Edinburgh, U.K., as a Post-Doctoral Research Fellow for two years. In 1994, he joined Zhejiang University as an Associate Professor. Since 1996, he has been a Full Professor in the College of Electrical Engineering, Zhejiang University. He was the Director of the Power Electronics Research Institute, the Head of the Department of Applied Electronics, the Vice Dean of the College of Electrical Engineering, and he is currently the Director of the National Specialty Laboratory for Power Electronics, Zhejiang University. His research interests are power electronics and their industrial applications. Dr. He is a Fellow of The Institute of Electrical and Electronics Engineers (IEEE) and was appointed as IEEE Distinguished Lecturer by the IEEE Power Electronics Society 2011--2015. He is also a Fellow of the Institution of Engineering and Technology (formerly IEE), U.K.