Study of gate oxide traps in Hf0[subscript 2]/AlGaN/ GaN metal-oxide-semiconductor high-electron-mobility transistors by use of ac transconductance method

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

| Citation     | Sun, X., O. I. Saadat, K. S. Chang-Liao, T. Palacios, S. Cui, and T.<br>P. Ma. "Study of Gate Oxide Traps in HfO[subscript 2]/AlGaN/GaN<br>Metal-Oxide-Semiconductor High-Electron-Mobility Transistors by<br>Use of Ac Transconductance Method." Appl. Phys. Lett. 102, no. 10<br>(2013): 103504. © 2013 American Institute of Physics |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| As Published | http://dx.doi.org/10.1063/1.4795717                                                                                                                                                                                                                                                                                                     |

| Publisher    | American Institute of Physics (AIP)                                                                                                                                                                                                                                                                                                     |

| Version      | Final published version                                                                                                                                                                                                                                                                                                                 |

| Citable link | http://hdl.handle.net/1721.1/90501                                                                                                                                                                                                                                                                                                      |

| Terms of Use | Article is made available in accordance with the publisher's policy and may be subject to US copyright law. Please refer to the publisher's site for terms of use.                                                                                                                                                                      |

DSpace@MIT

## Study of gate oxide traps in HfO2/AlGaN/GaN metal-oxide-semiconductor highelectron-mobility transistors by use of ac transconductance method

X. Sun, O. I. Saadat, K. S. Chang-Liao, T. Palacios, S. Cui, and T. P. Ma

Citation: Applied Physics Letters **102**, 103504 (2013); doi: 10.1063/1.4795717 View online: http://dx.doi.org/10.1063/1.4795717 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/102/10?ver=pdfcov Published by the AIP Publishing

Articles you may be interested in

Investigation of gate leakage mechanism in Al2O3/Al0.55Ga0.45N/GaN metal-oxide-semiconductor highelectron-mobility transistors Appl. Phys. Lett. **104**, 153510 (2014); 10.1063/1.4871802

Characterization of interface states in Al2O3/AlGaN/GaN structures for improved performance of high-electronmobility transistors J. Appl. Phys. **114**, 244503 (2013); 10.1063/1.4859576

Quantitative characterization of interface traps in Al2O3/AlGaN/GaN metal-oxide-semiconductor high-electronmobility transistors by dynamic capacitance dispersion technique Appl. Phys. Lett. **103**, 033510 (2013); 10.1063/1.4813912

Bulk and interface trapping in the gate dielectric of GaN based metal-oxide-semiconductor high-electron-mobility transistors Appl. Phys. Lett. **102**, 243509 (2013); 10.1063/1.4811754

A comprehensive analytical model for threshold voltage calculation in GaN based metal-oxide-semiconductor high-electron-mobility transistors Appl. Phys. Lett. **100**, 113509 (2012); 10.1063/1.3694768

## Study of gate oxide traps in HfO<sub>2</sub>/AlGaN/GaN metal-oxide-semiconductor high-electron-mobility transistors by use of ac transconductance method

X. Sun,<sup>1,a)</sup> O. I. Saadat,<sup>2</sup> K. S. Chang-Liao,<sup>3</sup> T. Palacios,<sup>2</sup> S. Cui,<sup>1</sup> and T. P. Ma<sup>1</sup> <sup>1</sup>Yale University, 15 prospect St, New Haven, Connecticut 06520, USA <sup>2</sup>Massachusetts Institute of Technology, 77 Massachusetts Avenue, Cambridge, Massachusetts 02139, USA <sup>3</sup>National Tsing Hua University Engineering and System Science, 101 Sec 2 Kuang-Fu Rd, Hsinchu 30013, Taiwan

(Received 22 November 2012; accepted 5 March 2013; published online 13 March 2013)

We introduce an ac-transconductance method to profile the gate oxide traps in a HfO<sub>2</sub> gated AlGaN/GaN Metal-Oxide-Semiconductor High-Electron-Mobility Transistors (MOS-HEMTs) that can exchange carriers with metal gates, which in turn causes changes in analog and pulsed channel currents. The method extracts energy and spacial distributions of the oxide and interface traps under the gate from the frequency dependence of ac transconductance. We demonstrate the method using MOS-HEMTs with gate oxides that were annealed at different temperatures. © 2013 American Institute of Physics. [http://dx.doi.org/10.1063/1.4795717]

Although introducing a gate dielectric in an AlGaN/ GaN High Electron Mobility Transistor (HEMT) can effectively reduce the gate leakage and increase the Ion/Ioff ratio,1-8 some of the problems in conventional HEMTs may still be lingering in the resulting Metal-Oxide-Semiconductor High-Electron-Mobility Transistors (MOS-HEMTs). One example is the so called "current collapse" phenomenon, decreases in drain current (Id) and transconductance (G<sub>m</sub>) under pulsed or high frequency conditions, which can be efficiently suppressed for HEMT devices as long as their access regions are properly passivated.<sup>9–14</sup> The re-occurrence of such a problem in MOS-HEMTs may then be attributable to what happens under the gate electrode. In a HEMT device, surface charge immediately under the gate electrode has basically no effect on the channel carriers due to the screening effect of the gate metal; In an MOS-HEMT, however, the trapped charges at the dielectric/AlGaN interface can cause partial depletion of the carriers in the underlying channel due to the presence of the dielectric layer that weakens the screening effect of the gate metal, leading to the current collapse phenomenon.

In this paper, we employ a newly developed  $ac-G_m$  method<sup>15,16</sup> to extract energy and spacial distributions of the interface and oxide traps in the gate region of the MOS-HEMT. It will be shown that, under low or medium drain bias (V<sub>ds</sub>) (<6 V), the current collapse phenomenon is associated with the traps in the gate oxide and its interface in HfO<sub>2</sub>-gated AlGaN/GaN MOS-HEMT devices, which depend on the annealing temperature.

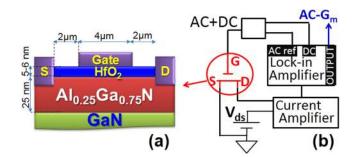

The HfO<sub>2</sub>-gated MOS-HEMTs used in this study are fabricated on AlGaN/GaN/Si HEMT structures grown by the Veeco Corporation, as shown in Fig. 1(a). Atomic Layer Deposition (ALD)—HfO<sub>2</sub> (5–6 nm) is deposited as the gate dielectric by the use of tetrakis dimethylamido-hafnium and de-ionized (DI)-water as precursors at a temperatures of 250 °C. Some devices received post-metal-anneal in N<sub>2</sub> at 400 °C or 600 °C. The access region width is 2  $\mu$ m on each

side of the gate, and the gate length is  $4 \,\mu\text{m}$ . More details of device processing can be found elsewhere.<sup>17</sup>

DC- and pulsed current-voltage (I-V) curves are measured by the use of a Keithley model 4200 parameter analyzer. The ac-G<sub>m</sub> in this study is measured by the use of a lock-in amplifier (see Fig. 1(b)), covering a frequency range from 1 mHz to 10 kHz, such that the effects of most of the slow oxide traps can be detected. During the measurement, a dc bias mixed with an ac sinusoidal signal ( $V_{rms} = 20 \text{ mV}$ ) is applied on the gate while a small dc bias (50 mV) is applied on the drain, and then the ac-G<sub>m</sub> is read out over a range of frequencies. The measurement details can be found elsewhere.<sup>15</sup> To investigate faster traps, an impedance meter or a network analyzer can also be used to extract G<sub>m</sub> at higher frequencies.<sup>18,19</sup> In any case, the ac-G<sub>m</sub> analyzing method should be readily applicable in a wide range of frequencies.

The frequency dispersion of the ac- $G_m$  reflects the frequency dependence of the carrier density in the channel, due to the capture/emission of carriers by the traps above the channel. For an ac signal on the gate with frequency  $\omega$ , the traps with time constant  $\tau$  higher than  $1/\omega$  are not likely to respond, and, therefore, have little influence on the ac- $G_m$ dispersion. As  $\omega$  decreases (increases), however, traps with longer (shorter)  $\tau$  start to respond and cause a change in the ac- $G_m$ . The magnitude of the change in  $G_m$  reflects the

FIG. 1. (a) Schematic of a MOS-HEMT device; (b) the set-up for measuring  $ac-G_m$  with a lock-in amplifier, where the device is biased in the linear region.

## © 2013 American Institute of Physics

nis article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 18.62.11.99

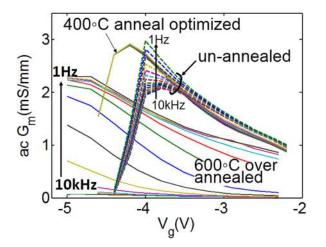

FIG. 2. The negative ac-G<sub>m</sub> frequency dispersions measured on unannealed, 400  $^\circ\text{C}$  and 600  $^\circ\text{C}$  annealed devices.

density of oxide traps  $(N_{ot})$  having that certain time constant. Our calculation<sup>16</sup> shows that the ac-G<sub>m</sub> probes mainly the traps with the energy E<sub>T</sub> aligned to the Fermi level of the reservoir of carriers. And the effective distance of traps from the reservoir (x) can be determined by the use of the quantum tunneling model.

Although the ac-G<sub>m</sub> method used here for the MOS-HEMT is the same as that originally used for MOSFETs.<sup>15,16</sup> there is an important difference in the trapping mechanisms between these two kinds of devices that causes drastically different frequency dispersions. In an MOSFET, it is known that electron trapping in the gate dielectric usually arises from electrons injected from the channel into the trap sites. In an MOS-HEMT, however, the electrons in the buried GaN channel are much less likely to be injected into the gate oxide, due to the presence of an additional thick barrier layer (25 nm AlGaN in Fig. 1(a)). On the other hand, electron trapping in the gate oxide layer (5-6 nm HfO<sub>2</sub>) of the MOS-HEMT may arise from electrons that tunnel from the gate electrode to the trap sites in the gate oxide or at its oxide/AlGaN interface. As a consequence, the MOS-HEMT shows the following two features that are opposite to those revealed in MOSFET: (1) counter-clockwise  $I_d$ -V<sub>g</sub> (gate bias) hysteresis, and (2) lower pulsed I-V's than the corresponding dc values. The 2nd feature mentioned above is also

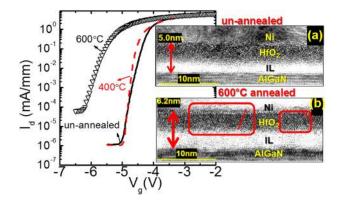

FIG. 3. The  $I_d$ - $V_g$  at several annealing temperatures ( $V_{ds}$  is 50 mV). The inset shows the TEM pictures of the gate stack in (a) un-annealed and (b) 600 °C annealed devices.

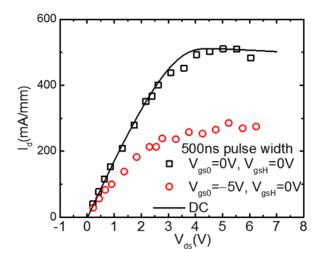

FIG. 4. The dc  $I_d$ - $V_d$  curve and two 500 ns pulsed  $I_d$ - $V_d$  curves for the unannealed device, measured by the double pulse technique, in which the gate quiescent points are 0 V and -5 V respectively, while the drain quiescent point and the gate pulse high level are both 0 V.

reflected by MOS-HEMT's negative frequency dispersion, i.e., the ac- $G_m$  has a higher value at a lower frequency, which has been observed in Ref. 20.

The ac-G<sub>m</sub> curves of an un-annealed, 400  $^\circ C$  and 600  $^\circ C$ annealed devices are plotted as functions of the dc gate bias with frequency as a parameter (1 Hz to 10 kHz) in Fig. 2. The un-annealed device shows a sharp decrease of the ac-G<sub>m</sub> with increasing frequency such that within a few Hertz of the incremental frequency the peak ac-G<sub>m</sub> falls below that of the dc value. As mentioned previously, the large negative ac-G<sub>m</sub> dispersion of the un-annealed device may have resulted from the traps in the gate HfO<sub>2</sub> and its interface. Also the dispersion appears more pronounced at higher negative gate voltages and slows down at high frequencies, suggesting that the traps are more active under higher gate electric fields and have long time constants. The large ac-G<sub>m</sub> dispersions in the un-annealed device can be effectively reduced by a  $400\,^\circ\mathrm{C}$ anneal. As shown in Fig. 2, the ac-G<sub>m</sub> dispersion has diminished after 400 °C anneal. However, a higher annealing temperature, such as 600 °C, causes a dramatic increase in the ac-G<sub>m</sub> dispersion.

The dependence on the annealing temperature is qualitatively consistent with the sub-threshold slope (SS) data

TABLE I. Equations used in the AC-G<sub>M</sub> method.

| $\overline{E_T - E_F} = (V_g - V_{th})x/x_0$<br>$x = \lambda \ln(1/\omega\tau_0), \ \tau_0 \approx (n_0 v_t \sigma)^{-1}, \ \lambda = \hbar/\sqrt{8m^*(E_c - E_F)}$ |                                  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| $N_{ot}(E_T, x) = \frac{dG_m}{dln\omega} \left[ \left( \frac{x}{x_0} \right)^2 q \cdot \lambda \cdot V_{ds} \mu_{dc} \frac{W}{L} \right]^{-1}$                      |                                  |  |  |

| $E_F$ : gate metal Fermi level                                                                                                                                      | $V_g$ : dc bias on gate          |  |  |

| $x_0$ : total thickness of gated oxide                                                                                                                              | $V_{th}$ : threshold voltage     |  |  |

| $\lambda$ : the decay constant of tunneling                                                                                                                         | $v_t$ : thermal velocity         |  |  |

| $\omega$ : the frequency of ac gate signals                                                                                                                         | $\sigma$ : capture cross section |  |  |

| $\tau_0: \tau$ for traps with $x = 0$ and $E_T = E_F$                                                                                                               | $N_{ot}$ : oxide trap density    |  |  |

| $n_0$ : carrier density in reservoirs                                                                                                                               | $V_{ds}$ : dc drain bias         |  |  |

| $m^*$ : the effective mass in gate oxides                                                                                                                           | $\mu_{dc}$ : dc mobility         |  |  |

| $E_c$ : gate oxide CB edge energy                                                                                                                                   | W/L: channel width/length        |  |  |

his article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 18.62.11.99 On: Thu, 12 Jun 2014 16:32:37

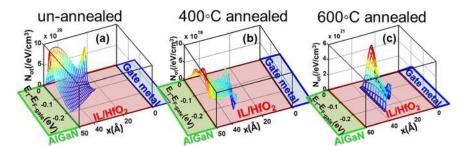

FIG. 5.  $N_{ot}$  distributions extracted by the use of the ac-G<sub>m</sub> method in (a) un-annealed, (b) 400 °C and (c) 600 °C N<sub>2</sub> annealed devices. Note that the x-axis depicts the physical dimension of the gate stack and it shows that after 600 °C anneal, the physical thickness of the IL/HfO<sub>2</sub> increased from ~5 to ~6 nm, according to the TEM in Fig. 3.

obtained from the dc I-V's, which however has lower sensitivity than the ac- $G_m$  dispersion. As seen in Fig. 3, the SS of the device after the 400 °C anneal is slightly steeper than the un-annealed, and after 600 °C annealing the SS collapsed. TEM results suggest the interfacial layer (IL) growth and oxide poly-crystallization in the gated region at 600 °C (the inset in Fig. 3), consistent with the serious degradation in the ac and dc results of the 600 °C annealed sample.

In addition to the gate traps, it is necessary to know how much the traps in access regions have contributed to the observed ac-G<sub>m</sub> dispersions, which can be evaluated by pulsed  $I_d$ - $V_d$  measurements. Figure 4 shows the dc- and pulsed Id-Vd's of the problematic un-annealed device, in which the two 500 ns pulsed curves have the same gate pulse high level (0 V) and drain quiescent point (0 V), but different gate quiescent points at -5V and 0V (the cold curve), respectively. As seen, similar drain currents are observed between the dc and the cold curves, independent of the drain voltage. In contrast, a large drop of drain current is observed when the gate pulse is first rested at -5 V. This is because the gate traps are occupied by gate injected electrons at -5 V and cannot be detrapped fast enough when the gate voltage is pulsed up to 0V. As a result, the un-detrapped electrons reduce the two-dimensional electron gas density in the channel and result in a lower pulsed drain current. The strong dependence on gate quiescent points indicates that, for  $V_{ds}$  below 6 V, the drop of the drain current is primarily due to the gate traps. Therefore, the observed ac-G<sub>m</sub> dispersions in Fig. 2 can be attributed to the gate traps rather than the traps in the access regions.

We then used the ac-G<sub>m</sub> method to extract the density distributions  $(N_{ot})$  of these traps in terms of the energy (E) and the distance from the gate metal (x), following the equations in Table I,<sup>15,16</sup> in which  $\tau_0$  is estimated to be  $1 \times 10^{-12}$  s with  $n_0 \sim 10^{22}$ /cm<sup>3</sup>,  $v_t \sim 10^7$  cm/s, and  $\sigma \sim 10^{-17}$ cm<sup>2</sup>;  $\lambda$  is taken as 1.8 Å with  $m^* \sim 0.1 m_0$  in  $HfO_2$  and  $E_c - E_F$ = 3.0 eV for Ni/HfO<sub>2</sub>. As shown in Fig. 5(a), there appears a large peak near the HfO2/AlGaN interface for the unannealed device with a peak value close to  $10^{21}$ /cm<sup>3</sup>/eV. The approximate energy level of these traps has been determined to be around  $\sim 1.5 \,\text{eV}$  below the conduction band edge of AlGaN, which is in agreement with that reported in the literature.<sup>21,22</sup> These traps should account for the observed degradations in the ac-G<sub>m</sub>, pulsed and dc currents in the unannealed device shown in Figs. 2-4. In contrast, after the 400 °C anneal, the corresponding peak  $N_{ot}$  is in the mid-10<sup>19</sup>/ cm<sup>3</sup> range in Fig. 5(b), which is more than an order of magnitude lower compared to the un-annealed Not. Actually, this annealing-optimized trap density is of the same order as in the ALD HfO<sub>2</sub> used in MOSFETs.<sup>23,24</sup> After the 600 °C anneal, the peak  $N_{ot}$  is in the mid- $10^{21}$ /cm<sup>3</sup>/eV range, with its peak position moving into the high  $\kappa$  dielectric in Fig. 5(c), consistent with the TEM results in Fig. 3.

In summary, we have shown that the  $ac-G_m$  dispersion of the HfO<sub>2</sub> gated MOS-HEMT devices measured at low to medium V<sub>ds</sub> is primarily caused by traps under the gate. We have also shown that one can extract energy and spatial distributions of the gate oxide interface traps in a MOS-HEMT from such  $ac-G_m$  dispersions. The method complements the existing techniques for MOS-HEMT gate stack characterization, such as dc-subthreshold swing and pulsed I-V measurements. It should also be noted that, although only negative  $ac-G_m$  frequency dispersions are discussed in this work, positive frequency dispersions could also be found under high positive gate biases, when there is a significant amount of traps exchanging carriers with the channel, such as the bulk traps in AlGaN. This will be an interesting topic for future studies.

This work was supported partially by the National Science Foundation (NSF) under Contract No. MRSEC DMR 1119826, and partially by the Office of Naval Research (ONR) under the MURI DEFINE program.

- <sup>1</sup>P. D. Ye, B. Yang, K. K. Ng, J. Bude, G. D. Wilk, S. Halder, and J. C. M. Hwang, Appl. Phys. Lett. **86**, 063501 (2005).

- <sup>2</sup>Y. Z. Yue, Y. Hao, J. C. Zhang, J. Y. Ni, W. Mao, Q. Feng, and L. J. Liu, IEEE Electron Devices Lett. **29**, 838–840 (2008).

- <sup>3</sup>F. Husna, M. Lachab, M. Sultana, V. Adivarahan, Q. Fareed, and A. Khan, IEEE Trans. Electron Devices **59**, 2424–2429 (2012).

- <sup>4</sup>C. C. Hu, M. S. Lin, T. Y. Wu, F. Adrianto, P. W. Sze, C. L. Wu, and Y. H. Wang, IEEE Trans. Electron Devices **59**, 121–127 (2012).

- <sup>5</sup>S. Basu, P. K. Singh, S.-K. Lin, P.-W. Sze, and Y.-H. Wang, IEEE Trans. Electron Devices **57**, 2978–2985 (2010).

- <sup>6</sup>L.-H. Huang, S.-H. Yeh, C.-T. Lee, H. P. Tang, J. Bardwell, and J. B. Webb, IEEE Electron Dev. Lett. **29**, 284–286 (2008).

- <sup>7</sup>O. I. Saadat, J. W. Chung, E. L. Piner, and T. Palacios, IEEE Electron Device Lett. **30**, 1254–1256 (2009).

- <sup>8</sup>J. W. Chung, T.-W. Kim, and T. Palacios, IEEE Electron Devices Meeting (IEDM) **2011**, 676–679.

- <sup>9</sup>S. C. Binari, P. B. Klein, and T. E. Kazior, Proc. IEEE **90**, 1048–1058 (2002).

- <sup>10</sup>R. Vetury, N. Q. Q. Zhang, S. Keller, and U. K. Mishra, IEEE Trans. Electron Devices 48, 560–566 (2001).

- <sup>11</sup>S. C. Binari, K. Ikossi, J. A. Roussos, W. Kruppa, D. Park, H. B. Dietrich, D. D. Koleske, A. E. Wickenden, and R. L. Henry, IEEE Trans. Electron Devices 48, 465–471 (2001).

- <sup>12</sup>B. Luo, J. W. Johnson, J. Kim, R. M. Mehandru, B. P. Gila, A. H. Onstine, C. R. Abernathy, S. J. Pearton, A. G. Baca, R. D. Briggs, R. J. Shul, C. Monier, and J. Han, Appl. Phys. Lett. **80**, 1661–1663 (2002).

- <sup>13</sup>T. Hashizume, S. Ootomo, and H. Hasegawa, Appl. Phys. Lett. 83, 2952–2954 (2003).

- <sup>14</sup>F. Gao, D. Chen, B. Lu, H. L. Tuller, C. V. Thompson, S. Keller, U. K. Mishra, and T. Palacios, IEEE Electron Device Lett. 33, 1378–1380 (2012).

- <sup>15</sup>X. Sun, S. Cui, A. Alian, G. Brammertz, C. Merckling, D. Lin, and T. P. Ma, IEEE Electron Device Lett. **33**, 438–440 (2012).

- <sup>16</sup>X. Sun, N. Xu, F. Xue, A. Alian, F. Andrieu, B.-Y. Nguyen, T. Poioux, O. Faynot, J. Lee, S. Cui, and T. P. Ma, IEEE Electron Devices Meeting (IEDM) **2012**, 462–465.

- <sup>17</sup>O. I. Saadat and T. Palacios, in *Solid-State Device Research Conference* (*ESSDERC*) (2011), pp. 287–290.

- <sup>18</sup>D. Lin, A. Alian, S. Gupta, B. Yang, E. Bury, S. Sioncke, R. Degraeve, M. L. Toledano, R. Krom, P. Favia, H. Bender, M. Caymax, K. C. Sarawat, N. Collaert, and A. Thean, IEEE Electron Devices Meeting (IEDM) **2012**, pp. 645–648.

- pp. 645–648.

<sup>19</sup>S. Johansson, M. Berg, K.-M. Persson, and E. Lind, IEEE Trans. Electron Devices 60, 776–781 (2013).

- <sup>20</sup>D. S. Lee, J. W. Chung, H. Wang, X. Gao, S. Guo, P. Fay, and T. Palacios, IEEE Electron Device Lett. **32**, 755–758 (2011).

- <sup>21</sup>J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, Appl. Phys. Lett. 77, 250–252 (2000).

- <sup>22</sup>I. P. Smorchkova, C. R. Elsass, J. P. Ibbetson, R. Ventury, B. Heying, P. T. Fini, E. Haus, S. P. DenBaars, J. S. Speck, and U. K. Mishra, J. Appl. Phys. 86, 4520–4526 (1999).

- <sup>23</sup>E. Simoen, A. Mercha, L. Pantisano, C. Claeys, and E. Young, IEEE Trans. Electron Devices **51**, 780–783 (2004).

- <sup>24</sup>D. Heh, C. D. Young, G. A. Brown, P. Y. Hung, A. Diebold, G. Bersuker, E. M. Vogel, and J. B. Bernstein, Appl. Phys. Lett. 88, 152907 (2006).