# université BORDEAUX

# THÈSE

#### Présentée à

## L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR

### Par Mathieu JAOUL

POUR OBTENIR LE GRADE DE

#### DOCTEUR

Spécialité : ÉLECTRONIQUE

\*\*\*\*

### Study of HBT operation beyond breakdown voltage. Definition of a Safe Operating Area in this operation regime including the aging laws

\*\*\*\*\*

Soutenue le: 5 Mai 2020

Après avis de :

#### M. Vincenzo D'ALESSANDRO M. Christophe LALLEMENT

Professeur, Université de Naples Professeur, Université de Strasbourg

Devant la Commission d'Examen formée de:

M. Didier CÉLIIngénieurM. Sorin CRISTOLOVEANUDirecteur dM. Vincenzo D'ALESSANDROProfesseurM. Yann DevalProfesseurM. Gerhard FISCHERIngénieurM. Christophe LALLEMENTProfesseurMme Cristell MANEUXProfesseurM. François MARCMaitre de CM. Thomas ZIMMERProfesseur

Ingénieur Directeur de recherche Professeur Ingénieur Professeur Professeur Maitre de Conférence Professeur STMicroelectronics (Crolles) CNRS Grenoble Université de Naples Université de Bordeaux IHP microelectronics Université de Strasbourg Université de Bordeaux Université de Bordeaux Université de Bordeaux Rapporteur Rapporteur

Examinateur Examinateur Rapporteur Président Examinateur Rapporteur Directeur de thèse Examinateur Co-directeur de thèse

-- 2020 --

私が愛していた、そして愛している人々のために.

### Acknowledgments

This thesis work is the result of my three (and more) years of experience as a PhD student at the University of Bordeaux. The presented work has been realized in two distant places, at Bordeaux in the University of Bordeaux (IMS) and in Crolles with STMicroelectronics. I would like to thank all the people who contributed to complete this work for all their kindness and patience and to make this thesis a reality.

I especially want to thank my supervisors, Cristell Maneux and Thomas Zimmer for their constant support and contribution to this work. It is thanks to your personal involvement that this thesis work went so far.

I'll not forget my mentor and industry supervisor, Didier Céli. I am so grateful for what you have done for me during this thesis. You always gave me a constant support whenever I needed it. Thanks you for all the work you have done for me. Back in my internship, you gave me all the necessary knowledge to understand everything during my thesis. You taught me so much about microelectronics and your bipolar world and to be interested in modeling. You deserve all the credit for this thesis work! Thank you so much Didier for being such a stimulating supervisor!

This work has been also possible thanks to the talks with the University of Dresden, and more particularly, to Michael Schröter thanks to whom, my work has been implemented in new HICUM versions.

I also would like to thank the entire modeling team at STMicroelectronics, including the people who were part of the team and left for a "better" company (Krishna and Tommy) for all the great time we spent together.

I want also to thank Nicolas Guitard and Frederic Monsieur for sharing their knowledge about TCAD. It helped me a lot to understand the bipolar physics and make my models even more consistent.

I express all my gratitude to the IMS nanoelectronics team for these two years in Bordeaux. Thanks Magali for the good times speaking with you in the measurement room. I enjoyed so much talking with you. Thanks Sebastien and Marina for always bringing positive vibes in our team. I will also give all the credit to Francois Marc, you support us a lot to develop the new aging model. A special thanks to Marine Couret. You helped me a lot to go through hard times ... From our measurement campaigns to modeling, our thesis were bounded. You are one of the reason I enjoyed my work at the IMS. It was a big pleasure. Thanks!

I do not forget my other fellow lab office mates, Albany, Florent, Mingming, JB, Matthieu, Isabel, Adrien, Quentin and Marco. Thanks for all the great extra-work activities!

Finally, a last but not least thank you to my entire family. I am particularly thankful to my parents, my brother's little family (with Charly and Sophie) and my cousin, Mylène. Thanks for your constant support during the three years of my PhD work and thanks for being with me all along this journey.

Mathieu

### Abstract

The development of new BiCMOS technology will be possible, thanks to the SiGe:C HBTs technological improvements to reach dynamic performance beyond 0.5 THz. An important aspect to be investigated is the Safe Operating Area (SOA) beyond the traditional  $BV_{CEO}$ . In fact, due to the complexity of future architectures of HBTs (like the B55X from STMicroelectronics) and their nanoscale size, an increase of the wear-out mechanisms occurring in these transistors is expected. In addition, because of the increasing dependence of circuit design on software tools, it is expected that additional efforts will be required to develop more predictive compact models. Thus, the SOA sub-project is designed to describe the functional safety area of nanoscale SiGe:C HBTs allowing the compact model to take into account critical aspects.

After a short introduction, a precise description of the transistor operations beyond the breakdown voltage is detailed in the second chapter. The compact model HICUM is improved to account for the mechanisms occurring in this region to accurately model the avalanche regime and the pinch-in effect. This new model is validated on TCAD simulations and through electrical measurements on different devices, architecture, geometries and temperatures.

In the third chapter, the investigation is deepen towards the device border's operation. A study of the pinch-in effect and the snapback behavior is therefore realized to understand the operation limitations at high currents and voltages and a stable operation regime is introduced.

In the fourth chapter, accelerated aging tests are carried out at the boundaries of the safe operating area to submit the transistor to thermal and hot carriers stresses during its operation. An aging model is developed to account for the wear-out mechanism occurring in that regime.

To conclude, this work allowed to increase the modeling of SiGe HBTs at high voltages and currents accounting for the wear-out mechanisms occurring in that operation regime.

### Résumé

Le développement de nouvelles filières BiCMOS permettra, grâce aux améliorations technologiques apportées aux TBH (Transistor Bipolaire à Hétérojonction) SiGe:C, d'atteindre des performance dynamiques au-delà de 0.5 THz. Un aspect important doit être investigué: il s'agit de l'aire de sécurité de fonctionnement (SOA : Safe operating area) au-delà du classique BVCEO. En effet, de par la complexité des futures architectures de TBH (comme la B55X de chez STMicroelectronics) et de par leur taille nanométrique, il est attendu une augmentation des effets physiques présents dans ces transistors. Par ailleurs, en raison de la dépendance croissante de la conception de circuits vis-à-vis des outils logiciels, on s'attend à devoir développer des efforts supplémentaires pour concevoir des modèles compacts davantage prédictifs. Ainsi, le sous-projet SOA est conçu pour décrire l'aire de sécurité de fonctionnement des TBH SiGe:C de taille nanométrique en vue de son intégration dans le modèle compact en tenant compte des aspects critiques.

Dans le premier chapitre, une description précise des régimes de fonctionnement audelà de la tension de claquage  $BV_{CEO}$  est développée. Le modèle compact HICUM est amélioré pour prendre en compte les mécanismes se produisant dans cette région afin de modéliser précisément le phénomène d'avalanche et l'effet de focalisation du courant au centre de l'émetteur. Une validation de ce nouveau modèle est réalisée au travers de simulations TCAD mais aussi par des caractérisations électriques de différents TBH de tailles variées et pour de multiples températures.

Dans le second chapitre, le comportement des transistors bipolaires proche des limites de fonctionnement a été étudié. Une étude de l'effet de focalisation du courant et du phénomène de "snapback" est réalisée pour en définir précisement les limites de fonctionnement à forts courants et tensions et une zone de stabilité est définie.

Dans de troisième chapitre, le vieillissement accéléré de TBH est réalisé pour des régimes de fonctionnement aux frontières de la zone de sécurité de fonctionnement. Un modèle de vieillissement est alors développé pour prendre en compte les mécanismes d'usure se produisant dans ces régimes de fonctionnement.

En conclusion, ce travail a permis de modéliser de manière précise les TBH SiGe à forts courant et tensions tout en prenant en compte les mécanismes d'usure se produisant dans ces régimes de polarisation.

## **Table of Contents**

| Ta       | able | of Con   | tents                                                                 | ix |

|----------|------|----------|-----------------------------------------------------------------------|----|

| 1        | Intr | oducti   | ion                                                                   | 1  |

|          | 1.1  | Motiv    | ation                                                                 | 1  |

|          | 1.2  | Thesis   | s content                                                             | 8  |

| <b>2</b> | Phy  | vsics ai | nd modeling of impact ionization in HBTs                              | 9  |

|          | 2.1  | Impac    | t Ionization Mechanism                                                | 9  |

|          | 2.2  | Weak     | and Strong Avalanche Model Description                                | 11 |

|          | 2.3  | High (   | Current Effects                                                       | 19 |

|          |      | 2.3.1    | Impact Ionization Formulation in TCAD Simulations                     | 19 |

|          |      | 2.3.2    | Impact Ionization at medium currents                                  | 23 |

|          |      | 2.3.3    | Impact Ionization at high currents                                    | 27 |

|          |      | 2.3.4    | Non constant doping concentration in the epi-layer                    | 29 |

|          |      | 2.3.5    | Unified expression to account for the high current effects $\ldots$ . | 31 |

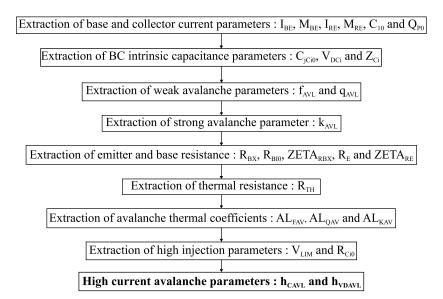

|          | 2.4  | Paran    | neter Extraction Flow                                                 | 36 |

|          |      | 2.4.1    | Measurement setups                                                    | 37 |

|          |      | 2.4.2    | Weak Avalanche parameters                                             | 38 |

|          |      | 2.4.3    | Strong Avalanche parameter                                            | 40 |

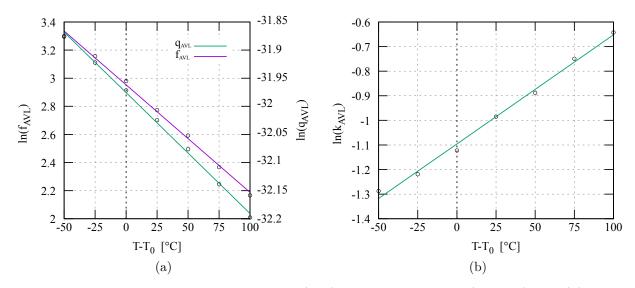

|          |      | 2.4.4    | Avalanche Thermal Coefficients                                        | 40 |

|          |      | 2.4.5    | Avalanche current dependency                                          | 42 |

|          | 2.5  | Model    | l validation                                                          | 43 |

|          |      | 2.5.1    | Temperature scaling                                                   | 44 |

|          |      | 2.5.2    | Geometry Scalable Model                                               | 49 |

|                                          |                                                                |                               | Geometry scalable weak avalanche model                                        | 49  |  |  |

|------------------------------------------|----------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------|-----|--|--|

|                                          |                                                                |                               | Geometry scalable impact ionization parameters extraction                     | 51  |  |  |

|                                          |                                                                |                               | Geometry scalable impact ionization simulation results $\ldots \ldots \ldots$ | 51  |  |  |

|                                          | 2.6                                                            | Conclu                        | usion                                                                         | 56  |  |  |

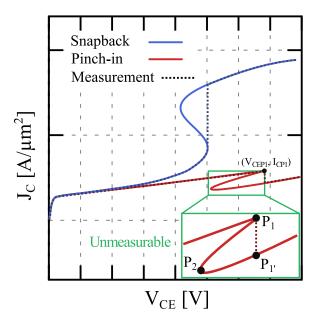

| 3                                        | Ope                                                            | erating                       | ; limitations at high current and high electric field                         | 57  |  |  |

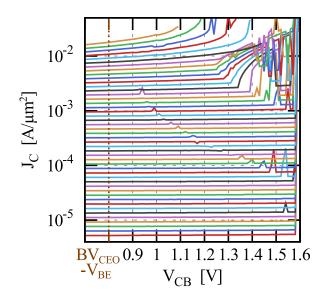

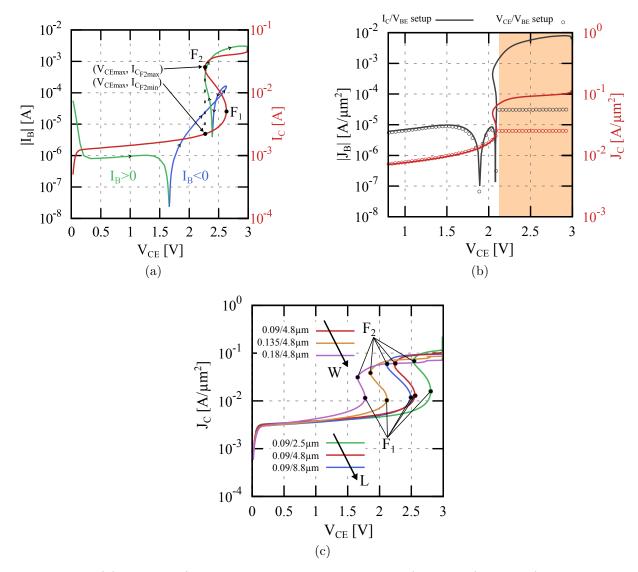

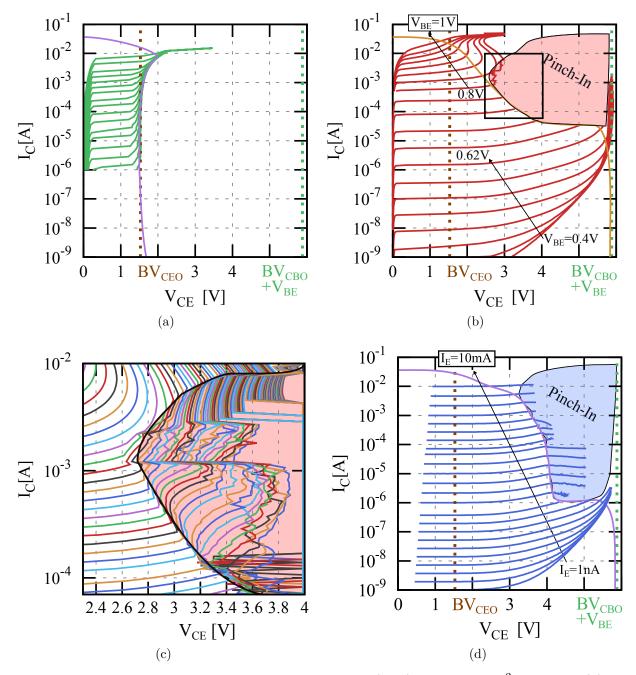

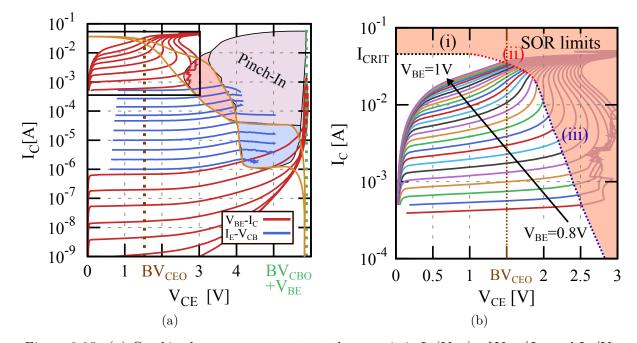

|                                          | 3.1                                                            | Snapb                         | ack behavior                                                                  | 61  |  |  |

|                                          |                                                                | 3.1.1                         | Snapback measurement setup                                                    | 61  |  |  |

|                                          |                                                                | 3.1.2                         | Snapback measurement results                                                  | 62  |  |  |

|                                          |                                                                | 3.1.3                         | Flyback locus determination                                                   | 64  |  |  |

|                                          |                                                                | 3.1.4                         | Model accuracy                                                                | 68  |  |  |

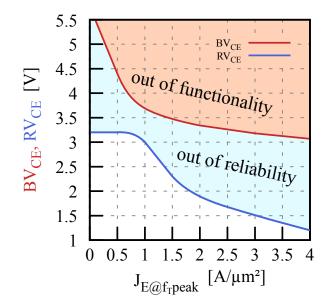

|                                          | 3.2                                                            | $BV_{CE}$                     | R · · · · · · · · · · · · · · · · · · ·                                       | 69  |  |  |

|                                          | 3.3                                                            | Pinch-                        | in mechanism                                                                  | 71  |  |  |

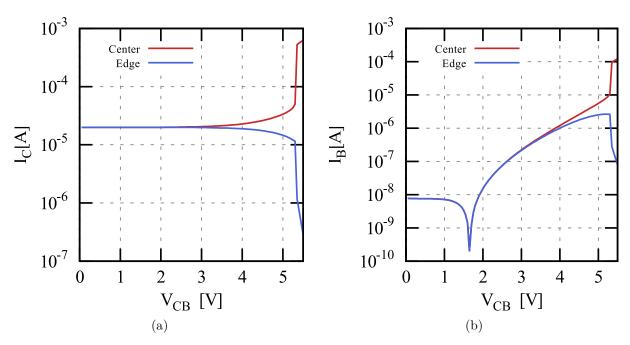

|                                          |                                                                | 3.3.1                         | Pinch-in signature                                                            | 72  |  |  |

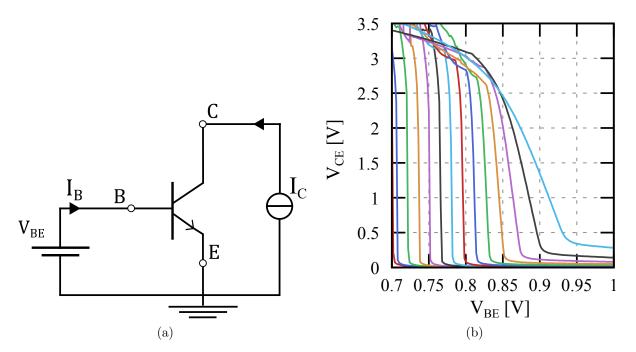

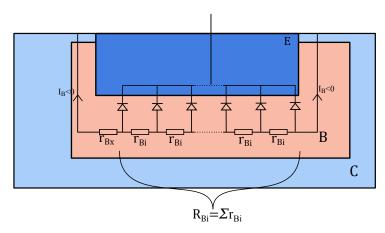

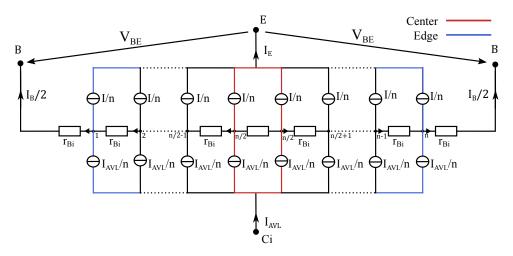

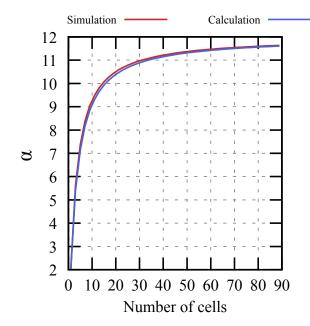

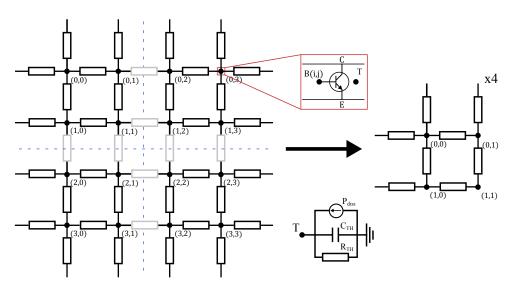

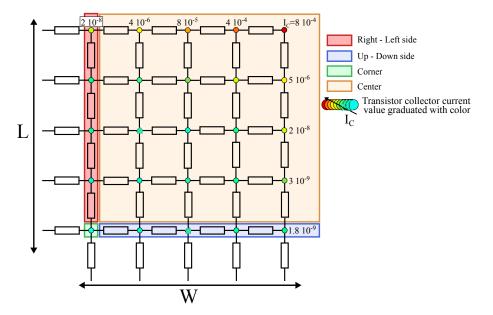

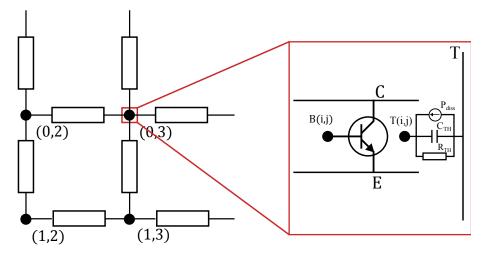

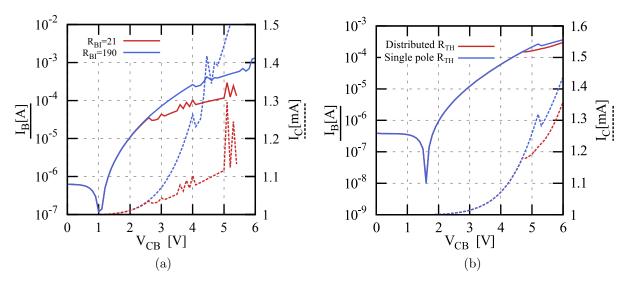

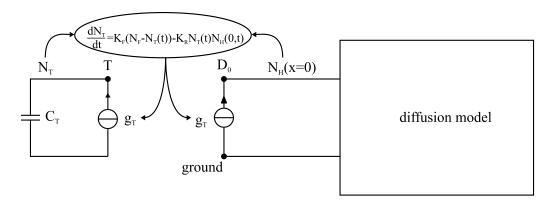

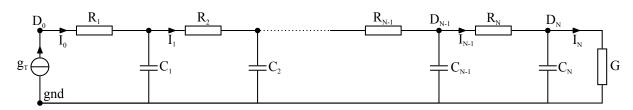

|                                          |                                                                | 3.3.2                         | Base distributed model                                                        | 74  |  |  |

|                                          |                                                                | 3.3.3                         | HICUM/L4 results                                                              | 78  |  |  |

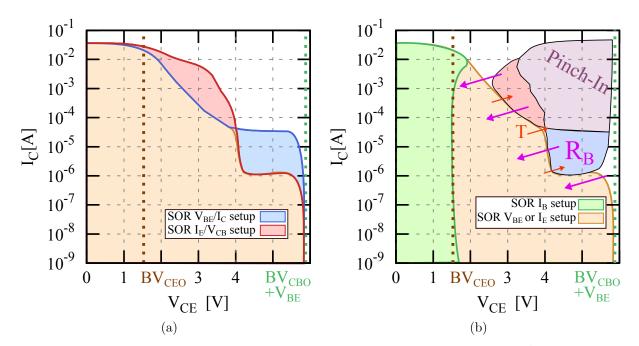

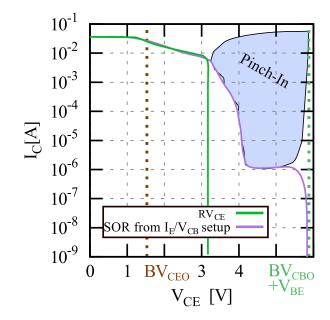

|                                          | 3.4                                                            | Stable                        | Poperation Regime                                                             | 81  |  |  |

|                                          | 3.5                                                            | Conclu                        | usion                                                                         | 88  |  |  |

| 4                                        | Failure mechanisms occurring in SiGe HBTs and compact model of |                               |                                                                               |     |  |  |

|                                          | $\operatorname{hot}$                                           | carrie                        | r degradation                                                                 | 91  |  |  |

|                                          | 4.1                                                            |                               |                                                                               | 93  |  |  |

| 4.2 Origin of the degradation mechanisms |                                                                | of the degradation mechanisms | 95                                                                            |     |  |  |

|                                          |                                                                | 4.2.1                         | Impact on DC characteristics                                                  | 95  |  |  |

|                                          |                                                                | 4.2.2                         | Impact on AC characteristics                                                  | 98  |  |  |

|                                          |                                                                | 4.2.3                         | Model parameter associated with the degradation mechanism $\ldots$            | 100 |  |  |

|                                          | 4.3                                                            | Physic                        | cal explanation                                                               | 103 |  |  |

|                                          |                                                                | 4.3.1                         | Degradation location                                                          | 103 |  |  |

|                                          |                                                                | 4.3.2                         | Impact-ionization and self-heating interactions                               | 107 |  |  |

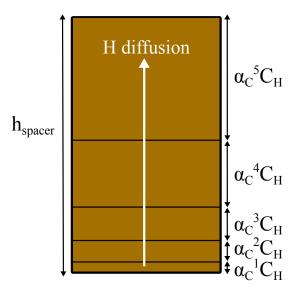

|                                          |                                                                | 4.3.3                         | Spacer morphology consideration                                               | 110 |  |  |

|                                          | 4.4                                                            | Hot C                         | arrier Degradation compact model                                              | 112 |  |  |

|                                          |                                                                | 4.4.1                         | Reaction-Diffusion model                                                      | 113 |  |  |

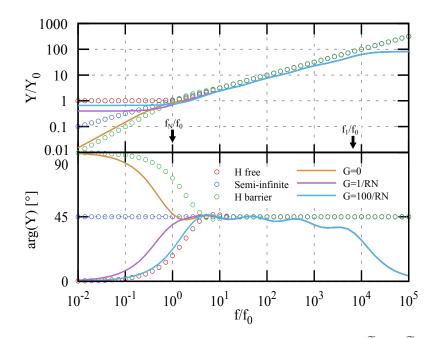

|                                          |                                                                | 4.4.2                         | Compact model implementation                                                  | 115 |  |  |

|    | 4.5 Parameter extraction |         |                                    | . 121 |

|----|--------------------------|---------|------------------------------------|-------|

|    |                          | 4.5.1   | Interface trap creation parameters | . 121 |

|    |                          | 4.5.2   | Recovery parameters                | . 122 |

|    |                          | 4.5.3   | Hydrogen diffusion parameters      | . 122 |

|    | 4.6                      | Simula  | ation results                      | . 123 |

|    |                          | 4.6.1   | Transistor level                   | . 123 |

|    |                          | 4.6.2   | Circuit level                      | . 125 |

|    | 4.7                      | Conclu  | usion                              | . 128 |

| 5  | Gen                      | eral co | onclusion and outlook              | 131   |

| Α  | $\operatorname{List}$    | of Pu   | blished work                       | 135   |

| В  | Agiı                     | ng mo   | del VerilogA implementation        | 137   |

| Re | eferei                   | nces    |                                    | 140   |

## Nomenclature

- $\alpha$  [ $cm^{-1}$ ] Ionization rate

- $\rho(x) \quad [C.cm^{-3}]$ , Charge density as a function of the depth

- $\varepsilon_S i \qquad [F.m^{-1}], \text{ Silicon permittivity}$

- $a \qquad [cm^{-1}], \text{ coefficient}$

- $A_E \qquad [m^2]$ , Emitter Area

- $A_{AVL}$  [m<sup>2</sup>], Avalanche effective emitter area

- $A_{E*}$  [m<sup>2</sup>], Effective emitter area

- $AL_{FAV}$  [T<sup>-1</sup>],  $f_{AVL}$  thermal coefficient

- $AL_{KAV}$   $[T^{-1}], k_{AVL}$  thermal coefficient

- $AL_{QAV}$   $[T^{-1}], q_{AVL}$  thermal coefficient

- $b \qquad [V.cm^{-1}]$ , Silicon critical field

- BV [V], Miller equation breakdown parameter

- $BV_{CBO}$  [V], Open emitter breakdown voltage

- $BV_{CEO}$  [V], Open base breakdown voltage

- $BV_{CES}$  [V], Breakdown voltage shorting the base and the emitter

- $BV_{CES}$  [V], Breakdown voltage using a resistance at the base terminal

- $BV_{CE}$  [V], Breakdown safe operating area

- $C_{jCi}$  [F], Internal base-collector capacitance

- $E_{jC}$  [V.m<sup>-1</sup>], Electric field value at the BC junction

- $E_{LIM}$  [V.m<sup>-1</sup>], Zero slope electrical field

- $F_1$  First snapback locus

- $F_2$  Second snapback locus

- $f_T \qquad [GHz], \text{ Transit Frequency}$

- $f_{AVL}$  [V<sup>-1</sup>], HICUM weak avalanche parameter

- $f_{cor}$  Corrective factor for the avalanche decrease at high current

- $f_{max}$  [GHz], Maximum oscillation Frequency

- $h_{CAVL}$  Factor for current dependent avalanche effect

$h_{VDAVL}\ I_{LIM}$  dependence for spatially varying collector doping

| $I_B$ $[A]$ | Base | $\operatorname{current}$ |

|-------------|------|--------------------------|

|-------------|------|--------------------------|

- $I_C$  Collector current

- $I_E$  [A], Emitter current

- $I_T$  [A], Transfer current

- $I_{B0}$  [A], Base current at  $V_{CB}=0$ V

- $I_{C0}$  [A], Collector current at  $V_{CB}=0$ V

- $I_{LIM}$  [A], Limited current

- $J_{AVLa}$  [A.m<sup>-1</sup>], Area avalanche current density

- $J_{AVLp}$  [A.m<sup>-1</sup>], Perimeter avalanche current density

- $k_{AVL}$  HICUM strong avalanche parameter

- $L_E$  [m], Emitter length

- M Multiplication factor

- N(x) [cm<sup>-3</sup>], Collector doping profile value

- $N_D$  [ $cm^{-3}$ ], Collector doping

- $n_{AVL}$  Miller equation parameter

- $q_{AVL}$  [C], HICUM weak avalanche parameter

- $R_{Bi}$  [ $\Omega$ ], Intrinsic base resistance

- $R_{Bx}$  [ $\Omega$ ], Extrinsic base resistance

- $R_B$  [ $\Omega$ ], Base resistance

- $R_{Ci0}$  [ $\Omega$ ], Internal collector resistance at low electric field

- $R_{CX}$  [ $\Omega$ ], Collector resistance

- $R_E$  [ $\Omega$ ], Emitter resistance

- $RV_{CE}$  [V], Reliability safe operating area

- $V_{BEi}$  [V], Internal EB voltage

- $V_{BE}$  [V], Base-Emitter Voltage

- $V_{CBi}$  [V], Internal CB voltage

- $V_{CB}$  [V], Base-Collector Voltage

- $V_{DCi}$  [V], Internal BC junction built-in voltage

- $V_{LIM}$  [V], Voltage separating ohmic and saturation velocity regime

- $v_{sat}$  [m.s<sup>-1</sup>], Saturation velocity

- $W_E$  [m], Emitter width

- $w_i$  [m], Injection width

- $w_{BC}$  [m], BC SCR width

- $w_{epi}$  [m], Collector width

- $x \qquad [m], \text{ Depth}$

- 2D Two-dimensional

- 3D Three-dimensional

- BC Base-Collector

- BiCMOS Bipolar CMOS

- BV Breakdown Voltage

- CMOS Complementary Metal Oxide Semiconductor

- EB Emitter-Base

- EDA Electronic design automation

- FoM Figure of Merits

- HBT Hetero-junction Bipolar Transistor

- HCD Hot Carrier Degradation

- HI High-Injection

- HICUM High Current Model

- HS High Speed

- HV High voltage

- II Impact Ionization

- III-V Material compound of elements from the III and V column of the periodic table

- LFN Low Frequency Noise

- MEXTRAM Most EXquisite TRAnsistor Model

- MTTF Mean Time To Failure

- MV Medium voltage

- PA Power Amplifier

- PDK Process Design Kit

- $\ensuremath{\mathsf{R\&D}}$  Research and development

- RD Reaction Diffusion

- RF Radio-Frequency

- SCR Space Charge Region

- SGP Spice-Gummel-Poon

- SH Self-Heating

- SiGe Silicon-Germanium

- SOA Safe Operating Area

- SOLT Short-Open-Load-Thru

- SOR Stable Operation Regime

- SRH Shockley Read Hall

- STI Shallow Trench Isolation

- TCAD Technology Computer-aided Design

- TEM Transmission Electron Microscopy

- THz Terahertz

- VBIC The Vertical Bipolar Inter-Company

- VCO Voltage Controlled Oscillator

## CHAPTER 1

### Introduction

### 1.1 Motivation

Over the past decades, the progressive interest for millimeter and sub-millimeter waves in advanced applications such as in the biology field [1, 2] and RF (Radio-Frequency) communications has been driven by the microelectronic integrated circuit modernization [2, 3]. Circuits have already showed applications close to the terahertz (THz) range (0.3 - 3THz) [4, 5, 6, 7]. They mainly rely on the RF performance improvements and through a technology diversification such as RF-CMOS (RF Complementary Metal Oxide Semiconductor), III-V (transistor based on elements from the III and V column of the periodic table), or BiCMOS (Bipolar CMOS) devices (More than Moore)[5, 8].

Recently, important research and development (R&D) resources have been focused on the high frequency CMOS performance improvements in order to substitute the BiCMOS technology in certain RF applications [9]. However, in the near future, BiCMOS technology will still be adopted thanks to its great integration capability, its considerable RF performance [6, 9, 10, 11, 12, 13] and more importantly, the low variation of the fabrication process (as for MOS technology) compared to III-V technology resulting in higher manufacturing costs and integration complexity.

Figure 1.1: TEM picture of a 55nm BiCMOS technology [18]

To address high frequency performance, Silicon-Germanium (SiGe) Hetero-junction Bipolar Transistor (HBT) BiCMOS technology has been chosen for many years for applications operating close to the THz range. In particular, applications in terahertz imaging (for healthcare and biology), very high speed communications (4G, 5G ...), radars and industrial automation (sensors) are now possible using SiGe HBTs. [5, 7, 14, 15, 16, 17]. Those transistors have recently reached high RF performance such as STMicroelectronics BiCMOS 55nm technology [18] ( $f_T = 320GHz$  and  $f_{max} = 370GHz$ ) and IHP HBTs [10, 19, 20]  $(f_T = 505GHz \text{ and } f_{max} = 720GHz)$ . Those performances are still increasing thanks to the down-scaling of the vertical and lateral transistor dimensions. Many European projects were then carried out to improve their high frequency performance (Dot-Five, DotSeven, Taranto...). The Taranto European project (http://tima.univ-grenoblealpes.fr/taranto/) started at the beginning of this Philosophiæ Doctor (PhD) thesis work and targets the development of the next BiCMOS technology towards the THz range. To reach high device performance, useful metrics such as the transit frequency  $f_T$  and the maximum oscillation frequency  $f_{max}$  are monitored and improved. These Figure of Merit (FoM) mainly depend on the transistor doping profile and the size of the device (emitter, base and collector width/depth).

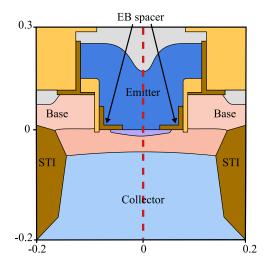

To increase the RF performance, several HBT improvements have been achieved over the past decades. Figure 1.1 shows a Transmission Electron Microscopy (TEM) picture of a BiCMOS 55nm technology [18]. In this figure, it can be noticed some HBT features such as a self-aligned structure, the EB spacers, the Shallow Trench Isolation (STI), the selective SiGe (Silicon-Germanium) epitaxy in the base or the Deep Trench (not shown). These technology features greatly improved the RF performance and the integration of the devices. To further increase the RF performance of such transistors, the base and the collector width/depth need to be shrunk down and the doping profiles have to be further increased [21]. Lately, the HBTs R&D improvements have slowed down as the device developments are getting much more complex to achieve.

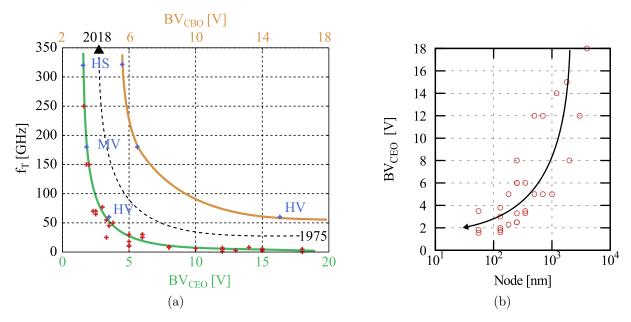

In order to address different circuit applications with a single technology platform, different transistor flavors are usually available, which are shown in Figure 1.2a (with blue crosses). Three different type of devices of the STMicroelectronics advanced 55nm node BiCMOS technology [18] were investigated in this work:

- A high speed (HS) NPN HBTs ( $f_T = 320GHz$ ,  $BV_{CEO} = 1.5V$ ,  $BV_{CBO} = 5.5V$ ),

- A medium voltage (MV) NPN HBTs ( $f_T = 180GHz$ ,  $BV_{CEO} = 1.9V$ ,  $BV_{CBO} = 7.3V$ ),

- A high voltage (HV) NPN HBTs ( $f_T = 70GHz$ ,  $BV_{CEO} = 3.2V$ ,  $BV_{CBO} = 14.4V$ ).

High-speed (HS) transistors are dedicated to high-frequency applications, high-voltage (HV) transistors are tailored toward high-power applications, and medium voltage (MV) transistors are designed for trade-offs between power and RF applications. The main difference between the HV and the HS transistor architecture is that the HV has a low-doped collector (epi-layer) at the BC junction. Due to its low doping, this transistor is very sensitive to high-current effects.

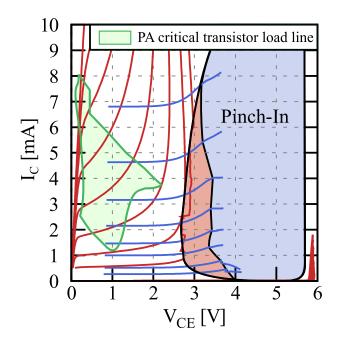

The bipolar technology improvements have led to a side effect. Indeed, boosting the HBT frequency performance has led to increased impact ionization (II) mechanisms due to higher doping profile and reduced collector width. Depending on the transistor configuration, different breakdown voltages (BV) can be observed. In an open base case (rarely used in designs), transistor can be biased up to the first breakdown voltage ( $BV_{CEO}$ ). On the contrary, in an open emitter configuration, the transistor operation is limited to the second breakdown voltage,  $BV_{CBO}$ . Those BV are expected to be further reduced in the close future [9, 13]. as presented in Figure 1.2a and 1.2b. For the past few decades, the

Figure 1.2: (a) Performance of STMicroelectronics and Thomson Semiconductor bipolar technologies along the time. In blue are represented the STMicroelectronics advanced 55nm node BICMOS device performance for the three devices high speed, medium voltage and high voltage. (b) Breakdown voltage  $BV_{CEO}$  as a function of the technology node for different STMicroelectronics bipolar technologies.

open base common emitter and open emitter breakdown voltages,  $BV_{CEO}$  and  $BV_{CBO}$ respectively have drastically been narrowed, shifting from 17V to 1.5V for the  $BV_{CEO}$ while in the same time the transit frequency has been multiplied by around 300. The  $BV_{CEO}$  and  $BV_{CBO}$  value for the technology of interest for high speed devices have been lowered to 1.5V and 5V, respectively.

Thus, the circuit operating at higher frequencies forces devices to work closer to their physical limits in order to compensate for the loss of output power. Power applications require a collector-base voltage range as large as possible, leading to operating point biases beyond  $BV_{CEO}$  and close to the edges of the transistor operating regime [22, 23].

This has led to further activation mechanisms such as the impact ionization (II) and the high injection (HI) effects. Moreover, the Self-Heating (SH) increase due to the size reduction has drastically modified the transistor output characteristics. A large work about the improvement of the thermal response has been achieved and published in [24, 25, 26, 27]. It has also allowed to model the thermal behavior in a 2D structure with an accurate extraction procedure.

Additionally, the gradual increase of the operating points closer to the breakdown

voltages has led to further activation failure wear-out mechanisms. The bipolar transistor reliability is currently an important topic. Degradation mechanisms are usually triggered through a high electric field, a high current density, a high temperature or a long stress time [28].

The regime at which the transistor is biased without main degradation concerns is named the Safe Operating Area (SOA) [29, 30, 31]. This regime is usually extracted from aging tests where wear-out mechanisms occur and change the transistor electrical behavior. Typically, a decrease of the current gain [28] and a shift of the Low Frequency Noise (LFN) [32, 33] are observed. Circuit design can be impacted by this wear-out mechanisms causing undesirable effects from a system point of view.

Thus, it is required to develop an accurate description of the transistor behavior in all operation regimes. More particularly an understanding of the safe operating area limits is required. Such a description can be efficiently performed using compact models.

To target circuit designs, compact models are used to describe the transistor electrical operations. These models give a good trade-off between simulation accuracy and computational time. Most of the effects occurring inside transistors are taken into account through physical equations. These equations often use several simplifications in order to get relatively simple and accurate solutions. The transistor voltages and currents are then assessed from an equivalent circuit (using capacitance, diodes, resistances and current sources) describing the electrical behavior. The description of such models is initially developed in a programming language called VerilogA.

In order to provide such solutions to circuit designers, compact models are embedded inside a Process Design Kit (PDK) allowing to describe the electrical behavior within the designer environment no matter what the configuration of the transistor is (biases, geometry, temperature...). To accurately reproduce its electrical behavior, the PDK relies on different aspects:

Compact models rely on a list of parameters describing the transistor electrical behavior. These parameters need to be extracted accurately. For example, the thermal resistance extraction procedure has recently been improved to account for the thermal distribution along the depth and with multiple emitter fingers [34, 35, 36, 37, 38, 39]. Moreover, with the increase of the RF performance, measurements

| Model              | Advantages                                                                                                                        | Limitations                                                                                                                                   |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| SGP                | Relatively simple model, fast<br>simulation run-time and rapid<br>parameters extraction.                                          | Empirical model for different<br>aspect such as the transit time.<br>No avalanche current source nor<br>thermal node. No parasitic PNP.       |

| ST-BJT             | SGP model with an avalanche<br>current source, high injection<br>effects and the thermal modeling<br>of the series resistances.   | Empirical model of the transit<br>time based on SGP.                                                                                          |

| HICUM/L0<br>and L2 | Physical description of the transit<br>time, modeling of hetero-junction<br>transistors, high injection effects.<br>BC breakdown. | Important number of parameter to<br>extract. Simulation time more<br>important than for previous<br>models (can be reduced with<br>HICUM/L0). |

| MEXTRAM            | Accurate model taking into<br>account the same effects as<br>HICUM.                                                               | Parameter extraction hard to realize on electrical characteristics.                                                                           |

| VBIC               | Model similar to HICUM and<br>MEXTRAM (improving SGP with<br>the modeling of the high injection<br>effects in the collector).     | Transit time modeling empirical<br>based on SGP.                                                                                              |

Table 1.1: Bipolar transistor model advantages and limitations summary

at high frequency became a big challenge for future applications. For now, most of industrial measurements are made at up to 70GHz, far from the transistor maximum operation frequency [17].

• To describe the entire picture of the transistor electrical behavior, compact models require to account for the different mechanisms occurring. However, compact models need to be improved due to the intensified mechanisms such as impact ionization, high injection effects or self-heating caused by the size reduction.

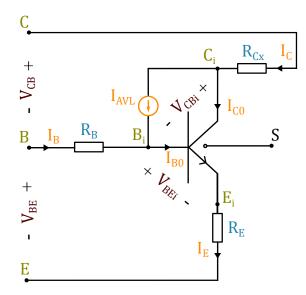

Different bipolar transistor compact models have been developed over the years to describe the transistor behavior as presented in Table 1.1. Ebers-Moll is the first bipolar model allowing a description of the DC electrical behavior of bipolar transistors [40]. Spice Gummel-Poon (SGP) model, increased the accuracy of the model introducing a charge control model [41, 42]. Due to high voltage concerns, STMicroelectronics introduced an improvement of the SGP model accounting for the avalanche current, the thermal effects and the base push-out effect (named ST-BJT model). Also the MEXTRAM model [43]

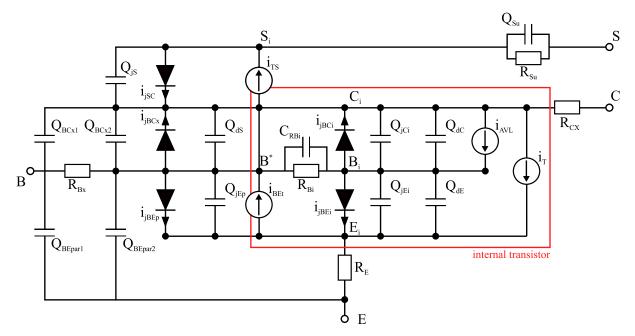

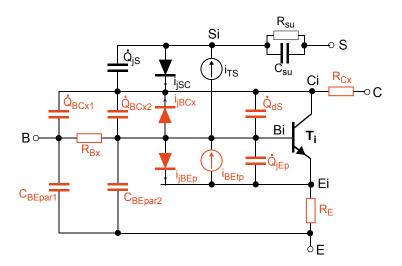

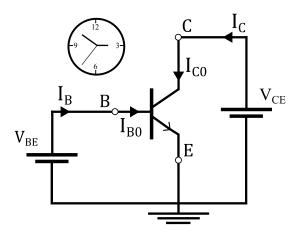

Figure 1.3: HICUM equivalent circuit showing the internal transistor nodes.

has been developed in the 1990 by Philips (NXP) to model accurately the transistor behavior for fast analog circuits. The VBIC model [44] was developed by Motorola in 1995 and accounts for the HI effects in the collector. The HICUM model [45, 46] have been introduced in 1985. It allows a precise description of the transit time and accounts for the avalanche current, for the HI effects, for the hetero-junctions (SiGe) and for the variation of the early voltages depending with the bias. The equivalent circuit is represented in Figure 1.3. This model is still being improved by the University of Dresden.

In this work, the study is focused on the most commonly used bipolar model, HICUM. More precisely, the HICUM level 2 has been used, thanks to its more complex equations that increases the accuracy of the model in comparison with the level 0. This work has been initiated with the HICUM/L2 v2.3.4 (latest version at the beginning of the study).

In summary, due to the circuit requirements, bipolar transistor now operates in a region where aggravated impact ionization and self-heating occur. In these operation regime, compact models reached their accuracy limitation (due to several simplifications) and a further modeling of the mechanisms occurring inside this regime is required.

### **1.2** Thesis content

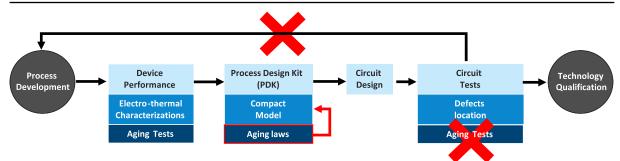

From this short overview, the main concerns regarding the RF performance improvements can be evaluated. This PhD thesis has been focused around recent improvements of the bipolar modeling to predict the transistor degradation mechanisms. We bring multiple solutions to improve the accuracy of the model close to the transistor operating limits. From the designer point of view, the model need to be improved to match circuit requirement and the failure mechanisms need to be accurately simulated regardless of the bias conditions. From the modeling and characterization point of view, a non-destructive method has to be investigated to look at the electrical behavior close to HBT electrical limitations.

At the beginning of this work, compact models were improved at very high current densities and voltages. To develop new models, various tools and research activities were combined: TCAD simulation, compact modeling and electrical characterization. The contribution of this PhD thesis was to develop an accurate compact model (implemented inside HICUM) of the impact ionization mechanism at high voltages and current densities. This will be developed in the second chapter.

Moreover, it has been required to deeply investigate the boundary mechanisms that limits the voltages/currents operating range. The third chapter will then focus on the high current and voltage characterization and the definition of an operating range where the transistor electrical behavior is stable. The main achievements described in this chapter are related to the improvement of the characterization techniques close to the destruction of the transistor and the definition of a stable operation regime for designer purposes.

Finally, an aging model need to be developed to account for the wear-out mechanisms. The last chapter will describe a way of modeling the degradation mechanisms occurring inside SiGe HBTs. The main work described in this chapter is related to accurately predict the degradation of the transistor regardless of its operating biases. From that model a Safe Operating Area (SOA) definition will also be carried out.

## CHAPTER 2

# Physics and modeling of impact ionization in HBTs

Compact models were developed for biases close to the first breakdown voltage,  $BV_{CEO}$ . Therefore, as the usable bias range has been extended up to the second breakdown voltage  $BV_{CBO}$ , some inaccuracies are observed at relatively high currents and voltages at the time of this work. The current implemented HICUM model accounted only for the avalanche mechanism for voltages close to the open base breakdown voltage  $BV_{CEO}$  (weak avalanche region) [47]. Moreover, it did not account for the avalanche dependence with the collector current .

Therefore, in this chapter, the strong avalanche and the avalanche dependence with the current will be investigated and an accurate model will be derived. Also, an impact ionization geometry scaling extraction will be presented with the corresponding parameter extraction procedure.

#### 2.1 Impact Ionization Mechanism

The bipolar transistor breakdown is due to the avalanche mechanism occurring inside PN junctions strongly biased in reverse mode. The avalanche mechanism and so the

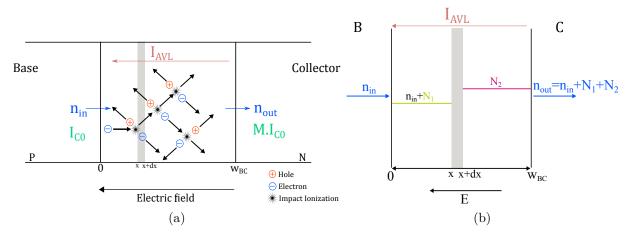

Figure 2.1: (a) Schematic view of the impact ionization phenomena inside the Base-Collector Space Charge Region highlighting the creation of electron-hole pairs - (b) Sketched BC junction showing the number of electrons created at the BC-SCR output  $(n_{out})$  depending on the input number of electrons  $(n_{in})$  and the number of electrons/holes created inside the BC-SCR  $(N_1$  and  $N_2$  resp.).

breakdown voltages cause major achievable output power limitations. The avalanche mechanism is triggered by the impact ionization taking place within the Base-Collector Space Charge Region (BC-SCR). At high electric field in the BC-SCR (high collector-base voltage), electrons can acquire sufficient kinetic energy to generate electron-hole pairs by collision with atoms within the depletion region. A schematic view of the avalanche in the BC-SCR is shown in Figure 2.1a. Those additional carriers contribute to a current named the avalanche current  $I_{AVL}$  and are quantified by the multiplication factor M, defined [48, 49] as the ratio of the number of carriers leaving the BC-SCR at the collector end  $(n_{out})$  divided by the number of carriers entering the BC-SCR at the base end  $(n_{in})$

$$M = \frac{n_{out}}{n_{in}} \tag{2.1}$$

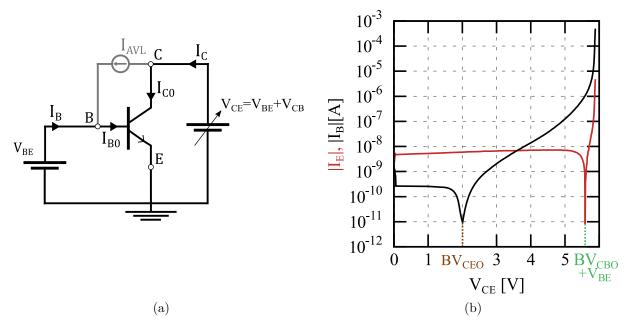

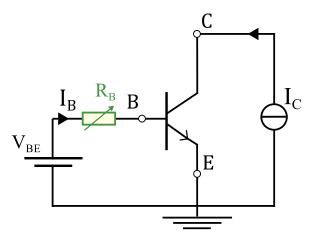

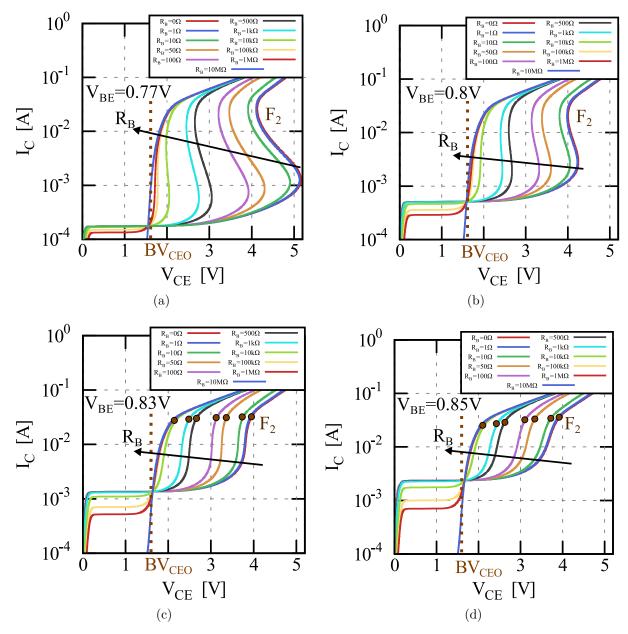

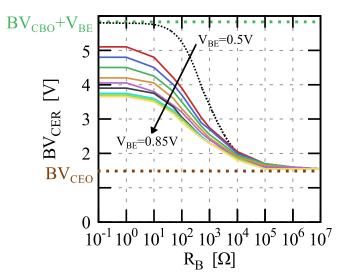

Subsequently, in the open base configuration, every hole generated by impact ionization will be re-injected inside the base, contributing to the transistor effect, limiting the voltage biases up to the open-base breakdown voltage  $BV_{CEO}$ . On the contrary, if the base isn't opened, holes can flow out of the base, and induce a negative base current beyond the  $BV_{CEO}$ . Further increase of the electric field increases the amount of ionization up to the point where every single carrier creates a new one within the BC-SCR. The  $BV_{CBO}$ is defined when the multiplication factor tends to infinity, or when  $I_E = 0$  (open-emitter case), meaning  $-I_B$  reaches  $I_C$  as shown in Figure 2.2b. This particular breakdown voltage is hardly measurable because it assumes an infinite avalanche current  $(M \to \infty)$ . Moreover, adding a resistance at the base terminal induces a premature breakdown  $BV_{CER}$ due to the voltage drop in the resistance. Its value is lower than  $BV_{CBO}$  since the higher this resistance value is, the closer the  $BV_{CER}$  is from the  $BV_{CEO}$ . Another breakdown voltage is also usually defined: the  $BV_{CES}$  which is established while shorting the base and the emitter ( $V_{BE} = 0V$ ). Contrary to the  $BV_{CBO}$ , this particular voltage, accounts for the parasitic resistance across the base and the emitter, leading to  $BV_{CES} < BV_{CBO}$ .

These different breakdown voltage definitions are generated by the impact ionization mechanism. A precise description of these BV will be presented in the next chapter.

Preliminary, to predict these breakdown voltages, an accurate description and modeling of the impact ionization is proposed hereafter.

#### 2.2 Weak and Strong Avalanche Model Description

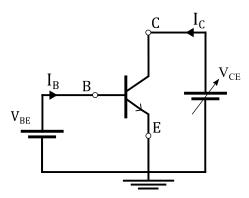

As the impact ionization mechanism occurs at the base-collector junction, in a compact model, a simple current source is added between the base and the collector to represent the generated avalanche current as represented in Figure 2.2a.

Many avalanche multiplication factor equations have been presented over the years to model this mechanism [42, 50, 51, 52, 53]. The simple Miller avalanche model [50, 54] was proposed in 1955. It is a consistent expression for older technological nodes where the impact ionization mechanism was not too much present due to their low doping values which is not the case in modern SiGe transistors.

The multiplication factor has been expressed as:

$$M = \frac{1}{1 - \left(\frac{V_{CBi}}{BV}\right)^{n_{AVL}}} \tag{2.2}$$

Here,  $V_{CBi}$  represents the internal base-collector voltage,  $n_{AVL}$  is a fitting parameter (close to 5) and BV is the breakdown voltage  $BV_{CBO}$ . Semi-empirical expressions such as in [55, 56, 57, 58, 59], presented an advanced way to model the impact ionization and its consequences (such as the pinch-in effect explained in Chapter 3).

Figure 2.2: (a) Transistor's equivalent circuit with an avalanche current source between the base and the collector. (b) Measured output characteristic showing the two breakdown voltages  $BV_{CEO}$  and  $BV_{CBO}$  as a function of  $V_{CE}$  for  $V_{BE} = 0.5V$ .

To calculate the multiplication factor, compact models are designed by solving the ionization integral (the number of electron generated by impact ionization) through different calculations such as in VBIC [44, 60], MEXTRAM [43, 61] and HICUM [62][63].

In the following section, the entire ionization integral calculation and the relation to the multiplication factor will be made explicit.

In order to compute the avalanche current induced by the impact ionization mechanism, the number of electrons created within the BC-SCR have to be determined. Figure 2.1b shows the number of electrons created between the base and the collector. Considering a one dimension transistor and defining n as the free electron density, the number of electron dn created inside a small region dx of the BC-SCR is calculated. As shown in Figure 2.1b, dn depends on the number of electrons  $N_1$  and the number of holes  $N_2$ created by impact ionization between 0 and x (respectively between  $w_{BC}$  and x + dx for holes) because of the direction of electrons which goes from the base to the collector and on the opposite side for holes. Therefore, the number of electrons created inside this region is calculated as presented in [48, 49],

$$dn = [(n_{in} + N_1) \alpha_n(x) + N_2 \alpha_p(x)] dx$$

(2.3)

where  $\alpha_n$ ,  $\alpha_p$  represent the electron and hole ionization rates respectively. The differential equation solution (2.3), gives a solution which cannot be determined without assuming that the ionization rates are the same for electrons and holes [64, 65]( $\alpha_n = \alpha_p = \alpha$ ). Therefore, equation (2.3) is replaced by

$$dn = (n_{in} + N_1 + N_2) \ \alpha(x) \ dx = n_{out} \ \alpha(x) \ dx$$

(2.4)

The integration of equation (2.4) along the BC-SCR gives

$$\int_{0}^{w_{BC}} dn = n_{out} - n_{in} = n_{out} \int_{0}^{w_{BC}} \alpha(x) \, dx \tag{2.5}$$

Here,  $\alpha$  has been empirically determined by Chynoweth [66] and expressed as a function of the electric field as,

$$\alpha(x) = a \, \exp\left(\frac{-b}{|E(x)|}\right) \tag{2.6}$$

Where a is the avalanche coefficient and b the silicon critical electric field. Typical values of these two parameters are given in [64]  $a = 7.03 \times 10^5 \, cm^{-1}$  and  $b = 1.23 \times 10^6 \, V.cm^{-1}$  for an electric field inside the range  $[1.75 \, 10^5 : 6.0 \, 10^5 \, V.cm^{-1}]$  which is the case for recent SiGe HBTs. Thus, from equations 2.1, (2.5) and (2.6), the multiplication rate is determined from the input and output number of electrons as

$$\frac{n_{out} - n_{in}}{n_{out}} = 1 - \frac{1}{M} = \int_0^{w_{BC}} a \, \exp\left(\frac{-b}{|E(x)|}\right) \, dx \tag{2.7}$$

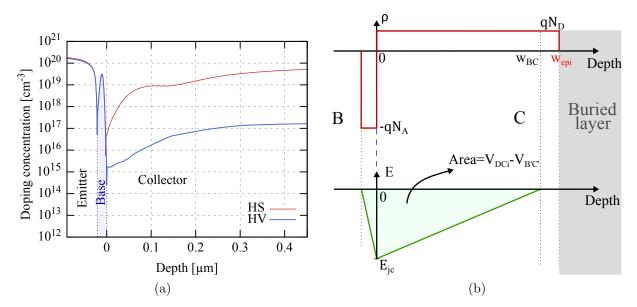

In equation (2.7), the electric field value is required. For that, several assumptions have to be made. Firstly, it is assumed that the doping profile of the transistor is represented by collector and base abrupt junctions as shown in Figure 2.3b. This figure shows the theoretical electric field and the charge distribution between the base and the collector as a function of the depth. The real doping profile for two different devices shown in Figure 2.3a validates the previous assumption (considering a constant collector doping profile). Therefore, at low current density, the ionized carrier density is defined by N(x) = $N_D$ . This assumption (N(x) constant) is more likely to be the case for HV than for HS transistors. Secondly, as shown in Figure 2.3b, it is assumed that the contribution of the electric field within the base is neglected in the calculation of the ionization integral. Therefore, the electric field is defined by the Poisson equation as

$$\frac{dE}{dx} = -\frac{\rho(x)}{\varepsilon_{Si}} = \frac{q}{\varepsilon_{Si}} N_D \tag{2.8}$$

Figure 2.3: (a) Net doping profile for two different bipolar transistors: HS and HV from STMicroelectronics 55nm technology [18] - (b) Base-Collector doping and electric field theoretical profiles. Is also presented the width of the buried-layer ( $w_{epi}$ ) and of the BC-SCR depth ( $w_{BC}$ ).

where  $\rho(x)$  is the charge density in the BC-SCR and  $\varepsilon_{Si}$  represents the silicon permittivity. Thus, integrating equation (2.8) along the BC-SCR and assuming that the electric field is equal to zero at the buried layer as represented in Figure 2.3b ( $E(w_{BC}) = 0$  and  $E(0) = E_{iC}$ ) for low current density, then,

$$E(x) - E_{jC} = \frac{qN_D}{\varepsilon_{Si}}x \qquad with \quad E_{jC} = E(0) = -\frac{qN_D}{\varepsilon_{Si}}w_{BC}$$

(2.9)

This equation is valid as long as the electric field equals zero at the end of the BC-SCR  $(x = w_{BC})$ . From the expression of the electric field (2.9), the ionization integral (equation (2.7)) can be calculated. However, there's no direct resolution of  $\int_0^{w_{BC}} \exp\left(-\frac{1}{x}\right) dx$ . A numerical solution can be found from the exponential integral (EI) function, however, such equation is not suitable for a VerilogA implementation (which requires compact and efficient models).

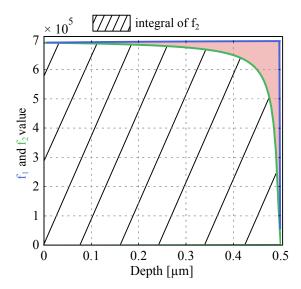

To calculate the ionization integral (2.7), the exponential term and the electric field expression must be simplified. As shown in Figure 2.8 where the TCAD impact ionization rate is plotted as a function of the depth, we observe that impact ionization mainly occurs at the BC junction: significant avalanche takes place only at the vicinity of the maximum

Figure 2.4: Comparison of the exponential expression of  $f_1$  (blue line) and  $f_2$  (green line) as a function of the depth x. To calculate both expressions shown at  $V_{CB} = 2V$ , it is given,  $E_{jC} = -4 \, 10^5 V. cm^{-1}$  and  $w_{BC} = 0.5 \mu m$ .

electric field. Thus, the expression of the electric field is simplified as,

$$\frac{1}{|E(x)|} = \frac{1}{|E_{jC}| \left(1 - \frac{x}{w_{BC}}\right)} \approx \frac{1}{|E_{jC}|} \left(1 + \frac{x}{w_{BC}}\right)$$

(2.10)

The assumption made in (2.10) has to be verified. That is why two expressions are introduced:  $f_1(x) = a \exp\left(\frac{1}{|E_{jC}|\left(1-\frac{x}{w_{BC}}\right)}\right)$  and  $f_2(x) = a \exp\left(\frac{1}{|E_{jC}|}\left(1+\frac{x}{w_{BC}}\right)\right)$  corresponding to the two expressions of  $a \exp\left(\frac{-b}{|E(x)|}\right)$ . Both equations are plotted as a function of the depth x in Figure 2.4. The area in red/pink, represents the difference between  $f_1$ and  $f_2$  integrals. This difference represents a 6.66% shift between the shaded green curve and the blue one. Therefore, it is assumed that both expressions are close as long as xremains close to the BC junction. Typically, for HS transistors, impact ionization occurs in the first  $0.3\mu m$  of the depth of the collector. Then, the ionization integral defined in equation (2.7) is approximated to

$$1 - \frac{1}{M} = \int_0^{w_{BC}} a \, \exp\left(\frac{-b}{|E_{jC}|} \left(1 + \frac{x}{w_{BC}}\right)\right) \, dx \tag{2.11}$$

Thus, an equation of the multiplication factor is found by integrating (2.11),

$$1 - \frac{1}{M} = \frac{a}{b} \left| E_{jC} \right| \ w_{BC} \ \exp\left(\frac{-b}{\left|E_{jC}\right|}\right) \left[1 - \exp\left(\frac{-b}{\left|E_{jC}\right|}\right)\right]$$

(2.12)

Since the critical field b, by definition, is the largest electric field usable in a PN junction (value of around  $1 MV.cm^{-1}$ ), it is much larger than the maximum electric field at the BC junction  $E_{jC}$  (here,  $E_{jC} = -4 \times 10^5 V cm^{-1}$ ). Therefore, we assume that  $\exp\left(\frac{-b}{E_{iC}}\right) \ll 1$ . Equation (2.12) is then rewritten,

$$1 - \frac{1}{M} = \frac{a}{b} |E_{jC}| \ w_{BC} \ \exp\left(\frac{-b}{|E_{jC}|}\right) \ or \ M - 1 = \frac{\frac{a}{b} |E_{jC}| \ w_{BC} \ \exp\left(\frac{-b}{|E_{jC}|}\right)}{1 - \frac{a}{b} |E_{jC}| \ w_{BC} \ \exp\left(\frac{-b}{|E_{jC}|}\right)}$$

(2.13)

In this equation, two physical parameters need to be assessed:  $w_{BC}$  and  $E_{jC}$ . The width of the BC-SCR,  $w_{BC}$ , is determined from the intrinsic BC depletion capacitance  $(C_{jCi})[67]$  and the emitter area  $A_E$  as  $w_{BC} = \frac{\varepsilon_{Si}A_E}{C_{jCi}}$  (for an abrupt junction). The electric field can also be determined from the definition of the internal base-collector voltage as shown in Figure 2.3b. In fact, the electric field is defined from the effective collector voltage  $V_{Ci}$  and from the relationship between an electric field and its corresponding potential as,

$$V_{Ci} = -\int_0^{w_{BC}} E(x) \, dx = V_{DCi} - V_{BCi} \tag{2.14}$$

where  $V_{DCi}$  is the built-in voltage of the internal BC junction. Here a negligible voltage drop in the undepleted portion of the epi-collector is assumed (i.e. very lowcurrent densities or a narrow undepleted region). Indeed, as predicted by TCAD and shown in Figure 2.9d, the electrostatic potential as a function of the depth shows no voltage drop under the undepleted region. Therefore,

$$V_{DCi} - V_{BCi} = -\frac{E_{jC} w_{BC}}{2}$$

(2.15)

Thus, solving (2.15) for  $E_{jC} = -\frac{2 (V_{DCi} - V_{BCi}) C_{jCi}}{\varepsilon_{Si} A_E}$  and the final expression of the multiplication factor can be found

$$M - 1 = \frac{\frac{2 a}{b} \left( V_{DCi} - V_{BCi} \right) \exp\left(\frac{-b \varepsilon_{Si} \frac{A_E}{2}}{C_{jCi}(V_{DCi} - V_{BCi})}\right)}{1 - \frac{2 a}{b} \left( V_{DCi} - V_{BCi} \right) \exp\left(\frac{-b \varepsilon_{Si} \frac{A_E}{2}}{C_{jCi} \left( V_{DCi} - V_{BCi} \right)}\right)}$$

(2.16)

Equation (2.16) might be embedded inside compact models. Hence, from the equation (2.16), the multiplication factor is written as expressed in HICUM [63],

$$M - 1 = \frac{f_{AVL} \left( V_{DCi} - V_{BCi} \right) \exp \left( \frac{-q_{AVL}}{C_{jCi} \left( V_{DCi} - V_{BCi} \right)} \right)}{1 - f_{AVL} \left( V_{DCi} - V_{BCi} \right) \exp \left( \frac{-q_{AVL}}{C_{jCi} \left( V_{DCi} - V_{BCi} \right)} \right)}$$

(2.17)

with  $f_{AVL} = \frac{2 a}{b}$  and  $q_{AVL} = b \varepsilon_{Si} \frac{A_E}{2}$  defined as model parameters. On the following sections, we will only consider the HICUM model.

From equation (2.17) two particular regimes can be observed:

• The weak avalanche regime, defined for voltages close to the  $BV_{CEO}$  in a non-open base transistor configuration. Here,  $BV_{CEO}$  represents the point where the base current start becoming negative. In that regime, the expression of the multiplication factor can be simplified at low  $V_{CB}$ , as M remains close to 1. Thus,

$$1 - \frac{1}{M} = \frac{M - 1}{M} \approx M - 1$$

(2.18)

The multiplication factor expression 2.17 can therefore be simplified,

$$M - 1 = f_{AVL} \left( V_{DCi} - V_{BCi} \right) \exp \left( \frac{-q_{AVL}}{C_{jCi} \left( V_{DCi} - V_{BCi} \right)} \right)$$

(2.19)

• The strong avalanche regime, defined for voltages close to  $BV_{CBO}$ . Amplified impact ionization effects in that regime, limits the accuracy of the previous assumption at high  $V_{CB}$ . The HICUM/L2 version 2.4.0 [68, 69] is based on equation (2.17) but with an additional parameter named  $k_{AVL}$  introduced to take care of the assumptions made in previous calculations:

$$M - 1 = \frac{g}{1 - k_{AVL} g} \quad with \quad g = f_{AVL} (V_{DCi} - V_{B'C'}) \\ \exp\left(\frac{-q_{AVL}}{C_{jCi} (V_{DCi} - V_{B'C'})}\right)$$

(2.20)

This additional parameter can be used for fine tuning or to turn off the strong avalanche model. Setting  $k_{AVL}$  to 0, allows to account only for the weak avalanche regime. Indeed, setting  $k_{AVL}$  to zero in (2.20) gives back equation (2.19). This equation is also the one used in the MEXTRAM model [43, 61] and the VBIC model [60, 44] avalanche current model.

In order to avoid non-physical negative values of the denominator when  $k_{AVL} g > 1$ , a smoothing function is applied:

$$M - 1 = \frac{2g}{1 - k_{AVL}g + \sqrt{(1 - k_{AVL}g)^2 + s_F}}$$

(2.21)

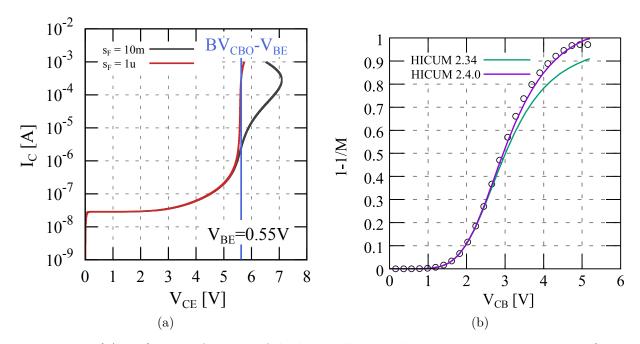

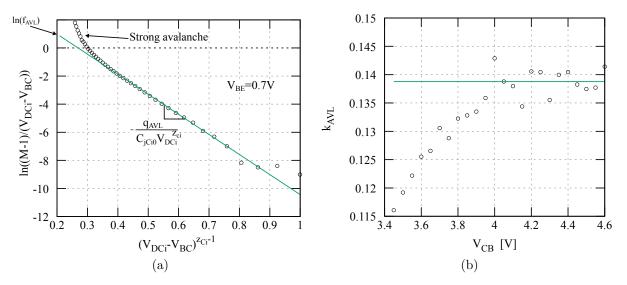

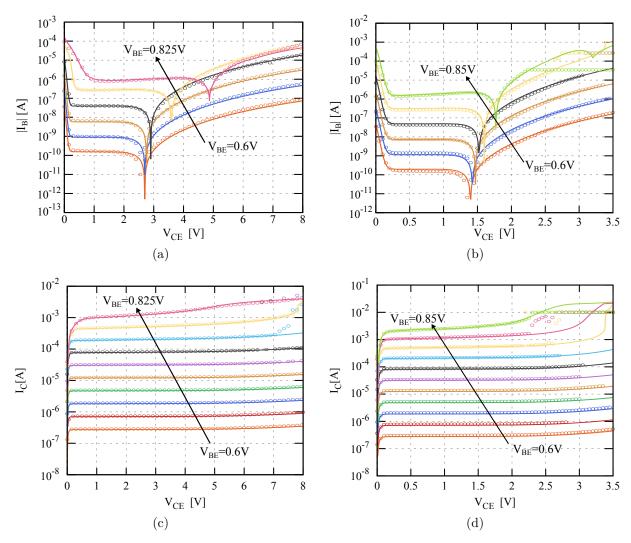

where  $s_F$  is a smoothing factor ( $s_F = 0.001$ ), used in order to avoid infinite values when  $V_{CB}$  reaches voltages close to  $BV_{CBO}$ . As shown in Figure 2.5a, with lower  $s_F$

Figure 2.5: (a) 1-1/M as a function of the base-collector voltage comparing measurement (symbols), and simulations using the multiplication factor equations (2.19) and (2.20). (b) HICUM simulation of the collector current as a function of the emitter-collector voltage for different  $s_F$  values. This graph shows the importance of low  $s_F$  values.

values, the model accuracy is improved, however the run-time calculation increases at the same time (up to 200% increase for very low  $s_F$  values). Moreover, (2.21) tends to expression (2.20) as long as  $k_{AVL}g \ll 1$ .

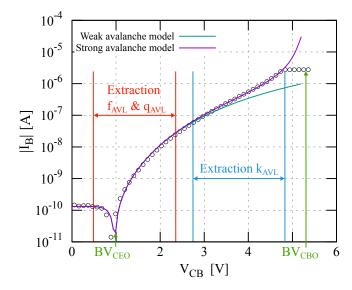

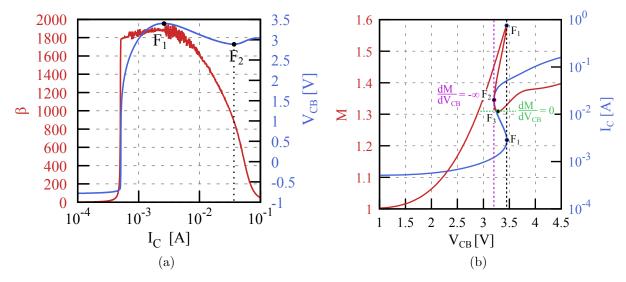

Figure 2.5b shows the multiplication factor as a function of the  $V_{CB}$ . This figure shows the accuracy limitations of both the weak and the strong avalanche model up to very high collector-base voltages. Strong avalanche starts to occur for  $V_{CB} > 3V$ . Equation (2.20) improves greatly the accuracy close to the  $BV_{CBO}$ .

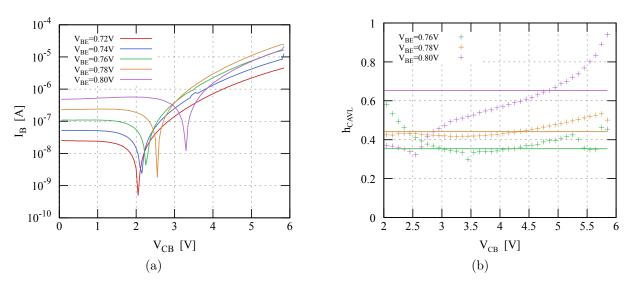

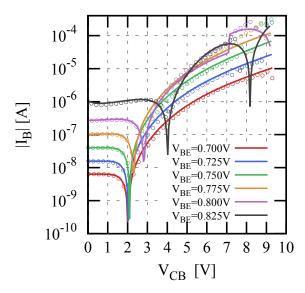

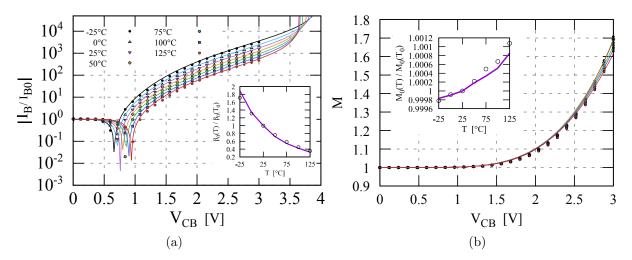

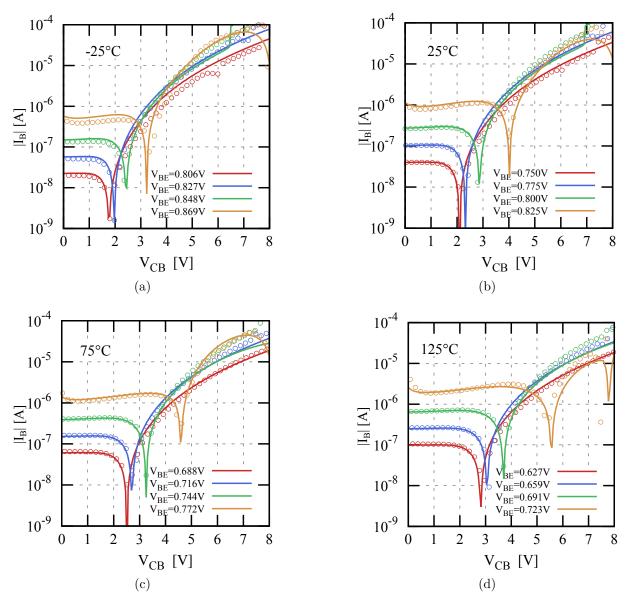

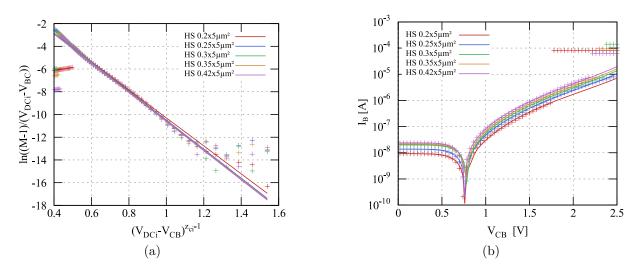

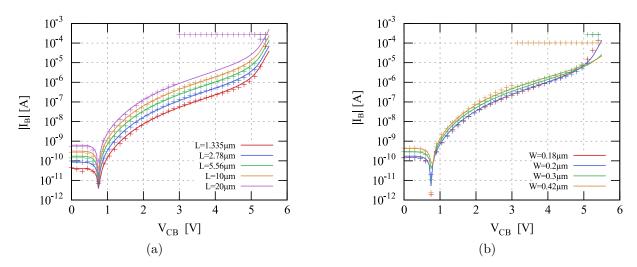

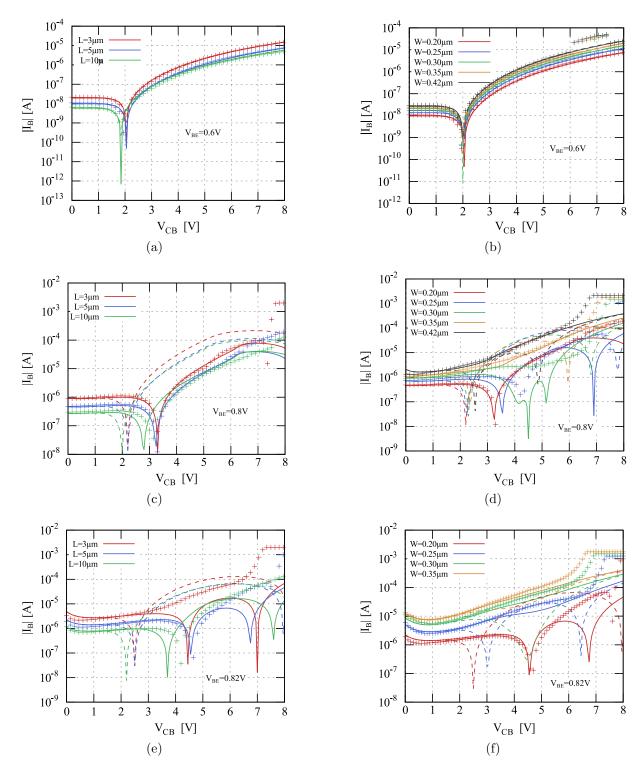

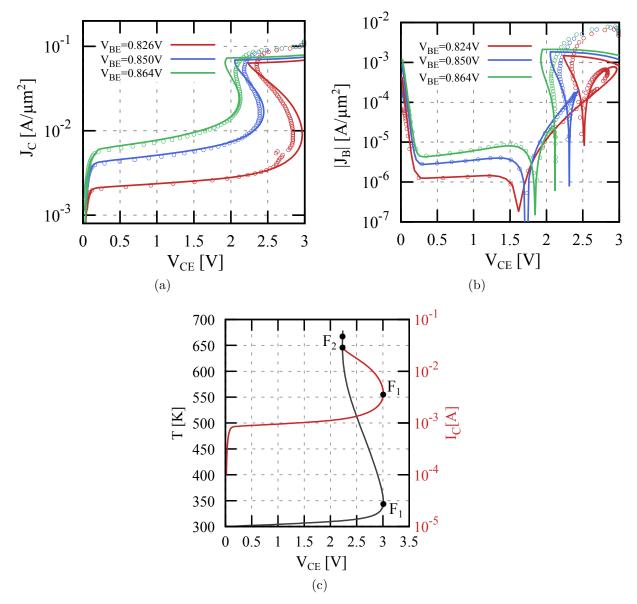

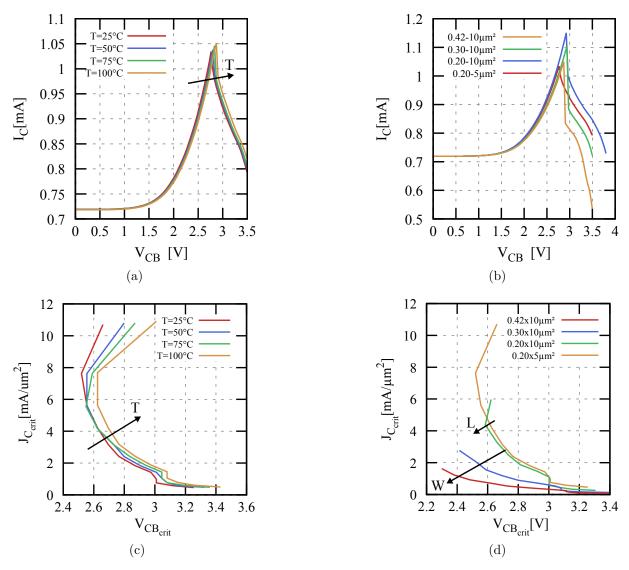

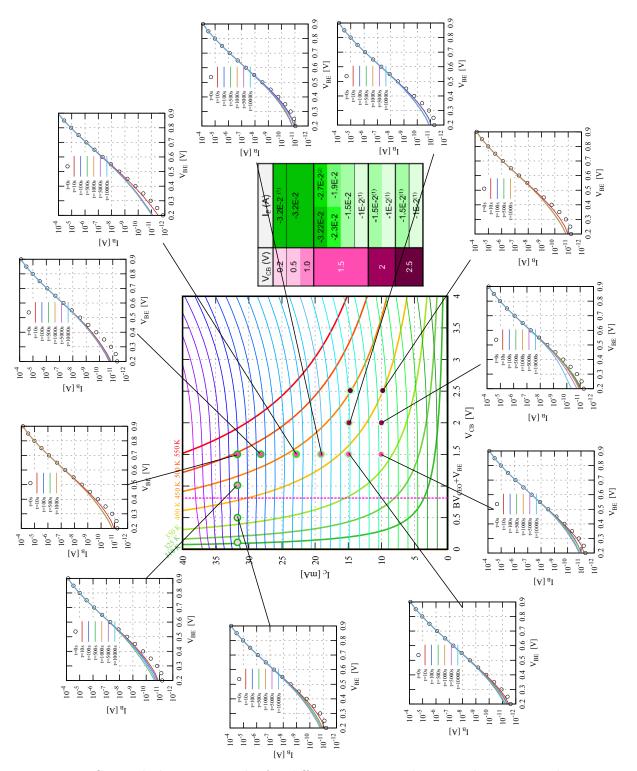

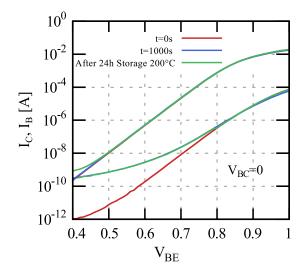

Figure 2.6 shows the measured base current as a function of the  $V_{CB}$  for different  $V_{BE}$  for a device with a relatively low collector doping profile (HV device). The electrical characteristic  $I_B(V_{CB})$  compares measurements with HICUM simulations. We can observe the model limitations at high current density. This figure highlights that  $BV_{CEO}$  increases with  $V_{BE}$  at high current. This  $BV_{CEO}$  shift is due to the decrease of the impact ionization at high current density. Therefore, a new model is required to account for this behavior.

Figure 2.6: Comparison between measurement (symbols) and model for HICUM/L2 version 2.4.0 (lines) at  $T = 25^{\circ}C$  for an HV transistor. Absolute value of the base current,  $|I_B|$ , as a function of the collector-base voltage,  $V_{CB}$  for different constant base-emitter voltages from  $V_{BE} = 0.7$  to 0.825V.

## 2.3 High Current Effects

The previous equation presented in section 2.2 gives satisfying results at low injection levels. However, toward higher injection, very significant deviations between simulated and measured electrical characteristics can be observed as shown in Figure 2.6. This is related to the high current effects which are particularly pronounced for HV HBTs featuring low collector doping. In the following section, we will deeply investigate this mechanism and its impact on the avalanche mechanism through a TCAD study.

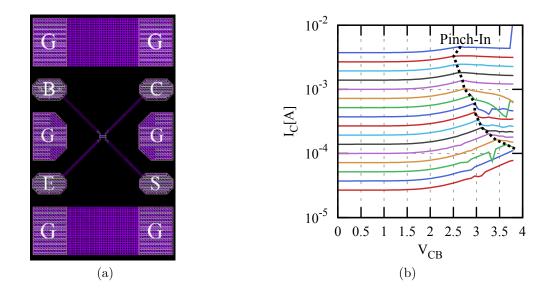

### 2.3.1 Impact Ionization Formulation in TCAD Simulations

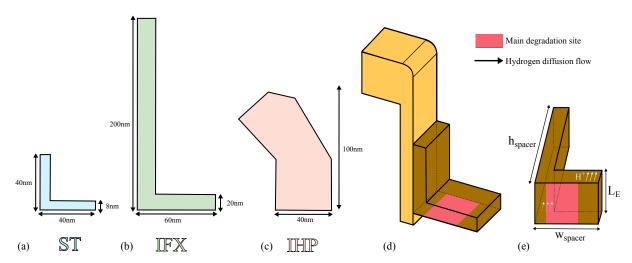

The TCAD structure used for the following simulations is close to what can be seen in STMicroelectronics bipolar transistor TEM picture [18] as presented in Figure 2.7. Germanium is used inside the intrinsic base.

TCAD simulations were performed to support the physical development of the impact ionization model. These simulations can be carried out through physical simulators such as Sentaurus [70]. These simulators allow to deeply explore the different mechanisms

Figure 2.7: Zoom of a sketch of a TCAD bipolar transistor structure. The red dashed-line represents the center of the emitter. The dimensions shown on the y and x axis are in  $\mu m$ .

involved in the transistor electrical behavior. Many avalanche generation models are implemented inside Sentaurus such as Okuto-Crowell [71], Van Overstraeten-de Man[64] etc... These models compute the impact ionization generation rate  $G_{ii}$  defined as the number of carrier created by impact ionization (*ii*). This rate is expressed as,

$$G_{ii} = \alpha_n \, n \, \nu_n + \alpha_p \, p \, \nu_p \tag{2.22}$$

This equation is similar to the one introduced in (2.3) with  $\nu_{n,p}$  the electron and hole velocity respectively. In this equation, the ionization coefficients  $\alpha_{n,p}$  need to be calculated. In Sentaurus, every model has its own  $\alpha_{n,p}$  definition, however, in the following development, only Okuto-Crowell avalanche generation model will be considered thanks to the improved accuracy that this model have already shown [71]. The Okuto-Crowell ionization coefficients are expressed as,

$$\alpha_{n,p}(F_{ava}) = a_{oc} \left(1 + c_{oc}(T - T_0)\right) F_{ava}^{\gamma} \exp\left(-\left(\frac{b_{oc}(1 + d_{oc}(T - T_0))}{F_{ava}}\right)^{\delta}\right)$$

(2.23)

The parameters  $a_{oc}$ ,  $b_{oc}$ ,  $c_{oc}$ ,  $d_{oc}$ ,  $\gamma$  and  $\delta$  are Okuto-Crowell coefficients that need to be extracted to accurately fit the impact ionization mechanism. The extraction procedure will not be explained here. This equation is empirical, but translate well the ionization behavior for recent HBTs for electric field values between 0.1 and  $1MV.cm^{-1}$  [64]. Their typical values for silicon can be found in [71].

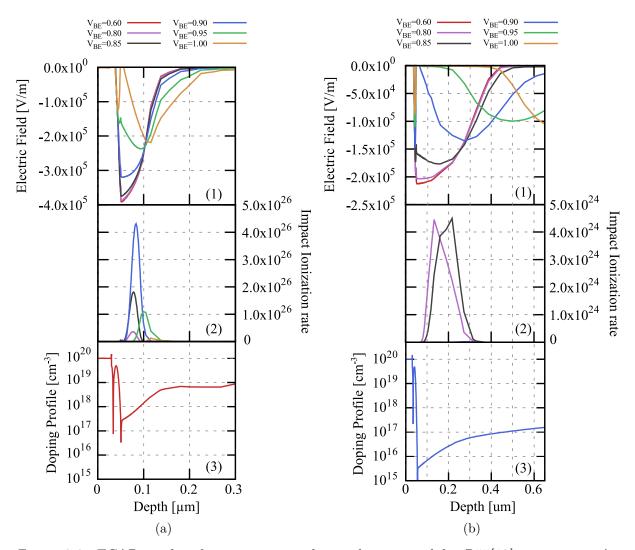

Figure 2.8: TCAD results of a structure similar to the one used for B55[18] transistors. Are plotted the electric field (1), the impact ionization generation rate (2) and the doping profile (3) for different  $V_{BE}$  at a constant  $V_{CB}$  close to the  $BV_{CEO}$  (1.5 and 3V respectively) for two different transistor flavors: (a) high speed - and (b) high voltage transistors.

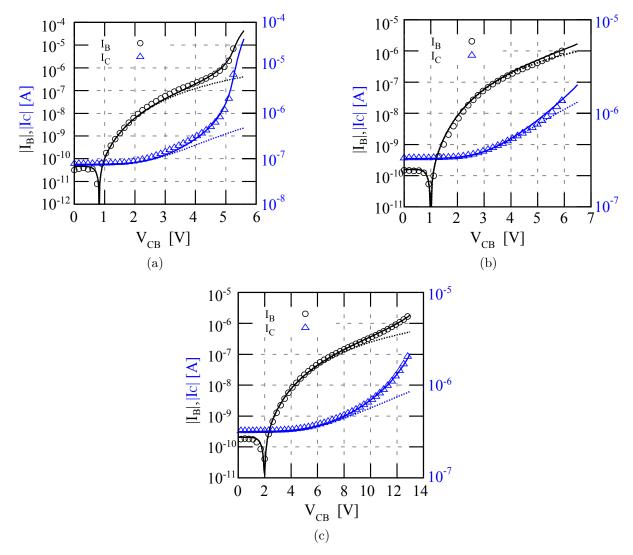

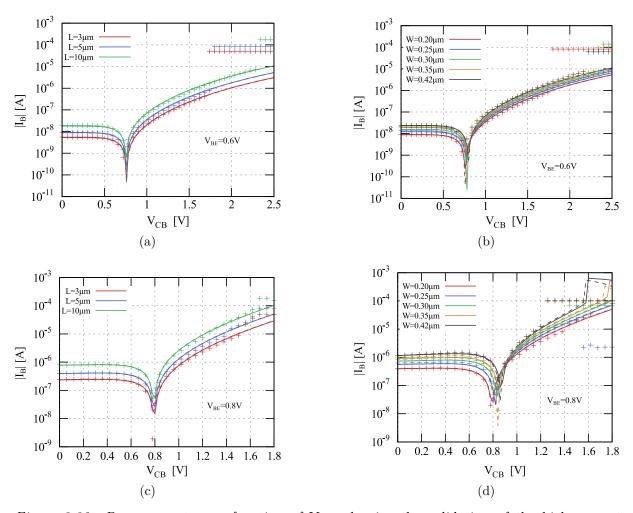

Figure 2.8 shows the TCAD simulation results of the electric field, the impact ionization generation rate and the corresponding doping profiles as a function of the depth for two different doping profiles (low and high collector doping profiles) and for different  $V_{BE}$ . It is highlighted that the impact ionization rate behavior changes with  $V_{BE}$  so as with the doping profile. The higher collector doping profile shows higher ionization rate peaks (4 × 10<sup>26</sup> versus 4 × 10<sup>24</sup>) implying, as expected, lower breakdown voltages.

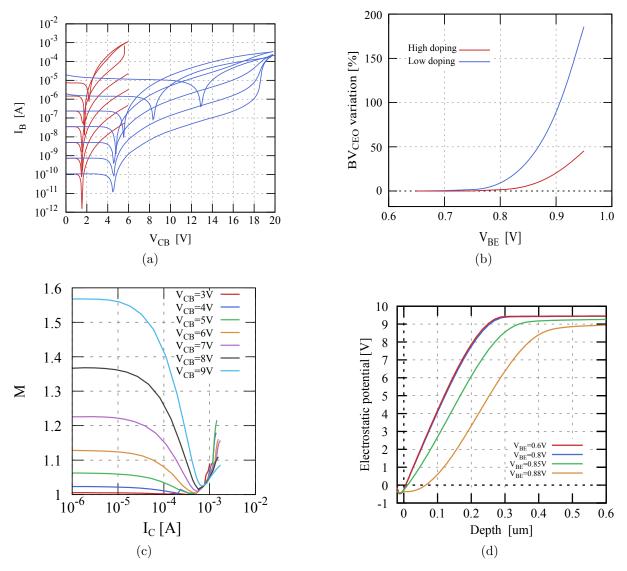

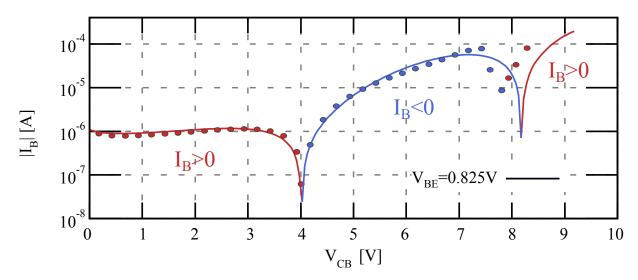

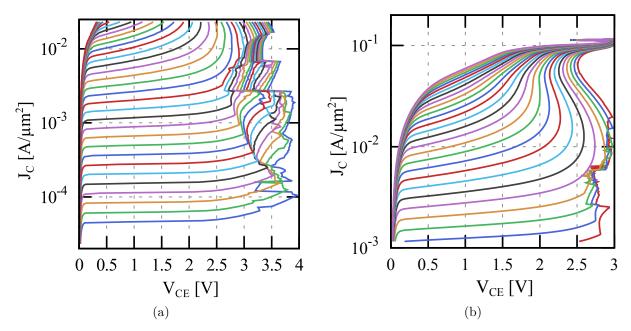

Moreover, the TCAD base current at constant  $V_{BE}$  for two different doping profiles is shown in Figure 2.9a and 2.9b. We can observe a larger  $BV_{CEO}$  increase in case of

Figure 2.9: (a) TCAD simulated base current as a function the base-collector voltage for different  $V_{BE} = [0.6:1V]$  (0.1V step) for low ( $N_D = 10^{16} \text{cm}^{-3}$ ) and high ( $N_D = 10^{18} \text{cm}^{-3}$ ) collector doping profiles - (b)  $BV_{CEO}$  calculation from Figure 2.9a. Increasing the doping concentration induces higher  $BV_{CEO}$  values. (c) TCAD simulation results of the avalanche multiplication factor as a function of the collector current with  $N_D = 10^{16} \text{cm}^{-3}$ . (d) Electrostatic potential as a function of the depth for  $V_{BE} = 0.6, 0.8, 0.85, 0.88V$  and  $V_{CB} = 9V$ .

a low doped collector (close to 200%) in comparison with the highly one. Figure 2.9c shows the TCAD multiplication factor as a function of the collector current for different base-collector voltages for bipolar transistors with a low collector doping profile. Here, for a given  $V_{CB}$ , M decreases with  $I_C$  and reaches a minimum at a current named  $I_{LIM}$ . Above that particular current, M increases again. Note that these TCAD simulations are

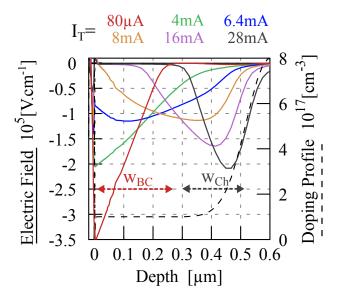

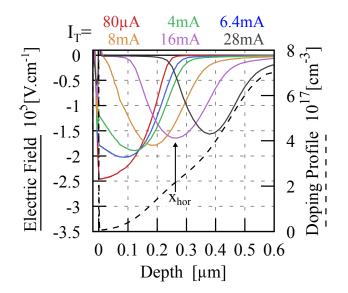

Figure 2.10: TCAD Electric field results for different currents (each color represent a different  $I_C$ ) at a constant  $V_{CB} = 7V$ . Are shown the three typical collector currents  $I_{KL} = 6.4mA$  corresponding to the current when  $w_{BC} = w_{epi}$ ,  $I_{LIM}$  (between 6.4 and 8mA) when the slope of the electric field is equal to 0,  $I_{KH} = 8mA$  when the BC-SCR does not touch the BC junction anymore (electric field equals to 0 at the BC junction).

made without self-heating, in order to clearly observe the impact ionization mechanism on the base current even at very high current density.

On the contrary, measurements show that due to the self-heating effects, the strong temperature increase leads not only to an increase in the collector current but also to an ionization coefficient decrease. Typically, for  $V_{BE} > 0.85V$  on HS transistors, the self-heating dominates the electrical behavior leading to no impact ionization effects at high base current value. On the contrary, for HV transistors, due to the early decrease of the impact ionization mechanism (as presented in Figure 2.9b), this particular avalanche shift is better observed.

Therefore, in the following section, a model that accounts for the avalanche collector current dependency will be developed. To that purpose, only low doped transistors will be studied but a similar approach can be performed also for highly doped transistors.

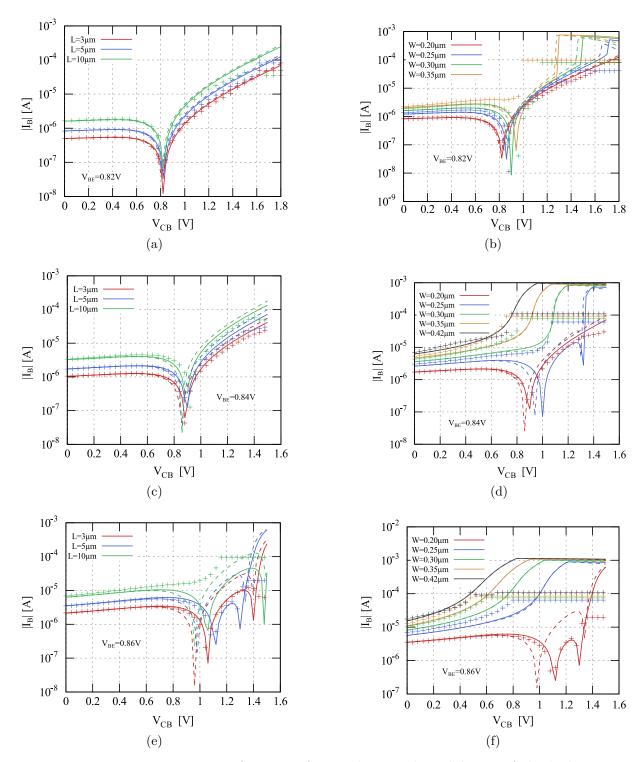

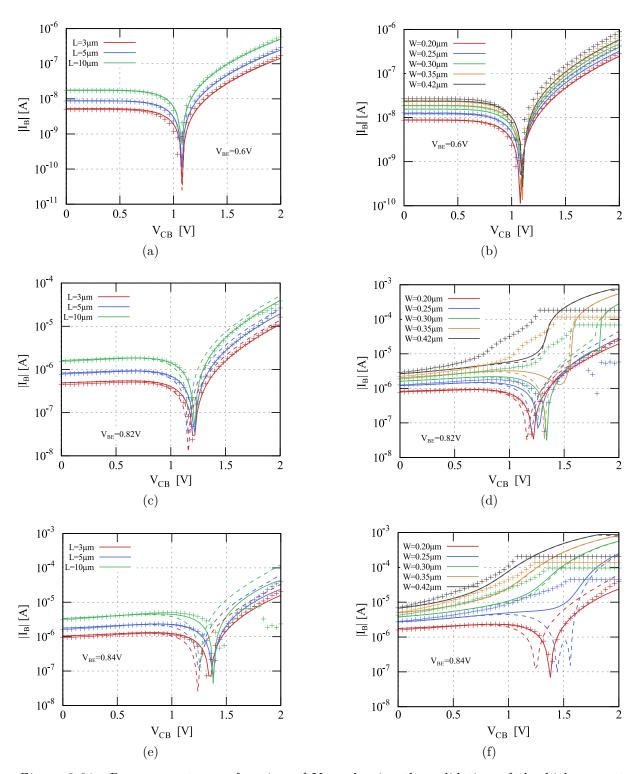

#### 2.3.2 Impact Ionization at medium currents

Here, for simplification purposes, we consider a simple constant doping profile in the epilayer as represented with dashed lines in Figure 2.10. This figure shows that the electric field changes with the collector current density (with  $V_{BE}$ ). The high current effects imply a drop of the electric field slope which becomes negative at very high current densities.

The electric field variation is due to the Poisson equation dependency with the collector current [72, 73]. The ionized carrier density along the depth x is current-dependent and is defined as  $N(x) = N_D - n$ . The transfer current density can be expressed as  $J_T = \frac{I_T}{A_E}$ . From these definitions, the transfer current can be re-expressed  $I_T = q A_E v_{sat} n$  assuming saturation velocity, which is justified since the electric field in the BC-SCR must be sufficiently high for impact ionization to occur. The Poisson equation expression is then given

$$\frac{dE}{dx} = \frac{q}{\varepsilon_{Si}} \left( N_D - n \right) \tag{2.24}$$

Thus leading to,

$$\frac{dE}{dx} = \frac{qN_D}{\varepsilon_{Si}} \left(1 - \frac{I_T}{I_{LIM}}\right) \tag{2.25}$$

Where  $I_{LIM} = q A_E v_{sat} N_D$  is defined as the transfer current corresponding to an electric field slope in the BC-SCR equal to 0.

Considering a constant electric field along the collector, the expression of the zeroslope electric field  $E_{LIM}$  is very simple:  $E_{LIM} = -\rho_{epi}J_{LIM}$ . The corresponding potential defined as the voltage separating ohmic and saturation velocity regime can therefore be expressed as  $V_{LIM} = -E_{LIM}w_{epi}$ . Finally, the internal collector resistance at low electric field  $R_{Ci0}$  is defined as equals to  $\frac{\rho_{epi}w_{epi}}{A_E}$ . Therefore,  $I_{LIM} = \frac{V_{LIM}}{R_{Ci0}}$ .

At a constant  $V_{CB}$ , the area below the electric field is constant and cannot change. Thus, as the slope of the electric field decreases with the current, the BC-SCR width increases up to a point when the BC-SCR reaches the buried layer. Here, the BC-SCR width can no longer increase. The slope keep decreasing with the current up to the zero-slope point ( $I_T = I_{LIM}$ ). Then, the slope sign changes becoming negative and the BC-SCR leaves the BC junction.

In the literature, many expressions have already presented the dependence of the impact ionization with the current density [42, 74]. For example, in MEXTRAM [75, 76, 77], the impact ionization is calculated through the width of the depletion layer thickness which is dependent of the current density inside the model. Here, we additionally account for the impact ionization increase at very high current density and the dependence of the impact ionization mechanism with the doping profile.

In order to obtain a close-form solution of equation (2.25), the following section will discuss two asymptotic cases:

- $I_T < I_{LIM}$  (medium current density)

- $I_T > I_{LIM}$  (high current density)

Depending on the slope of the electric field, different boundary conditions are used for the Poisson equation solution. The electric field can be obtained integrating equation (2.25) over the BC-SCR with a zero-field boundary condition at  $x = w_{BC}$ . Thus, solving equation (2.25), an expression of the electric field in the  $I_T < I_{LIM}$  region is

$$E(x) - E_{jC} = \frac{qN_D}{\varepsilon_{Si}} \left(1 - \frac{I_T}{I_{LIM}}\right) x$$

(2.26)

This equation can also be re-written,

$$E(x) = \frac{qN_D}{\varepsilon_{Si}} \left(1 - \frac{I_T}{I_{LIM}}\right) (x - w_{BC})$$

(2.27)

As shown in Figure 2.10, the depletion width  $w_{BC}$  is dependent of the transfer current. The depletion region moves towards the buried layer for an extracted current  $I_T$  value higher than 1mA for HV transistors. Thus, the calculation presented in section 2.2 is not modified. Using the definition of the electric field gradient, (2.26) is integrated along the BC-SCR,

$$\int_{0}^{w_{BC}} E(x) \, dx = \frac{q \, N_D}{2 \, \varepsilon_{Si}} \left( 1 - \frac{I_T}{I_{LIM}} \right) w_{BC}^2 + E_{jC} w_{BC} \tag{2.28}$$

Thus, using (2.14) and (2.15),

$$\frac{q N_D}{2 \varepsilon_{Si}} \left( 1 - \frac{I_T}{I_{LIM}} \right) w_{BC}^2 = V_{DCi} - V_{BCi}$$

(2.29)

That yields the current dependent BC-SCR width,

$$w_{BC} = \sqrt{\frac{V_{DCi} - V_{BCi}}{\frac{qN_D}{2\varepsilon_{Si}} \left(1 - \frac{I_T}{I_{LIM}}\right)}}$$

(2.30)

Equation (2.30) is dependent on the collector current. Finally, the equations of  $w_{BC}$ and  $E_{jC}$  are reformulated according to their expression developed previously in section 2.2 for low current densities  $(w_{BC_{low}} \text{ and } E_{jC_{low}})$ , respectively

$$w_{BC} = \left(\sqrt{1 - \frac{I_T}{I_{LIM}}}\right)^{-1} w_{BC_{low}} \quad with \quad w_{BC_{low}} = \frac{\varepsilon_{Si} A_E}{C_{jCi}} \tag{2.31}$$

And  $E_{jC}$  can also be expressed as,

$$E_{jC} = \sqrt{1 - \frac{I_T}{I_{LIM}}} E_{jC_{low}} \quad with \quad E_{jC_{low}} = -\frac{2\left(V_{DCi} - V_{BCi}\right)C_{jCi}}{\varepsilon_{Si}A_E} \tag{2.32}$$

The impact ionization integral (2.7), can then be rewritten with (2.27),

$$1 - \frac{1}{M} = \int_0^{w_{BC}} a \exp\left(\frac{-b}{\left|\frac{qN_D}{\varepsilon_{Si}}w_{BC}\left(1 - \frac{I_T}{I_{LIM}}\right)\left(1 - \frac{x}{w_{BC}}\right)\right|}\right) dx$$

(2.33)

Using the previous definition of  $w_{BC}$  (2.31) and  $E_{jC}$  2.32, equation (2.33) can be expressed,

$$1 - \frac{1}{M} = \int_0^{w_{BC}} a \, \exp\left(\frac{-b}{\left|E_{jC}\left(1 - \frac{x}{w_{BC}}\right)\right|}\right) \, dx \tag{2.34}$$

The same equation as (2.10) is found. Thus, this integral can be calculated assuming that  $x \ll w_{BC}$ . That particular assumption is true as long as the electric field peak is located close to the BC junction which is true for  $I_T < I_{LIM}$ . Therefore, (2.34) is re-expressed. Its expression is similar to (2.13),

$$1 - \frac{1}{M} = \frac{a}{b} E_{jC} w_{BC} \exp\left(\frac{-b}{|E_{jC}|}\right)$$

(2.35)

Finally, the multiplication factor can be expressed from equation (2.31) and (2.32),

$$M - 1 = \frac{f_{AVL}E_{jC_{low}}\exp\left(\frac{-q_{AVL}}{E_{jC_{low}}f_{cor_L}}\right)}{1 - f_{AVL}E_{jC_{low}}\exp\left(\frac{-q_{AVL}}{E_{jC_{low}}f_{cor_L}}\right)}$$

(2.36)

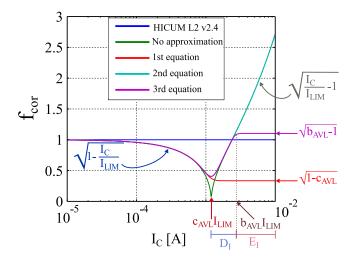

where the low current corrective factor  $f_{corL}$  is defined as,

$$f_{cor_L} = \sqrt{1 - \frac{I_T}{I_{LIM}}} \tag{2.37}$$

Figure 2.11: Base-Collector charge and theoretical electric field at high current density. Is also represented the injection zone (of width  $w_i$ ) and the buried layer.

### 2.3.3 Impact Ionization at high currents

In the previous part, it has been assumed that the collector current was below the limit current,  $I_{LIM}$ . When going beyond  $I_{LIM}$  it is necessary to account for the electric field increase arising at the buried layer. As presented in Figure 2.9c, beyond  $I_{LIM}$ , the multiplication factor increases. This particular mechanism need to be taken into account.

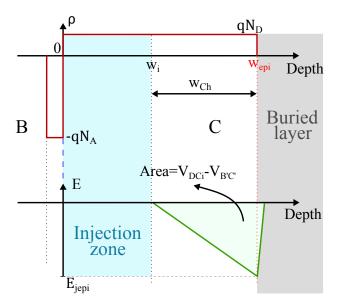

In the case of  $I_T > I_{LIM}$ , the space charge region reaches the buried layer. Its width,  $w_{Ch}$  is shown in Figure 2.10. A first order solution for the corresponding electric field can be obtained by assuming a negligible field in the (high current) injection zone. This injection zone is represented in Figure 2.11. In this region, carriers are not accelerated anymore by the electric field.

The Poisson equation (2.25) can therefore be re-expressed

$$E(x) - E_{jepi} = \frac{q \ N_D}{\varepsilon_{Si}} \left(1 - \frac{I_T}{I_{LIM}}\right) (x - w_{epi})$$

(2.38)

where  $E_{jepi}$  represents the maximum electric field localized close to the buried layer junction and  $w_{epi}$  is the collector width,  $E_{jepi} = \frac{qN_D}{\epsilon_{Si}} \left(1 - \frac{I_T}{I_{LIM}}\right) (w_i - w_{epi})$ . The injection width  $w_i$  can be defined as  $w_i = w_{epi} - w_{Ch}$ . The electric field expression (2.38) can thus be written,

$$E(x) = \frac{q N_D}{\varepsilon_{Si}} \left( 1 - \frac{I_T}{I_{LIM}} \right) (x - w_i)$$

(2.39)

Integrating along the BC-SCR (2.38),

$$\int_{0}^{w_{epi}} E(x) \, dx = \int_{w_i}^{w_{epi}} E(x) \, dx = \frac{q \, N_D}{2 \, \varepsilon_{Si}} \left( 1 - \frac{I_T}{I_{LIM}} \right) (w_i - w_{epi})^2 = \frac{q \, N_D}{2 \, \varepsilon_{Si}} \left( 1 - \frac{I_T}{I_{LIM}} \right) w_{Ch}^2$$

(2.40)

Additionally, from the definition of the electrostatic potential, a similar formulation as (2.15) is found,

$$E_{jepi}w_{Ch} = -2 \ (V_{DC_i} - V_{BC_i}) \tag{2.41}$$

The final expression of the depletion width is then determined from (2.40) and (2.41),

$$w_{Ch} = \sqrt{\frac{(V_{DC_i} - V_{BCi})}{\frac{q N_D}{2 \varepsilon_{Si}} \left(\frac{I_T}{I_{LIM}} - 1\right)}}$$

(2.42)

The expression of  $w_{Ch}$  (2.42) is comparable to the one presented previously in equation (2.30). However, here, the sign of the collector current dependency has changed. The ionization integral can be calculated in a similar way as presented in section 2.3.2,

$$1 - \frac{1}{M} = \int_{w_i}^{w_{epi}} a \exp\left(\frac{-b}{\frac{q N_D}{\varepsilon_{Si}} \left(1 - \frac{I_T}{I_{LIM}}\right) (x - w_i)}\right) dx \approx \frac{a}{b} E_{jepi} w_{Ch} \exp\left(\frac{-b}{|E_{jepi}|}\right)$$

(2.43)

Analogous expressions as developed in the previous section are further obtainable.  $w_{Ch}$ and  $E_{jepi}$  equations are also assessed from the internal BC depletion capacitance and from the emitter area as,

$$w_{Ch} = \left(\sqrt{\frac{I_T}{I_{LIM}} - 1}\right)^{-1} w_{BC_{low}} \tag{2.44}$$

And

$$E_{jepi} = \sqrt{\frac{I_T}{I_{LIM}} - 1} E_{jC_{low}}$$

$$(2.45)$$

Finally, the multiplication factor expression is reduced to

$$M - 1 = \frac{f_{AVL} E_{jC_{low}} \exp\left(\frac{-q_{AVL}}{E_{jC_{low}} f_{cor_H}}\right)}{1 - f_{AVL} E_{jC_{low}} \exp\left(\frac{-q_{AVL}}{E_{jC_{low}} f_{cor_H}}\right)}$$

(2.46)

where the high current corrective factor  $f_{corH}$  is defined as,

$$f_{cor_H} = \sqrt{\frac{I_T}{I_{LIM}}} - 1 \tag{2.47}$$

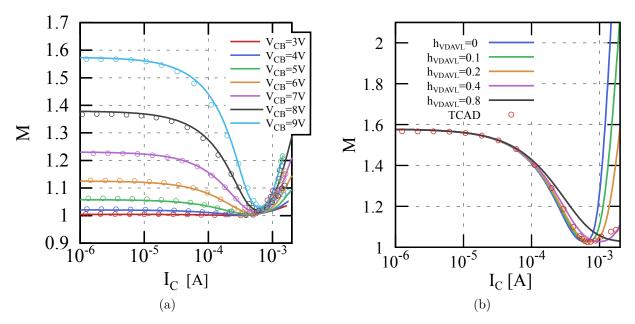

#### 2.3.4 Non constant doping concentration in the epi-layer

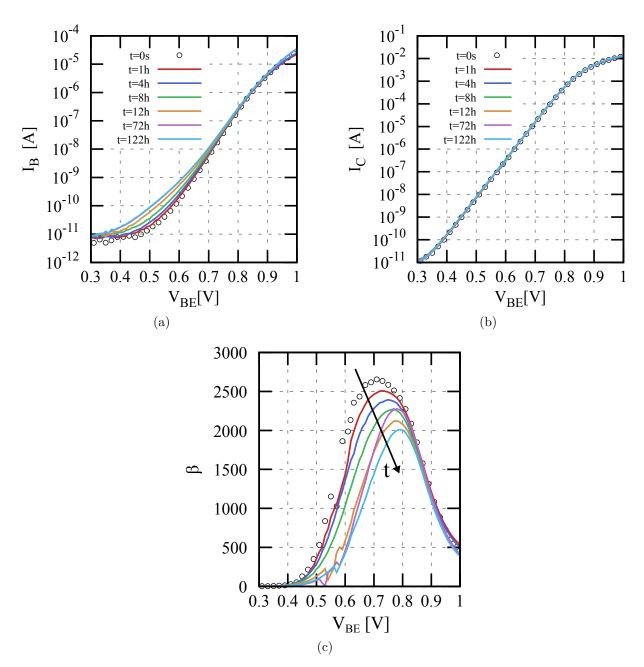

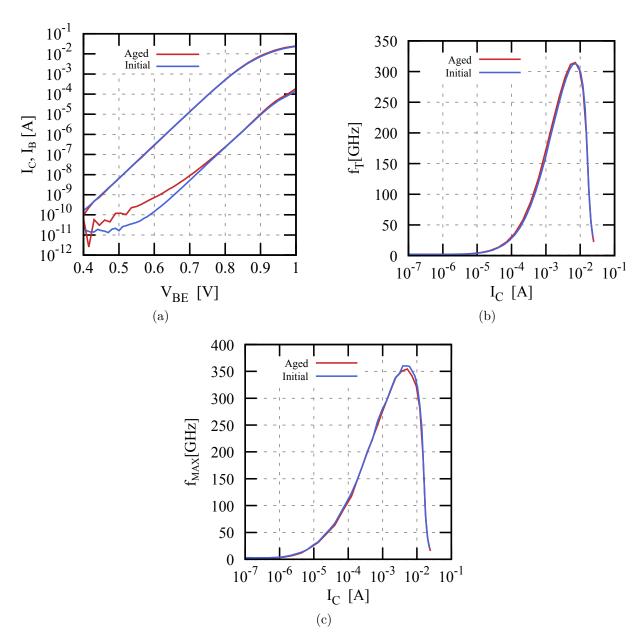

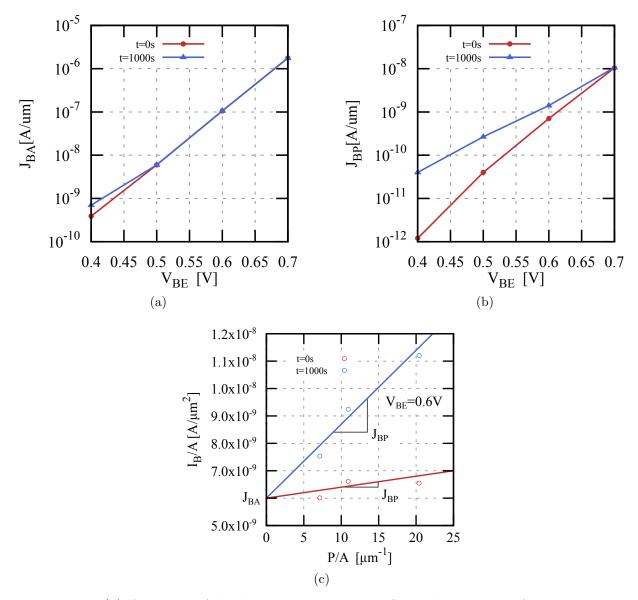

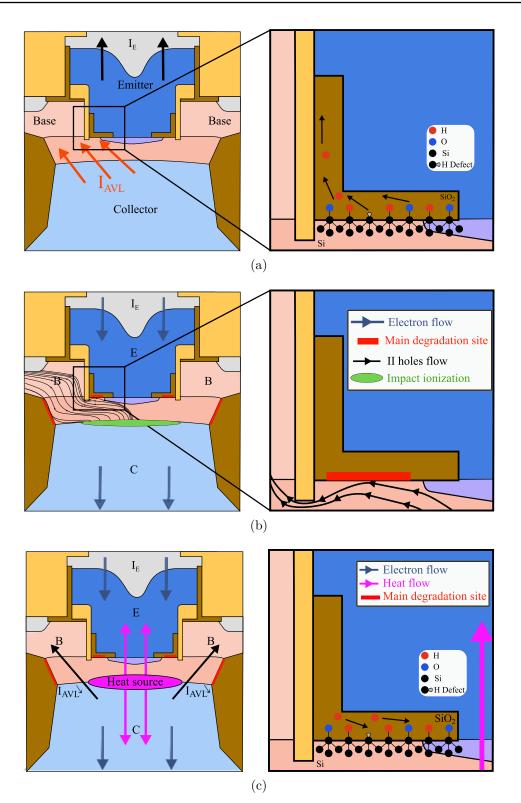

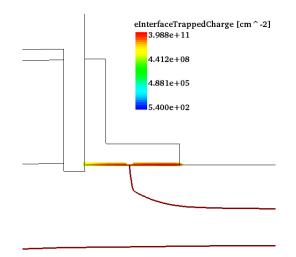

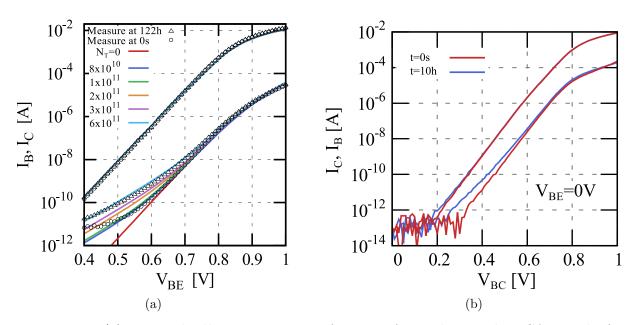

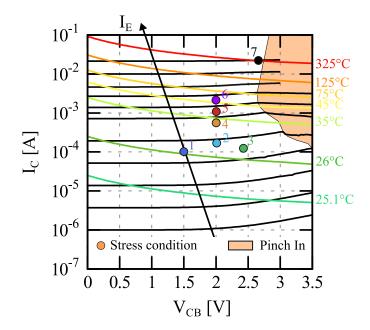

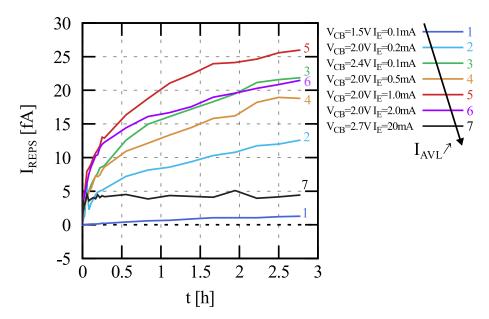

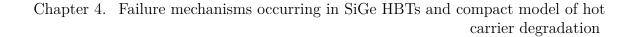

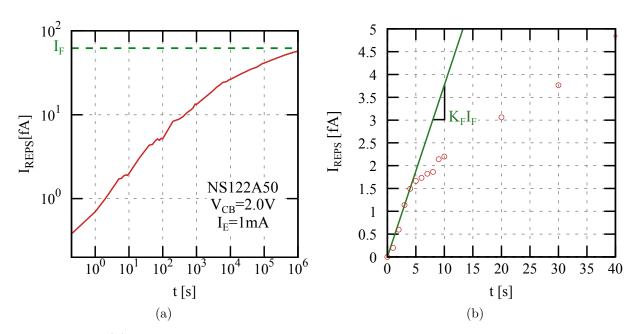

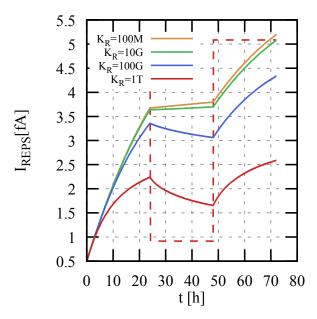

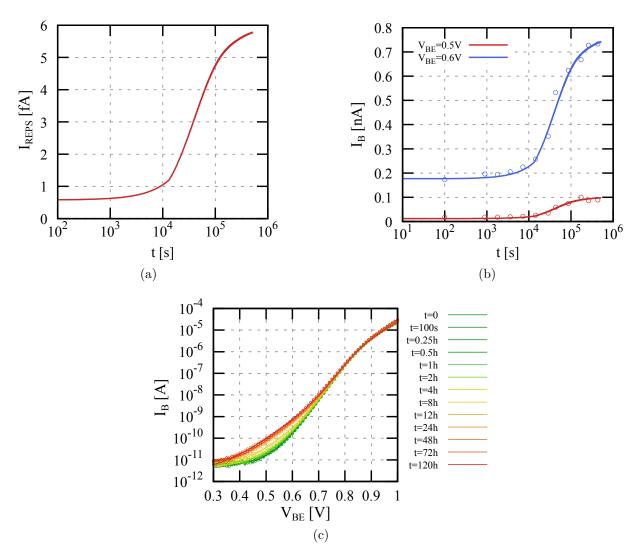

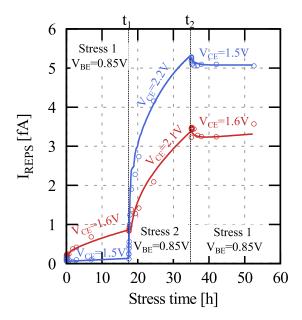

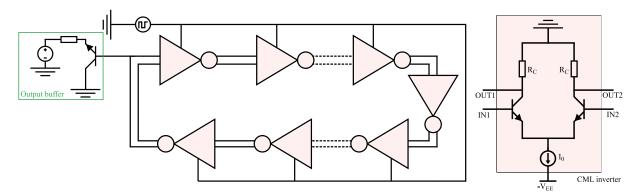

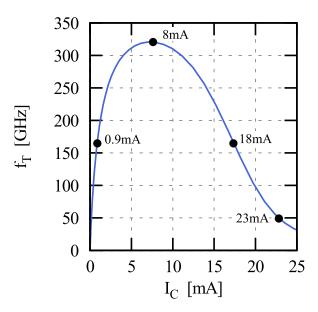

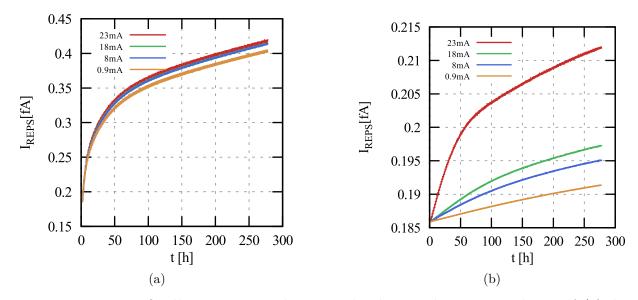

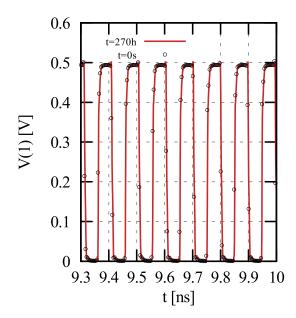

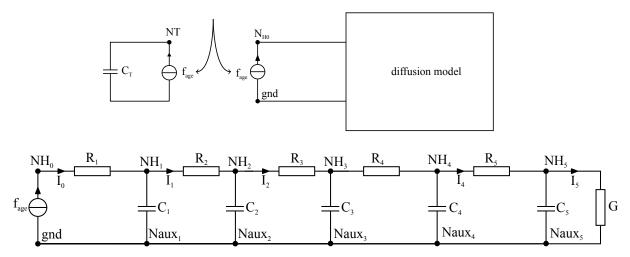

The expressions presented in the previous part (equation (2.37) and (2.47)) are valid for a constant doping profile. In order to account for a spatially dependent doping profile, different field distributions as shown in Figure 2.12 need to be considered. Here, to enable a direct comparison between constant and non-constant doping profiles, the doping has been chosen in such a way that the mean concentration over the entire epi-layer is the same. This particular doping profile is sufficiently close to the measured one in order to directly compare both profiles.