# Study on CDM ESD Robustness Among On-Chip Decoupling Capacitors in CMOS Integrated Circuits

Yi-Chun Huang and Ming-Dou Ker, Fellow, IEEE

*Abstract*— The integrated circuit (IC) products fabricated in the scaled-down CMOS processes with higher clock rate and lower power supply voltage (VDD) are more sensitive to the transient/switching noises on the power lines with the parasitic inductance induced by the bonding wire. The typical method to suppress the power line noise is to add on-chip decoupling capacitors. Meanwhile, electrostatic discharge (ESD) is also a challenging issue on IC reliability in advanced CMOS technology. For the ICs fabricated in an advanced process, with the thinner gate oxide, the circuits are particularly vulnerable to the chargeddevice model (CDM) ESD events. However, there was very limited research to investigate the ESD robustness on the decoupling capacitors, especially during the CDM ESD events. In this work, the CDM ESD robustness among different types of decoupling capacitors in ICs was investigated in a 0.18-µm CMOS technology.

*Index Terms*— Power line noise, transient/switching noise, parasitic inductance, decoupling capacitor, charged-device model (CDM), electrostatic discharge (ESD).

## I. INTRODUCTION

Wing to the continued scaling down of CMOS technology, the IC products had been operated under the condition of higher clock rate and lower power supply voltage. Maintaining the quality of power supply voltage has become a critical issue, because modern IC products were increasingly sensitive to noise sources, such as the simultaneous switching noise on power lines [1]. The power line noise is related to the switching activity and the current consumption of the circuits [2] with the parasitic component of parasitic inductance induced by the bonding wire. The noise on the power line will cause the degradation of the circuit performance, and also cause the reliability issue. To maintain the quality of the power supply voltage, the most common method is to place the on-chip decoupling capacitors between the power lines of V<sub>DD</sub> and Vss to reduce the noise arising from IR drop and Ldi/dt effect.

With the progress of CMOS technology, the thinner gate oxide encounters serious ESD reliability issue, especially the charged-device model (CDM) ESD events. The lower oxide breakdown voltage caused by thinner gate oxide was very vulnerable to the charged-device model (CDM) ESD events, which can easily cause damage to the internal circuits and hence need additional ESD protection design [3]-[8]. The discharging current of CDM ESD can be taken as a high-frequency signal.

\*This work was supported in part by the "Center for Neuromodulation Medical Electronics Systems" from The Featured Areas Research Center Program within the framework of the Higher Education Sprout Project by the Ministry of Education (MOE) in Taiwan. This work was also supported in part by the Ministry of Science and Technology (MOST), Taiwan, under Contracts of MOST 109-2221-E-009-100-MY3 and MOST 110-2622-8-009-017-TP1. (Corresponding author: *Ming-Dou Ker.*)

Y.-C. Huang and M.-D. Ker are with the Institute of Electronics, National Yang Ming Chiao Tung University, Hsinchu 300, Taiwan (e-mail: mdker@ieee.org).

For a high-frequency signal, a low resistive path is provided by the decoupling capacitor due to the physical characteristic (Z=1/sC). Thus, the CDM ESD current will be easily discharged through the decoupling capacitor to cause damage on it, when the CDM ESD is directly discharged from the V<sub>DD</sub> pin. So far, there were some few reports on investigating the decoupling capacitors with HBM (human-body model) ESD events [9]-[10]. Recently, a study to optimize the MIM (metalinsulator-metal) decoupling capacitor with consideration on CDM robustness was reported [11]. But, no report has studied the MOS decoupling capacitors with CDM ESD events.

1

In this work, the test circuits realized with a ring oscillator and three types of decoupling capacitors are used to verify the effectiveness of decoupling capacitors on suppressing the power line noise, and especially to investigate the CDM ESD robustness among three types of decoupling capacitors.

> II. INTERNAL ESD THREATS OF ON-CHIP DECOUPLING CAPACITORS

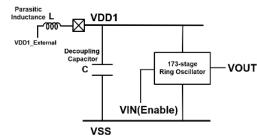

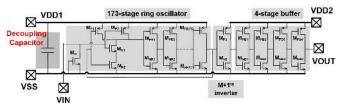

Fig. 1 illustrates the block diagram of the test circuit used in this work. The internal circuit is realized by a ring oscillator of 173-stage inverter chain. With the decoupling capacitor (C) added between the power lines (VDD1 and VSS), the decoupling capacitor can suppress the noise on VDD1 which is induced by the switching of the inverter chain inside the ring oscillator. When an enable signal (VIN) is given to the input pin of the ring oscillator, the ring oscillator starts oscillating, and the inverters inside the inverter chain are switching rapidly to cause rapid current variation. This rapid current variation will flow through the bonding wire of VDD1, the parasitic inductance of the bonding wire will cause the Ldi/dt effect of voltage variation, and hence result in power supply noise on VDD1.

Fig. 1. Block diagram of the test circuit and the parasitic inductance induced by the bonding wire. The test circuit includes a ring oscillator of 173-stage inverter chain and a decoupling capacitor.

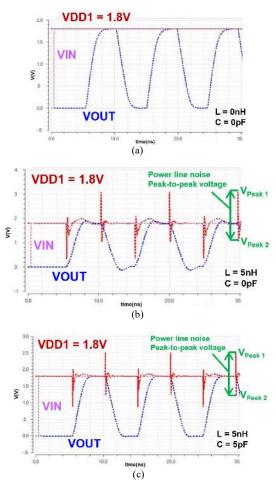

In order to suppress the power line noise, the decoupling capacitor (C) is placed between VDD1 and VSS. From the simulation results shown in Fig. 2 and Table I, the parasitic inductance is selected as 5nH due to the average bonding wire

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2021.3116961, IEEE Journal of the Electron Devices Society

2

length in our testkey package, which is estimated with the rule of thumb 1nH/1mm [12]. In addition, the capacitance of decoupling capacitor is selected as 5pF for study purpose. Fig. 2(a) shows the ideal condition of the circuit with an output frequency of 97 MHz generated from the ring oscillator, which is without the presence of parasitic inductance and decoupling capacitor. Fig. 2(b) shows the results with the presence of parasitic inductance (5nH) but without the decoupling capacitor. Fig. 2(c) shows the results with the presence of both parasitic inductance (5nH) and decoupling capacitor (5pF). It is clearly observed that the peak-to-peak voltage of power line noise is reduced in Fig. 2(c), as compared with Fig. 2(b). As listed in Table I, the simulation results show that the decoupling capacitor indeed achieves the purpose of suppressing the power line noise.

Fig. 2. Simulation results of the test circuit (a) without parasitic inductance, (b) with parasitic inductance of 5nH, and (c) with parasitic inductance of 5nH and decoupling capacitor of 5pF. Power line noise induced by the parasitic inductance can be suppressed by decoupling capacitor (the output freq. of ring oscillator is 97MHz).

TABLE I SIMULATION RESULTS OF POWER LINE NOISE WITH OR WITHOUT DECOUPLING CAPACITOR

|                              | VPeak 1(V) | VPeak 2 (V) | Power line noise         |

|------------------------------|------------|-------------|--------------------------|

|                              |            |             | Peak-to-peak voltage (V) |

| Without decoupling capacitor | 3.012      | 1.036       | 1.976                    |

| With decoupling capacitor    | 2.514      | 1.243       | 1.271                    |

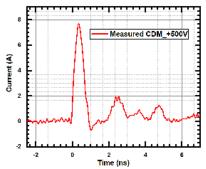

The CDM ESD issue, which can discharge a huge current in a very short time, has become more challenging to modern IC products with the thinner gate oxide fabricated in the advanced CMOS processes [3]-[8]. Fig. 3 shows the discharging current waveform with the CDM ESD level of +500V from the device under test (DUT) with an equivalent capacitance of 41 pF, as estimated from JEDEC standard [13]. As seen from the measured current transient waveform, the discharging current can reach 7.68A in just 275ps, and the main current pulse is within ~1 ns.

Fig. 3. Measured CDM ESD current waveform ( $\pm$ 500V) from the device under test (DUT) with an equivalent capacitance of 41 pF. The current reaches 7.68A within 275ps, and the main current pulse is within  $\sim$ 1 ns.

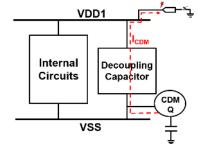

When the CDM ESD is discharging from the VDD1 pin, as illustrated in Fig. 4, a low resistive discharging path is provided by the decoupling capacitor that placed between VDD1 and VSS. The discharging current waveform of CDM can be seen as a high-frequency signal. The low resistive path with its impedance of Z=1/sC is provided by the decoupling capacitor, thus the CDM discharging current will be concentrated to flow through the decoupling capacitor. If the decoupling capacitor was implemented by the MOS devices with thinner gate oxide, it would be easily damaged during CDM ESD events, especially when the CDM ESD is discharging from the power pin (VDD1) of internal circuits.

Fig. 4. The illustration to show CDM ESD current path that will be concentrated to flow through the decoupling capacitor during CDM ESD events, especially when the CDM ESD is discharging from the power pin (VDD1) of internal circuits.

# III. TEST CIRCUITS FOR INVESTIGATING CDM ROBUSTNESS AMONG DIFFERENT DECOUPLING CAPACITORS

#### A. Ring Oscillator Design

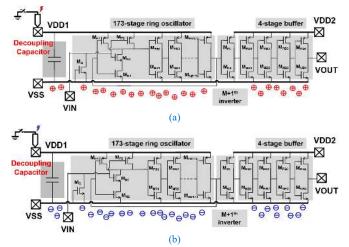

The internal circuit for test chip is realized by a ring oscillator with 173-stage inverter chain, where a decoupling capacitor of  $\sim 5 \text{ pF}$  is added between the power (VDD1) line and ground (VSS) of the ring oscillator. Different types of decoupling capacitors are selected and added to the test chip with the ring oscillator to verify their CDM ESD levels. As

shown in Fig. 5, the ring oscillator is designed with 173 inverter stages, not only for the odd number stages to oscillate but also a prime number to minimize the probability of higher harmonic signals [14]. In the inverter chain of 173 inverter stages, one of the inverter stages is replaced by a two-input NAND gate to achieve the purpose of a switch that is used to start or stop the oscillator. The M+1th inverter between the 173-stage ring oscillator and the 4-stage buffer serves the purpose to partially isolate the effect of the capacitive load [15]. The ring oscillator with decoupling capacitor is separated from the 4-stage buffer, which are placed in two isolated power domains. The 4-stage buffer is used to drive the signal to the output pin for observation on the oscillation frequency that is generated by the 173-stage ring oscillator. To drive the heavy loading at the output pad and the external connection, the traditional tapered buffer circuit with the increased large transistor dimensions was applied [16]. The power line of the 4-stage buffer is supplied by a standalone power pad (VDD2), therefore the power line noise induced by the ring oscillator at the VDD1 can be clearly observed.

Fig. 5. The ring oscillator of 173-stage inverter chain with decoupling capacitor was used as the internal circuits of test chip for CDM ESD study, which was designed and fabricated in a 0.18-µm 1.8V CMOS process.

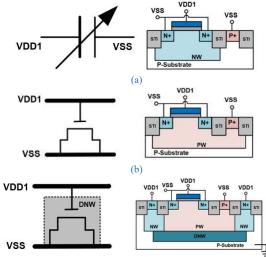

## B. Decoupling Capacitors

Three decoupling capacitors were selected and implemented in the test chip with the ring oscillator of 173-stage inverter chain, which were the varactor, NMOS capacitor, and NMOS capacitor with deep N-well (DNW), respectively. The symbol and cross-sectional view of the varactor as decoupling capacitor is shown in Fig. 6(a), whereas Fig. 6(b) shows the symbol and cross-sectional view of the NMOS capacitor. The varactor and NMOS capacitor are selected as the decoupling capacitors, because they have a larger value of effective capacitance per area [2], [17]. Fig. 6(c) shows the symbol and cross-sectional view of the NMOS with deep N-well (DNW) as decoupling capacitor, where a deep n-well (DNW) layer is used to surround the whole NMOS capacitor.

To verify the effectiveness of different decoupling capacitors on suppressing the power line noise of internal circuits (the ring oscillator of 173-stage inverter chain), four combinations of test circuits are set and listed in Table II. A baseline test circuit is built with the ring oscillator and the 4-stage buffer only, without any decoupling capacitor between the power lines. The other three test circuits are built by the baseline test circuit with the additional on-chip decoupling capacitors of varactor, NMOS capacitor, and NMOS capacitor with deep N-well (DNW), respectively.

The capacitance of the decoupling capacitors is selected as 5 pF. With the device and process parameters provided by foundry, the simulation results of different types of capacitors in the chip layout are listed in Table III. The device dimensions of all capacitors and transistors used in test circuits are listed in Table

IV, which were designed in a 0.18- $\mu$ m CMOS process with 1.8-V devices.

(c) Fig. 6. The symbols and cross-sectional views of (a) varactor, (b) NMOS capacitor, and (c) NMOS capacitor with DNW.

TARLE II. COMPINATIONS OF TEST CIRCUITS

| TABLE II COMBINATIONS OF TEST CIRCUITS |                      |                |  |

|----------------------------------------|----------------------|----------------|--|

| Symbol                                 | Description          | Decoupling     |  |

|                                        |                      | capacitor type |  |

| (1) Baseline                           | ring osc. only       | -              |  |

| (2) Var.                               | ring osc. + Varactor | Varactor       |  |

| (3) NMOS_cap.                          | ring osc. + NMOS     | NMOS           |  |

| (4)                                    | ring osc. + NMOS w/  | NMOS w/ DNW    |  |

| NMOS_cap_DNW                           | DNW (DNW is biased   |                |  |

at VDD1)

TABLE III

Simulation Results of Decoupling Capacitors in Layout

| Capacitor type | Spec (pF) | Post-sim (pF) | Area (µm <sup>2</sup> ) |

|----------------|-----------|---------------|-------------------------|

| Var.           | 5         | 5.0768        | 1503.4992               |

| NMOS_cap       | 5         | 5.0247        | 1389.0072               |

| NMOS_cap_DNW   | 5         | 6.6539        | 2704.7219               |

TABLE IV

DEVICE DIMENSIONS OF THE TEST CIRCUITS

| 0.1.5.5                    | D. I.            |                                     |                                |

|----------------------------|------------------|-------------------------------------|--------------------------------|

| Subcircuit                 | Device parameter |                                     |                                |

| On-chip                    | MOS W/L          | Var.                                | 270/2.16                       |

| decoupling capacitor       | (µm/µm)          | NMOS_cap                            | 131.1/4.32                     |

| (5pF)                      |                  | NMOS_cap_DNW                        | 262/2.16                       |

|                            |                  | $M_{P1} = M_F$                      | $_{2} = 2.8/0.18$              |

| 173-stage                  | MOS W/L          | $M_{N1} = M_{N2} = 2/0.18$          |                                |

| ring oscillator            | (µm/µm)          | $M_{PR1} \sim M_{PR173} = 2.8/0.18$ |                                |

|                            |                  | $M_{NR1} \sim M_{NR173} = 1/0.18$   |                                |

|                            |                  | $M_G = 120/0.18$                    |                                |

| M+1 <sup>th</sup> inverter | MOS W/L          | $M_{P3} = 2.8/0.18$                 |                                |

|                            | (µm/µm)          | $M_{N3} = 1/0.18$                   |                                |

|                            |                  | Buffer_1                            | $M_{PB1} = 9.24/0.18$          |

|                            |                  |                                     | $M_{\rm NB1}=3.3/0.18$         |

|                            |                  | Buffer_2                            | $M_{PB2} = 30.8/0.18$          |

| 4-stage buffer             | MOS W/L          |                                     | $M_{\rm NB2} = 11/0.18$        |

|                            | (μm/μm)          | Buffer_3                            | $M_{\text{PB3}} = 101.64/0.18$ |

|                            |                  |                                     | $M_{\rm NB3}=36.3/0.18$        |

|                            |                  | Buffer_4                            | $M_{PB4}=335/0.18$             |

|                            |                  |                                     | $M_{\rm NB4}{=}118.59/{0.18}$  |

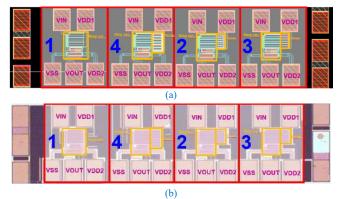

# IV. EXPERIMENTAL RESULTS AND FAILURE ANALYSIS

The baseline circuit and other three test circuits with different decoupling capacitors have been fabricated in a 0.18- $\mu$ m 1.8-V CMOS process. The illustration of layout top view and the optical microscope (OM) micrograph of the test chip are shown in Fig. 7. All the test circuits were fabricated in the same die, which was assembled in a 48-pin COB package for function verification and CDM ESD test, as shown in Fig. 8. In addition, the extra two pads in a pair with metal connected between them are placed on the left and right sides of the die. The pad pairs can be bonded with two wires in series between the pin of IC and the lead frame of the package to extend the length of bonding wire for testing with the increased parasitic inductance. After the CDM ESD tests are finished, the standby leakage current and electrical function verification are used to judge whether the device under test (DUT) is passed or failed.

Fig. 7. The illustrations of (a) layout top view and (b) optical microscope (OM) micrograph of the test circuits in a silicon chip. The numbers on the illustration are corresponding to the symbol numbers of test circuits in Table. II. The additional pad pairs at two sides are specially designed to extend the length of bonding wire for testing with the increased parasitic inductance.

Fig. 8. Wire bonding plan for the fabricated silicon chip with the test circuits. Bonding two wires in series to the pin of IC to extend the length of bonding wire for testing with increased inductance through the VDD1 extended pin.

# A. Function Verification

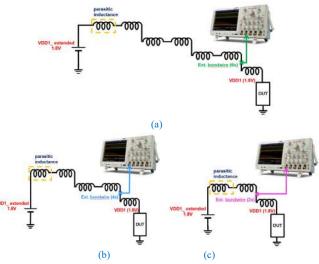

Before CDM ESD testing, the output functions of all test circuits were verified. In order to verify the effectiveness of the decoupling capacitors, the wire-bonding plan and measure setups for observing the transient/switching noise on the power line are shown in Fig. 9. The oscilloscope (MSO 5104) is connected at the VDD1\_extended pin to observe the transient/ switching noise that was generated by the ring oscillator of 173-stage inverter chain. To observe the power line noise induced by different lengths of bonding wires, Fig. 9(a) shows the

measurement setup for observing the power line noise induced by 6x bonding wires. The measurement setups for observing the power line noise induced by 4x and 2x bonding wires through VDD1 pin on IC and VDD1\_extended pin on the package are illustrated in Fig. 9(b) and Fig. 9(c), respectively.

Fig. 9. Measurement setups for observing the power line noise induced by (a) 6x extending bonding wires, (b) 4x extending bonding wires, and (c) 2x extending bonding wires, through VDD1 pin on IC and VDD1\_extended pin on the package.

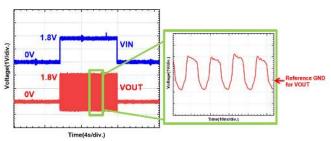

Fig. 10. Function verification on the fabricated test circuits. The ring oscillator starts to generate the clock-like output waveform (VOUT), when the input signal (VIN) is switched from 0V to 1.8V.

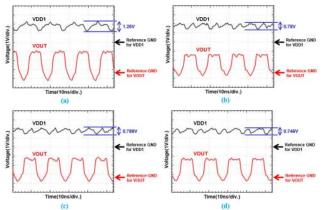

As the measured waveforms shown in Fig. 10, when the VIN pin is given with a logic high signal (1.8V), the ring oscillator starts to oscillate out a clock-like voltage waveform with a frequency of 81 MHz. The transient/switching noise on VDD1 (which supported the 1.8-V power source to the ring oscillator of 173-stage inverter chain) and the VOUT signal are probed and observed with the oscilloscope in Fig. 11 under the package condition of 2x bonding wires. In Fig. 11, the waveforms of power line noises on VDD1 without or with different decoupling capacitors are observed. As seen among Fig. 11(a) (the ring oscillator without decoupling capacitor) and Fig.  $11(b) \sim Fig.$ 11(d) (the ring oscillators with different decoupling capacitors), the power line peak-to-peak noise voltages on VDD1 in Fig.  $11(b) \sim Fig. 11(d)$  are indeed reduced, thus the effectiveness of the on-chip decoupling capacitor can be successfully verified. With the presence of decoupling capacitors, the power line peak-to-peak noise voltage is reduced from 1.26V to 0.78V (by varactor), 0.788V (by NMOS capacitor), and 0.746V (by NMOS capacitor with DNW). Among them, the test circuit of a ring oscillator with the decoupling capacitor of NMOS capacitor

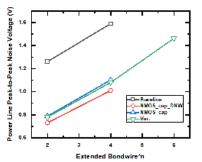

with DNW has the smallest value of the power line peak-to-peak noise voltage. The measurement results of four test circuits with different lengths of bonding wire are compared in Fig. 12, where the power line peak-to-peak noise voltage is increased as the bonding wire length increasing. The longer the bonding wire is, the larger the value of parasitic inductance, and hence a larger peak-to-peak noise voltage on the power line due to Ldi/dt effect is observed.

Fig. 11. The measured voltage waveforms on VDD1 and VOUT of the test circuits (a) without decoupling capacitor, (b) with decoupling capacitor of the varactor, (c) with decoupling capacitor of NMOS, and (d) with decoupling capacitor of NMOS with DNW.

Fig. 12. Comparisons among the measurement results of four test circuits without or with different decoupling capacitors under different lengths of bonding wires.

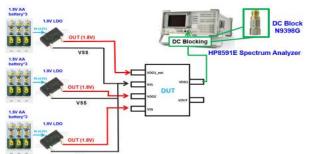

## B. Noise Measurement with Spectrum Analyzer

The spectrum analyzer (HP8591E) is applied to measure the power line noise spectrum waveform. To fully remove the noise from the machine of switch power supply that was supplied by the external electrical power source of AC 110V, the DUT is powered by the standalone batteries with 1.8-V LDO regulators. Three standalone batteries are connected in series to produce a 4.5-V DC voltage source, which is sent to the input of the LDO to produce a clean output voltage of 1.8V, as the setup shown in Fig. 13. The VDD1 pin of DUT is connected to the signal input of spectrum analyzer with a DC-blocking device (N9398G) to measure the transient/switching noise on VDD1. Between the pins of VDD1\_ext. and VDD1, there is the extending bonding wires, as that illustrated in Fig. 9.

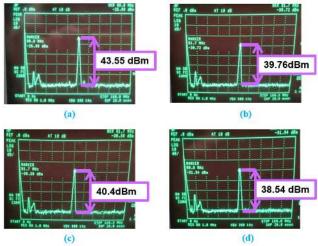

The measurement results from the spectrum analyzer are shown in Fig. 14 with the package condition of 2x bonding wires. Among Figs. 14(a) ~ 14(d), the x-axis represents frequency and the y-axis represents power spectrum. The peak tones of power line noise observed on VDD1 pins are all located at 81MHz, which is the output frequency of the ring oscillator built with

173-stage inverter chain. The measured power line noise spectrum on the ring oscillator without any decoupling capacitor is 43.55 dBm, as shown ion Fig. 14(a). The noise spectrums on the test circuits of ring oscillators added with decoupling capacitors by varactor, NMOS capacitor, and NMOS capacitor with DNW are 39.76 dBm, 40.4 dBm, and 38.54 dBm, respectively, as shown in Fig. 14(b)  $\sim$  Fig. 14(d). Among the results, the ring oscillator with decoupling capacitor of NMOS capacitor with DNW has the lowest transient/switching noise spectrum on VDD1.

Fig. 13. The setup to measure the power line noise spectrum by the spectrum analyzer. The DUT is powered by the clean 1.8-V voltage sources those generated from the standalone batteries with 1.8-V LDO regulators. The VDD1 pin is connected through a DC blocking component into the spectrum analyzer to observe the noise spectrum waveform on the VDD1 power line.

Fig. 14. The measured spectrum waveforms on the VDD1 power lines of the test circuits, (a) without decoupling capacitor, with decoupling capacitors of (b) varactor, (c) NMOS capacitor, and (d) NMOS capacitor with DNW. The x-axis represents frequency, and the y-axis represents power spectrum. The peak tones of power line noise on VDD1 are all located at 81 MHz.

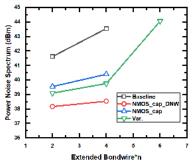

Fig. 15. Comparisons among the measured power line noise spectrums on the four test circuits without or with different decoupling capacitors under different lengths of bonding wires.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2021.3116961, IEEE Journal of the Electron Devices Society

Comparisons among the measured power line noise spectrums on the four test circuits without or with different decoupling capacitors under different lengths of bonding wires are shown in Fig. 15. It is observed that the power line noise spectrum is increased with the increasing length of bonding wires. The longer the bonding wire is, the larger the value of parasitic inductance, and hence a larger noise spectrum on the power line due to Ldi/dt effect is observed.

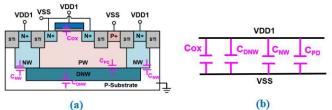

From the aforementioned experimental results, the ring oscillator with the decoupling capacitor of NMOS capacitor with DNW has a better performance on suppressing power line noise. Fig. 16(a) shows the cross-sectional view of the NMOS capacitor with DNW, where the NMOS capacitor are fully surrounded by the DNW and N-well (NW) layers with the additional parasitic reverse junction capacitance in parallel to the original Cox. By sorting out all the capacitive components between the VDD1 and VSS power rails, the equivalent schematic of decoupling capacitor is shown in Fig. 16(b). The total capacitance between VDD1 and VSS is increased from Cox to  $C_{ox} + C_{DNW} + C_{NW} + C_{PD}$ , where the  $C_{ox}$  represents the main capacitance (formed by the gate oxide) in the original NMOS capacitor, C<sub>DNW</sub> represents the reverse junction capacitor of DNW and P-substrate, C<sub>NW</sub> represents the reverse junction capacitor of NW and P-substrate, and CPD represents the reverse junction capacitor of P-well (PW) and DNW.

The value of each capacitive component is listed in Table V, which is calculated with the junction area and the relative process parameters. The  $C_{PD}$  component has a larger value than  $C_{DNW}$ , because the doping concentration of PW is higher than that of P-substrate. With the parasitic capacitive components added into the total capacitance, the NMOS capacitor with DNW results in a better performance on suppressing power line noise.

Fig. 16. (a) The cross-sectional view of the NMOS capacitor with DNW, and (b) the equivalent circuit to show the total capacitance between power lines.

TABLE V

THE CAPACITANCE OF COMPONENTS IN DECOUPLING CAPACITOR OF NMOS

CAPACITOR WITH DNW

| CAPACITOR WITH DIN W |                  |  |  |

|----------------------|------------------|--|--|

| Component            | Capacitance (pF) |  |  |

| Cox                  | 5.0488           |  |  |

| C <sub>NW</sub>      | 0.0677           |  |  |

| C <sub>DNW</sub>     | 0.3078           |  |  |

| CPD                  | 1.2296           |  |  |

## C. CDM ESD Robustness

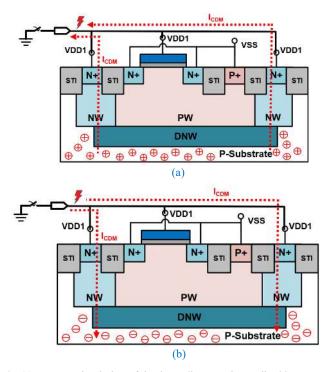

The CDM ESD test is performed by pointing the pogo pin to VDD1 pin with both positive and negative polarity stresses. The schematics of CDM ESD discharging with positive and negative polarities are shown in Figs. 17(a) and 17(b), respectively. The CDM ESD tester used in this work is Thermo Scientific Orion3. The failure criterion is defined as one of the electrical or function verification results out of specifications.

6

Fig. 17. Schematic diagrams to illustrate CDM ESD discharging on the VDD1 pin of the test chip under (a) positive, and (b) negative, CDM ESD polarities.

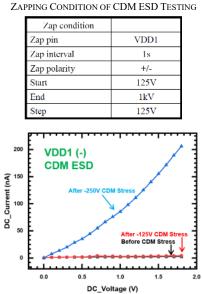

The CDM test is performed on the fabricated silicon chip with different test circuits (listed in Table II) inside a 48-pin COB package. The zapping condition of the CDM ESD test is shown in Table VI. For electrical verification, the failure criterion is defined as the I-V curve shifting over 30% from its initial curve, or the leakage current under 1.8-V bias increasing 10 times of magnitude from the initial leakage current before CDM stress. Fig. 18 shows the traced DC I-V characteristic on the test circuit of a ring oscillator with the decoupling capacitor of varactor before and after CDM ESD stress. The I-V curve after CDM stress of -250V shifts significantly, and the leakage current under 1.8-V bias increases over 10 times of magnitude.

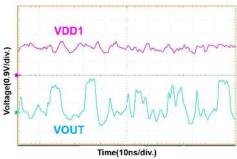

For function verification, the failure criterion is defined as the output function after CDM stress is incorrect or deviates from its original output waveform. For example, the measured output waveform of the ring oscillator with the decoupling capacitor of varactor after CDM stress of -250V is shown in Fig. 19. The output waveform has a significant deviation after CDM stress.

TABLE VI

Fig. 18. DC I-V characteristics on VDD1 of the test circuit with decoupling capacitor of varactor before and after CDM ESD stress.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2021.3116961, IEEE Journal of the Electron Devices Society

Fig. 19. The measured voltage waveform of VOUT in the test circuit with decoupling capacitor of varactor after CDM ESD stress of -250V, the output function is incorrect.

All measured results of four test circuits under CDM ESD stress are listed in Table VII, where if the DUT passed 125V qualification but failed at 250V, the CDM level is listed as 125V. The test circuits with decoupling capacitors show worse CDM ESD robustness than that of the baseline design (without decoupling capacitor), except for the ring oscillator with the decoupling capacitor realized by NMOS capacitor with DNW. The decoupling capacitor realized by NMOS capacitor with DNW can sustain higher CDM ESD robustness of over +/1 kV, whereas the decoupling capacitor realized by varactor (NMOS capacitor) can sustain CDM ESD stress of only +/-125V (+/-250V), respectively. In the test circuits, the gate length of the NMOS capacitor is longer than that of the varactor. With a longer channel length, the decoupling capacitor has a larger equivalent series resistance along its ESD discharging path, and thus the discharging peak current would be somewhat reduced to get a higher CDM ESD test result.

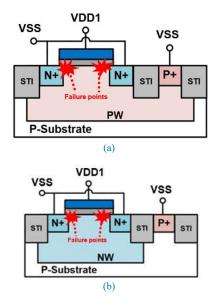

Fig. 20. Cross-sectional view of the decoupling capacitor realized by NMOS capacitor with DNW during (a) positive, and (b) negative, CDM ESD stressing on VDD1 pin. The CDM ESD current is discharged through the parasitic junction that formed between P-substrate and the DNW to result in a higher CDM ESD robustness.

TABLE VII

CDM TESTING RESULTS (PASS LEVEL) OF TEST CHIP

|                  | (                       | <i>,</i>         |                  |

|------------------|-------------------------|------------------|------------------|

| L                | Designs                 | Positive CDM (V) | Negative CDM (V) |

| (1) Baseline     | ring osc. only          | Over 1k          | Over -1k         |

| (2) Var.         | ring osc. + Varactor    | 125              | -125             |

| (3) NMOS_cap     | ring osc. + NMOS        | 250              | -250             |

| (4) NMOS_cap_DNW | ring osc. + NMOS w/ DNW | Over 1k          | Over -1k         |

|                  | (DNW is biased at VDD1) |                  |                  |

From the illustration in Fig. 20(a) under positive CDM stress on VDD1 pin, with the presence of DNW and NW layers surrounding the whole NMOS capacitor, the CDM ESD current can be discharged through the parasitic junction that formed between P-substrate and the DNW to reduce the probability of ESD damage on the thin gate oxide layer of NMOS capacitor. Therefore, it results in higher CDM ESD robustness than that of the other two designs with decoupling capacitors realized by of varactor and NMOS capacitor. The CDM ESD discharging path under negative CDM stress on VDD1 pin was also illustrated in Fig. 20(b). The results of using DNW to improve CDM ESD robustness were ever reported in several prior works [18], [19].

#### D. Failure Analysis

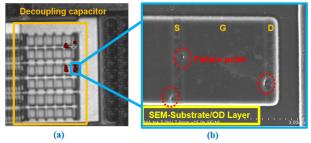

The electrical failure analysis (EFA) is performed with InfraRed Optical Beam Induced Resistance Change (IR-OBIRCH) to locate the failure point. By scanning and heating through the surface of voltage-applied IC with an IR-laser, the position of impedance variation different from other regions has a higher probability to be considered as the abnormal failure point.

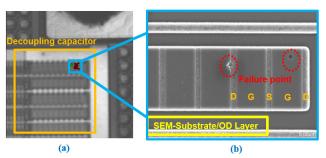

As shown in Fig. 21(a) and Fig. 22(a), the failure points are detected and located on the decoupling capacitors realized by NMOS capacitor and varactor, after -500V / +500V CDM stress on VDD1, respectively. The failure spots were observed by IR-OBIRCH, when the test circuits were with 1.8-V bias at VDD1 in the off state of the ring oscillator (VIN=0V). According to the IR-OBIRCH failure locations, the physical failure analysis (PFA), as those shown in Fig. 21(b) and Fig. 22(b), on the decoupling capacitors of NMOS capacitor and varactor is performed with de-layer and Scanning Electron Microscope (SEM), respectively. With the inspection of contact anomalies and poly profile by High Acceleration Voltage (HKV) SEM, it is clearly observed that the failure points are on the gate oxide or on the source/drain edges near to the gate oxide. The source/drain regions of the NMOS capacitor and varactor are directly connected to VSS to form the decoupling capacitor. Such failure locations can be confirmed due to the gate oxide breakdown causing by CDM ESD stress, as illustrated in Fig.23.

Fig. 21. Failure analysis results of the ring oscillator with decoupling capacitor of NMOS capacitor. The (a) EFA and (b) SEM results after -500V CDM stress on the VDD1 pin are shown.

Fig. 22. Failure analysis results of the ring oscillator with decoupling capacitor of the varactor. The (a) EFA and (b) SEM results after +500V CDM stress on the VDD1 pin are shown.

Fig. 23. Cross-sectional view to illustrate the failure location on the gate oxide of (a) NMOS capacitor and (b) varactor, after the CDM ESD stress.

# V. CONCLUSIONS

CDM ESD threats on the on-chip decoupling capacitors realized by three different decoupling capacitors have been investigated and verified in silicon chip fabricated by a 0.18µm CMOS technology. The measured results on the power line transient/switching noises and CDM ESD robustness have revealed that the NMOS capacitor surrounding with DNW is the best solution to realize the decoupling capacitor. In addition, the IR-OBIRCH and the de-layer SEM results showed that the decoupling capacitors realized by varactor or NMOS capacitor are very sensitive to gate oxide damage during CDM ESD stresses. The comprehensive study results of this work can be really benefit and helpful to IC designers on how to optimize the on-chip decoupling capacitors with higher CDM ESD robustness.

#### References

W. Kim, "Estimation of simultaneous switching noise from frequency-domain impedance response of resonant power distribution networks," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 1, no. 9, pp. 1359-1367, Sept. 2011, doi: 10.1109/ TCPMT.2011.2157503. [2] T. Charania, A. Opal, and M. Sachdev, "Analysis and design of on-chip decoupling capacitors," *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 21, no. 4, pp. 648-658, Apr. 2013, doi: 10.1109/TVLSI.2012.2198501.

8

- [3] C. -Y. Hsueh and M. -D. Ker, "Stacking-MOS protection design for interface circuits against cross-domain CDM ESD stresses," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 1461-1470, Apr. 2021, doi: 10.1109/TED.2021.3061325.

- [4] S. Chen et al., "Local CDM ESD protection circuits for crosspower domains in 3D IC applications," *IEEE Trans. Device Mater. Rel.*, vol. 14, no. 2, pp. 781-783, Jun. 2014, doi: 10.1109/ TDMR.2014.2320538.

- [5] P. Peng et al., "Low-capacitance SCR for on-chip ESD protection with high CDM tolerance in 7nm bulk FinFET technology," in *Proc. 41st Elect. Overstress/Electrostatic Discharge (EOS/ESD) Symp.*, 2019, pp. 1-5, doi: 10.23919/EOS/ESD.2019.8869982.

- [6] C. Troussier, J. Bourgeat, E. Simeu, J.-D. Arnould, J. Jimenez, and B. Jacquier, "Study of inter-power domain failures during a CDM event," in *Proc. 42nd Elect. Overstress/Electrostatic Discharge (EOS/ESD) Symp.*, 2020, pp. 1-5.

- [7] N. Olson, V. Shukla, and E. Rosenbaum, "Test chip design for study of CDM related failures in SoC designs," in *Proc. Int. Rel. Phys. Symp.*, 2011, pp. 719–724, doi: 10.1109/IRPS.2011. 5784566.

- [8] C.-Y. Lin and M.-D. Ker, "CDM ESD protection design with initial-on concept in nanoscale CMOS process," in *Proc. 17th Int. Symp. Phys. Failure Anal. Integr. Circuits*, 2010, pp. 1-4, doi: 10. 1109/IPFA.2010.5532223.

- [9] X. Meng, K. Arabi, and R. Saleh, "Novel decoupling capacitor designs for sub-90nm CMOS technology," in *Proc. 7th Int. Symp. Quali. Electron. Des.*, 2006, pp. 266-271, doi: 10.1109/ISQED. 2006.93.

- [10] J.-H. Lee, J. R. Shih, H. P. Kuan, and K. Wu, "The influence of decoupling capacitor on the discharge behavior of fully silcided power-clamped device under HBM ESD event," in *Proc. 17th Int. Symp. Phys. Failure Anal. Integr. Circuits*, 2010, pp. 1-5, doi: 10.1109/IPFA.2010.5532248.

- [11] X. Liu, W. Beyene, S. Sivarajah, and J. Jiang, "Optimizing onchip decoupling capacitors to improve power supply noise induced jitter and ESD robustness," in *Proc. IEEE 71st Electron. Compon. Technol. Conference*, 2021, pp. 1211-1218, doi: 10.1109/ECTC32696.2021.00198.

- [12] B. Boesman, D. Pissoort, G. Willems, A. Carton, and D. Vanoost, "Modeling the low- and high-frequency impedance of thermal reliefs," in *Proc. Int. Symp. Electromagn. Compat.*, 2013, pp. 138-142.

- [13] Electrostatic Discharge (ESD) Sensitivity Testing: Charged Device Model (CDM)-Device Level, ESD Association, Standard ANSI/ESDA/JEDEC JS-002-2018, 2018

- [14] N. Sasaki, "Higher harmonic generation in CMOS/SOS ring oscillators," *IEEE Trans. Electron Devices*, vol.29, no. 2, pp. 280-283, Feb. 1982, doi: 10.1109/T-ED.1982.20696.

- [15] B. Pontikakis, F.-R. Boyer, and Y. Savaria, "A 0.8V algorithmically defined buffer and ring oscillator low-energy design for nanometer SoCs," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2006, pp. 1259-1262, doi: 10.1109/ISCAS.2006.1692821.

- [16] J.-S. Choi and K. Lee, "Design of CMOS tapered buffer for minimum power-delay product," *IEEE J. of Solid-State Circuits*, vol. 29, no. 9, pp. 1142-1145, Sept. 1994, doi: 10.1109/4.309912.

- [17] P. Larsson, "Parasitic resistance in an MOS transistor used as onchip decoupling capacitance," *IEEE J. of Solid-State Circuits*, vol. 32, no. 4, pp. 574-576, Apr. 1997, doi: 10.1109/4.563679.

- [18] J.-H. Lee, J.-R. Shih, S. Guo, D.-H. Yang, J.F. Chen, D. Su, and K. Wu, "The study of sensitive circuit and layout for CDM improvement," in *Proc. 16th Int. Symp. Phys. Failure Anal.*

Integr. Circuits, 2009, pp. 228-232, doi: 10.1109/IPFA.2009. 5232664.

[19] M.-D. Ker, C.-Y. Lin, and T.-L. Chang, "Layout styles to improve CDM ESD robustness of integrated circuits in 65-nm CMOS process," in *Proc. Int. Symp. VLSI Des. Auto. Test*, 2011, pp. 1-4, doi: 10.1109/VDAT.2011.5783551.

**Yi-Chun Huang** received the B.S. degree from the Department of Electronic Engineering, National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 2020. She is currently working toward the M.S. degree on the topic of circuit design for ESD protection with the Institute of Electronics, National Yang Ming Chiao Tung University, Hsinchu, Taiwan.

Ming-Dou Ker (Fellow, IEEE) received the Ph. D. degree from the Institute of Electronics, National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1993. Now, he is the Distinguished Professor in the Institute of Electronics, National Yang Ming Chiao Tung University (NYCU), Hsinchu, Taiwan, and also the Director of *Biomedical Electronics Translational Research Center*, NYCU,

working on biomedical electronics translational projects. In the technical field of reliability and quality design for microelectronic circuits and systems, he has authored/co-authored over 600 technical papers in international journals and conferences. He has proposed many solutions to improve the reliability and quality of integrated circuits, which have been granted with hundreds of U.S. patents. He had been invited to teach and/or to consult the reliability and quality design by hundreds of design houses and semiconductor companies in the worldwide IC industry. Some of his inventions or designs had been widely used in the modern IC products and electronic systems. His current research interests include the reliability and quality design for nanoelectronics and gigascale systems, as well as the circuits and systems for biomedical applications.

Prof. Ker had served as member of the Technical Program Committee and the Session Chair of numerous international conferences for many years, including IEEE Symp. on VLSI Circuits, IEEE International Solid-State Circuits Conference (ISSCC), IEEE International Symp. on Circuits and Systems (ISCAS), and IEEE International Reliability Physic Symp. (IRPS). He ever served as the Distinguished Lecturer in the IEEE Circuits and Systems Society (2006–2007) and in the IEEE Electron Devices Society (2008–2020). He ever served as Associate Editor of IEEE Transactions on VLSI Systems, Associate Editor of IEEE Transactions on Biomedical Circuits and Systems (TBioCAS), and the Guest Editor of ISCAS2019 Special Issue in TBioCAS. He was the Founding President of Taiwan ESD Association, and the 3rd President of Taiwan Engineering Medicine Biology Association. He ever served as the Vice-President of IEEE Taipei Section. Currently, he is serving as the Editor of IEEE Trans. on Device and Materials Reliability, Editor of IEEE Journal of the Electron Devices Society, and a Guest Editor for Frontiers in Neuroscience on the research topic of microelectronic implants for central and peripheral nervous system.