# Study on on-Chip Antenna Design Based on Metamaterial-Inspired and Substrate-Integrated Waveguide Properties for Millimetre-Wave and THz Integrated-Circuit Applications

Mohammad Alibakhshikenari<sup>1</sup> · Bal S. Virdee<sup>2</sup> · Ayman Abdulhadi Althuwayb<sup>3</sup> · Sonia Aïssa<sup>4</sup> · Chan H. See<sup>5</sup> · Raed A. Abd-Alhameed<sup>6</sup> · Francisco Falcone<sup>7,8</sup> · Ernesto Limiti<sup>1</sup>

Received: 5 September 2019 / Accepted: 12 October 2020 / Published online: 26 October 2020 The Author(s) 2020

### Abstract

This paper presents the results of a study on improving the performance parameters such as the impedance bandwidth, radiation gain and efficiency, as well as suppressing substrate loss of an innovative antenna for on-chip implementation for millimetre-wave and terahertz integrated-circuits. This was achieved by using the metamaterial and the substrate-integrated waveguide (SIW) technologies. The on-chip antenna structure comprises five alternating layers of metallization and silicon. An array of circular radiation patches with metamaterial-inspired crossed-shaped slots are etched on the top metallization layer below which is a silicon layer whose bottom surface is metalized to create a ground plane. Implemented in the silicon layer below is a cavity above which is no ground plane. Underneath this silicon layer is where an open-ended microstrip feedline is located which is used to excite the antenna. The feed mechanism is based on the coupling of the electromagnetic energy from the bottom silicon layer to the top circular patches through the cavity. To suppress surface waves and reduce substrate loss, the SIW concept is applied at the top silicon layer by implementing the metallic via holes at the periphery of the structure that connect the top layer to the ground plane. The proposed on-chip antenna has an average measured radiation gain and efficiency of 6.9 dBi and 53%, respectively, over its operational frequency range from 0.285–0.325 THz. The proposed on-chip antenna has dimensions of  $1.35 \times 1 \times 0.06$  mm<sup>3</sup>. The antenna is shown to be viable for applications in millimetre-waves and terahertz integrated-circuits.

**Keywords** On-chip antenna  $\cdot$  Terahertz (THz) integrated circuits  $\cdot$  Metamaterial (MTM)  $\cdot$  Substrate-integrated waveguide (SIW)  $\cdot$  Silicon process  $\cdot$  Millimetre-waves (mm-waves)  $\cdot$  Antenna feed mechanism

Mohammad Alibakhshikenari alibakhshikenari@ing.uniroma2.it

Extended author information available on the last page of the article

## 1 Introduction

This is an era of millimetre-wave (mm-wave) and terahertz (THz) wireless communications, which is necessary to deliver multi-Gbps data rates using standard, low-cost integrated-circuit technology. The THz regime of the electromagnetic spectrum is located between the micro-wave and optical frequencies and normally defined as the band from 0.1 to 10 THz [1–3]. Currently, the industry is commercializing the unlicensed 60-GHz wireless band (e.g. IEEE 802.11ad/WiGig) for indoor short-range communication networks [1–5]. The atmospheric attenuation property of 60 GHz was one of the driving forces for regulatory agencies such as the U.S. FCC to unlicense the multi-GHz of bandwidth at 60 GHz [6]. Beyond 60 GHz, more research is needed on how to design and develop THz on-chip antennas [7–12].

Active components functioning at mm-wave and THz circuits are highly integrated except for the antennas [13, 14]. Antenna integration is of great importance [15, 16]. At these frequencies, the antennas need to be assembled using expensive high-frequency ground-signal-ground (GSG) probes, bulky waveguides and horn antennas, which is not conducive for mass production and future industrial application. For high-efficiency and gain, the off-chip antenna in the package design is usually fabricated on either the printed circuit board (PCB) [17], low-temperature cofired ceramic (LTCC) [15] or low-loss materials [17]. At mm-wave and THz frequencies, the interconnect loss of the packaging is significant (~2 dB at 60 GHz) because of the incompatibility of the antennas and the silicon-based active circuits [18–21].

In this paper, an on-chip antenna design is presented for millimetre-wave and THz applications that is constructed from five alternating layers of metallization and silicon. The antenna's performance in terms of impedance bandwidth, radiation gain and efficiency is enhanced by employing the metamaterial (MTM)-inspired technology [22–24]. Surface waves and loss in the silicon substrate are mitigated using substrate-integrated waveguide (SIW) technology [25, 26]. A simple method based on an open-ended microstrip line is employed to excite the antenna. The next section describes the on-chip antenna structure design along with the simulated and measured results, and the paper is finally concluded.

### 2 High-Performance on-Chip Antenna for Applications in mm-Wave and THz Integrated Circuits

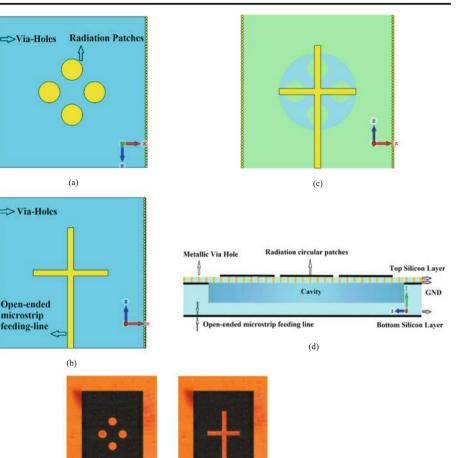

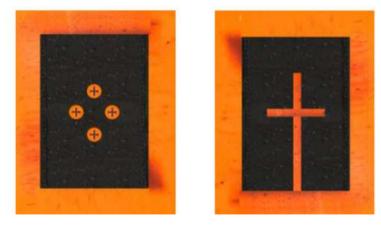

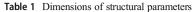

Configuration of the reference on-chip antenna in Fig. 1 comprises five layers consisting of metallization-silicon-metallization-metallization. The silicon layers have a dielectric constant of 11.7 and a loss tangent of 0.00025 [27]. The overall fabrication process used here is based on CMOS technology. Fabricated in the top silicon layer are four conventional circular radiation patches. The conductive material used for the radiation patches and the ground plane is aluminium. A circular cavity is created in the bottom silicon layer under the four circular patches, and the ground plane over this region is removed. The patches are excited by an open-ended microstrip line in the form of a cross-shaped line that is constructed on the backside of the bottom silicon layer. In this way, the four circular patches on the top layer are aligned with the feedline to maximize coupling. The feeding mechanism is based on coupling the electromagnetic energy from the bottom silicon layer to the top radiation patches through the cavity whose dominant resonance mode is  $TE_{11\delta}^2$ . The proposed feed mechanism improves the antenna's impedance matching and consequently its impedance bandwidth and

Fig. 1 Configuration of the proposed reference on-chip antenna. **a** Top view. **b** Back view. **c** View showing relative positions of the feeding line on the bottom layer, the radiation patches on the top layer and the cavity in the bottom silicon substrate. The cross-shaped feedline is located under the radiation patches to maximize coupling. **d** Cross-section view showing the various layers of the on-chip antenna structure. **e** Fabricated prototype, top view (left side) and back view (right side)

radiation characteristics. The periphery of the top silicon layer is punctuated with metallic via holes to actualize substrate-integrated waveguide (SIW) and thereby suppress surface waves and minimize substrate loss. The analysis showed that the radius of the metallic via holes and their spacing from each other are very important to realize low substrate loss and suppress surface waves. The radius of the via holes and their separation were 9.0  $\mu$ m and 3.5  $\mu$ m, respectively.

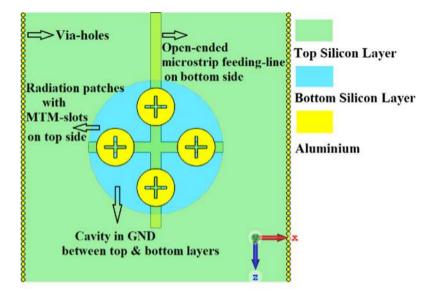

To increase the performance of the antenna, its effective aperture area is enlarged without affecting its physical size by applying the metamaterial concept, as illustrated in Fig. 2. In this approach, an optimized cross-shaped slot is created inside each circular patch. The periodic array of subwavelength slots act like resonators or scatters that exhibits metamaterial left-handed properties (negative refractive index) when interacting with EM fields. The resulting

structure is referred to as a metasurface, which is a 2D form of a metamaterial [28–30]. The effective permittivity ( $\varepsilon$ ) and effective permeability ( $\mu$ ) of the metamaterials when analysed using the retrieval extraction algorithm show the structure exhibits negative permittivity over the frequency range of interest, which is a unique characteristic of metamaterials. The physical parameters of the proposed on-chip antenna for optimum performances over 0.285 THz to 0.325 THz are tabulated in Table 1.

The proposed structure was modelled and simulated using CST microwave studio, which is a 3D electromagnetic solver based on the finite integration technique. The antenna was then fabricated to validate its performance. The antenna's feedline was excited using WR3

(a)

(b)

Fig. 2 Proposed on-chip antenna with metamaterial-inspired crossed-shaped slot implemented on the radiation patches. a Simulated layout (top view). b Fabricated prototype, top view (left side) and back view (right side)

| $1350\times1000\times60~\mu m^3$ |

|----------------------------------|

| 5 µm                             |

| 50 μm                            |

| 5 μm                             |

| 400 µm                           |

| 9 μm                             |

| 3.5 µm                           |

| 70 µm                            |

| 85 μm                            |

| 10 µm                            |

| 1100 µm                          |

| 100 µm                           |

|                                  |

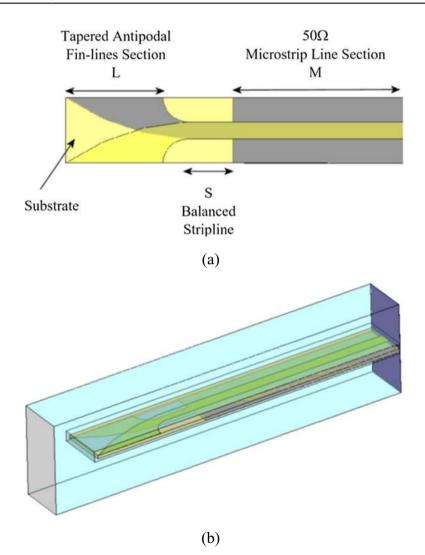

Fig. 3 Antipodal fin-line transition (a) consists of three sections: fin-line tapers L, balanced microstrip S and microstrip line M. The antipodal fin-line transition is located at the centre line of the waveguide broad walls (b)

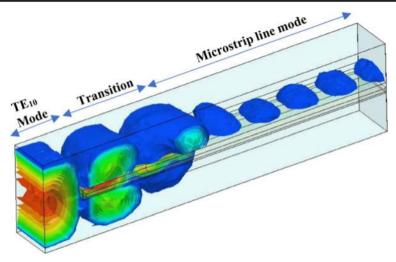

Fig. 4 E-field distribution at 0.305 THz. The  $TE_{10}$  mode entering the transition from left is split, rotated and finally matched to the microstrip quasi-TEM mode

transition using in-line fin-lines. By using antipodal fin-lines, shown in Fig. 3, a wide range of impedance values can be realized. The impedance match can be accomplished by tuning the fin-line dimensions (L and S) and by tapering the two fins to form a microstrip signal line and ground plane, respectively. The tapered fins gradually allow a change from the rectangular waveguide impedance to the microstrip impedance. Hence, the length and shape of the taper determine reflection and operating bandwidth.

A 3D plot of the E-field relative to the transition mechanism of antipodal fin-line at 0.305 THz is shown in Fig. 4 highlighting the E-field intensity pattern in the three cascaded sections. The waveguide  $TE_{10}$  mode, coupled to the structure as its input, splits at the fin-line taper point and finally converts into the microstrip line mode.

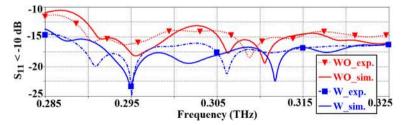

The simulated and measured reflection-coefficient response of the reference antenna with no MTM and the proposed antenna with MTM-inspired cross-shaped slots are shown in Fig. 5. It is evident that with MTM, the impedance match and impedance bandwidth are significantly improved. The proposed structure is shown to effectively operate over the frequency range from 0.285 to 0.325 THz for  $S_{11} < -15$  dB, which corresponds to a fractional bandwidth of 13.11%.

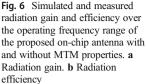

The simulated and measured radiation gain and efficiency performances of the reference antenna with no MTM and the proposed antenna with MTM are shown in Fig. 6. It is evident that the proposed antenna structure with MTM properties exhibits improvement in the

Fig. 5 Simulated (sim.) and experimental (exp.) reflection-coefficient responses of the reference antenna with no MTM (WO) and proposed on-chip antennas with MTM (W)

measured gain by 2.4 dBi and radiation efficiency by 14%, which is achieved with no increase in the antenna's physical dimensions. The measured average radiation gain and efficiency of the proposed on-chip antenna operating between 0.285 THz and 0.325 THz are 6.9 dBi and 53%, respectively. The performance characteristics of the reference and proposed antenna are

Table 2

Measured radiation gain and efficiency performance of the on-chip antennas with and without MTM-inspired technology

| Reference on-chip antenna without MTM properties |                   |

|--------------------------------------------------|-------------------|

| Min. gain & efficiency @ 0.325 THz               | 3.65 dBi & 33.12% |

| Max. gain & efficiency @ 0.305 THz               | 5.33 dBi & 46.43% |

| Ave. gain & efficiency (0.285 THz-0.325 THz)     | 4.5 dBi & 39%     |

| Proposed on-chip antenna with MTM properties     |                   |

| Min. gain & efficiency @ 0.285 THz               | 5.86 dBi & 44.10% |

| Max. gain & efficiency @ 0.305 THz               | 8.05 dBi & 62.95% |

| Ave. gain & efficiency (0.285 THz–0.325 THz)     | 6.9 dBi & 53%     |

| Improvements after applying MTM properties       |                   |

| Min. gain & efficiency                           | 2.21 dBi & ~11%   |

| Max. gain & efficiency                           | 2.72 dBi & 16.52% |

| Ave. gain & efficiency                           | 2.4 dBi & 14%     |

summarized in Table 2. There is good coherence between the simulation and the measurement in results presented in Figs. 5 and 6, and the discrepancy can be attributed to several factors,

(b)

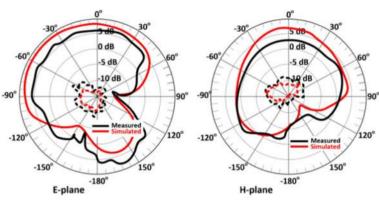

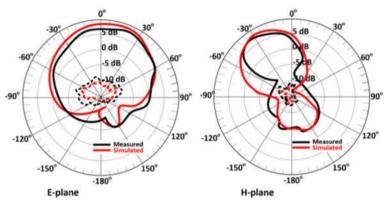

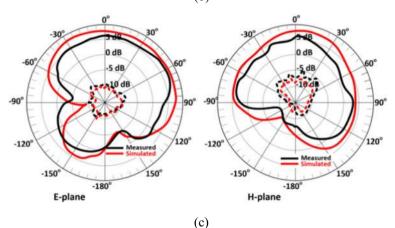

Fig. 7 Simulated and measured E-plane and H-plane radiation patterns of the proposed metamaterial on-chip antenna at various spot frequencies in the antenna's operating frequency range. Solid lines represent co-polarization, and dotted lines represent cross-polarization. **a** 0.285 THz. **b** 0.305 THz. **c** 0.325 THz

| Ref.              | Antenna type                                                       | Operation mode         Freq./BW         Gain (dBi)         Eff. (%)         Fab.           (GHz/%)         (GHz/%)         proce | Freq./BW<br>(GHz/%) | Gain (dBi) | Eff. (%) | Fab.<br>process | DR<br>material εr | DR type     | Size (mm <sup>2</sup> ) | Height<br>(mm) |

|-------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|----------|-----------------|-------------------|-------------|-------------------------|----------------|

| [7]               | Patch fed higher order mode DRA                                    | $\mathrm{TE}_{\delta 17}$                                                                                                        | 341 /7              | 7.9        | 74       | 0.18-µm SiGe    | 11.9              | Rectangular | 0.2                     | 0.5            |

| 8                 | On-chip 3D (Yagi-like concept)                                     | TE <sub>116</sub>                                                                                                                | 340/12              | 10         | 80       | 0.13-µm SiGe    | 10                | Rectangular | 0.49                    | 0.43           |

| [10]              | Slot-loaded magnetic loop on SIW                                   | I                                                                                                                                | 340/7               | 3.3        | 45       | 0.13-µm SMOS    | NA                | NA          | 0.49                    |                |

| [31]              | Patch                                                              |                                                                                                                                  | 280/2.5             | -1.6       | 21       | 0.13-µm CMOS    | NA                | NA          | 0.2                     |                |

| [32]              | Ring antenna                                                       |                                                                                                                                  | 296/-               | 4.2        |          | 65-nm CMOS      | NA                | NA          | 0.3                     |                |

| [33]              | Slot ring antenna + superstrate                                    |                                                                                                                                  | 375/8               | 1.6        |          | 45-nm CMOS SOI  | NA                | NA          | 0.05                    |                |

| [34]              | Ring antenna with silicon lens                                     |                                                                                                                                  | 288/NA              | 18.3       |          | 65-nm CMOS      | NA                | NA          | 12.56                   | 2.55           |

| [ <b>35</b> ] - a | Half-mode cavity fed DRA                                           | $TE_{\delta 11}$                                                                                                                 | 135/13              | 3.7        |          | 0.18-µm CMOS    | 10                | Rectangular | 0.63                    | 0.25           |

| [ <b>35</b> ] - b | Half-mode cavity fed higher order mode DRA                         | $TE_{\delta 13}/TE_{\delta 15}$                                                                                                  | 135/7               | 6.2/7.5    | 46/42    | 0.18-µm CMOS    | 10                | Rectangular | 0.72                    | 1.3/2.2        |

| [36]              | Slot fed stacked DRA                                               | $TE_{\delta 11}$                                                                                                                 | 130/11              | 4.7        |          | 0.18-µm CMOS    | 10                | Rectangular | 0.72                    | 1.5            |

| [37]              | DRA                                                                | $TE_{\delta 11}$                                                                                                                 | 135/11              | 2.7        |          | 0.18-µm CMOS    | 10                | Rectangular | 0.72                    | 0.6            |

| This Work         | This Work MTM & SIW                                                | $\mathrm{TE}_{11\delta}$                                                                                                         | 305/13.11           | 8.05       |          | 0.13-µm CMOS    | NA                | NA          | 2.35                    | 0.06           |

| Note: DR re       | Note: DR represents dielectric resonator, and NR is not applicable | cable                                                                                                                            |                     |            |          |                 |                   |             |                         |                |

Table 3 Comparison of the proposed on-chip antenna with the recent publications

namely, imprecise simulation models at terahertz, fabrication tolerances and unwanted signal reflections from surrounding objects during measurements.

The simulated and measured E-plane and H-plane radiation patterns of the proposed metamaterial on-chip antenna at spot frequencies of 0.285, 0.305 and 0.325 THz are shown in Fig. 7. This figure shows that in the E-plane, the 3-dB beamwidth narrows at the mid-band frequency of 0.305 THz. It also shows the radiation in the E-plane rotates by 90° in the clockwise direction from 0.285 to 0.305 THz, and again from 0.305 to 0.325 THz. In the H-plane, the beamwidth narrows significantly in the mid-band frequency of 0.325 THz.

Table 3 compares the characteristics of the proposed on-chip antenna with other techniques. With the proposed technique a better factional bandwidth can be achieved. The gain and efficiency of the proposed antenna is comparable to other techniques and in some cases better. In addition, compared to previously reported on-chip antenna designs, the proposed design is of a simpler structure and easy to fabricate at low cost, which makes it viable for mass production.

#### 3 Conclusion

The feasibility of the proposed metamaterial-inspired antenna is demonstrated for on-chip applications at the lower end of the THz region. The novelty introduced includes (i) the feed mechanism for effective coupling of electromagnetic energy from the bottom layer to the top radiation patches; (ii) combining metamaterial-inspired and SIW technologies to improve the antenna's performance parameters while preserving its physical dimensions and (iii) using stacked layers to create a highly compact on-chip antenna structure. The proposed silicon-based antenna structure provides low integration loss and is relatively simple to design and fabricate and therefore a promising candidate in the millimetre-wave and terahertz integration applications.

**Funding** Open access funding provided by Università degli Studi di Roma Tor Vergata within the CRUI-CARE Agreement. This work is partially supported by RTI2018-095499-B-C31, Funded by Ministerio de Ciencia, Innovación y Universidades, Gobierno de España (MCIU/AEI/FEDER, UE), innovation programme under grant agreement H2020-MSCA-ITN-2016 SECRET-722424 and the financial support from the UK Engineering and Physical Sciences Research Council (EPSRC) under grant EP/E022936/1.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

### References

T. S. Rappaport et al., "State of the art in 60-GHz integrated circuits and systems for wireless communications," Proceedings of the IEEE, vol. 99, no. 8, Aug. 2011, pp. 1390–1436.

- C. Doan et al., "Millimeter-wave CMOS Design," IEEE Journal of Solid-State Circuits, vol. 40, no. 1, Jan. 2005, pp. 144–155.

- A. Babakhani et al., "A 77-GHz phased-array transceiver with on-chip antennas in silicon: Receiver and antennas," IEEE Journal of Solid-State Circuits, vol. 41, no. 12, Dec. 2006, pp. 2795–2806.

- E. Seok et al., "A 410 GHz CMOS push-push oscillator with an on-chip patch antenna," in 2008 IEEE International Solid-State Circuits Conference (ISSCC), 3-7 Feb. 2008, pp. 472–629.

- R. Daniels et al., "60 GHz wireless: up close and personal," IEEE Microwave Magazine, vol. 11, Dec. 2010, pp. 44–50.

- F. Gutierrez et al., "On-chip integrated antenna structures in CMOS for 60 GHz WPAN systems," IEEE Journal on Selected Areas in Communications, vol. 27, Oct. 2009, pp. 1367–1378.

- C.-H. Li and T.-Y. Chiu, "340-GHz low-cost and high-gain on-chip higher order mode dielectric resonator antenna for THz applications," IEEE Trans. THz Sci. Technol., vol. 7, no. 3, May. 2017, pp. 284–294.

- X.-D. Deng, Y. Li, C. Liu, W. Wu and Y. -Z. Xiong , "340 GHz on-chip 3-D antenna with 10 dBi gain and 80% radiation efficiency," IEEE Trans. THz Sci. Technol., vol. 5, no. 4, July. 2015, pp. 619–627

- X.-D. Deng, Y. Li, H. Tang, W. Wu and Y. -Z. Xiong, "Dielectric loaded endfire antennas using standard silicon technology," IEEE Trans. Ant. Propag., vol. 65, no. 6, Jun. 2017, pp. 2797-2807

- X.-D. Deng, Y. Li, W. Wu and Y. -Z. Xiong, "340-GHz SIW cavity-backed magnetic rectangular slot loop antennas and arrays in silicon technology," IEEE Trans. Ant. Propag., vol. 63, no. 12, Dec. 2015, pp. 5272-5279.

- Z. Hou, Y. Yang, X. Zhu, S. Liao, M. Shum and Q. Xue, "A 320 GHz On-Chip Slot Antenna Array Using CBCPW Feeding Network in 0.13-µm SiGe Technology," IEEE MTT-S Int. Microwave Symposium, Honolulu, Hawaii, Jun. 2017.

- S. Hu, Y.-Z. Xiong, B. Zhang, L. Wang, T.-G. Lim, M. Je and M. Madihian, "A SiGe BiCMOS transmitter/ receiver chipset with on-chip SIW antennas for terahertz applications," IEEE Jour. Solid-State Cir., vol. 47, no. 11, Nov. 2012, pp. 2654-2664.

- A. Tomkins, R. A. Aroca, T. Yamamoto, S. T. Nicolson, Y. Doi, and S. P. Voinigescu, "A zero-IF 60 GHz 65 nm CMOS transceiver with direct BPSK modulation demonstrating up to 6 Gb/s data rates over a 2 m wireless link," IEEE J. Solid-State Circuits, vol. 44, Aug. 2009, pp. 2085-99.

- S. T. Nicolson, P. Chevalier, B. Sautreuil, and S. P. Voinigescu, "Single-chip W-band SiGe HBT transceivers and receivers for Doppler radar and millimeter-wave imaging," IEEE J. Solid-State Circuits, vol. 43, Oct. 2008, pp. 2206-2217.

- Y. P. Zhang, M. Sun, K. M. Chua, L. L. Wai, and L. Duixian, "Antenna-in-package design for wire bond interconnection to highly integrated 60-GHz radios," IEEE Trans. Antennas and Propag., vol.57, Oct. 2009, pp. 2842-2852.

- S. Hu, Y. Z. Xiong, L. Wang, D. Hou, and T. G. Lim, "A low-cost high-gain antenna array and its integration with active circuits," IEEE Electrical Design of Advanced Packag. Systems Symp., Dec. 2010.

- U. R. Pfeiffer, J. Grzyb, L. Duixian, B. Gaucher, T. Beukema, B. A. Floyd, and S. K. Reynolds, "A chipscale packaging technology for 60-GHz wireless chipsets," IEEE Trans. Microw. Theory Tech., vol.54, Aug. 2006, pp. 3387-3397.

- J. Li, Y. Z. Xiong, S. Hu, W. L. Goh, D. Hou, and W. Wu, "Performance analyse on millimetre-wave bonding-wire interconnection," IEEE Electrical Design of Advanced Package. Systems Symp., Dec. 2010.

- B. Y. Y. Liu, Y. Ye, J. Ren, X. Liu, and Q. J. Gu, "High efficiency micromachined sub-THz channels for low cost interconnect for planar integrated circuits," IEEE Trans. on Microwave Theory and Techniques, vol.64, no.1, Jan. 2016, pp.96-105.

- B. Y. Y. Liu, Y. Ye, X. Liu, and Q. J. Gu, "Low-loss and broadband G-band dielectric interconnect for chipto-chip communication," IEEE Microwave & Wireless Components, vol.26, no.7, July 2016, pp.478-480.

- U. Dey and J. Hesselbarth, "Millimeter-wave multicast chip-to-chip interconnect network using dielectric slab waveguide," IEEE/MTT-S Int. Microwave Symp., 10-15 June 2018, Philadelphia, PA, USA.

- Yuandan Dong, and Tatsuo Itoh, "Metamaterial-Based Antennas", Proceedings of the IEEE, Vol. 100, No. 7, July 2012, pp. 2271-2285.

- M. Mohammadi, F. H. Kashani, J. Ghalibafan, A partially ferrite-filled rectangular waveguide with CRLH response and its application to a magnetically scannable antenna, J. Magn. Magn. Mater. 491 (2019) 165551.

- Morteza Mohammadi, F. H. Kashani, J. Ghalibafan, Backfire-to-endfire scanning capability of a balanced metamaterial structure based on slotted ferrite-filled waveguide, Waves Random Complex Media. (2019) 1-15.

- M. Mohammadi Shirkolaei, J. Ghalibafan, "Unbalanced CRLH behavior of ferrite-loaded waveguide operated below cutoff frequency, Waves in Random and Complex Media, 2020.

- K. Wu, Y. J. Cheng, T. Djerafi, and W. Hong, "Substrate-Integrated Millimeter-Wave and Terahertz Antenna Technology", Proceedings of the IEEE, vol. 100, no. 7, July 2012, pp. 2219-2232.

- B. Benakaprasad, A. Eblabla, X. Li, D.J. Wallis, I. Guiney, and K. Elgaid, "Design and Performance Comparison of Various Terahertz Microstrip Antennas on GaN-on-Low Resistivity Silicon Substrates for TMIC," Asia-Pacific Microwave Conference 2016, pp.1-4.

- C. Caloz and T. Itoh, "Electromagnetic Metamaterials: Transmission Line Theory and Microwave Applications", New York: Wiley-IEEE Press, 2005.

- Y. Dong, and T. Itoh, "Metamaterial-Based Antennas," Proceedings of the IEEE, vol. 100, no. 7, pp. 2271-2285, July 2012.

- W. Yang, S. Chen, W. Che, Q. Xue, and Q. Meng, "Compact high-gain metasurface antenna arrays based on higher-mode SIW cavities," IEEE Transactions on Antennas and Propagation, vol. 66, no. 9, September 2018, pp. 4918-4923.

- R. Han et al., "A 280-GHz Schottky diode detector in 130-nm digital CMOS," IEEE J. Solid-State Circuits, vol. 46, no. 11, pp. 564–580, Nov. 2011.

- S. Jameson, E. Halpern, and E. Socher, "A 300 GHz wirelessly locked 2×3 array radiating 5.4 dBm with 5.1% DC-to-RF efficiency in 65 nm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. Tech. Dig., Feb. 2016, pp. 348–349.

- F. Golcuk, O. D. Gurbuz, and G. M. Rebeiz, "A 0.39-0.44 THz 2×4 amplifier-quadrupler array with peak EIRP of 3-4 dBm," IEEE Trans. Microw. Theory Techn., vol. 61, no. 12, Dec. 2013, pp. 4483–4491.

- J. Grzyb, Y. Zhao, and U. R. Pfeiffer, "A 288-GHz lens-integrated balanced triple-push source in a 65-nm CMOS technology," IEEE J. Solid-State Circuits, vol. 48, no. 7, Jul. 2013, pp. 1751–1761.

- D. Hou et al., "D-band on-chip higher-order-mode dielectric-resonator antennas fed by half-mode cavity in CMOS technology," IEEE Antennas Propag. Mag., vol. 56, no. 3, Jun. 2014, pp. 80–89.

- D. Hou, Y.-Z. Xiong, W.-L. Goh, S. Hu, W. Hong, and M. Madihian, "130-GHz on-chip meander slot antennas with stacked dielectric resonators in standard CMOS technology," IEEE Trans. Antennas Propag., vol. 60, no. 9, Sep. 2012, pp. 4102–4109.

- D. Hou, Y.-Z. Xiong, W. Hong, W.-L. Goh, and J. Chen, "Silicon based on-chip antenna design for millimeter-wave/THz applications," in Elect. Design of Adv. Pkg. and Syst. Symp. (EDAPS), 2011, pp. 1–4.

Publisher's Note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

#### Affiliations

# Mohammad Alibakhshikenari<sup>1</sup> • Bal S. Virdee<sup>2</sup> • Ayman Abdulhadi Althuwayb<sup>3</sup> • Sonia Aïssa<sup>4</sup> • Chan H. See<sup>5</sup> • Raed A. Abd-Alhameed<sup>6</sup> • Francisco Falcone<sup>7,8</sup> • Ernesto Limiti<sup>1</sup>

- <sup>1</sup> Electronic Engineering Department, University of Rome "Tor Vergata", Via del Politecnico 1, 00133 Rome, Italy

- <sup>2</sup> Center for Communications Technology, London Metropolitan University, London N7 8DB, UK

- <sup>3</sup> Electrical Engineering Department, Jouf University, Sakaka, Aljouf 72388, Kingdom of Saudi Arabia

- <sup>4</sup> Institut National de la Recherche Scientifique (INRS), University of Quebec, Montreal, QC H5A 1K6, Canada

- <sup>5</sup> School of Engineering & the Built Environment, Edinburgh Napier University, 10 Colinton Rd., Edinburgh EH10 5DT, UK

- <sup>6</sup> Faculty of Engineering & Informatics, University of Bradford, Bradford, West Yorkshire BD7 1DP, UK

- <sup>7</sup> Electric, Electronic and Communication Engineering Department, Public University of Navarre, 31006 Pamplona, Spain

- <sup>8</sup> Institute of Smart Cities, Public University of Navarre, 31006 Pamplona, Spain