## Sub-50 nm high aspect-ratio silicon pillars, ridges, and trenches fabricated using ultrahigh resolution electron beam lithography and reactive ion etching

P. B. Fischer and S. Y. Chou

University of Minnesota Department of Electrical Engineering, Minneapolis, Minnesota 55455

(Received 29 July 1992; accepted for publication 24 December 1992)

We present the fabrication of sub-50 nm Si pillars, ridges, and trenches with aspect ratios greater than 10 using ultrahigh resolution electron beam lithography and chlorine based reactive ion etching. These nanoscale Si features can be further reduced to 10 nm using an additional HF wet etch. No photoluminescence was observed from arrays of 10 nm Si structures passivated with HF.

The ability to etch nanoscale features in Si is of great interest for trench isolation<sup>1</sup> and trench capacitors<sup>2</sup> in very large scale integrated circuits and for novel quantum effect Si devices. Another attractive aspect for nanoscale Si structures is to study possible light emission which has been observed in porous Si.<sup>3</sup> Techniques such as wet chemical etching are not suitable for etching nanoscale, high aspectratio Si structures due to undercutting of the mask and sloped sidewalls. Chlorine based reactive ion etching (RIE), however, is well suited for etching nanoscale Si features with good control of undercutting and etch profiles.<sup>4</sup>

Previous letters have addressed various aspects of Clbased RIE of Si such as: the role of chemistry in highly anisotropic Si trench etching,<sup>1</sup> elimination of mask undercutting,<sup>4</sup> mechanisms leading to RIE etch lag,<sup>5</sup> and the relationship between the RIE process and physical and electrical trench capacitor characteristics.<sup>6</sup> Light emission studies have been performed on Si nanostructures prepared using wet chemical dissolution<sup>3,7</sup> and sputter deposition<sup>8</sup> techniques. This letter focuses on the minimum achievable feature sizes in Si using Cl-based RIE. It also reports the preliminary results of a photoluminescence (PL) study of these Si nanostructures. We found that with an optimized composition of Cl<sub>2</sub> and SiCl<sub>4</sub>, we can readily and repeatedly achieve sub-50 nm diam pillars 500 nm high at a pitch of 100 nm and gratings with a spacing of 30 nm and a linewidth of 50 nm which are 500 nm deep. Subsequent wet etching in HF was used to remove the Si skin damaged during the RIE process and to passivate the surface. No PL was observed in these structures.

The starting Si wafers, p type with a 10  $\Omega$  cm resistivity and a (100) orientation, were first cleaned using H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (1:1:5) for 10 min at 120 °C, DI rinse for 5 min, and buffered HF:H<sub>2</sub>O (1:9) for 30 s. Then, a layer of 950 K molecular weight poly-methyl-methacrylate (PMMA), 70 nm thick, was spun on the sample and baked at 165 °C for 12 h. Arrays of dots and lines were exposed in the PMMA using a modified JEOL-840A SEM, described elsewhere,<sup>9</sup> and developed in a mixture of 2-ethoxyethanol and methanol. Cr, 50 nm thick, was then deposited via electron beam evaporation at a rate of 0.1 nm/s. A lift-off process left arrays of Cr dots and lines on the Si wafers, which were used as the mask for RIE. Final surface cleaning, prior to RIE, consisted of an  $\mathrm{O}_2$  plasma etch and an HF dip.

RIE was performed using a Plasma-Therm parallel plate RIE system operated at 13.56 MHz. A variety of recipes consisting of Cl<sub>2</sub>, SiCl<sub>4</sub>, and He gases were tested. Chlorine was used because it has been shown to produce vertical sidewalls<sup>4</sup> due to the ion assisted etching mechanism,<sup>10</sup> but has the drawback of producing trenches in the bottom corners. SiCl<sub>4</sub> and He were added to control trench formation by simultaneous redeposition.<sup>11</sup> Prior to etching, the chamber was always cleaned for 10 min with an Ar plasma and then preconditioned for 10 min using the same etching recipe that was to be used. After inserting the sample, the chamber was pumped below  $2 \times 10^{-5}$  Torr.

All samples were etched with the same  $Cl_2$  and  $SiCl_4$ flow rates, 76.6 and 13.3 sccm respectively, a power density of 0.32 W/cm<sup>2</sup>, and a pressure of 40 mTorr. These parameters were found to produce the sidewall profiles necessary for high aspect ratio nanoscale features without trenching at the bottom corners. The He flow rate was varied from 0 to 60 sccm to further optimize the etch parameters. After etching, the samples were analyzed using high-resolution scanning electron microscopy.

Previously, when etching with  $Cl_2$  chemistries, the formation of roughened Si surfaces, "black Si," was reported.<sup>4,12</sup> The appearance of black Si has been attributed to the presence of SiO<sub>2</sub> micromasks. Maluf *et al.*,<sup>13</sup> also using mixtures of  $Cl_2$ , SiCl<sub>4</sub>, and He, only observed black Si with high He flow rates. We found that proper cleaning of the sample and chamber resulted in relatively smooth surfaces with profile variations of 10–30 nm. Etched Si surfaces were typically light brown in color.

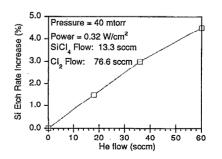

FIG. 1. Percent increase in Si etch rate vs He flow.

1414 Appl. Phys. Lett. 62 (12), 22 March 1993

0003-6951/93/121414-03\$06.00

© 1993 American Institute of Physics 1414

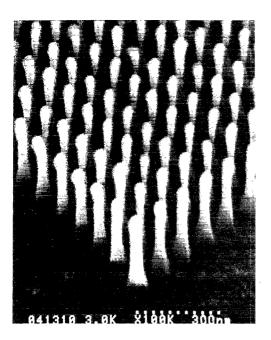

FIG. 2. Scanning electron micrograph of sub-40 nm diam Si pillars with a period of 100 nm and height of 520 nm. Sample tilt is  $40^{\circ}$ .

A series of experiments in which the He flow was varied from 0 to 60 sccm was carried out to determine the effect of He flow on black Si formation, etch rate, and sidewall geometry. We found that the He flow in this range did not affect the Si surface roughness or sidewall profiles. As shown in Fig. 1, the etch rate was found to increase slightly and almost linearly with He flow. Because He does not noticeably affect the surface or sidewall profiles, our final etching recipe consisted of only  $Cl_2$  and  $SiCl_4$  with the flow rate mentioned previously. The etch rate was measured to be 260 nm/min.

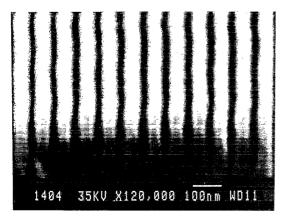

Figure 2 shows an array of etched Si pillars having diameters of about 40 nm, a period of 100 nm, and a height of 520 nm. The hemispherical Cr dots were not removed for this picture; no undercutting of the mask or trenching at the bottom corners has occurred. Figure 3 shows 50 nm wide Si ridges spaced by 30 nm and 520 nm high. The Cr mask has been left in place to verify that no undercutting

FIG. 3. Scanning electron micrograph of 50 nm wide Si ridges spaced by 30 nm with a height of 520 nm. Sample tilt is 40°.

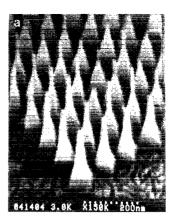

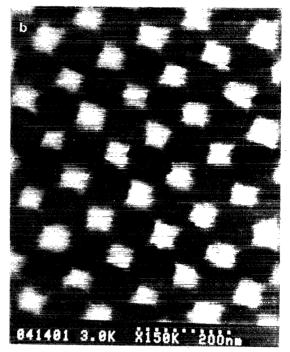

FIG. 4. Scanning electron micrographs of the same pillar array shown in Fig. 2 after Cr etch mask removal and etching in HF for 10 h: (a) view from a tilt of 40°, and (b) aerial view.

of the mask occurred during etching. In both cases, the aspect ratio is in excess of 10. Si pillars, trenches, and ridges which are, to the best of our knowledge, smaller than that previously reported, have been achieved.

Although the Cr dots used as the etch mask for the pillars are, as verified by SEM analysis prior to RIE, round, the base of each pillar is actually pyramidal. This might suggest that the pyramidal features could be due to crystallographic preferences, with the {111} planes having the slowest etch rate. However, subsequent experiments on (110) Si wafers show similar pyramidal features, indicating that they are not caused by crystallographic preferences. The exact cause of the pyramidal base is still under study at this time.

It is clear that highly uniform sub-50 nm features with near vertical profiles can be achieved using this technique. These results suggest that the ultimate limit on etched feature size is determined by the ability to pattern nanoscale

1415 Appl. Phys. Lett., Vol. 62, No. 12, 22 March 1993

P. B. Fischer and S. Y. Chou 1415

Downloaded 07 Aug 2003 to 128.112.49.65. Redistribution subject to AIP license or copyright, see http://ojps.aip.org/aplo/aplcr.jsp

masks and the fundamental mechanical stability of Si, rather than by the etching mechanism itself.

HF acid was used to further reduce the size of the RIE etched features. HF was found to etch Si at a rate as slow as 1.9 nm/h, allowing excellent control in etching nanoscale Si structures and providing the advantage of passivating the Si surface.<sup>14</sup> Figure 4(a) is a scanning electron micrograph showing the same pillar array shown in Fig. 2 after etching in HF acid for 10 h. The Cr mask was removed prior to HF etching. The columnar structures have been transformed into pyramids with sharp tips less than 10 nm wide. Figure 4(b) shows an aerial view of the same array, which further verifies the pyramidal geometry.

PL studies at room temperature were performed on etched Si features identical to those shown in Fig. 4 using a pulsed Nd<sup>3+</sup>:YAG laser with a wavelength of 532 nm and an average intensity of  $2.8 \times 10^4$  W/cm<sup>2</sup>. Light emission was checked for by using a spectrometer and by visual inspection with a 532 nm band stop filter. No photoluminescence has been observed.

In summary, using high resolution electron beam lithography and RIE with  $Cl_2$  and  $SiCl_4$  gases, we have etched sub-50 nm Si pillars, trenches, and ridges with aspect ratios greater than 10. These are among the smallest features fabricated using these techniques. We believe that the size of these Si features etched with the recipe described here is limited by the size of the etching mask, rather than the etching process itself. Furthermore, we demonstrated that the nanoscale structures can be further reduced to 10 nm by wet HF etching. No photoluminescence has been detected from arrays of Si pillars with feature sizes of the order of 10 nm and passivated using HF acid.

The work was partly supported by a Packard Fellowship, ARO, SRC Contract 91-SJ-231, and AFOSR through an Air Force Laboratory Graduate Fellowship to P.B.F.

- <sup>1</sup>I. W. Rangelow and A. Fichelscher, Proc. SPIE 1392, 240 (1990).

- <sup>2</sup>M. Engelhard, Proc. SPIE **1392**, 210 (1990).

- <sup>3</sup>L. T. Canham, Appl. Phys. Lett. 57, 1046 (1990).

- <sup>4</sup>G. C. Schwartz and P. M. Schaible, J. Vac. Sci. Technol. 16, 410 (1979).

- <sup>5</sup>A. Kassam, C. Meadowcroft, C. A. T. Salama, and P. Ratnam, J. Electrochem. Soc. 137, 1613 (1990).

- <sup>6</sup>M. Sato, S. Kato, and Y. Arita, Jpn. J. Appl. Phys. 30, 1549 (1991).

- <sup>7</sup>V. V. Doan and M. J. Sailor, Appl. Phys. Lett. 60, 619 (1992).

- <sup>8</sup>S. Furukawa and T. Miyasato, Jpn. J. Appl. Phys. 27, L2207 (1988).

- <sup>9</sup>S. Y. Chou and P. B. Fischer, J. Vac. Sci. Technol. B 8, 1919 (1990).

- <sup>10</sup>J. W. Coburn and H. F. Winters, J. Appl. Phys. 50, 3189 (1979).

- <sup>11</sup>M. Sato and Y. Arits, J. Electrochem. Soc. 134, 2856 (1987).

- <sup>12</sup>J. Olschimke, I. W. Rangelow, and R. Kassing, Microelectronik Eng. 6, 547 (1987).

- <sup>13</sup> N. I. Maluf, S. Y. Chou, J. P. Mcvittie, S. W. J. Kuan, D. R. Allee, and R. F. W. Pease, J. Vac. Sci. Technol. B 7, 1497 (1989).

- <sup>14</sup>C. Tsai, K. H. Li, D. S. Kinosky, R. Z. Qian, T. C. Hsu, J. T. Irby, S. K. Banerjee, A. F. Tasch, J. C. Cambell, B. K. Hance, and J. M. White, Appl. Phys. Lett. **60**, 1700 (1992).

## Published without author corrections

Downloaded 07 Aug 2003 to 128.112.49.65. Redistribution subject to AIP license or copyright, see http://ojps.aip.org/aplo/aplcr.jsp