**DTU Library**

# Submicron InP DHBT technology for high-speed high-swing mixed-signal ICs

Godin, Jean; Nodjiadjim, V.; Riet, Muriel; Berdaguer, Pierre; Drisse, O.; Derouin, Eric; Konczykowska, Agnieszka; Moulu, Jean; Dupuy, Jean-Yves; Jorge, Fellipe

Total number of authors:

14

Published in:

Proceedings of the IEEE Compound Semiconductor Integrated Circuits Symposium

Link to article, DOI: 10.1109/CSICS.2008.28

Publication date:

2008

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Godin, J., Nodjiadjim, V., Riet, M., Berdaguer, P., Drisse, O., Derouin, E., Konczykowska, A., Moulu, J., Dupuy, J-Y., Jorge, F., Gentner, J-L., Krozer, V., Johansen, T. K., & Scavennec, A. (2008). Submicron InP DHBT technology for high-speed high-swing mixed-signal ICs. In *Proceedings of the IEEE Compound Semiconductor Integrated Circuits Symposium* IEEE. https://doi.org/10.1109/CSICS.2008.28

# General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Submicron InP DHBT technology for high-speed high-swing mixed-signal ICs

J. Godin, V. Nodjiadjim, M. Riet, P. Berdaguer,

O. Drisse, E. Derouin, A. Konczykowska, J. Moulu,

J.-Y. Dupuy, F. Jorge, J.-L. Gentner, and A. Scavennec

ALCATEL THALES III-V LAB,

Route de Nozay, 91460 Marcoussis, France

jean.godin@3-5lab.fr

Abstract— We report on the development of a submicron InP DHBT technology, optimized for the fabrication of ≥50-GHz-clock mixed-signal ICs. In-depth study of device geometry and structure has allowed to get the needed performances and yield. Special attention has been paid to critical thermal behavior. Various size submicron devices have been modeled using UCSD-HBT equations. These large signal models have allowed the design of 50-GHz clocked 50G Decision and 100G Selector circuits. The high quality of the measured characteristics demonstrates the suitability of this technology for the various applications of interest, like 100 Gbit/s transmission.

### I. INTRODUCTION

InP HBT technology has long been identified as a technology of choice for demanding applications, such as high bit-rate optical communications (53-107 Gbit/s), RF communications in higher frequency bands (E, W, G, i.e. 80-200+ GHz), and high bandwidth data conversion, thanks to its unique capability to provide both very high speed and large breakdown voltage. Mimicking Silicon, a roadmap toward higher performances, relying on scaling, has proposed [1]. Various teams have reported on such advanced technologies [2-3] and on ICs using scaled InP HBTs for digital [4-5], analog [6-9] and data conversion [10-11] applications. Alcatel-Thales III-V Lab has been delivering for some times 40 Gbit/s mixed-signal ICs using its 1.5 µm technology [12]. To address present day applications, in particular 100+ Gbit/s transmission, and deliver ≥50-GHzclock ICs, development of a submicron process was undertaken.

## II. DEVICE OPTIMIZATION

### A. Geometry & process optimization

To achieve ≥50 GHz clocking, it appears (rule of thumbs) that the transistor should have Ft/Fmax in the 250-300 GHz range. The vertical structure optimization (layer thickness reduction) and the geometry scaling have to be carefully balanced in order to achieve the expected improvements. To insure yield and process robustness, we have kept the selfaligned 3-mesa approach used in the previous generation. A

T. Johansen, V. Krozer

Electro-Science Section, Ørsted - DTU Department, Technical University of Denmark, DK-2800 Kgs. Lyngby, Denmark

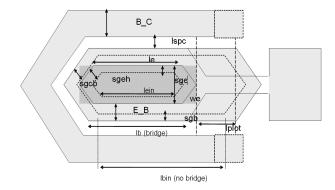

specific tool (ACPAR-2) has been developed to assess the performance impact of the various – geometry (Figure 1) and structure – parameters.

Figure 1: geometry parameters used in ACPAR-2

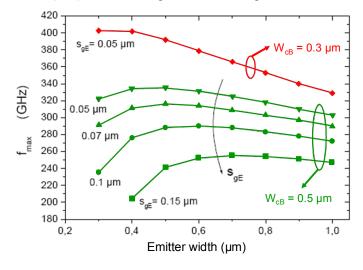

For example, Figure 2 illustrates the expected  $F_{MAX}$  for various underetching  $(S_{gE})$  values, for two base contact width values  $(W_{cB})$ , demonstrating how critical this parameter is.

Figure 2: under-etching impact on Fmax, for 2 base contact width values

This work is supported by funding under the Sixth Research Framework Program of the European Community, Project GIBON (Contract Number 034183; <a href="http://www.ist-gibon.eu">http://www.ist-gibon.eu</a>) and under French SYSTEM@TIC Cluster program, Project MINOS (http://www.systematic-paris-region.org)

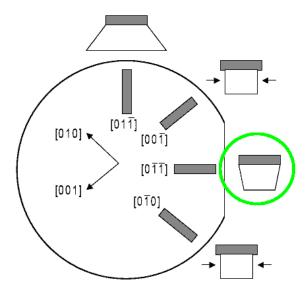

Figure 3: under-etching control w.r.t crystallographic axes

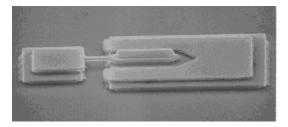

Figure 4: FIB device cut

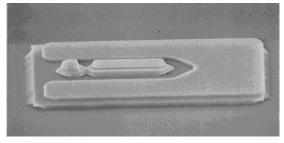

As etching control is related to crystallographic axes (Figure 3) hexagonal geometry has been chosen with a fixed orientation. Figure 4 shows the device quality achieved through self-alignment and under-etching control.

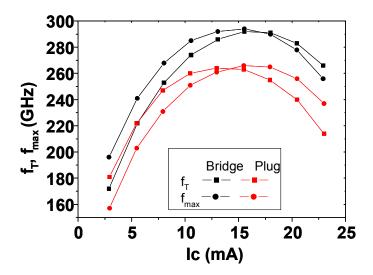

ACPAR-2 allowed also to compare two approaches to tackle the extrinsic base resistance and collector capacitance problem, the bridge – lower capacitance – and the plug – lower resistance – (Figure 5). Bridge was predicted to yield better frequency performances, which was confirmed by actual measurements (Figure 6). However, less predictable features such as yield and robustness led us to rather use the plug devices for circuit fabrication.

### B. Structure optimization

The devices were grown by GSMBE epitaxy; their structure is comprised of a 40 nm Emitter, a  $8 \times 10^{19}$  cm<sup>-3</sup> Carbon-doped 28 nm graded Base and a  $5 \times 10^{16}$  cm<sup>-3</sup> doped 130-250 nm composite Collector.

Figure 5: bridge (top) and plug (bottom) device microphotographs

Figure 6: bridge (top) and plug (bottom) device performances

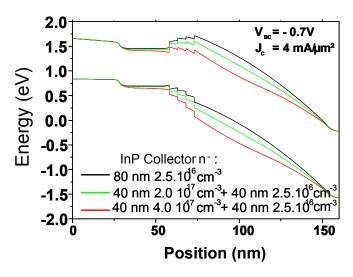

As the major contribution to  $F_T$  is the transit time in both Base and Collector, optimization has focused on the base-collector junction; we need to balance short transit time with breakdown voltage [which is a specific advantage of DHBTs], Kirk effect/blocking effect due to conduction band discontinuity and inter-valley scattering (Figure 7). A combination of an InGaAs spacer, a doping plane and quaternaries [13] has allowed to get simultaneously high  $BVcE_0 = 4.75V$ ,  $J_{Kirk} = 9mA/\mu m^2$ , and  $F_T = 290~GHz$ .

Thermal effects have been identified as a key issue for advanced HBTs [14]. For our devices, the InGaAs subcollector layer (which serves as both an etch-stop layer and to improve collector ohmic contact) has been identified as the major contributor to temperature rise, due to its poor (5 W/K.m) thermal conductivity. This layer thickness has been optimized [15] to significantly improve thermal behavior (30% overall thermal resistance reduction), while maintaining the frequency performances.

Figure 7: Example of band diagram for collector optimization

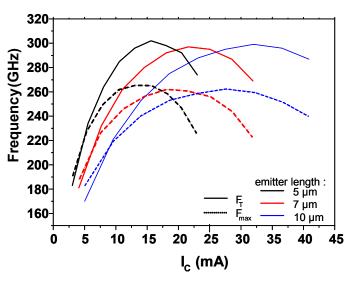

Figure 8: various size HBTs performances

# III. DEVICE FABRICATION & PERFORMANCES

As mentioned, a triple-mesa self-aligned process was used. 0.3  $\mu$ m-wide Base and 0.7  $\mu$ m-wide Emitter contacts were defined by E-beam lithography, while the other steps rely on optical lithography. Benzocyclobutene (BCB) is used for passivation, isolation and planarization. DC gain is about 20, BVcE<sub>0</sub> $\cong$  5V, and Ft/Fmax are in the 250-300 GHz range for various (0.7x5-10  $\mu$ m²) HBT dimensions (Figure 8). These performances are suitable for very high speed large-signal circuits design and fabrication.

### IV. MODELING

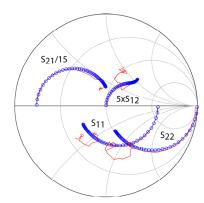

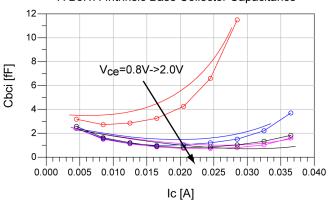

For accurate circuit simulation, large signal modeling needs to take into account various physical effects specific to InP HBTs, such as forward transit time and base-collector capacitance modulation with bias, and saturation influenced by base-collector heterojunction behavior. Based on the methodology described in [16-18], parameters for an UCSD-like model were extracted from various bias small-signal

measurements. Figure 9 illustrates the model accuracy, for both small-signal and  $C_{BC}$  modulation.

# S-Parameters (Vce=1.6V, Ic=28.5mA)

freq (250.0MHz to 65.00GHz)

## T7B3H7: Intrinsic Base Collector Capacitance

Figure 9: measurements vs. model comparison (rings are for model)

### V. IC DESIGN & CHARACTERIZATION

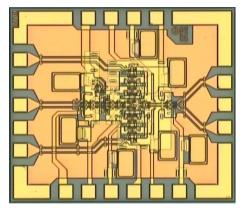

To assess the capability of this technology for 50 GHz clock mixed-signal ICs fabrication, two such circuits were first designed: (i) a 50 Gbit/s (full-rate) decision circuit and (ii) a 100 Gbit/s (half-rate) selector were designed, using the developed models. They are comprised of about 30 transistors of various size (from 5 to 10  $\mu$ m-long 0.7  $\mu$ m-wide HBTs).

Figure 10: Selector circuit microphotograph

Three different wafers were processed, to assess reproducibility and yield. Good to excellent characteristics were achieved on all wafers, with yield ranging from 40% up

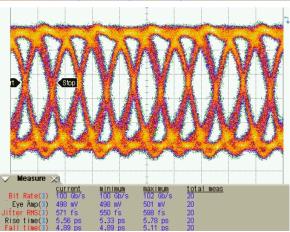

to 80%. Figure 10 show the microphotographs of the 1.4x1.6 mm<sup>2</sup> selector IC. Both ICs' eye diagrams, which were measured on-wafer, are shown on Figure 11. 50 Gbit/s input signals were provided, based on a commercial 4x12.5 Gbit/s PRBG and an in-house 50 Gbit/s MUX [19], to assess the functional performances of the circuits:

(i) for the decision circuit, the clock phase margin is 10 ps (180°) at 50 Gbit/s [and up to 15 ps (230°) at 43 Gbit/s]; rise and fall times are below 6.5 ps, and (scope-limited) RMS jitter is below 300 fs.

Thanks to the very high quality achieved, improved 100 Gbit/s (based on 50 GBaud modulation formats) transmission experiments are made possible.

(ii) For the selector circuit, 500 mV output swing has been obtained at 100 Gbit/s, with rise time below 6 ps and fall time below 5 ps; RMS jitter is less than 600 fs; vertical and horizontal eye opening are 54% and 66% respectively. This selector is the core of a selector-EML-driver, key building block for a 100 Gbit/s OOK transmission experiment being set up.

The very short rise and fall time, as well as the very low jitter, indicate that still higher than 50 GHz clock may be achievable; combined with the breakdown voltage high value, >100 Gbit/s large-signal ICs may be contemplated, such as a 107 Gbit/s OOK driver.

Figure 11: Decision (top) & Selector (bottom) ICs eye diagrams

### VI. CONCLUSION

A submicron InP DHBT process has been developed, with special care devoted to structure optimization, thermal effects mitigation, and process robustness. Thanks to accurate modeling, meaningful circuits have been designed which demonstrate the suitability of this process for 100+ Gbit/s transmission, be it OOK or 50 GBaud. The large breakdown voltage will allow to design 107 Gbit/s driver.

### REFERENCES

- [1] M.J.W. Rodwell, Minh Le, B. Brar, "InP Bipolar ICs: Scaling Roadmaps, Frequency Limits, Manufacturable Technologies", Proceedings of the IEEE, Volume 96, Issue 2, Feb. 2008 pp. 271-286

- [2] C. Monier, et al., "High-Speed InP HBT Technology for Advanced Mixed-signal and Digital Applications", IEDM 2007, pp. 671-674

- [3] M. Le, et al., "Self-aligned InP DHBTs for 150 GHz digital and mixed signal circuits", IPRM '05, pp. 325-330

- [4] J. Hallin, T. Kjellberg, T. Swahn, "A 165-Gb/s 4:1 Multiplexer in InP DHBT Technology", JSSC-41, n° 10, Oct. 06, pp. 2209-2214

- [5] K. Ishii, "Very-High-Speed InP/InGaAs HBT Multiplexer ICs for Optical Communication Systems", ISPACS '06, pp. 247-250

- [6] Z. Griffith, *et al.*, "Transistor and circuit design for 100-200-GHz ICs", IEEE Journal of Solid-State Circuits, Volume 40, Issue 10, Oct. 2005, pp. 2061-2069

- [7] V. Radisic, et al., "Demonstration of 184 and 255-GHz Amplifiers Using InP HBT Technology", MWCL-18, n° 4, April 2008, pp. 281-283

- [8] Y. Baeyens, N. Weimann, V. Houtsma, J. Weiner, Y. Yang, J. Frackoviak, P. Roux, A. Tate, Y.K. Chen, "Submicron InP D-HBT single-stage distributed amplifier with 17 dB gain and over 110 GHz bandwidth", IMS 06 Digest, June 2006, pp. 818-821

- [9] R.-E. Makon, R. Driad, K. Schneider, R. Aidam, M. Schlechtweg, G. Weimann, "Fundamental W-Band InP DHBT-Based VCOs With Low Phase Noise and Wide Tuning Range", IMS 07 Digest, 3-8 June 2007, pp. 649-65

- [10] D. Ching, et al., "Ultra wideband digital to analog conversion based on advanced InP DHBT", CSICS '05, pp. 93-96

- [11] A. Gutierrez-Aitken, J. Matsui, E. Kaneshiro, B. Oyama, D. Sawdai, and D. C. Streit, "Ultrahigh-speed direct digital synthesizer using InP DHBT technology", IEEE Journal of Solid State Circuits, Vol.37 (2002), pp. 1115-1119

- [12] J. Godin, M. Riet, P. Berdaguer, V. Nodjiadjim, A. Konczykowska, A. Scavennec, "InP DHBT Technology Development for High Bitrate Mixed-Signal IC Fabrication", IPRM '06, 7-11 May 2006, pp. 258-261

- [13] V. Nodjiadjim, M. Riet, A. Scavennec, P. Berdaguer, J.L. Gentner, J. Godin, P. Bove, M. Lijadi, "Comparative Collector Design in InGaAs and GaAsSb-based InP DHBTs", to be presented at IPRM '08, 26-29 May 2008

- [14] I. Harrison, M. Dalhlström, S. Krishnan, Z. Griffith, Y. M. Kim, M. J. W. Rodwell, "Thermal limitations of InP HBTs in 80- and 160-Gb ICs", IEEE Transactions on Electron Devices, Vol 51, n° 4, 2004, pp. 529-534

- [15] V. Nodjiadjim, M. Riet, P. Berdaguer, J.L. Gentner, O. Drisse, E. Derouin, A. Scavennec, J. Godin, "Performances and self-heating reduction of submicron InP/InGaAs/InP Heterojunction Bipolar Ttansistors", WOCSDICE '07, 20-23 May 2007

- [16] T.K. Johansen, V. Krozer, A. Konczykowska, M. Riet, J. Vidkjaer, "Large-Signal Modeling of High-Speed InP DHBTs using Electromagnetic Simulation Based De-embedding", IMS '06, June 2006, pp. 655-656

- [17] T. K. Johansen, V. Krozer, V. Nodjiadjim, A. Konczykowska, J.-Y. Dupuy, "Improved Extrinsic Base Resistance Extraction for InP DHBT Devices", in 2008 German Microwave Conf., March. 2008, pp. 491-494

- [18] T. K. Johansen, V. Krozer, D. Hadziabdic, C. Jiang, A. Konczykowska, J.-Y. Dupuy, "A Novel Method for HBT Intrinsic Collector Resistance Extraction from S-parameters", in 2007 Asia-Pacific Microwave Conference, Dec. 2007, pp. 1825-1828

- [19] P. André, S. Blayac, P. Berdaguer, J.-L. Benchimol, J. Godin, N. Kauffmann, A. Konczykowska, Abed-Elhak Kasbari, and Muriel Riet, "InGaAs/InP DHBT Technology and Design Methodology for Over 40 Gb/s Optical Communication Circuits", IEEE Journal on Solid-State Circuits, Vol. 36, N°. 9, Sept. 2001, pp. 1321-1327