# Substrate loss reduction in antenna-on-chip design

# Citation for published version (APA):

Johannsen, U., Smolders, A. B., Máhmoudi, R., & Akkermans, J. A. G. (2009). Substrate loss reduction in antenna-on-chip design. In Proceedings IEEE Antennas and Propagation Society International Symposium, 2009, APSURSI '09, 1-5 June 2009, Charleston, SC (pp. 1-4). Institute of Electrical and Electronics Engineers. https://doi.org/10.1109/APS.2009.5172243

DOI: 10.1109/APS.2009.5172243

## Document status and date:

Published: 01/01/2009

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

#### Substrate Loss Reduction in Antenna-on-Chip Design

U. Johannsen<sup>\*1</sup>, A.B. Smolders<sup>2</sup>, R. Mahmoudi<sup>3</sup>, and J.A.G. Akkermans<sup>3</sup> <sup>1</sup> TUHH, Hamburg, Germany <sup>2</sup> NXP Semiconductors, Nijmegen, The Netherlands <sup>3</sup> TU/e, Eindhoven, The Netherlands Ulf.Johannsen@tuhh.de, Bart.Smolders@nxp.com

### 1 Introduction

State-of-the-art BiCMOS processes have transit frequencies  $f_T$  well above 200 GHz, making them suitable for new emerging mm-wave applications in the 57-64 GHz band. Several integrated mm-wave antennas on silicon have been published in the past years with a typical antenna gain below -8 dBi [1]. The low gain is caused by severe losses in the silicon substrate due to substrate modes propagating through the low-resistive silicon. The purpose of this work is to present an approach to reduce substrate losses.

## 2 Substrate effect

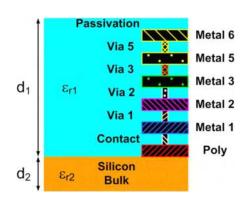

The cross-section of a typical chip in CMOS/BiCMOS technology is illustrated in Fig. 1. It is composed of a metal stack, in which an antenna structure can be implemented, on top of a silicon bulk substrate.

The bulk substrate can be considered as a slab waveguide. The cut-off frequencies of the TE-modes of a dielectric slab with infinite lateral extension placed in air can be determined from

$$f_c^{(n)} = \frac{n \cdot c_0}{2d_2 \cdot \sqrt{\epsilon_{r2} - 1}}, \ n \in \mathbb{N}_0, \qquad (1)$$

with *n* the mode number,  $c_0$  the speed of light in vacuum,  $d_2$  and  $\epsilon_{r2}$  the thickness and permittivity of the slab's material, respectively, [2]. As can be seen from Equation (1) the 0<sup>th</sup> order mode has a 0 Hz cut-off frequency and therefore always gets excited. Since the chip is of finite size the excited substrate modes

Figure 1: Sketched cross-section of a typical CMOS/BiCMOS technology.

eventually reach an edge where they get partly reflected and transmitted. The reflection, finally, results in a standing wave between opposite edges. The transmitted part radiates from the chip's edge and interferes with the waves radiated directly from the antenna and from other edges. This results in a deteriorated antenna radiation pattern which is chip size dependent. Furthermore, the radiation efficiency is affected by the substrate modes as the high permittivity of the silicon leads to a high energy coupling into these modes and the low resistivity of the silicon (usually

#### 978-1-4244-3647-7/09/\$25.00 ©2009 IEEE

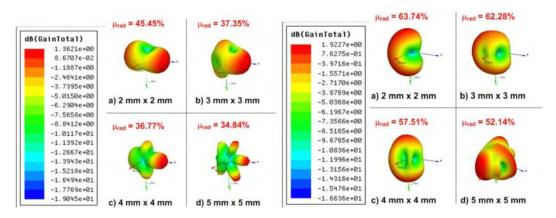

$\rho \leq 20 \ \Omega \text{cm}$ ) results in high substrate losses. These effects can be well observed from the results on the left in Fig. 2. It shows the simulated radiation patterns and efficiencies of a 60 GHz dipole antenna integrated in four chips of 200  $\mu$ m substrate thickness, but different area sizes. The dipoles were placed 50  $\mu$ m from the chip's

Figure 2: Left: Simulated radiation characteristics of a dipole antenna integrated in chips of different area size. Right: Improved radiation characteristics by covering the chip with a metal plate.

edge and the substrate resistivity is 20  $\Omega$ cm. A simple measure that can be taken to enhance the off-chip radiation is the implementation of a metal plate covering the chip. The substrate can be considered as a surface waveguide for this case with corresponding surface-wave modes. Assuming the metal plate resides in the Metal 1 layer (see Fig. 1), the cut-off frequencies of the TE-modes can be obtained from the solutions of the following set of equations ([3]):

$$\tan(x_d) = \frac{d_2}{d_1} C \cot(Cx_d), \quad x_d = k_0 d_2 \sqrt{\varepsilon_{r2} - 1}, \quad C = \frac{d_1 \sqrt{\varepsilon_{r1} - 1}}{d_2 \sqrt{\varepsilon_{r2} - 1}}, \quad (2)$$

where  $k_0 = \omega \sqrt{\varepsilon_0 \mu_0}$  is the wave number in free space. The lowest-order TE surfacewave mode is the  $TE_1$  mode. The advantage compared to a slab waveguide is its nonzero cut-off frequency. Hence, for frequencies below cut-off TE-modes are suppressed and the radiation pattern and efficiency is improved. In the semiconductor world it is already a standard post-processing technique to back-grind the silicon wafer to a thickness of 200  $\mu$ m or lower, while maintaining the mechanical stability for handling and packaging purposes. With a thickness of 200  $\mu$ m, the corresponding cut-off frequency of the  $TE_1$  mode is 112 GHz, while at 60 GHz the thickness of the silicon substrate needs to be well below 350  $\mu$ m to avoid the TE<sub>1</sub> mode. On the right in Fig. 2 the radiation patterns and efficiencies of the on-chip antennas are depicted when a rectangular metal plate has been added. This plate is placed at a distance of 650  $\mu$ m from the dipole as shown in Fig. 3 ( $r = 650 \mu$ m). Thus, the plate acts as a reflector with the length of the chip's dimension while suppressing the TE-modes behind the reflecting edge. Hence, the design can be understood as a rudimentary on-chip Yagi-antenna [4]. As can be seen in the figure the radiation pattern does still change with varying chip size, but the sensisitivity of its shape to the chip's dimension is reduced. The remaining chip size dependence might be caused by the  $0^{th}$  order TM-mode or the varying reflector length.

#### 3 Design

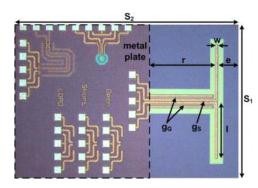

The metal covered chip approach has been used to design an on-chip antenna. For noise-matching purposes we have chosen  $Z_{ant} = (30 + j30) \Omega$  as antenna impedance at 60 GHz (direct matching scheme). In the chip design the metal plate is implemented in the lowest metal layer. The transmission line, connecting the dipole

| $S_1$       | $S_2$        | l             | w            |

|-------------|--------------|---------------|--------------|

| 2 mm        | 2 mm         | $540~\mu m$   | $20 \ \mu m$ |

| $g_S$       | $g_G$        | r             | e            |

| $6 \ \mu m$ | $20 \ \mu m$ | $630 \ \mu m$ | $50 \ \mu m$ |

Figure 3: Chip Design (photograph).

and the RF circuitry above the plate, is similar to those investigated in [5] with a characteristic impedance  $Z_0 = 60 \ \Omega$ . In the simulation setup the resistivity of the silicon substrate was set to 200  $\Omega$ cm which is in agreement with the specifications of the process used. With the parameters from Fig. 3 the simulated reflection coefficient of the antenna shows a -20 dB bandwidth of 7 GHz around 60 GHz. The radiation pattern basically looks like the one depicted on the right in Fig. 2 a) with a maximum directivity of 2.35 dBi and an efficiency of 78.43 %.

## 4 Measurement results and discussion

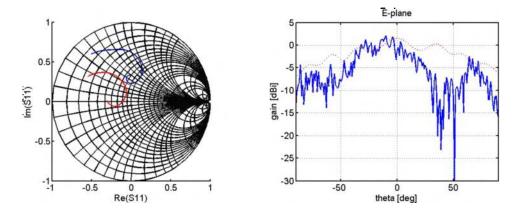

The design from the preceding section has been manufactured in a standard SiGe:C BiCMOS process. This design differs slightly from the simulation setup, i.e.  $S_1$  has been reduced to 1.5 mm and landing pads have been implemented that are required for the probe-based measurement (see Fig. 3). Additional measurements indicated that the silicon bulk resisitivity is about 20  $\Omega$ cm (instead of the specified 200  $\Omega$ cm) and its thickness is 220  $\mu$ m. A comparison of the simulated and measured antenna impedance is provided in Fig. 4. For this measurement the chips have been glued on PCB's of 3 mm thickness and a permittivity of 4. The simulation setup has been adjusted in order to compensate for this. A detailed description of the measurement setup can be found in [6]. The result still does not entirely match the measured curve. A reason for the difference might be the simplifications which have been made for the landing pads model. Furthermore, even-mode reflections introduced by small asymmetries in the measurement setup could not be measured with our balun. A comparison of the simulated and measured radiation pattern is also provided in Fig. 4. It shows the gain of the on-chip antenna measured from  $-90^{\circ}$  to  $+90^{\circ}$  from the normal of the top side of the chip. For the radiation pattern measurements the chips were directly glued on a metal plate to avoid the existence of substrate modes in the PCB material. The simulation setup was changed accordingly. The

Figure 4: Left: Input reflection coefficient of on-chip antenna for a system impedance of  $100 \Omega$  (red: measurement, blue: simulation). Right: Radiation pattern at 60 GHz (solid: measurement, dashed: simulation).

asymmetry of the E-plane measurement might be caused by reflections from the probe's body which might be slightly misaligned to the chip. Nevertheless, the comparison between measured and simulated radiation pattern basically confirms the good radiation efficiency.

#### 5 Conclusion

We have explained the effect of the silicon substrate on the off-chip radiation of an integrated antenna on chip. From this consideration a low-cost approach for an enhanced antenna-on-chip design has been derived and its improved radiation efficiency has been confirmed by measurements.

#### References

- A. Shamim et al., "24 GHz On-Chip Antennas and Balun on Bulk Si for Air Transmission," Antennas and Propagation, IEEE Transactions on, vol. 56, no. 2, pp. 303–311, Feb. 2008.

- [2] R. F. Harrington, Time-Harmonic Electromagnetic Fields. Mc Graw-Hill, 1990.

- [3] N. Alexopoulos, D. Jackson, "Fundamental superstrate (cover) effects on printed circuit antennas," Antennas and Propagation, IEEE Transactions on, vol. 32, no. 8, pp. 807– 816, Aug. 1984.

- [4] Y.P. Zhang et al., "On-chip antennas for 60-GHz radios in silicon technology," Electron Devices, IEEE Transactions on, vol. 52, no. 7, pp. 1664–1668, July 2005.

- [5] W.D. van Noort et al., "On-chip mm-Wave passives," Bipolar/BiCMOS Circuits and Technology Meeting, 2007. BCTM '07. IEEE, pp. 168–171, 30 2007-Oct. 2 2007.

- [6] J.A.G. Akkermans et al., M.H.A., "Millimeter-wave antenna measurement," Microwave Conference, 2007. European, pp. 83–86, Oct. 2007.