# Super Thin-Film Transistor with SOI CMOS Performance Formed by a Novel Grain Enhancement Method

Hongmei Wang, Mansun Chan, Member, IEEE, Singh Jagar, Vincent M. C. Poon, Member, IEEE, Ming Qin, Yangyuan Wang, Senior Member, IEEE, and Ping K. Ko, Fellow, IEEE

Abstract—High performance super TFT's with different channel widths and lengths, formed by a novel grain enhancement method, are reported. High temperature annealing has been utilized to enhance the polysilicon grain and improve the quality of silicon crystal after low temperature MILC treatment on amorphous silicon. With device scaling, it is possible to fabricate the entire transistor on a single grain, thus giving the performance of single crystal SOI MOSFET. The effects of grain boundaries on device performance have been studied, indicating the existence of extra leakage current paths caused by the grain boundaries traversing the channel, which induced subthreshold hump and early punchthrough of wide devices. The probability for the channel region of a TFT to cover multiple grains decrease significantly when the device is scaled down, resulting in better device performance and higher uniformity.

Index Terms—Grain enhancement, thin-film transistor, 3-D VLSI.

## I. INTRODUCTION

■ HIN-FILM-TRANSISTORS (TFT's) inherently have the potential advantages of silicon-on-insulator (SOI) MOSFET's such as high density, easy isolation, and simple process, as well as the possibility to be used in vertical integration. However, the application of TFT's is mainly limited to low-temperature flat-panel display due to its substantially worse performance caused by the grain boundaries in the channel region [1], [2]. With the increasing demand for portable system and the pursuance of tera-scale integrated circuits, truly three-dimensional (3-D) device and interconnect technology, which provide a revolutionary breakthrough in circuit compactness, has become an important topic in research [3]. Thin-film-transistor (TFT) technology has been receiving more attention now because it is a promising mean of achieving 3-D integration. It has also been utilized in various 3-D circuits such as SRAM's and DRAM's [4]-[7]. Unfortunately, the low on-current, high threshold voltage, and significant device to device variation in conventional polysilicon TFT's restrain

Y. Wang is with the Institute of Microelectronics, Peking University, Beijing, 10087, China.

Publisher Item Identifier S 0018-9383(00)06034-2.

their further applications in other 3-D structures, especially when device size is scaled down and supply voltage is reduced.

It is believed that electrical properties of the TFT's can be improved if the grain size can be enhanced and the number of grain boundaries in the channel region can be minimized. Single-grainlike TFT's have been fabricated by solid phase crystallization (SPC) [8] and germanium-seeded laterally crystallization technology [9], [10], but the grain size ( $\sim 1 \ \mu m$ ) is still small compared to the size of the transistor. Thus the performance is still unsatisfactory. Metal-Induced-Lateral-Crystallization (MILC) has been studied in the past to obtain large and regular polysilicon grain from amorphous silicon, while keeping the silicon grains mostly free of metal contamination [11], [12]. Despite the considerable grain length obtained by this method, the grain width achieved is limited to less than one micron, which is too small to realize single crystal device with high controllability. In this work, we have discovered that by applying high temperature annealing to amorphous silicon with metal-induced-lateral-crystallization (MILC) treatment, the grain size of the resulting silicon can be significantly enhanced in both grain length and width direction [13], [14]. With device scaling, it is possible to fabricate the entire channel region of a MOSFET in a single grain. Single grain super TFT's with SOI CMOS performance have been fabricated on these grain-enhanced regions. The super TFT's technology can be easily integrated into a CMOS technology, without any requirement for extra equipment. The crystallization and device fabrication process will be briefly described in Section II. In Section III, we will discuss the mechanisms of MILC grain size enhancement at high temperature annealing. We believe that large grain size is caused by the secondary recrystallization of MILC polysilicon grains, and the thin silicon film with the same grain crystal orientation further enhance the secondary recrystallization. The device characterization will be described in Section IV. It is found that super TFT's with SOI CMOS performance and good uniformity can be obtained through the reduction of the channel dimensions. The influence of grain boundaries on device performance will also be discussed in this section. Finally, Section V will give a conclusion on the results obtained.

## II. CRYSTALLIZATION AND DEVICE FABRICATION

The formation of super TFT's with enhanced grain started by growing 3000 Å of oxide on normal silicon wafer to serve

Manuscript received January 21, 2000. This work was supported by a Competitive Earmarked Research Grant from Research Grant Council of Hong Kong. The review of this paper was arranged by Editor C.-Y. Lu.

H. Wang, M. Chan, S. Jagar, V. M. C. Poon, M. Qin, and P. K. Ko are with the Department of Electrical and Electronic Engineering, Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong (e-mail: mchan@ee.ust.hk).

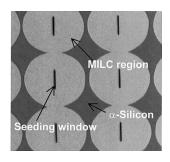

Fig. 1. Top view of MILC region.

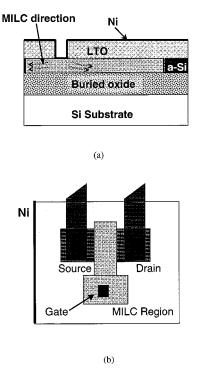

as the buried oxide. 1000 Å of amorphous silicon was then deposited by low pressure chemical vapor deposition (LPCVD) at 550 °C. SiH<sub>4</sub> was used as the Si source with a flow rate of 70 sccm. The deposition pressure was about 300 mtorr. 3000 Å low temperature oxide (LTO) was then deposited, patterned and dry/wet etched to expose the seeding window for nickel deposition. After depositing 100 Å Ni, lateral crystallization was carried out subsequently at 560 °C for 20 h in N<sub>2</sub> ambient. Nickel contacts with the amorphous silicon only in the seeding window; other areas of wafers outside the seeding window are mostly free of Ni contamination. The top view of the MILC region is shown in Fig. 1. The MILC rate was found to be about 4.3  $\mu$ m/hour at this temperature. 100 to 200  $\mu$ m MILC region can be obtained at different MILC annealing temperature by only 2  $\mu$ m Ni strip. By optimizing the process, it is expected that the MILC region can be enlarged furthermore. The remaining Ni was then removed in H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> (4:1) at 70 °C, and the sacrificial LTO was removed in HF completely after the crystallization process. The wafers were subsequently annealed at 900 °C for 30 min in N2 ambient to enlarge the grain size of MILC region. This temperature has not been optimized and reduction to lower temperature is possible. Finally, conventional dual gate SOI CMOS process was used to fabricate TFT's on the grain-enhanced area. Devices on all of the wafers were grouped into two parts; MILC crystallization was done only in one parts and normal poly TFT's were formed on other parts for comparison. As a result, most of the device parameters are the same for both kinds of TFT's. The channel implant dose used for NMOS and PMOS transistors are  $2 \times 10^{12}$ /cm<sup>2</sup> (Boron) and  $8 \times 10^{12}$ /cm<sup>2</sup> (Phosphorus) respectively. The gate oxide was thermally grown at 850 °C. The key processing steps for the formation of the large poly-Si grain and the top-view of transistor studied are illustrated in Fig. 2. The super TFT's process is compatible with conventional SOI CMOS technology, with only one extra mask added for the seed window definition.

## III. MECHANISM OF SIGNIFICANT GRAIN ENHANCEMENT AT HIGH TEMPERATURE

Compared with the extensive research done on the low temperature behavior of MILC structure [11], [12], [16], [17], the high temperature behavior of MILC structures have not received much attention. In this section, we will discuss the mechanism of grain enhancement at post-MILC high temperature annealing.

In the conventional low temperature nickel-induced-lateral-crystallization process, the Ni layer in the small exposed

Fig. 2. (a) Key processing steps for the formation of the large poly-Si grain and MILC growth direction. (b) Layout of transistors studied. The space between the seeding window and active area is  $10 \ \mu$ m.

window transforms to NiSi<sub>2</sub> at 550 °C, which acts as a nucleus for amorphous silicon crystallization. From these small "crystal nuclei", crystallization begins to propagate in the lateral direction, initially free of Ni [11]. The activation energy for crystallization of  $\alpha$ -Si in the presence of nickel was found to be 1.86 eV, which is much lower than that of solid state recrystallization (3.1 eV) of intrinsic silicon [15]. With the fast diffusion of nickel in the silicon and low activation energy, higher growth rate into the lateral area and larger crystallization region are obtained, benefiting the device and circuit design.

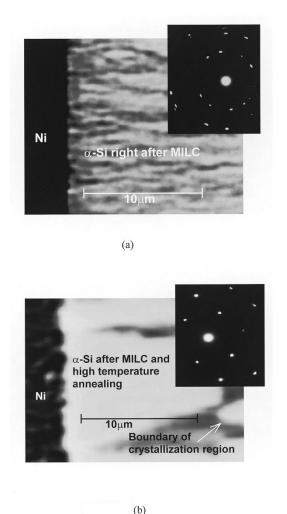

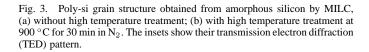

It is observed that amorphous silicon is crystallized mainly with (110) planes parallel to surface of the film by the MILC treatment [11], [12], [16], and the shape of the silicon grain is elongated with the major axis aligned in the direction perpendicular to the Ni strip. Most of the grain lengths are longer than 1  $\mu$ m, and in some cases, reaching a few tens of microns. But the width is limited to less than one micron as shown in Fig. 3(a). Although it was reported that the longitudinal grain boundaries are less impeding to carrier flow [17], we found that the boundaries caused the large leakage current and early punchthrough in short-channel TFT's. To fabricate high performance single grain super TFT's, it is necessary to enhance the grain size in both the length and width direction.

We have discovered that high temperature annealing can be utilized to enhance the grain size significantly in both the length and the width direction up to tens of microns as shown in Fig. 3(b). Secondary grain crystallization at high temperature (900 °C, 30 min) is the process responsible for the grain size enhancement. During secondary grain crystallization, a small number of grains will expand due to surface energy anisotropy [18]. As a result, smaller grains will be consumed. The process

continues until the secondary grains impinge on one another, forming monomodal distributed grain with large grain size. It is easy to obtain very large secondary grain because only a few percent difference in surface energy is required to promote secondary grain growth in the thin film sample [18]. Moreover, the same grain orientation (110) and the low activation energy in MILC region encourage the secondary grain growth. In addition, the integrity of the silicon crystal is also improved by high temperature annealing, which is verified by the TED pattern as shown in inset of Fig. 3. Some irregular patterns in the low temperature MILC region are explained by the existence of some noncrystal region. However, the TED pattern of high temperature MILC region approaches that of single crystal silicon, indicating its improvement of crystal integrity.

### IV. DEVICE CHARACTERIZATION AND DISCUSSION

#### A. Device Characterization

With the enhanced grain size as described in previous section, it is expected that the TFT's fabricated on the high temperature MILC region have much improvement in device

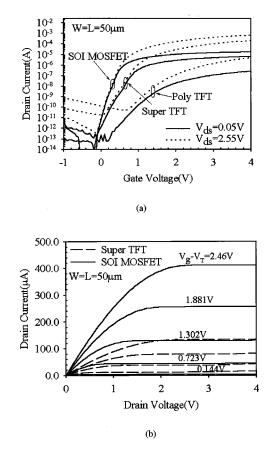

Fig. 4. (a) Subthreshold current and (b) I-V characteristics of a large n-channel super TFT. Conventional poly TFT and SOI NMOSFET are also plotted as reference. The gate oxide thickness of polys TFT, super TFT and SOI MOSFET are 140 Å, 110 Å, and 105 Å, respectively. The thickness of silicon film in SOI MOSFET's is 780 Å.

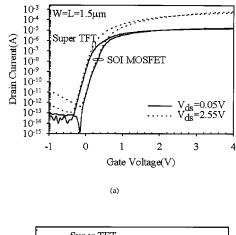

performance compared with conventional TFT's. We shall call the TFT fabricated on the enhanced grain region super-TFT. To verify this concept, MOS transistors with different channel lengths and widths have been fabricated on the crystallized island. Fig. 4 showed the subthreshold conduction and output characteristics of a large dimension n-channel super TFT together with SOI nMOSFET and polysilicon TFT for comparison. Compared with poly TFT, a significant performance improvement was observed in the super TFT's mainly due to the larger grain size and smaller intragrain microdefects. But the performance of the super TFT is still inferior to that of SOI MOSFET's, implying the channel region is not single grain. However, with the reduction of device dimensions, it is possible to fabricate the entire transistor on a single grain. Fig. 5 shows the subthreshold conduction and output characteristics of a small dimension ( $W = L = 1.5 \ \mu m$ ) n-channel super TFT. Excellent device characteristics were observed, including steep subthreshold slope, low threshold voltage, large current drive and high on/off current ratio, which are compatible to the performance of devices fabricated on SOI substrate. The excellent device performance of super TFT's result from the real single-crystal silicon formed at the channel region by the crystallization of amorphous silicon. This can also be verified by the suppression of GIDL current as shown in Fig. 5. The comparison of performance parameters for different devices

(b)

Fig. 5. (a) Subthreshold current and (b) I-V characteristics of a small n-channel super TFT.

TABLE I SUMMARY OF MEASURED TRANSISTOR PARAMETERS FROM n-CHANNEL SUPER TFTS WITH DIFFERENT DIMENSIONS

| Device Size<br>(W=L) | V <sub>T</sub> (V) | S(mV/dec) | Mobility<br>(cm <sup>2</sup> /V.s) | Max. ON/OFF<br>Current ratio |

|----------------------|--------------------|-----------|------------------------------------|------------------------------|

| 50µm                 | 0.96               | 175       | 176                                | 3.6×10 <sup>6</sup>          |

| 9.5µm                | 0.78               | 130       | 208                                | 7.12×10 <sup>7</sup>         |

| 4.5µm                | 0.64               | 95        | 288                                | $1.05 \times 10^{8}$         |

| 1.5µm                | 0.29               | 73        | 430                                | 1.66×10 <sup>9</sup>         |

with different dimensions is summarized in Table I. An obvious improvement in device performance is observed when the device is scaled down, demonstrating the decrease in the number of grain boundaries and final achievement of single crystal TFT's.

#### B. Analysis of Boundary Effect

Although the grain sizes are enhanced substantially by this novel high temperature MILC method, grain boundaries still have influence on devices performance when channel region covers the multiple polysilicon grains. In this section, we will study the effect of grain boundaries and provide a device design guideline.

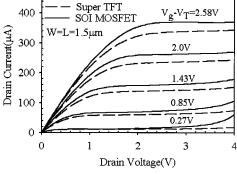

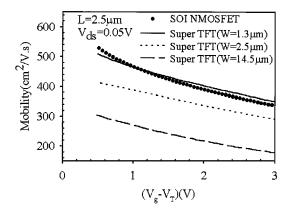

The electron mobility of super TFT's with large channel width and different channel length is shown in Fig. 6. A big improvement of electron mobility is observed with channel length

Fig. 6. Mobility versus  $V_g - V_T$  of super TFT's with different channel length. The mobility of SOI nMOSFET is also plotted as a reference. The channel length and width of SOI MOSFET is 2  $\mu$ m and 1.1  $\mu$ m, respectively.

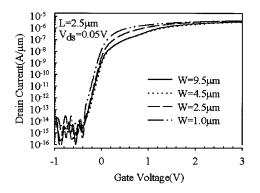

Fig. 7. Subthreshold characteristics of super TFT's with different channel width.

reduction, but it is still lower than that of SOI MOSFET's. Moreover, it is difficult to reduce the channel length of wide devices beyond 1  $\mu$ m due to the serious punchthrough effects. It is due to the existence of grain boundaries in the channel region of wide devices despite the small channel length, which degrade the electron mobility. In the grain enhancement process, the Ni strip is placed along the direction of gate as shown in Fig. 2. As a result, the longitudinal grain and their boundaries are parallel to the direction of carrier flow in the channel. For the wide and short channel super TFT's, it mostly happen that grain boundaries traverse from source to drain, which provide extra current paths and cause early punchthrough in short-channel devices. The existence of the extra leakage current path is also verified by the hump in the subthreshold region of wide devices as shown in Fig. 7. The hump disappeared when the width is reduced, indicating that the hump effect is not caused by the island edge effect, but from other leakage current path.

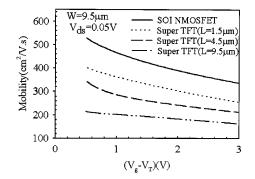

When the channel width is reduced, the probability of the channel region to cover a grain boundary in the width direction decreased significantly. Because the shape of the silicon grain is elongated with the major axis aligned in the direction perpendicular to the Ni strip, the dimension of grain along the channel length is normally larger than the dimension along the channel width as shown in Fig. 3. So the reduction of channel width is more important for getting a single grain TFT in our case. The carrier mobility of super TFT with different channel width is shown in Fig. 8. The mobility improved significantly with the channel width reducing. When channel width is equal

Fig. 8. Mobility versus  $V_g - V_T$  of super TFT's with different channel width. The mobility of SOI nMOSFET is also plotted as a reference. The device parameters of SOI MOSFET are the same as Fig. 6.

Fig. 9. (a) Subthreshold characteristics and (b)  $I_d$ - $V_d$  of n-channel and p-channel submicron super TFT's. The channel width is 0.7  $\mu$ m.

to 1.5  $\mu$ m, the carrier mobility is more or less identical with that of SOI MOSFET's, implying the whole device is already on a single crystal grain. An effective device design strategy can be obtained by adjusting the position of nickel strip as discussed in [14]. The channel length can be easily scaled down to submicron region for narrow width super TFT's due to its single crystal nature. Fig. 9 shows the subthreshold and  $I_d$ - $V_d$  characteristics of n-channel and p-channel super TFT's with  $L_G = 0.4 \ \mu$ m and 0.5  $\mu$ m respectively. The submicron super TFT's exhibit

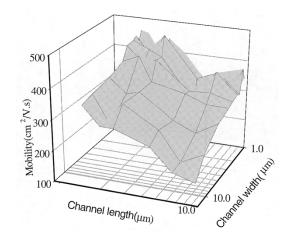

Fig. 10. Influence of device dimension on the mobility (at  $V_q - V_T = 1.0$  V).

very good characteristics, including a subthreshold slope of 72 mV/dec, a  $g_m$  of 198 mS/mm and an  $I_{d \text{ sat}}$  of 0.30 mA/ $\mu$ m at  $V_g - V_T = 1.5$  V for NMOS, which is much better than other reported high temperature TFT's developed for 3-D circuit application [9], [10]. The variation in mobility improvement as function of both channel length and width is shown in Fig. 10. Both channel width and length scaling are important to obtain high mobility because the smaller the channel region, the higher probability to get single grain super TFT's.

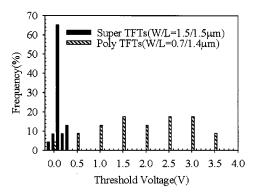

# C. Uniformity of Super TFT's

Device performance uniformity is another important factor for 3-D VLSI application. When the grain size is on the order of the device dimensions, uniformity can become very poor [8], [19]. In conventional poly TFT technology, it is difficulty to fabricate small-size devices with high performance and maintain uniform. It is because the average grain size is about 1  $\mu$ m by conventional crystallization method [20], [21]. Uniformity can be improved by significantly reducing the grain size or enhancing the grain size relative to channel dimension. The former is helpful for uniformity, but sacrifices the device performance. It is expected that the uniformity of device characteristics will improve when the device size becomes much smaller than the grain size. As very large grain can be obtained by this new high temperature MILC technique, we anticipated that small dimension super TFT's will demonstrate a good uniformity while maintaining high performance. The uniformity of device performance can be revealed by measuring the statistical variation of some device parameters. Threshold voltage  $V_T$  has been chosen in this particular study and result is shown in Fig. 11. 25 devices of each type have been measured for the statistical study. Conventional TFT's exhibit a serious performance variation, which is introduced by the random distribution of grains in channel region. The super TFT's exhibits much better uniformity due to the single-grain nature of their channel regions. Further improvement in uniformity is possible by optimized layout methodology.

Further study on the crystallization and device fabrication is in progress, recent experimental data show that the grain size

Fig. 11. Uniformity of the threshold voltage across the device wafer for conventional polysilicon TFT's and super TFT's. The standard deviation of the distribution for super TFT's and poly TFT's are 0.095 V and 1.05 V, respectively.

and grain growth rate can be increased furthermore through temperature optimizing.

#### V. CONCLUSION

A novel grain enhancement technique has been proposed in this paper to fabricate the high performance super TFT's. High temperature annealing has been introduced into conventional MILC process to enhance the grain size and improve the crystal integrity through secondary recrystallization. Significant improvements in TFT performance have been observed even for large devices with multiple grains in the channel. With the device size reduction, super TFT's with SOI CMOS performance, was achieved when the device channels were located with individual silicon grains. Very high uniformity were observed when devices were scaled down, indicating the technique's potential applicability in submicron or even in deep submicron circuits. The super TFTs process is compatible with CMOS technology, with only one extra mask added. This technique can be directly used in the load device of a SRAM cell to enhance the noise margin and reduce the leakage current, and further application can be used in mixed bulk/SOI circuits as well as 3-D stacked circuits with SOI-like transistor.

## REFERENCES

- [1] T. Uchida, "Present and future trend of electron device technology in flat panel display," in *IEDM Tech. Dig.*, 1991, pp. 5–10.

- [2] T. Tanaka *et al.*, "An LCD addressed by a-Si:H TFT's with peripheral poly-Si TFT circuits," in *IEDM Tech. Dig.*, 1993, pp. 389–392.

- [3] D. J. Radack, "Advanced microelectronics: The role of SOI," in *Proc. IEEE Int. SOI Conf.*, Oct. 1999, pp. 5–7.

- [4] F. Hayashi et al., "A highly stable SRAM memory cell with top-gated P<sup>-</sup>-N drain poly-Si TFT's for 1.5 V operation," in *IEDM Tech. Dig.*, 1996, pp. 283–286.

- [5] S. Miyamoto *et al.*, "High performance gate-all-around TFT (GAT) fro high-density, low-voltage-operation, and low-power SRAMs," in *Proc. Int. Symp. VLSI Technology, Systems, and Applications*, 1997, pp. 128–132.

- [6] H. Kuriyama et al., "A C-switch cell for low-voltage and high-density SRAM's," *IEEE Trans. Electron Devices*, vol. 45, pp. 2483–2488, Dec. 1998.

- [7] H. J. Cho, F. Nemati, P. B. Griffin, and J. D. Plummer, "A novel pillar DRAM cell for 4 Git and beyond," in *Proc. 1998 Symp. VLSI Technology Dig. Tech. Papers*, pp. 38–39.

- [8] T. Noguchi, "Appearance of single-crystalline properties in fin-patterned Si thin film transistor (TFT's) by solid phase crystallization (SPC)," *Jpn. J. Appl. Phys.*, vol. 32, pp. 1584–1587, Nov. 1993.

- [9] V. Subramanian and K. C. Saraswat, "High-performance germaniumseeded laterally crystallized TFT's for vertical device integration," *IEEE Trans. Electron Devices*, vol. 45, pp. 1934–1939, Sept. 1998.

- [10] V. Subramanian et al., "Low-leakage germanium-seeded laterally-crystallized single-grain 100-nm TFT's for vertical integration applications," *IEEE Electron Device Lett.*, vol. 20, pp. 341–343, July 1999.

- [11] S. Lee, Y. Jeon, and S. Joo, "Pd induced lateral crystallization of amorphous Si thin film," *Appl. Phys. Lett.*, vol. 66, no. 13, pp. 1671–1673, Mar. 1995.

- [12] S. Lee and S. Joo, "Low temperature poly-Si thin-film transistor fabrication by metal-induced lateral crystallization," *IEEE Electron Device Lett.*, vol. 17, pp. 160–162, Apr. 1996.

- [13] S. Jagar *et al.*, "SOI formation from amorphous silicon by metal-induced-lateral-crystallization (MILC) and subsequent high temperature annealing," in *Proc. IEEE Int. SOI Conf.*, Rohnert Park, CA, Oct. 1999, pp. 112–113.

- [14] S. Jagar *et al.*, "Single grain thin-film-transistor (TFT) with SOI COMS performance formed by metal-induced-lateral-crystallization," in *IEDM Tech. Dig.*, 1999, pp. 293–296.

- [15] L. K. Lam, S. Chen, and D. G. Ast, "Kinetics of nickel-induced lateral crystallization of amorphous silicon thin-film transistors by rapid thermal and furnace anneals," *Appl. Phys. Lett.*, vol. 74, pp. 1866–1868, Mar. 1999.

- [16] Z. Jin, K. Moulding, H. S. Kwok, and M. Wong, "The effects of extended heat treatment on Ni induced lateral crystallization of amorphous silicon thin films," *IEEE Trans. Electron Devices*, vol. 46, pp. 78–82, Jan. 1999.

- [17] G. A. Bhat, Z. Jin, H. S. Kwok, and M. Wong, "Effects of longitudinal grain boundaries on the performance of MILC-TFT's," *IEEE Electron Device Lett.*, vol. 20, pp. 97–99, Feb. 1999.

- [18] J. E. Palmer, C. V. Thompson, and H. I. Smith, "Grain growth and grain size distributions in thin germanium films," *J. Appl. Phys.*, vol. 62, pp. 2492–2497, Sept. 1987.

- [19] N. Yamauchi, J. J. Hajjar, and R. Reif, "Polysilicon thin-film transistors with channel length and width comparable to or smaller than the grain size of the thin film," *IEEE Trans. Electron Devices*, vol. 38, pp. 55–59, Jan. 1991.

- [20] M. K. Hatalis and D. W. Greve, "High-performance thin-film transistors in low-temperature crystallized LPCVD amorphous silicon films," *IEEE Electron Device Lett.*, vol. 8, p. 361, 1987.

- [21] V. Subramanian, P. Dankoski, L. Degertekin, B. T. Khuri-Yakub, and K. C. Saraswat, "Controlled two-step solid-phase crystallization for high-performance polysilicon TFT's," *IEEE Electron Device Lett.*, vol. 18, pp. 378–380, 1997.

**Hongmei Wang** received the B.S. and M.S. degrees in material science and engineering from Zhejiang University, Hangzhou, China, in 1990 and 1995, respectively, and the Ph.D. degree in electrical engineering from Peking University, Beijing, China in 1999.

Currently, she is a Postdoctoral Research Associate at the Hong Kong University of Science and Technology (HKUST). After receiving the B.S. degree, she joined in TunXi High-Pressure Valve Corporation, AnHui, China, as an Engineer for two

years, where she worked on mechanical mould design. From 1992 to 1995, she was engaged in research of microwave measurement in the department of material science and engineering at Zhejiang University, China. From January 1998 to April 1999, she was a Research Assistant in the Department of Electrical and Electronic Engineering, HKUST, Kowloon, Hong Kong. Her research interests include SOI CMOS technology, characterization, device modeling, novel devices structure and process.

Mansun Chan (M'96) received the B.S. degree in electrical engineering (highest honors) and the B.S. degree in computer science (highest honors) in 1990 and 1991 respectively, both from University of California at San Diego, La Jolla, and the M.S. and Ph.D. degrees, in 1994 and 1995, respectively, from the University of California, Berkeley.

During his undergraduate study, he worked with Rockwell International Laboratory on heterojunction bipolar transistor (HBT) modeling, where he developed the self-heating SPICE model for HBT. His re-

search at Berkeley covered a broad area in silicon devices ranging from process development to device design, characterization, and modeling. A major part of his work was on the development of recording breaking SOI technologies. he has also maintained a strong interest in device modeling and circuit simulation. He is one of the major contributors to the unified BSIM3 model for SPICE, which has recently been accepted by most US companies and SEMATECH as an industrial standard model. In January 1996, he joined Hong Kong University of Science and Technology, Kowloon, Hong Kong. His research interests include deep-submicron device technologies, image sensors, SOI technologies, high-speed and low power integrated circuite, device modeling, and automated characterization systems.

Singh Jagar was born in Manpur, HRY, India, in 1972. He received the B.Sc. degree and M.Sc. degrees in electronics from Kurukshetra University, India, in 1993 and 1995, respectively. He is currently pursuing the Ph.D. degree at the Hong Kong University of Science and Technology, Kowloon, Hong Kong. His Ph.D. research activities include fabrication and characterization of submicron TFT, MOS device simulation and modeling and flash EEPROM.

From 1996 to 1998, he was a Research Associate at the Indian Institute of Technology, Delhi, India. His research engaged in the development of silicon microswitch.

Vincent M. C. Poon (M'89) was born in Hong Kong in 1957. He received the B.Sc. degree in physics, M.Phil. and Ph.D. degrees in electronics from the Chinese University of Hong Kong in 1980, 1983, and 1989, respectively.

In 1988, he joined the Department of Electronic Engineering of the City Polytechnic of Hong Kong. In 1991, he joined the Department of Electrical and Electronic Engineering of the Hong Kong University of Science and Technology as a founding faculty. Since 1980, he has been working in the research and

development of various semiconductor materials and devices. His current work is on metal-induced silicon crystallization, flash memory, and nickel silicide technology. **Ming Qin** was born in Yangzhou, China, in 1967. He received the M.S., and Ph.D. degrees in electronic engineering from Southeast University, Nanjing, China, in 1994 and 1997, respectively.

From 1998 to 1999, he was a Visiting Research Associate in the Department of Electrical and Electronic Engineering, Hong Kong University of Science and Technology, Hong Kong. His current research interests are in low temperature crystallization of amorphous silicon, application of silicide on VLSI and sensors, and mirco-electro-mechanic systems.

Yangyuan Wang (SM'89) was born in Ningbo, China, in 1935. He graduated from the Department of Physics, Peking University, Beijing, China.

He is Director and Professor at the Institute of Microelectronics, Peking University. He has been reseaching in advanced technology devices and structure of VLSI and has published more than 100 papers.

Prof. Wang is an academician of the Academy of Science of China.

**Ping K. Ko** (F'96) received the B.S. degree in physics with special honors from Hong Kong University in 1974, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Berkeley (UCB), in 1978 and 1982, respectively. His research interest includes high speed VLSI devices, technology, and circuits; MOS device modeling for circuits simulation; and CAD tools for integrated circuit design.

In 1982 and 1983, he was with Bell Laboratories, Holmdel, NJ, leading a research team to develop

high-speed MOS technologies for communications circuits. He joined the UCB faculty in 1984. He was the Director of the Berkeley Microfabrication Laboratory from 1984 to 1993 and the Vice Chairman of the Department of Electrical, Electronic, and Computer Science from 1991 to 1993. He came to the Hong Kong University of Science and Technology in August 1993 as Visiting Professor in the Department of Electrical and Electrical Engineering until April 1995, and has been Dean of Engineering since May 1995. He has authored or co-authored one book and over 200 research papers. His works on MOS technology, MOS device physics and modeling, and integrated circuit reliability are renowned worldwide. He has extesive experience serving the the industrial as well as the professional and academic communities.

Prof. Ko was Associate Editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES from 1988 to 1990 and was on the program committee of many major international conferences. He has been chairman of HK Research Grants Council since January 1994 and member of the UPGC since April 1993.