# Superconductive Circuits and the General-Purpose Electronic Simulator APLAC

# Mikko Kiviranta 🕩

*Abstract*—The general-purpose circuit simulator analysis program for linear active circuits (APLAC) is not widely known within the superconductor circuit community, regardless of its built-in Josephson junction model and capability of modeling the superconductive phase transition with controlled sources. We review the use of APLAC to model, e.g., noisy dc SQUIDs and transition-edge sensors. Based on an APLAC simulation, we also comment on the preference of voltage bias over current bias in dc SQUIDs in applications where large dynamic range and high bandwidth are simultaneously required.

*Index Terms*—Circuit simulation, Josephson junctions (JJ), SQUIDs, superconducting device noise, superconducting integrated circuits, superconducting photodetectors.

# I. INTRODUCTION

**B** EHAVIOR of linear superconductive circuits can be assessed with standard analytic techniques of the electronic circuit theory when the second Kirchhoff's law is replaced by the statement that rather than voltages, time integrals of voltages (i.e., fluxes) around closed loops sum to zero, or more generally to integer multiples of the flux quantum  $\Phi_0$ . Numerical treatment is however often necessary when second-order effects, such as the kinetic inductance or nonlinear phenomenon such as the Josephson effect or the superconductive phase transition, are of interest. In the early days of Josephson junction (JJ) studies, a lot of effort was invested in task-specific computer code for Josephson-dynamical simulation, but some general-purpose electronics simulators were also devised. These include WR-SPICE [1], PSCAN [2], and JSIM [3]. More recently, interest in large-scale implementations of RSFQ logic has driven further development of the electronic design automation (EDA) tools for Josephson circuits, leading to such simulators as [4] and [5]. Over the past decades, the slow speed of interpreted EDA simulators has prevented their serious use in studying, e.g., noisy Josephson dynamics, but the rapid increase of easily accessible computation power has made their use feasible in many cases.

Regardless of its moderately wide use at least within the Finnish superconductor community, in the literature one design

Manuscript received September 21, 2020; revised February 8, 2021; accepted March 4, 2021. Date of publication March 25, 2021; date of current version April 20, 2021. This work was supported by the Finnish Centre of Excellence in Quantum Technology, Academy of Finland, under Grant 312059. This article was recommended by Associate Editor J. Beyer.

The author is with the VTT Technology Research Centre of Finland, 02150 Espoo, Finland (e-mail: mikko.kiviranta@vtt.fi).

This article has supplementary material provided by the authors and color versions of one or more figures available at https://doi.org/10.1109/TASC.2021. 3068780.

Digital Object Identifier 10.1109/TASC.2021.3068780

tool has been rarely mentioned: the Analysis Program for Linear Active Circuits (APLAC). In this article, we describe how APLAC has been used at VTT for superconducting circuits, in particular for studying noise behavior of dc SQUIDs and dynamics of transition edge sensors (TESs).

# II. APLAC AS A SIMULATION TOOL

Originating from the Radio Laboratory and the Circuit Theory Laboratory of the Helsinki University of Technology (HUT, currently Aalto University), roots of the APLAC program are almost as old [6], [7] as those of the more famous SPICE circuit simulator. From the mid-1980s onwards, a significant amount of resources was invested into APLAC development [8], owing to the interest of the Nokia Corporation to utilize it as a microwave design tool. A commercial company APLAC Solutions Corporation was founded in 1998 for further development, first acquired in 2005 by AWR Corporation, further acquired by the Cadence Design Systems recently.

It is moderately easy to implement the JJ by using controlled sources, with one voltage node reserved to represent the quantum phase [2]. An example JJ circuit implemented for LT-SPICE IV is available in [9]. A similar construction with controlled sources is also possible in APLAC. In the late 1980s, Heikki Seppä of VTT and Tapani Ryhänen of HUT, however, collaborated with Timo Veijola to build the JJ as a standard library item [10] compiled into the APLAC core. The addition of new elements was alleviated by the 1988 rewrite of the APLAC code in the C language with fully object-oriented techniques [11]. A builtin JJ model brought in faster simulation times as well as easy schematic capture and compact representation in the captured diagrams.

The JJ as a library component has continued to be available up to the current APLAC version 8.70 as of the year 2020. A quirk, worth noting in the JJ implementation in APLAC, is that the value of the flux quantum is precisely 2.07 mV·ps rather than its correct value 2.0678 ... mV·ps.

#### **III. SIMULATION OF JOSEPHSON DYNAMICS**

# A. DC-SQUID Example

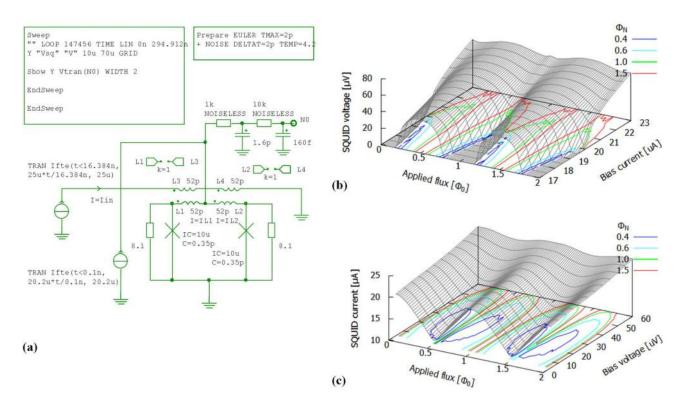

An example of a current biased dc SQUID is shown in Fig. 1(a), as copy-pasted from the APLAC schematic editor. The schematic and netlist files are available in [9]. The SQUID loop is formed by inductors L1 and L2, coupled to the input coil L3 and L4 by mutual couplings with the coupling constant k = 1. The shown dimensioning leads to the Stewart–McCumber parameter

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Fig. 1. (a) Current-biased APLAC circuit for simulating a noisy dc-SQUID, with the Josephson critical current  $I_{\rm C} = 10 \ \mu$ A, junction capacitance  $C_{\rm J} = 0.35$  pF, and shunt resistance  $R_{\rm S} = 8.1 \ \Omega$  chosen for  $\beta_C = 0.7$ ; loop inductance  $L_{\rm SQ} = 104$  pH chosen for  $\beta_L = 1.0$ , and simulation temperature T = 4.2 K. (b) Current-biased SQUID characteristics and flux noise contours  $\Phi_{\rm N}$  in the units of  $\mu \Phi_0 / \text{Hz}^{1/2}$ , obtained by simulating the circuit (a) at many bias and flux setpoints. Flux noise levels were computed by Fourier transforming the time trace of the output voltage in the manner detailed in [9]. (c) Voltage-biased SQUID characteristics were obtained with an added bias inductor [15].

(dimensionless junction capacitance) [12]  $\beta_C = 0.7$ , and the dimensionless loop inductance of  $\beta_L = 2L_{SQ}I_C/\Phi_0 = 1.0$ . The time-domain simulation with  $\Delta t = 2$  ps starts with a 2<sup>14</sup>-step initialization phase, whereby the SQUID bias and the input coil currents are driven from zero to their nominal values and the dynamics is settled. This is followed by a 2<sup>17</sup>-step stationary state, during which data are acquired, e.g., for noise analysis. There is a two-pole low-pass filter to remove the Josephson oscillation from the signal and to provide just the average voltage when plotting the SQUID characteristics. If characteristics alone are desired, the long steady state is not needed. Examples of the generated waveforms are found in [9].

## B. Simulating the Noisy DC-SQUID

The noise estimation for a dc SQUID with APLAC can be performed in many ways. It is possible to use time-domain simulation to obtain the mixing coefficients, akin to the approach [13], as has been performed in [14]. As APLAC also includes the Harmonic Balance (HB) analysis mode, in the voltage-biased case (where the Josephson frequency is *a prior*i known) it is in principle possible to separate the evolution of the quantum phase into the linearly progressing and periodic parts:  $\theta(t) = \frac{2\pi U_B}{\Phi_0} \times t + \chi(t)$ , where  $U_B$  is the bias voltage. An HB circuit can then be constructed for  $\chi(t)$  for obtaining mixing coefficients via simulation. These HB circuits have tended to be unreliable in convergence, however. Most straightforward is the Langevin approach in the time domain, where time-domain Gaussian voltage noise generators are added in series with the junction shunt resistors. In the early versions of APLAC, we inserted the generators by hand as elaborated in [9], but in the more recent versions, we have found the built-in noise models of APLAC to function quite reliably, and the explicit generators are no longer necessary. The APLAC-internal noise models are activated by the Prepare ... NOISE statement in the schematic Fig. 1(a).

In Fig. 1(b), the results from the current-biased circuit of Fig. 1(a) are shown when the circuit is invoked at 13 bias current and 100 applied flux values, and the output voltage noise during the  $2^{17}$ -step steady state is estimated by a Fourier transform of the time trace. In the noise simulation, the  $2^{14}$ -step initialization stage is followed by another  $2^{14}$ -step stage where a sinusoidal 10 m $\Phi_{0p-p}$  flux excitation is applied and the SQUID gain  $dV/d\Phi$  is determined. Noise sources are then activated for  $2^{17}$ -step output voltage record. The output voltage noise is then scaled by the  $dV/d\Phi$  to obtain the flux noise, which is plotted as contours in Fig. 1(b). This APLAC simulation consisting of 1300 iterations with 163 840 time steps at each iteration takes roughly 75 min on a Core-i7 equipped laptop computer running Windows 10.

Fig. 1(c) shows the noise contours of a similar circuit with voltage bias. An inductor has been added between the bias voltage source and the SQUID, as described in [15]. The SQUID output current is recorded here and scaled by the  $dI/d\Phi$  to obtain

FIMPLACU PAPERILU W CAP L

\data\aplac\jjdyn\JJ N lacVar Vgp=2.7m CONST lacVar VgpW=0.1m CONST

CONST

GAP E.

flux noise. Both current- and voltage-biased simulations were performed with the noise-generating temperature of T = 4.2 K.

#### C. Remarks on the Noisy DC-SQUID Results

Although the circuit of Fig. 1(a) implements a particular set of component values, the results can be scaled into dimensionless units [16], whereby they should be applicable to any dc-SQUID with the dimensionless junction capacitance  $\beta_C = 0.7$ , the dimensionless loop inductance  $\beta_L = 1.0$ , and the dimensionless noise energy  $\Gamma = 2\pi k_B T / I_C \Phi_0 = 0.018$ . We are particularly interested to compare the numerically determined prefactor  $\gamma$ in the formula  $\varepsilon = \gamma k_B T \sqrt{L_{SQ}C_J}$  for the SQUID energy resolution  $\varepsilon$  in terms of the loop inductance  $L_{SQ}$  and junction capacitance  $C_J$ . The flux noise contours in the plots Fig. 1(b) and (c) of  $\Phi_N = 0.4, 0.6, 1.0$  and  $1.5 \ \mu \Phi_0 / H z^{1/2}$  correspond to  $\gamma = 9.4, 21, 60$ , and 130, respectively.

The canonical work for finding the SQUID noise optimum [16]–[18] has taken place solely with current bias, and only a narrow flux range of low-noise operating points has been deemed necessary as the flux-locked loop (FLL) [19] has traditionally been assumed to keep the SQUID flux close to the sweet spot. For instance, de Waal *et al.* [17] find  $\gamma = 12$  in a narrow flux range with bias current  $I_B = 1.6 \cdot I_C$  where not all flux settings lead to a finite SQUID voltage. We verify comparable or better  $\gamma$  values in the current-biased case [see Fig. 1(b)] in narrow ranges of applied flux when the bias current  $I_B < 2I_C$ . The value  $\gamma = 16/\beta_C^{1/2}$  from [20] is compatible with our data at  $I_B \gtrsim 2I_C$ . In addition to the intrinsic flux noise, also the  $dV/d\Phi$  finds a wider range of high values when using voltage bias [9]. The gain  $dV/d\Phi$  determines how voltage noise of the readout amplifier translates into the effective flux noise. In the voltage biased case, an equivalent gain is determined as  $dV/d\Phi = R_D \cdot dI/d\Phi$ , where  $R_D = dV/dI$  is the SQUID dynamic resistance at the setpoint.

We note that modern wideband SQUID applications, such as detector multiplexing [21], require a wide operating flux range, as large loop gain cannot be achieved in FLL-like negative feedback schemes if large bandwidth is desired [19]. Voltage bias [see Fig. 1(c)] not only yields more linear characteristics, but also a wider flux range of low-noise setpoints. Matched bias [22] lies between voltage and current bias and yields behavior (not shown here) between the current and voltage biased cases. In the matched bias, the load line due to the bias source is chosen roughly equal to the dynamic resistance of the SQUID.

The advantage of using an APLAC-like EDA tool is that it is trivial to augment the circuit [see Fig. 1(a)], e.g., by the backaction noise measurement or by adding parasitic circuit elements. Due to the targeted main commercial use of the simulator, APLAC natively contains a large number of microwave-related elements, such as transmission lines, stubs, and couplers.

# D. Beyond the Resistively and Capacitively Shunted Junction (RCSJ) Model

It is possible to simulate the behavior of JJs shunted in a more complex manner than the standard RCSJ model. This opens the possibility of modeling, e.g., the DROS [23], the un-SQUID

$I_C = 100 \ \mu\text{A}$  and the subgap current modeled by the tanh() function. (Bottom left) The simulated JJ characteristics plotted on the current-voltage axes, with the bias current swept 1.6  $\mu$ A -> 156.6  $\mu$ A -> 1.6  $\mu$ A, and exhibiting a switch to the finite-voltage state at the 100  $\mu$ A bias current. (Bottom right) The time trace of the junction voltage demonstrates how the 1.6  $\mu$ A end current leaves the JJ above the retrapping threshold where the JJ remains at a finite voltage and keeps Josephson oscillating.

[24], or non-RCSJ style RSFQ circuits. Fig. 2(a) demonstrates a model that generates characteristics typically observed for a physical thin-film JJ. Here, the nonlinear subgap resistance is modeled by a nonlinear voltage-controlled current source, utilizing the hyperbolic tangent function. The current-biased model shows the hysteretic [12] IV-response [see Fig. 1(b)] familiar to any experimentalist. The response contains the zero-voltage branch when  $I_B < I_C$ , transition to the finite-voltage state at  $I_B = I_C$ , and the approach toward the zero voltage along the subgap branch when the bias current  $I_B$  is lowered.

In this particular simulation, the bias current is designed not to return to zero at the end of the sweep, for the sake of demonstrating the retrapping behavior of hysteretic JJs. The current remains at  $I_B = 1.6 \ \mu A$  for the final 2 ns at t > 8ns [see the time-to-voltage plot Fig. 2)c)]. Such  $I_B$  causes the average voltage in the subgap branch  $\langle V_{JJ} \rangle \approx 200 \ \mu V$  to remain above the retrap voltage, and the supercurrent keeps oscillating at ~100 GHz. If bias is lowered to  $I_B = 1.5 \ \mu A$ , the supercurrent oscillation frequency gets sufficiently below the plasma frequency of the JJ that retrapping occurs, and the JJ decays to the non-oscillating zero-voltage state within the final 2 ns of the simulation.

Although the circuit [see Fig. 2(a)] has converged fine with APLAC 7.61, we note that the statement Prepare TRANMODE 0 needs to be added in APLAC 8.70 for stable simulation.

65536 TIME LIN 0 10

WINDOW 1 Y Vtran(NO)

0) Itran(Itot)

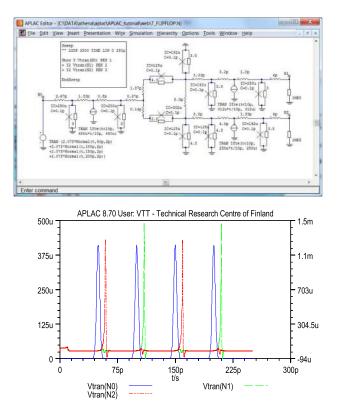

Fig. 3. Example of an RSFQ circuit simulation: the T-flip flop taken from [25]. When the toggle input (blue, solid, voltage referred to the left Y-axis) is driven with Gaussian-shaped SFQ pulses, the Q- (dashed) and Q-hat (dash-dot) outputs show alternating SFQ pulses (referred to the right Y-axis). JJs are resistively shunted to obtain  $\beta_{\rm C} = 0.7$ .

# E. More Complex Josephson Circuits

As a demonstration, we show in Fig. 3 the APLAC simulation of the RSFQ T-flip flop taken from [25]. Simulating over 2500 time steps with  $\Delta t = 0.1$  ps consumes 0.2 s of CPU time on the Core-i7 laptop. The netlist and schematic are available in [9]. The waveforms indicate the correct T-flip flop operation, with alternating SFQ pulses appearing in the two outputs.

## **IV. SIMULATING TESS**

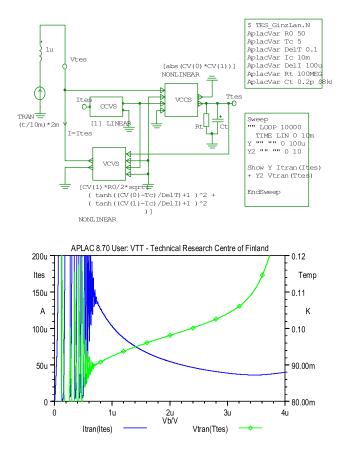

Voltage nodes of a circuit simulator can be used to represent other physical quantities and current branches to represent other physical flows, in a similar manner as the quantum phase is represented as a node voltage in the LT-SPICE implementation of the JJ in [9]. Fig. 4 shows an implementation of a TES, taken from [26] and updated for the current APLAC version 8.70. We have used the TES model primarily to study the TES-readout interaction, e.g., electrothermal stability related to the *LC* resonator settling time in frequency-domain multiplexed SQUID readouts [21] and feasibility of the pulsed-bias time-domain multiplexing [26].

To get the TES simulation started, it is necessary to model both temperature-driven and bias current-driven (magnetic) transition from the superconducting to the resistive state. All variables in the simulation start from zero, and the TES is driven to its setpoint through the transition during the first few milliseconds of simulation. The model of the transition used here is

Fig. 4. (Top) Implementation of the TES utilizing controlled sources. (Bottom) The simulated TES current (plain line) as the bias voltage is swept from zero to  $4 \mu V$ . The current shows the characteristic negative dynamic resistance, as well as the electrothermal oscillation due to the series inductance in the bias circuit at low voltages. The TES internal temperature (with markers) is also plotted.

phenomenological, rather than one describing the accurate internal functioning of the TES.

The voltage of the "Ttes" node represents the TES temperature, and the node can be driven by current to model the heat flow due to incoming radiation. Examples of a dc-biased and ac-biased TES reacting to X-ray photons are given in [9], where a more detailed description of the model is also available.

#### V. CONCLUSION

We have found, over the years, APLAC to be a very useful tool in the design of practical SQUIDs and in understanding TES dynamics. Its long-standing commercial support and wide range of library components make it easier to simulate hybrids of Josephson-, TES- and more traditional electronic circuits. The APLAC facilities for hierarchical design alleviate modeling complex circuitry.

As a demonstration of APLAC capabilities, we have reproduced the canonical noise optima of the dc SQUID, while extending the set of simulated bias and flux region to exhaust the assumed "reasonable" range of values. In addition, we have extended the flux noise estimation to the voltage-biased case.

#### ACKNOWLEDGMENT

The author would like to thank J. Luomahaara and D. Hazra for commenting on the article.

#### REFERENCES

- S. R. Whiteley, "Josephson junctions in SPICE3," *IEEE Trans. Magn.*, vol. 27, no. 2, pp. 2902–2905, 1991.

- [2] S. V. Polonsky, "PSCAN—Personal superconductor circuit analyzer," Supercond. Sci. Technol., vol. 4, pp. 667–670, 1991.

- [3] E. S. Fang and T. van Duzer, "An efficient method for finding dc solutions for Josephson circuits," *IEEE Trans. Appl. Supercond.*, vol. 1, no. 3, pp. 126–133, Sep. 1991.

- [4] J. A. Delport, K. Jackman, P. le Roux, and C. J. Fourie, "JoSIM— Superconductor SPICE simulator," *IEEE Trans. Appl. Supercond.*, vol. 29, no. 5, Aug. 2019, Art. no. 1300905.

- [5] S. Razmkhah and P. Febvre, "JOINUS: A user-friendly open-source software to simulate digital superconductor circuits," *IEEE Trans. Appl. Supercond.*, vol. 30, no. 5, Aug. 2020, Art. no. 1300807.

- [6] M. Valtonen, "APLAC1—A flexible frequency domain circuit analysis program for small computers," Radio Laboratory, Helsinki Univ. Technol., Espoo, Finland, Rep. S55, 1973.

- [7] M. Valtonen, "APLAC2—A flexible DC and time domain circuit analysis program for small computers," Radio Laboratory, Helsinki Univ. Technol., Espoo, Finland, Rep. S56, 1973.

- [8] O. Pekonen, A. Karhumäki, and M. Valtonen, "An object-oriented circuit simulator," Microw. J., Jul./Jan. 2000. [Online]. Available: https://www.microwavejournal.com/articles/3010-an-object-orientedcircuit-simulator

- [9] M. Kiviranta, "Josephson dynamical simulation using the electronic circuit simulator APLAC: A tutorial," arXiv:2103.11465.

- [10] H. Seppä, private communication, May 2020.

- [11] APLAC 6.0 User's Manual, Helsinki Univ. Technol., Helsinki, Finland, Oct./Nov. 1991, p. 1.

- [12] D. E. McCumber, "Effect of ac impedance on dc voltage-current characteristics of superconductor weak-link junctions," *J. Appl. Phys.*, vol. 39, no. 7, pp. 3113–3118, 1968.

- [13] K. K. Likharev and V. K. Semenov, "Fluctuation spectrum in superconducting point junctions," *JETP Lett.*, vol. 15, no. 6, pp. 442–445, 1972.

- [14] M. Kiviranta, "The unshunted SQUID revisited," *Supercond. Sci. Technol.*, vol. 24, no. 6, 2011, Art. no. 065003.

- [15] M. Kiviranta and H. Seppä, "Effect of voltage bias on the dc SQUID characteristics," J. Low Temp. Phys., vol. 123, no. 1/2, pp. 127–136, 2001.

- [16] C. D. Tesche and J. Clarke, "DC SQUID: Noise and optimization," J. Low Temp. Phys., vol. 29, no. 3/4, pp. 301–331, 1977.

- [17] V. J. de Waal, P. Schrijner, and R. Llurba, "Simulation and optimization of a dc SQUID with finite capacitance," *J. Low Temp. Phys.*, vol. 54, no. 3/4, pp. 215–232, 1984.

- [18] T. Ryhänen, H. Seppä, R. Ilmoniemi, and J. Knuutila, "SQUID magnetometers for low-frequency applications," J. Low Temp. Phys., vol. 76, no. 5/6, pp. 287–386, 1989.

- [19] D. Drung, "High- $T_c$  and low- $T_c$  dc SQUID electronics," *Supercond. Sci. Technol.*, vol. 16, no. 12, pp. 1320–1336, 2003.

- [20] J. Clarke, "Principles and applications of SQUIDs," Proc. IEEE, vol. 77, no. 8, pp. 1208–1223, Aug. 1989.

- [21] J. N. Ullom and D. A. Bennett, "Review of superconducting transitionedge sensors for X-ray and gamma-ray spectroscopy," *Supercond. Sci. Technol.*, vol. 28, no. 8, 2015, Art. no. 084003.

- [22] M. Kiviranta, L. Grönberg, and H. Sipola, Two-stage locally linearized SQUID readout for frequency domain multiplexed calorimeter arrays," *Supercond. Sci. Technol.*, vol. 24, no. 4, 2015, Art. no. 045003.

- [23] D. J. Adelerhof, H. Nijstad, J. Flokstra, and H. Rogalla, "Relaxation oscillation SQUIDs with high dV/dΦ," *IEEE Trans. Appl. Supercond.*, vol. 3, no. 1, pp. 1862–1865, Mar. 1993.

- [24] H. Seppä, M. Kiviranta, and L. Grönberg, "DC SQUID based on unshunted josephson junctions: Experimental results," *IEEE Trans. Appl. Supercond.*, vol. 5, no. 2, pp. 3248–3251, Jun. 1995.

- [25] S. V. Polonsky *et al.*, "New RSFQ circuits (Josephson junction digital devices)," *IEEE Trans. Appl. Supercond.*, vol. 3, no. 1, pp. 2566–2577, Mar. 1993.

- [26] M. Kiviranta, J. van der Kuur, H. Seppä, and P. de Korte, "SQUID multiplexers for transition-edge sensors," in *Proc. Far-IR, Sub-mm mm Detect. Technol. Workshop*, Monterey CA, USA, Apr. Jan./Mar. 2002, pp. 237–242. [Online]. Available: http://www.iki.fi/msk/xeus/mm02\_ 505pre.pdf