## Supervised Design-Space Exploration

## Hung-Yi Liu

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

©2015

Hung-Yi Liu

All Rights Reserved

#### **ABSTRACT**

### Supervised Design-Space Exploration

### Hung-Yi Liu

Low-cost Very Large Scale Integration (VLSI) electronics have revolutionized daily life and expanded the role of computation in science and engineering. Meanwhile, process-technology scaling has changed VLSI design to an exploration process that strives for the optimal balance among multiple objectives, such as power, performance, and area, i.e. multi-objective Pareto-set optimization. Besides, modern VLSI design has shifted to synthesis-centric methodologies in order to boost the design productivity, which leads to better design quality given limited time and resources. However, current decade-old synthesis-centric design methodologies suffer from: (i) long synthesis tool runtime, (ii) elusive optimal setting of many synthesis knobs, (iii) limitation to one design implementation per synthesis run, and (iv) limited capability of digesting only component-level designs as opposed to holistic system-wide synthesis. These challenges make Design Space Exploration (DSE) with synthesis tools a daunting task for both novice and experienced VLSI designers, thus stagnating the development of more powerful (i.e. more complex) computer systems.

To address these challenges, I propose Supervised Design-Space Exploration (SDSE), an abstraction layer between a designer and a synthesis tool, aiming to autonomously supervise synthesis jobs for DSE. For system-level exploration, SDSE can approximate a system Pareto set given limited information: only lightweight component characterization is required, yet the necessary component synthesis jobs are discovered on-the-fly in order to compose the system Pareto set. For component-level exploration, SDSE can approximate a component Pareto set by iteratively refining the approximation with promising knob settings, guided by synthesis-result estimation with machine-learning models. Combined, SDSE has been applied with the three major synthesis stages, namely high-level, logic, and physical synthesis, to the design of heterogeneous accelerator cores as well as high-performance processor cores. In particular, SDSE has been successfully integrated

into the IBM Synthesis Tuning System, yielding 20% better circuit performance than the original system on the design of a 22nm server processor that is currently in production.

Looking ahead, SDSE can be applied to other VLSI designs beyond the accelerator and the programmable cores. Moreover, SDSE opens several research avenues for: (i) new development and deployment platforms of synthesis tools, (ii) large-scale collaborative design engineering, and (iii) new computer-aided design approaches for new classes of systems beyond VLSI chips.

# Contents

| Li       | st of | Figure | es                                       | vi   |

|----------|-------|--------|------------------------------------------|------|

| Li       | st of | Tables | 5                                        | xii  |

| 1        | Intr  | oducti | ion                                      | 1    |

|          | 1.1   | What   | is Design?                               | . 1  |

|          | 1.2   | Copin  | g with Complex Computer System Design    | 3    |

|          | 1.3   | Challe | enges of Electronic System Level Design  | 6    |

|          | 1.4   | Thesis | Contributions                            | 11   |

|          | 1.5   | Outlin | ne of The Dissertation                   | 13   |

| <b>2</b> | Bac   | kgroui | ${f ad}$                                 | 15   |

|          | 2.1   | Design | a Complexity of SoC with CAD Tools       | 15   |

|          |       | 2.1.1  | The Rise of Heterogeneous Architectures  | 16   |

|          |       | 2.1.2  | ASIC Design Flow                         | 17   |

|          |       | 2.1.3  | Next Generation CAD Tools                | 20   |

|          | 2.2   | Overv  | iew of Related Works                     | 22   |

|          |       | 2.2.1  | Component-Level Design-Space Exploration | 22   |

|          |       | 2.2.2  | System-Level Design-Space Exploration    | . 24 |

| Ι  | $\mathbf{Sys}$ | stem-Level Design-Space Exploration                | 25 |

|----|----------------|----------------------------------------------------|----|

| 3  | Syn            | thesis Planning for Exploring ESL Design           | 26 |

|    | 3.1            | Problem Description                                | 27 |

|    | 3.2            | An Exploration-and-Reuse Design Methodology        | 30 |

|    | 3.3            | Component Design-Space Pruning                     | 34 |

|    | 3.4            | System Design-Space Exploration                    | 40 |

|    | 3.5            | Experimental Results                               | 44 |

|    | 3.6            | Remarks                                            | 48 |

| 4  | Cor            | npositional Approximation for SoC Characterization | 53 |

|    | 4.1            | Problem Description                                | 55 |

|    | 4.2            | Compositional Approximation of Pareto Sets         | 58 |

|    |                | 4.2.1 Single Component                             | 58 |

|    |                | 4.2.2 Many Components                              | 60 |

|    | 4.3            | Experimental Results                               | 62 |

|    | 4.4            | Remarks                                            | 72 |

| II | C              | omponent-Level Design-Space Exploration            | 73 |

| 5  | Kno            | ob-Setting Optimization for High-Level Synthesis   | 74 |

|    | 5.1            | Problem Description                                | 76 |

|    | 5.2            | An Iterative Refinement Framework                  | 77 |

|    | 5.3            | Learning-Model Selection                           | 78 |

|    | 5.4            | Transductive Experimental Design                   | 81 |

|    | 5.5            | Scalable Design-Space Sampling                     | 84 |

|    | 5.6            | Case Study on DFT                                  | 86 |

|    |                | 5.6.1 Basic DSE-with-HLS Results                   | 87 |

|    |                | 5.6.2 Extreme DSE-with-HLS Results                 | 88 |

|    | 5 7            | Additional Results on CHStone Suite                | 89 |

|    |     | 5.7.1          | Experimental Setup                                 | . 90  |

|----|-----|----------------|----------------------------------------------------|-------|

|    |     | 5.7.2          | Discussions                                        | . 92  |

|    | 5.8 | Remai          | rks                                                | . 97  |

| 6  | Par | amete          | r Tuning for Physical Synthesis                    | 100   |

|    | 6.1 | Proble         | em Description                                     | . 100 |

|    | 6.2 | IBM S          | Synthesis Tuning System                            | . 102 |

|    |     | 6.2.1          | Initial Design Space Reduction                     | . 104 |

|    |     | 6.2.2          | Rules File and Cost Function                       | . 106 |

|    |     | 6.2.3          | Tuning/Archiving Loops and Macro Construction Flow | . 107 |

|    |     | 6.2.4          | Addressing SynTunSys Overhead                      | . 108 |

|    | 6.3 | Decisi         | on Engine Algorithms                               | . 110 |

|    |     | 6.3.1          | The Base Decision Algorithm                        | . 110 |

|    |     | 6.3.2          | The SDSE Learning Algorithm                        | . 111 |

|    |     | 6.3.3          | The SDSE Jump-Start Sensitivity Test               | . 114 |

|    | 6.4 | Exper          | imental Results                                    | . 115 |

|    |     | 6.4.1          | Application to an IBM 22nm Server Processor        | . 115 |

|    |     | 6.4.2          | Learning vs. Base Algorithm Results                | . 117 |

|    |     | 6.4.3          | Jump-Start Sensitivity Test Exploration            | . 121 |

|    | 6.5 | Remai          | rks                                                | . 122 |

| II | I E | $\Sigma$ xtend | ling Supervised Design-Space Exploration           | 124   |

| 7  | Coc | le Refa        | actoring with Frequent Patterns                    | 125   |

|    | 7.1 | Proble         | em Description                                     | . 126 |

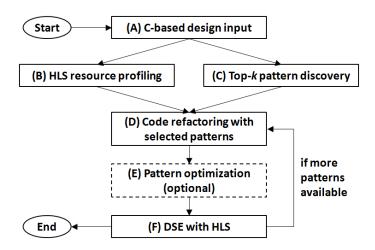

|    | 7.2 | A Coo          | de-Refactoring Design Methodology                  | . 127 |

|    |     | 7.2.1          | Pattern Selection                                  | . 131 |

|    | 7.3 | Patter         | en Discovery Algorithms                            | . 133 |

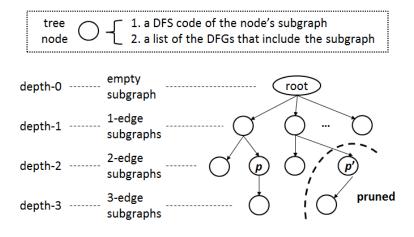

|    |     | 7.3.1          | The gSpan Algorithm                                | . 134 |

|    |     | 732            | Enhanced   Span                                    | 135   |

|              | 7.4                       | Exper                                     | imental Results                   | . 136                       |

|--------------|---------------------------|-------------------------------------------|-----------------------------------|-----------------------------|

|              |                           | 7.4.1                                     | DSE Result Improvements           | . 139                       |

|              |                           | 7.4.2                                     | HLS Runtime Reduction             | . 140                       |

|              |                           | 7.4.3                                     | gSpan vs. Enhanced gSpan          | . 142                       |

|              | 7.5                       | Remai                                     | rks                               | . 144                       |

| 8            | Fut                       | ure Re                                    | esearch Directions                | 147                         |

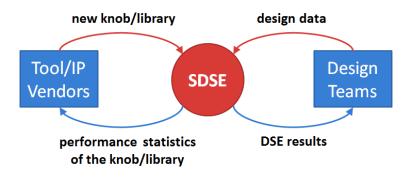

|              | 8.1                       | SDSE                                      | as a Platform                     | . 147                       |

|              | 8.2                       | Collab                                    | porative Design-Space Exploration | . 149                       |

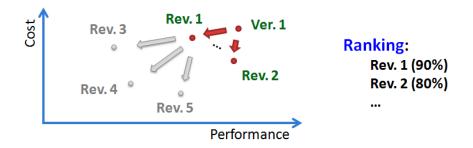

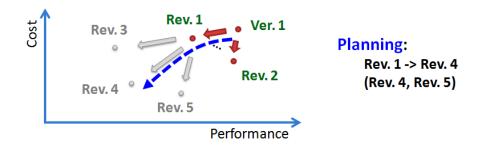

|              |                           | 8.2.1                                     | Revision Ranking                  | . 150                       |

|              |                           | 8.2.2                                     | Revision Planning                 | . 152                       |

|              | 8.3                       | Beyon                                     | d Synthesis and SoC-Design        | . 153                       |

| 9            | Con                       | clusio                                    | ns                                | 158                         |

| IJ           | / В                       | Sibliog                                   | raphy                             | 160                         |

| Bi           | ibliog                    | graphy                                    |                                   | 161                         |

| $\mathbf{V}$ |                           |                                           |                                   |                             |

| ٧            | $\mathbf{A}_{\mathbf{l}}$ | ppend                                     | ices                              | 182                         |

|              | •                         |                                           | ices<br>e Tools                   | 182<br>183                  |

|              | Pro                       | totype                                    |                                   | 183                         |

|              | Pro                       | totype<br>SPEE                            | e Tools                           | <b>183</b>                  |

|              | Pro                       | totype<br>SPEE                            | e <b>Tools</b><br>D               | 183 . 184 . 184             |

|              | Pro                       | totype<br>SPEE<br>A.1.1                   | e Tools D                         | 183 . 184 . 184 . 184       |

|              | Pro                       | totype<br>SPEE<br>A.1.1<br>A.1.2          | E Tools D                         | 183 . 184 . 184 . 185       |

|              | Pro                       | totype<br>SPEE<br>A.1.1<br>A.1.2<br>A.1.3 | E Tools D                         | 183 . 184 . 184 . 185 . 188 |

|              | Pro                       | SPEE A.1.1 A.1.2 A.1.3 CAPS               | E Tools  D                        | 183 . 184 . 184 . 185 . 188 |

| A.3 | LEIST | TER                   |

|-----|-------|-----------------------|

|     | A.3.1 | Software Requirements |

|     | A.3.2 | File Structure        |

|     | A.3.3 | Tutorial              |

| A.4 | EgSpa | n                     |

|     | A.4.1 | Software Requirements |

|     | A.4.2 | File Structure        |

|     | A.4.3 | Tutorial              |

# List of Figures

| 1.1 | A conceptual model of design (source: [150])                                                    | 2  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 1.2 | Design-space exploration. The function $f$ for specification-to-object mapping cor-             |    |

|     | responds to the construction of the design object. Suppose that the objectives are              |    |

|     | design cost and performance in terms of latency (both to be minimized). The red                 |    |

|     | Pareto front features the optimized objects.                                                    | 5  |

| 1.3 | A synthesis-centric design flow                                                                 | 8  |

| 1.4 | Challenges of ESL design with synthesis tools                                                   | 9  |

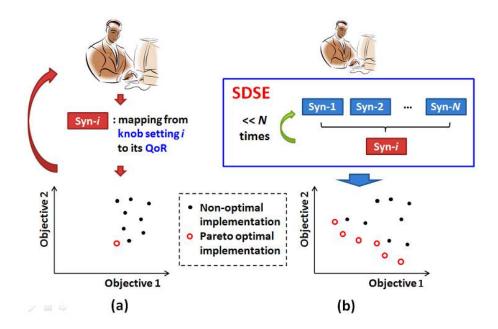

| 1.5 | (a) Traditional DSE is an ad hoc process to search one (or few) optimal design                  |    |

|     | implementation. (b) Supervised DSE (SDSE) is an abstraction layer that returns an               |    |

|     | approximate Pareto set by autonomously supervising synthesis jobs                               | 11 |

| 2.1 | The evolution of design abstraction for VLSI design (source: [157])                             | 18 |

| 2.2 | An ASIC design flow                                                                             | 19 |

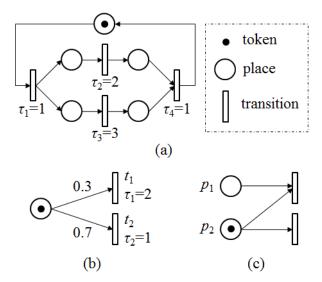

| 3.1 | (a) A timed marked graph; (b) A stochastic timed free-choice net where the token                |    |

|     | goes to $t_1$ ( $t_2$ ) with a 30% (70%) probability; (c) A net that is not free-choice because |    |

|     | $\bullet(p_2\bullet)=\{p_1,p_2\}\neq\{p_2\}.$                                                   | 28 |

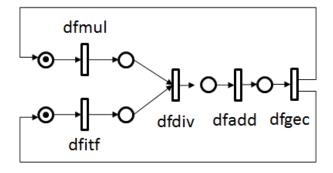

| 3.2 | HLS-driven implementation for a Discrete Cosine Transform                                       | 31 |

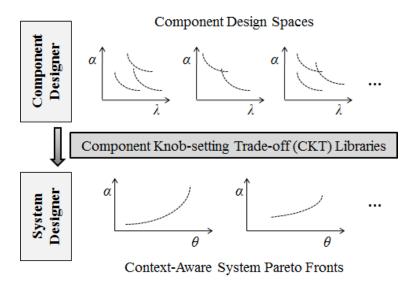

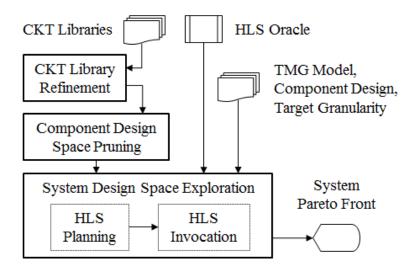

| 3.3 | The proposed design methodology                                                                 | 32 |

| 3.4 | Our algorithm flowchart in the context of system design                                         | 33 |

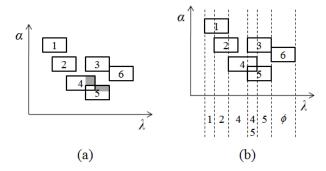

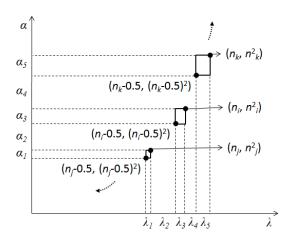

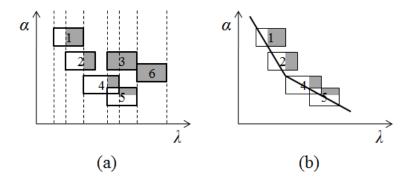

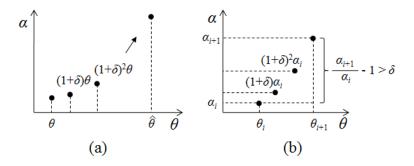

| 3.5  | (a) An instance of Problem 2. (b) Dashed lines identify six non-overlapping $\lambda$ inter-       |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | vals; their optimal knob-setting candidates for deriving Pareto-optimal instances are              |    |

|      | shown below the $\lambda$ axis                                                                     | 34 |

| 3.6  | Visualization for the proof of Theorem 1                                                           | 36 |

| 3.7  | Illustration of Algorithm 1                                                                        | 37 |

| 3.8  | The pruning and piecewise-linear-fitting results of a double-precision floating-point              |    |

|      | divider (DIV) component                                                                            | 38 |

| 3.9  | (a) Pruned component design space: shaded space is sub-optimal. (b) Pruned-space                   |    |

|      | approximation by a convex piecewise-linear function                                                | 12 |

| 3.10 | Illustration of Algorithm 2                                                                        | 14 |

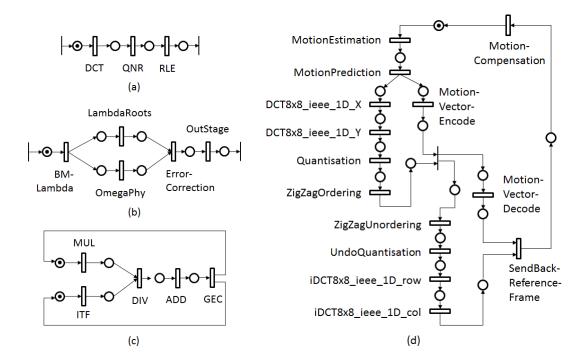

| 3.11 | The TMG models of the four benchmark systems (a) JPEG, (b) RS, (c) DFSIN, and                      |    |

|      | (d) MPEG2. The transitions represented by solid lines are for modeling the token                   |    |

|      | generation, receiving, or synchronization, whose transition times are small constants              |    |

|      | and are independent of the system exploration (so they are ignored when computing                  |    |

|      | the effective throughputs of the systems)                                                          | 15 |

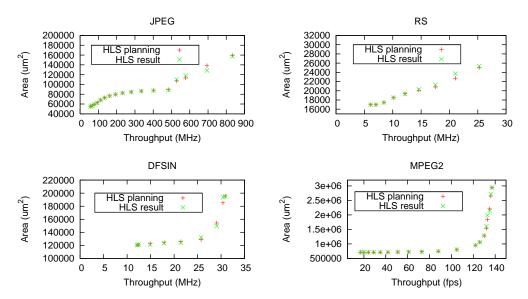

| 3.12 | System design-space-exploration results for JPEG, RS, DFSIN, and MPEG2 in terms                    |    |

|      | of area vs. throughput trade-off, with a target granularity $\delta=0.2.$                          | 16 |

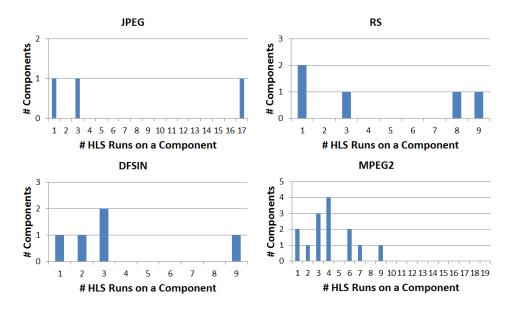

| 3.13 | Component query distributions for the explorations in Fig. 3.12                                    | 17 |

| 3.14 | Adaptive component query of the MPEG2 system. The top row from left to right                       |    |

|      | shows the query results (red from planning; green from HLS) of the MotionEsti-                     |    |

|      | $mation,Quantization,DCT8x8\_ieee\_1D\_X,andMontionCompensationcomponents.$                        |    |

|      | These components are the top-4 most influential components toward the area-throughput              |    |

|      | optimization of the MPEG2 system                                                                   | 19 |

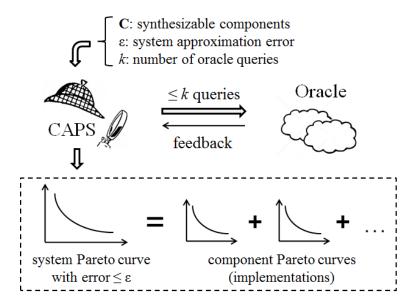

| 4.1  | Supervised design-space exploration by Compositional Approximation of Pareto Sets                  |    |

|      | (CAPS)                                                                                             | 54 |

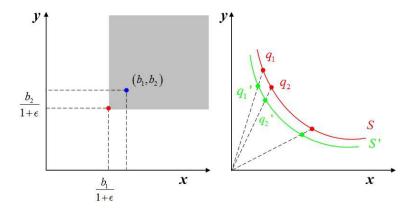

| 4.2  | The point $b$ $\epsilon$ -covers all points in the shaded region (left). Illustration of the ratio |    |

|      | distance between two curves $S, S'$ (right)                                                        | 56 |

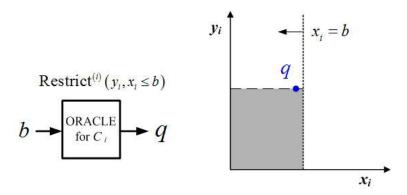

| 4.3  | The oracle solves the Restricted Problem (left) while guaranteeing that there are no                          |    |

|------|---------------------------------------------------------------------------------------------------------------|----|

|      | solution points in the shaded region (right)                                                                  | 57 |

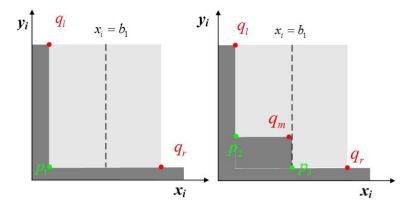

| 4.4  | A geometric interpretation of the algorithm for the case of one component. The ideal                          |    |

|      | oracle guarantees that there exist no solution points in the dark-shaded region                               | 59 |

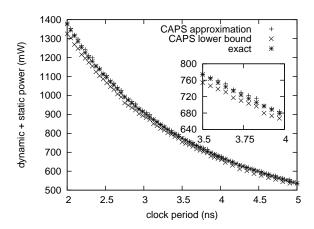

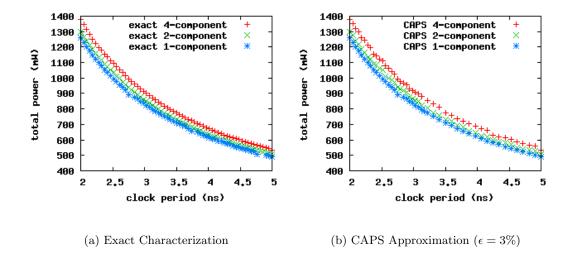

| 4.5  | Power/performance trade-off of StereoDepth at 90nm ( $\epsilon=3\%$ )                                         | 63 |

| 4.6  | Component sampling of StereoDepth at $90nm$ to build the system approximation of                              |    |

|      | Fig. 4.5                                                                                                      | 64 |

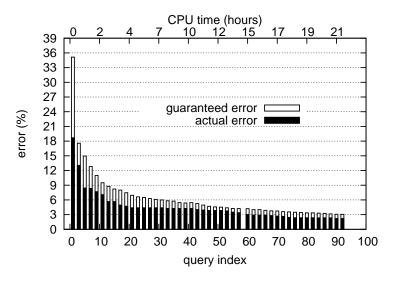

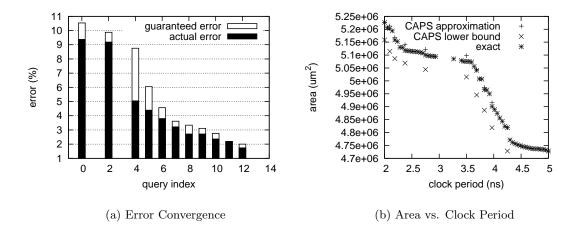

| 4.7  | Error convergence of MPEG2 Encoder by query index (lower axis) and by CPU time                                |    |

|      | (upper axis)                                                                                                  | 65 |

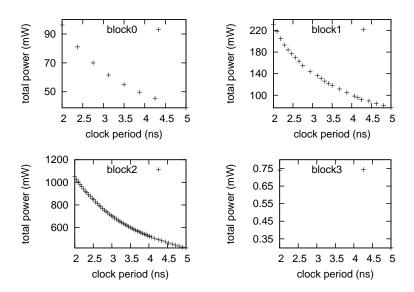

| 4.8  | Power/performance trade-offs of StereoDepth at $90nm$ composed of 1, 2, and 4                                 |    |

|      | components, by (a) exact characterization and (b) CAPS approximation with $\epsilon =$                        |    |

|      | 3%                                                                                                            | 66 |

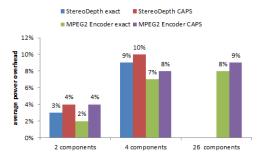

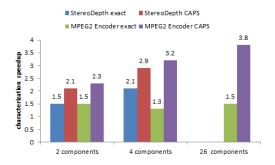

| 4.9  | $Sensitivity analysis \ by \ comparing \ multi-component \ synthesis \ with \ whole-system \ (single-system)$ |    |

|      | component) synthesis, in terms of (a) power consumption overhead and (b) charac-                              |    |

|      | terization runtime speedup. CAPS runs with $\epsilon=3\%$ on both benchmarks                                  | 67 |

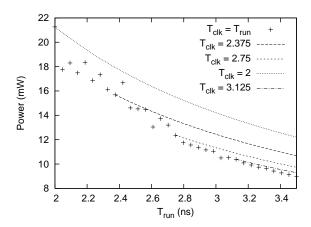

| 4.10 | The importance of synthesis for power/performance characterization. $T_{clk}$ and $T_{run}$                   |    |

|      | are the target clock frequency during synthesis and the operative clock frequency,                            |    |

|      | respectively.                                                                                                 | 68 |

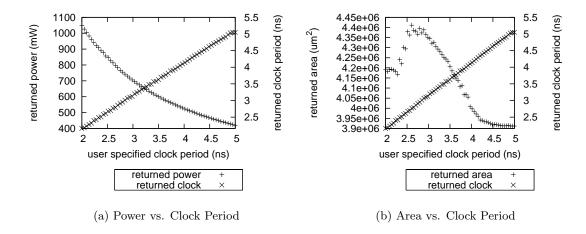

| 4.11 | Comparing the oracle behavior in terms of: (a) returned power and (b) area when                               |    |

|      | synthesizing the $block2$ component of StereoDepth at $90nm$ for various $T_{clk}$ values.                    |    |

|      | The diagonal line shows the returned clock period                                                             | 69 |

| 4.12 | Area/performance trade-offs (coping with a noisy oracle behavior) for StereoDepth                             |    |

|      | at 90nm                                                                                                       | 71 |

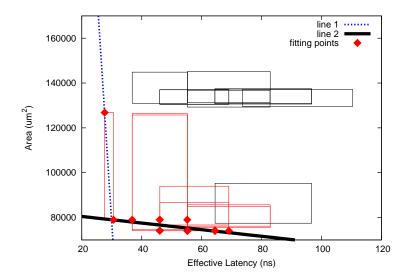

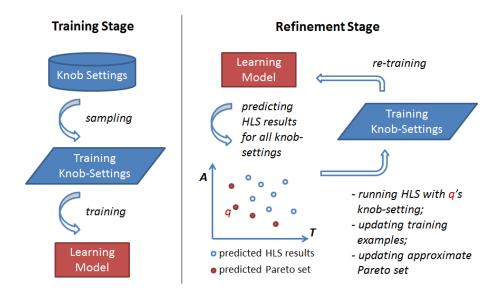

| 5.1  | An iterative-refinement DSE framework [121; 134; 186; 197]                                                    | 78 |

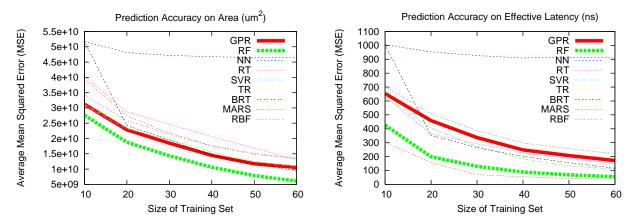

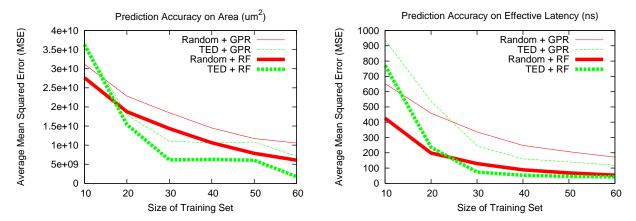

| 5.2  | Learning-model accuracy for predicting DFT area (left) and effective latency (right).                         |    |

|      | The training sets are randomly sampled                                                                        | 80 |

| 5.3  | Training-set sampling by Transductive Experimental Design (TED).                                              | 83 |

| 5.4 | Learning-model accuracy for predicting DFT area (left) and effective latency (right).                 |     |

|-----|-------------------------------------------------------------------------------------------------------|-----|

|     | "Random" and "TED" indicates training-set sampling algorithms. "GPR" and "RF" $$                      |     |

|     | are learning models                                                                                   | 84  |

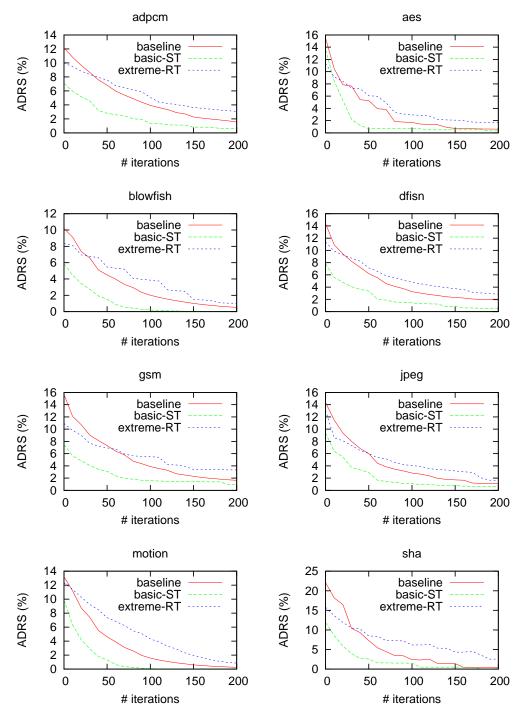

| 5.5 | The average ADRS (%) vs. the number of refinement iterations for DSE methods                          |     |

|     | baseline, basic-ST, and extreme-RT                                                                    | 93  |

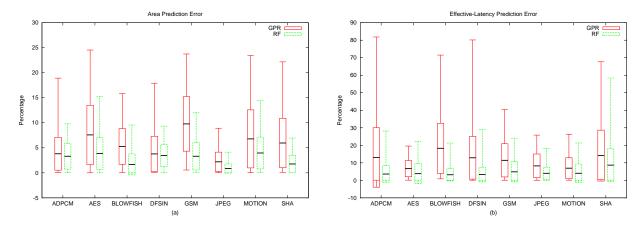

| 5.6 | Model prediction error rates with GPR and RF for (a) area prediction and (b)                          |     |

|     | effective-latency prediction. Each candlestick shows from top to bottom: the maxi-                    |     |

|     | mum, the average plus standard deviation, the average, the average minus standard                     |     |

|     | deviation, and the minimum errors.                                                                    | 95  |

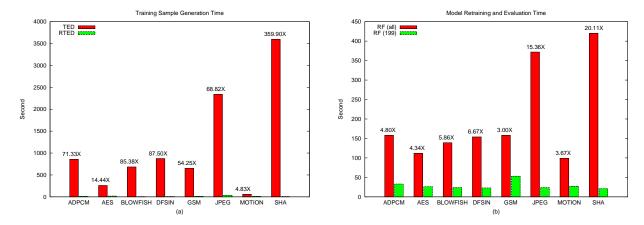

| 5.7 | CPU time for (a) generating 30 training HLS scripts (without running HLS) and (b)                     |     |

|     | retraining a learning model and evaluating the new model on all or 199 unseen HLS                     |     |

|     | scripts, aggregated over 55 iterations. For each benchmark, the factor over each red                  |     |

|     | bar shows the ratio of the height of the red bar over that of the green bar. The                      |     |

|     | average factors are 93.31X and 7.98X for (a) and (b), respectively                                    | 96  |

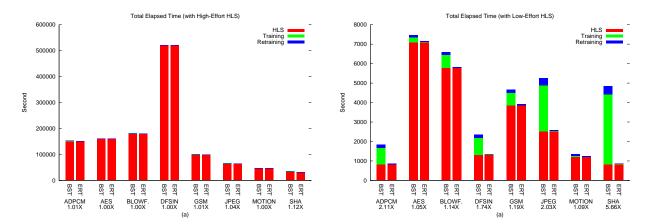

| 5.8 | Total CPU time with (a) high-effort HLS and (b) low-effort HLS. For each bench-                       |     |

|     | mark, "BST" and "ERT" stand for the results obtained by basic-ST and extreme-RT,                      |     |

|     | respectively. For each stacked bar, the "HLS" time includes $30$ and $55$ HLS runs at                 |     |

|     | the training and the refinement stages, respectively; the "Training" and "Retrain-                    |     |

|     | ing" times are the CPU times shown in Fig. 5.7(a) and Fig. 5.7(b), respectively.                      |     |

|     | Therefore, for the two stacked bars of each benchmark, the "HLS" time is constant,                    |     |

|     | while the "Training" and "Retraining" times can vary. For each benchmark, the                         |     |

|     | factor below the benchmark name shows the ratio of the height of the "BST" bar                        |     |

|     | over that of the "ERT" bar. The average factors are $1.02\mathrm{X}$ and $2.00\mathrm{X}$ for (a) and |     |

|     | (b), respectively                                                                                     | 97  |

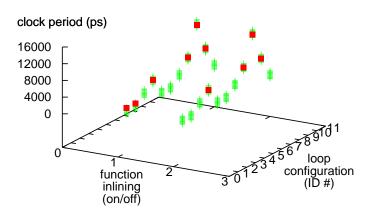

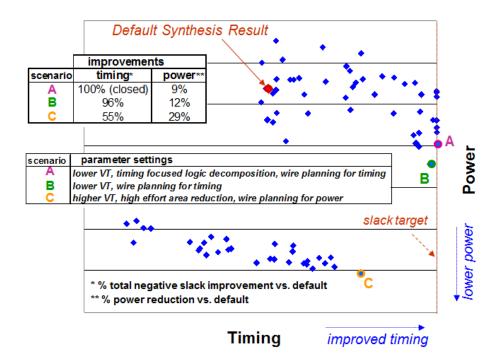

| 6.1 | An example of the available design space by modifying synthesis parameters. The                       |     |

|     | macro in this specific case is a portion of a floating point multiplier                               | 101 |

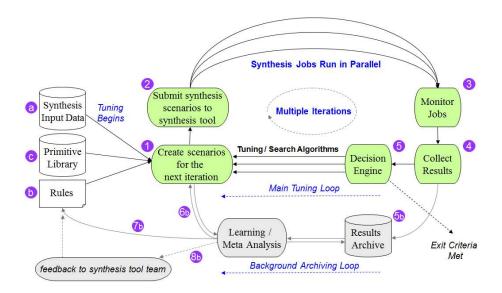

| 6.2 | Architecture of the SynTunSys process. The program employs a parallel and iterative                   |     |

|     | tuning process to optimize macros                                                                     | 103 |

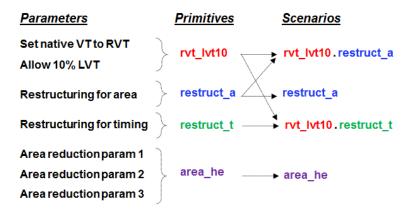

| 6.3  | Illustration of the interaction of parameters, primitives, and scenarios. Primitives                         |     |

|------|--------------------------------------------------------------------------------------------------------------|-----|

|      | can consists of one or more parameters                                                                       | 105 |

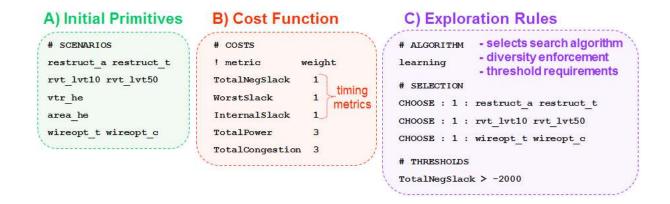

| 6.4  | Components of the SynTunSys Rules file: A) the primitives to be explored during                              |     |

|      | DSE; B) the cost function guiding the DSE; C) the search algorithm selection and                             |     |

|      | configuration parameters                                                                                     | 106 |

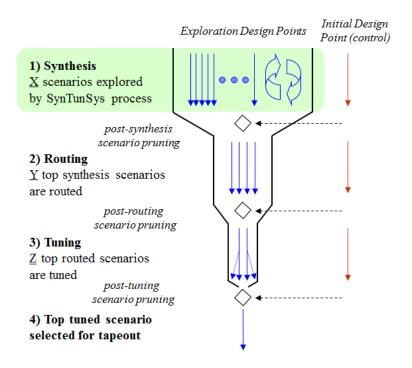

| 6.5  | Overview of the DSE-based macro construction flow                                                            | 109 |

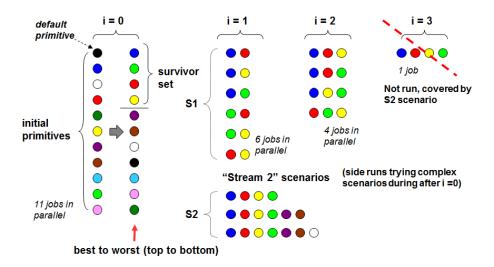

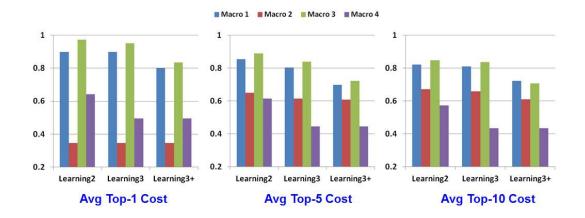

| 6.6  | The Base decision algorithm, where each colored bubble represents a primitive, a                             |     |

|      | horizontal sequence of adjacent bubbles represents a scenario, and "i" denotes the                           |     |

|      | iteration number                                                                                             | 110 |

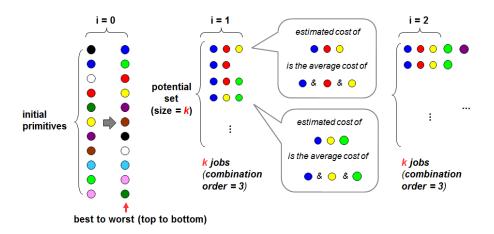

| 6.7  | Illustration of the Learning decision algorithm                                                              | 112 |

| 6.8  | Cost estimation process for the Learning algorithm                                                           | 113 |

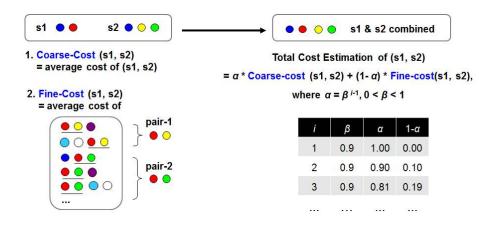

| 6.9  | Illustration of the Jump-Start sensitivity test                                                              | 114 |

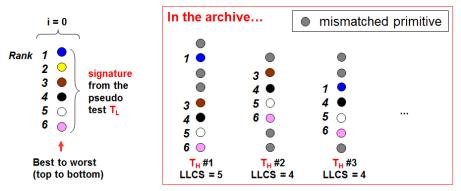

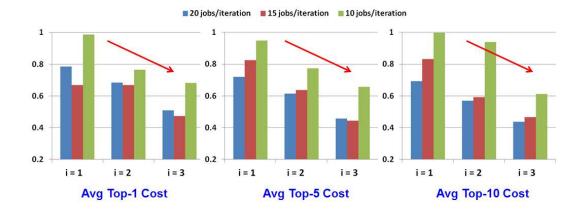

| 6.10 | Results comparing the Base vs. Learning algorithms                                                           | 118 |

| 6.11 | Iteration-by-iteration costs: Learning<br>3+ vs. Base                                                        | 119 |

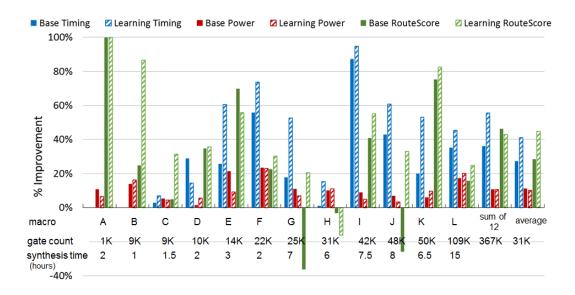

| 6.12 | Macro-by-macro breakdown of Learning3+ vs. Base                                                              | 121 |

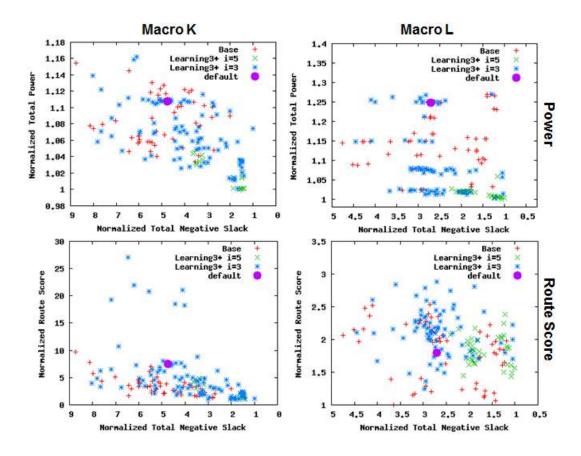

| 6.13 | Power (top row) and Route-Score (bottom row) vs. Total Negative Slack for large                              |     |

|      | macros K (left column) and L (right column)                                                                  | 122 |

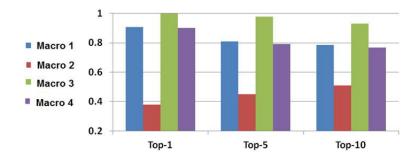

| 6.14 | Average cost comparison between the Just-Start test vs. the Base test (Base as 1.0).                         | 123 |

| 7.1  | Enhanced DSE with HLS using automatic and interactive processes                                              | 126 |

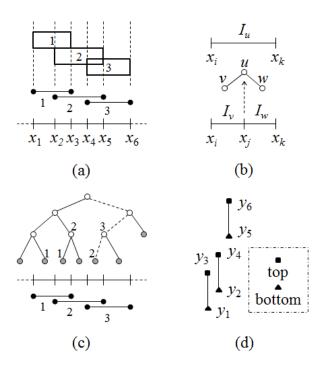

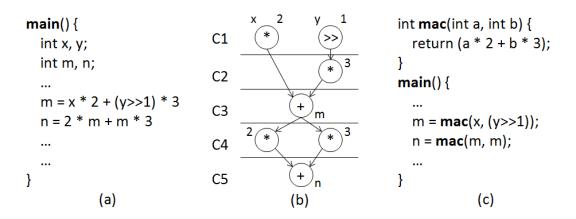

| 7.2  | (a) Example original specification. (b) A sub-optimal schedule for the original spec-                        |     |

|      | ification. (c) Suppose that a frequent pattern consisting of two multipliers plus an                         |     |

|      | adder is selected. Accordingly, we can refactor the specification with a customized                          |     |

|      | function call $\mathtt{mac}$ , which is essentially a composite operation if $\mathtt{mac}$ is $not$ inlined |     |

|      | during HLS                                                                                                   | 128 |

| 7.3  | A code-refactoring design methodology for enhanced DSE with HLS. $\ \ \ldots \ \ \ldots \ \ .$               | 129 |

| 7.4  | (a) Example original specification. Under func body, we list two transformation                              |     |

|      | steps S1 and S2 that derive equivalent "if" statements to the original "if" in func.                         |     |

|      | (b) A refactoring of func with top2.                                                                         | 133 |

| 7.5 | An example DFS-Code Tree                                                                  |

|-----|-------------------------------------------------------------------------------------------|

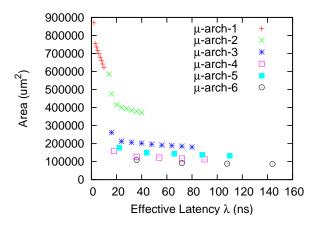

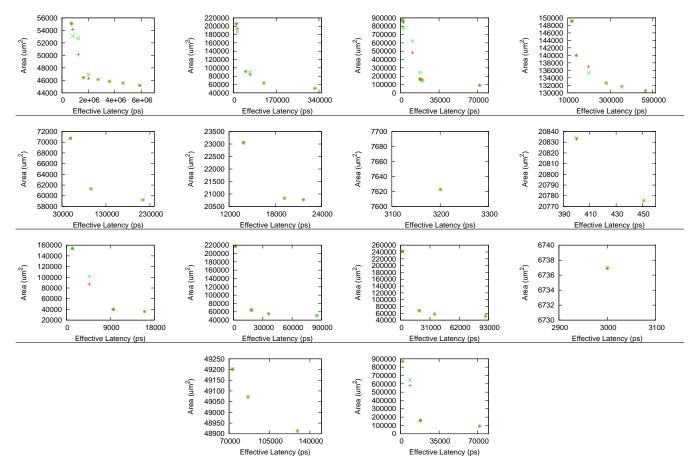

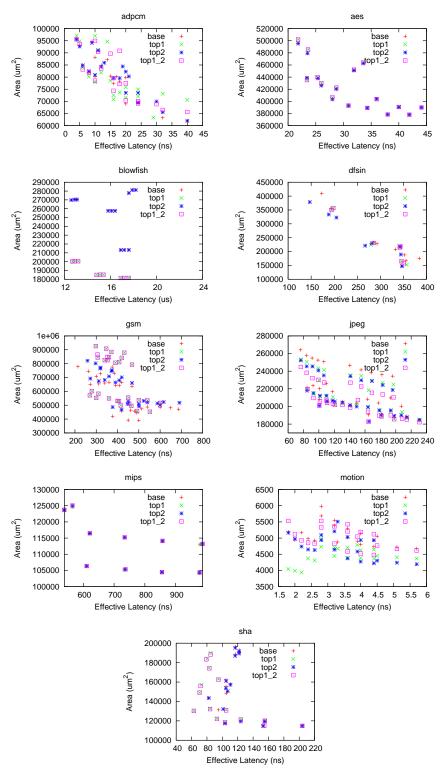

| 7.6 | DSE results on the CHStone suite. Each point represents a distinct implementation         |

|     | synthesized by HLS                                                                        |

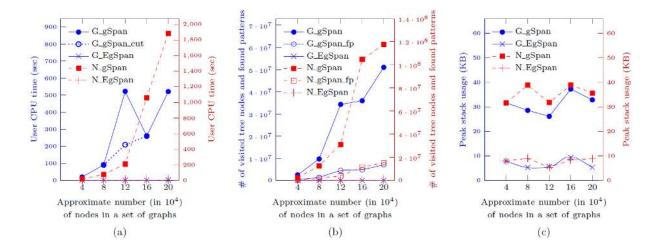

| 7.7 | (a) User CPU time for the execution of gSpan and EgSpan. (b) Numbers of visited           |

|     | DFS Code Tree nodes and numbers of found patterns. (c) Peak stack memory usage.           |

|     | For all plots, the left vertical axis corresponds to the G group of input sets (where     |

|     | the number $G$ of graphs in a set varies), and the right vertical axis corresponds to the |

|     | N group of input sets (where the average number $N$ of nodes in each graph varies.)       |

|     | The horizontal axes represent the size of an input set, which is equal to $G \cdot N$ 142 |

| 8.1 | SDSE as a platform                                                                        |

| 8.2 | CDSE by revision ranking                                                                  |

| 8.3 | CDSE example: (a) Ver. 1: initial design. (b) Rev. 1: pattern-based customiza-            |

|     | tion after Ver. 1. (c) Rev. 2: conversion to constants after Ver. 1. (d) Rev. 3:          |

|     | function/thread parallelization after Rev. 1                                              |

| 8.4 | CDSE with revision planning                                                               |

| A.1 | The TMG model of dfsin                                                                    |

# List of Tables

| 1.1 | Examples of Design Elements                                                                  | 3   |

|-----|----------------------------------------------------------------------------------------------|-----|

| 1.2 | Thesis Contributions to The Design Elements [150]                                            | 13  |

| 3.1 | Some Typical High-Level Synthesis Knobs and Their Settings                                   | 30  |

| 3.2 | System area vs. throughput exploration as function of $\delta$                               | 50  |

| 4.1 | Power/Performance trade-offs by CAPS. Note that the unit of CPU time is hours,               |     |

|     | and the parenthesized value of "k" and "CPU Time" is a ratio over <i>Exhaustive Search</i> . | 65  |

| 5.1 | Comparison of DSE Methods                                                                    | 86  |

| 5.2 | Number of HLS Runs to Find the Exact Pareto Set                                              | 87  |

| 5.3 | baseline vs. basic (bs) vs. basic-ST (ST) given HLS budget $b$                               | 88  |

| 5.4 | extreme (ex) vs. extreme-RT (RT) given HLS budget $b$                                        | 89  |

| 5.5 | Benchmark Characteristics                                                                    | 90  |

| 5.6 | Comparison of DSE Method Convergence                                                         | 92  |

| 6.1 | An example library of primitives                                                             | 104 |

| 6.2 | Average SynTunSys improvement over best known prior solution based on post-route             |     |

|     | timing and power analysis                                                                    | 116 |

| 6.3 | Macros for Tuning Learning-Based Algorithms                                                  | 117 |

| 6.4 | Algorithm Configuration                                                                      | 118 |

| 6.5 | Comparison of Learning3+ and Base algorithms across a 12 macros test suite that              |     |

|     | is representative of a larger processor                                                      | 120 |

| 7.1 | Benchmark Characteristics                                                | . 136 |

|-----|--------------------------------------------------------------------------|-------|

| 7.2 | DSE Result Improvements                                                  | . 140 |

| 7.3 | Reduction of Average Initial Operations and Average HLS Runtime (Minute) | . 141 |

| 8.1 | Computer-Science Applications of Pareto-Set Discovery                    | . 154 |

## Acknowledgments

First of all, I would like to express my sincere appreciation and gratitude toward my PhD advisor, Prof. Luca Carloni. During my PhD journey, Prof. Carloni believed in my talent and potential, inspired me with countless research ideas, supported me to resolve research and life difficulties, and acted as a role model for research and teaching excellence. I look forward to our continued collaboration in the years to come. Besides my advisor, I would like to thank all the other members who served in my thesis defense committee, including Prof. Steven Nowick, Prof. Kenneth Shepard, Prof. Mihalis Yannakakis, and Dr. Matthew Ziegler. In particular, special thanks to Prof. Steven Nowick, who was virtually my secondary advisor, providing me invaluable research feedbacks and writing me strong recommendation letters; special thanks to Prof. Kenneth Shepard, who provided practical comments from a designer's perspective and generously offered design tools as well as computing resource for me to perform experiments; special thanks to Prof. Mihalis Yannakakis, who pioneered the research in multi-objective optimization that led to my first PhD publication, a joint work with one of his prior PhD students; special thanks to Dr. Matthew Ziegler, who acknowledged my internship request, brainstormed and collaborated with me on exiting research projects, and complemented the committee as a researcher from an industrial research lab.

In addition, I would like to thank all my research colleagues, my mentors/managers from the industry, and the members/alumni of the System Level Design (SLD) group at Columbia University. Specifically, I enjoyed the collaboration with the following talented and inspiring researchers: Prof. Nicola Bombieri, Prof. Ilias Diakonikolas, Prof. Franco Fummi, PhD student Jihye Kwon, and Dr. Michele Petracca. Moreover, on sponsored internships I was privileged to be mentored by two topnotch research scientists, Robert Condon (Intel) and Dr. Matthew Ziegler (IBM), and be coached by several empathetic managers, Dr. Yatin Hoskote (Intel), Dr. Christy Tyberg (IBM), and Dr. Victor

Zyuban (IBM). Also, special thanks to Dr. Michael Theobald (D. E. Shaw Research), who offered me a timely Teaching Assistant position at Columbia and has provided influential career advices since then. Furthermore, I would like to thank the fellow PhD students and research scientists in the SLD group. In particular, special thanks to Emilio Cota and Dr. Marcin Szczodrak for their selfless contributions to the group's network and web infrastructure, which was very helpful when I served as a teaching assistant for multiple times. Also, special thanks to Dr. Giuseppe Di Guglielmo, who fearlessly tested, evaluated, and improved my prototype tools.

Needless to say, my family played a central role during my pursuit of the PhD. I am particularly grateful for the supports in any form extended by my parents as well as my parents in law. Without their supports, it would be impossible for me to see the light at the end of the tunnel. Besides, during this special journey I considered myself extremely blessed to have my first kid, Ryan, come to my life and explore the world with me. Since the very first day I was aware of this new life, he has been teaching me how to be a good son, a good father, and a good husband. As for my beloved wife, Melody, I truly do not know how to express my appreciation, gratitude, and apologies for her devotion, caring, and sacrifices. On the other hand, I truly thank Lord for giving my wife as my helper, who has been perfecting me with the Lord's word and exercising with me to become a vessel for the Lord's grace.

Finally, I would like to thank all the brothers and sisters in His body. All their prayers witness to how faithful our Lord is. I also very much thank Lord for giving me this PhD journey, during which I appreciated the fact that I am nothing but He is everything. Glory to Him.

To Lord, My Shepherd.

### Chapter 1

### Introduction

Design is an ubiquitous concept in every pursuit of knowledge, but has different connotations in different fields. Yet in general, the process of design corresponds to the exploration of a large (often infinite) space for creating complex objects. To facilitate the design process, a clear "taxonomy of design" can help analyze various design paradigms. Hence, I first review a recent design taxonomy and apply it to analyze common paradigms for designing complex computer systems. Then, I point out major challenges for designing integrated electronic systems and propose Supervised Design-Space Exploration for addressing these challenges.

#### 1.1 What is Design?

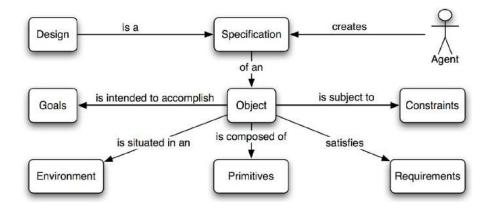

Based on 33 proposals in existing literature, Ralph and Wand proposed in 2009 the following definition for design (as a noun): a specification of an object, manifested by an agent, intended to accomplish goals, in a particular environment, using a set of primitive components, satisfying a set of requirements, subject to constraints [150]. The definition, illustrated in Figure 1.1, captures the following elements.

• Object is the entity being designed, such as a physical artifact, a system, a process, or a policy.

The entity is not necessarily a physical object.

Figure 1.1: A conceptual model of design (source: [150]).

- Specification is a description of the design object in terms of its structures, such as the primitives used and their connections.

- Agent is the entity or group of entities that specifies the structural properties of the design object, e.g., scientists, engineers, or government officials.

- Environment of the object is the context in which the object is intended to exist or operate.

On the other hand, Environment of the agent is the context in which the agent creates the design.

- Goals describe the desired impacts of the design object on its environment.

- Primitives are the set of elements from which the design object may be composed.

- Requirements are structural or behavioral properties that the design object must possess. A structural property is a quality the design object must possess regardless of environmental conditions or stimuli. A behavioral property is a required response to a given set of environmental conditions or stimuli.

- Constraints are structural or behavioral restrictions on the design object, where "structural" and "behavioral" have the same meaning as for requirements. Even if the design agent had infinite time and resources, a design is still constrained by, e.g., the law of physics.

Applying this definition, Table 1.1 gives two design examples of computer software and hardware systems.

Table 1.1: Examples of Design Elements.

| Table 1.1. Examples of Besign Elements. |                            |                             |  |  |  |  |

|-----------------------------------------|----------------------------|-----------------------------|--|--|--|--|

| Object Type                             | Symbolic Script [150]      | Physical Artifact           |  |  |  |  |

| Object                                  | a software system          | a hardware system           |  |  |  |  |

| Specification                           | software programs          | circuit layouts             |  |  |  |  |

| Agent                                   | programmers                | engineers                   |  |  |  |  |

| Goals                                   | support management of      | support multimedia          |  |  |  |  |

|                                         | customer information       | processing                  |  |  |  |  |

| Environment                             | personal computers with    | printed circuit boards with |  |  |  |  |

|                                         | specific operating systems | specific I/O protocols      |  |  |  |  |

| Requirements                            | identify customers with    | encode and decode certain   |  |  |  |  |

|                                         | certain characteristics;   | multimedia standards;       |  |  |  |  |

|                                         | query latency              | processing throughput       |  |  |  |  |

| Primitives                              | instructions in a          | transistors with a          |  |  |  |  |

|                                         | programming language       | fabrication technology      |  |  |  |  |

| Constraints                             | CPU speed and memory size  | gate and wire delay         |  |  |  |  |

A clear taxonomy of "design" can help organize, share, and reuse design knowledge [150]. Furthermore, understanding the elements of design would be useful in determining the issues and information relevant to the process of design and in planning this process [150]. Based on the taxonomy [150], I examine complex computer system design in the next section and for each design element present common approaches to addressing the system design complexity.

### 1.2 Coping with Complex Computer System Design

Computing is becoming ubiquitous [79], penetrating personal devices such as smart phones, smart watches, and eye glasses. The ubiquitous computing is enabled by powerful computer systems, which have been becoming more complex than ever. For example, Linux kernel 3.10 has 15,803,499 lines of code in its 2013 release, increasing by 90X with respect to its release in 1994 (176,250 lines of code) [110]. The Intel Core i7 processor has 2.6B transistors in 2014, increasing by 473X with respect to its Pentium Pro processor in 1995 (5.5M transistors) [90]. The trend of transistor density

doubling every two years is known as Moore's Law [115].

To cope with the design complexity of complex computer systems, many paradigm shifts have taken place by efficiently handling the aforementioned design elements. For example:

- Specification: to raise the level of abstraction for more productive design capture, software programming languages have evolved from machine/assembly code to various high-level languages, such as Java and Python, supporting high-level concepts like variables, objects, complex arithmetic/control expressions, and threads. For synchronous digital circuit design, the abstraction has also been raised from schematics to Register Transfer Level (RTL) hardware-description languages, such as Verilog and VHDL, which can describe sequential elements and combinational circuits. Sequential elements synchronize the circuit's operation with clock edges and stores the temporal operation results. On the other hand, combinational logic performs all the logic functions in the circuit using proper connection of logic gates.

- Agent: aiming for high design productivity, Computer-Aided Design (CAD) tools are widely adopted by human designers to automate (parts of) the design process, which leads to better design quality given limited design time and resources. In large software designs that typically involve multiple programmers, build-automation and version-control tools are essential for the development, maintenance, and integration of the entire software. In circuit design, logic synthesis tools are the standard for the automatic generation of gate-level netlists from RTL descriptions.

- Environment: to reduce the gap between the object and the agent environments, software developed for a guest machine can now run on a different host machine through virtualization techniques [170]. For hardware design, emulation and simulation techniques also become common practices, such as hardware prototyping using Field-Programmable Gate Array (FPGA) [9] and logic verification using simulation programs [78].

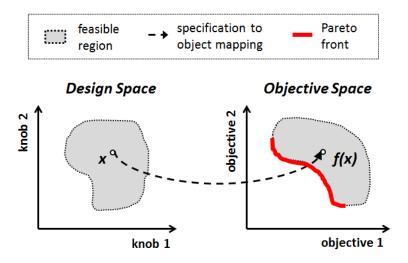

- Goals: "design" as a verb is to explore a design space for achieving a design object that exhibits multiple design objectives. The exploration process is illustrated in Figure 1.2, where two-dimensional design and objective spaces are used as examples. The axes of the design space represent the controllable *knobs* (aka variables or parameters) to manipulate the object within a feasible region, which is confined by the design requirements and constraints. For instance,

Figure 1.2: Design-space exploration. The function f for specification-to-object mapping corresponds to the construction of the design object. Suppose that the objectives are design cost and performance in terms of latency (both to be minimized). The red Pareto front features the optimized objects.

the knobs of a software compiler are its compilation flags. On the other hand, the objective axes stand for the qualities of the achievable objects. In many scientific and engineering fields, the objectives are conflicting [23], e.g., the development cost, memory footprint, and query efficiency of database design in computer science. Therefore, from an optimization perspective, the "best" design objects are the ones that cannot improve in any objective without sacrificing at least another. For instance, the database systems that are either "most query efficient with largest memory usage" or "least memory hungry with longest query latency" are equally best in a multi-objective setting. These design objects are considered Pareto-optimal (or Pareto-efficient) and are called Pareto points [23]. The collection of Pareto points are called Pareto set (or Pareto front, or Pareto curve) [23]. In Section 8.3, I survey more computer-science applications of Pareto-set discovery.

• Primitives: to avoid reinventing the wheel, standard libraries are common features of highlevel programming languages. The libraries are collections of frequent and generic routines that were optimized beforehand for later reuse, such as sorting on arbitrary data types. Object-oriented programming also promotes the design of standard template libraries using abstract data types [95]. For circuit design, standard cells and Intellectual Property (IP) blocks are finer- and coarser-grained design primitives, respectively: a standard cell is a group of wired transistors that provides a basic Boolean function or a storage function; an IP block is a functional unit that is synthesizable (aka soft IP) or already defined in a transistor-layout format (hard IP) [155]. Both standard cells and IP blocks are instrumental in the success of the fabless business model in the semiconductor industry [128].

- Requirements: to verify a specification with critical design requirements, such as safety requirements, formal verification methods have been applied to both software and hardware design in industrial settings. Formal methods, such as model checking [38], guarantee the completeness (i.e., stimuli independent) and are able to return counterexamples for fixing the specification. Another approach for tackling design requirements is based on correct-by-construction methodologies. Software examples for algorithm design are the problem-solving paradigms "divide and conquer" and "dynamic programming", where the solution to the main problem can be constructed from the solutions to its subproblems [44], A hardware example for electronic system design is the "globally asynchronous locally synchronous" architecture for composing locally-clocked IP components via asynchronous communication protocols, while preserving semantics and avoiding deadlocks [146].

- Constraints: the limits of computing have been continuously pushed with new platforms, such

as networked, distributed, or parallel computer systems. Each computer unit in these systems

has also been continuously improved with new technologies. In the context of computer

hardware design, the next section introduces major technology breakthroughs and presents

new challenges.

#### 1.3 Challenges of Electronic System Level Design

Low-cost Very Large Scale Integration (VLSI) electronics have revolutionized daily life and expanded the role of computation in science and engineering [100]. The revolution was supported by three main semiconductor areas: (i) device and manufacturing, (ii) circuits and architectures, and (iii) CAD methodologies and tools. For the first two areas, the past decade has witnessed some technology breakthroughs reaching production, e.g., new manufacturing technologies such

as FinFET [46; 88] and 3D integration [47; 152], and new computer architectures such as multicore processors [97; 126; 127; 141; 183] and heterogeneous System-on-Chip (SoC) [37; 49; 103;

193]. In contrast, there have not been major CAD breakthroughs making an industrial impact

comparable to such innovations of the past as circuit simulation, automatic place and route, RTL

description languages, and logic synthesis. These CAD technologies were already mature in the 90s.

In order to continue sustaining the progress of the semiconductor industry in the face of growing

system-design complexity, CAD researchers must rely on design reuse to address the complexity [34;

155] and raise the level of abstraction above RTL to enable Electronic System Level (ESL) design [15; 76].

The heterogeneous SoC, which features a mix set of programmable cores and task-specialized accelerators, has become the dominant computer architecture thanks to its energy efficiency<sup>1</sup>. The SoC structure is composed of heterogeneous components, each responsible for either computation, communication, or data cache. This modular structure addresses the ESL design complexity by parameterizing, exploring, and integrating primitive components. These components can be predesigned, pre-verified, and pre-characterized as IP blocks, aiming for broad reuse in various systems (or subsystems) for maximum design productivity, i.e. component-based design [34; 155]. In order to achieve a 10X design-productivity improvement, ITRS predicted that by 2020 a stationary or consumer SoC would consist of 90% reused components (assuming a constant tool effort) [91]. In industry, the 2001–2013 CAGR of semiconductor-IP revenue is indeed a good 13% [65]. Preferably, the design of SoC component is specified in high-level languages (i.e. soft IP's), so that they can be implemented with automatic synthesis tools to serve various ESL requirements.

The synthesis of RTL code from C-like languages (such as SystemC [4]) is known as High-Level Synthesis (HLS) [48]. Empirically, when designers move from RTL to high-level specifications, the code density can be reduced by 7X–10X [42], and therefore the specifications are easier to develop, debug, and maintain. Given a high-level specification with user-specified *knob settings* (see footnote <sup>2</sup>), HLS can automatically generate RTL implementations with different micro-architectures,

<sup>&</sup>lt;sup>1</sup> Section 2.1 provides more background for the rise of heterogeneous architectures.

<sup>&</sup>lt;sup>2</sup> A knob setting is a complete configuration of synthesis knobs onto a design specification. In other words, a knob setting corresponds to a synthesis scenario or a synthesis script, which is conceptually depicted as the point x in Figure 1.2. Throughout this dissertation, I use "knob setting" and "synthesis scenario" interchangeably.

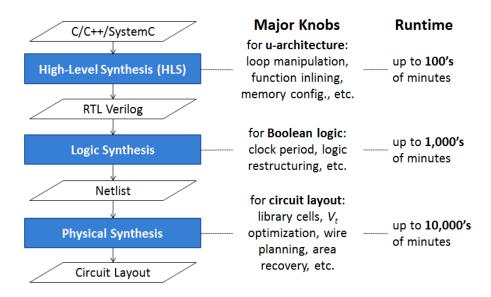

Figure 1.3: A synthesis-centric design flow.

each exhibiting unique trade-offs among multiple design objectives<sup>3</sup>. Moreover, by adopting high-level languages, the co-design of software and hardware for embedded systems can start earlier in the design cycle [175] using virtual platforms [111]. In industry, the 2001–2013 CAGR of ESL-tool revenue (11%) is already ranked at the top among all the front-end VLSI-design tools, which include logic synthesis, RTL simulation, formal verification, timing analysis, etc [65].

Overall, in order to realize component-based ESL design, powerful automatic synthesis tools are essential, because the creation and maintenance of reusable components are estimated to be 2–5X more difficult than their creation for one-time use [91]. A synthesis-centric design flow includes three synthesis stages: HLS, logic synthesis, and physical synthesis (Figure 1.3). HLS translates a high-level design specification to an RTL implementation, which is further synthesized to a gate-level netlist by logic synthesis, and finally placed and routed by physical synthesis. The goals of the three synthesis stages are different: (i) HLS optimizes RTL implementations with various micro-architectural knobs, such as loop manipulation, function inlining, memory configuration, and many others, (ii) logic synthesis optimizes the area/power of a netlist by restructuring Boolean logic and mapping it to standard cells, under a clock-period constraint, and (iii) physical synthesis

<sup>&</sup>lt;sup>3</sup> The trade-offs are conceptually captured by the feasible region of the objective space in Figure 1.2. HLS (or "synthesis" in general) is represented by the mapping function f in the figure.

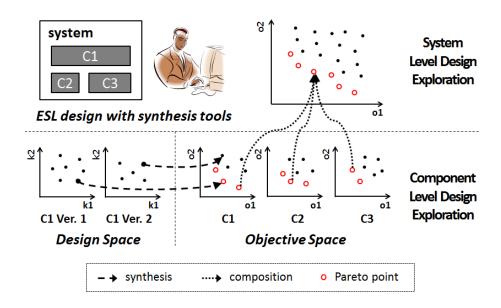

Figure 1.4: Challenges of ESL design with synthesis tools.

determines the layout of the netlist using various optimization techniques, such as gate/wire sizing, buffer insertion/sizing,  $V_t$  swapping, routing layer/track assignment, and many others. Although modern synthesis tools are powerful thanks to these many synthesis knobs, the runtime of a synthesis job is significant, ranging from hours to days on modern workstations.

Across all the synthesis stages, the synthesis-driven design methodology faces several big challenges as described below. Figure 1.4 illustrates these challenges using a simple example of a system design that is composed of three components (C1, C2, and C3).

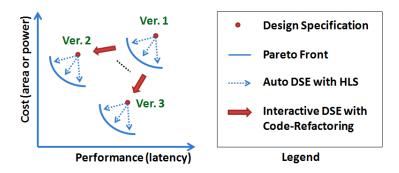

• Design-Space Exploration (DSE) (represented by the Pareto points in Figure 1.4). Classical DSE optimizes one single objective given others as constraints, such as the area minimization with clock-period constraints that is used in logic synthesis. However, modern VLSI design requires to explore a multi-objective design space, such as performance vs. energy [164] and other objectives such as area [52], power [119], manufacturability [36], and reliability [102]. To this end, multi-objective DSE should search for a Pareto set, as opposed to a single Pareto point. Unfortunately, existing synthesis tools can only return one implementation per synthesis run and that implementation is not even guaranteed to be a Pareto point. Therefore, the search of the Pareto set requires extensive synthesis runs, each taking significant runtime.

- System-Level Composition (represented by the composition arcs in Figure 1.4). The design of heterogeneous SoCs relies on the effective reuse and integration of optimal component implementations. As holistic synthesis is infeasible (due to prohibitively high requirements in terms of tool runtime and memory occupation), efficient system-composition tools are desirable for SoC optimization. The composition is done by first running component-level synthesis and then combining proper component implementations that form the system-level Pareto set. The ideal composition tool should be able to identify the critical components that can have the most contributions to the system-level Pareto set. Moreover, considering the long synthesis-tool runtime, this tool should be adaptive in spending component synthesis jobs (top-down), without the need to fully characterize each component-level Pareto set (bottom-up).

- Synthesis-Tool Usage (represented by the synthesis arcs in Figure 1.4). The elusive optimal setting of synthesis knobs and the long runtime of synthesis jobs make synthesis tools hard to use. The synthesis Quality of Results (QoR) is often design specific; there is no universal recipe of knob settings for achieving the best QoR. Although the example of Figure 1.4 shows only two knobs, the actual number of knob settings for HLS grows exponentially with the specification complexity; for integrated logic and physical synthesis, the number can reach  $O(2^p)$  with the number of knobs  $p \in [100, 400]$ . The sheer number of synthesis scenarios (i.e. knob settings) together with the long runtime required by each synthesis scenario prohibits exhaustive synthesis in practice.

- Synthesis-Aware Specification Refinement (represented by the design space derived from different versions of a component specification (C1 Ver. 1 and C1 Ver. 2) in Figure 1.4). These versions satisfy the same functional requirements, but differ in the detailed descriptions, e.g. using different algorithms for sorting. The exploration of synthesizable specifications has long been done manually and is not addressed automatically by CAD tools. Very often, a restructure of the specification can change the synthesis-explorable design space, thus yielding different synthesis QoR. However, component-based design requires extensive reuse of high-quality synthesizable components across product cycles, design teams, and system companies. Therefore, as SoC designs are becoming more complex, the tool support for synthesis-aware

Figure 1.5: (a) Traditional DSE is an ad hoc process to search one (or few) optimal design implementation. (b) Supervised DSE (SDSE) is an abstraction layer that returns an approximate Pareto set by autonomously supervising synthesis jobs.

specification refinement is becoming more and more desirable.

#### 1.4 Thesis Contributions

In order to address the aforementioned challenges, I propose **Supervised Design-Space Exploration** (SDSE): SDSE is an abstraction layer between a designer and a synthesis tool, aiming to autonomously supervise synthesis jobs for design-space exploration. The system Pareto set is approximated by combing the required component implementations, which are achieved by running a minimum number of synthesis jobs. The synthesis jobs are adapted to the most influential system components with the most effective knob settings for synthesizing them.

Specifically, my thesis makes the following contributions:

• I introduce a new abstraction layer for autonomous DSE with synthesis tools. Figure 1.5 illustrates the traditional and the supervised DSE approaches. The traditional approach requires (i) human analysis on synthesis QoR and (ii) human decision among a huge number of candidates to select the next synthesis scenario [123]. The manual efforts required by the

traditional approach limit the exploration result to one (or few) optimal implementation. In contrast, SDSE offloads the analysis and decision making to an autonomous process, such that the designer can focus on extra design optimizations beyond synthesis exploration. Moreover, SDSE aims at not only minimizing the number of synthesis jobs for DSE but also returning an approximate Pareto set. The Pareto set brings the following benefits: (i) at the stage of early design exploration, when the preferences of design objectives are unclear or subjective to change, the Pareto set provides a global view of equally good design options, thus limiting the risk of being trapped into local optima, (ii) in a design/implementation flow, the Pareto set can be refined at the next level(s) of abstraction without the need to start from scratch, and (iii) for final design optimization, the Pareto set features a portfolio of optimal implementations that can be reused in the future across design projects and design teams/houses.

- I propose two novel compositional frameworks that can minimize the number of component synthesis jobs for approximating the system-level Pareto set (to optimize the composition arcs of Figure 1.4). Together with the frameworks, I propose novel algorithms for identifying the most influential system components, so that most of the synthesis jobs are adapted to those components for the maximum return of investment. The system Pareto set is approximated by combining the component synthesis results. I have applied SDSE for system-level exploration with commercial high-level and logic synthesis tools.

- I present two enhanced iterative-refinement frameworks that can minimize the number of synthesis jobs for component-level DSE using advanced learning methods (to optimize the synthesis arcs of Figure 1.4). The learning methods can better estimate synthesis QoR for unknown synthesis scenarios, thereby avoiding unnecessary synthesis jobs and adapting instead to the Pareto-promising scenarios. I have applied SDSE for component-level exploration with industrial high-level and physical synthesis tools, and have successfully integrated SDSE research into the IBM Synthesis Tuning System for production processor design.

- I consider SDSE extensible and general, seeing great potential for applications beyond synthesis and electronic system design. SDSE is extensible with code-refactoring techniques which introduce "virtual" knobs that are not natively offered by the synthesis tools (to optimize the

Table 1.2: Thesis Contributions to The Design Elements [150].

| Design Element | Contributions                                     | Chapter |

|----------------|---------------------------------------------------|---------|

| Specification  | a new abstraction layer between designers         | 3–6     |

|                | and synthesis tools;                              |         |

|                | a code-refactoring methodology                    | 7       |

| Agent          | automatic setting of synthesis knobs;             | 3–6     |

|                | automatic selection of component implementations; | 3–4     |

|                | automatic suggestion of code-refactoring options  | 7       |

| Goals          | discovery of post-synthesis Pareto set            | 3–7     |

| Environment    | learning methods as synthesis surrogates          | 5–6     |

|                | for design evaluation                             |         |

| Requirements   | adaptive component synthesis while satisfying     | 3–4     |

|                | system performance requirements                   |         |

| Primitives     | synthesis tools as query oracles                  | 3–7     |

| Constraints    | automation of large-scale                         | 3–7     |

|                | design-space exploration                          |         |

component specification of Figure 1.4). In particular, I propose a pattern-based refactoring methodology to further improve the DSE results in terms of both HLS QoR and tool runtime. Moreover, SDSE could be generalized (i) to create a platform for synthesis knob/library deployment/testing on real customer designs, (ii) to promote more collaboration between system architects and component designers, and (iii) to explore designs beyond VLSI chips, for applications which also require extensive CAD-tool invocations with different knob settings.

Table 1.2 summarizes my contributions to the design elements that were defined in Section 1.1.

#### 1.5 Outline of The Dissertation

The rest of this dissertation is organized as follows. In Chapter 2, I describe the background for the rise of heterogeneous SoCs, existing CAD tools for SoC design, and the need for a new generation

of CAD tools. I also present an overview of the related works on the topic of "multi-objective DSE with CAD tools" in Chapter 2. Afterwards, the dissertation is partitioned into three parts before Chapter 9 draws conclusions:

- Part I: System-Level Design-Space Exploration describes two SDSE frameworks for compositional system exploration. In particular, this part presents "synthesis planning for exploring ESL design" using HLS (Chapter 3) and "compositional approximation for SoC characterization" using logic synthesis (Chapter 4).

- Part II: Component-Level Design-Space Exploration describes two SDSE frameworks for iterative component exploration. In particular, this part presents "knob-setting optimization for high-level synthesis" (Chapter 5) and "parameter tuning for physical synthesis" (Chapter 6).

- Part III: Extending Supervised Design-Space Exploration describes a pattern-based code-refactoring methodology to enhance the HLS DSE results (Chapter 7) and sketches several future research directions based on SDSE (Chapter 8).

Finally, in Appendix A I describe four prototype SDSE tools that I develop:

- Synthesis Planning for Exploring ESL Design (SPEED): a prototype tool that implements SDSE with HLS for system-level DSE. The SPEED methodology and its companion algorithms are presented in Chapter 3.

- Compositional Approximation of Pareto Sets (CAPS): a prototype tool that implements SDSE with logic synthesis for system-level DSE. The CAPS algorithm and its companion heuristic modifications are presented in Chapter 4.

- Learning-based Exploration with Intelligent Sampling, Transductive Experimental Design, and Refinement (LEISTER): a prototype tool that implements SDSE with HLS for component-level DSE. LEISTER's underlying algorithms are presented in Chapter 5.

- Enhanced gSpan (EgSpan): a prototype tool for enhanced DSE with pattern-based coderefactoring. The code-refactoring methodology and the EgSpan algorithm are presented in Chapter 7.

### Chapter 2

## Background

Semiconductor chips have been the major driving force for the advancements of diverse computer systems, including personal computers, network servers, government/bank mainframes, and supercomputers. The semiconductor performance and cost continuously improve, making possible the global expansion of information technology, which is estimated to ascribe up to 40 percent of the global productivity growth in the period of 1993–2013 [17]. The improvements have, however, become increasingly difficult ever since early 2000. This chapter gives a brief introduction to the rise of heterogeneous System-on-Chip (SoC) and its design complexity, the existing Computer-Aided-Design (CAD) tools for addressing the design complexity, and the need for a new generation of CAD tools. After the introduction section, an overview of the related works on "design-space exploration with CAD tools" is presented to highlight the novelty of SDSE.

### 2.1 Design Complexity of SoC with CAD Tools

Since mid 80s, the application-level uniprocessor performance and the semiconductor device speed have increased by over 3,000X and 100X, respectively [87]; meanwhile, the fabrication cost per semiconductor gate has decreased linearly up to the 28nm-technology node [89]. The improvements were driven by a triplet of actions: (i) scale the process technology down, (ii) scale the supply voltage down, and (iii) scale the clock frequency up. Technology scaling shrinks the feature size (e.g. the size of the transistor gate), such that more transistors can be crammed onto a single die at the next technology node. Ideally, power density should remain constant with technology

scaling and voltage scaling (aka Dennard scaling [57]). However, voltage scaling slowed down due to excessive leakage current [56]; meanwhile, frequency was scaled faster than dictated by technology scaling [87]. Since technology scaling continued, processor design soon became power-limited and the frequency scaling practically stopped in the early 2000.

Given the power constraint, processor design resorted to homogeneous multi-core architectures by adding more processor cores to each die. Parallel processing allows each core to be more energy efficient by having a lower peak performance (due to the lower frequency), whereas multiple cores can increase the overall computing throughput performance. Even better, for maximum power saving, each core can dynamically adjust its operating voltage and frequency according to the currently-expected workloads, a technique known as Dynamic Voltage and Frequency Scaling. However, parallelism alone hits diminishing returns at both the low-energy and high-performance extremes [87]. That is, sacrificing large performance factors returns small energy savings, and vice versa. Moreover, other factors affecting the effectiveness of parallelism exist: (i) the parallelizable portions of an application can be limited by its nature (aka Amdahl's law) [7], (ii) a parallel algorithm may require higher time complexity than its sequential counterparts [116], and (iii) with advanced technology, cache-memory power consumption can be comparable to the power spent on computation [118]. As a result, homogeneous parallelism alone can not promise a long-term performance scaling similar to the one allowed by technology scaling for four decades.

#### 2.1.1 The Rise of Heterogeneous Architectures

Given the limitations of technology scaling and homogeneous parallelism, specialized hardware components (aka accelerators) emerge as energy-efficient solutions to work together with general-purpose processor cores. Accelerators are application-specific integrated circuits (ASICs) customized for dedicated tasks with improved computation and memory-access efficiencies. Graphic Processing Units (GPUs) can be regarded as a programmable form of accelerators [132]. A heterogeneous System-on-Chip (SoC) integrates general-purpose processor cores, GPU cores, and accelerator cores, in addition to other components for on-chip communication and data caching [21]. In fact, in the 2011–2013 period, the energy efficiency of commercial "processor + GPU" SoCs based on 22nm–32nm technologies is still below 10 MOPS/mW [49; 139; 192], while the efficiency of dedicated hardware designs based on 65nm–0.13um technologies can already reach the 100–1,000 MOPS/mW

range for applications such as multimedia [101], biomedicine [12], artificial intelligence [129], and computer vision [138; 179].

Despite the energy advantage, SoC design is facing demanding time-to-market schedules as well as ever increasing design costs. Typically, consumer processors or desktop SoCs follow a 12–18 month product cycle [6; 90], which is even shorter for mobile SoCs [148; 156]. Within the stringent cycles, the design complexity of a consumer SoC ranging from 47M transistors (Intel 45nm Atom, 2008) to 2B transistors (Apple 20nm A8, 2014) needs to be carefully addressed by usually teams of 10's–100's of engineers [184]. Converted into design costs, the sheer design complexity corresponds to high Non-Recurring-Engineering (NRE) investments. For instance, a 180M-gate chip costs \$80M-\$90M with a 28nm technology, and a 240M-gate chip would cost \$150M-\$160M with a 20nm technology [89; 94; 168]. Even worse, an over 300M-gate 16/14nm chip is projected to cost more than \$310M [89; 94; 168]. Moreover, the fabrication of an SoC from the photomask generation to the chip packaging can take 6–8 weeks [184]. With all these economic factors considered, the first-pass success is critical for commercial SoC design.

#### 2.1.2 ASIC Design Flow

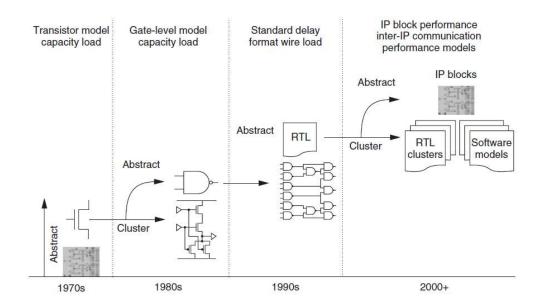

In order to address the enormous design complexity, Very Large Scale Integration (VLSI) design methodologies have progressed over 40+ years, from full-custom (manual) design to computer-aided design (CAD) with increasingly higher levels of abstraction for design capture. Fig. 2.1 depicts the chronological evolution across four decades when chip design has progressed from (i) schematic models to (ii) logic-gate (aka standard-cell) models, (iii) Register Transfer Level (RTL) models described by hardware description languages such as VHDL or Verilog, and finally (iv) Transaction Level Modeling (TLM) using high-level languages such as SystemC. By raising the level of abstraction, VLSI designs are captured in coarser granularity. This makes the number of design primitives remain manageable, thus increasing design productivity to handle the growing design scale. The multi-decade evolution is a joint result of the tight collaboration between industry (including worldwide design houses, CAD-tool vendors, and semiconductor foundries) and academia (including dedicated publication venues of 10+ active IEEE and/or ACM journals and conferences). From an economic perspective, the established ecosystem that makes building VLSI design successful is a reason why replacing the semiconductor technology (e.g. with quantum computing) for

Figure 2.1: The evolution of design abstraction for VLSI design (source: [157]).

resolving the power problem can be too expansive in the foreseeable future [87].

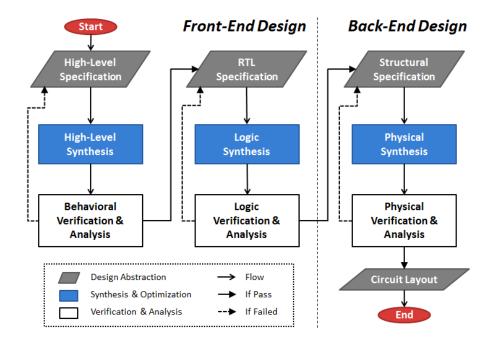

Fig. 2.2 shows a common ASIC design flow with CAD tools starting from high-level specification<sup>1</sup>. The flow is divided into two parts: (i) front-end design and (ii) back-end design. Regarding synthesis and verification, the front-end and back-end design focus on the functional and physical aspects, respectively. While the mainstream front-end design starts with a hand-crafted RTL specification, High-Level Synthesis (HLS) is becoming popular as explained in Chapter 1. The flow proceeds as follows.

- First, the high-level specification is synthesized by HLS tools into a synthesizable RTL specification. This needs to be verified that is behaviorally correct via simulation tools (e.g. virtual platforms [111]) or formal approaches (e.g. sequential equivalence checking [124]). The high-level design emphasizes micro-architectural optimization and its interaction with software.

- Afterwards, the RTL specification is synthesized by Logic Synthesis tools to a netlist of standard cells which implements the design with logic gates (such as AND and OR), sequential elements (such as registers and memories), and the connection among them. Also, the netlist needs to be verified via logic simulation or equivalence checking. In addition, Static Timing

<sup>&</sup>lt;sup>1</sup> More details about an ASIC design flow can be found in [184]. For instance, Fig. 2.2 omits scan-logic insertion for circuit testing, which per se is a research field in CAD [108].

Figure 2.2: An ASIC design flow.

Analysis (STA) is performed on the netlist for assessing its performance (i.e. the minimum clock period) based on primitive interconnect-load models.

• The verified netlist (i.e. structural specification) kicks off the back-end design by running Physical Synthesis tools, which generate the circuit layout of the design. If the layout passes physical verification and analysis (including STA with refined interconnect models, design-rule checking, logic-versus-schematic checking, and many others), the circuit can be signed off for fabrication (aka design closure).

Nowadays, this flow is not only common to ASIC design but also increasingly adopted for high-performance processor design, in order to cope with its sheer complexity [196].

Each synthesis step in the ASIC design flow involves multiple computation-intensive tasks [52; 166]:

• Major HLS tasks include: (i) allocating resources (e.g. adders, multipliers, etc.) for implementing target behaviors, (ii) scheduling operators (e.g. additions, multiplications, etc.) across multiple clock cycles for optimizing the latency of the design and the utilization of resources, and (iii) binding operators to resource instances and binding variables to register

instances to minimize implementation costs such as area and power.

- Major logic-synthesis tasks include: (i) minimizing a multi-level Boolean network by factoring with common sub-expressions and sharing minterms, (ii) mapping the Boolean network with technology-dependent standard cells to minimize implementation costs, and (iii) iteratively refining the synthesis results.