# Surface charge sensitivity of silicon nanowires: Size dependence

Niklas Elfström<sup>1\*</sup>, Robert Juhasz<sup>1,2</sup>, Ilya Sychugov<sup>1</sup>, Torun Engfeldt<sup>3</sup>, Amelie Eriksson Karlström<sup>3</sup> and Jan Linnros<sup>1</sup>

<sup>1</sup>Department of Microelectronics and Applied Physics, Royal Institute of Technology, SE-16440, Stockholm, Sweden

<sup>2</sup> Current address: Optical and Semiconductor Devices Group, Electrical and Electronic Engineering, Imperial College, London SW7 2AZ

<sup>3</sup>Department of Biotechnology, Royal Institute of Technology, SE-106 91 Stockholm,

Sweden

\*niklasel@imit.kth.se

#### **Abstract**

Silicon nanowires of different widths were fabricated in silicon on insulator (SOI) material using conventional process technology combined with electron beam lithography. The aim was to analyze the size-dependence of the sensitivity of such

nanowires for biomolecule detection and for other sensor applications. Results from electrical characterization of the nanowires show a threshold voltage increasing with decreasing width. When immersed in an acidic buffer solution smaller nanowires exhibit large conductance changes while larger wires remain unaffected. This behavior is also reflected in detected threshold shifts between buffer solutions of different pH and we find that nanowires of width > 150 nm are virtually insensitive to the buffer pH. The increased sensitivity for smaller sizes is ascribed to the larger surface/volume ratio for smaller wires exposing the channel to a more effective control by the local environment, similar to a surrounded gate transistor structure. Computer simulations confirm this behavior and show that sensing can be extended even down to the single charge level.

Semiconductor nanowires and (semiconducting) carbon nanotubes have been reported as promising building blocks for future biosensors enabling direct electrical detection of biomolecules<sup>1,2,3,4</sup>. The small size or more specifically the small diameter, typically below 50 nm, causes their electrical properties to be very dependent on the local environment where charge changes on the surface induce a field effect which significantly changes the carrier concentration and thus, the conductance. This charge sensitivity is in principle not limited to the surface of the device but is usually set by the Debye screening length in the liquid which could be on a nanometer range at high molar concentrations. The sensitivity of nanowires for biomolecule detection has been shown to extend down to the attomolar range<sup>5</sup> although single molecule detection has (to authors knowledge) not yet been observed.

The electrical characteristics of low- to medium doped nanowires resemble that of field effect transistors where a channel is induced (or depleted) in the nanowire depending on the local charge and on the bias of an external gate<sup>6,7</sup>. Doping of the nanowire plays here a minor role and whether electrons or holes are the active current carrying species is effectively determined by the contacts to the nanowire. The high sensitivity for local charges has also a parallel in conventional silicon technology where MOS transistors are sensitive to charges in the gate oxide largely affecting their threshold behavior. Indeed, at very small channel dimensions this can be extended down to the single charge level as demonstrated at room temperature in the 1990's<sup>8</sup>.

Up to now, most reports of nanowires as biosensors have been based on nanowires grown in the gas phase by CVD techniques that were subsequently deposited onto silicon wafers. The wafers had an insulating top oxide and contacts were either patterned before deposition or after. The first method relies on a random alignment of nanowires between contacts whereas the second method involves inspection with SEM and subsequent lithography. Both methods involve a large randomness in fabrication and do not seem to be easily scaleable for mass fabrication and for multiple detection devices involving a large number of sensors. The advantage of the technique, on the other hand, is the relative ease of production of small diameter nanowires of very homogeneous width.

Recent reports have, however, pointed out the possibility to use ordinary silicon CMOS technology to achieve similar effects<sup>1,9</sup>. The nanowire is then defined in the active top layer of a SOI wafer (silicon on insulator) thinned down to the order of ~100 nm and contacts are formed using conventional metallization schemes. The small width, crucial to the sensitivity, is achieved by electron beam lithography but may eventually be defined using deep UV lithography as CMOS technology move into the sub 50 nm range.

Modeling of the electrical behavior of silicon nanowires is difficult because size and geometry may not be known accurately including e.g. oxide charges. As a result, simple surface charge arguments or even changes in the mobility at small diameters have been invoked<sup>9,10</sup>. Thus, the large sensitivity of small diameter nanowires for local charges compared to large devices has not been explained<sup>11,12</sup>. This would require full 3-

dimensional simulations including relevant built-in charges of all surfaces of the nanowire.

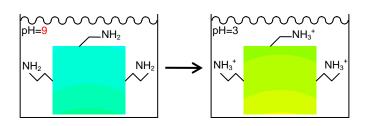

In this work we address the size dependence of the sensitivity of silicon nanowires for local charge changes as e.g. during biomolecule detection. We have therefore fabricated nanowires of different widths (including a micron sized wire) on the same chip to be able to compare electrical characteristics as a function of only nanowire width under equal processing conditions. The nanowires were defined in SOI material using electron-beam lithography while large silicon leads and contacts were defined using optical lithography. Electrical characteristics were studied both for as–fabricated wires and under buffer solutions of pH = 3.0 and pH = 7.4, to positively charge the amino groups (and negatively charge remaining silanol groups) on the nanowire surface and thus change the electrical properties of the device<sup>4</sup>. Our measurements and extraction of threshold voltages for the different sizes are supported by simulations of the cross-sectional charge density in the nanowire at different surface charge concentrations. This enables us to demonstrate the superior charge sensitivity as the nanowire width is reduced, in fact approaching the single charge level as demonstrated previously for narrow channel MOS devices.

Nanowires were fabricated on silicon on insulator (SOI) material using e-beam lithography and optical lithography followed by plasma etching. Their widths were varied using different dose in the e-beam lithography process thus creating an opening in the resist of different size. The top silicon layer was 100 nm thick (p-doped,  $\rho = 17 - 22$   $\Omega$ cm) separated through a 400 nm thick buried oxide layer from the bulk silicon. The

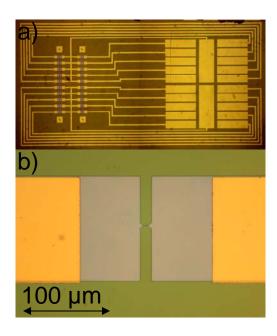

nanowires were oxidized in a dry oxidation process at 900 °C for 10 minutes (nominally resulting in a 5 nm thick oxide) to provide electrical isolation and to increase the stability and decrease the number of dangling bonds. After oxidation the nanowire surface was modified with APTES molecules that react with the -SiOH groups on the surface resulting in an -NH<sub>2</sub> surface termination. Two buffer solutions were used, 40 mM NaOAc with pH = 3.0 and 10 mM NaPO<sub>4</sub> with pH = 7.4. A top view of the chip layout can be found in Figure 1 (a). 22 gold pads (0.2  $\mu$ m thick) to the right connect to 20 nanowires to the left. The gold wires connect to 100  $\mu$ m wide Si pads which are in connection to the nanowires shown in Figure 1 (b). The nanowire width was varied from ~50 nm to ~170 nm and the length was 1  $\mu$ m for all of them. A SEM image of a typical nanowire is shown as inset in Figure 3. Two microwires were included on all chips next to the nanowires.

**Figure 1.** Optical micrographs of a silicon nanowire chip, 10 mm long. (a) Full chip with gold contact pads to the right and gold interconnects to the Silicon nanowires to the left. (b) Detail showing the Schottky junction contact area (TiW/Au) partly covering the silicon leads connected to the nanowire in the centre.

For electrical characterization a computer-controlled picoammeter/voltage source (Keithley 6487) and a KPCI-3201 D/A – A/D card was used. A voltage,  $V_{DS} = V_D - V_S$ , was applied between the source and the drain of the nanowire and another voltage,  $V_{GS} = V_G - V_S$ , was applied to the bulk Si layer working as a back gate.

The electrical properties of the nano and micro-devices were simulated in a twodimensional semiconductor simulation package (ISE-TCAD). The devices were simulated in a cross-section perpendicular to the wires.

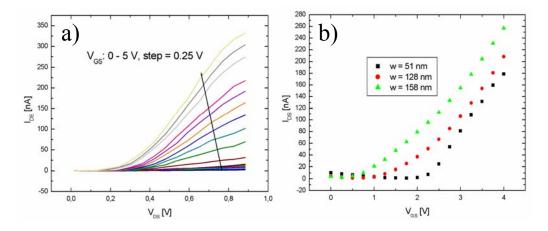

We have previously reported<sup>13</sup> that the nanowires work in a similar way as MOS transistors, conducting through an inversion layer close to the silicon dioxide layer. Typical  $I_{DS}$ - $V_{DS}$  curves from such a device are shown in Figure 2 (a). Different saturation currents,  $I_{DS}$  (sat), are observed for different back gate voltages,  $V_{GS}$ , which confirm the MOS behavior. However, for smaller nanowires,  $w < \sim 140$  nm there is a quenching of the channel due to surface charges at low  $V_{DS}$  bias also seen before<sup>14</sup>. This is due to surface charges blocking the channel and this behavior is increased with decreasing width<sup>15</sup>. For intermediate sized nanowires, 140 nm < w < 160 nm, the  $I_{DS} - V_{DS}$  characteristics is similar to a MOS transistor. This also confirms that the Schottky junctions at the contacts

do not limit the current through the device (largely because of the large contact area). For larger wires,  $w > \sim 140$  nm, at high gate voltage and high bias there is a limit in the current due to the Schottky junctions<sup>15</sup>. Based on the contact area,  $100 \mu m \times 100 \mu m$ , the Schottky barrier between Ti/W and Si,  $\Phi_B = 0.46$  eV and room temperature, T = 300 K, using the standard Schottky current formula this current can be calculated to  $\sim 20 \mu A$ . In our nanowires and microwire the limiting current amounts to  $\sim 0.5 \mu A$  possibly due to the entire contact area not being active (injection closer to nanowires should dominate).

In order to measure the sensitivity of such a device a crucial parameter is the threshold voltage,  $V_{TH}$ . A change of surface charges should either enhance the current (positive charges) or decrease the current (negative charges) and thus work as a top gate. As a result, the threshold voltage for the back gate,  $V_{GS}$ , would be changed. Moreover, at small widths surface charges on the sidewall of the nanowires will become increasingly important influencing the charge density in the channel. This is essentially a surface to volume ratio argument and we expect, thus, an increased sensitivity for surface charges for smaller widths which should be reflected in a difference in threshold voltage with respect to width. A relevant scaling parameter for this effect to set in would be the thickness (here 100 nm). Indeed, Figure 2 (b) shows  $I_{DS}$  vs.  $V_{GS}$  curves for three nanowires of different size confirming a threshold voltage dependence on nanowire width.

**Figure 2.** (a) Typical  $I_{DS}$ - $V_{DS}$  curves for a nanowire ~50 nm wide at different back gate voltages  $V_{GS}$ : 0-5 V, step = 0.25 V. (b)  $I_{DS}$  vs.  $V_{GS}$  for three different nanowires of widths 51, 128 and 158 nm extracted from  $I_{DS}-V_{DS}$  curves of each nanowire respectively at  $V_{DS}$  = 0.77 V.

To further explore this effect, the threshold voltage has been extrapolated from the  $I_{DS}$  –  $V_{GS}$  curves for nine nanowires of size ~50 nm to ~170 nm and one microwire of ~1  $\mu$ m of width as shown in Figure 3. The threshold voltage clearly decreases with increasing nanowire width approaching a constant value at widths larger than ~150 nm. This is in agreement with the idea that the influence from surface charges is enhanced when the width of the nanowire is decreased.

Figure 3. Threshold voltage plotted vs. width for nanowires of 50-160 nm width and for one microwire of  $\sim 1~\mu m$  width. The threshold voltage has been extrapolated from  $I_{DS}$ - $V_{GS}$  plots<sup>16</sup> at 0.77 V (error bars show variation in fits). Inset shows a top SEM image of a typical nanowire of 154 nm width.

This scenario is somewhat more complicated in reality since it is a well known fact that a positive charge density is present at the silicon/silicon dioxide interface and also inside the oxide layer<sup>17</sup>. This charge will thus increase the conduction of the nanowire, assuming an electron channel. The fabrication process of the nanowires can also be assumed to give some nonzero surface charges surrounding the nanowire, which may be negative. If so, they will counter-act the positive oxide charges and they will thus decrease the conductivity of the nanowire.

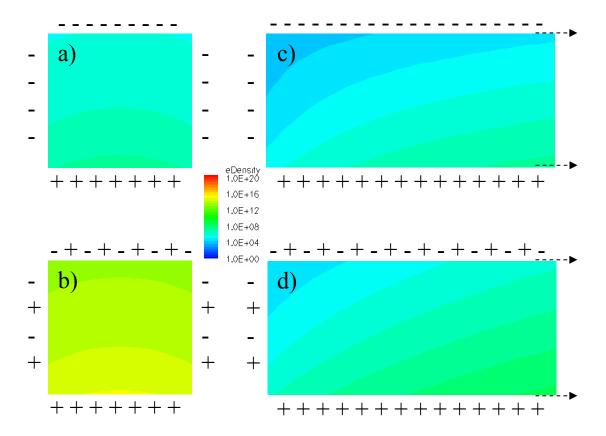

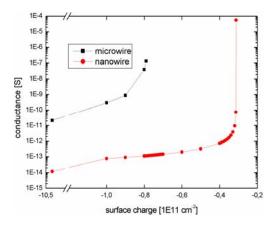

In the computer simulation it is thus relevant to explore a scenario where both positive and negative charges are present at the surface. We have calculated the electron density over the 2-dimensional cross section of a 100 nm wide nanowire and of a 1  $\mu$ m wide microwire, both of 100 nm thickness. This is shown in Fig. 4 for two different negative

surface charge states where the less negative surface charge is indicated with repeated + and - signs. In the simulations a positive interface charge density has been set to  $+1\cdot10^{11}$  cm<sup>-2</sup> at the bottom of the cross section as a realistic oxide charge<sup>17</sup>. The plots clearly demonstrate the effect of the negative charge at the surface shrinking the channel towards the centre of the channel, an effect which is more dramatic for the 100 nm wire.

**Figure 4.** (a) –(b) Simulated electron concentration for a perpendicular cross section of a nanowire of 100 nm width. (c)-(d) Simulated electron concentration for the left 200 nm part of the microwire (1  $\mu$ m total width) cross section. An assumed interface charge of  $+1\cdot10^{11}$  cm<sup>-2</sup> (in all cases) is indicated with repeated "+" signs at the bottom of both cross sections. For the nanowire, (a) illustrates the electron concentration at a surface charge of

$-3.2 \cdot 10^{10}$  cm<sup>-2</sup> indicated with repeated "-" signs while (b) shows the electron concentration at a surface charge of  $-3.1 \cdot 10^{10}$  cm<sup>-2</sup> indicated with repeated "+" and "-" signs. For the microwire (c) illustrates the electron concentration at a surface charge of  $-9.10^{10}$  cm<sup>-2</sup> indicated with repeated "-" signs while (d) shows the electron concentration at a surface charge of  $-8.10^{10}$  cm<sup>-2</sup> indicated with repeated "+" and "-" signs.

To see the effect on the conductance, the cross sectional electron density has been integrated to get the conductance at the assumed surface charge according to:

$$G = \frac{q\mu_n}{L} \int_A n dA ,$$

where L is the nanowire length,  $\mu_n$  is the electron mobility (here set as 1000 cm²/Vs as typical for an n-channel MOS transistor), q is the electron charge and n is the electron density for each area element. This yields the conductance in the linear region (for small  $V_{DS}$ ), far from pinch-off (note that serial resistance such as from the Schottky contact is not included in these calculations). The result is plotted in Fig. 5 versus surface charge for the two differently wide wires. Apparently, the conductance changes quite abruptly at a specific surface charge density which is more positive for the nanowire due to the negative charge also at the side edges. Moreover, the rate of change in conductance per added surface charge is much larger for the nanowire than for the microwire. For instance a change of only  $\sim 6 \times 10^8$  cm<sup>-2</sup> in surface charge close to the abrupt transition at  $\sim 3 \times 10^{10}$  cm<sup>-2</sup> induces a tenfold increase in conductance (from  $\sim 1 \times 10^{11}$  cm<sup>-2</sup> to  $1 \times 10^{10}$  cm<sup>-2</sup>). Assuming that such a change in conductance can be detected, we calculate that for a 1  $\mu$ m long and 100 nm wide nanowire (100 nm thick) this surface charge density corresponds to only  $\sim 2$  elementary charges! Thus, the nanowire could in principle

approach single-charge detection sensitivity (of course averaged on the time scale of binding/unbinding events at the surface).

**Figure 5.** Calculated conductance vs. surface charge for a nanowire of 100 nm width and a microwire of  $1\mu$ m width, both assuming an interface charge of  $+1\cdot10^{11}$  cm<sup>-2</sup>. The calculated conductance is based on integrations of perpendicular cross sections of simulated electron concentrations as shown in Fig. 4.

These observations show that the presence of charges on the surface as well as interface properties have a large impact on these devices due to the large surface to volume ratio enabling efficient control of the induced channel. To further prove this, an experiment was designed to change the surface charges by the addition of a buffer solution. By adding a buffer solution of pH=3 to the nanowire the -NH<sub>2</sub> groups on the surface become positively charged and are protonated into -NH<sub>3</sub><sup>+</sup> groups, and thus works as a positive top gate<sup>4</sup>. This enhances the current through the nanowire at a certain  $V_{DS}$ . Figure 6 (a) shows the conductance shift at a certain  $V_{DS}$  for nanowires of different widths and a microwire when a buffer solution is added to the surface of the wire. In accordance with previous

results the smallest nanowire reacts more to the surface charge change than the microwire whose conductance remains constant. In another experiment, the buffer solution was changed from one with pH = 3.0 to one with pH = 7.4. This resulted in large threshold voltage shifts for the smaller wires but essentially no difference was observed for nanowires larger than  $\sim 150$  nm, see Fig. 6 (b). Note that in these experiments contacts were protected from the buffer solution by a polymer and only the nanowire was exposed to the different solutions (see supporting information).

**Figure 6.** (a) Conductance ratio vs. width for nanowires in the range  $\sim$ 50-100 nm and for a microwire at  $V_{DS} = 0.65$  V. Here the shift occurred when the bare surface was covered with a buffer solution of pH = 3.0. (b) Threshold voltage shift,  $\Delta V_{TH}$ , vs. width for

nanowires in the range  $\sim$ 50-100 nm and for a microwire of  $\sim$ 1 $\mu$ m width at  $V_{DS}$  = 0.65 V. The shift occurred when the pH value of the buffer solution added to the surface was changed from 3.0 to 7.4.

These data clearly show that the impact of surface charges is dependant on the surface to volume ratio and that this can explain the increasing threshold voltage for decreasing nanowire width and confirms the simulations and theory. For nanowires of larger width than  $\sim$ 150 nm the behavior is similar to that of the microwires and no detection sensitivity seems to be left.

Summarizing, we have shown that the threshold voltage increases, due to an increasing surface charge effect, with decreasing nanowire width. This effect has been demonstrated through computer simulation and experimentally for a oxide covered nanowire and microwire surface and for surfaces exposed to a buffer solution of pH = 3.0 and pH = 7.4. This shows that the silicon nanowire could work as a sensitive detector for sensing pH and charged molecules attached to the surface down to the single-charge level. We also demonstrate that extraction of the threshold voltage is a promising way of characterizing changes of the surface charge. Finally, large nanowires with widths  $> \sim 150$  nm loose their detection sensitivity similar to micron-sized wires.

### Acknowledgement

The authors want to thank Dr. Björn Renberg for providing the buffer solutions of different pH-value. Funding was provided by the National Swedish Research Counsil (VR).

**Supporting Information Available**:  $I_{DS} - V_{DS}$  characteristics for several nanowires and a microwire and pH experiment preparation. This material is available free of charge via the Internet at <a href="http://pubs.acs.org">http://pubs.acs.org</a>.

### **References and Notes**

- (1) Li, Z.; Chen, Y.; Li, X.; Kamins, T. I.; Nauka, K.; Williams, R. S.; *Nano Lett.* **2004**, 4 (2), 245-247

- (2) Hsu, J.-F.; Huang, B.-R.; Huang, C.-S.; Chen, H.-L.; *J. J. Appl. Phys.* **2005**, 44 (4B), 2626-2629

- (3) Chen, R. J.; Choi, H. C.; Bangsaruntip, S.; Yenilmez, E.; Xiaowu, T.; Wang, Q.; Chang, Y-L.; Dai, H.; *J. Am. Chem. Soc.* **2004**, 126, 1563-1568

- (4) Cui, Y.; Wei, Q.; Park, H.; Lieber, C. M.; Science 2001, 293, 1289

- (5) Patolsky, F., Zheng, G., Hayden, O., Lakadamyali, M., Zhuang, X., Lieber, C. M., PNAS 2004, 101 (39), 14017-14022

- (6) Koo, S.-M.; Fujiwara, A.; Han, J.-P.; Vogel, E. M.; Richter, C. A.; Bonevich, J. E.; *Nano Lett.* **2004**, 4 (11), 2197-2201

- (7) Cui, Y.; Duan, X.; Hu, J.; Lieber, M.; J. Phys. Chem. **2000**, 104 (22)

- (8) S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe', and K. Chan, *Appl. Phys. Lett.* **1996**, 68, 1377

- (9) Stern, E., Klemic, J. F., Routenberg, D. A., Wyrembak, P. N., Turner-Evans, D. B., Hamilton, A. D., LaVan, D. A., Fahmy, T. M., Reed, M. A., *Nature* **2007**, 445

- (10) Ashcroft, B.; Takulapalli, B.; Yang, J.; Laws, G. M.; Zhang, H. Q.; Tao, N. J.; Lindsay, S.; Gust, D.; Thornton, T. J.; *Phys. Stat. Sol.* **2004**, 241 (10), 2291-2296

- (11) Sensitivity vs. inverse surface area has been found but not explained in Stern, E. et al., *Nature* **2007**, 445

- (12) An analytical approach assuming a homogeneous electron density on ZnO nanowires have been shown in Fan, Z.; Lu, J. G.; *IEEE Trans. Nanotech.* **2006**, 5, 393-396

- (13) Juhasz, R.; Elfström, N.; Linnros J.; Nano Lett. 2004, 5 (2), 275-280

- (14) See supplementary fig. 5 (b) in Supplementary Information; Stern, E., Klemic, J. F., Routenberg, D. A., Wyrembak, P. N., Turner-Evans, D. B., Hamilton, A. D., LaVan, D. A., Fahmy, T. M., Reed, M. A., *Nature* **2007**, 445

- (15) See supplementary fig. 1 in Supporting Information of this paper.

- (16) Sze, S. M., *Physics of semiconductor devices*, 2<sup>nd</sup> Ed., Wiley Inc., New York, **1981** (17) Seo, K.-I., Sharma, S., Yasseri, A. A., Stewart, D. R., Kamins, T. I., *Electrochemical and Solid-State Letters* **2006**, 9 (3), G69-G72

## **Table of Contents Graphic**