# Surface-Passivated High-Resistivity Silicon Substrates for RFICs

B. Rong, J. N. Burghartz, Fellow, IEEE, L. K. Nanver, Member, IEEE, B. Rejaei, and M. van der Zwan

Abstract—Surface passivation of high-resistivity silicon (HRS) by amorphous silicon thin-film deposition is demonstrated as a novel technique for establishing HRS as a microwave substrate. Metal–oxide–silicon (MOS) capacitor measurements are used to characterize the silicon surface properties. An increase of the quality factor (Q) of a 10-nH spiral inductor by 40% to Q = 15 and a 6.5-dB lower attenuation of a coplanar wave guide (CPW) at 17 GHz indicate the beneficial effect of the surface passivation for radio frequency (RF) and microwave applications. Regarding CPW attenuation, a nonpassivated 3000- $\Omega \cdot$  cm substrate is equivalent to a 70- $\Omega \cdot$  cm passivated substrate. Surface-passivated HRS, having minimum losses, a high permittivity, and a high thermal conductivity, qualifies as a close-to-ideal radio frequency and microwave substrate.

Index Terms—Attenuation, conductivity, coplanar waveguides, dielectric losses, eddy currents, excimer lasers, high-frequency (HF) measurements, HF receivers, HF transmitters, inductors, integrated circuit doping, losses, lossless circuits, loss measurement, magnetic fields, microwave circuits, microwave technology, monolithic microwave integrated circuits (MMICs), mobile communication, Q factor, scattering parameters, semiconductor device fabrication, semiconductor materials, silicon, transmission lines.

### I. INTRODUCTION

IGH-RESISTIVITY SILICON (HRS) has long been viewed as an ideal substrate for radio frequency integrated circuits (RFICs) [1]-[5], but surface effects tend to overshadow the potentially low RF loss levels in HRS [6]–[9]. Charges within the insulating  $SiO_2$  layer and at the  $SiO_2/Si$ interface lead to accumulation or inversion layers at the silicon surface, contributing to an increased attenuation of integrated transmission lines [6]–[11], a reduced quality factor (Q) of on-chip spiral inductors [12], and a leakage path between integrated devices [6]. Furthermore, the surface-channel losses can be bias-dependent, leading to difficulties in parameter control [7]. The impact of a parasitic surface channel is consequently more pronounced in coplanar wave guide (CPW) structures, in which the electric field is more concentrated at the wafer surface, [6]–[9], [11] than in microstrip structures [7], [10], or spiral inductors [12]. In view of the recent attention to the application of HRS substrates in RFIC processes [13],

The authors are with the Laboratory of Electronic Components, Technology and Materials (ECTM), Delft Institute of Microelectronics and Submicron technology (DIMES), Delft University of Technology, 2600 GA Delft, The Netherlands (b.rong@dimes.tudelft.nl).

Digital Object Identifier 10.1109/LED.2004.826295

elimination of surface channels on HRS is highly desirable. The conventional surface channel stopper is not very applicable since the additional doping at the surface will lead to even higher losses [14]. Solutions will come from techniques that will transform the silicon surface region underneath the passive components into a highly damaged but still semiconducting material, having a very high trap density in the bandgap and possibly an increased bandgap. Conceptually, either a thin film having such properties can be deposited at the silicon surface or the silicon surface can be damaged by a high-dose implantation of, e.g., argon (Ar-I/I) prior to the interconnect formation in an IC fabrication process. Surface passivation by polysilicon thin-film deposition [10] and by amorphization through Ar-I/I [11], [12] have recently been proposed and demonstrated. The reliability and stability in subsequent hot-processing steps, which are crucial criteria in manufacturing, however, have not been addressed to date.

In this letter, a new HRS surface passivation technique, using an amorphous silicon thin-film deposition, is presented. The effectiveness of the new technique is demonstrated by a considerable improvement in CPW attenuation and inductor-*Q*. Process temperature stability is demonstrated for the first time and shown to be superior to the mentioned passivation technique by Ar-I/I.

# II. FABRICATION AND CHARACTERIZATION

Float-zone HRS p-type wafers with nominally  $3000-\Omega \cdot cm$  resistivity were used to fabricate metal-oxide-semiconductor capacitors (MOS-caps) and CPWs for characterization of the HRS surface region. Half of the wafer received a 30-nm thermally grown SiO<sub>2</sub> layer, through which a  $10^{15}$  cm<sup>-2</sup> Ar dose was implanted. That Ar dose is close to the critical dose for amorphization by Ar-I/I. A 300-nm-thick surface layer of silicon was amorphized by the Ar-I/I [verified by transmitting electron microcope (TEM)]. On the other half of the wafer, a 300-nm amorphous silicon ( $\alpha$ -Si) layer was formed by plasma-enhanced chemical vapor deposition (PECVD, 350 °C for 3.5 h) directly on the HRS. Note that both techniques will require an additional photolithographic mask in an IC process. Next, a 500-nm-thick SiO<sub>2</sub> layer was deposited over the entire wafer by PECVD at 350 °C for 1.2 min. Finally, a 4- $\mu$ m-thick metallization was added to form MOS-caps with a radius of 1 mm, having the second contact at the wafer backside. That backside contact was formed at the end of the process by using excimer laser annealing in order not to expose the wafer frontside initially to any additional thermal budget [15]. Also, 10-nH spiral inductors and CPWs (signal line width = 50  $\mu$ m signal-ground spacing

Manuscript received December 8, 2003; revised January 19, 2004. The authors wish to acknowledge the financial support by Philips Semiconductors and the collaboration with Philips Research in the research program Philips Associated Center at DIMES (PACD). The review of this paper was arranged by Editor S. Kawamura.

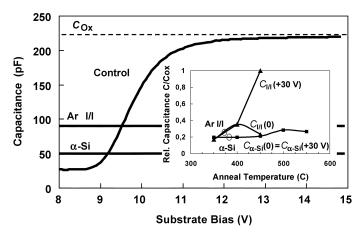

Fig. 1. C-V characteristics of MOS capacitors on a 3000- $\Omega$  · cm silicon wafer without (control) and with surface passivation either by Ar implantation (Ar-I/I) or by amorphous silicon deposition ( $\alpha$ -Si), measured at 100 kHz after a 400- °C, 30-min anneal. The oxide capacitance ( $C_{\text{Ox}}$ ) is indicated as a reference. The inset shows the relative change in capacitance at biases of 0 (inversion regime) and 30 V (accumulation regime), indicating that with the Ar-I/I passivation the bias-dependence of the capacitance reappeared at 450 °C, while with  $\alpha$ -Si passivation, the capacitance remained constant even at 550 °C. Note that the data shown in the inset are not de-embedded, thus, having somewhat lower  $C/C_{\text{Ox}}$  values.

= 25  $\mu$ m) were fabricated. The test structures were then measured and subsequently annealed in nitrogen N(<sub>2</sub>) ambient at 400 °C, 450 °C, 500 °C, and 550 °C, for 30 min with remeasurement after each interval. The MOS-caps were measured at frequencies ranging from 1 kHz to 1 MHz for dc biases between 0 and +30 V by using an HP-4284 LCR meter. Inductors and CPWs were characterized through *S*-parameter measurements up to 30 GHz by using an HP-8110 network analyzer.

#### **III. RESULTS AND DISCUSSION**

The capacitance–voltage (C-V) characteristics of a MOS-cap without any surface passivation (control) and with an Ar-I/I or an  $\alpha$ -Si thin-film deposition at 100 kHz after a 400 °C, 30 min anneal are shown in Fig. 1. The considerable impedance of the HRS substrate was subtracted from the measured data by applying a special de-embedding technique [16]. It is obvious from Fig. 1 that the Control showed a typical high-frequency MOS-cap characteristics at 100 kHz, indicating the buildup of a depletion region in inversion regime (substrate bias < 9 V), while with the Ar-I/I and the  $\alpha$ -Si there was no bias dependence and the capacitances were far lower than the oxide capacitance  $(C_{\text{Ox}}; \text{Fig. 1})$ . For the measurement frequencies  $\ll 100 \text{ kHz}$  a clear low-frequency characteristic was found for the control (not shown). The surface-passivated MOS-caps still did not show any bias dependence, but the capacitance value did increase with lowering of the frequency; for the Ar-I/I device, a value equal to  $C_{\text{Ox}}$  was reached at the minimum test frequency of 1 kHz (not shown). This indicated that apparently no depletion region was building up in the highly damaged silicon surface region and that the majority carriers could only accumulate directly at the surface at very low test frequencies. Both types of surface passivation were stable up to an anneal temperature of 400 °C (inset Fig. 1). At 450 °C, the high-frequency MOS-cap C-V characteristics reappeared for the Ar-I/I case. The  $\alpha$ -Si device remained

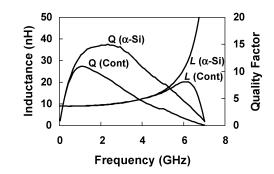

Fig. 2. Inductance and quality factor (Q) of a 10-nH inductor versus frequency on a 3000- $\Omega$  · cm substrate without (control) and with ( $\alpha$ -Si) surface passivation.

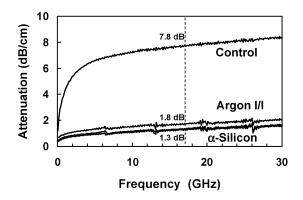

Fig. 3. Attenuation of coplanar wave guides versus frequency on a 3000- $\Omega$  cm substrate without (control) and with ( $\alpha$ -Si; Ar-I/I) surface passivation.

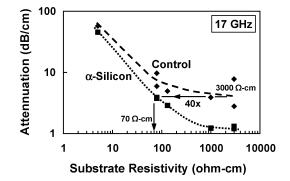

Fig. 4. Attenuation of coplanar wave guides at 17 GHz as a function the substrate resistivity and without (Control) and with ( $\alpha$ -Si) surface passivation (data from two experimental runs). It is indicated that the 3000- $\Omega$  · cm silicon Control exhibits an attenuation that is equivalent to a surface-passivated substrate having 70- $\Omega$  · cm resistivity.

bias-independent up to the maximum annealing temperature of  $550 \,^{\circ}$ C. Higher anneal temperatures could not be evaluated because of melting of the Al contacts near 600  $^{\circ}$ C.

The fact that the  $\alpha$ -Si passivation was successful in preventing the formation of a conductive channel at the silicon surface led to a substantial increase in inductor-Q by ~40% (Fig. 2). For the CPWs, the effect of surface passivation was even more pronounced (Fig. 3). The application of the Ar-I/I led to a 6.0-dB lower attenuation at 17 GHz, while another 0.5-dB reduction was achieved with using the  $\alpha$ -Si passivation layer. Fig. 4 shows the attenuation losses of CPWs built on silicon substrates and having resistivities in the range of 5–3000  $\Omega$  · cm with and without  $\alpha$ -Si passivation at 17 GHz. It is indicated that

a 3000- $\Omega$  · cm substrate without any surface passivation exhibits a CPW attenuation that is equivalent to that of a 70- $\Omega$  · cm passivated substrate. Besides, the data spread was much smaller with the surface passivation compared to the untreated HRS.

## **IV. CONCLUSION**

Surface-passivated HRS, having minimum losses, a high permittivity, and a high thermal conductivity, qualifies as a close-toideal RF and microwave substrate. Passivation can be achieved through amorphization of the silicon surface in order to prohibit the buildup of a conductive surface channel. Amorphization through the deposition of a thin amorphous silicon film is superior to amorphization by argon implantation in terms of loss reduction and stability in post annealing. The demonstrated stability of the surface passivation after an annealing temperature up to 550 °C is more than sufficient to make high-resistivity silicon passivation by amorphous silicon deposition applicable to RFIC process technology prior to the backend processing.

## ACKNOWLEDGMENT

The authors wish to thank the sample fabrication and support in testing that was provided by the technical staff of the DIMES Integrated Circuit Processing (ICP) group, and the Microwave Components Lab (MCL).

#### References

- T. M. Hyltin, "Microstrip transmission on semiconductor dielectrics," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-13, pp. 777–781, June 1965.

- [2] P. J. Stabile, A. Rosen, W. M. Janton, A. Gombar, and M. Kolan, "Millimeter wave silicon device and integrated circuit technology," in *MTT-S Dig.*, vol. 84, 1984, pp. 448–450.

- [3] J. Büchler, E. Kasper, P. Russer, and K. M. Strohm, "Silicon high-resistivity substrate millimeter wave technology," *IEEE Trans. Microwave Theory Tech.*, vol. MTT–34, pp. 1516–1521, Dec. 1986.

- [4] M. H. Hanes, A. K. Agarwal, T. W. O'Keefe, H. M. Hobgood, J. R. Szedon, T. J. Smith, R. R. Siergiej, P. G. McMullin, H. C. Nathanson, M. C. Driver, and R. N. Thomas, "MICROX—an all-silicon technology for monolithic microwave integrated circuits," *IEEE Electron Device Lett.*, vol. 14, pp. 219–221, May 1993.

- [5] A. C. Reyes, S. M. El-Ghazaly, S. Dorn, M. Dydyk, D. K. Schroder, and H. Patterson, "High-resistivity silicon as a microwave substrate," in *Proc. Electronic Components and Technology Conf.*, 1996, pp. 382–391.

- [6] D. Beck, E. Herrmann, and E. Kasper, "CMOS on FZ-high-resistivity substrate for monolithic integration of SiGe-RF-circuitry and readout electronics," *IEEE Trans. Electron Devices*, vol. 44, pp. 1091–1101, July 1997.

- [7] B. Rejaei, K. T. Ng, C. Floerkemeier, N. P. Pham, L. K. Nanver, and J. N. Burghartz, "Integrated transmission lines on high-resistivity silicon: coplanar waveguides or microstrips?," in *Proc. ESSDERC*, 2000, pp. 460–463.

- [8] C. Schöllhorn, W. Zhao, M. Morschbach, and E. Kasper, "Attenuation mechanism of aluminum millimeter wave coplanar waveguides on silicon," *IEEE Trans. Electron Devices*, vol. 50, pp. 740–746, Mar. 2003.

- [9] J. N. Burghartz, M. Bartek, B. Rejaei, P. M. Sarro, A. Polyakov, N. P. Pham, E. Boullaard, and K. T. Ng, "Substrate options and add-on process modules for monolithic RF silicon technology," in *Proc. BCTM*, 2002, pp. 17–23.

- [10] H. S. Gamble, B. M. Armstrong, S. J. N. Mitchell, Y. Wu, V. F. Fusco, and J. A. C. Stewart, "Low-loss CPW lines on surface stabilized high-resistivity silicon," *IEEE Microwave Guided Wave Lett.*, vol. 9, pp. 395–397, Oct. 1999.

- [11] E. Valetta, J. van Beek, A. den Dekke, N. Pulsford, H. F. F. Jos, L. C. N. de Vreede, L. K. Nanver, and J. N. Burghartz, "Design and characterization of integrated passive elements on high-ohmic silicon," in *MTT-S Dig.*, vol. 2, 2003, pp. 1235–1238.

- [12] A. B. M. Jansman, J. T. M. van Beek, M. H. W. M. Van Delden, A. L. A. M. Kemmeren, A. D.A. Den. Dekker, and F. P. Widdershoven, "Elimination of accumulation charge effects for high-resistivity silicon substrate," in *Proc. ESSDERC*, 2003, pp. 3–6.

- [13] K. Benaissa, Y. Jau-Yuann, D. Crenshaw, B. Williams, S. Sridhar, J. Ai, G. Boselli, Z. Song, T. Shaoping, S. Ashburn, P. Madhani, T. Blythe, N. Mahalingam, and H. S. Shichijo, "RF-CMOS on high-resistivity substrates for system-on-chip applications," *IEEE Trans. Electron Devices*, vol. 50, pp. 567–576, Mar. 2003.

- [14] J. N. Burghartz, M. Soyuer, and K. A. Jenkins, "Integrated RF and microwave components in BiCMOS technology," *IEEE Trans. Electron Devices*, vol. 43, pp. 1559–1570, Sept. 1996.

- [15] L. K. Nanver, E. J. G. Goudena, and J. Slabbekoorn, "Kelvin test structure for measuring contact resistance of shallow junctions," in *Proc. IEEE Int. Conf. Microelectronic Test Structures*, vol. 9, 1996, pp. 241–245.

- [16] B. Rong, L. K. Nanver, J. N. Burghartz, A. B. M. Jansman, A. G. R. Evans, and B. S. Rejaei, "C-V characterization of MOS capacitors on high resistivity silicon substrate," in *Proc. ESSDERC*, 2003, pp. 489–492.