# Symbolic Model Checking for Incomplete Designs With Flexible Modeling of Unknowns

**Tobias Nopper and Christoph Scholl**

**Abstract**—We consider the problem of checking whether an incomplete design (i.e., a design containing 'unknown parts', so-called Black Boxes) can still be extended to a complete design satisfying a given property or whether the property is satisfied for all possible extensions. There are many applications of property checking for incomplete designs, such as early verification checks for unfinished designs, error localization in faulty designs and the abstraction of complex parts of a design in order to simplify the property checking task.

To process incomplete designs we present an approximate, yet sound algorithm. The algorithm is flexible in the sense that for every Black Box a different approximation method can be chosen. This permits us to handle less relevant Black Boxes (in terms of the property) with larger approximation and thus faster, whereas we do not lose important information when the possible effect of more relevant Black Boxes is modeled by more exact methods.

Additionally, we present a concept to decide *exactly* whether Black Boxes with bounded memory can be implemented so that they satisfy a given property. This question is reduced to conventional symbolic model checking.

The effectiveness and feasibility of the methods is demonstrated by a series of experimental results.

Index Terms—Symbolic model checking, verification, Black Boxes, incomplete designs, abstraction, approximation, BDDs

## **1** INTRODUCTION

**D** ECIDING the question whether a circuit implementation fulfills its specification is an essential problem in computer-aided design of VLSI circuits. Growing interest in universities and industry has led to new results and significant advances concerning topics like property checking, state space traversal and combinational equivalence checking.

For proving properties of sequential designs, Clarke, Emerson, and Sistla presented model checking for the temporal logic CTL [3]. Burch et al. improved the technique by using symbolic methods based on binary decision diagrams [4] for both state set representation and state traversal in [5], [6].

In this paper we consider how to perform model checking of *incomplete* designs, i.e., designs which contain unknown parts, combined into so-called Black Boxes. In doing so, we address two interesting questions: The question whether it is still possible to replace the Black Boxes by circuit implementations, so that a given property is satisfied ('realizability') and the question whether the property is satisfied for any possible replacement ('validity').

- The authors are with the Department of Computer Science, University of Freiburg, 79110 Freiburg i. Br., Germany, (e-mail: {nopper,scholl}@informatik.uni-freiburg.de)

- Parts of the article have been presented at DAC 2001 [1] and FMCAD 2004 [2].

There are three major benefits symbolic model checking for incomplete designs can provide: First, instead of forcing verification runs to the end of the design process where the design is completed, it rather allows model checking in early stages of design, where parts may not yet be finished, so that errors can be detected earlier. Second, complex parts of a design can be replaced by Black Boxes, simplifying the design, while many properties of the design still can be proven, yet in shorter time. Third, the location of design errors in circuits not satisfying a model checking property can be narrowed down by iteratively masking potentially erroneous parts of the design.

In principle, the realizability problem could be solved *exactly* by synthesis approaches such as [7], [8]. Of course, a property for an incomplete design is realizable, if a complete design can be synthesized from the property and the parts of the design which are already known. However, due to complexity reasons, we are mainly interested in approximate solutions to the realizability and the validity problem. Whereas an exact solution to the realizability problem for incomplete designs with several Black Boxes (potentially containing an unrestricted amount of memory) is even undecidable in general [9], we use symbolic methods providing approximate answers: Our algorithm does not give a definite answer in every case, but it is guaranteed to be sound in the sense that it never gives an incorrect answer; it provides proofs of validity and disproofs of realizability for arbitrary CTL formulas (unlike approaches using 'non-deterministic signals' implemented in SMV [6] and VIS [10] which are only sound for certain subclasses of CTL).

Our method is based on symbolic representations of incomplete designs. Using these representations we provide different methods for approximating the sets of states satisfying a given property  $\varphi$ . One set is an over-approximation of the set of states satisfying the given CTL formula  $\varphi$  for at least one substitution of the Black Boxes and the second set is an under-approximation of the set of states satisfying the formula for all Black Box substitutions. Approximate yet sound answers for realizability and validity are computed based on these sets.

Our approach is able to use different methods for modeling unknowns at the outputs of different Black Boxes within a single model checking run. This permits us to handle less relevant Black Boxes (in terms of the CTL formula) with larger approximation and thus faster, whereas we do not lose important information when the possible effect of more relevant Black Boxes is modeled by more exact methods.

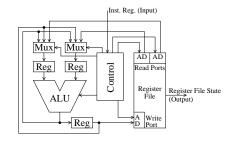

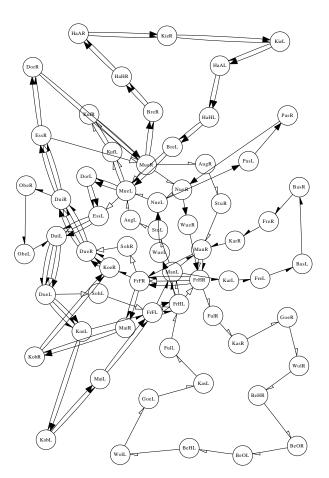

For an experimental evaluation we considered pipelined ALUs with varying bit widths. The results show that our approximate methods are able to provide proofs for large designs with bit widths up to 64, whereas standard model checking succeeded only for much smaller benchmarks. Moreover, the results show that the flexibility of choosing approximations with different accuracy for different Black Box outputs is essential for the success of our method. These observations were also confirmed by an additional case study from the railway domain.

Although the main focus of our paper lies on approximate solutions to the realizability and validity problems - in order to make our presentation more complete - we also present a concept how to provide an *exact* solution to a restricted problem by means of a conventional symbolic model checker: We assume an upper bound to the number of internal states of the Black Boxes and symbolically compute the exact set of Black Box replacements for which a property is satisfied, i.e., we give exact answers to both the realizability and the validity question. In contrast to controller synthesis approaches such as [7], [8], we do not assume that Black Boxes have unlimited access to all signals in the design, but we take into account that they are only able to read the input signals connected to them. In Sect. 7 we applied this concept to a design where we checked the realizability of an arbiter which was specified by CTL formulas.

Our approach shares ideas with 3-valued model checking introduced in the context of software model checking (e.g. [11]-[13]); it extends these ideas, improves and adapts them making use of characteristics of modular hardware designs and it provides an efficient implementation based on symbolic methods. Compared with methods from hardware verification such as Symbolic Trajectory Evaluation (STE) [14] or verification using Uninterpreted Functions (UIFs) [15], our method supports full CTL and allows Black Boxes for sequential designs. Our approach (in its aspect of abstraction by Black Boxes) is also related to localization reduction [16]. Bounded model checking approaches with localization reduction (e.g. [17], [18]) make use of efficient SAT solvers and are restricted to safety properties. If the property allows a non-trivial amount of abstraction of the full model, our BDD based symbolic method proves to be competitive for large designs (and even for saftey properties) due to property specific abstractions of different strengths. The method is based on user knowledge about the design and on user assumptions about the importance of certain parts of the design for the property at hand. Especially if the interfaces of some Black Boxes are wide (i.e. contain many signals), by our flexible modeling of unknowns we are not only able to abstract complex implementations of Black Boxes, but also to reduce the number of variables for interface signals (which is an additional source of complexity). A more detailed discussion of the relationship between our work and other approaches from the literature can be found in Sect. 8.

The paper is structured as follows: After giving a brief review of sequential designs and symbolic model checking in Sect. 2, we define incomplete designs and the set of their completions in Sect. 3. Sect. 4 introduces our method to perform symbolic simulation for incomplete designs and in Sect. 5, we present a new algorithm capable of performing sound and approximate symbolic model checking for incomplete designs. In Sect. 6, we introduce a concept for an exact algorithm to process incomplete designs in which a fixed upper bound on the number of internal states is assumed for each Black Box. We give a series of experimental results demonstrating the effectiveness and feasibility of the methods in Sect. 7. Finally, Sect. 8 provides a detailed discussion of related work and Sect. 9 concludes the paper.

## 2 PRELIMINARIES

Before we introduce symbolic model checking for incomplete designs we give a brief review of symbolic model checking for complete designs [5]. Symbolic model checking is applied to Kripke structures (which may be derived from sequential designs) on the one hand and to a formula of a temporal logic (in our case CTL ('Computation Tree Logic')) on the other hand.

## 2.1 Sequential Designs and Kripke Structures

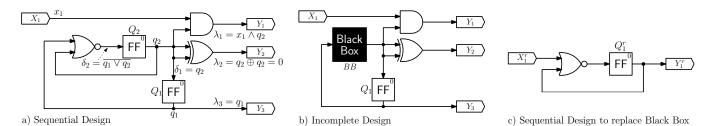

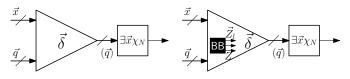

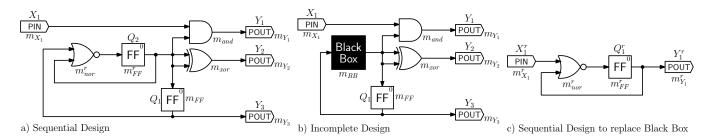

(Complete) sequential designs consist of nodes which are connected by signals.<sup>1</sup> The nodes represent primary inputs, primary outputs, memory elements (flip-flops) storing single bits, or logic gates implementing Boolean functions. In following we denote the list of primary input nodes by  $\vec{X} = (X_1, X_2, \dots, X_{|\vec{X}|})$ , the list of primary output nodes by  $\vec{Y} = (Y_1, Y_2, \dots, Y_{|\vec{Y}|})$ , and the list of flip-flops by  $\vec{Q} = (Q_1, Q_2, \dots, Q_{|\vec{Q}|})$ .  $\vec{q}^0 \in \mathbb{B}^{|\vec{Q}|}$  gives the initial values (initial state) of the flip-flops. Fig. 1 a) shows an example for a sequential design with one primary input, three primary outputs, two flip-flops initialized to 0, and three gates implementing Boolean functions nor<sub>2</sub>, and<sub>2</sub>, xor<sub>2</sub>, respectively.

Each output of a node in the sequential design computes a Boolean function  $f: \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|} \to \mathbb{B}$ . Each primary input  $X_j$  computes a Boolean function  $x_i$  (which – strictly speaking – is the projection function mapping  $(x_1, \ldots, x_{|\vec{X}|}, q_1, \ldots, q_{|\vec{Q}|}) \in \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|}$  to  $x_j$ ) and each flip-flop  $Q_k$  computes  $q_k$ . The output functions of the logic gates are computed recursively according to their gate function. In Fig. 1 a) the corresponding Boolean functions of the nodes are shown as Boolean expressions.

In symbolic model checking, BDD based representations of these Boolean functions are computed by symbolic simulation [19]. For this, the primary inputs and the outputs of the flip-flops are associated with unique BDD variables and BDDs for the functions computed by the gates of the design are built in topological order using BDD operations.

The input functions  $\delta_i$  of the flip-flops  $Q_i$  compute the next state of the flip flops and the functions  $\lambda_j$  corresponding to the primary outputs compute the current output values (based on the current state and the current input). Altogether a sequential design defines a transition function  $\vec{\delta} : \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|} \to \mathbb{B}^{|\vec{Q}|}$  and an output function  $\vec{\lambda} \colon \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|} \to \mathbb{B}^{|\vec{Y}|}$ . Again, see Fig. 1 a) for an example.

Now we can define the Kripke structure of a complete design D. The states of the Kripke structure are defined as a combination of states and inputs of D. The transition relation R of the Kripke structure connects states according to the transition function  $\delta$  of D. The labeling function L labels states with the information which inputs (represented by atomic propositions  $x_i$ ) and outputs (represented by atomic propositions  $y_i$ ) are 1 in these states.

**Definition 1** (Kripke Structure of a Complete Design). Let *D* be a sequential design with transition function  $\vec{\delta} \colon \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|} \to \mathbb{B}^{|\vec{Q}|}$ , output function  $\vec{\lambda} \colon \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|} \to \mathbb{B}^{|\vec{Y}|}$ , and initial state  $\vec{q}^0$ . A Kripke structure for D is struct(D) := (S, R, L) where

- $S := \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|}, R \subseteq S \times S, L: S \to V,$

- $\begin{array}{l} \bullet & V := \{x_1, \dots, x_{|\vec{X}|}\} \cup \{y_1, \dots, y_{|\vec{Y}|}\}, \\ \bullet & R := \left\{ \left( (\vec{q}, \vec{x}), (\vec{q}', \vec{x}') \right) \mid \vec{q}, \vec{q}' \in \mathbb{B}^{|\vec{Q}|}, \vec{x}, \vec{x}' \in \mathbb{B}^{|\vec{X}|}, \vec{\delta}(\vec{q}, \vec{x}) = \vec{q}' \right\}, \\ \bullet & and \; L((\vec{q}, \vec{\epsilon})) := \left\{ x_i \mid \epsilon_i = 1 \right\} \cup \left\{ y_i \mid \lambda_i(\vec{q}, \vec{\epsilon}) = 1 \right\}. \end{array}$

All states  $(\vec{q}^{0}, \vec{x})$  with  $\vec{x} \in \mathbb{B}^{|\vec{X}|}$  are called initial states of struct(D).

#### 2.2 Symbolic Model Checking for Complete Designs

Model checking decides whether a given design fulfills its specification given as a formula of a temporal logic. In this paper we consider the widespread branching time logic CTL (Computation Tree Logic) [3], [6]. CTL formulas specify properties of states of Kripke structures. The semantics of CTL formulas can be defined recursively based on their structure:

**Definition 2** (Semantics of CTL). As usual we write struct(D),  $s \models$  $\varphi$  if the CTL formula  $\varphi$  is satisfied in state  $s = (\vec{q}, \vec{x}) \in S$  of struct(D). If it is clear from the context which Kripke structure is

1. For a formal definition see Appendix A.

Fig. 1. Complete and incomplete sequential designs

used, we simply write  $s \models \varphi$  instead of  $struct(D), s \models \varphi$ . " $\models$ " is defined as follows:

$$\begin{split} s &\models \varphi; \ \varphi \in V \iff \varphi \in L(s) \\ s &\models \neg \varphi \iff s \not\models \varphi \\ s &\models (\varphi_1 \lor \varphi_2) \iff s \models \varphi_1 \text{ or } s \models \varphi_2 \\ s &\models EX\varphi \iff \exists s' \in S \colon R(s,s') \text{ and } s' \models \varphi \\ s &\models EG\varphi \iff \text{there is a path } (s_0, s_1, s_2, \ldots) \text{ with} \\ s &= s_0 \text{ and } \forall i \ge 0 \colon (s_i, s_{i+1}) \in R \text{ and } s_i \models \varphi \\ s &\models E\varphi_1 U\varphi_2 \iff \text{there is a path } (s_0, s_1, s_2, \ldots) \text{ with} \\ s &= s_0 \text{ and } \forall i \ge 0 \colon (s_i, s_{i+1}) \in R \text{ and there is} \\ j \text{ so that } s_j \models \varphi_2 \text{ and } \forall 0 \le i < j \colon s_i \models \varphi_1 \end{split}$$

The remaining CTL operations  $\land$ , *EF*, *AX*, *AU*, *AG*, and *AF* can be expressed by using  $\neg$ ,  $\lor$ , *EX*, *EU*, and *EG* [6].

In *symbolic* model checking, sets of states are represented by characteristic functions (which are in turn represented by BDDs). Before we define symbolic model checking, we need the following three definitions:

**Definition 3** (Cofactor). For a Boolean function  $f : \mathbb{B}^n \to \mathbb{B}$  the cofactor (or partial evaluation) wrt.  $\vec{y} = \vec{\epsilon} \ (\vec{\epsilon} \in \mathbb{B}^{|\vec{y}|})$  is defined as the Boolean function  $f|_{\vec{y}=\vec{\epsilon}} : \mathbb{B}^n \to \mathbb{B}$  with  $f|_{\vec{y}=\vec{\epsilon}}(\vec{x}, \vec{y}, \vec{z}) = f(\vec{x}, \vec{\epsilon}, \vec{z})$  for all  $(\vec{x}, \vec{y}, \vec{z}) \in \mathbb{B}^n$ .

**Definition 4.** Let  $f : \mathbb{B}^n \to \mathbb{B}$  be a Boolean function.  $\exists \vec{y} f$  is defined as the Boolean function  $\bigvee_{\vec{e} \in \mathbb{B}^{|\vec{y}|}} f|_{\vec{y}=\vec{e}}, \forall \vec{y} f$  as  $\bigwedge_{\vec{e} \in \mathbb{B}^{|\vec{y}|}} f|_{\vec{y}=\vec{e}}$ .

**Definition 5** (Compose). Let  $f,g : \mathbb{B}^n \to \mathbb{B}$  be Boolean functions. The composition of  $x_i$  by g in f is defined as the Boolean function  $f|_{x_i \leftarrow g} : \mathbb{B}^n \to \mathbb{B}$  with  $f|_{x_i \leftarrow g}(x_1, \ldots, x_i, \ldots, x_n) := f(x_1, \ldots, g(x_1, \ldots, x_n), \ldots, x_n) = (\overline{g} \cdot f|_{x_i=0} + g \cdot f|_{x_i=1})(x_1, \ldots, x_n)$  for all  $(x_1, \ldots, x_n) \in \mathbb{B}^n$ .

Composition (see e.g. [4]) can be naturally generalized to vectors of variables and functions. In the definition of symbolic model checking only the special case of renaming variables is needed.

Let  $Sat(\varphi)$  be the set of states of struct(D) which satisfy formula  $\varphi$  and let  $\chi_{Sat(\varphi)}$  be its characteristic function, then  $\chi_{Sat(\varphi)}$ can be computed recursively based on the characteristic function  $\chi_R(\vec{q}, \vec{x}, \vec{q}') := \prod_{i=1}^{|\vec{q}|} (\delta_i(\vec{q}, \vec{x}) \equiv q'_i)$  of the transition relation R:

$$\begin{split} \chi_{Sat(x_i)}(\vec{q}, \vec{x}) &:= x_i \\ \chi_{Sat(y_i)}(\vec{q}, \vec{x}) &:= \lambda_i(\vec{q}, \vec{x}) \\ \chi_{Sat(\neg\varphi)}(\vec{q}, \vec{x}) &:= \overline{\chi_{Sat(\varphi)}}(\vec{q}, \vec{x}) \\ \chi_{Sat((\neg\varphi)}(\vec{q}, \vec{x})) &:= \chi_{Sat(\varphi_1)}(\vec{q}, \vec{x}) \lor \chi_{Sat(\varphi_2)}(\vec{q}, \vec{x}) \\ \chi_{Sat(EX\varphi)}(\vec{q}, \vec{x}) &:= \chi_{EX}(\chi_{Sat(\varphi)})(\vec{q}, \vec{x}) \\ \chi_{Sat(EG\varphi)}(\vec{q}, \vec{x}) &:= \chi_{EG}(\chi_{Sat(\varphi)})(\vec{q}, \vec{x}) \\ \chi_{Sat(E\varphi_1U\varphi_2)}(\vec{q}, \vec{x}) &:= \chi_{EU}(\chi_{Sat(\varphi_1)}, \chi_{Sat(\varphi_2)})(\vec{q}, \vec{x}) \\ \chi_{Sat(E\chi\chi)}(\vec{q}, \vec{x}) &:= \exists \vec{q}' \exists \vec{x}' \Big( \chi_R(\vec{q}, \vec{x}, \vec{q}') \cdot \big( \chi_N | \vec{q} \leftarrow \vec{q}' \big) (\vec{q}', \vec{x}') \Big) \end{split}$$

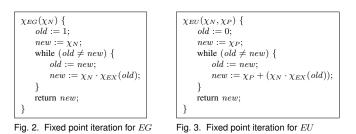

$\chi_{EG}$  and  $\chi_{EU}$  can be evaluated by the fixed point iteration algorithms shown in Figs. 2 and 3.

A complete sequential design satisfies a formula  $\varphi$  iff  $\varphi$  is satisfied in all initial states of the corresponding Kripke structure struct(D):

$$D \models \varphi :\iff \forall \vec{x} \in \mathbb{B}^{|X|} \ struct(D), (\vec{q}^0, \vec{x}) \models \varphi$$

$$\iff \forall \vec{x} \left( \left( \chi_{Sat(\varphi)}(\vec{q}, \vec{x}) \right) |_{\vec{q} = \vec{q}^0} \right) = 1$$

## **3** INCOMPLETE DESIGNS

*Incomplete* sequential designs may contain additional "Black Box" (BB) nodes which represent parts of the design with unknown (sequential) behavior, see Fig. 1 b) for an example with one input, three outputs, one flip-flop, two gates implementing the Boolean  $and_2$  resp. the Boolean  $xor_2$  function and one Black Box.

A Black Box BB in an incomplete design D can be replaced by any sequential design  $D^r$  (without Black Boxes and with an arbitrary number of flip-flops), as long as  $D^r$  has the same number of inputs and outputs as the Black Box. The inputs and outputs of  $D^r$  are then connected to the inputs and outputs of the former Black Box BBin D; the result of this substitution is another (possibly incomplete) sequential design  $D^c$ . E.g. the sequential design in Fig. 1 a) results from the incomplete design in Fig. 1 b) by replacing the Black Box with the sequential design in Fig. 1 c).<sup>2</sup>

If the incomplete design D resulted from a complete design by abstractions replacing subcircuits by Black Boxes, then replacing Black Boxes again by their concrete counterparts corresponds to the well-known notion of *abstraction refinement* [16].

**Definition 6** (Completion of an Incomplete Design). A sequential design  $D^c$  that was constructed from an incomplete design D by replacing all Black Boxes by sequential designs is called a completion of D. C(D) is the set of all possible completions of D.

The two main questions we address in this paper are the realizability and the validity question:

**Definition 7** (Realizability and Validity). *Given an incomplete design* D and a CTL formula  $\varphi$ :

- 1) If there is a completion  $D^c \in C(D)$  of D which satisfies  $\varphi$ , then the property  $\varphi$  is called realizable for D.

- 2) If all possible completions  $D^c \in C(D)$  of D satisfy  $\varphi$ , then the property  $\varphi$  is called valid for D.

2. For formal definitions see Appendix A.

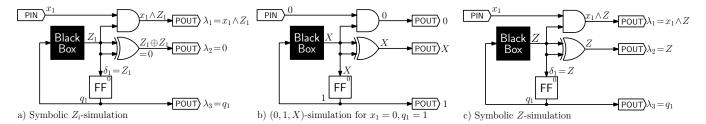

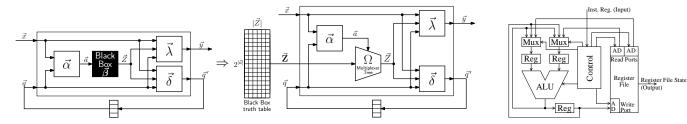

Fig. 4. Different methods to analyze an incomplete design

#### 4 SYMBOLIC SIMULATION FOR INCOMPLETE DESIGNS

For symbolic CTL model checking of complete designs, symbolic representations of the output functions  $\vec{\lambda}$  and the transition functions  $\vec{\delta}$  are needed first. Of course, we cannot compute  $\vec{\lambda}$  and  $\vec{\delta}$  for *incomplete* designs due to the unknown Black Boxes. However, in order to define an approximate model checking method for *incomplete* designs in Sect. 5, we compute 'approximate representations' of output functions  $\vec{\lambda}$  and transition functions  $\vec{\delta}$  which contain information on the potential effect of the Black Boxes.

### Symbolic $Z_i$ -simulation

For that purpose we first consider symbolic  $Z_i$ -simulation which replaces the Black Box outputs by free input variables and in that way evaluates the effect that Black Box outputs have on  $\vec{\lambda}$  and  $\vec{\delta}$ . Apart from handling the Black Box outputs as additional inputs, symbolic  $Z_i$ -simulation works exactly as conventional symbolic simulation [19]. (Replacing signals by free variables is not a new idea, but has been used for a long time, e.g. for localization abstraction [16].)

**Definition 8** (Symbolic  $Z_i$ -Simulation). Let D be an incomplete design over the library  $STD = \{and_2, or_2, not\}$ .<sup>3</sup> Let zvar be a function mapping distinct Boolean variables  $Z_i$  to the outputs of the Black Boxes. Moreover, we use Boolean variables  $x_1, \ldots, x_{|\vec{X}|}$  for the primary inputs and Boolean variables  $q_1, \ldots, q_{|\vec{Q}|}$  for the flip-flop outputs. The Boolean function  $f_{Z_i}(m, j)$  for the j-th output of a node m is defined as follows:

- (1) If m is a primary input  $X_i$ , then  $f_{Z_i}(m, 1) = x_i$ .

- (2) If m is a flip-flop  $Q_k$ , then  $f_{Z_i}(m, 1) = q_k$ .

- (3) If m is a Black Box, then  $f_{Z_i}(m, j) = zvar(m, j)$ .

- (4) If m is a not-gate whose predecessor is output k of node p, then  $f_{Z_i}(m, 1) = \overline{f_{Z_i}(p, k)}.$

- (5) If m is an and<sub>2</sub>-gate (or<sub>2</sub>-gate) whose predecessors are output  $k_1$  of  $p_1$  and output  $k_2$  of  $p_2$ , then  $f_{Z_i}(m, 1) = f_{Z_i}(p_1, k_1) \wedge f_{Z_i}(p_2, k_2)$ ( $f_{Z_i}(p_1, k_1) \vee f_{Z_i}(p_2, k_2)$ ).

Fig. 4 a) shows an example for symbolic  $Z_i$ -simulation of the incomplete design from Fig. 1 b).

The following lemma shows how the result of symbolic  $Z_i$ -simulation can be interpreted regarding the Black Boxes:

**Lemma 1.** Let D be an incomplete design and let  $D^c \in C(D)$ be an arbitrary completion of D. For the j-th output of gate m in D let  $f_{Z_i}(m, j)$  be the Boolean function over variables  $(\vec{q}, \vec{x}, \vec{Z})$ computed by symbolic  $Z_i$ -simulation of D. Furthermore, let f(m, j)be the Boolean function over variables  $((\vec{q}, \vec{q}^r), \vec{x})$  computed by (conventional) symbolic simulation of  $D^c$   $(\vec{q}^r$  are variables introduced by substitutions of Black Boxes by sequential designs). Then the following holds for constants  $\alpha \in \mathbb{B}$  and  $\vec{\beta} \in \mathbb{B}^{|\vec{q}|}, \vec{\gamma} \in \mathbb{B}^{|\vec{x}|}$ :

$$f_{Z_i}(m,j)|_{\substack{\vec{q}=\vec{\beta}\\\vec{x}=\vec{\gamma}}} = \alpha \Rightarrow f(m,j)|_{\substack{\vec{q}=\vec{\beta}\\\vec{x}=\vec{\gamma}}} = \alpha$$

Proof:

The proof simply follows from the fact that  $f_{Z_i}(m,j)|_{\vec{q}=\vec{\beta}\atop \vec{q}=\vec{\alpha}} = \alpha \in \mathbb{B}$

3. W.l.o.g. we restrict the library in the following to STD, since all types of gates can be expressed using 2-input  $and_2$  gates,  $or_2$  gates and not gates.

implies that  $f_{Z_i}(m,j)|_{\substack{\overline{q}=\overline{\beta}\\\overline{x}=\overline{\gamma}}}$  does not depend on the outputs of the Black Boxes. Therefore  $f(m,j)|_{\substack{\overline{q}=\beta\\\overline{x}=\overline{\gamma}}} = \alpha$  for an arbitrary substitution of the Black Boxes by sequential designs.

## Symbolic Z-simulation

For analyzing combinational circuits with Black Boxes in [1] we introduced symbolic Z-simulation. Compared to symbolic  $Z_i$ -simulation, this method is usually less expensive in terms of run time and memory consumption, but it is also less accurate as measured by the amount of information which can be extracted from the results.

Symbolic Z-simulation is motivated by the well-known (0, 1, X)simulation [14], [20], [21]. The value X represents unknown values which come from the unknown functionality of the Black Boxes in our context. If some input values of a gate are set to X during (0, 1, X)-simulation, the output value is equal to X if and only if there are two different replacements of the X values at the inputs by 0's and 1's, which lead to different outputs of the gate. Fig. 4 b) shows a (conventional) (0, 1, X)-simulation for the incomplete design shown in Fig. 1 b) (with the input set to 0 and the flip-flop state set to 1).

For symbolic Z-simulation, the symbolic version of (0, 1, X)simulation, a new variable Z is introduced, which is used to model unknown values at the outputs of Black Boxes. Now, for each output of a node in the incomplete design, the output function is obtained by using a slightly modified version of symbolic simulation:

**Definition 9** (Symbolic Z-Simulation). Let D be an incomplete design over  $STD = \{and_2, or_2, not\}$ . Let Z be a new variable different from  $x_1, \ldots, x_{|\vec{X}|}, q_1, \ldots, q_{|\vec{Q}|}$ . The Boolean function  $f_Z(m, j)$  for the j-th output of a node m is defined as in Def. 8 with (3) and (4) replaced by

- (3') If m is a Black Box, then  $f_Z(m, j) = Z$ .

- (4') If m is a not-gate whose predecessor is output k of node p, then  $f_Z(m, 1) = \overline{f_Z(p, k)}|_{Z \leftarrow \overline{Z}}$ .

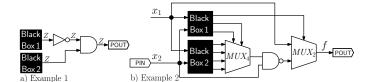

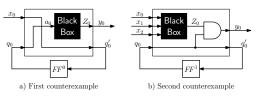

The main difference to conventional symbolic simulation is the evaluation of *not*-gates: The *not* operation on the function for the predecessor gate is followed by a *compose* operation (see Def. 5) which composes  $\overline{Z}$  for Z (written as  $\overline{f_Z(p,k)}|_{Z\leftarrow\overline{Z}}$ ). Fig. 5 (a) shows a first example of Z-simulation for a design with two Black Boxes. If the compose operation after processing the *not*-gate would be omitted, then its output would compute  $\overline{Z}$ , leading to the result 0 at the output of the *and*<sub>2</sub>-gate, i.e. we would then lose the information that the output value is always unknown (modeled by Z) due to the Black Boxes.

Symbolic Z-simulation has the following property:

**Lemma 2.** Given an incomplete design D and a Boolean function  $f_Z(m, j)$  computed by symbolic Z-simulation for the j-th output of node m. For all  $\vec{\beta} \in \mathbb{B}^{|\vec{q}|}$ ,  $\vec{\gamma} \in \mathbb{B}^{|\vec{x}|}$ :  $f_Z(m, j)|_{\substack{\vec{q}=\vec{\beta}\\ \vec{x}=\vec{\gamma}}} \in \{0, 1, Z\}$ .

The lemma can be proved by induction on the structure of D. The proof is given in Appendix B. If  $f_Z(m,j)|_{\vec{x}=\vec{\gamma}} = Z$ , then the function value for input  $(\vec{\beta},\vec{\gamma})$  is unknown due to the Black Boxes.

Fig. 5. Two incomplete designs

Fig. 4 c) shows another example of symbolic Z-simulation. Note that — in contrast to symbolic  $Z_i$ -simulation in Fig. 4 a) — the second output cannot be proved to be constant 0. Since Z-simulation cannot distinguish between unknown values at different Black Box outputs, some information is lost. According to the following lemma,  $Z_i$ -simulation is always at least as accurate as Z-simulation:

**Lemma 3.** Let D be an incomplete design,  $f_Z(m, j)$  the function computed by symbolic Z-simulation for the j-th output of m and  $f_{Z_i}(m, j)$  the corresponding function computed by symbolic  $Z_i$ simulation. Then the following holds for constants  $\alpha \in \mathbb{B}$  and  $\vec{\beta} \in \mathbb{B}^{|\vec{\alpha}|}, \vec{\gamma} \in \mathbb{B}^{|\vec{\alpha}|}$ : If  $f_Z(m, j)|_{\vec{x}=\vec{\gamma}}^{\vec{\alpha}=\beta} = \alpha$ , then  $f_{Z_i}(m, j)|_{\vec{x}=\vec{\gamma}}^{\vec{\alpha}=\beta} = \alpha$ .

Again, the lemma is proved by induction on the structure of D; the proof can be found in Appendix C.

#### Symbolic $Z/Z_i$ -simulation

Finally, we provide a mixed (symbolic)  $Z/Z_i$ -simulation in order to give the user more flexibility in controlling the trade-off between higher efficiency of Z-simulation and higher accuracy of  $Z_i$ simulation. Here, some Black Box outputs are represented by variable Z as in symbolic Z-simulation and some Black Box outputs by distinct variables  $Z_i$  as in symbolic  $Z_i$ -simulation. Basically, symbolic  $Z/Z_i$ -simulation considers the  $Z_i$ -modeled Black Box outputs as additional inputs and then performs symbolic Z-simulation (always replacing Z by  $\overline{Z}$  when processing not gates):

**Definition 10** (Symbolic  $Z/Z_i$ -Simulation). Let D be an incomplete design over STD. Let  $\vec{Z}_l = (Z_1, \ldots, Z_n)$  be a vector of new variables and Z be a new variable, all different from  $x_1, \ldots, x_{|\vec{X}|}, q_1, \ldots, q_{|\vec{Q}|}$ . Let zvar be a function mapping distinct Boolean variables  $Z_i$  or the variable Z to the outputs of the Black Boxes. The Boolean function  $f_{Z/Z_i}(m, j)$  for the *j*-th output of a node m is defined as in Def. 8 with (4) replaced by

(4") If m is a not-gate whose predecessor is output k of node p, then  $f_{Z/Z_i}(m, 1) = \overline{f_{Z/Z_i}(p, k)}|_{Z \leftarrow \overline{Z}}$ .

*Example.* Figure 5 (b) shows an example comparing Z-,  $Z_i$ - and combined  $Z/Z_i$ -simulation. If this design is simulated by using symbolic Z-simulation (meaning that Z is assigned to the outputs of both Black Box 1 and Black Box 2), a total number of 3 variables are needed  $(x_1, x_2, Z)$  and the resulting function for the output is  $f_Z = Z$ .

If the design is simulated by using symbolic  $Z_i$ -simulation instead (meaning that for each output of Black Box 1 and Black Box 2 a new  $Z_i$  variable is used), 9 variables are needed  $(x_1, x_2, Z_1, \ldots, Z_7)$ , and the function for the output is  $f_{Z_i} = \overline{Z}_1 x_1 + Z_1 \cdot (\overline{x}_2 + \neg (\overline{Z}_2 \overline{Z}_3 Z_4 + Z_2 \overline{Z}_3 Z_5 + \overline{Z}_2 Z_3 Z_6 + Z_2 Z_3 Z_7))$  (when variables  $Z_1, \ldots, Z_7$  are assigned top down to the Black Box outputs appearing in Fig. 5 (b).

When using symbolic  $Z/Z_i$ -simulation for modeling Black Box outputs, assigning Z to all outputs of Black Box 2, but different  $Z_i$ 's to the outputs of Black Box 1, e.g., we end up using 6 variables  $(x_1, x_2, Z, Z_1, Z_2, Z_3)$  and obtain the function  $f_{Z/Z_i} = \overline{Z}_1 x_1 + Z_1 \cdot (\overline{x}_2 + Z)$ .

Thus,  $Z/Z_i$ -simulation generates an output function that is obviously less complicated than the result of symbolic  $Z_i$ -simulation, yet contains more information than the result of symbolic Z-simulation.

To give an example, for  $x_1 = 1$  and  $x_2 = 0$ , the output can be proven to be 1 using  $Z/Z_i$ -simulation, while it is not possible to obtain this information from symbolic Z-simulation.

In general,  $Z/Z_i$ -simulation is at most as exact as symbolic  $Z_i$ simulation, but at least as exact as symbolic Z-simulation. Moreover, if for a node function in an incomplete design computed by Z-,  $Z/Z_i$ or  $Z_i$ -simulation a cofactor wrt. input and state variables is constant, then the cofactor of the corresponding node function always evaluates to the same constant, no matter how the Black Boxes are replaced by sequential designs. This is summarized by the following theorem:

**Theorem 4.** Let D be an incomplete design, let  $D^c \in C(D)$  be an arbitrary completion of D, let  $f_Z(m, j)$ ,  $f_{Z_i}(m, j)$ ,  $f_{Z/Z_i}(m, j)$  be the functions computed for the *j*-th output of node m in D by symbolic Z-simulation,  $Z_i$ -simulation, and  $Z/Z_i$ -simulation, respectively, and let f(m, j) be the function computed for the *j*-th output of node m in  $D^c$  by symbolic simulation. For constants  $\alpha \in \mathbb{B}$  and for all  $\vec{\beta} \in \mathbb{B}^{|\vec{\alpha}|}$ ,  $\vec{\gamma} \in \mathbb{B}^{|\vec{x}|}$ :

$$\begin{aligned} f_Z(m,j)|_{\substack{\vec{q}=\vec{\beta}\\\vec{x}=\vec{\gamma}}} &= \alpha \quad \stackrel{(1)}{\Rightarrow} \quad f_{Z/Z_i}(m,j)|_{\substack{\vec{q}=\vec{\beta}\\\vec{x}=\vec{\gamma}}} &= \alpha \\ \stackrel{(2)}{\Rightarrow} \quad f_{Z_i}(m,j)|_{\substack{\vec{q}=\vec{\beta}\\\vec{x}=\vec{\gamma}}} &= \alpha \quad \stackrel{(3)}{\Rightarrow} \quad f(m,j)|_{\substack{\vec{q}=\vec{\beta}\\\vec{x}=\vec{\gamma}}} &= \alpha \end{aligned}$$

Proof: Implication (1) is proved by induction on the structure of D exactly as in the proof of Lemma 3 (simply replace  $f_{Z_i}$  by  $f_{Z/Z_i}$  in the proof). Implication (2) follows from Lemma 3: Let  $\vec{Z}_l$  be the vector of  $Z_i$ -variables also used in  $Z/Z_i$ -simulation. Since  $f_{Z/Z_i}(m,j)|_{\substack{\vec{a}=\vec{\beta}\\ \vec{a}=\vec{\gamma}}} = \alpha$ , also  $f_{Z/Z_i}(m,j)|_{\substack{\vec{a}=\vec{\beta}\\ \vec{a}=\vec{\gamma}}} = \alpha$  for all  $\vec{\epsilon} \in \mathbb{B}^{|\vec{Z}_l|}$ . Considering the  $\vec{Z}_l$ -variables as primary inputs for the time being, we can apply Lemma 3 and have  $f_{Z_i}(m,j)|_{\substack{\vec{a}=\vec{\beta}\\ \vec{Z}_l=\vec{\epsilon}}} = \alpha$  for all  $\vec{\epsilon} \in \mathbb{B}^{|\vec{Z}_l|}$ . This implies  $f_{Z_i}(m,j)|_{\substack{\vec{a}=\vec{\beta}\\ \vec{x}=\vec{\gamma}}} = \alpha$ . Implication (3) directly follows from Lemma 1.

## 5 SYMBOLIC MODEL CHECKING FOR INCOMPLETE DE-SIGNS

#### 5.1 Basic Principle

Symbolic model checking for *complete* designs computes the set  $Sat(\varphi)$  of all states satisfying a CTL formula  $\varphi$  and then checks whether all initial states are included in this set. If so, the design satisfies  $\varphi$ . The situation becomes more complex if we consider incomplete designs, since for each replacement of the Black Boxes we may have different state sets satisfying  $\varphi$ .

In contrast to conventional model checking we do not compute the set  $Sat(\varphi)$ , but we consider two sets  $Sat_E^{\text{exact}}(\varphi)$  and  $Sat_A^{\text{exact}}(\varphi)$ : The set  $Sat_E^{\text{exact}}(\varphi)$  is defined to contain all states, for which *there* is at least one completion so that  $\varphi$  is satisfied. In a similar manner,  $Sat_A^{\text{exact}}(\varphi)$  contains all states, for which  $\varphi$  is satisfied for *all* possible completions.

**Definition 11.** Let D be an incomplete design and C(D) be the set of completions of D.

$$\begin{split} &Sat_{E}^{\text{exact}}(\varphi) := \left\{ (\vec{q}, \vec{x}) \in \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|} \mid \\ & \exists D^{c} \in \mathcal{C}(D), \, \exists \vec{q}^{\, r} \in \mathbb{B}^{|\vec{Q}^{\, c}| - |\vec{Q}|} : struct(D^{c}), ((\vec{q}, \vec{q}^{\, r}), \vec{x}) \models \varphi \right\} \\ & Sat_{A}^{\text{exact}}(\varphi) := \left\{ (\vec{q}, \vec{x}) \in \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|} \mid \\ & \forall D^{c} \in \mathcal{C}(D), \, \forall \vec{q}^{\, r} \in \mathbb{B}^{|\vec{Q}^{\, c}| - |\vec{Q}|} : struct(D^{c}), ((\vec{q}, \vec{q}^{\, r}), \vec{x}) \models \varphi \right\} \end{split}$$

$(|\vec{Q}^c| - |\vec{Q}| \text{ is the number of flip-flops in } D^c \text{ added to } D \text{ by Black}$ Box replacements.) We say that states  $(\vec{q}, \vec{x}) \in Sat_E^{exact}(\varphi)$  'possibly satisfy  $\varphi$ ' and that states  $(\vec{q}, \vec{x}) \in Sat_E^{exact}(\varphi)$  'definitely satisfy  $\varphi$ '.

Of course, Def. 11 does not suggest a feasible algorithm for computing  $Sat_E^{exact}(\varphi)$  and  $Sat_A^{exact}(\varphi)$ , since the set of all possible completions for an incomplete design is not finite. (This motivates our approach to compute approximations of  $Sat_E^{exact}(\varphi)$  and  $Sat_A^{exact}(\varphi)$

in Sect. 5.2.) Nevertheless, given  $Sat_E^{\text{exact}}(\varphi)$  and  $Sat_A^{\text{exact}}(\varphi)$ , it is easy to prove validity and to falsify realizability for the incomplete design:

**Lemma 5.** A property  $\varphi$  is valid for an incomplete design D with initial state  $\vec{q}^0$ , if all states  $(\vec{q}^0, \vec{x})$  with  $\vec{x} \in \mathbb{B}^{|\vec{X}|}$  are included in  $Sat_A^{exact}(\varphi)$ . A property  $\varphi$  is not realizable for D, if there is at least one such state  $(\vec{q}^0, \vec{x})$  not belonging to  $Sat_E^{exact}(\varphi)$ .

Proof: Let  $D^c \in \mathcal{C}(D)$  be an arbitrary completion of D and let  $\vec{q}^{0r}$  be the initial states of the flip-flops introduced by the replacements of the Black Boxes. If  $\forall \vec{x} \in \mathbb{B}^{|\vec{X}|} : (\vec{q}^0, \vec{x}) \in Sat_A^{\text{exact}}(\varphi)$ , then  $\forall \vec{x} \in \mathbb{B}^{|\vec{X}|} : struct(D^c), ((\vec{q}^0, \vec{q}^{0r}), \vec{x}) \models \varphi$  (by Def. 11). This means that  $D^c$  satisfies  $\varphi$ .  $\varphi$  is valid, since we assumed  $D^c$  to be an arbitrary completion. If  $(\vec{q}^0, \vec{x}) \notin Sat_E^{\text{exact}}(\varphi)$ , then for all completions  $D^c \in \mathcal{C}(D)$  with initial states  $\vec{q}^{0r}$  of the additional flip-flops  $\varphi$  is not satisfied in the initial state  $((\vec{q}^0, \vec{q}^{0r}), \vec{x})$  of  $struct(D^c)$ . Thus,  $\varphi$  is not realizable for D.

Just as Black Boxes in incomplete designs lead to states only *possibly* satisfying  $\varphi$ , there are also '*possible transitions*' between states in an incomplete design which may or may not exist in a completion of the design — depending on the replacement of the Black Boxes:

**Definition 12.** Let D be an incomplete design and let C(D) be the set of completions of D. We define the incomplete design to have a possible transition between states  $(\vec{q}, \vec{x}), (\vec{q}', \vec{x}') \in \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|}$ , if there is a completion  $D^c \in C(D)$  for which there is a transition between  $((\vec{q}, \vec{q}^r), \vec{x})$  and  $(\vec{q}', \vec{q}'^r), \vec{x}')$  for some values  $\vec{q}^r, \vec{q}'^r \in \mathbb{B}^{|\vec{Q}^c| - |\vec{Q}|}$ .  $(|\vec{Q}^c| - |\vec{Q}| \text{ is the number of flip-flops in } D^c \text{ added to } D$  by Black Box replacements.)

Possible transitions are used later on in order to *compute* states that possibly or definitely satisfy a property  $\varphi$ .

#### 5.2 Approximations

As mentioned above, for reasons of efficiency we compute approximations  $Sat_E^{appr}(\varphi)$  and  $Sat_A^{appr}(\varphi)$  for  $Sat_E^{exact}(\varphi)$  and  $Sat_A^{exact}(\varphi)$ , respectively – and similarly for the set of possible transitions. To be more precise, we compute over-approximations  $Sat_E^{appr}(\varphi) \supseteq$  $Sat_E^{exact}(\varphi)$  of  $Sat_E^{exact}(\varphi)$  and under-approximations  $Sat_A^{appr}(\varphi) \subseteq$  $Sat_A^{exact}(\varphi)$  of  $Sat_A^{exact}(\varphi)$ .

Then Lemma 5 directly implies the following lemma:

**Lemma 6.** Let  $Sat_{E}^{\text{appr}}(\varphi) \supseteq Sat_{E}^{\text{exact}}(\varphi)$  and  $Sat_{A}^{\text{appr}}(\varphi) \subseteq Sat_{E}^{\text{exact}}(\varphi)$ . If all initial states  $(\vec{q}^{0}, \vec{x})$  are included in  $Sat_{A}^{\text{appr}}(\varphi)$ , then  $\varphi$  is valid. If there is an initial state  $(\vec{q}^{0}, \vec{x})$  that is not included in  $Sat_{E}^{\text{appr}}(\varphi)$ , then  $\varphi$  is not realizable.

Approximations  $Sat_E^{appr}(\varphi)$  and  $Sat_A^{appr}(\varphi)$  are computed based on an approximate transition relation and on approximate output functions for the incomplete design D.

To take account of the unknown behavior of the Black Boxes in D we use the symbolic methods from Sect. 4: Let there be a number of Black Box outputs modeled by Z and some other Black Box outputs modeled by  $Z_i$ -variables from  $\{Z_1, \ldots, Z_n\}$ . Symbolic  $Z/Z_i$ -simulation computes symbolic representations of the output functions  $\lambda_i(\vec{q}, \vec{x}, Z, \vec{Z_i})$  and transition functions  $\delta_i(\vec{q}, \vec{x}, Z, \vec{Z_i})$ .

In standard model checking for complete designs, an atomic property  $y_i$  is satisfied for a state  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \in \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|}$  if  $\lambda_i|_{\vec{q}=\vec{q}^{\text{fix}}, \vec{x}=\vec{x}^{\text{fix}}} = 1$ . Here we include a state  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \in \mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|}$  if  $\lambda_i|_{\vec{q}=\vec{q}^{\text{fix}}, \vec{x}=\vec{x}^{\text{fix}}} = 1$ . Here we include a state  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  into  $Sat_A^{\text{appr}}(y_i)$ , if  $\lambda_i$  is 1 for a fixed value  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  assigned to  $(\vec{q}, \vec{x})$  and all possible assignments to Z and  $\vec{Z}_l$ . We include  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  into  $Sat_E^{\text{appr}}(y_i)$ , if  $\lambda_i$  is 1 for  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  assigned to  $(\vec{q}, \vec{x})$  and some assignment to Z and  $\vec{Z}_l$ . Thus we define the characteristic functions of  $Sat_A^{\text{appr}}(y_i)$  and  $Sat_E^{\text{appr}}(y_i)$  as follows:

#### Definition 13.

$$\chi_{Sat_{F}^{\operatorname{appr}}(y_{i})}(\vec{q},\vec{x}) := \forall Z \forall \vec{Z}_{l} \left( \lambda_{i}(\vec{q},\vec{x},Z,\vec{Z}_{l}) \right)$$

(1)

$$\chi_{Sat_{F}^{\operatorname{appr}}(y_{i})}(\vec{q},\vec{x}) := \exists Z \exists \vec{Z}_{l} \left( \lambda_{i}(\vec{q},\vec{x},Z,\vec{Z}_{l}) \right)$$

(2)

**Lemma 7.** For  $Sat_A^{appr}(y_i)$  and for  $Sat_E^{appr}(y_i)$  as defined in Def. 13:

$$Sat_A^{\mathsf{appr}}(y_i) \subseteq Sat_A^{\mathsf{exact}}(y_i), \quad Sat_E^{\mathsf{exact}}(y_i) \subseteq Sat_E^{\mathsf{appr}}(y_i).$$

Proof: If  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \in Sat_A^{\text{appr}}(y_i)$ , i.e.,  $\chi_{Sat_A^{\text{appr}}(y_i)}(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) = 1$ , then  $\lambda_i|_{\vec{q}=\vec{q}^{\text{fix}}, \vec{x}=\vec{x}^{\text{fix}}} = 1$  according to Def. 13, Eqn. (1). Consider an *arbitrary* completion  $D^c \in \mathcal{C}(D)$  where the replacement of the Black Boxes introduces the additional state variables  $\vec{q}^r \in \mathbb{B}^{|\vec{Q}^c|-|\vec{Q}|}$  and let  $\lambda_i^c((\vec{q}, \vec{q}^r), \vec{x})$  be the *i*-th output function of  $D^c$ . According to Thm. 4,  $\lambda_i^c|_{\vec{q}=\vec{q}^{\text{fix}}, \vec{x}=\vec{x}^{\text{fix}}} = 1$ , and thus  $\lambda_i^c((\vec{q}^{\text{fix}}, \vec{q}^r), \vec{x}^{\text{fix}}) = 1$  for all  $\vec{q}^r \in \mathbb{B}^{|\vec{Q}^c|-|\vec{Q}|}$ . That means that  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \in Sat_A^{\text{exact}}(y_i)$ , since  $D^c$  was chosen arbitrarily.

If  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \notin Sat_E^{\text{appr}}(y_i)$ , then  $\lambda_i|_{\vec{q}=\vec{q}^{\text{fix}}, \vec{x}=\vec{x}} = 0$  according to Def. 13, Eqn. (2). Then for an arbitrary completion  $D^c$  as given above we have according to Thm. 4:  $\lambda_i^c|_{\vec{q}=\vec{q}^{\text{fix}}, \vec{x}=\vec{x}} = 0$ , and thus  $\lambda_i^c((\vec{q}^{\text{fix}}, \vec{q}^r), \vec{x}^{\text{fix}}) = 0$  for all  $\vec{q}^r \in \mathbb{B}^{|\vec{Q}^c|-|\vec{Q}|}$ . That means that  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \notin Sat_E^{\text{exact}}(y_i)$ , since  $D^c$  was chosen arbitrarily.

The computation of  $Sat_A^{appr}(\varphi)$  and  $Sat_E^{appr}(\varphi)$  for general CTL formulas  $\varphi$  is performed based on possible transitions. Here we work with an approximation, too. We compute an over-approximation of the possible transitions, represented by the characteristic function  $\chi_{R_E}(\vec{q}, \vec{x}, \vec{q'})$ :

## Definition 14.

$\chi_{R_E}(\vec{q}, \vec{x}, \vec{q}') := \exists \vec{Z}_l \Big( \prod_{i=1}^{|\vec{q}|} \exists Z \big( \delta_i(\vec{q}, \vec{x}, Z, \vec{Z}_l) \equiv q_i' \big) \Big).$

The following lemma states that  $\chi_{R_E}$  over-approximates the possible transitions:

**Lemma 8.** If  $\chi_{R_E}(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, \vec{q}'^{\text{fix}}) = 0$ , then there is no possible transition from  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  to  $(\vec{q}'^{\text{fix}}, \vec{x}'^{\text{fix}})$  (for an arbitrary next input  $\vec{x}'^{\text{fix}}$ ).

**Proof:** If  $\chi_{R_E}(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, \vec{q}'^{\text{fix}}) = 0$ , then  $\forall \vec{Z}_l \left( \bigvee_{i=1}^{|\vec{q}|} \forall Z \left( \delta_i(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, Z, \vec{Z}_l) \neq q_i'^{\text{fix}} \right) \right) = 1$ . This means that for an arbitrary fixed output  $\vec{Z}_l^{\text{fix}}$  of the Black Boxes modeled by  $Z_i$ 's there is an  $i \in \{0, \ldots, |\vec{q}| - 1\}$  with

$$\forall Z \left( \delta_i(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, Z, \vec{Z}_l^{\text{fix}}) \neq q_i^{\prime \text{fix}} \right) = 1.$$

(3)

$\delta_i(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, Z, \vec{Z}_l^{\text{fix}}) = Z, \ \delta_i(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, Z, \vec{Z}_l^{\text{fix}}) = q'_i^{\text{fix}} \text{ or } \delta_i(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, Z, \vec{Z}_l^{\text{fix}}) = \neg q'_i^{\text{fix}} \text{ according to Lemma 2. In the two former cases,} Eq. (3) would not hold, thus we have <math>\delta_i(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, Z, \vec{Z}_l^{\text{fix}}) = \neg q'_i^{\text{fix}}$ , i.e., the output value of  $\delta_i$  differs from  $q'_i^{\text{fix}}$  for each replacement of the Z-modeled Black Boxes (Thm. 4).

Altogether we can conclude that the output value of  $\vec{\delta}$  for input  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  differs from  $\vec{q}'^{\text{fix}}$  independently from the values at the outputs of Black Boxes, i.e., there cannot be a possible transition from  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  to  $(\vec{q}'^{\text{fix}}, \vec{x}'^{\text{fix}})$ .

*Remark.* Extending Definitions 11 and 12 with respect to our approximations, we denote in the following not only the states in  $Sat_E^{\text{exact}}(\varphi)$ , but also the states in  $Sat_E^{\text{appr}}(\varphi)$  by 'states *possibly* satisfying  $\varphi$ '. Similarly, we characterize the states in  $Sat_A^{\text{appr}}(\varphi)$  by 'states *definitely* satisfying  $\varphi$ ' and all transitions described by  $\chi_{R_E}$  as 'possible transitions'.

Based on  $\chi_{R_E}$ ,  $Sat_A^{appr}(y_i)$  and  $Sat_E^{appr}(y_i)$ , it is possible to define rules how arbitrary CTL formulas can be recursively evaluated. We show here how to compute sets  $Sat_A^{appr}(\cdot)$  and  $Sat_E^{appr}(\cdot)$  for CTL formulas  $EX\psi$ ,  $\neg\psi$ ,  $(\psi_1 \lor \psi_2)$ ,  $EG\psi$ , and  $E\psi_1U\psi_2$ . We start with  $EX\psi$ :

The basic idea behind the definition of  $Sat_E^{appr}(EX\psi)$  and  $Sat_A^{appr}(EX\psi)$  is the following: If there is a possible transition from a

state  $(\vec{q}, \vec{x})$  to another state possibly satisfying  $\psi$ , then  $(\vec{q}, \vec{x})$  possibly satisfies  $EX\psi$ . If all possible transitions from a state  $(\vec{q}, \vec{x})$  lead to states definitely satisfying  $\psi$ , then  $(\vec{q}, \vec{x})$  definitely satisfies  $EX\psi$ . The next definition formalizes and refines this idea:

#### Definition 15.

$$\begin{split} \chi_{Sat_{E}^{\mathsf{appr}}(EX\psi)}(\vec{q},\vec{x}) &:= \exists \vec{q}' \Big( \chi_{R_{E}}(\vec{q},\vec{x},\vec{q}') \cdot \exists \vec{x}' \big( \chi_{Sat_{E}^{\mathsf{appr}}(\psi)} \mid \vec{q} \leftarrow \vec{q}' \big) (\vec{q}',\vec{x}') \Big) \\ \chi_{Sat_{A}^{\mathsf{appr}}(EX\psi)}(\vec{q},\vec{x}) &:= \forall \vec{q}' \Big( \chi_{R_{E}}(\vec{q},\vec{x},\vec{q}') \rightarrow \exists \vec{x}' \big( \chi_{Sat_{A}^{\mathsf{appr}}(\psi)} \mid \vec{q} \leftarrow \vec{q}' \big) (\vec{q}',\vec{x}') \Big) \end{split}$$

**Lemma 9.** Let  $Sat_A^{appr}(\psi)$  be an under-approximation of  $Sat_A^{exact}(\psi)$ and  $Sat_{E}^{appr}(\psi)$  be an over-approximation of  $Sat_{E}^{exact}(\psi)$ , let  $Sat_A^{appr}(EX\psi)$  and  $Sat_E^{appr}(EX\psi)$  be defined as in Def. 15. Then

$$Sat_{E}^{\mathsf{exact}}(EX\psi) \subseteq Sat_{E}^{\mathsf{appr}}(EX\psi), \quad Sat_{A}^{\mathsf{appr}}(EX\psi) \subseteq Sat_{A}^{\mathsf{exact}}(EX\psi).$$

Proof: To prove the first part of Lemma 9, we assume that  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \in Sat_E^{\text{exact}}(EX\psi)$ . This implies that there is a possible transition from  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  to some state  $(\vec{q}'^{\text{fix}}, \vec{x}'^{\text{fix}}) \in Sat_E^{\text{exact}}(\psi)$ . Since  $Sat_E^{\text{exact}}(\psi) \subseteq Sat_E^{\text{appr}}(\psi)$ , there is also a possible transition (given by  $\chi_{R_E}$ ) from  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}})$  to some state  $(\vec{q}'^{\text{fix}}, \vec{x}'^{\text{fix}}) \in$  $Sat_{E}^{appr}(\psi)$ . By Def. 15, this means that  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \in Sat_{E}^{appr}(EX\psi)$ .

The proof for the second part is slightly more involved: Assume that  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \notin Sat_A^{\text{exact}}(EX\psi)$ . That means that there exists a completion  $D^c$  of the incomplete design (with transition function  $\vec{\delta}^c$ , and additional state variables  $\vec{q}^{\,r} \in \mathbb{B}^{|\vec{Q}^c| - |\vec{Q}|}$  introduced by replacements of Black Boxes) and there exists  $\vec{q}^{\text{fix}r} \in \mathbb{B}^{|\vec{Q}^c| - |\vec{Q}|}$ , such that  $((\vec{q}^{\text{fix}}, \vec{q}^{\text{fix}r}), \vec{x}^{\text{fix}})) \not\models EX\psi$ . I.e., with  $\vec{\delta}^c((\vec{q}^{\text{fix}}, \vec{q}^{\text{fix}r}), \vec{x}^{\text{fix}}) = (\vec{q}'^{\text{fix}}, \vec{q}'^{\text{fix}r}), \vec{x}'^{\text{fix}}) \not\models \psi \forall \vec{x}'^{\text{fix}} \in \mathbb{B}^{|\vec{X}|}$ . This leads to  $\chi_{B_E}(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}, \vec{q}'^{\text{fix}}) = 1 \land \forall \vec{x}'^{\text{fix}} \in \mathbb{B}^{|\vec{X}|} : (\vec{q}'^{\text{fix}}, \vec{x}'^{\text{fix}}) \notin \psi \forall \vec{x}'^{\text{fix}} \in \mathbb{B}^{|\vec{X}|}$ .  $\begin{aligned} & Sat_A^{\operatorname{resc}}(\psi). \text{ Since } Sat_A^{\operatorname{appr}}(\psi) \subseteq Sat_A^{\operatorname{exact}}(\psi): \\ & \chi_{R_E}(\vec{q}^{\operatorname{fix}}, \vec{x}^{\operatorname{fix}}, \vec{q}'^{\operatorname{fix}}) = 1 \land \forall \vec{x}'^{\operatorname{fix}} \in \mathbb{B}^{|\vec{X}|}: (\vec{q}'^{\operatorname{fix}}, \vec{x}'^{\operatorname{fix}}) \notin Sat_A^{\operatorname{appr}}(\psi) \\ & \text{and thus } \left(\chi_{R_E}(\vec{q}^{\operatorname{fix}}, \vec{x}^{\operatorname{fix}}, \vec{q}'^{\operatorname{fix}}) \cdot \forall \vec{x}' \overline{\chi_{Sat_A^{\operatorname{appr}}}(\psi)}(\vec{q}'^{\operatorname{fix}}, \vec{x}')\right) = 1. \text{ Acc} \end{aligned}$

cording to Def. 15 this implies  $\chi_{Sat_{A}^{appr}(EX\psi)}(\vec{q}^{fix}, \vec{x}^{fix}) = 0$ , i.e.,  $(\vec{q}^{\text{fix}}, \vec{x}^{\text{fix}}) \notin Sat_A^{\text{appr}}(EX\psi).$

Negation and disjunction are handled as follows:

## **Definition 16.**

$$\begin{split} \chi_{Sat_{A}^{\texttt{appr}}(\neg\psi)}(\vec{q},\vec{x}) &:= \overline{\chi_{Sat_{E}^{\texttt{appr}}(\psi)}}(\vec{q},\vec{x}) \quad and \\ \chi_{Sat_{A}^{\texttt{appr}}(\neg\psi)}(\vec{q},\vec{x}) &:= \overline{\chi_{Sat_{A}^{\texttt{appr}}}}(\psi)(\vec{q},\vec{x}), \\ \chi_{Sat_{A}^{\texttt{appr}}(\psi_{1}\vee\psi_{2})}(\vec{q},\vec{x}) &:= (\chi_{Sat_{A}^{\texttt{appr}}(\psi_{1})} \vee \chi_{Sat_{A}^{\texttt{appr}}(\psi_{2})})(\vec{q},\vec{x}) \quad and \\ \chi_{Sat_{A}^{\texttt{appr}}(\psi_{1}\vee\psi_{2})}(\vec{q},\vec{x}) &:= (\chi_{Sat_{A}^{\texttt{appr}}(\psi_{1})} \vee \chi_{Sat_{A}^{\texttt{appr}}(\psi_{2})})(\vec{q},\vec{x}). \end{split}$$

Note that negation plays a special role here, since it turns an overapproximation of the set of states which possibly satisfy  $\psi$  into an *under-approximation* of the set of states which *definitely* satisfy  $\neg \psi$ (and vice versa).

**Lemma 10.** Let  $Sat_A^{appr}(\psi)$  be an under-approximation of  $Sat_{A}^{exact}(\psi)$  and  $Sat_{E}^{appr}(\psi)$  be an over-approximation of  $Sat_{E}^{\mathsf{exact}}(\psi)$ , let  $Sat_{A}^{\mathsf{appr}}(\neg\psi)$ ,  $Sat_{E}^{\mathsf{appr}}(\neg\psi)$ ,  $Sat_{A}^{\mathsf{appr}}(\psi_{1}\lor\psi_{2})$ , and  $Sat_E^{appr}(\psi_1 \vee \psi_2)$  be defined by Def. 16. Then

$$Sat_A^{\mathsf{appr}}(\neg\psi) \subseteq Sat_A^{\mathsf{exact}}(\neg\psi),$$

(4)

(6)

$$Sat_E^{exact}(\neg\psi) \subseteq Sat_E^{appr}(\neg\psi),$$

(5)

$$Sat_A^{\text{appr}}(\psi_1 \lor \psi_2) \subseteq Sat_A^{\text{cacc}}(\psi_1 \lor \psi_2),$$

$$Sat_{E}^{\mathsf{exact}}(\psi_{1} \vee \psi_{2}) \subseteq Sat_{E}^{\mathsf{appr}}(\psi_{1} \vee \psi_{2}).$$

(7)

Proof:

$$Sat_{A}^{\mathsf{appr}}(\neg \psi) = (\mathbb{B}^{|Q|} \times \mathbb{B}^{|X|}) \setminus Sat_{E}^{\mathsf{appr}}(\psi) \quad (\text{Def.16})$$

$$\subseteq (\mathbb{B}^{|\vec{Q}|} \times \mathbb{B}^{|\vec{X}|}) \setminus Sat_{E}^{\mathsf{exact}}(\psi) \quad (\text{Precond. Lemma 10})$$

$$= Sat_{A}^{\mathsf{exact}}(\neg \psi). \qquad (\text{Def.11})$$

This proves Eqn. (4). With an analogous argument Eqn. (5) can be proved. Eqn. (6) and Eqn. (7) follow easily by appropriate set operations.

Finally, we define  $\varphi = EG\psi$  and  $\varphi = E\psi_1U\psi_2$  to be evaluated by their standard fixed point iterations (see Figs. 2, 3) based on the evaluation of EX defined above (two separate fixed point iterations for  $Sat_A^{appr}(\cdot)$  and  $Sat_E^{appr}(\cdot)$ ).

**Lemma 11.** If  $Sat_A^{appr}(\psi) \subseteq Sat_A^{exact}(\psi)$  and  $Sat_E^{exact}(\psi) \subseteq$  $Sat_{E}^{appr}(\psi), Sat_{A}^{appr}(EG\psi), Sat_{E}^{appr}(EG\psi), Sat_{A}^{appr}(E\psi_{1}U\psi_{2}), and$  $Sat_{E}^{appr}(E\psi_{1}U\psi_{2})$  are obtained by the fixed point iteration of Figs. 2 and 3, then  $Sat_A^{appr}(EG\psi) \subseteq Sat_A^{exact}(EG\psi)$ ,  $Sat_E^{exact}(EG\psi) \subseteq Sat_E^{appr}(EG\psi)$ ,  $Sat_A^{appr}(E\psi_1U\psi_2) \subseteq Sat_A^{exact}(E\psi_1U\psi_2)$  and  $Sat_E^{\mathsf{exact}}(E\psi_1U\psi_2) \subseteq Sat_E^{\mathsf{appr}}(E\psi_1U\psi_2).$

*Proof:* Since the evaluation of EG and EU is done by iterated application of the EX-operator according to Figs. 2 and 3, the proof follows immediately from the corresponding properties of EX (see Lemma 9) and monotonicity of set union resp. intersection.  $\square$

**Theorem 12.** If  $\chi_{Sat^{appr}(\varphi)}$  and  $\chi_{Sat^{appr}(\varphi)}$  are computed recursively according to Definitions 13, 15, 16, then

$$\begin{aligned} \forall \vec{x} \Big( \left( \chi_{Sat_A^{\text{appr}}(\varphi)}(\vec{q}, \vec{x}) \right) |_{\vec{q} = \vec{q}^0} \Big) &= 1 \implies \varphi \text{ is valid} \\ \exists \vec{x} \Big( \overline{\chi_{Sat_E^{\text{appr}}(\varphi)}(\vec{q}, \vec{x})} |_{\vec{q} = \vec{q}^0} \Big) &= 1 \implies \varphi \text{ is not realizable} \end{aligned}$$

*Proof:* The proof follows directly from Lemmas 6–11. Note that the results in this section have a strong relationship to 3-valued model checking known from the context of software model checking [12], [13]. Details are discussed in Sect. 8.

#### 5.3 Including Z<sub>i</sub>-Variables into the State Space

Sometimes the approximations considered above are too coarse to obtain definite answers concerning validity or non-realizability of CTL formulas (see also Sect. 7). A further improvement on the accuracy of the two approximated sets can be obtained by including  $Z_i$ -variables assigned to Black Box outputs into the state space.

As a motivation for this, consider the CTL formula  $\varphi = (y_1 \to EXy_3) = (\neg y_1 \lor EXy_3)$  for the design illustrated in Fig. 1 b). The formula essentially says that if the first output  $Y_1$ holds the value 1 in the initial state, then the third output  $Y_3$  holds the value 1 in the next state of the design. The formula is valid, since 'output  $Y_1$  is 1' implies that the flip flop input is 1 and thus output  $Y_3$  is 1 in the next state. This holds independently from the implementation of the Black Box.

If we recursively compute  $\chi_{Sat_A^{appr}(\neg y_1 \lor EXy_3)}$  according to the previous section (modeling the Black Box output by  $Z_1$ ), we obtain:

$$\begin{split} \chi_{Sat_{A}^{\operatorname{appr}}(\neg y_{1})}(q_{1},x_{1}) &= \forall Z_{1}(\lambda_{1}) = \overline{x}_{1} \\ \chi_{Sat_{A}^{\operatorname{appr}}(y_{3})}(q_{1},x_{1}) &= \forall Z_{1}(\lambda_{3}) = q_{1} \\ \chi_{Sat_{A}^{\operatorname{appr}}(EXy_{3})}(q_{1},x_{1}) &= \forall q_{1}' \Big( \big( \exists Z_{1}(\delta_{1} \equiv q_{1}')\big) \to \exists x_{1}'(\chi_{Sat_{A}^{\operatorname{appr}}(y_{3})})|_{\substack{q_{1} \leftarrow q_{1}' \\ x_{1} \leftarrow x_{1}'}} \Big) \\ &= \forall q_{1}' \Big( \big( \exists Z_{1}(Z_{1} \equiv q_{1}')\big) \to q_{1}' \Big) = 0. \end{split}$$

The validity of  $\varphi$  cannot be shown, since

$$\forall x_1(\chi_{Sat_A^{\operatorname{appr}}(y_1 \vee EXy_3)}|_{q_1=q_1^0}) = \forall x_1(\overline{x}_1 \vee 0) = 0.$$

Having a closer look at the computation above, we observe: On the one hand, only those states with  $x_1 = 0$  are included into  $Sat_A^{appr}(\neg y_1)$ , since the output of the Black Box output might be 1 in the current state. On the other hand,  $Sat_A^{appr}(EXy_3)(q_1, x_1) = \emptyset$ , since the output of the Black Box output might be 0 in the current state. Clearly the Black Box output cannot be 0 and 1 at the same time and by case distinction wrt.  $Z_1$  we can prove that  $\varphi$  is valid.

Based on this consideration, our model checking routine for incomplete designs is improved by including  $Z_i$ -variables assigned to Black Box outputs into the state space. In this way the corresponding Black Box output values  $Z_i$  are constant within each single state and therefore in our example  $Z_1$  has a fixed value for each state.

Note that it is not always necessary to include *all*  $Z_i$ 's into the state space; this provides another possibility of flexibly processing the unknowns at this point, which can be used as a tradeoff between efficiency and accuracy.

Let  $\vec{Z}_o$  be the  $Z_i$ -simulated Black Box outputs that are included into the state space and let  $\vec{Z}_l$  be the  $Z_i$ -simulated Black Box outputs that are not included. Then the values of  $\vec{Z}_o$  are constant within each single state, while the values of  $\vec{Z}_l$  are arbitrary as they were before.

Both the output function  $\vec{\lambda}(\vec{q}, \vec{x}, Z, \vec{Z}_l, \vec{Z}_o)$  and the transition function  $\vec{\delta}(\vec{q}, \vec{x}, Z, \vec{Z}_l, \vec{Z}_o)$  can be computed by using the symbolic simulation from Sect. 4 for which it is not necessary to distinguish between  $\vec{Z}_l$  and  $\vec{Z}_o$ .

Now the computation of sets  $Sat_A^{\text{appr,incl}}(\cdot)$  and  $Sat_E^{\text{appr,incl}}(\cdot)$  is performed in a manner similar to the previous section. We start with the sets of states definitely or possibly satisfying the atomic CTL formula  $y_i$ :

### Definition 17.

$$\begin{split} \chi_{Sat_A^{\text{appr,incl}}(y_i)}(\vec{q}, \vec{x}, \vec{Z}_o) &:= \forall Z \forall \vec{Z}_l \left( \lambda_i(\vec{q}, \vec{x}, Z, \vec{Z}_l, \vec{Z}_o) \right) \\ \chi_{Sat_E^{\text{appr,incl}}(y_i)}(\vec{q}, \vec{x}, \vec{Z}_o) &:= \exists Z \exists \vec{Z}_l \left( \lambda_i(\vec{q}, \vec{x}, Z, \vec{Z}_l, \vec{Z}_o) \right). \end{split}$$

**Lemma 13.** For  $Sat_A^{appr,incl}(y_i)$ ,  $Sat_E^{appr,incl}(y_i)$  as defined in Def. 17:

$\left(\forall \vec{Z}_o \chi_{Sat_A^{\operatorname{appr},\operatorname{incl}}(y_i)}\right) \leq \chi_{Sat_A^{\operatorname{exact}}(y_i)}, \quad \chi_{Sat_E^{\operatorname{exact}}(y_i)} \leq \left(\exists \vec{Z}_o \chi_{Sat_E^{\operatorname{appr},\operatorname{incl}}(y_i)}\right).$

*Proof:* The proof follows immediately from Lemma 7, since  $(\forall \vec{Z}_o \chi_{Sat_A^{\text{appr,incl}}(y_i)}) = \chi_{Sat_A^{\text{appr}}(y_i)}$  and  $(\exists \vec{Z}_o \chi_{Sat_E^{\text{appr,incl}}(y_i)}) = \chi_{Sat_E^{\text{appr}}(y_i)}$ .

Analogously, we define an over-approximation  $\chi_{R_E^{\text{incl}}}$  for the characteristic function of possible transitions:

#### Definition 18.

$$\chi_{R_E^{\text{incl}}}(\vec{q}, \vec{x}, \vec{Z}_o, \vec{q}') := \left( \exists \vec{Z}_l \prod_{i=1}^{|\vec{q}|} \exists Z \left( \delta_i(\vec{q}, \vec{x}, Z, \vec{Z}_l, \vec{Z}_o) \equiv q_i' \right) \right).$$

As in the previous section the sets  $Sat_A^{\text{appr,incl}}(EX\psi)$  and  $Sat_E^{\text{appr,incl}}(EX\psi)$  are computed based on  $Sat_A^{\text{appr,incl}}(\psi)$ ,  $Sat_E^{\text{appr,incl}}(\psi)$  and  $\chi_{R_{\text{incl}}^{\text{incl}}}$ :

#### Definition 19.

$$\begin{split} &\chi_{Sat_{E}^{\text{appr,incl}}(EX\psi)}(\vec{q},\vec{x},\vec{Z}_{o}) := \\ &\exists \vec{q}' \Big( \chi_{R_{E}^{\text{incl}}}(\vec{q},\vec{x},\vec{Z}_{o},\vec{q}') \cdot \exists \vec{x}' \exists \vec{Z}'_{o} \big( \chi_{Sat_{E}^{\text{appr,incl}}(\psi)} \big|_{\vec{x} \leftarrow \vec{x}'}^{\vec{q} \leftarrow \vec{x}'} \big) (\vec{q}',\vec{x}',\vec{Z}'_{o}) \Big). \\ &\chi_{Sat_{A}^{\text{appr,incl}}(EX\psi)}(\vec{q},\vec{x},\vec{Z}_{o}) := \\ &\forall \vec{q}' \Big( \chi_{R_{E}^{\text{incl}}}(\vec{q},\vec{x},\vec{Z}_{o},\vec{q}') \rightarrow \exists \vec{x}' \forall \vec{Z}'_{o} \big( \chi_{Sat_{A}^{\text{appr,incl}}(\psi)} \big|_{\vec{x} \leftarrow \vec{x}'_{o}}^{\vec{q} \leftarrow \vec{q}'} \big) (\vec{q}',\vec{x}',\vec{Z}'_{o}) \Big). \end{split}$$

**Lemma 14.** If both  $Sat_A^{\text{appr,incl}}(EX\psi)$  and  $Sat_E^{\text{appr,incl}}(EX\psi)$ are defined as in Def. 19,  $(\forall \vec{Z}_o \chi_{Sat_A^{\text{appr,incl}}(\psi)}) \leq \chi_{Sat_A^{\text{exact}}(\psi)}$  and  $(\exists \vec{Z}_o \chi_{Sat_E^{\text{appr,incl}}(\psi)}) \geq \chi_{Sat_E^{\text{exact}}(\psi)}$ , then

$$\left( \forall Z_o \chi_{Sat_A^{\text{appr,incl}}(EX\psi)} \right) \leq \chi_{Sat_A^{\text{exact}}(EX\psi)} \text{ and } \\ \chi_{Sat_E^{\text{exact}}(EX\psi)} \leq \left( \exists \vec{Z}_o \chi_{Sat_B^{\text{appr,incl}}(EX\psi)} \right).$$

Proof:

Part

1:

$$(\forall Z_o \chi_{Sat^{appr,incl}_A(EX\psi)})$$

=  $\forall \vec{Z}_o \forall \vec{q}' ((\neg \chi_{R^{incl}_E}) \lor \exists \vec{x}' \forall \vec{Z}'_o (\chi_{Sat^{appr,incl}_A(\psi)} | \frac{\vec{a} \leftarrow \vec{a}'}{\vec{z}_o \leftarrow \vec{z}'_o}))$

=  $\forall \vec{q}' ((\neg \exists \vec{Z}_o \chi_{R^{incl}_E}) \lor \exists \vec{x}' \forall \vec{Z}'_o (\chi_{Sat^{appr,incl}_A(\psi)} | \frac{\vec{a} \leftarrow \vec{a}'}{\vec{z}_o \leftarrow \vec{z}'_o}))$

From Definitions 14 and 18 we conclude  $(\exists \vec{Z}_o \chi_{R_E^{\text{ind}}}) = \chi_{R_E}$  and from the precondition of the lemma we know

Fig. 6. Illustration for the functional preimage computation for complete designs.

Fig. 7. Illustration for the functional preimage computation for incomplete designs

$(\forall Z_o \chi_{Sat_A^{\operatorname{appr,incl}}(\psi)}) \leq \chi_{Sat_A^{\operatorname{exact}}(\psi)}$ . So we can apply Lemma 9 and obtain  $(\forall Z_o \chi_{Sat_A^{\operatorname{appr,incl}}(EX\psi)}) \leq \chi_{Sat_A^{\operatorname{exact}}(EX\psi)}$ .

Part 2:

$$(\exists \vec{Z}_o \chi_{Sat_E^{\operatorname{appr,incl}}(EX\psi)}) =$$

$$= \exists \vec{Z}_o \exists \vec{q}' \left( \chi_{R_E^{\operatorname{ind}}} \cdot \exists \vec{x}' \exists \vec{Z}'_o \left( \chi_{Sat_E^{\operatorname{appr,incl}}(\psi)} \middle|_{\vec{Z}_o \leftarrow \vec{Z}'_o} \right) \right)$$

$$= \exists \vec{q}' \left( \underbrace{\exists \vec{Z}_o \chi_{R_E^{\operatorname{incl}}} \cdot \exists \vec{x}'}_{E} \exists \vec{Z}'_o \left( \chi_{Sat_E^{\operatorname{appr,incl}}(\psi)} \middle|_{\vec{Z}_o \leftarrow \vec{Z}'_o} \right) \right)$$

Again, we apply Defs. 14, 18, the precondition of the lemma and Lemma 9 and obtain  $\left(\exists \vec{Z}_o \chi_{Sat_E^{\text{appr,incl}}(EX\psi)}\right) \geq \chi_{Sat_E^{\text{exact}}(EX\psi)}$ .

For all remaining CTL operators  $\neg$ ,  $\lor$ , EG and EU,  $Sat_A^{\text{appr,incl}}(\cdot)$ and  $Sat_E^{\text{appr,incl}}(\cdot)$  are computed as already described in Sect. 5.2. Lemmas like Lemma 10 and 11 hold with exactly the same arguments as in Sect. 5.2.

**Theorem 15.** If  $\chi_{Sat_A^{appr,incl}(\varphi)}$  and  $\chi_{Sat_E^{appr,incl}(\varphi)}$  are computed recursively as described above, then

$$\forall \vec{x} \left( \left( \forall Z_o \left( \chi_{Sat_A^{\operatorname{appr}, \operatorname{incl}}(\varphi)}(\vec{q}, \vec{x}, Z_o) \right) \right) |_{\vec{q} = \vec{q}^0} \right) = 1 \implies \varphi \text{ is valid}$$

$$\exists \vec{x} \left( \exists \vec{Z}_o \left( \chi_{Sat_E^{\operatorname{appr}, \operatorname{incl}}(\varphi)}(\vec{q}, \vec{x}, \vec{Z}_o) \right) |_{\vec{q} = \vec{q}^0} \right) = 1 \implies \varphi \text{ not realizable}$$

*Proof:* As shown above we have  $(\forall \vec{Z}_o \chi_{Sat_A^{\text{appr,incl}}(\varphi)}) \leq \chi_{Sat_E^{\text{exact}}(\varphi)}$  and  $(\exists \vec{Z}_o \chi_{Sat_E^{\text{appr,incl}}(\varphi)}) \geq \chi_{Sat_E^{\text{exact}}(\varphi)}$ . So the theorem follows from Lemma 6.

*Example.* Again, we consider the CTL formula  $\varphi = (\neg y_1 \lor EXy_3)$  for the design illustrated in Fig. 1 b):

$$\begin{split} \chi_{Sat_A^{\text{appr,incl}}(\neg y_1)}(q_1, x_1, Z_1) &= \lambda_1 = \overline{x}_1 \lor Z_1 \\ \chi_{Sat_A^{\text{appr,incl}}(y_3)}(q_1, x_1, Z_1) &= \lambda_3 = q_1 \\ \chi_{Sat_A^{\text{appr,incl}}(EXy_3)}(q_1, x_1, Z_1) &= \forall q_1' \big( (\delta_1 \equiv q_1') \to \exists x_1' \forall Z_1'(\chi_{Sat_A}(y_3)) \big|_{x_1 \leftarrow x_1'}^{q_1 \leftarrow q_1'} \big) \\ &= \forall q_1' \big( (Z_1 \equiv q_1') \to q_1' \big) = Z_1 \qquad Z_1 \leftarrow Z_1' \end{split}$$

Now the validity of  $\varphi$  can be shown:

$$\forall x_1 \forall Z_1 (\chi_{Sat_A^{\mathsf{appr,incl}}(y_1 \lor EXy_3)}|_{q_1 = q_1^0}) = \forall x_1 \forall Z_1 (\overline{x}_1 \lor \overline{Z}_1 \lor Z_1) = 1$$

#### 5.4 Functional Preimage Computation

For complete designs, there are two methods to compute the preimage of a given set of states, as it is needed for the computation of  $Sat(EX\psi)$  [22], [23]:

So far, we used the *relational* approach in our approximate model checking procedures for incomplete designs. For complete designs this approach builds the characteristic function of the transition relation  $\chi_R(\vec{q}, \vec{x}, \vec{q}') := \prod_{i=1}^{|\vec{q}|} (\delta_i(\vec{q}, \vec{x}) \equiv q'_i)$  which is then used in the actual preimage computation for a given set of states (represented by  $\chi_N$  in this case):

$$\chi_{EX}(\chi_N)(\vec{q},\vec{x}) := \exists \vec{q}' \exists \vec{x}' (\chi_R(\vec{q},\vec{x},\vec{q}') \cdot (\chi_N | \vec{q} \leftarrow \vec{q}'_{\prime})(\vec{q}',\vec{x}'))$$

The functional approach uses the compose operator, with  $f|_{x_i \leftarrow g} := \overline{g} \cdot f|_{x_i=0} + g \cdot f|_{x_i=1}$  for  $f, g: \mathbb{B}^n \to \mathbb{B}$  and an input variable  $x_i$  of f (see Def. 5). Based on the compose operator, the preimage of a set of states given by  $\chi_N$  can be computed as follows:

$$\chi_{EX}(\chi_N)(\vec{q},\vec{x}) := \left(\exists \vec{x}\chi_N(\vec{q},\vec{x})\right)|_{\vec{q}\leftarrow\vec{\delta}(\vec{q},\vec{x})}$$

(Here the composition of different variables  $q_i$  by functions  $\delta(\vec{q}, \vec{x})$  is performed in parallel.) Fig. 6 illustrates this composition as the

composition of the Boolean circuit for  $\vec{\delta}$  into the Boolean circuit for the characteristic function  $(\exists \vec{x}\chi_N)(\vec{q})$  (variables  $q_i$  of  $(\exists \vec{x}\chi_N)(\vec{q})$ are replaced by the corresponding transition functions  $\delta_i(\vec{q}, \vec{x})$ ).

Note that the number of necessary variables can be decreased by using compose operations instead of transition relations, since the  $\vec{q}'$  variables are no longer needed. Moreover, the computation of the transition *relation* is not needed. Due to this, the functional version of preimage computation is often more efficient than the relational version [22].

We now look into the question of how to generalize functional preimage computation so that we can use it for model checking of incomplete designs. In doing so, we first confine ourselves to the case that  $Z_i$ -variables are *not* included in the state space in order to keep the presentation compact.

Taking into account that the transition function  $\vec{\delta}(\vec{q}, \vec{x}, Z, \vec{Z}_l)$  now depends on the additional variables Z and  $\vec{Z}_l$ , we have to replace the usual *compose* operator by a new *compose-Z* operator:

**Definition 20.** The compose-*Z* operator " $|^{cZ}$ " for  $f : \mathbb{B}^n \to \mathbb{B}$  with input variables  $y_1, \ldots, y_n$  and  $g : \mathbb{B}^{n+1} \to \mathbb{B}$  with input variables  $y_1, \ldots, y_n$ , *Z*, is defined as:

$$f|_{y_i \leftarrow g}^{cZ} := \overline{g}|_{Z \leftarrow \overline{Z}} \cdot f|_{y_i = 0} + g \cdot f|_{y_i = 1}$$

$$\tag{8}$$

Just as in the definition of symbolic Z-simulation in Sect. 4 we have to replace Z by  $\overline{Z}$  after negation in the formula for *compose-Z*.

A composition of a *vector* of variables by *compose-Z* is computed by a recursive computation of compositions (as for the original *compose* operator) and the formula  $(\exists \vec{x}\chi_N(\vec{q}, \vec{x}))|_{\vec{q}\leftarrow\vec{\delta}(\vec{q},\vec{x},Z,\vec{z}_l)}$  for the complete case is now replaced by  $(\exists \vec{x}\chi_N(\vec{q}, \vec{x}))|_{\vec{q}\leftarrow\vec{\delta}(\vec{q},\vec{x},Z,\vec{z}_l)}^{cZ}$  for the incomplete case.

For a better understanding of *compose-Z* (together with its deficiencies explained in the following and a corresponding improvement) please assume for a moment that  $(\exists \vec{x}\chi_N(\vec{q},\vec{x}))$  is represented as a BDD which in turn can be seen as a multiplexer circuit. In Fig. 7 the output functions  $\delta_i(\vec{q}, \vec{x}, Z, \vec{Z}_l)$  of  $\vec{\delta}$  are inputs to the BDD for  $(\exists \vec{x}\chi_N(\vec{q}, \vec{x}))$ , i.e., they correspond to select-inputs of the multiplexers in the circuit representation. Now it is easy to see that  $(\exists \vec{x}\chi_N(\vec{q}, \vec{x}))|_{\vec{q}\leftarrow\vec{\delta}(\vec{q},\vec{x},Z,\vec{Z}_l)}^{cZ}$  as defined above can be interpreted as the result of a symbolic  $Z/Z_i$ -simulation of the Boolean circuit given in Fig. 7 ( $\delta_i$  play the role of g in Eqn. (8)).

However, there is an obvious deficiency of simple symbolic  $Z/Z_i$ -simulation applied to multiplexer circuits derived from BDDs: Consider the case that  $(f|_{y_i=0})|_{\vec{y}=\vec{e}} = 1$ ,  $(f|_{y_i=1})|_{\vec{y}=\vec{e}} = 1$ and  $g|_{\vec{y}=\vec{e}} = Z$  in Eqn. (8). Symbolic  $Z/Z_i$ -simulation computes  $(f|_{y_i\leftarrow g}^{C})|_{\vec{y}=\vec{e}} = Z$ . In this special case it is easy to see that this is an inaccuracy (inherited from conventional (0, 1, X)-simulation) which is not really needed:  $g|_{\vec{y}=\vec{e}}$  selects between  $(f|_{y_i=0})|_{\vec{y}=\vec{e}} = 1$  and  $(f|_{y_i=1})|_{\vec{y}=\vec{e}} = 1$ . Even if the value of  $g|_{\vec{y}=\vec{e}}$  is unknown, we can easily conclude that the output of  $(f|_{y_i\leftarrow g}^{CZ})|_{\vec{y}=\vec{e}}$  is 1. Based on this observation we define an improved *compose-Z* operator which improves the accuracy of the simple symbolic  $Z/Z_i$ -simulation by replacing Eqn. (8) as follows:

**Definition 21.** The improved compose-Z operator " $|^{cZ, impr}$ " for  $f: \mathbb{B}^n \to \mathbb{B}$  with input variables  $y_1, \ldots, y_n$  and  $g: \mathbb{B}^{n+1} \to \mathbb{B}$  with input variables  $y_1, \ldots, y_n$ , Z, is defined as:

$$f|_{y_i \leftarrow g}^{cZ, \text{impr}} := \overline{g}|_{Z \leftarrow \overline{Z}} \cdot f|_{y_i = 0} + g \cdot f|_{y_i = 1} + f|_{y_i = 0} \cdot f|_{y_i = 1}$$

(9)

The additional term in (9) may seem to be unnecessary at first sight, yet it is easy to see that for  $(f|_{y_i=0})|_{\vec{y}=\vec{\epsilon}} = 1$ ,  $(f|_{y_i=1})|_{\vec{y}=\vec{\epsilon}} = 1$  and  $g|_{\vec{y}=\vec{\epsilon}} = Z$  Eqn. (9) results in  $(f|_{x_i \leftarrow g}^{cZ, impr})|_{\vec{y}=\vec{\epsilon}} = 1$  which is more exact than the result of simple  $Z/Z_i$ -simulation (i.e., the result contains more accurate information).

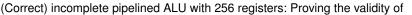

Fig. 8. Motivating Example for Exact Symbolic Model Checking

Fig. 9. Extracting the flip-flops from a Black Box with bounded memory size of 2.

For the case that more than one variable is replaced by a function, we have to define composition recursively:

**Definition 22.** Let  $f: \mathbb{B}^n \to \mathbb{B}$  be a Boolean function over variables  $\vec{y} = (y_1, \ldots, y_n)$  and  $g_i: \mathbb{B}^{n+1} \to \mathbb{B}$   $(1 \le i \le k)$  be Boolean functions over variables  $(y_1, \ldots, y_n, Z)$ . The improved compose-*Z* operator " $|^{cZ, \text{impr}}$ " is then recursively defined as:

$$\begin{split} f|^{cZ, \mathsf{impr}}_{\mathcal{B}} &:= \overline{g}_k|_{Z \leftarrow \overline{Z}} \cdot \left(f|_{y_k=0}\right)|^{cZ, \mathsf{impr}}_{\substack{y_1 \leftarrow g_1 \\ y_1 \leftarrow g_1 \\ y_k \leftarrow g_k \\ }} + g_k \cdot \left(f|_{y_k=0}\right)|^{cZ, \mathsf{impr}}_{\substack{y_1 \leftarrow g_{k-1} \\ y_1 \leftarrow g_k - 1 \\ y_1 \leftarrow g_k - 1 \\ }} \cdot \left(f|_{y_k=1}\right)|^{cZ, \mathsf{impr}}_{\substack{y_{k-1} \leftarrow g_{k-1} \\ y_{k-1} \leftarrow g_{k-1} \\ y_{k-1} \leftarrow g_{k-1} \\ y_{k-1} \leftarrow g_{k-1} \\ }} f|^{cZ, \mathsf{impr}}_{\mathcal{B}} &:= f \end{split}$$

(Note that composition is performed in parallel here; a straightforward reduction of the composition for k variables to a series of k compositions for single variables would lead to a different result, since functions  $g_j$  may depend on replaced variables  $y_i$ .)

The consideration given above can be extended to the case that some Black Box outputs are modeled by  $\vec{Z}_o$  variables in the state space. Then, using the improved *compose-Z* operator, we can define  $\chi_{Sat_A^{func}(EX\psi)}$  and  $\chi_{Sat_E^{func}(EX\psi)}$  by functional preimage computation:

## Definition 23.

$$\begin{aligned} \chi_{Sat_{A}^{\mathsf{func}}(EX\psi)}(\vec{q},\vec{x},\vec{Z}_{o}) &:= \forall \vec{Z}_{l} \forall Z \left( (\exists \vec{x} \forall \vec{Z}_{o} \chi_{Sat_{A}^{\mathsf{func}}(\psi)}) \big|_{\vec{q} \leftarrow \vec{\delta}(\vec{q},\vec{x},Z,\vec{z}_{l},\vec{z}_{o})} \right) \\ \chi_{Sat_{E}^{\mathsf{func}}(EX\psi)}(\vec{q},\vec{x},\vec{Z}_{o}) &:= \exists \vec{Z}_{l} \exists Z \left( (\exists \vec{x} \exists \vec{Z}_{o} \chi_{Sat_{E}^{\mathsf{func}}(\psi)}) \big|_{\vec{q} \leftarrow \vec{\delta}(\vec{q},\vec{x},Z,\vec{z}_{l},\vec{z}_{o})} \right) \end{aligned}$$

For all other operators  $\chi_{Sat_E^{\text{ppr,incl}}(\varphi)}$  and  $\chi_{Sat_A^{\text{sppr,incl}}(\varphi)}$  are defined just as  $\chi_{Sat_A^{\text{sppr,incl}}(\varphi)}$  and  $\chi_{Sat_A^{\text{sppr,incl}}(\varphi)}$ .

Interestingly, we are able to prove that functional preimage computation with the improved *compose-Z* operator as defined above gives *exactly the same* results as relational preimage computation:

**Theorem 16.** For arbitrary CTL formulas  $\varphi$ :

$$\chi_{Sat_{E}^{\mathsf{func}}(\varphi)} = \chi_{Sat_{E}^{\mathsf{appr},\mathsf{incl}}(\varphi)} and \chi_{Sat_{A}^{\mathsf{func}}(\varphi)} = \chi_{Sat_{A}^{\mathsf{appr},\mathsf{incl}}(\varphi)}$$

*Proof:* The proof is performed by induction on the structure of  $\varphi$ . The main part consists of the equivalence of the relational and functional definitions for the *EX*-operator. This is proven in Appendix D by induction on the number of state bits in the design.

Experiments showing advantages of model checking using the improved compose-Z operator instead of the relational approach are given in Sect. 7.

## 6 EXACT SYMBOLIC MODEL CHECKING FOR BLACK BOXES WITH BOUNDED MEMORY

## 6.1 Motivation

In the last section, we introduced a method to approximate both  $Sat_E^{exact}(\varphi)$ , the set of states, for which there is at least one Black Box replacement so that  $\varphi$  is satisfied, and  $Sat_A^{exact}(\varphi)$ , the set of states, for which  $\varphi$  is satisfied for all Black Box replacements. Experiments in Sect. 7 show that, based on these sets, we are able to provide sound results for falsifying realizability and for proving validity of incomplete designs. Yet, it is not possible to provide a result in every scenario due to the approximate nature of our methods.

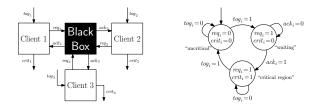

Fig. 10. Incomplete design with one combinational Black Box and the modified design in which the Black Box has been replaced by its truth table variables and a select function.

Fig. 11. Pipelined ALU