#### Open access • Report • DOI:10.2172/4483427

# Synthetic tree model: a formal methodology for fault tree construction — Source link

Jerry Bernard Fussell

Published on: 01 Dec 1972

Topics: Event tree, Fault tree analysis, Reliability (statistics) and Decision tree model

#### Related papers:

- · Computer-aided Synthesis of Fault-trees

- Prep and kitt: computer codes for the automatic evaluation of a fault tree.

- Fault tree synthesis for chemical processes

- Allcuts: a fast, comprehensive fault tree analysis code

- DICOMICS-TWIN: self-adaptive algorithm for minimal cut sets determination from fault trees

In presenting the dissertation as a partial fulfillment of the requirements for an advanced degree from the Georgia Institute of Technology, I agree that the Library of the Institute shall make it available for inspection and circulation in accordance with its regulations governing materials of this type. I agree that permission to copy from, or to publish from, this dissertation may be granted by the professor under whose direction it was written, or, in his absence, by the Dean of the Graduate Division when such copying or publication is solely for scholarly purposes and does not involve potential financial gain. It is understood that any copying from, or publication of, this dissertation which involves potential financial gain will not be allowed without written permission.

7/25/68

#### SYNTHETIC TREE MODEL

.

#### A FORMAL METHODOLOGY FOR FAULT TREE CONSTRUCTION

#### A THESIS

#### Presented to

The Faculty of the Division of Graduate

Studies and Research

Ву

Jerry Bernard Fussell

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

in the School of Nuclear Engineering

### Georgia Institute of Technology

December, 1972

## SYNTHETIC TREE MODEL

A FORMAL METHODOLOGY FOR FAULT TREE CONSTRUCTION

#### FOREWORD

I have enjoyed preparing this dissertation. The technical aspects were exciting but more important, the people involved, each in a special way, provided me an atmosphere in which to work that allowed me to use all my abilities as effectively as I could. Dr. C. J. Roberts began making this thesis a reality when he arranged for my being able to retain my financial aid while studying under Dr. W. E. Vesely at the Aerojet Nuclear Company in Idaho during the summer of 1971. Dr. Roberts did much to provide an environment that gave me, and other students, the freedom to learn. If I could repeat my dissertation experience, I would again choose Dr. J. D. Clement as my advisor. Dr. Clement always found time to help me and showed genuine concern. His guidance and patience were most valuable.

Dr. W. E. Vesely receives special thanks for the time and effort he gave so generously. Dr. Vesely introduced me to the dissertation topic and his continued enthusiasm kept my spirits high. His technical assistance was invaluable. I would also like to thank Dr. J. R. Penland of the Babcock and Wilcox Company for helping me get fault tree analysis in proper perspective and for his willingness to lend a hand when I needed help.

Every faculty member of the School of Nuclear Engineering here at the Georgia Institute of Technology has my thanks. Each gave me a great deal to appreciate. Additional gratitude is extended to members of my

reading committee, Dr. G. G. Eichholz, Dr. W. W. Graham, III, and Dr. W. W. Hines, for their most valuable professional support.

To list my fellow students to whom I am indebted would be a much too ambitious task. Special consideration is given to the individuals in the 1972 summer quarter NE 707-F class, Reliability Analysis of Nuclear Reactor Systems. These students questioned and finally accepted Synthetic Tree Model as a valid, formal means of fault tree construction. They had a large influence concerning the manner in which the model is presented in this dissertation.

Recognition is given to Mrs. Lydia Geeslin, a truly professional typist, for producing a handsome thesis from a very rough looking rough draft.

My love for Nancy and our son, Tye, has leveled the rough spots I experienced during this effort. It seems useless to try to select words to express my sincere appreciation of Nancy's being with me.

iii

# TABLE OF CONTENTS

| FOREWO | RD.   | Page                                                  |

|--------|-------|-------------------------------------------------------|

| LIST O | F TAB | LESvii                                                |

| LIST O | F ILL | USTRATIONS                                            |

| SUMMAR | ¥     | •••••••••••••••••••••••••••••••••******               |

| Chapte | r     |                                                       |

| I.     | INTR  | ODUCTION                                              |

|        | 1.1   | Background                                            |

|        | 1.2   | Objectives                                            |

|        |       | Importance of the Study                               |

|        |       | Limitations                                           |

|        | 1.5   | Method of Approach                                    |

| II.    | CONC  | EPTS OF SYNTHETIC TREE MODEL                          |

|        | 2.1   | Basic Definitions                                     |

|        | 2.2   | An Introduction to the Failure Transfer<br>Functions  |

|        | 2.3   | Ordered Fault Events                                  |

|        | 2.4   | Boundary Conditions                                   |

|        |       | Class of Third Order Fault Events                     |

|        | 2.6   | Category of Second Order Fault Events                 |

| III.   | FAUL  | T TREE TERMINOLOGY                                    |

|        | 3.1   | Fault Tree Symbols                                    |

|        |       | The OR Gate                                           |

|        | 3.3   | The AND Gate                                          |

|        | 3.4   | Cut Sets                                              |

| IV.    | CHAR  | ACTERISTIC FACTORS OF SYNTHETIC TREE MODEL            |

|        | 4.1   | Particulars of the Failure Transfer<br>Functions      |

|        | 4.2   | Examples of Determining Failure Transfer<br>Functions |

iv

## TABLE OF CONTENTS (Continued)

| Chaster |                                                                                                                                 | Daga |

|---------|---------------------------------------------------------------------------------------------------------------------------------|------|

| Chapter |                                                                                                                                 | Page |

|         | 4.3 Particulars of the Component Coalition<br>Scheme                                                                            |      |

|         | 4.4 Particulars of the Category of the Second<br>Order Fault Event                                                              |      |

|         | 4.5 Particulars of the Class of Third Order<br>Fault Events                                                                     |      |

|         | 4.6 Particulars of the Inter-Correlation Between<br>Fault Events and Boundary Conditions                                        |      |

| ۷.      | FAULT TREE DEVELOPMENT STRATEGY OF SYNTHETIC<br>TREE MODEL                                                                      | 55   |

|         | 5.1 Catalogued First Order Fault Events                                                                                         |      |

|         | 5.2 How to Use Boundary Conditions                                                                                              |      |

|         | 5.3 How to Develop a Second Order Fault Event                                                                                   |      |

|         | 5.4 How to Develop Third Order Fault Events                                                                                     |      |

|         | 5.5 How to Develop Fourth Order Fault Events                                                                                    |      |

|         | 5.6 Final Editing Concerns                                                                                                      |      |

|         | ste kanda -aserud teoneotus                                                                                                     |      |

| VI.     | MANUAL FAULT TREE CONSTRUCTION USING SYNTHETIC                                                                                  |      |

|         | TREE MODEL                                                                                                                      | 62   |

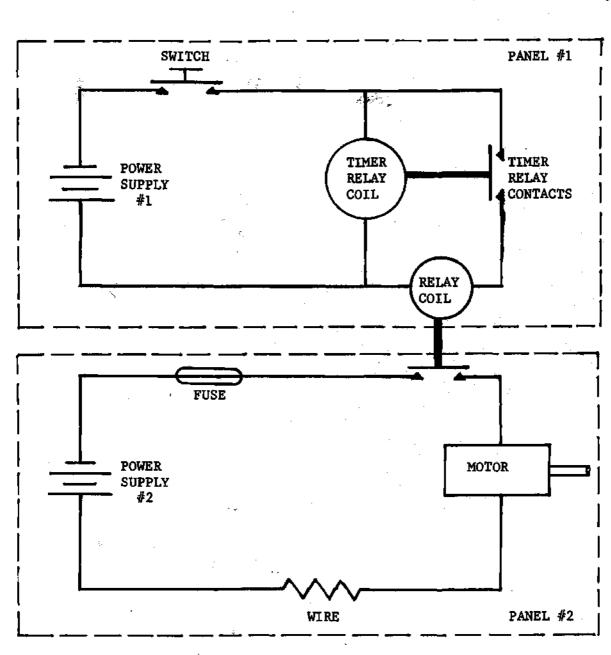

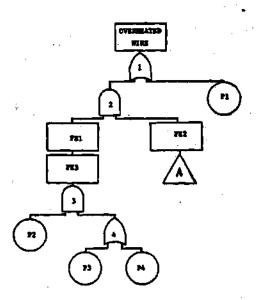

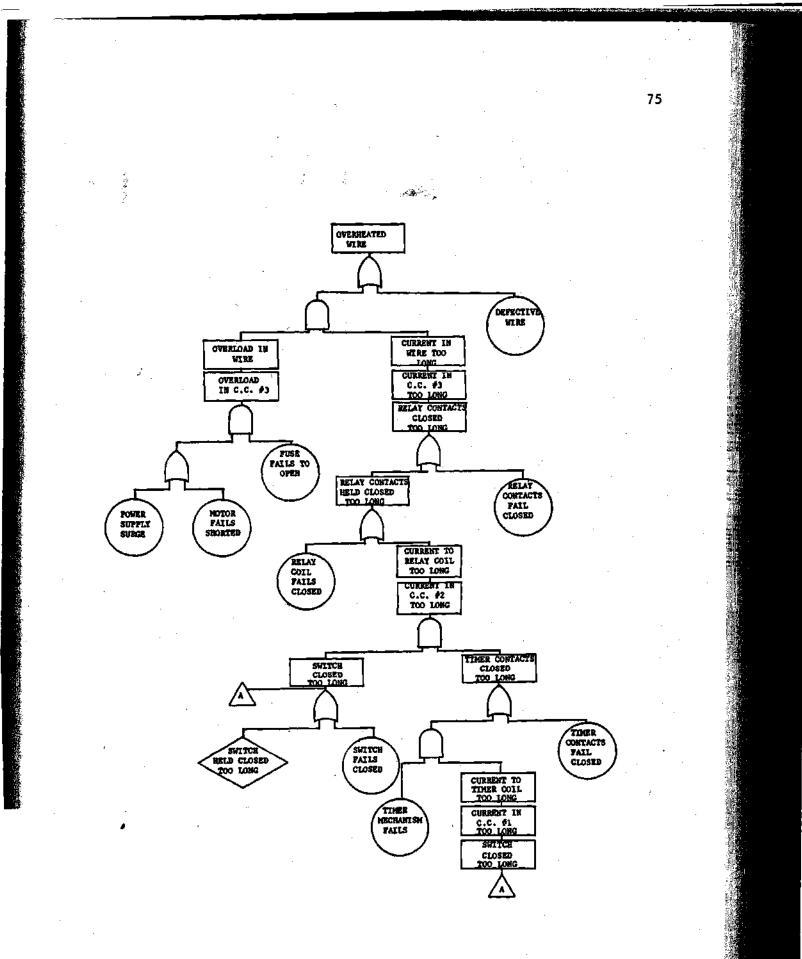

|         | 6.1 Development of the Third Order Fault Event,<br>Overload in Wire                                                             | -    |

|         | 6.2 Development of the Second Order Fault<br>Event, Overload in Component Coalition #3                                          | •    |

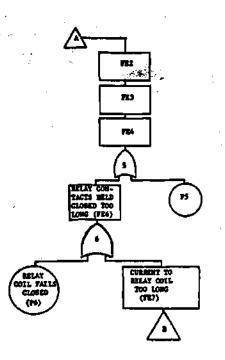

|         | 6.3 Development of the Third Order Fault Event,<br>Current in Wire Too Long                                                     |      |

| •       | 6.4 Development of the Second Order Fault Event,<br>Current in Component Coalition #3 Too Long                                  |      |

|         | 6.5 Development of the Fourth Order Fault Event,<br>Relay Contacts Held Closed Too Long                                         |      |

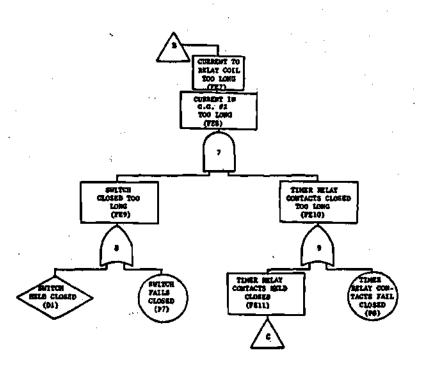

|         | 6.6 Development of the Third Order Fault Event,<br>Current to Relay Coil Too Long                                               |      |

|         | 6.7 Development of the Second Order Fault Event,<br>Current in Component Coalition #2 Too Long                                  |      |

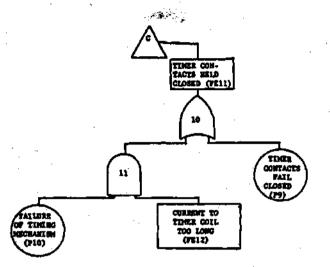

|         | 6.8 Development of the Fourth Order Fault Event,<br>Input to Timer Relay Coil Contacts Causes<br>Contacts to be Closed Too Long | ·    |

|         | 6.9 Development of the Second Order Fault Event,<br>Current Applied Too Long in Component<br>Coalition #1                       |      |

|         |                                                                                                                                 |      |

## TABLE OF CONTENTS (Concluded)

| Chapter          | C C C C C C C C C C C C C C C C C C C                                                    | Page  |

|------------------|------------------------------------------------------------------------------------------|-------|

| VII.             | A COMPLETE, AUTOMATED PROBABILISTIC RELIABILITY<br>PREDICTION USING SYNTHETIC TREE MODEL | . 76  |

|                  | 7.1 Fault Tree Evaluation<br>7.2 Pressure Tank System Example                            |       |

| VIII.            | CONCLUSIONS AND RECOMMENDATIONS                                                          | . 98  |

| A <b>P</b> PENDI | ICES                                                                                     | . 102 |

| Α.               | EXAMPLE OF LIBRARY DATA OF SYNTHETIC TREE MODEL                                          | . 103 |

| в.               | BASIC DESCRIPTION OF DRAFT                                                               | . 115 |

|                  | Input<br>Output<br>Routine                                                               |       |

| c.               | EXAMPLE OF FAULT TREE CONSTRUCTION FOR A REACTOR<br>SCRAM SYSTEM USING DRAFT             | . 123 |

| BIBLIO           | GRAPHY                                                                                   | . 156 |

| VITA .           |                                                                                          | . 159 |

vi

## LIST OF TABLES

| Table |                                                                                            | Page         |

|-------|--------------------------------------------------------------------------------------------|--------------|

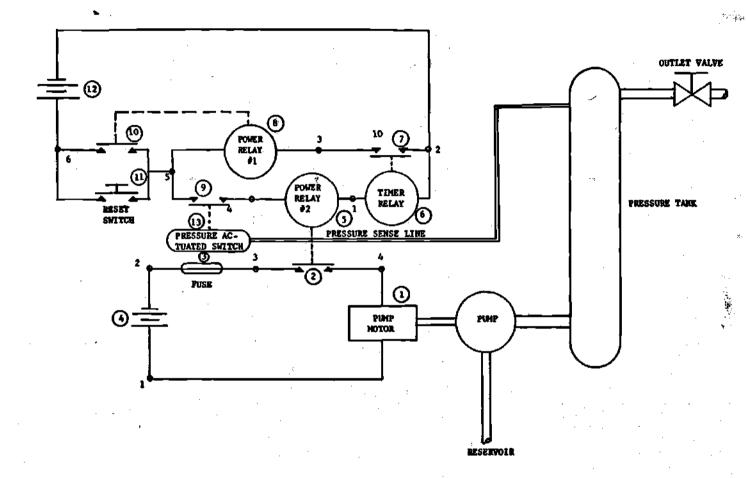

| 1.    | DRAFT Input Edit for Pressure Tank System                                                  | 87           |

| 2.    | Component Coalitions for Pressure Tank System                                              | 88           |

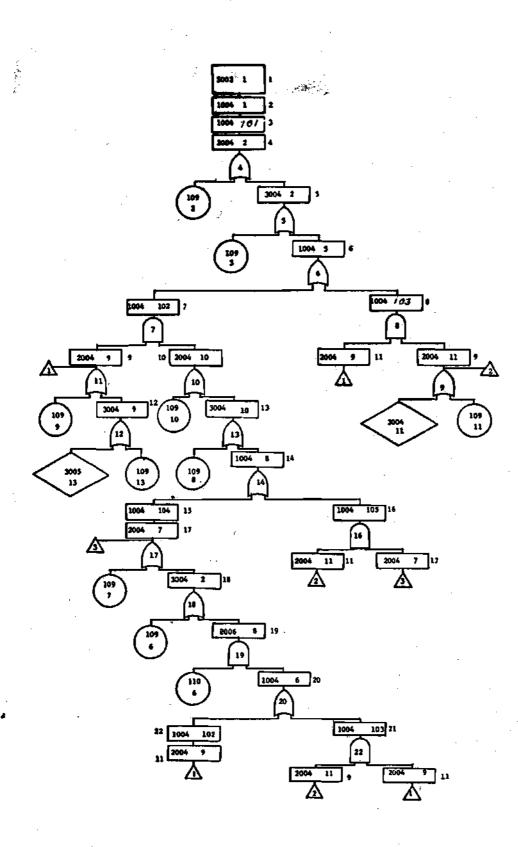

| 3.    | Fault Tree Output from DRAFT for Pressure Tank<br>System                                   | 89           |

| 4.    | Minimal Cut Sets for Pressure Tank System                                                  | 93           |

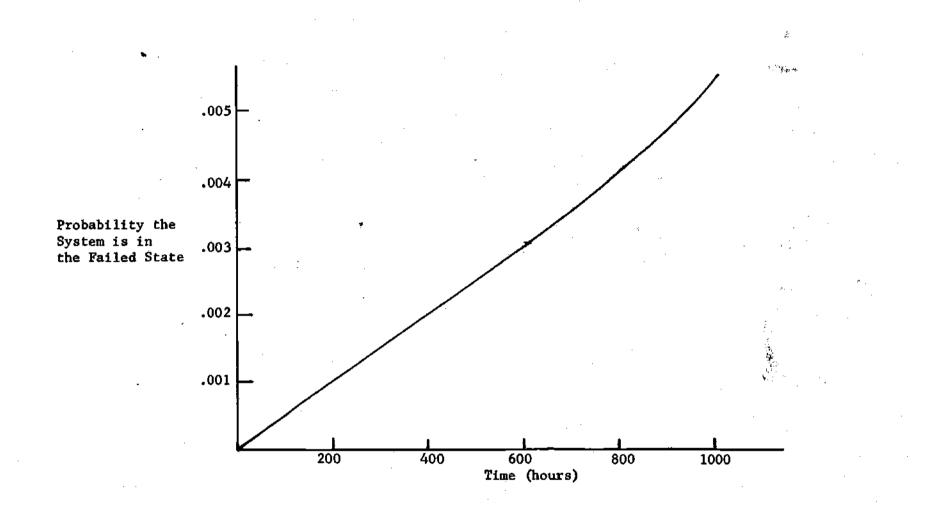

| 5.    | Failure Intensities for Components of Pressure<br>Tank System                              | 96           |

| 6.    | Class of the Third Order Fault Event Library<br>Data                                       | 111          |

| 7.    | Category of the Second Order Fault Event<br>Library Data                                   | 111.         |

| 8.    | Inter-Correlation Between Second Order Fault<br>Events and Boundary Condition Library Data | 111          |

| 9.    | Inter-Correlation Between Second Order Fault<br>Events and Boundary Condition Library Data | 112          |

| 10.   | Inter-Correlation Between Second Order Fault<br>Events and Boundary Condition Library Data | 113          |

| 11.   | Example Input Edit for DRAFT                                                               | 117          |

| 12.   | Decoding List for Incident Identification                                                  | 118          |

| 13.   | Example of Component Coalition Output from DRAFT                                           | 120          |

| 14.   | Example of Fault Tree Output from DRAFT                                                    | 121          |

| 15.   | DRAFT Input Edit for Reactor Scram System                                                  | <b>127</b> - |

| 16.   | Component Coalitions for Reactor Scram System                                              | 1 <b>29</b>  |

| 17.   | Fault Tree Output from DRAFT for Reactor Scram<br>System                                   | 130          |

**vii**

# LIST OF ILLUSTRATIONS

| Figure |                                                                                     |        |   |    |   |     |   |   |   | Page |

|--------|-------------------------------------------------------------------------------------|--------|---|----|---|-----|---|---|---|------|

| 1.     | Concept of the Failure Transfer Function<br>of Synthetic Tree Model                 |        | • | •  | • | .•  | • | • | • | 16   |

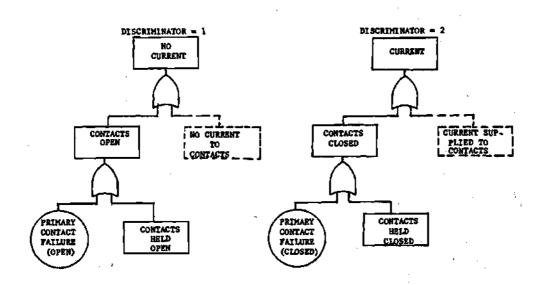

| 2.     | Example of Failure Transfer Function for<br>Electrical Contacts                     | •      | • | •  | • | •   | • | • | • | 17   |

| 3.     | Boolean Logic Representation of the Failure<br>Transfer Functions Shown in Figure 2 | •      | • | •  | • | •   | • | • | • | 17   |

| 4.     | Fault Tree Logic Symbols                                                            | •      | ٠ | •  | • | •   | • | ٠ | • | 24   |

| 5.     | Fault Tree Event Symbols                                                            | •      | • | •  | ٠ | •   | • | • | • | 25   |

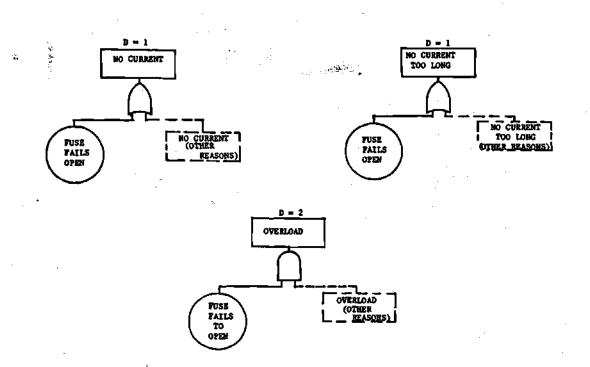

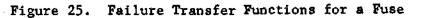

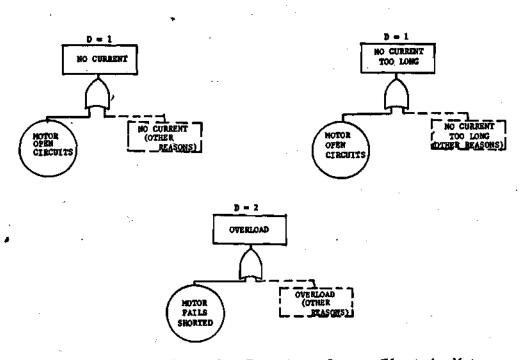

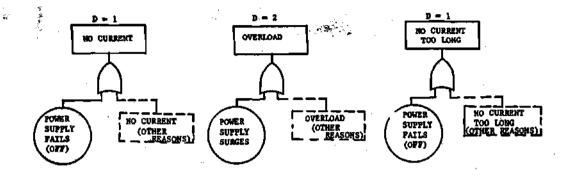

| 6.     | Failure Transfer Functions for a Fuse in<br>Boolean Logic Notation                  | •      | • | •  | • | •   | • | • | • | 44   |

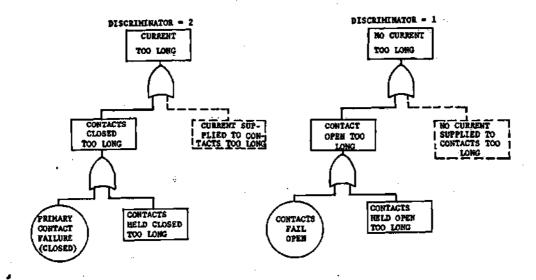

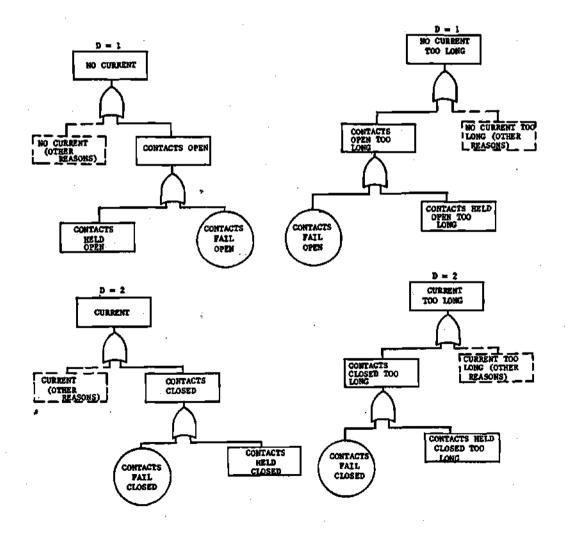

| 7.     | Failure Transfer Functions for Contacts in<br>Boolean Logic Notation                | •      | • | •  | • | •   | • | • | • | 46   |

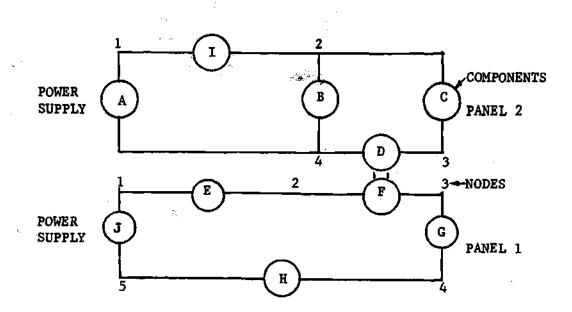

| 8.     | Schematic for Manual Fault Tree Construction<br>Using Synthetic Tree Model          | •      | • | •  | • | •   | • | • | • | 63   |

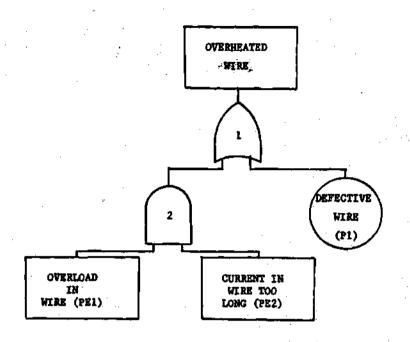

| 9.     | Sufficient Development of the First Order Faul<br>Event                             |        | • | •  | • | •   | • | • | • | 65   |

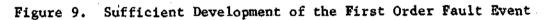

| 10.    | Development Stage Number 1 of Sample Fault Tre<br>Construction                      |        | • | •  | • | •   | • | • | • | 65   |

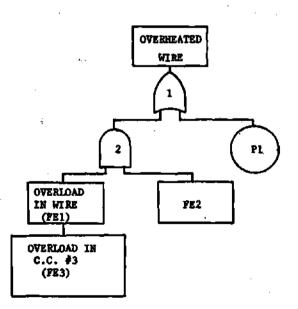

| 11.    | Development Stage Number 2 of Sample Fault Tre<br>Construction                      |        | • | ٠  | • | •   | • | • | • | 67   |

| 12.    | Development Stage Number 3 of Sample Fault Tre<br>Construction                      |        | • | •. | • | •   | • | • | • | 67   |

| 13.    | Development Stage Number 4 of Sample Fault Tre<br>Construction                      |        | • | •  | • | ×.  | • | • | • | 69   |

| 14.    | Development Stage Number 5 of Sample Fault Tre<br>Construction                      | e<br>• | • |    | • | ٠   | • | • | • | 69   |

| 15.    | Development Stage Number 6 of Sample Fault Tre<br>Construction                      |        | • | •  | • | • . | • | • | • | 71   |

## LIST OF ILLUSTRATIONS (Continued)

| Figure |                                                                 | Doeo       |

|--------|-----------------------------------------------------------------|------------|

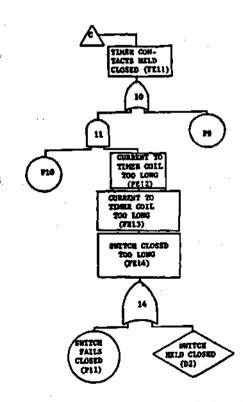

| l6.    | Development Stage Number 7 of Sample Fault Tree<br>Construction | Page<br>71 |

| 17.    | Development Stage Number 8 of Sample Fault Tree<br>Construction | 73         |

| 18.    | Development Stage Number 9 of Sample Fault Tree<br>Construction | 73         |

| 19.    | Complete Fault Tree for Sample System                           | 75         |

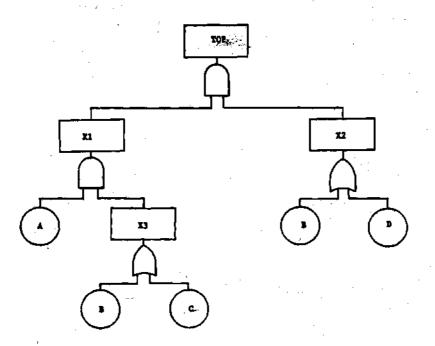

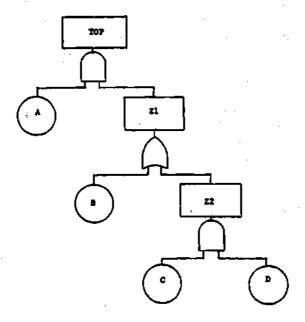

| 20.    | Sample Fault Tree for Probability Evaluation                    | 80         |

| 21.    | Boolean Equivalent of Sample Fault Tree Shown in Figure 3       | 80         |

| 22.    | Schematic of Pressure Tank System                               | 85         |

| 23.    | Fault Tree for Pressure Tank System                             | 92         |

| 24.    | System Failed Probability vs. Time for Pressure<br>Tank System  | 97         |

| 25.    | Failure Transfer Functions for a Fuse                           | 105        |

| 26.    | Failure Transfer Functions for an Electric<br>Motor             | 105        |

| 27.    | Failure Transfer Functions for a Power Supply • • • • • • • •   | 106        |

| 28.    | Failure Transfer Functions for Contacts                         | 106        |

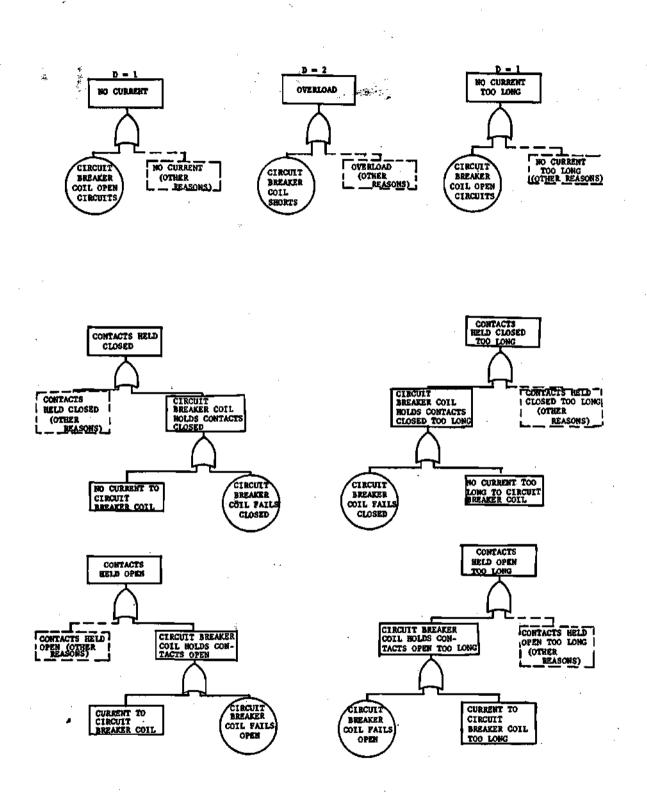

| 29.    | Failure Transfer Functions for a Circuit<br>Breaker Coil        | 107        |

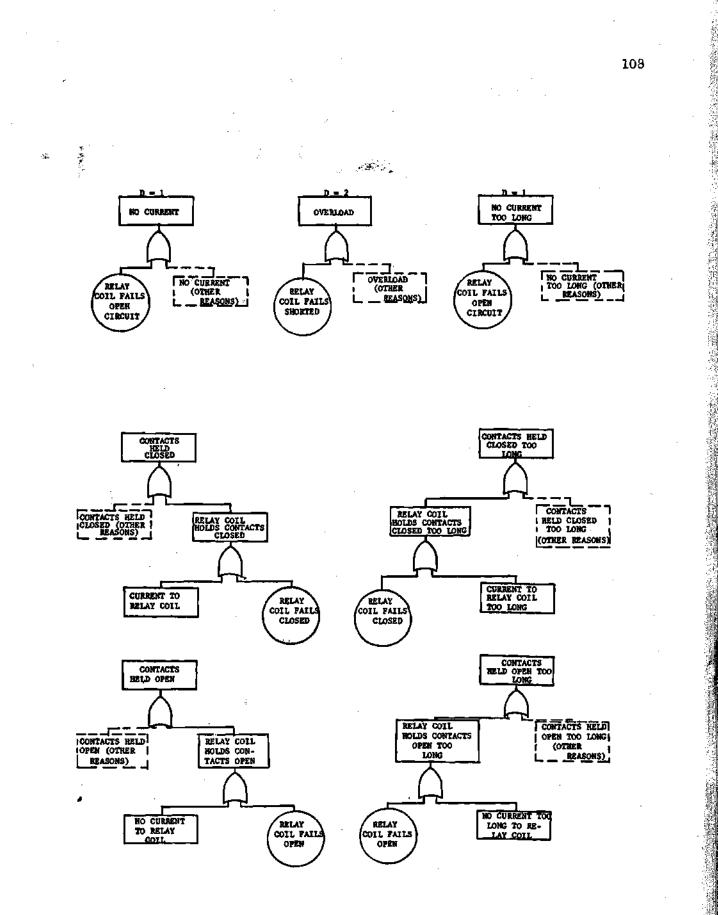

| 30.    | Failure Transfer Functions for a Relay Coil                     | 108        |

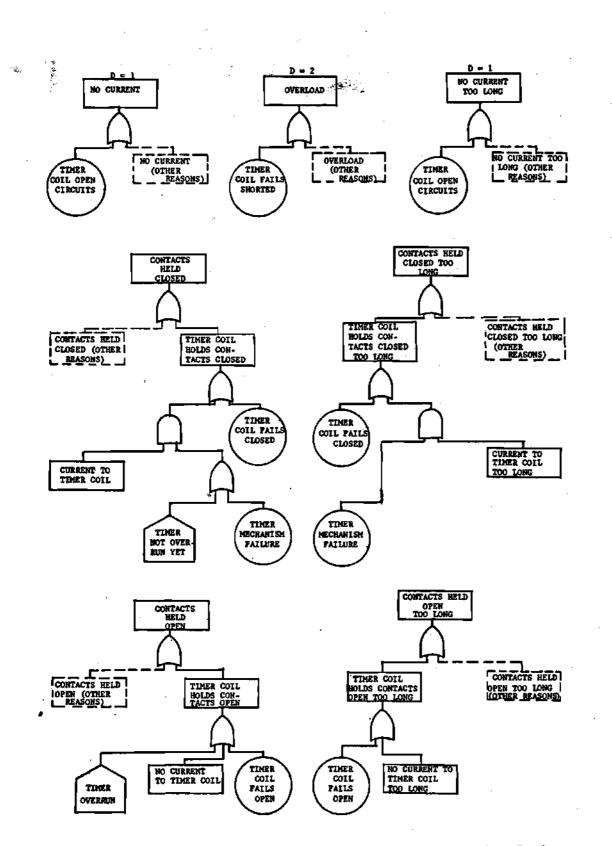

|        | Failure Transfer Functions for a Timer Relay<br>Coil            | 109        |

| 32.    | Failure Transfer Functions for Wiring                           | 110        |

| 33.    | Failure Transfer Functions for a Pressure<br>Switch             | 110        |

のためのないので、「ないではないないない」であるというないで、「ないない」ではない

## LIST OF ILLUSTRATIONS (Concluded)

ж

| Figure | the state of the | Page        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

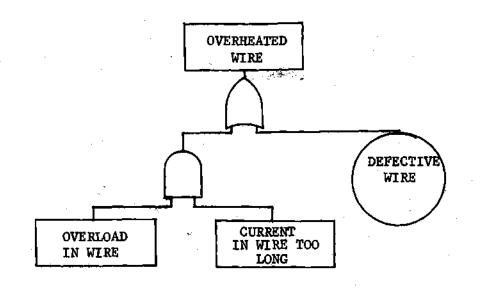

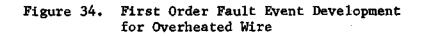

| 34.    | First Order Fault Event Development for<br>Overheated Wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 114         |

| 35.    | First Order Fault Event Development for<br>Motor Operating Too Long                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 114         |

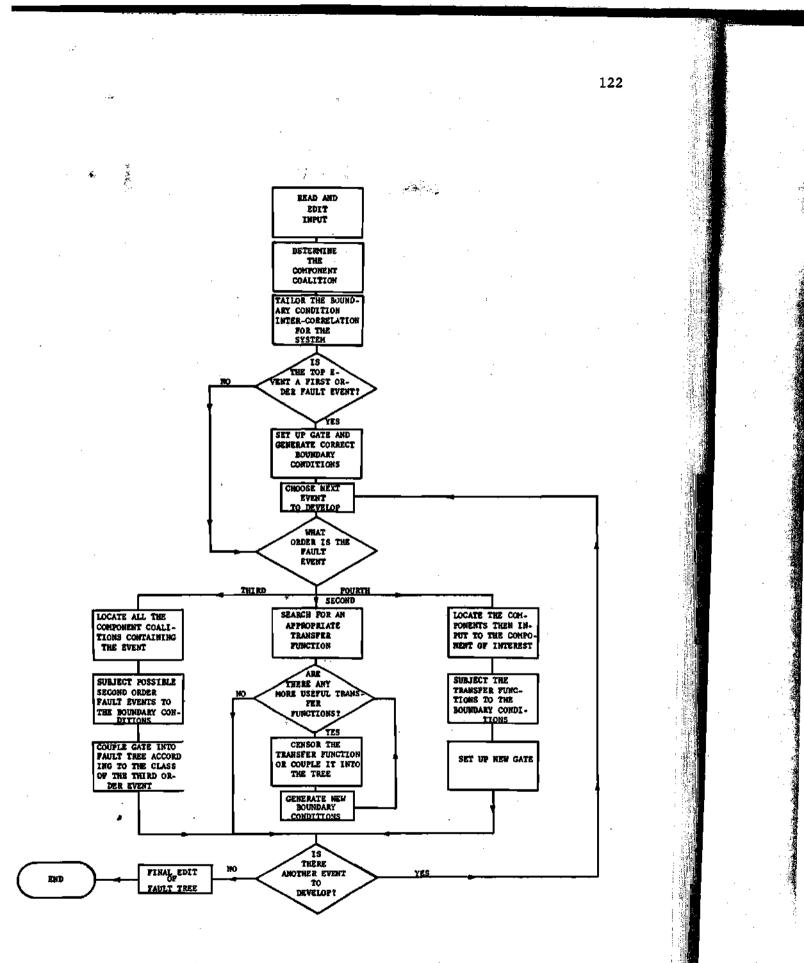

| 36.    | Diagram of Procedure of DRAFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 <b>22</b> |

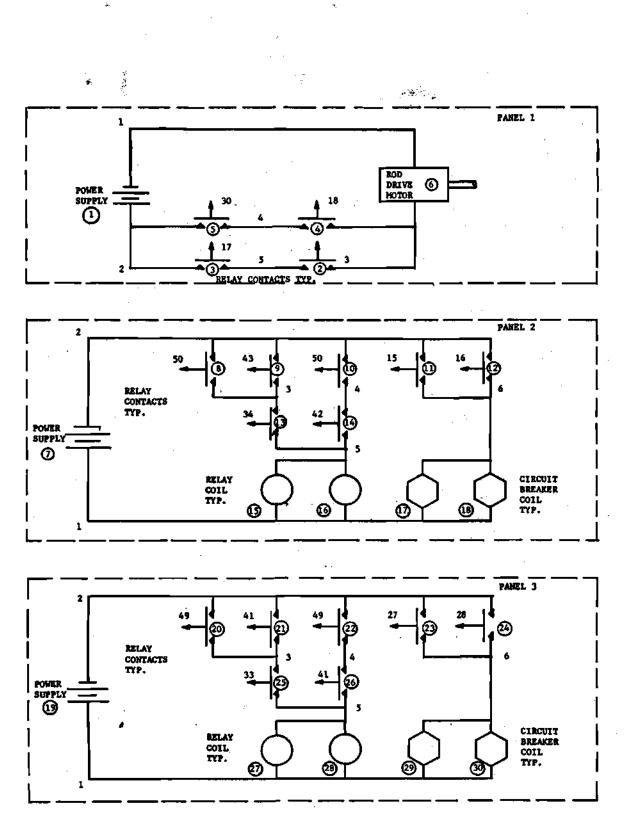

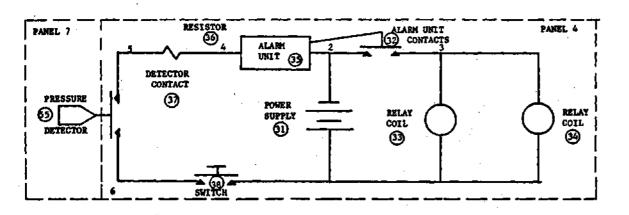

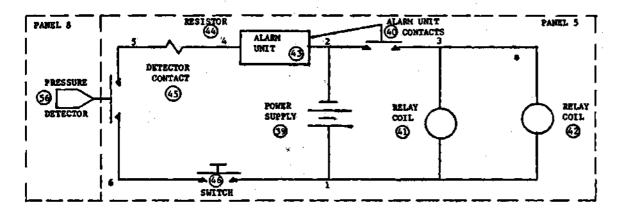

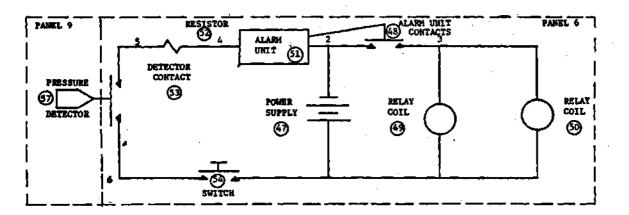

| 37.    | Schematic of Reactor Scram System Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 124         |

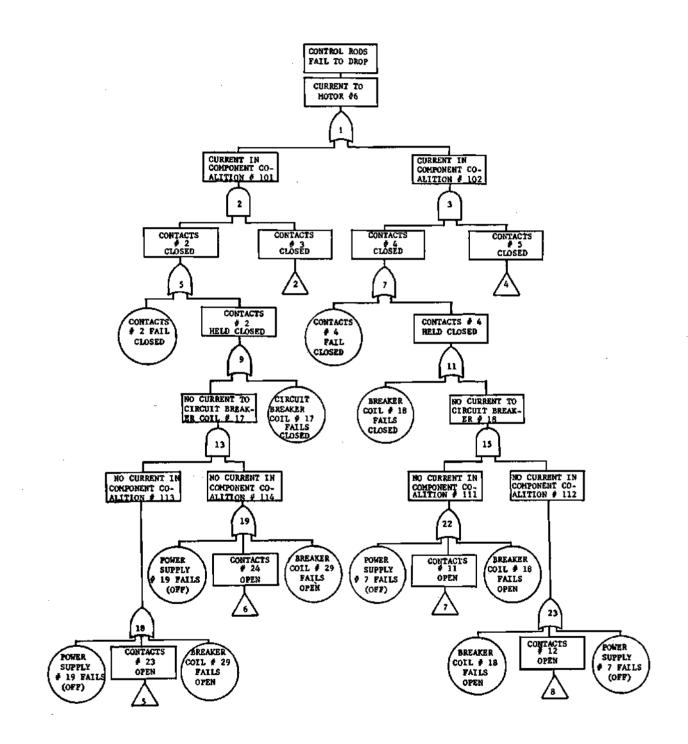

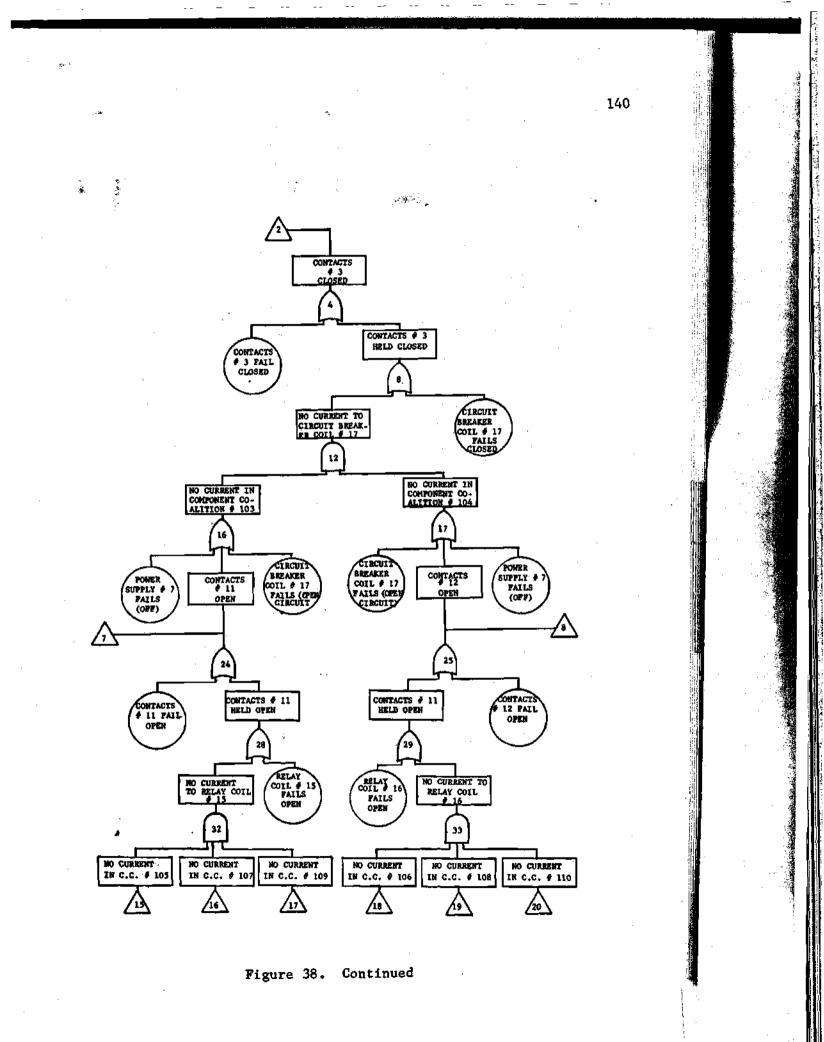

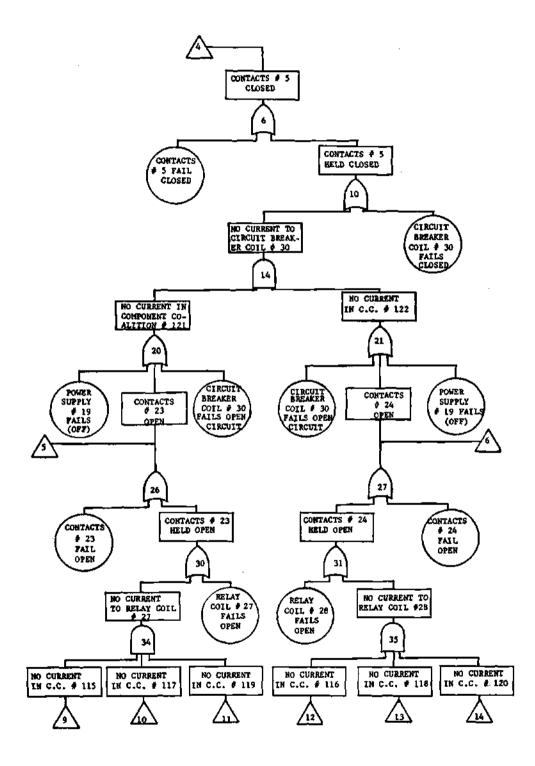

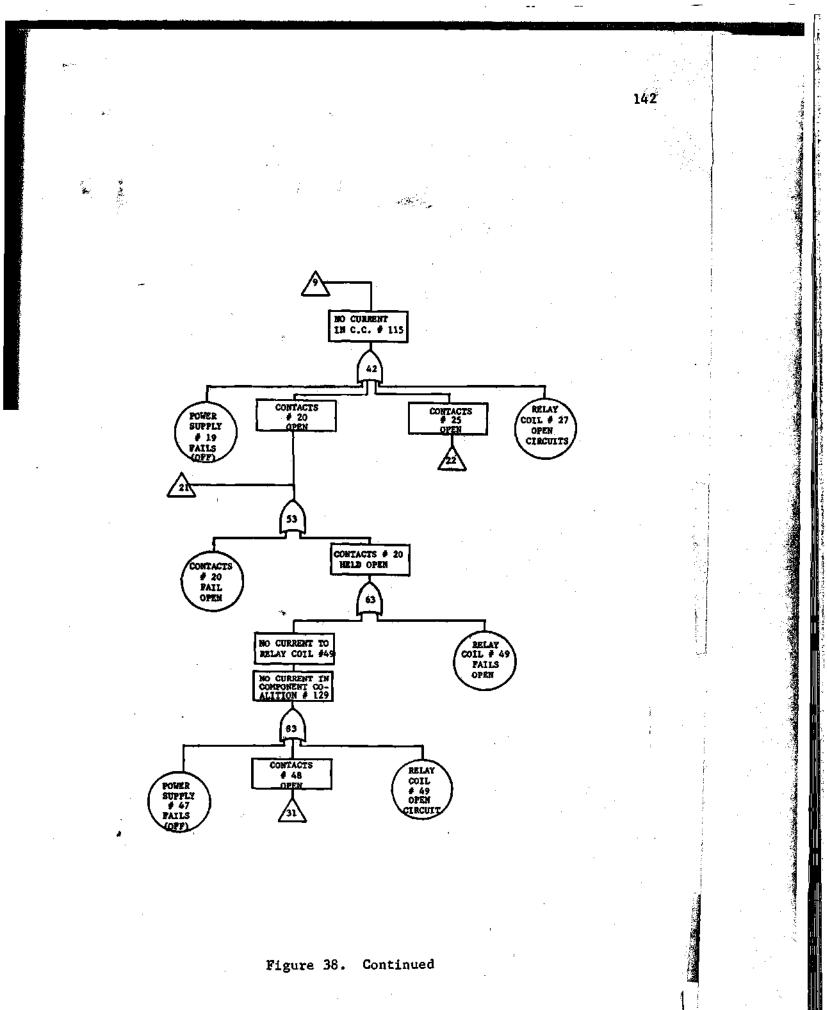

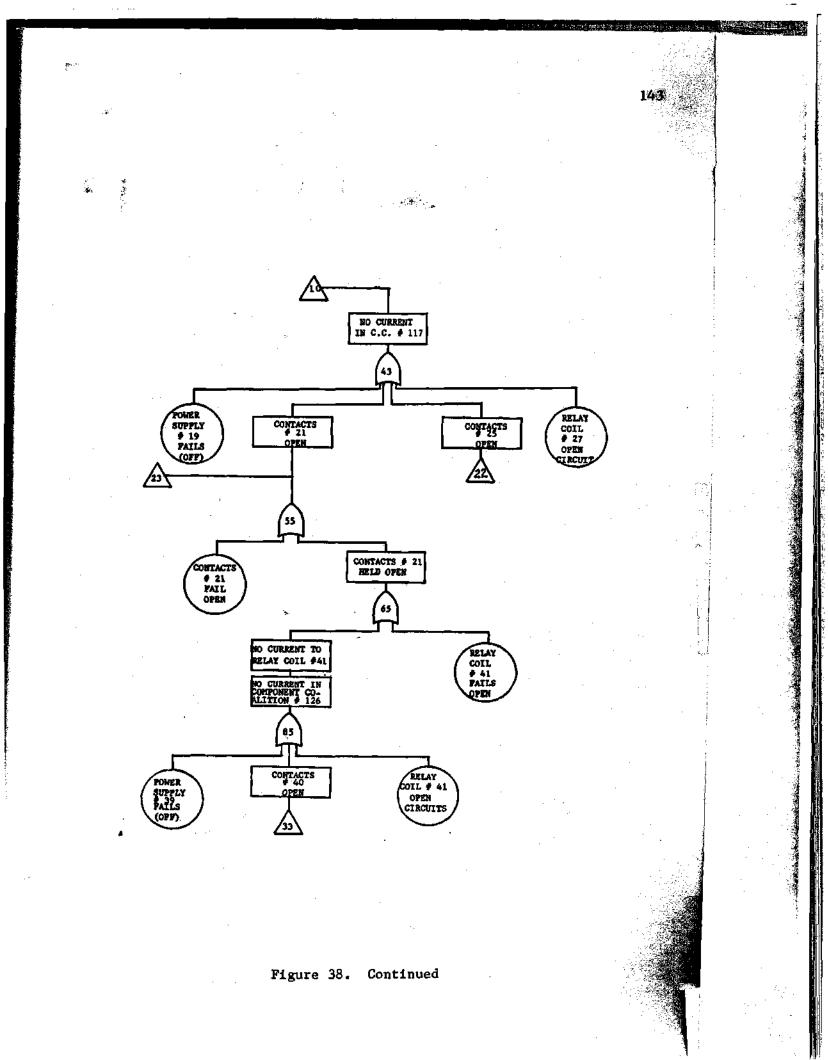

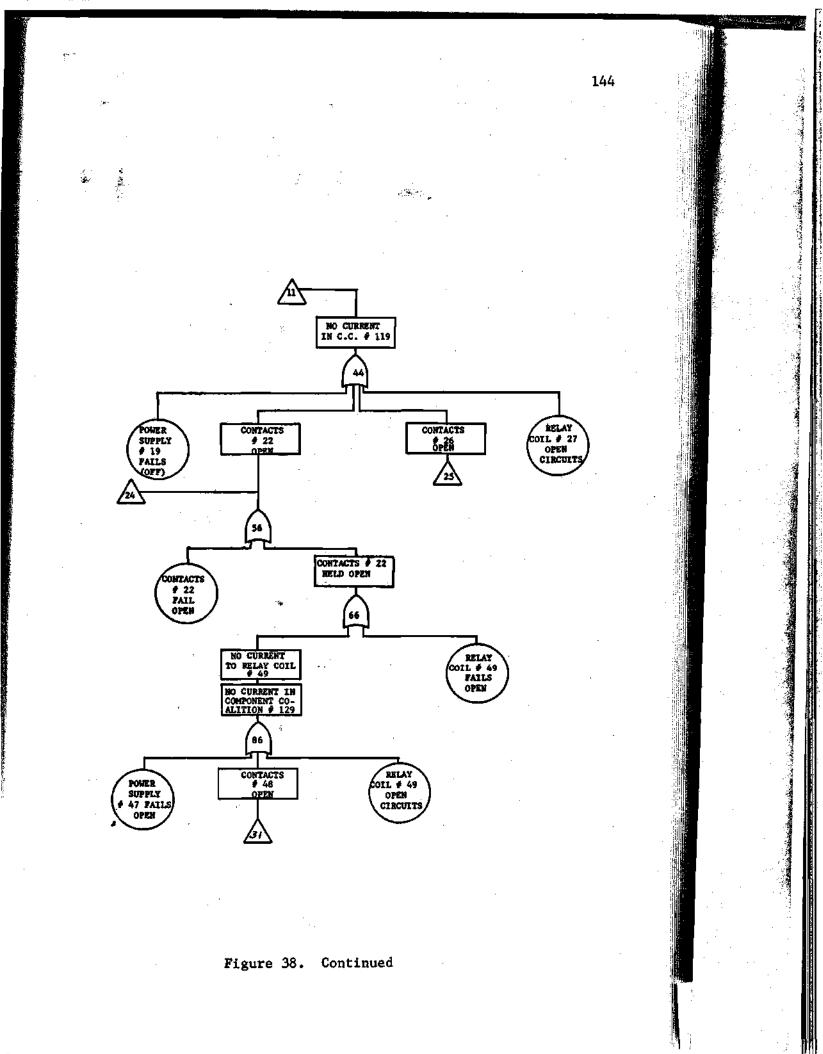

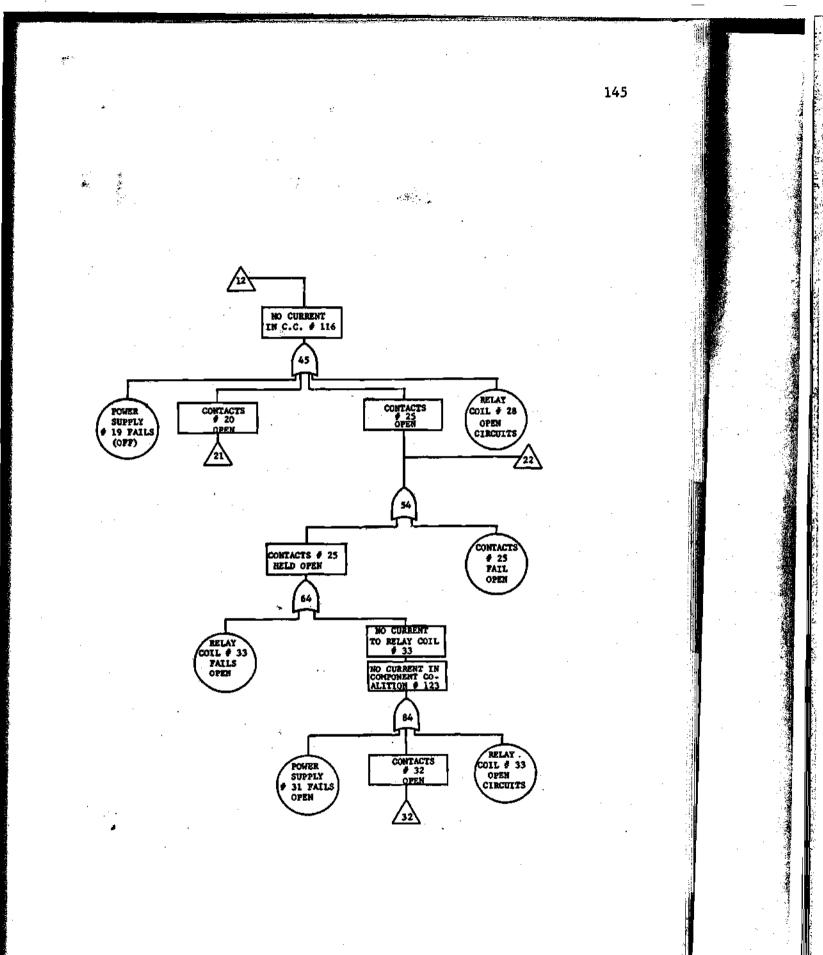

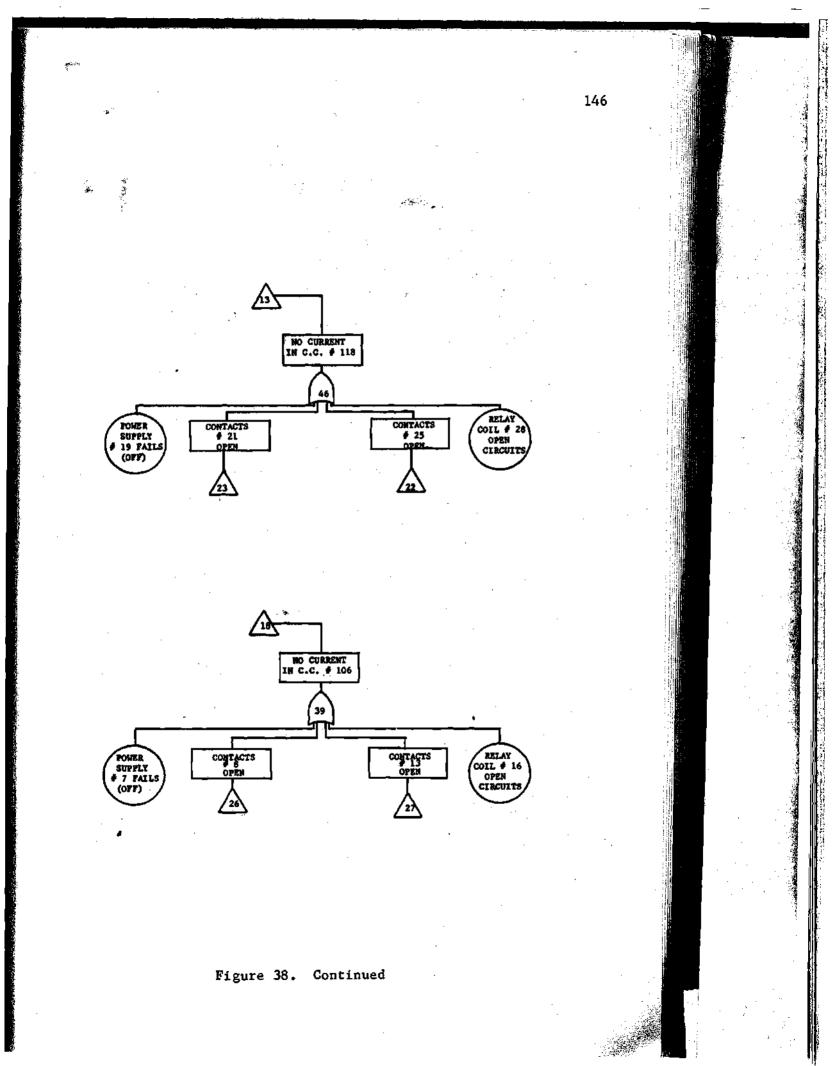

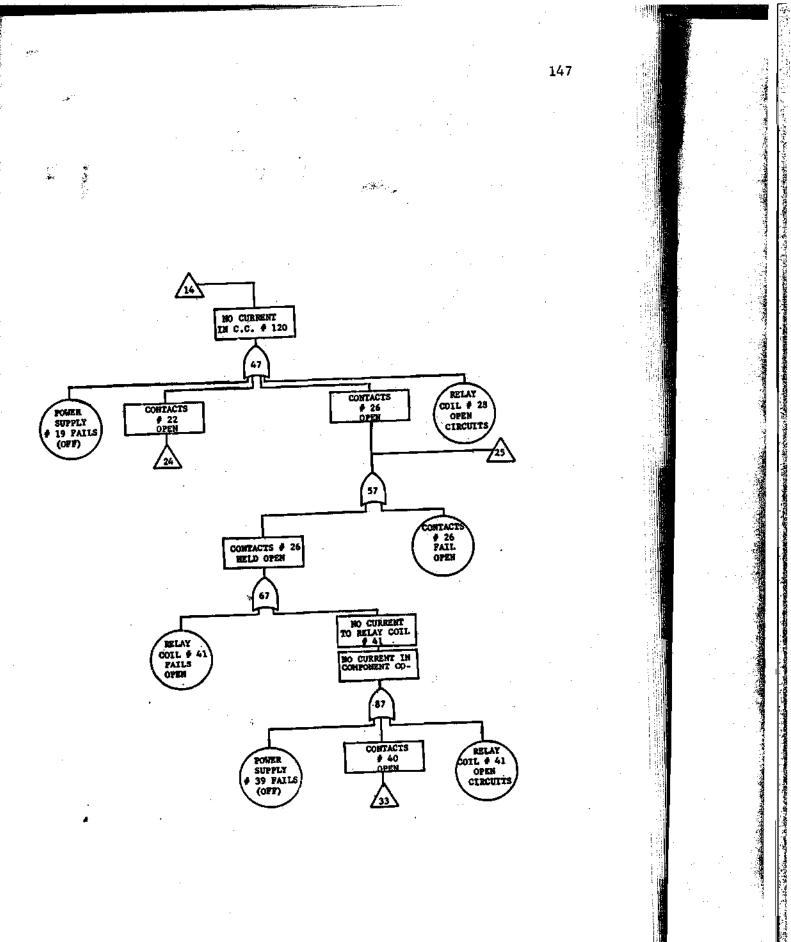

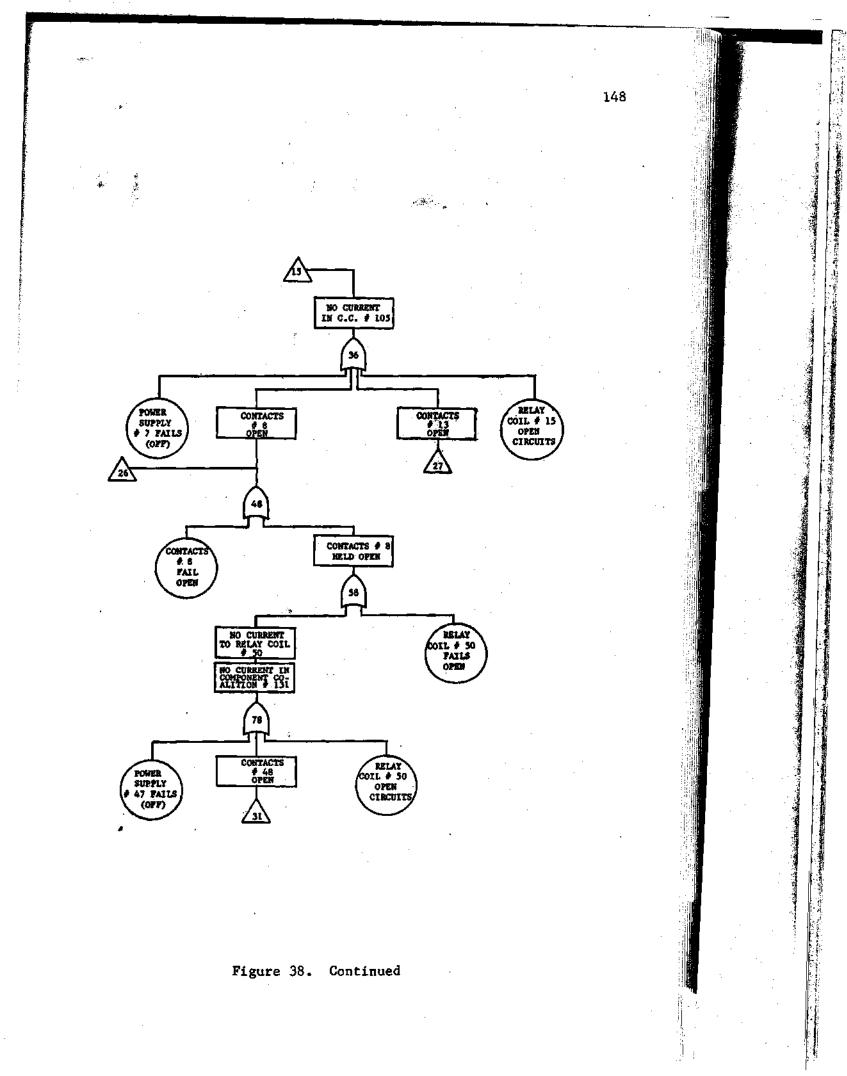

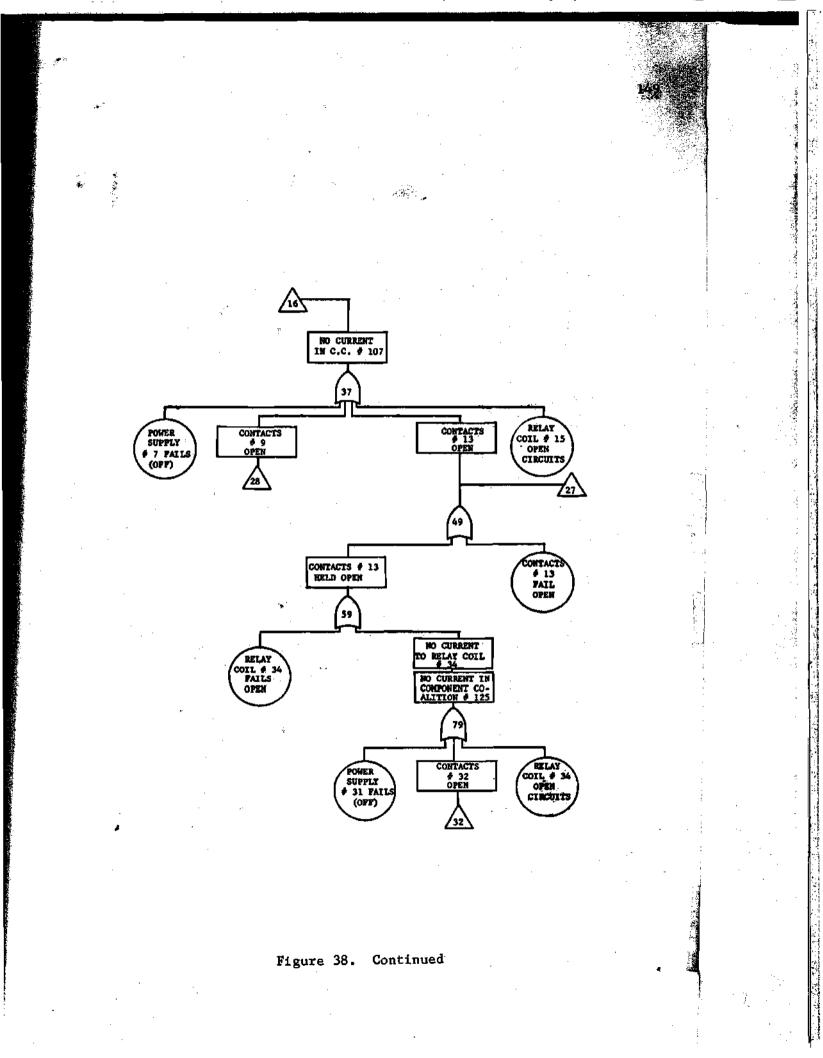

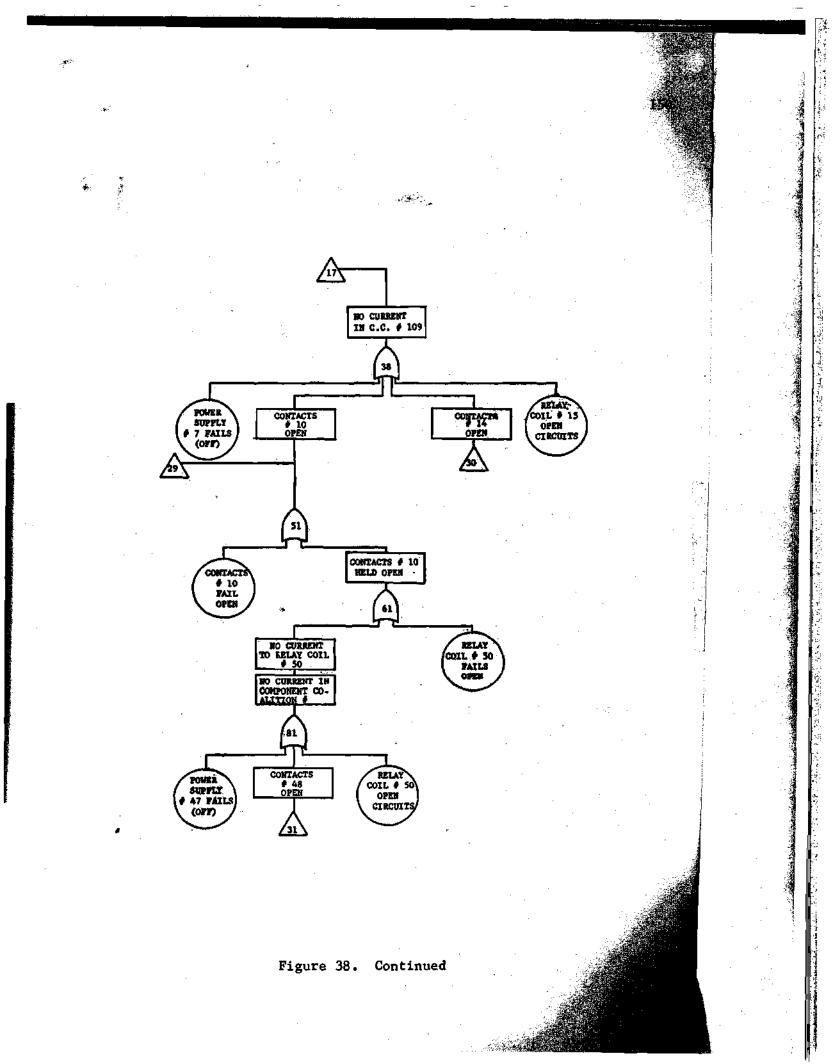

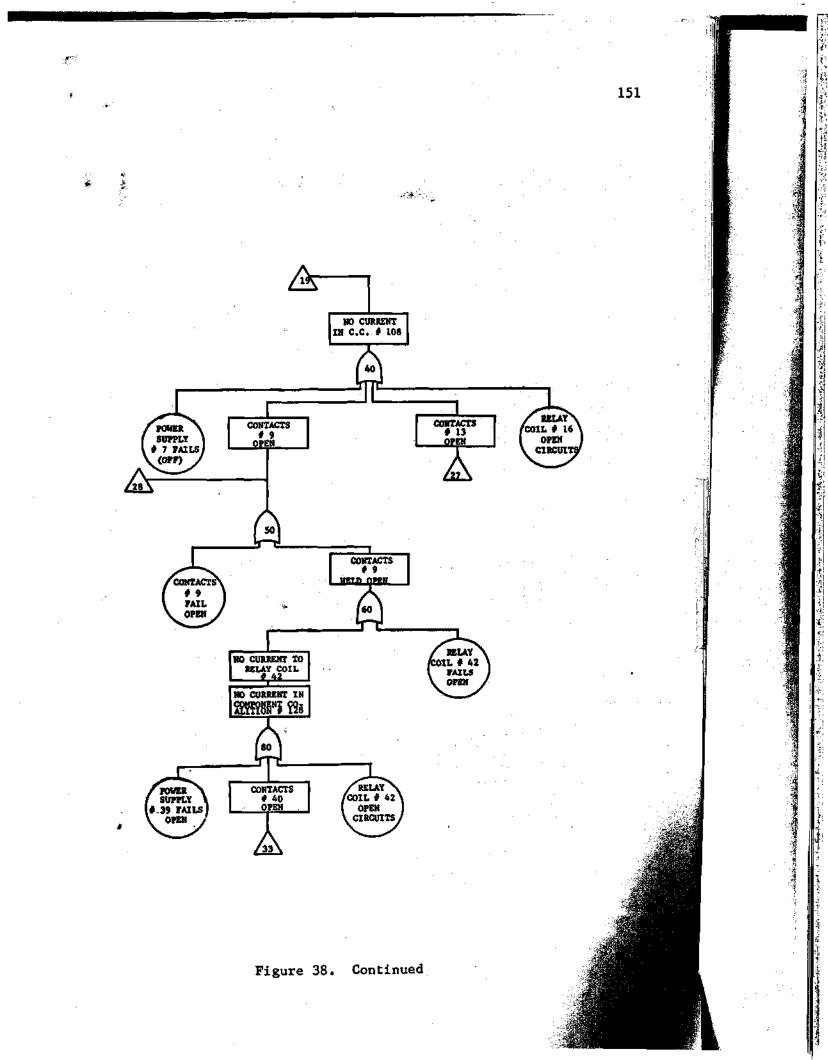

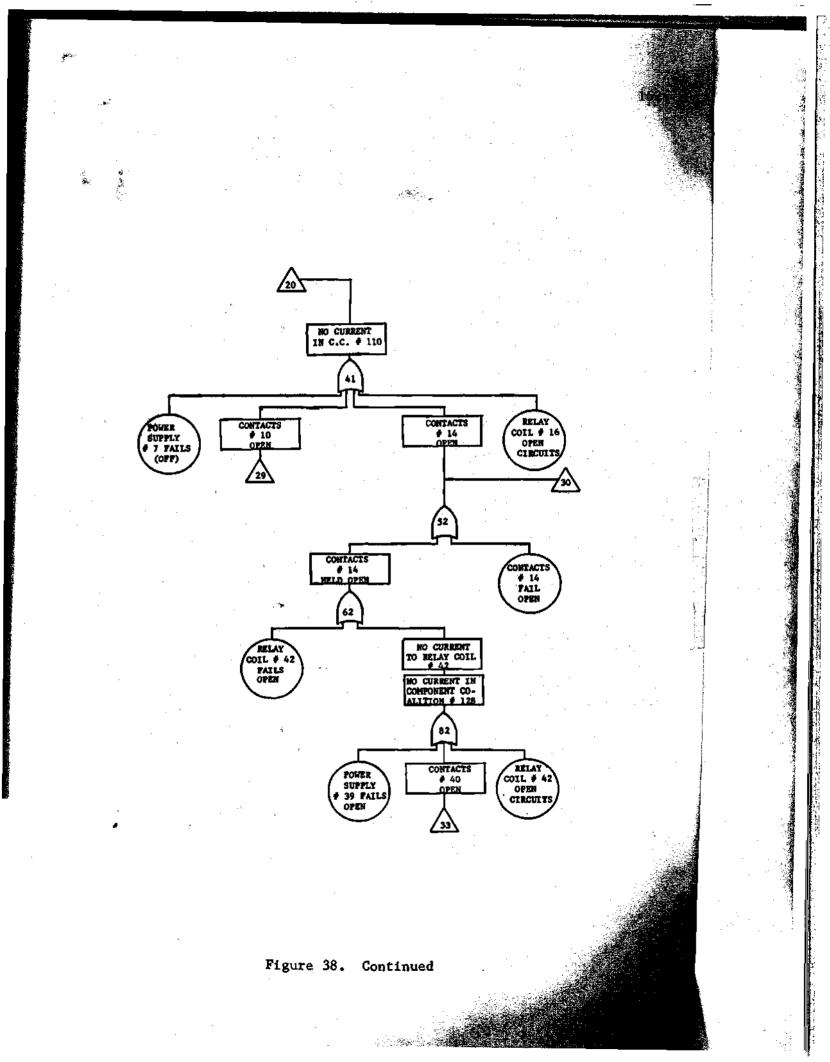

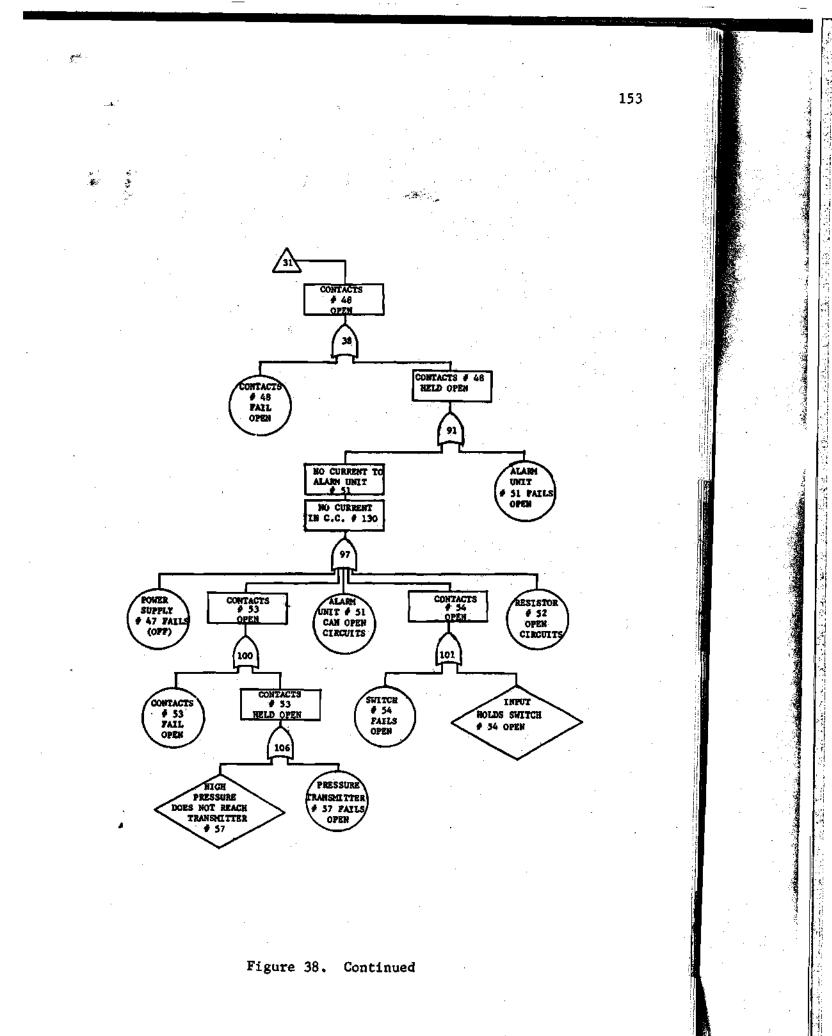

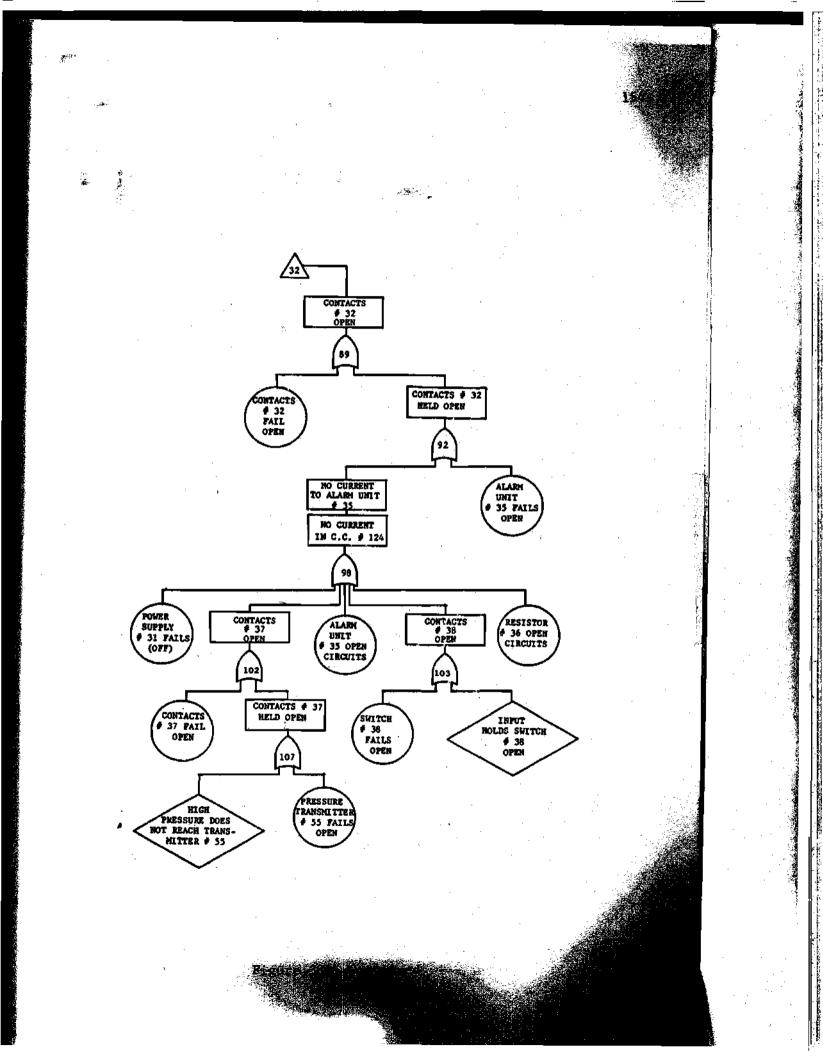

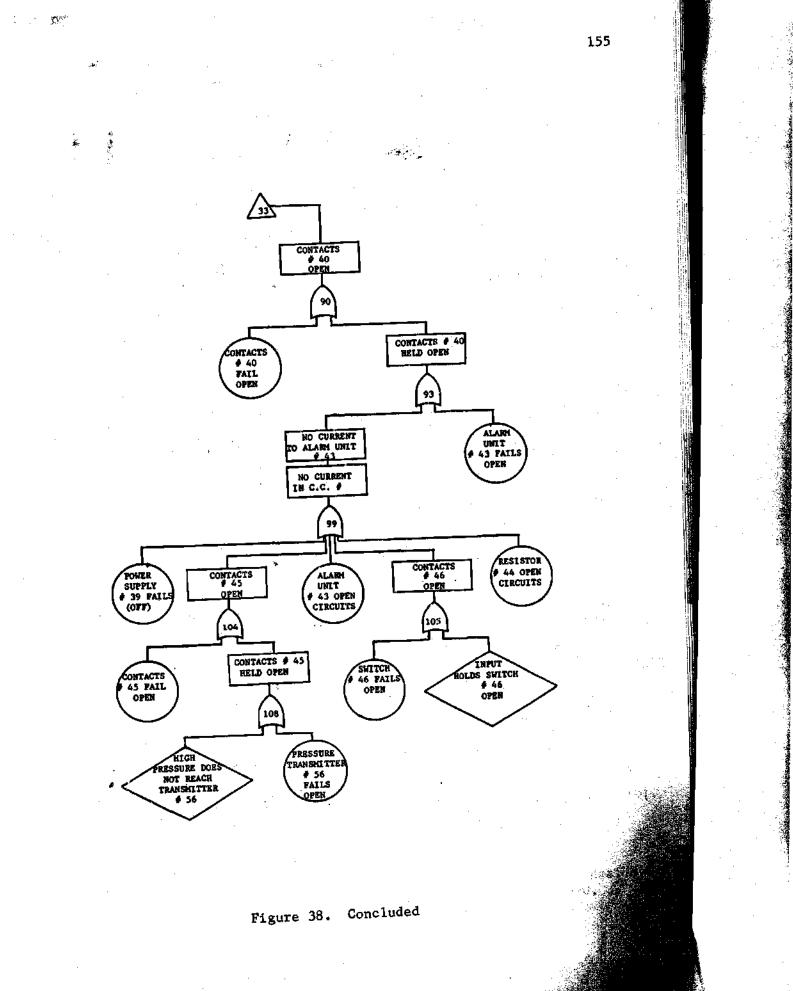

| 38.    | Fault Tree for Reactor Scram System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 139         |

## SUMMARY

Fault tree analysis is a recently developed method of reliability analysis and is generally applicable to complex, dynamic systems which include nuclear reactor systems. Fault tree analysis offers a tool by which nuclear reactor systems may be optimized in design to achieve, within the limits of engineering capabilities, the dual requirements for maximum safety and plant availability and minimum cost and complexity. The influence of the application of formal reliability analysis to all nuclear plant systems will result in higher probability of the systems functioning properly when they are called upon to operate. The greatest need today, however, is in the area of nuclear safety systems.

This dissertation provides a formal methodology, Synthetic Tree Model, for constructing fault trees for electrical systems to the point where identifiable primary component failures will directly produce the required fault events. Existing fault tree terminology is used in Synthetic Tree Model. The resultant fault trees are in a conventional format and are, consequently, immediately compatible with presently used fault tree solution techniques. Actually, they differ from a conventionally constructed fault tree in few ways. A difference is that, should any number of analysts construct fault trees independently for a given system and main failure event, using Synthetic Tree Model, they will all obtain identical fault trees. This is not a characteristic of conventional fault tree construction. This dissertation offers a model of considerable

xi

importance since it puts forth a model that affords the opportunity to reduce the cost of and time required for a fault tree analysis as well as provides potential for a standard by which fault trees can be constructed or checked.

Synthetic Tree Model is a synthesis technique for piecing together, with proper editing, a fault tree from small segments called component failure transfer functions. The component failure transfer functions are obtained from a system-independent failure mode analysis of individual components. This piecing together is an uncomplicated process but does involve "bookkeeping" such that the appropriate editing of the component failure transfer functions can be carried out. The component failure transfer functions are a limiting factor on the resolution of the fault trees resulting from Synthetic Tree Model.

While automation of fault tree construction is possible in the framework of Synthetic Tree Model, a computer program, DRAFT, has been written to accomplish this for certain electrical systems, this automation formulates yet another distinct type of analysis. The automated construction has potential as an overall, summary-type analysis that can be routinely done in a relatively small amount of time. Automation of Synthetic Tree Model provides the fault tree analyst a valuable tool to complement his present skills while Synthetic Tree Model itself is immetiately applicable to manual fault tree construction with the advantages of this manual analysis.

While Synthetic Tree Model is developed herein only for electrical systems, its implications extend to all fault tree constructions. The model is purposely left "open ended" to allow for its extension.

xii

Synthetic Tree Model shows potential for becoming a standard for fault tree construction as it is a formal approach to fault tree construction. The technique is of a general enough nature to allow fault tree construction for systems both in the nuclear industry and elsewhere.

## CHAPTER I

#### INTRODUCTION

#### 1.1 Background

Reliability analysis is a relatively new subject, continuously developing and expanding. Consequently its extent as a subject is not clearly defined. On one hand, it might be thought of as simply analysis to obtain statistical estimations of numerical reliability. On the other extreme, it might be thought of as analysis encompassing the whole development program. In reality it is neither of these extremes, but rather is a set of analytical techniques generated by an attitude of anticipation of unreliability and an appreciation of the necessity of pre-planned elimination of the associated problems.<sup>1</sup>

A commonly accepted definition of reliability is the following: "The reliability of a system is the probability that it will perform a required function under specified conditions, without failure, for a specified period of time."<sup>2</sup> As this definition implies, reliability prediction is based on detailed knowledge of system configuration, knowledge of the conditions of system use, and the failure characteristics of its components.

Concepts and methods of reliability prediction have been continually developed and refined over the past decade, and now reliability prediction is an important condition in the design of many systems such as aircraft, ships and their electronic systems, missiles, and spacecraft.<sup>3</sup> These systems are characterized by requirements for safety, predictable mission success and minimum maintenance per operating hour--three attributes that apply strongly to nuclear reactor systems.

Reliability, like several other important reactor parameters, for example the Departure from Nucleate Boiling ratio, is not a directly measurable property of the system; it can be estimated only from other measurable parameters. Reliability analysis methodology offers a tool by which nuclear reactor systems may be optimized in design to achieve, within the limits of engineering capabilities, the dual requirements for maximum safety and plant availability and minimum cost and complexity. The influence of the application of formal reliability analysis to all nuclear plant systems will result in higher probability of the systems functioning properly when they are called upon to operate. The greatest need today, however, is in the area of nuclear safety systems.

Formal reliability methods do not evaluate a system's capability to meet the functional requirements for which it was designed. Rather, reliability prediction methods establish the relative probability of the system performing adequately for the period intended under the operating conditions specified. The capability of the system to adequately meet the design function is not a part of the reliability analysis, but rather is the design adequacy. For example, the ability of a pump to deliver a given flow rate is a measure of its design adequacy. The probability of the pump functioning at some future time is its reliability.

1.1.1 System Structure Models

In the development of relevant system structure models, the concern is not with failure rates or distribution functions; rather, it should be

focused on an adequate logical description of all events that must occur to cause system failure.<sup>4</sup> An adequate logical description can be derived only if the functional design, physical layout, and method of operation of a system are known.

Approximations to reality can be achieved with probability models derived from reliability block diagrams.<sup>5</sup> Basically, block diagram models are probabilistic statements of component and part combinations necessary to achieve satisfactory operation. The sophistication or realism in block diagram models can vary greatly from simple part-count models modified to reflect redundancy to computerized programs that consider dependency, redundancy, end time sequencing in system operation by defining a system in terms of functions and components essential to the functions.<sup>6</sup> Block diagram models allow consideration of redundancy, are well suited to available data and system descriptions, and provide some capability to handle .dependency.

The complexity of the more sophisticated block diagram models, suggests a more logical approach to the development of reactor system probabilistic models. In effect what is required is a definition of all event sequences that give rise to the failure event or events of interest. In this approach a system logic model is developed that is addressed solely to the failure of interest; for example, the maximum credible accident and how this failure might develop. Such an approach does not require assumptions about independence in redundancy. It is solely based on the physical design and functional description of a system. Fault tree analysis is the method used to develop system failure logic. In this approach

an undesired event is defined. This event must be real and measurable. Subsequently the subevents necessary to cause the undesired event are developed in a graphical display by using various logic gates; for example, AND or OR gates. The appeal of fault tree analysis is that it simulates the critical aspects of system failure behavior as closely as possible without construction of the real system. Other advantages of system logic models are that they account for redundancy, repair, interdependence, and second order failures. Second order failures are failures induced by interaction of the component with the results of other component's failures. For example, if a relay fails in a valve actuation system, it is possible to observe the direct effect of the failure, as well as the effect of failures that may be induced in other parts of the system such as improper valve sequencing and false system status information. Also an unusual failure mode in one component may be examined for its effect, if it occurs, on the other similar components in the system.

#### 1.1.2 Fault Tree Analysis

Fault tree analysis provides an all inclusive, versatile mathematical tool for analyzing complex systems.<sup>7</sup> Its application can include a complete plant as well as any of the systems and subsystems. Fault tree analysis provides an objective basis for analyzing system design, performing trade-off studies, analyzing common mode failures, demonstrating compliance with Atomic Energy Commission requirements, and justifying system changes or additions.

The logic of the approach makes it a visibility tool for both engineering and management. Conventional reliability analysis techniques

are inductive in nature and are primarily concerned with assuring that hardware will reliably accomplish its assigned functions. The fault tree method is concerned with assuring that all critical activities are identified and eliminated or controlled.

In 1961 the concept of fault tree analysis was originated by Bell Telephone Laboratories as a technique with which to perform a safety evaluation of the Minuteman Launch Control System.<sup>8</sup> At the 1965 Safety Symposium, sponsored by the University of Washington and the Boeing Company, several papers were presented that expounded the virtues of fault tree analysis.<sup>9</sup> The presentation of these papers marked the beginning of a widespread interest in the possibility of using fault tree analysis as a reliability tool in the nuclear reactor industry. In the early 1970's great strides were made in the solution of fault trees to obtain complete reliability information about relatively complex systems.<sup>10,11,12,13,14</sup> The collection and evaluation of failure data is still of the utmost importance.<sup>7,15,16,17</sup>

Main benefits of fault tree analysis include:

1. Directing the analyst to ferret out failures in a deductive way.

2. Pointing out the aspects of the system important in respect to the failure of interest.

3. Providing a graphical aid giving system management visibility to those removed from the system design changes.

4. Providing options for qualitative or quantitative system reliability analysis.

5. Allowing the analyst to concentrate on one particular system at a time.

6. Providing the analyst with genuine insight into system behavior.

Fault tree models do have disadvantages. Probably the most outstanding is the cost of development in first time application to a system.<sup>3</sup> As in the development of engineering drawings for a nuclear reactor system, the cost is somewhat offset by future application of the models in accident prevention and system modifications. Another possible disadvantage is that the validity of the model is controlled by the skill and thoroughness of the analyst. This is true of all safety analysis work.

Fault tree analysis is a sophisticated form of reliability analysis and is consequently relatively expensive. The additional expense is justified by detail of the qualitative or quantitative analysis resulting from fault tree analysis. Another aspect of fault tree analysis that limits its application at this time is the relatively small number of people skilled in the techniques of fault tree analysis.<sup>18</sup> Even skilled personnel might develop a fault tree for a given system in different ways.<sup>19</sup>

The worst pitfalls that can confront one unskilled in performing fault tree analysis is over-sight and omission.<sup>19</sup> Significant omissions sometimes occur if the analyst jumps ahead two or more logical levels in his development of a deductive chain of factors and causes. For example, he may skip from initiation of a command to its acceptance, and neglect transmission. The tendency for this to happen is minimized if one follows the rule of listing very direct, immediate causes of any factor considered before going on to consider the next lower level of causes.

While certain single failures that can result in several component failures simultaneously, common mode failures, can be pointed out by a

detailed fault tree analysis, the analyst must be alert to include other common mode failures properly in the fault tree. At any rate, the analyst should be aware that fault tree analysis does not inherently ferret out common mode failures.

#### 1.2 Objectives

The objective of this thesis is to present a formal methodology for fault tree construction. A method formal enough to allow automated hardware-oriented fault tree construction for certain electrical systems as examples is sought, with its implications extending to fault tree construction in general, neglecting secondary failures. The methodology, called Synthetic Tree Model (STM), is to be "open ended" to allow for its extension to various types of systems and to allow increased resolution of the resultant fault trees.

The fault trees resulting from Synthetic Tree Model are to be in conventional format, use conventional symbols, and are to be constructed beginning with the main fault event of interest and proceeding to the individual component failure as is done in conventional fault tree construction. Actually, they should differ from a conventionally constructed fault tree in few ways. A main difference should be that should any number of analysts construct fault trees independently for a given system and main failure event using Synthetic Tree Model, they will all obtain identical fault trees. This is not a characteristic of conventional fault tree construction.

Being a formal methodology, Synthetic Tree Model is to offer potential as a standard for fault tree construction. The technique is to be

. 7

of a general enough nature to allow fault tree construction for systems both in the nuclear industry and elsewhere.

#### 1.3 Importance of the Study

Fault tree analysis has become of considerable importance as a tool of safety and reliability analysis in the nuclear industry. Much has been published dealing with developing techniques to quantify existing fault trees during the past decade while little has been published dealing with the construction of the fault tree itself. There is no published formal model for fault tree construction other than Synthetic Tree Model as presented herein. Other techniques for fault tree construction depend on the analyst ferreting out system logic, a technique that has the advantage of insuring that the analyst obtains a detailed knowledge of the system.  $^{1,7,8,19}$  A major disadvantage of fault tree analysis has been the large amount of time required to develop the fault tree itself. This thesis offers a method of considerable importance since it presents a model that affords the opportunity to reduce the cost of and time required for a fault tree analysis as well as provides potential for a standard by which fault trees can be evaluated and checked.

#### 1.4 Limitations

While all the objectives were obtained for Synthetic Tree Model, there are certain limitations. The method does not account for secondary failures--that is, failure related feedback between components is ignored. This is not a limitation of fault tree analysis but only of Synthetic Tree Model. The fault trees are constructed to the point where identifiable primary component failures will directly produce the fault event in question.

Synthetic Tree Model provides the basis for totally automated reliability prediction. Automated analysis should be thought of as a distinct type of analysis that could never replace conventional fault tree analysis. This automated tool could stop the system analyst from thinking. A value of the fault tree technique is that the analyst is forced to truly understand the system. Many weaknesses are typically corrected while constructing the fault tree. A value of the technique is the construction process, as well as the tree itself and resulting probability numbers. The automated analysis presented herein is a hardware oriented approach that does not include environmental and human effects that can cause failures and, therefore, is apart from an in-depth fault tree analysis.

Some systems may not lend themselves to analysis using Synthetic Tree Model since it may not be possible to determine certain necessary parameters for these systems. Indeed, there is no guarantee that a sufficient set of these parameters can be determined for systems other than the types presented in this thesis.

#### 1.5 Method\_of Approach

Synthetic Tree Model is a synthesis method for constructing fault trees from small segments called component failure transfer functions. The component failure transfer functions are obtained from a systemindependent analysis of every component appearing in the system for which the fault tree is to be constructed. Once the component failure transfer

functions are obtained, they may be used repeatedly, without modification, for any other system in which the component appears.

The system is defined by its associated schematic diagram and by system boundary conditions. The system boundary conditions give the main failure of interest, the one for which the fault tree is to be drawn, and also define the configurations of the components that have more than one operating state in the "non-failed" system. These boundary conditions along with other boundary conditions generated during the fault tree construction itself provide a basis for editing the failure transfer functions as they are connected into the fault trees.

The component failure transfer functions, inter-correlation between boundary condition and fault events, and several other parameters are catalogued as library data and are thereby available to the analyst or computer.

Basic concepts and definitions of Synthetic Tree Model are presented in Chapter II. Conventional fault tree terminology is presented in Chapter III. Details about basic parameters of Synthetic Tree Model are provided in Chapter IV, while the synthesis and editing processes are described in Chapter V. Chapter VI provides an example demonstrating Synthetic Tree Model. A complete, automated reliability prediction is then given in Chapter VII demonstrating the role of Synthetic Tree Model. Appendix C presents a computer constructed fault tree for a reactor scram system using Synthetic Tree Model.

## CHAPTER II

#### CONCEPTS OF SYNTHETIC TREE MODEL

Synthetic Tree Model is a formal methodology for constructing fault trees for electrical systems to the point where identifiable primary component failures will directly produce the required fault events. Synthetic Tree Model (STM) is unique in that it is formal enough to have permitted automated fault tree construction for certain electrical systems. While STM is developed herein only for electrical systems, its implications, extend to all fault tree construction.

STM is a synthesis technique for piecing together, with proper editing, a fault tree from small segments called component failure transfer functions. These component failure transfer functions are obtained from a system-independent failure mode analysis of individual components. Failure mode analysis is identifying all possible means by which a component can fail to perform its required functions. In some cases failure mode analysis has included not only the systematic identification of all the mechanisms of each mode of failure, but also assessing the probability of occurrence of these mechanisms. For STM the probability assessment can be neglected or at least deferred until a quantitative analysis is appropriate. This piecing together is an uncomplicated process but does involve "bookkeeping" such that the appropriate editing of the component failure transfer functions can be carried out. The component failure transfer functions are a limiting factor on the quality of the fault trees

resulting from STM.

## 2.1 Basic Definitions

<u>Primary failures</u> are basic component failures that require no further dissection since probability data for these failures are available. These probabilistic data are inputs to the quantitative analysis using the fault tree.

A <u>fault event</u> is a failure situation resulting from one of the logical interactions of more than one primary failure. The most undesired fault event is at the top of the fault tree and is called the <u>TOP event</u>. The TOP event is the starting point of fault tree construction. There is only one TOP event in any given fault tree.

A system <u>component</u> is a basic system constituent for which failures are considered primary failures during fault tree construction. Consequently, the components of a given system can change depending on the TOP event being studied or the detail the analyst wishes to include in the fault tree analysis. Some components have several operating states, none of which are necessarily failed states. Relay contacts can be open or closed for example. The description of these states is called the <u>com-</u> ponent configuration.

Fault tree construction is the logical development of the TOP event. As the construction proceeds each fault event is also developed until primary failures are reached. The development of any event results in a <u>branch</u> of the fault tree. The event being developed is called the <u>base event</u> of the branch. The branch is complete only when all events in the branch are developed to the level of primary failures. Every event

in a branch is in the <u>domain</u> of the base event. In addition, if the base event is an input to an AND gate, every event in the branch is in the domain of every input to that AND gate.

A fault tree <u>gate</u> is composed of two parts, (1) the Boolean logic symbol that relates the inputs of the gate to its output event and (2) the output event description. However, a gate is equivalent to another gate if, and only if, the logic symbol, the output event description, and another parameter, the "effective boundary conditions" associated with the output event, are identical. These effective boundary conditions will be considered in detail later.

There are two parts to the <u>event description</u>, (1) the incident identification and (2) the entity identification. The <u>incident identifi-</u> <u>cation</u> defines, as briefly as possible, the fault without indicating any hardware involved. The <u>entity identification</u> specifies the component or sub-system involved. These two parts are both required to describe the fault event.

#### 2.2 An Introduction to the Failure Transfer Functions

The key to STM is associating a complete set of failure transfer functions with each system component. A component failure transfer function describes one mode of failure for a component and is a fundamental property of the component. The failure transfer functions are then independent of the system being analyzed.

It is convenient at this time to define a <u>device</u>. A device is a piece of hardware whose modes of failure are somewhat different from the modes of failure of all other devices. Systems are composed of devices.

All components are devices. All components that are of identical design are the same device. Components that are not of identical design may, however, be the same device. If the complete set of failure transfer functions for a component is identical to the complete set of transfer functions of another component, they are then the same device. The number of devices in a given system is then always less than or equal to the number of components. Usually there are many more components than devices. Failure transfer functions can be thought of as a minute sub-fault tree. However, their appearance in the final system fault tree may be altered considerably.

Once a failure transfer function for a device has been determined it may be catalogued as library data. This library data can then be updated to reflect as much detail as desired. Otherwise, it is a constant property of the device.

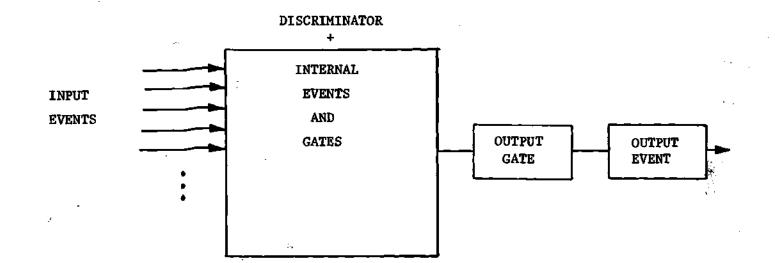

A failure transfer function may consist of as many as six parts, (1) an output event, (2) an output logic gate, (3) internal events, (4) internal logic gates, (5) input events, and (6) a discriminator. All of these parts can be determined from the fundamental workings of the component isolated from any system environment.

The <u>output event</u> is the mode of failure being considered. For a particular component, there is only one failure transfer function for a given output event. The output event is different from a fault event in that it requires no entity identification.

The <u>output gate</u> designates the logic with which the failure transfer function is coupled into the fault tree with other appropriate failure transfer functions having the same output event. There is one output

gate for each transfer function.

<u>Internal events</u> are fault events requiring further logical development within the failure transfer function. There is always enough information available from the component isolated from any system environment to allow further development of these events. <u>Internal gates</u> designate the logical development of the internal events as required by the output and input events.

<u>Input events</u> can be either primary events or undeveloped fault events. Input events represent the furthest development of the output event possible by considering the isolated component.

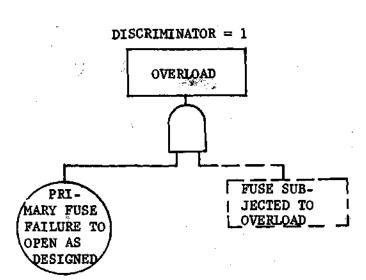

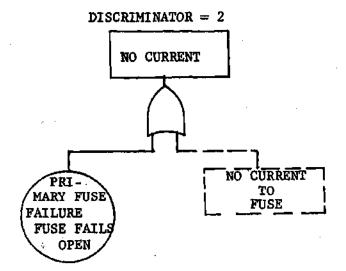

The <u>discriminator</u> is a flag designating which failure transfer functions may coexist in the final fault tree. The discriminator can be determined from the component since it indicates which output events can actually coexist within the same component. There is no more than one discriminator assigned to each failure transfer function.

A concept of the failure transfer function is illustrated in Figure 1. In a conventional sense, only the internal events and gates would be considered a transfer function; however, for the purposes of STM the conglomerate of all the parameters shown in Figure 1 is designated as the failure transfer function.

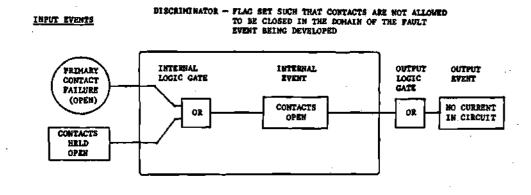

An example of a failure transfer function for electrical contacts causing no current in a circuit is shown in Figure 2. An equally valid representation of this failure transfer function is shown as a Boolean logic diagram in Figure 3. The implication of the discriminator is that when developing the input event, system input to the contacts causes the

### Figure 2. Example of a Failure Transfer Function for Electrical Contacts

¢

DISCRIMINATOR - FLAG SET SUCH THAT CONTACTS ARE NOT ALLOWED TO BE CLOSED IN THE DOMAIN OF THE FAULT EVENT BEING DEVELOPED

Figure 3.

3. Boolean Logic Representation of the Failure Transfer Functions Shown in Figure 2

contacts to be open. Any event that is excluded by the output event, no current in the circuit, is considered to be not-allowed. In short, this means in this case that the contacts cannot be open and closed at the same time.

In reflection, important characteristics of failure transfer functions are:

1. The component failure transfer functions are independent of the system being analyzed.

2. A complete set of failure transfer functions for a device may be used to represent many system components.

3. Failure transfer functions may be catalogued and used as library data.

4. There are as many failure transfer functions for a component as there are modes of failure for that component.

5. When a failure transfer function is used to develop an event, the use of certain other failure transfer functions can be excluded from the domain of that event.

#### 2.3 Ordered Fault Events

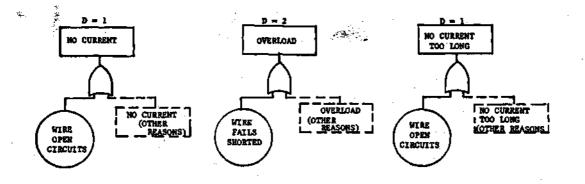

Fault events that are used <u>only</u> as TOP events are <u>First Order</u> <u>Fault Events</u>. This development may be catalogued for frequently used First Order Fault Events or provided as input to STM for each individual fault tree constructed.

Fault events that state a condition of the system that extends beyond any single component are <u>Second Order Fault Events</u>. The entity identification then refers to a particular sub-system, or, more specifically, to a variable that will later be defined as the "component coalition." Component failure transfer functions are always used as the first step in developing the Second Order Fault Events. Examples of Second Order Fault Events are "current too long in a particular circuit" and "no current in a particular circuit."

Fault events that cause a component to "behave failed" because part of the system itself, not simply another individual component, is causing that component to behave failed are <u>Third Order Fault Events</u>. An example of a Third Order Fault Event is "no current to a particular light bulb." Second Order Fault Events are always used as the first step in developing Third Order Fault Events.

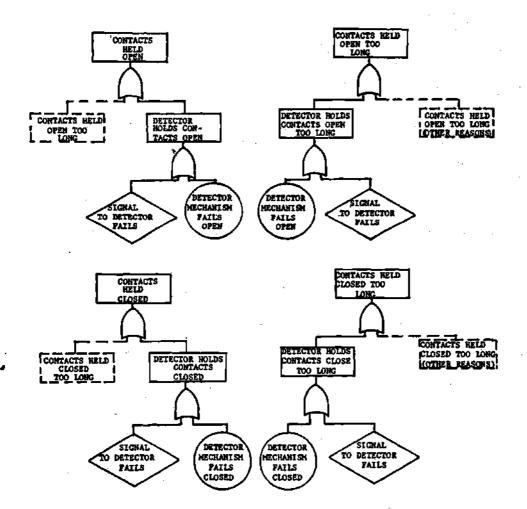

Fault events that result in component A behaving failed because another component has direct input to component A, are <u>Fourth Order Fault</u> <u>Events</u>. An example of a Fourth Order Fault Event is "relay contacts held open." Component failure transfer functions are always used to develop Fourth Order Fault Events.

#### 2.4 Boundary Conditions

#### 2.4.1 System Boundary Conditions

Without System Boundary Conditions it would not be possible to construct a fault tree. The boundary conditions in conjunction with the system schematic define the situation for which the fault tree is to be constructed. The System Boundary Conditions must be determined before any fault tree construction begins.

A most important system boundary condition is the TOP event. For

any given system, a multitude of possibilities for TOP events exist. The selection of the "correct" TOP event is sometimes a difficult task. There are, however, no limitations on the event chosen as the TOP event.

The system initial configuration is described by additional System Boundary Conditions. This configuration must represent the system in the unfailed state. Consequently these System Boundary Conditions depend on the TOP event. <u>Initial Conditions</u> are then System Boundary Conditions that define the operating condition of the system, i.e. all component configurations, for which the TOP event is applicable.

System Boundary Conditions also include any fault event declared to exist or to be not-allowed for the duration of the fault tree construction. These events are called <u>Existing System Boundary Conditions</u> or <u>Not-allowed System Boundary Conditions</u>. An Existing System Boundary Condition is treated as certain to occur while a Not-allowed System Boundary Condition is treated as an event with no possibility of occurring. Neither Existing nor Not-allowed System Boundary Conditions ever appear as events in the final system fault tree.

#### 2.4.2 Event Boundary Conditions

Event Boundary Conditions are boundary conditions associated with fault events in a fault tree and are implied by System Boundary Conditions or fundamental principles of set theory. A fault event is defined only when both the event description and the corresponding Event Boundary Conditions are known. A most important corollary is that a fault event is equivalent to another fault event if, and only if, their event descriptions and their associated Event Boundary Conditions are, in effect, identical.

Event Boundary Conditions are fault events or failure transfer functions that are considered as not-allowed or existing. All Not-allowed or Existing System Boundary Conditions are Event Boundary Conditions for every fault event in the fault tree. All other Event Boundary Conditions are generated by fault events as they appear in the fault tree. Once an Event Boundary Condition has been generated it is a boundary condition for every fault event that is in the domain of the fault event that generated the boundary condition. Fault events outside the domain of this base event are in no way affected by the boundary condition.

## 2.4.3 Effective Boundary Conditions

Effective Boundary Conditions are Event Boundary Conditions of a gate that actually affect the development of the gate. An event with an arbitrary number of Event Boundary Conditions may have no Effective Boundary Conditions. In practice, Effective Boundary Conditions are the only boundary conditions of any significance. Unfortunately, it is not possible to predict which Event Boundary Conditions are Effective Boundary Conditions; an event must be developed before its Effective Boundary Conditions are known. However, an observation that proves to be helpful in STM is that if the Event Boundary Conditions of two gates are identical the Effective Boundary Conditions must also be identical.

#### 2.5 Class of Third Order Fault Events

Recall that Third Order Fault Events require development using Second Order Fault Events. Several Second Order Fault Events may be required as input to a single gate whose event is a Third Order Fault Event.

The logic symbol used for this gate is dependent on the Third Order Fault Event being developed and is independent of the system being analyzed. Each incident identification for Third Order Fault Events is assigned to a Class. The entity identification does not affect the Class of the Third Order Fault Event. Class I indicates a Third Order Fault Event that requires an OR gate while Class II requires an AND gate.

#### 2.6 Category of Second Order Fault Events

Recall that Second Order Fault Events are developed using failure transfer functions of the components. However, it is possible for a Second Order Fault Event to appear during fault tree construction for which no transfer functions are available as input. This occurs because no appropriate component can fail in a manner so as to cause (or transmit) the Second Order Fault Event or Event Boundary Conditions can censor all, otherwise appropriate, failure transfer functions.

A Second Order Fault Event is in Category I if it is considered not-allowed if no failure transfer functions are available for its development. Category II indicates a Second Order Fault Event that is considered existing if no failure transfer functions are available.

#### CHAPTER III

#### FAULT TREE TERMINOLOGY

#### 3.1 Fault Tree Symbols

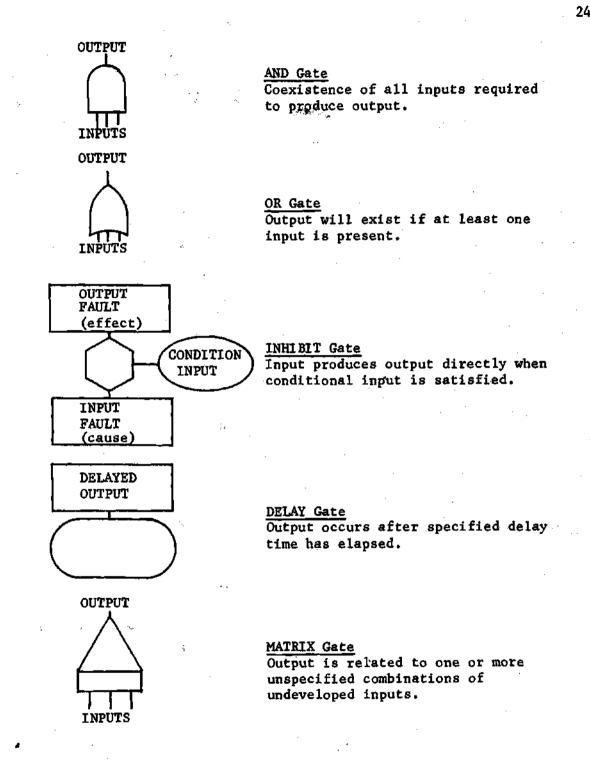

Fault tree symbols fall, basically, into two categories: logic symbols and event symbols. Logic symbols are shown in Figure 4 while event symbols are shown in Figure 5. $^{7,8,20}$

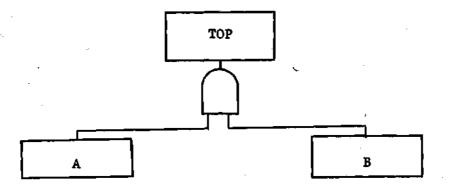

The logic symbols, or logic gates, are used to interconnect the events that could cause the specified main event, or TOP event. The logic gates that are most frequently used to develop fault trees are the basic AND and OR Boolean expressions. The AND gate provides an output event only if all input events are presented simultaneously. The OR gate provides an output event if one or more of the input events are present. The Boolean algebra associated with these two logic gates is presented in greater detail in the next section.

The more frequently used event symbols are the rectangle, circle and diamond. The rectangle represents a fault event resulting from the combination of more basic faults acting through logic gates. They may indeed be thought of as part of their associated logic gate. The circle designates a basic system component failure or fault input that is mutually independent from all other events designated by circles and diamonds. The diamond symbol describes fault inputs that are considered basic in a given fault tree. However, the event described is not basic in the

sense that laboratory data is applicable. Rather, the fault tree is simply not developed further, either because the event is of insufficient consequence or the necessary information is unavailable. Nevertheless, in order to obtain a solution for a fault tree, both circles and diamonds must represent events for which reliability information is input to the fault tree. For the study presented herein, events that appear as circles or diamonds are referred to as primary events.

The triangles shown in Figure 5 are not strictly event symbols although they have traditionally been classified as such. The triangle indicates a transfer from one part of the fault tree to another. A line from the side of the triangle (transfer out triangle) denotes an event transfer out from the associated logic gate. A line from the apex of the triangle denotes an event transfer into the associated logic gate from the transfer out triangle with the same identification number.

The other logic gates and events symbols are shown in Figure 4 and Figure 5 and are explained in those figures.

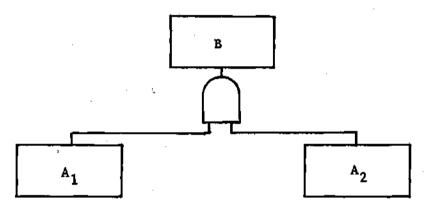

## 3.2 The OR Gate<sup>21</sup>

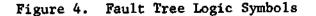

The fault tree symbol  $\bigcap$  is an OR gate and represents the union of the events attached to the gate. Any one or more of the events input to the gate must occur in order for the event above the gate to occur. The OR gate is equivalent to the Boolean symbol  $\bigcup$ . For example, the OR gate with two input events, as shown below, is equivalent to the Boolean expression,  $B = A_1 \bigcup A_2$ .

$$\mathbf{B} = \mathbf{A}_1 \bigcup \mathbf{A}_2$$

In the above illustration, the symbol " $\int$ " is to be interpreted as "in equivalent to." Either of the events  $A_1$  or  $A_2$ , or both, must occur in order for B to occur.

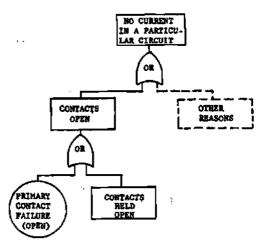

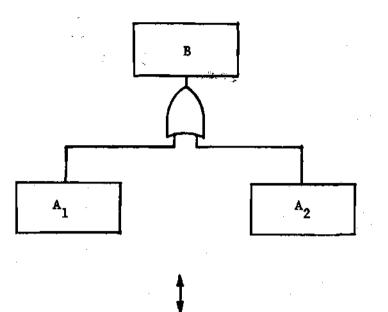

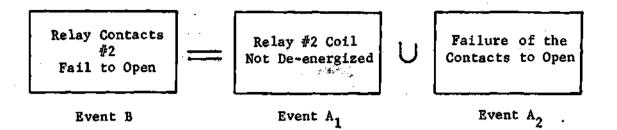

Shown below is a realistic example of an OR gate for a fault condition of a set of normally open contacts.

This OR gate is equivalent to the Boolean expression

27

An "OR" gate is merely a re-expression of the event above the gate (B) in terms of the more elementary input events  $(A_1, A_2)$ . The event above the gate encompasses all of these more elementary events; if any one or more of these elementary events occurs, then B occurs. This "reexpression" interpretation is quite important since it characterizes an OR gate and differentiates it from an AND gate. Whenever an event can be broken into more elementary events, then an OR gate is immediately drawn. The input events to an OR gate do not cause the event above the gate, they simply are the event above the gate "separated" into more detail.

If any one or more of the more particular events  $A_1 \dots A_n$ , assuming a case where n events are attached to B by an OR gate, occurs, then the more general event B occurs.

$A_{i} \rightarrow B; i = 1, ..., n$

where the symbol "\_\_\_" is to be interpreted as "implies."

## 3.3 The AND Gate<sup>21</sup>

The fault tree symbol  $\bigcap$  is an AND gate and represents the intersection of the events attached to the gate. The AND gate is equivalent to the Boolean symbol  $\bigcap$ . All of the events input to the AND gate must occur in order for the event above the gate to occur. For two events

28

2年の現在では他見なながれたかない いまつ

attached to the AND gate, the equivalent Boolean expression is

The event is only caused, or happens, if every one of the input events occurs. The cause relationship is what differentiates an AND gate from an OR gate. If the event above the gate occurs when any one of the input events occurs, then the gate is an OR gate and the event is merely a restatement of the input events. If the event above the gate occurs only when combinations of more elementary events occur, then the gate is an AND gate and each input is a cause of the event above the gate. (In set theory terminology, for an OR gate, each input event is a subset of the event above the gate while for an AND gate each input is not a subset of the event above the gate.)

For n events attached to the AND gate, the equivalent Boolean expression is

$B = A_1 \bigcap A_2 \dots \bigcap A_n$

The event B is caused by  $A_1$  and  $A_2$  and  $A_3$ ...and  $A_n$  all occurring simultaneously.

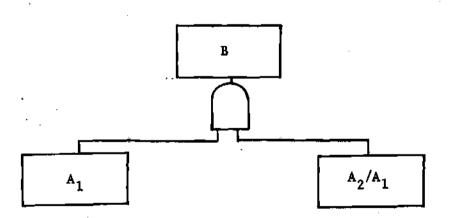

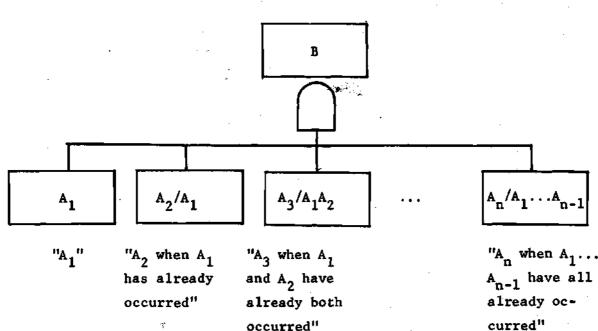

In general, the events attached to the AND gate are not interpreted to be independent, but instead are interpreted as occurring when the events to its left have already occurred. For example, in the two event illustration of the AND gate,

means

where  $A_2/A_1$  is the event  $A_2$  given that  $A_1$  has already occurred.  $A_1$  is a failure occurring with no other failures already existing in the system; it is the "first" failure.  $A_2/A_1$  is the failure  $A_2$  occurring with the failure  $A_1$  already existing in the system;  $A_2$  is thus the "second"

failure. If  $A_1$  is traced to more basic failures or causes, then the system will be examined with no previous, failure already having occurred. If  $A_2$  is traced to more basic failures or causes the system already having the failure  $A_1$  will be examined for more basic events. The system examined for  $A_1$  is thus of a different nature from the system examined for  $A_2$ . For example, the failure  $A_1$  may have caused the system to undergo a different operation. The failure  $A_2$  will then be traced to the more primary failures with the system in this different operation.

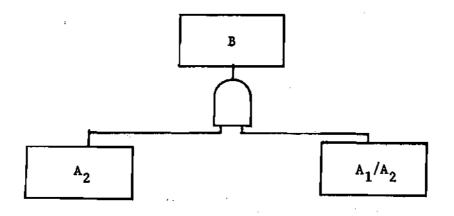

The AND gate may also be represented with A<sub>2</sub> as the "first" event, i.e., the event leftmost in the gate.

For those instances in which order of cause is not significant (which applies to most situations), this representation is entirely equivalent with the preceding one (where  $A_1$  was the "first" event). For  $A_2$ represented first, as shown above,  $A_1$  will now be traced with the failure  $A_2$  already existing. Where order of cause is not important, which failure is represented first is completely arbitrary and the particular sequence chosen is that which most simplifies the analysis.

When the order of occurrence of the failures is pertinent, the

$\mathbb{Q}_{2}^{r}$

first failure having to occur is represented leftmost on the gate and then the second failure necessary is the fight failure on the gate. The second failure will still be analyzed with the first failure already existing, as before.

One may say then that when order is unimportant, an ordering of the causes for further analysis is arbitrarily picked. When order is important the particular ordering necessary is dictated from the failure being investigated. In either case, the second failure is investigated with the first failure already existing.

For the case of n events  $A_1, \ldots A_n$  attached to the AND gate refer to the figure on the next page. The event B is caused by all of the events  $A_1, A_2, \ldots A_n$  having to occur. For  $A_2/A_1$  we are examining the occurrence of  $A_2$  under the condition that  $A_1$  has occurred. For  $A_n/A_1 \ldots A_{n-1}$ we are examining the occurrence of  $A_n$  under the condition that  $A_1, \ldots A_{n-1}$ have already all previously occurred. In general, we are examining the possible causes or re-expressions of the event  $A_k$  with the system in the state such that  $A_1, A_2, \ldots A_{k-1}$  are already existing. We are thus looking at the system with succeedingly more failures already existing.

Only when the event  $(A_k)$  is independent of the events to its left  $(A_{k-1}, \ldots A_1)$  can we neglect these left events as having already occurred. That is, if  $A_1, A_2, \ldots A_{k-1}$  have not changed in any way the nature of the system, then we can neglect all of these failures already existing and consider  $A_k$  as occurring in a system free of other failures.

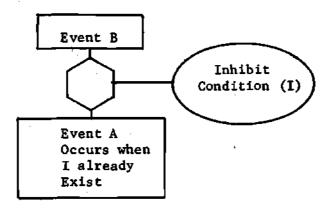

The INHIBIT condition representation is shown below.

In Boolean representation

$B = I \bigcap (A/I) = I \bigcap A$

An INHIBIT gate therefore is equivalent to an AND gate. The INHIBIT condition represents an event, a condition, or an environment that must exist along with A in order to cause B. The INHIBIT condition is only different from an event in that the causes of the inhibit condition are of no concern and are not further traced on the tree. The event A is traced to its causes with the condition that I is not existing.

## 3.4 Cut Sets<sup>22</sup>

The events of a fault tree can be Boolean manipulated in order to obtain the minimal cut sets of a fault tree. A minimal cut set is the smallest set of primary events which must all occur in order for the TOP event to occur. A primary event is a circle or diamond on the tree of is an INHIBIT condition. A primary event is thus a component failure, environmental effect, administrative error, etc. The primary events represent the resolution of the fault tree. The minimal cut sets represent the modes by which the TOP event can occur. For example, the minimal cut set  $A_1A_2$  means that both the primary events  $A_1$  and  $A_2$  must occur in order for the TOP event to occur.  $A_1$  and  $A_2$  is a mode by which the TOP event occurs. If either  $A_1$  or  $A_2$  does not occur, then the TOP event does not occur by this mode. The set of events  $A_1A_2^C$ , where C is another primary event, is not a minimal cut set since C is redundant and is not necessary for the occurrence of the TOP event; C can either occur or not occur and as long as  $A_1$  and  $A_2$  both occur, then the TOP event will occur.

The minimal cut sets are significant since they depict which failures must first be corrected in order for the TOP failure to be cor-

rected.\* The minimal cut sets often give the "weakest links" in the system. The primary failures (i.e., primary events) in the one event minimal cut sets usually should first be corrected. With these single failures corrected, the failures in the two event critical paths should then usually be corrected, and so forth. A single failure analysis is an investigation, or fault tree drawn, in order to obtain only the one primary event minimal cut set, (single failures) of the TOP event. For a single failure analysis, the fault tree ends whenever an AND gate is reached, that does not have deeper common causes (which effectively transform an AND gate to an OR gate).

The basic Boolean operations are summarized below.<sup>23</sup>

1. Distributive Laws