# System Interconnection Design Trade-offs in Three-Dimensional (3-D) Integrated Circuits

ROSHAN WEERASEKERA

Doctoral Thesis Stockholm, Sweden 2008

TRITA

ICT/ECS AVH 08:12

ISSN

1653-6363

ISRN

KTH/ICT/ECS AVH-08/12-SE

ISBN

978-91-7415-169-5

© Roshan Weerasekera, December 2008

KTH School of Information and Communication Technologies Department of Electronic, Computer, and Software Systems ELECTRUM 229, Kista SE-164 40, Sweden.

Thesis submitted to the School of Information and Communication Technologies, the Royal Institute of Technology in partial fulfillment of the degree Doctor of Philosophy in Electronic and Computer System Design on Tuesday 16 December 2008 at 13.00 hrs in Stockholm.

#### Abstract

Continued technology scaling together with the integration of disparate technologies in a single chip means that device performance continues to outstrip interconnect and packaging capabilities, and hence there exist many difficult engineering challenges, most notably in power management, noise isolation, and intra and inter-chip communication. Significant research effort spanning many decades has been expended on traditional VLSI integration technologies, encompassing process, circuit and architectural issues to tackle these problems. Recently however, *threedimensional* (3-D) integration has emerged as a leading contender in the challenge to meet performance, heterogeneous integration, cost, and size demands through this decade and beyond.

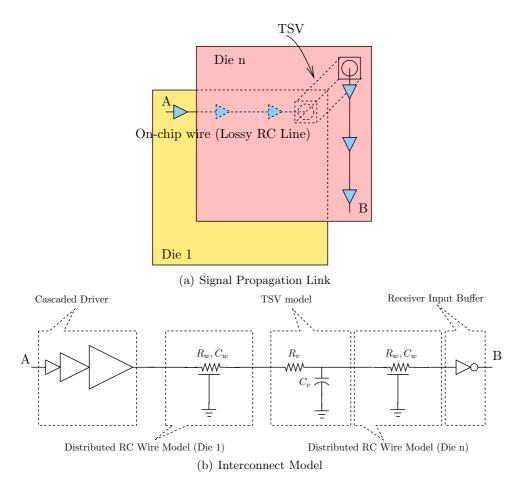

Through silicon via (TSV) based 3-D wafer-level integration is an emerging vertical interconnect methodology that is used to route the signal and power supply links through all chips in the stack vertically. Delay and signal integrity (SI) calculation for signal propagation through TSVs is a critical analysis step in the physical design of such systems. In order to reduce design time and mirror well established practices, it is desirable to carry this out in two stages, with the physical structures being modelled by parasitic parameters in equivalent circuits, and subsequent analysis of the equivalent circuits for the desired metric. This thesis addresses both these issues. Parasitic parameter extraction is carried out using a field solver to explore trends in typical technologies to gain an insight into the variation of resistive, capacitive and inductive parasitics including coupling effects.

A set of novel closed-form equations are proposed for TSV parasitics in terms of physical dimensions and material properties, allowing the electrical modelling of TSV bundles without the need for computationally expensive field-solvers. Suitable equivalent circuits including capacitive and inductive coupling are derived, and comparisons with field solver provided values are used to show the accuracy of the proposed parasitic parameter models for the purpose of performance and SI analysis.

The deep submicron era saw the interconnection delay rather than the gate delay become the major bottleneck in modern digital design. The nature of this problem in 3-D circuits is studied in detail in this thesis. The ubiquitous technique of repeater insertion for reducing propagation delay and signal degradation is examined for TSVs, and suitable strategies and analysis techniques are proposed. Further, a minimal power smart repeater suitable for global on-chip interconnects, which has the potential to reduce power consumption by as much as 20% with respect to a traditional inverter is proposed. A modeling and analysis methodology is also proposed, that makes the smart repeater easier to amalgamate in CAD flows at different levels of hierarchy from initial signal planning to detailed place and route when compared to alternatives proposed in the literature.

Finally, the topic of system-level performance estimation for massively integrated systems is discussed. As designers are presented with an extra spatial dimension in 3-D integration, the complexity of the layout and the architectural trade-offs also increase. Therefore, to obtain a true improvement in performance, a very careful analysis using detailed models at different hierarchical levels is crucial. This thesis presents a cohesive analysis of the technological, cost, and performance trade-offs for digital and mixed-mode systems, outlining the choices available at different points in the design and their ramifications.

|  | - |  |  |  |

|--|---|--|--|--|

|  |   |  |  |  |

|  |   |  |  |  |

# Acknowledgements

This thesis comes at the end of four formative years, which has contributed enormously to my professional and personal growth, spent at the Department of Electronic, Computer, and Software Systems (ECS) of the School of Information and Communication technologies (ICT), the Royal Institute of Technology (KTH), Stockholm, Sweden. Here are the people to whom I want to express my deepest gratitude for what they have facilitated to this work.

First and foremost, I must thank my supervisors Prof. Hannu Tenhunen and Prof. Li-Rong Zheng for their guidance and support throughout my PhD studies. Their constant enthusiasm for learning, and finding new research avenues is highly appreciated, and both of them have a knack for explaining the most intricate theories with such a simple approach.

I owe a huge debt of thanks to Dinesh - Dr. Dinesh Pamunuwa of Lancaster University - for being a collaborator on almost all my publications and giving the necessary comments and criticism when I desperately needed them. Not only that I must greatly remember his endeavour on recruiting me as a research associate in Lancaster University under the EU-FP7 funded ELITE project. This stay was quite successful and effective on making series of new publications and also it opened up new research avenues.

I greatly appreciate the financial support for my research from SIDA under the auspices of the research capacity building project at the Department of Electrical and Electronic Engineering, University of Peradeniya (UPDN), Sri Lanka, without which this thesis would not have been possible. My thanks are also due to its coordinators, Dr. Sanath Alahakoon of UPDN and Tekn. Lic. Mats Leksell of KTH, not only for their exceptional administration capabilities but also for their humanism. Also, I must thank the SIDA/SAREC PhD student colleagues from UPDN in KTH and Chalmers University of Technology, Sweden.

I must thank the financial support of European Union research funding under grant FP7-ICT-215030 (ELITE) of the  $7^{th}$  framework programme for my internship at Lancaster University, UK. Also, the support received from the members in ELITE collaborative partner companies Qimonda Gmbh in Germany, LETI in France, and Hyperstone in Germany is highly regarded. Many thanks are due to colleagues at ECS too numerous to mention here, especially in the iPack center, ESD, SAM and RaMSIS groups, for their friendship, support on learning various tools and help on understanding some theoretical aspects.

Also, a special word of thanks should go to the administrative staff in ECS and the IT support group in ICT.

Thanks are also due to the staff of the Centre for Microsystems Engineering at Lancaster University, UK, especially the humanism, great support, and friendship of Prof. Andrew Richardson, the Center Director.

The friendship of Sri Lankan postgraduate students community in Stockholm, and some other colleagues has made the time spent in Stockholm more pleasant.

I express my deepest gratitude to my parents for their restless efforts on growing and taking care of me through thick and thin; and to my brother and the sister, for being close associates and mentors on various other occasions.

I compliment most warmly my loving and caring wife, Indu, who had to endure and share the pain and the pleasures of my arduous professional life. Last but not least, I must thank our son, Savinu, who missed me sometimes from dawn to dusk for not being available to play with.

Roshan Weerasekera December, 2008 Stockholm

# List of Publications

- 1. Roshan Weerasekera, Dinesh Pamunuwa, Hannu Tenhunen, and Li-Rong Zheng, "Modelling Through-Silicon-Vias in 3D-ICs," *IET Electronic Letters*, September, 2008, Under Review.

- Roshan Weerasekera, Dinesh Pamunuwa, Matt Grange, Hannu Tenhunen, and Li-Rong Zheng, "Parasitic Parameter Estimation and Electrical Modelling of Through-Silicon Vias in 3-D ICs," *IEEE International Symposium* on Circuits and Systems, Under Review.

- Matt Grange, Roshan Weerasekera, Dinesh Pamunuwa, and Hannu Tenhunen, "Exploration of Through Silicon Via Interconnect Parasitics for 3-Dimensional Integrated Circuits," *IEEE International Symposium on Circuits and Systems*, Under Review.

- 4. Botao Shao, Roshan Weerasekera, Abraham Tareke Woldegiorgis, Li-Rong Zheng, Ran Liu, and Werner Zapka, "High Frequency Characterization and Modeling of Inkjet Printed Coplanar Strips on Flexible Substrate," in Proceedings of the 2<sup>nd</sup> Electronics System-Integration Technology Conference, London, UK, September, 2008, pp. 695-699.

- Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng, and Hannu Tenhunen, "2-D and 3-D Integration of Heterogeneous Electronic Systems under Cost, Performance and Technological Constraints," *IEEE Transactions* on Computer Aided Design of Integrated Circuits and Systems, September, 2008, Under Review.

- Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng, and Hannu Tenhunen, "Minimal-Power, Delay-Balanced Smart Repeaters for Global Interconnects in the Nanometer Regime," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 16, no. 5, pp. 589-593, May, 2008.

- Botao Shao, Roshan Weerasekera, Li-Rong Zheng, Ran Liu, Werner Zapka, and Peter Lindberg, "High Frequency Characterization of Inkjet Printed Coplanar Waveguides," 12<sup>th</sup> IEEE Workshop on Signal Propagation on Interconnects, May, 2008, pp.1-4.

- Roshan Weerasekera, Li-Rong Zheng, Dinesh Pamunuwa, and Hannu Tenhunen, "Extending Systems-on-Chip to the Third Dimension: Performance, Cost and Technological Tradeoffs," in Proceedings of the IEEE/ACM international conference on Computer-aided design, IEEE Press, November, 2007, pp. 212-219.

- 9. Roshan Weerasekera, Li-Rong Zheng, Dinesh Pamunuwa, and Hannu Tenhunen, "Early selection of system implementation choice among SoC, SoP and 3-D Integration," *IEEE International System-on-Chip Conference*, Sep-

tember, 2007, pp.187-190.

- Botao Shao, Roshan Weerasekera, Abraham Tareke Woldegiorgis, Li-Rong Zheng, Ran Liu, Werner Zapka, and Peter Lindberg, "Electrical Characterization of Inkjet Printed Interconnections on Flexible Substrates", *IEEE CPMT Symposium on Green Electronics*, Göteborg, Sweden, 2007.

- 11. Roshan Weerasekera, Abraham Tareke Woldegiorgis, Botao Shao, Saul Rodriguez Duenas, Li-Rong Zheng, Peter Lindberg, Werner Zapka, and Hannu Tenhunen, "Electrical Characterization of Ink-Jet Printed Interconnects on Plastic for Low-Cost RFID," *IEEE International Conference on Industrial* and Information Systems, Peradeniya, Sri Lanka, 2007.

- Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng, and Hannu Tenhunen, "Delay-Balanced Smart-Repeaters for on-chip Global Signaling," 20<sup>th</sup> International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems, 2007, pp. 308-313.

- Jian Liu, Roshan Weerasekera, Li-Rong Zheng, and Hannu Tenhunen, "Exploration of Autonomous Error-Tolerant (AET) Celluar Networks in Systemon-a Package (SoP) for Future Nanoscale Electronic Systems," *IEEE International Conference on Industrial and Information Systems*, Peradeniya, Sri Lanka, 2006.

- 14. Dinesh Pamunuwa and Roshan Weerasekera, "Nanoelectronics: from novelty toys to functional Devices - an integration perspective," *IEEE International Conference on Industrial and Information Systems*, Peradeniya, Sri Lanka, 2006, Invited Paper.

- Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng, and Hannu Tenhunen, "Minimum-Power, Delay-Balanced Drivers for interconnects in the Nanometer Regime," *Proceedings of the international workshop on Systemlevel interconnect prediction*, German, March, 2006, pp. 113-120.

- Roshan Weerasekera, Li-Rong Zheng, Dinesh Pamunuwa, and Hannu Tenhunen, "Switching sensitive interconnect Driver to Combat Dynamic Delay in on-Chip Buses," *Lecture Notes in Computer Science (Proceedings of PAT-MOS)*, vol. LNCS 3728, pp. 277-285, 2005.

- Roshan Weerasekera, Jian Liu, Li-Rong Zheng, and Hannu Tenhunen, "A Nanocore/ CMOS Hybrid System-on-Package (SoP) Architecture for Future Nanoelectronic Systems," *Conference on High Density Microsystem Design* and Packaging and Component Failure Analysis, June, 2005, pp.1-4.

- Jian Liu, Roshan Weerasekera, Li-Rong Zheng, and Hannu Tenhunen. "Nanocore/ CMOS hybrid system-on-package(sop) architecture for autonomous error-tolerant (aet) cellular array network," In 5th IEEE Conference on Nanotechnology, Nagoya, Japan, 2005.

- Jian Liu, Roshan Weerasekera, Li-Rong Zheng, and Hannu Tenhunen, "Nano scale autonomous error-tolerant (aet) cellular network," In Technical Proceedings of the 2005 Nanotechnology Conference and Trade Show, California, USA, May, 2005, pp. 748-751.

- Roshan Weerasekera, Jian Liu, Li-Rong Zheng, and Hannu Tenhunen. "A nanocore/cmos hybrid system-on-package (sop) architecture for future nanoelectronic systems," In Technical Proceedings of the 2005 Nanotechnology Conference and Trade Show, California, USA, May, 2005, pp. 157-160.

- 21. Roshan Weerasekera, Li-Rong Zheng, Dinesh Pamunuwa, and Hannu Ten-

#### List of Publications

hunen, "Crosstalk Immune Interconnect Driver Design," in the Proceedings of International Symposium System-on-Chip, November, 2004, pp. 139 - 142.

|  | - |  |  |  |

|--|---|--|--|--|

|  |   |  |  |  |

|  |   |  |  |  |

# Table of Contents

| A             | cknov  | ledgements    |                                                       | iii          |

|---------------|--------|---------------|-------------------------------------------------------|--------------|

| $\mathbf{Li}$ | st of  | Publication   | 3                                                     | $\mathbf{v}$ |

| Ta            | able o | f Contents    |                                                       | ix           |

| 1             | Intr   | oduction      |                                                       | 1            |

|               | 1.1    | Evolution of  | Microelectronic Systems                               | 1            |

|               |        | 1.1.1 Mici    | roelectronic                                          | 2            |

|               |        | 1.1.2 Pack    | caging                                                | 3            |

|               | 1.2    | Trends in Fu  | urther Miniaturization                                | 4            |

|               |        | 1.2.1 Dev     | ice and Interconnect Scaling                          | 4            |

|               |        | 1.2.2 Inte    | grated Circuit Packaging                              | 6            |

|               |        | 1.2.3 Dea     | ling with Complexity: System-Level Integration        | 7            |

|               | 1.3    | Interconnect  | Challenges and Strategic Solutions                    | 9            |

|               |        | 1.3.1 Eme     | erging Solutions - Alternatives for Cu/Low- $\kappa$  | 11           |

|               | 1.4    | Scope of Th   | esis and Author's Contribution                        | 12           |

|               |        | 1.4.1 Sma     | rt Repeaters for Interconnections in Nanometer Tech-  |              |

|               |        | nolo          | gies                                                  | 13           |

|               |        | 1.4.2 Cost    | t and Performance Trade-offs for 2-D and 3-D Mixed-   |              |

|               |        | 0             | al ICs                                                | 14           |

|               |        |               | trical Modelling of Through-Silicon Vias in 3-D Inte- |              |

|               |        | 0             | ed Circuits                                           | 15           |

|               | 1.5    | Thesis Orga   | nization                                              | 16           |

| <b>2</b>      | Inte   | rconnect M    | odelling and Analysis                                 | 17           |

|               | 2.1    |               |                                                       | 17           |

|               |        |               | tromagnetic View of Interconnects                     | 19           |

|               | 2.2    | Parasitic Es  | timation and Extraction                               | 20           |

|               |        | 2.2.1 Resi    | stance                                                | 21           |

|               |        | 2.2.2 Indu    | actance                                               | 25           |

|               |        | 2.2.3 Cap     | acitance                                              | 29           |

|               |        | 2.2.4 Con     | duction                                               | 32           |

|               | 2.3    | Electrical Le | evel Modelling                                        | 33           |

|               |        |               | osing a Wire Model                                    | 35           |

|               | 2.4    |               | Timing Analysis                                       | 39           |

|               |        | 2.4.1 Inter   | rconnect Driver Modelling                             | 39           |

## TABLE OF CONTENTS

|   |      | 2.4.2                                       | Interconnect Delay Modelling                                                                     |   | 43              |

|---|------|---------------------------------------------|--------------------------------------------------------------------------------------------------|---|-----------------|

|   |      | 2.4.3                                       | Noise-on-Delay Effect                                                                            |   | 45              |

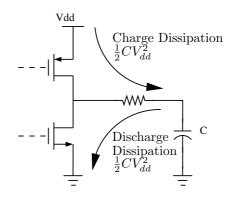

|   | 2.5  | Interco                                     | onnect Energy Dissipation Analysis                                                               |   | 48              |

|   |      | 2.5.1                                       | Switching Energy                                                                                 |   | 48              |

|   |      | 2.5.2                                       | Short Circuit Energy                                                                             |   | 49              |

|   |      | 2.5.3                                       | Leakage or Static Energy                                                                         |   | 50              |

|   | 2.6  | Summ                                        | ary                                                                                              | • | 50              |

| 3 | Elec | ctrical ]                                   | Modelling of Through-Silicon Vias                                                                |   | <b>53</b>       |

|   | 3.1  |                                             | uction $\ldots$ |   | 53              |

|   | 3.2  |                                             | Specification and Physical Modelling                                                             |   | 54              |

|   | 3.3  |                                             | s in Parasitic Parameter Values                                                                  |   | 55              |

|   |      | 3.3.1                                       | Isolated TSV                                                                                     |   | 55              |

|   |      | 3.3.2                                       | Two Parallel TSVs                                                                                |   | 58              |

|   |      | 3.3.3                                       | TSV Bundle                                                                                       |   | 62              |

|   | 3.4  | -                                           | act Modelling of TSV Parameters                                                                  |   | 67              |

|   |      | 3.4.1                                       | RLC Extraction of an Isolated TSV                                                                |   | 67              |

|   |      | 3.4.2                                       | RLC Extraction of a TSV Bundle                                                                   |   | 70              |

|   | 3.5  | Summ                                        | ary                                                                                              | • | 77              |

| 4 | -    | -                                           | Techniques for On-Chip Global Interconnects                                                      |   | 79              |

|   | 4.1  |                                             | uction                                                                                           |   | 79              |

|   | 4.2  |                                             | Methodologies for On-Chip Interconnects                                                          |   | 80              |

|   |      | 4.2.1                                       | Layout and Routing Level                                                                         |   | 80              |

|   |      | 4.2.2                                       | Circuit Level                                                                                    |   | 81              |

|   | 4.0  | 4.2.3                                       | Architectural and System Level                                                                   |   | 83              |

|   | 4.3  |                                             | T Driver Circuit                                                                                 |   | 84<br>87        |

|   |      | $4.3.1 \\ 4.3.2$                            | Limitations in Existing Driver circuits                                                          |   | 85<br>05        |

|   |      | $\begin{array}{c} 4.5.2\\ 4.3.3\end{array}$ | The ConceptCircuit Realization                                                                   |   | $\frac{85}{86}$ |

|   |      | 4.3.3<br>4.3.4                              | Noise Resiliency of the SMART Driver                                                             |   | 80<br>90        |

|   |      | 4.3.4<br>4.3.5                              | Energy Saving of the SMART Driver                                                                |   | 90<br>91        |

|   |      | 4.3.6                                       | Design Methodology                                                                               |   | 92              |

|   |      | 4.3.7                                       | Energy and Delay Model Validation                                                                |   | 92<br>96        |

|   |      | 4.3.8                                       | Impact of Technology Scaling                                                                     |   | 98              |

|   | 4.4  |                                             | al Signal Transmission Methodologies                                                             |   | 99              |

|   |      | 4.4.1                                       | Signal Transmission Characteristics of TSV interconnects                                         |   |                 |

|   |      | 4.4.2                                       | Signalling Link Design for Layer-to-Layer Communication                                          |   |                 |

|   | 4.5  |                                             | ary                                                                                              |   |                 |

| 5 | IC   | Cost M                                      | odelling at the System Conceptual Level                                                          |   | 109             |

|   | 5.1  |                                             | uction                                                                                           |   | 109             |

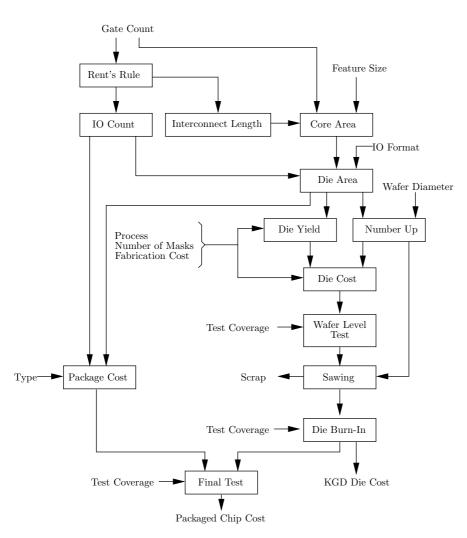

|   | 5.2  |                                             | Analysis and Modelling                                                                           |   | 109             |

|   |      | 5.2.1                                       | Rent's Rule                                                                                      |   |                 |

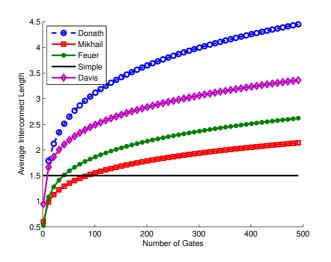

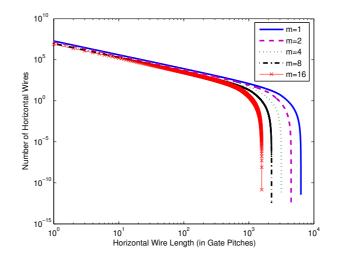

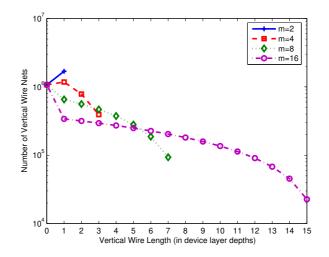

|   |      | 5.2.2                                       | Wire-Length Modelling                                                                            |   | 112             |

|   | 5.3  | Bare I                                      | Die/Packaged Chip Cost Analysis                                                                  |   | 113             |

|   |      | 5.3.1                                       | Packing Density and Area                                                                         |   | 114             |

|   |      | 5.3.2                                       | Chip Size                                                                                        |   | 117             |

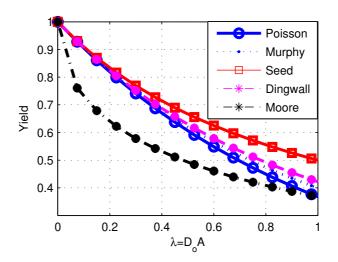

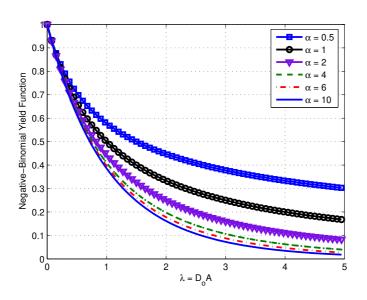

|   |      |                                             |                                                                                                  |   |                 |

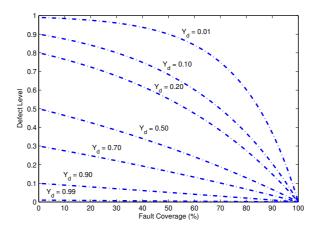

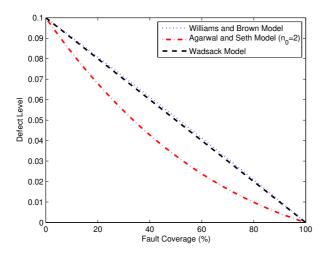

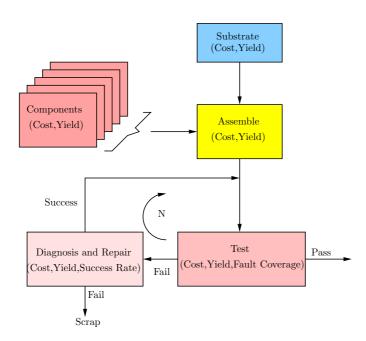

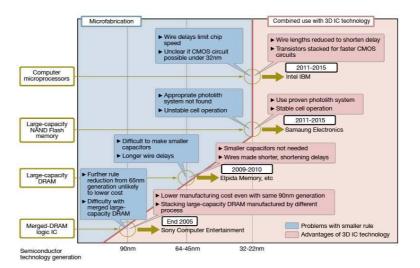

|    | 5.4<br>5.5 | 5.3.3Die Yield Analysis1185.3.4Chip Cost Model124Board- or Package-Level Model1285.4.1Number of Pins per Chip1285.4.2Module Level Average Interconnection Length1285.4.3Chip Footprint1295.4.4Yield and Cost Analysis130Summary132 |

|----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6  | Het        | erogeneous System-on-Chip Integration: 2-D or 3-D? 133                                                                                                                                                                             |

|    | 6.1        | Introduction                                                                                                                                                                                                                       |

|    | 6.2        | Three-Dimensional Integration                                                                                                                                                                                                      |

|    |            | 6.2.1 Benefits of 3-D Integration over 2-D Planar                                                                                                                                                                                  |

|    |            | 6.2.2 Challenges for 3-D integration                                                                                                                                                                                               |

|    |            | 6.2.3 Three-Dimensional Integration Options                                                                                                                                                                                        |

|    | 6.3        | Early Estimation of Cost and Performance                                                                                                                                                                                           |

|    |            | 6.3.1 Models for Trade-off Analysis                                                                                                                                                                                                |

|    | 6.4        | Tradeoff Analysis for SoC, SoP and 3-D Implementations 147                                                                                                                                                                         |

|    |            | 6.4.1 Monolithic SoC                                                                                                                                                                                                               |

|    |            | 6.4.2 2D-SoP                                                                                                                                                                                                                       |

|    |            | 6.4.3 3D-SiP                                                                                                                                                                                                                       |

|    |            | 6.4.4 3D-WLI                                                                                                                                                                                                                       |

|    | 6.5        | Discussion                                                                                                                                                                                                                         |

|    | 6.6        | Summary                                                                                                                                                                                                                            |

| 7  | Con        | clusions 159                                                                                                                                                                                                                       |

|    | 7.1        | Summary                                                                                                                                                                                                                            |

|    | 7.2        | Future Work                                                                                                                                                                                                                        |

| Re | eferei     | nces 163                                                                                                                                                                                                                           |

|  | - |  |  |  |

|--|---|--|--|--|

|  |   |  |  |  |

|  |   |  |  |  |

# 1

# Introduction

'I believe the best is yet to come'

Jack S. Kilby [1]

# **1.1 Evolution of Microelectronic Systems**

**O** ver the last fifty years, the synergistic interaction between solid-state physics, electrical engineering, and materials science has fueled the growth of the solid-state circuits industry from infancy to become one of the largest industries in the world. The technologies behind almost all modern electronic products, which touch every aspect of human life, from computers to communication equipments, toys, food, medical technology and the automobile industry are all based on microelectronic devices and packaging technologies.

The miniaturization of electronic systems goes back to the days of World War II. During this time, there was a increased demand for small size, light weight, low power, and reliable military electronic systems because of the increased use of these systems and ease in carrying them especially in aircrafts or for infantry personnel who carried equipment in combat. Due to this demand, electronic systems has moved from room-sized products toward hand-held devices with considerably greater computational horsepower; the functions that a today's chip performs are essentially no different from those earlier products. Even for today's applications the performance metrics remain the same, but cost the constraint has come into picture as a major design requirement especially in consumer electronic systems.

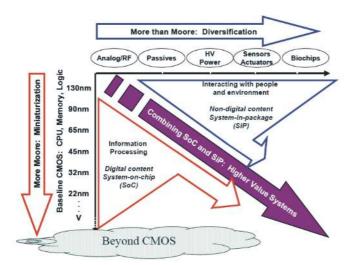

Consequently the process of device miniaturization evolved from few micrometers to nanometers today, and circuit complexity has advanced from Small-Scale Integration (SSI) in 1960s, to Medium/Large Scale Integration (MSI/LSI) in 1970s, to Very Large Scale Integration (VLSI) 1990s, and to Giga-Scale Integration (GSI) in 2000s. This tighter integration continues at a break-neck speed toward a trillion transistors per chip, Tera-Scale Integration (TSI) era, in 2020s. With the passage of time, not only digital devices and memory, but also analog/mixed-signal blocks, MEMS based sensors, biological functions are also being integrated on the same die or package to build a complete system. In reconciling with feature size miniaturization and technology divergence, and achieving smaller, faster, and cheaper products, there exists many unprecedented difficult technological challenges at different hierarchy levels in electronic system design process [2, 3].

## 1.1.1 Microelectronic

The electronics industry was launched by the invention of the Vacuum Tube, and its basic usage was to amplify signals for radio and other audio devices. But, Vacuum Tubes steadily spread into other devices, and the first tube was used as a switch in calculating machines in 1939. The ENIAC of 1947, intended for computing artillery firing tables, was the first electronic computer developed by John W. Mauchly and J. Presper Eckert, Jr. During that time ENIAC was the fastest computer, but it contained around 18,000 vacuum tubes which failed at the rate of one in every 7 minutes, occupied 16,200 cubic-feet, weighted 60,000 pounds, and consumed 174 kW (= 233 horsepower) of electricity. The reliability problems with the vacuum tubes and the excessive power consumption made the implementation of larger engines economically and practically infeasible. These problems were visible to many in the industry and hence momentum on research into miniaturization of electronic systems grew. One can clearly see that there are three inventions in the  $20^{th}$  century which has been greatly instrumental in the evolution of the Integrated Circuit (IC) and thus in Information Technology (IT): the invention of the transistor, monolithic concept and the planar process.

While searching for switches and amplifiers to replace mechanical relays and the valves that so troubled ENIAC, J. Bardeen, W.H. Brattain and W. Shockley of Bell labs, USA, invented the first point contact transistor. Thereafter, in 1950, Shockley invented a new device called a bipolar junction transistor (BJT), which was more reliable, easier and cheaper to build than the point contact devices.

On July 24, 1958, Jack Kilby of Texas Instruments scribed in his note book what has come to be known as the idea of monolithic circuits, that circuit elements such as resistors, capacitors, distributed capacitors and transistors - if all made of

Figure 1.1: First Point Contact Transistor and it's co-inventors.

Figure 1.2: Jack Kilby and the first IC (source: Texas instruments).

the same material - could be included in a single chip. On September 12, 1958, he succeeded in fabricating a phase shift oscillator on a single piece of semiconductor, which earned him the Nobel Price for Physics in 2000, for the invention which revolutionized the modern electronic industry [1].

In 1959, the swiss physicist Jean Hoerni at Fairchild Semiconductor invented the planar process, in which optical lithographic techniques were used to diffuse the base into the collector and then diffuse the emitter into the base to produced a transistor. This process consists of three basic steps: Oxidization, Photolithography, and Etching. One of Hoerni's colleagues, Robert Noyce, invented a technique for growing an insulating layer of silicon dioxide over the transistor, leaving small areas over the base and emitter exposed and diffusing thin layers of aluminium into these areas to create wires, which led directly to modern ICs.

Gordon E. Moore, a co-founder of Intel, while working at Fairchild Semiconductor in 1964, foresaw that the number of components, as well as the functionality, that could be integrated on a single die would grow exponentially with time [4]. He also observed that the microprocessor performance (clock frequency  $\times$  instructions per clock) also doubles every 1.5 to 2 years. As years went by, it turned out that Moore was right, and it became less of a prediction and more of a self-fulfilling prophecy known as Moore's Law. It has been a goal and key performance indicator of successful leading-edge semiconductor products and companies for the past four decades.

#### 1.1.2 Packaging

Packaging is an essential and integral part of semiconductor products. According to [5], packaging serves major functions at the IC or device level, and at the systemlevel. At the IC or device level, it serves four purposes: interconnection of electrical signals, mechanical and environmental protection of circuits, distribution of power (i.e., electrical energy), and dissipation of heat generated by the semiconductor devices [5, 6, 7]. The approach for packaging must be selected based on the application, because system requirements for computer, handheld, automotive, medical, and bioapplications are all different. For example, miniaturization is more important for handheld devices than automotive applications. However, regardless of the application, the functionality and complexity of the IC have been increasing and driving the development of microelectronic packaging over the decades [5, 6, 7].

The microelectronics packaging technology started with the discovery of the transistor in the late 1940s, and has evolved to serve the increasing complexity and performance of the IC with the passage of time. Early transistors were housed in plastic packages providing just the protection for the device. Once the military became interested in highly reliable applications, the need for hermetic packages were incorporated to prevent transistor gain degradation and junction leakage current due to contamination and moisture. This led to the development of the metal Transistor Outline (TO) packages [7]. With the development of silicon planar technology, electronic packages were developed to fulfill the requirements of high performance ICs containing large numbers of devices as it affects the operating frequency, power, complexity, reliability, and cost of semiconductor products.

In much of the literature [5, 7] the evolution of microelectronic packaging is described starting with the Dual-In-line Package (DIP) of the 1970s. The DIP contained a single chip connected with wire-bonds to interconnections on the package, and the connections from package to system board were made with pins located on both sides of the package. As the Input/Output (I/O) count in chips increased with the passage of time, more connections were needed. Then, in the 1980s, the whole package area was filled with pins forming a Pin-Grid Array (PGA) package. Also at the same time, a Surface Mount Technology (SMT) was adopted for electronic production. SMT facilitated the assembly process, and the Quad-Flat Package (QFP) was introduced. Later, in the 1990s, area array SMT contacts provided by the Ball Grid Array (BGA) package started a new era in microelectronic packaging enabling much smaller package size. The evolution of packaging technology has increased the chip area to package area ratio, resulting in a much smaller, thinner, and lighter package with an increased number of I/O pins. This again has led to the Chip-Scale Package (CSP), which, by definition, is a package with an area of less than 1.2 times the area of the chip [8] and a pitch of a few hundred micrometers for the package I/O pads. At the beginning of the millennium, Wafer-Level Packages (WLP), Three-Dimensional (3-D) integration, stacked packages, and System-in-Packages (SiP) were adopted in the packaging industry to allow even higher packaging density. The latest packaging concept is the System-on-Package (SoP), which involves the integration of a whole system including passive components into a single package, leading to miniaturized systems [9].

# **1.2 Trends in Further Miniaturization**

### 1.2.1 Device and Interconnect Scaling

Historical facts reveal that the reduction of feature size used to fabricate ICs continues at a rate of 0.7 per year [2] in compliance with Moore's Law [4]. It is quite interesting to note that the smallest dimension on a wafer has been reduced from several times the size of a red blood cell (6-8  $\mu m$ ) to that of the common cold virus (20 nm). Table 1.1 summarizes the effects of technology scaling to the transistor and interconnect performance metrics. As can be seen from the table, technology scaling basically achieves three goals [10]: doubles the gate density, reduces the energy per switching by 65%, and decreases the gate delay by 30%.

#### **1.2. TRENDS IN FURTHER MINIATURIZATION**

To meet the technology goals, according to the simple interconnect scaling theory, interconnect cross-sectional dimensions are scaled at the same rate as gates' dimensions. As a result, the resistance of a unit length wire increases at the rate of 104% per year. In general, die area should decrease by 50% per year in successive technologies, but new designs integrate more transistors and functionality per chip, resulting in die area increment instead, and die size has been increasing at 13% per year. Consequently global interconnect length increases at a rate of 6% per year, and it's RC time constant increases by approximately 130% per year! Delay of wires has dominated that of gates, and the ratio of wire delay to gate delay increases at a rate of 300% annually. Therefore, designers have had to pay attention to the interconnect delay bottleneck.

As transistor count per unit area increases, the current required per unit area increases by 43%. At the same time, the wire resistance rises rapidly, increasing IR drop over wires. The worst effect of this is, with decreasing voltage, the tolerable IR decreases proportionally. To account for total interconnect length, and to optimize signal and power distribution networks effectively across the chip, manufacturers have added more interconnection layers, which adds to the design complexity.

When the linear dimensions scale by a factor, the voltage must also be scaled by the same factor to keep the electric field within a certain limit. However, a higher supply voltage is necessary to provide a performance boost, because transistor drive current is proportional to gate over drive  $(V_{dd} - V_t)^n$ , where n is in the range of 1-2. Recently, the International Technology Roadmap for Semiconductors

|        | Parameter                       | Symbol                                                                                        | Scaling/year |

|--------|---------------------------------|-----------------------------------------------------------------------------------------------|--------------|

|        | Dimensions                      | $W, L, t_{ox}$                                                                                | 0.7          |

|        | Supply Voltage                  | V                                                                                             | 0.7          |

|        | Drain Current                   | $I_{DS} \Rightarrow \frac{W}{L} \frac{1}{t_{ox}} V^2$                                         | 0.7          |

| CE     | Gate Capacitance                | $c_g \Rightarrow \frac{W\bar{L}}{t_{or}}$                                                     | 0.7          |

| Device | On Resistance                   | $c_g \Rightarrow \frac{W\bar{L}}{t_{ox}} \xrightarrow{V} R_{tr} \Rightarrow \frac{V}{I_{DS}}$ | 1            |

| р      | Intrinsic Delay                 | $\tau \Rightarrow R_{tr} c_g^{DS}$                                                            | 0.7          |

|        | Power Dissipation               | $P \Rightarrow VI_{DS}$                                                                       | 0.49         |

|        | Switching Energy                | $E \Rightarrow P\tau$                                                                         | 0.34         |

|        | Gate Density                    | $n \Rightarrow \frac{1}{WL}$                                                                  | 2.04         |

|        | Chip Area                       | A                                                                                             | 1.13         |

| CHIP   | Chip Edge                       | $y \Rightarrow \sqrt{A}$                                                                      | 1.06         |

| Ū      | Current per unit area           | $ \begin{array}{c} I_a \Rightarrow \frac{I_{DS}}{WL} \\ I_a y^2 \end{array} $                 | 1.43         |

|        | Total Chip Current              | $I_a y^2$                                                                                     | 1.61         |

|        | Cross-sectional Dimensions      | w,h,s,t                                                                                       | 0.7          |

|        | Resistance per unit length      | $r \Rightarrow 1/wt$                                                                          | 2.04         |

|        | Capacitance per unit length     | $c \Rightarrow w/h$                                                                           | 1            |

| E      | RC Constant                     | rc                                                                                            | 2.04         |

| WIRE   | RC delay/Gate Delay             | rc/	au                                                                                        | 2.9          |

|        | Local Interconnection Length    | $L_l$                                                                                         | 0.7          |

|        | Local Interconnection RC delay  | $rcL_l^2$                                                                                     | 1            |

|        | Global Interconnection Length   | $L_g \Rightarrow y$                                                                           | 1.06         |

|        | Global Interconnection RC delay | $rcL_g^2$                                                                                     | 2.29         |

Table 1.1: Constant Field Scaling of Device and Wire Properties [2, 6, 11].

(ITRS) predicts a slow down for scaling maximum supply voltage in the nanometer regime due to the inability to further reduce threshold voltage due to leakage power consumption and process variations. Moreover, lowering supply voltage on one hand reduces the dynamic power consumption, and on the other hand naturally increases operation current, which in turn requires thicker metal layers in order to reduce IR drop. Total chip current increases at an annual rate of 61%, thus creating challenges in power distribution system design and in package level thermal management [2].

Transistor switching energy is reducing at an annual rate of 66%, and it is reaching the minimum energy that must be transferred in a single interconnect's binary transition, which is  $E_s = kTln(2)$ , where k is Boltsmann's constant and T is absolute temperature [3, 12]. In essence, in the regime of tera-scale integration innovative and radical changes in logic devices are essential to overcome the challenges that hinder the performance and reliability of electronic systems.

#### 1.2.2 Integrated Circuit Packaging

As narrated, the continuous reduction of cost per function has been the key to exponential growth of electronic industry. But, the cost of assembling and packaging ICs has not kept pace with the cost reduction in wafer fabrication; packaging cost exceeds the wafer production cost. Other driving forces for the evolution of electronic packaging are performance, size and volume, time-to-market and reliability.

As the technology advances towards nanometer generations, density and performance of individual chips are continually enhanced. Unfortunately, today, not all of these merits can be translated to the system level due to the problem of electronic packaging, which has presented a bottleneck for increasing system speed, reducing power, and shrinking system size [5, 7].

When the complexity of chips expand, the number of I/O pins rises exponentially according to Rents rule [13], which consequently increases wiring demands for system level interconnections. Thus, in order to provide enough wires for system interconnections at a reduced substrate size, interconnect pitch has to be reduced providing stringent limits on signal integrity at the package-level.

| Technology             | Wire-bond | Solder bump | Adhesive bumps | Micro-via    |

|------------------------|-----------|-------------|----------------|--------------|

| Resistance $(m\Omega)$ | 30 - 100  | 1.0-3.0     | 15-30          | 0.2-1.0      |

| Inductance $(nH)$      | 1.0-3.0   | 0.05-0.1    | 0.05-0.1       | 0.01-0.3     |

| Capacitance $(pF)$     | 0.01-0.05 | 0.002-0.01  | 0.002-0.01     | 0.0002-0.001 |

| Discontinuities        | Severe    | Moderate    | Moderate       | None         |

**Table 1.2:** Typical values of parasitic components in different chip interconnection technologies[8].

When chip speed is higher than several hundred MHz, the package exhibits very large parasitic effects. For example, in today's VLSI chips, the chip I/O pads are still quite large, which requires very large buffers and off-chip drivers for off-chip communications. In addition, the package itself and on-board interconnects have much larger dimensions than that of the on-chip's. They are hence large loads for the off-chip drivers. Besides the higher power consumption and larger chip size for these off-chip drivers, system performance is severely degraded. With higher

#### **1.2. TRENDS IN FURTHER MINIATURIZATION**

operating frequencies and signal rise time shorter than two and a half times the timeof-flight, transmission line effects become significant. Consequently, preservation of signal integrity and timing becomes a difficult challenge as signals move from chip to chip within the system. Table 1.2 summarizes typical values of chip to package interconnection parasitic parameters. Also, it is essential to minimize impedance discontinuities at chip-to-package and package-to-board interconnection junctions and reduce cross-talk noise between adjacent lines.

The dearth of I/O pins also places more restrictions on the power supply network design, as more gates per pin means longer current paths and increased current in each path, requiring more on-chip bypass capacitance [5, 11]. With the area array bonding techniques where the pins are placed over the entire surface of the package, the number of pins grow with the square of the chip dimension. Also with the elimination of bond wire inductance, and the resistive drop over the on-chip power supply grid is much less, as the current paths are shorter. This eases the requirements on on-chip bypass capacitance, but there still exists a need for innovative off-chip signalling schemes. Multi-chip packaging techniques, where several chips exist in one package in a vertical stack (SiP), and the inter-chip links are implemented locally, are another option to System-on-Chip (SoC).

As per most of the predictions if the current technology scaling continues without particular low power design techniques, the power density of future microprocessors will be a main limiting factor. With the dimension of chip and package scaling down and clock frequency scaling up, electronic products have experienced a dramatic increase in power density. The task of dissipating heat from ICs while maintaining acceptable junction temperature has been a significant challenge for semiconductor and system manufactures. With low power circuit and system architectures, it is projected that in 2013, power dissipation of a high-performance CMOS chip will be around  $0.64 W/mm^2$  while its area is around 750  $mm^2$ , and the maximum allowable junction temperature is about 90 °C [2]. This will result in a thermal resistance budget at 0.19 °C/W for the whole module, indicating a great challenge for heat removal in high performance products even with power efficiency circuit and system architectures.

## 1.2.3 Dealing with Complexity: System-Level Integration

As the functionality and the number of gates in a chip has increased, the chip complexity has also increased. Hence, a modular based approach is used. Today, for example, an IC performs very different functionalities and uses diverse implementation styles such as processor cores, DSP blocks, FPGA blocks, analog/RF circuits and memory, and it is designed from blocks of such interconnected resources - the overall system is designed at a higher abstraction level. Usually such building blocks can be shared and also re-uses as Intellectual Property (IP) blocks, which further improves the productivity and reduces the time-to-market. This methodology has been termed as *System-on-a-Chip*.

Many of today's systems consists of complex SoCs with embedded processors, significant amounts of memory and FPGAs, but they do not provide the total system solution for real world systems. Such electronic systems digital and storage blocks coexists with many other functional devices such as analog/RF, passive components, sensors, and biological functions. These sensors and biological functions

can be non-CMOS and non-silicon technologies, with different design and implementation styles. In integrating such disparate technologies in to a single chip, designers are confronted with many technical and economic barriers [2, 14], namely huge initial investment for masks and their development, process dependent memory blocks, high precision analog blocks and the management of substrate coupled noise, and process incompatibility with non-Si materials and/or MEMS. The mask count increases as much if different types of technologies merge together to form a single die. For example, dozens of smaller chips with different functionalities are interconnected on a substrate using chip-to-chip interconnections, and packaged as a single module. System level integration methodologies are preferred to overcome most of the above mentioned barriers, reduce time-to-market, and offers greater flexibility than single chip solutions.

Multi-chip modules (MCMs) were introduced by IBM in 1970s to enable highperformance systems and in such a system dozens of smaller chips have been interconnected. The MCM technology allows the chips to be spaced more tightly with less volume and weight than individually packaged ICs. There are three major variations of MCM implementations: MCM-D, a multilayer, thin-film structures on semiconductor or ceramic base layers, with deposited metal conductors and dielectrics; MCM-C, a thick-film or co-fired ceramic technology; and MCM-L, organic laminated multilayer boards.

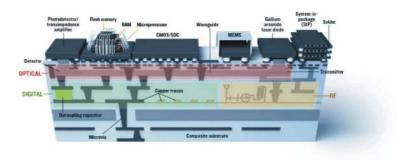

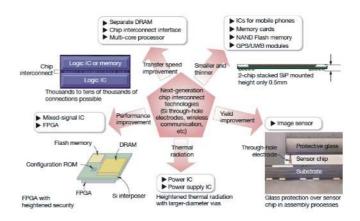

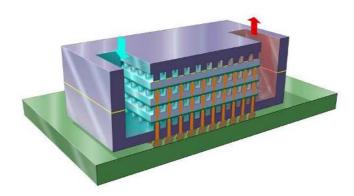

**Figure 1.3:** System-on-Package, latest packaging concept, is involved in integrating a whole system into a single package [15].

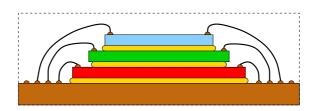

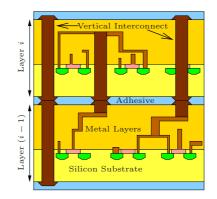

Moreover, due to ever increasing demands for low cost, smaller chips with more functionality, and smaller time-to-market for portable systems, vertical integration found to be an attractive option. Interconnecting bare or packaged chips in the vertical dimension, known as three-dimensional integration.

By contrast, stacking packaged dies sometimes known as Package-on-Package (PoP) - has its own advantages, including the ability to integrate chips from multiple suppliers and different IC technologies, such as analog, digital, mixed-signal, RF, and optoelectronic. In addition, packaged dies can be tested and burned in before being stacked. Stacked packaging and wafer-level packaging methods are both rising in popularity. After 3-D designs, the next highest efficiency can be achieved by wafer-level packaging, especially CSP designs. These provide a footprint that is just barely larger than the size of the die.

#### 1.3. INTERCONNECT CHALLENGES AND STRATEGIC SOLUTIONS

Multiple-die packages must address key logistics issues, such as being able to accommodate incompatible die shrinks; simplify management of multiple IC vendors; enable package-level test and burn-in; enable the combination of high- and low-yield devices; contribute to product quality and reliability; maximize configuration flexibility and minimize time to market; and risk, because time is our most precious commodity.

Figure 1.4: Moore's Law and More - all the functions in a Electronic System does not scale with Moores Law [2].

# 1.3 Interconnect Challenges and Strategic Solutions

Continued transistor scaling will not be as straightforward in the future as it has been in the past because fundamental material and process limits are rapidly being approached. Meindel *et.al.* in [3] derived five key fundamental limits for Tera-scale integration from thermodynamics, quantum mechanics, and electromagnetism. These limits are independent of material, device structure, circuit configuration, or system architecture.

The problem of interconnect delay and the possible solution domain can be explained simply by the RC time constant of a wire [16, 17], which is:

$$\tau = rcL^2 = \frac{\rho}{wt} \frac{\epsilon w}{t} = [\rho \epsilon] \left[ \frac{1}{ht} \right] [L^2].$$

(1.1)

As (1.1) expresses, the growing interconnect delay issue can be addressed by material processes, reverse scaling (reduce the width while maintaining the same aspect ratio) and reducing interconnect length.

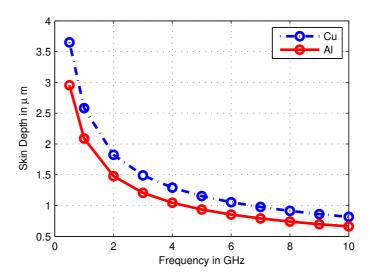

Copper (Cu) interconnects perform better than aluminium (Al) because resistivity of Cu is approximately 40% lower than that of aluminium [18]. Also, Cu has a higher resistance to electromigration effects. Electromigration lifetime of Cu is

#### **CHAPTER 1. INTRODUCTION**

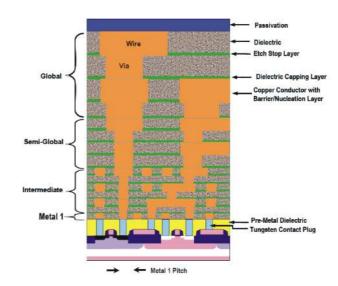

Figure 1.5: Cross-section of Hierarchical Wiring with steadily increasing pitch and thickness at each conductor levels to alleviate the impact of interconnect delay on performance [2].

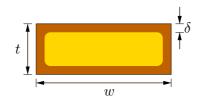

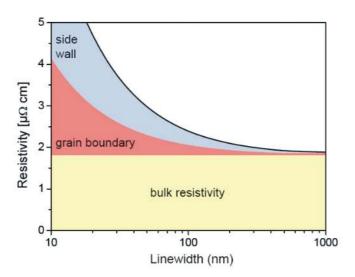

about 100 times longer than Al at the same current density. However, a drawback with Cu as interconnect material is that Cu readily diffuses in most dielectrics and acts as a recombination center in Silicon. Hence, a metallic (such as Ta, TaN) or dielectric (such as SiN, SiC) diffusion barrier is generally needed to encapsulate a Cu line to prevent electrical leakage and degradation of transistor performance. These barrier films have much higher resistivity than Cu and approximately 20% of the wire width is consumed by the film. Also, the cross-sectional dimesion of the wire is close to the electron mean free path hence the electron scattering effect at the conductor surface as well as the grain boundaries result in increased resistance.

In order to reduce the rate of resistance increase, the thickness is increased to achieve a larger cross-section, which leads to tall and thin wires. Contemporary technologies use wires with an Aspect Ratio (AR) approximately equal to 2-2.5. By doing so, the annual increment of RC constant can be maintained at a constant rate, and the delay over a global wire increases at a rate of 13% per year. Nonetheless, the continuous increment of aspect ratio will not bring similar benefits because the reduction in resistance will be offset by the dominance of inter-wire capacitance to the total wire capacitance. The impact of this effect is a rise in coupling noise, which is in two forms: cross-talk and signal integrity, and dynamic delay. Since the reduction in packing density is not an option, the only way of reducing capacitance is to use low permitivity (low- $\kappa$ ) dielectrics instead of SiO<sub>2</sub> whose dielectric constant is about 3.9. The low- $\kappa$  and porous SiO<sub>2</sub> currently being proposed are not robust enough to withstand assembly and packaging process such as wire bonding. IBM, who introduced the Cu/low- $\kappa$  interconnect technology has announced recently their new strategy to use air gaps as dielectric for the power hungry advanced technology nodes.

As is evident from (1.1), another key technique in reducing interconnect delay is

#### **1.3. INTERCONNECT CHALLENGES AND STRATEGIC SOLUTIONS**

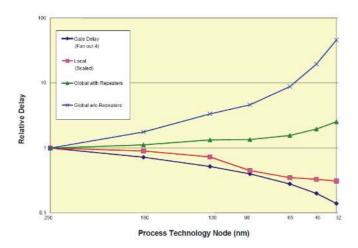

**Figure 1.6:** Delay for Metal 1 and Global Wiring versus Feature Size. From 180nm down to 15 nm, the delay of scaled wires increases by approximately 10 ps while that of fixed length wires increases by about 2000 ps. If these wires are modified with repeaters, these delays reduce to approximately 3 ps for scaled wires and 40 ps for fixed length wires. [2].

to reduce its length. The most simple way to do is to insert repeaters by breaking the wire into several sections [19, 20]. Usually these wire sections are highly capacitive and high strength repeaters are needed. The adverse effect of this is increased power consumption; it has been estimated that over 50% of the power in a high performance microprocessor is dissipated by repeaters charging and discharging interconnects [21, 22, 23]. Further, over 90% of this power is concentrated in only 10% of the interconnects; *i.e.* those which are classed as global and run for a significant fraction of the die length. The length of global interconnects can effectively be reduced by integrating blocks in a stack and hence power consumption can be reduced significantly.

## 1.3.1 Emerging Solutions - Alternatives for Cu/Low- $\kappa$

For some of the manufacturing challenges and limitations in Cu/low- $\kappa$  interconnect systems, the strategic solutions for the technology node beyond 45 nm is not shown. Alternative to that some predominant options for interconnect design are of greater importance for further miniaturization because: there are no metals with conductivity significantly higher than that of copper; Dielectric constants cannot go below 1, and to achieve dielectric constants below 2.5 porosity needs to be incorporated into the material, which weakens it; and unlike transistors, scaling or shrinking deteriorate the performance of interconnects, and that deterioration will (already has) become a significant limiter in overall circuit performance.

The performance limitation of interconnects and packaging shows clearly the inadequacy of conventional solutions to meet the overall performance requirements in high performance electronic systems in the nanometer regime. Traditionally, the interconnect requirements have been met through distinctly separate functions of

#### **CHAPTER 1. INTRODUCTION**

**Figure 1.7:** Next generation chip interconnect technologies, such as Si through-hole vias. They boost chip-to-chip data transfer tares, contribute to smaller and thinner chips with higher performance, and improve heat radiation and yield [24].

on-chip interconnects, package, silicon chip, and board-level technologies, but integrated system level solutions are required for growing interconnect and packaging challenges.

ITRS [2] suggest some of the possible solutions which can and have already been proven to be effective in alleviating tyranny of interconnects. They are:

- Use different signaling methods: Circuit techniques, signaling techniques such as multi-level, near speed of light, signal coding techniques. (Uses the available technology with innovative approaches to reduce delay, crosstalk etc.)

- Innovative design and package options: interconnect-centric design, Package intermediated interconnect, Chip-Package co-design

- Use geometry: Three-Dimensional integration (reduces the wire length)

- Use different physics: optics, RF microwaves, Tera-hertz photonics (introduce different information carriers other than charge.)

- **Radical Solutions**: Nanowires/nanotubes, Molecules, Spin, Quantum wave functions

# 1.4 Scope of Thesis and Author's Contribution

During the last decade KTH has a track record of research in response to interconnectcentric design [25, 26], chip-package co-design [27], and different signaling and interconnect optimization strategies [25, 26]. The scope of this thesis is the design, modelling and analysis of system interconnections and their effects in massively integrated 3-D ICs under cost, performance, and other technological constraints. The technical contributions of this thesis are three-fold: signalling techniques for global on-chip interconnects; cost, performance and technological trade-offs for 2-D and 3-D mixed-signal ICs; and electrical modelling of Through-Silicon Vias (TSV) in 3-D ICs. The author's contributions are discussed in the next few sections, with a brief summary and key publications.

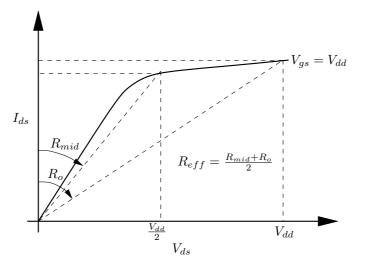

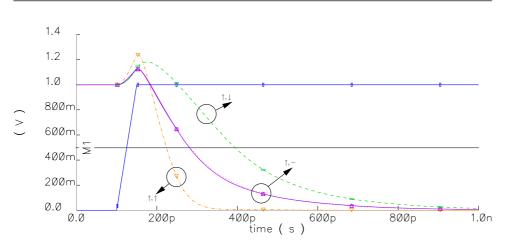

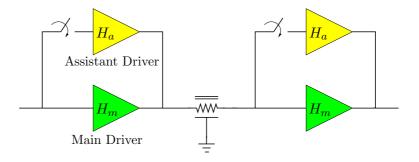

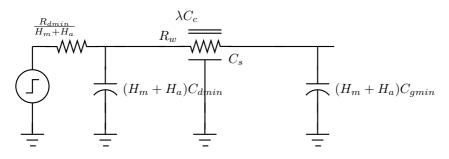

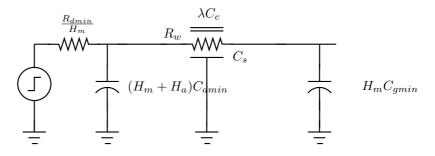

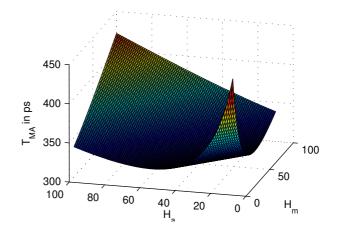

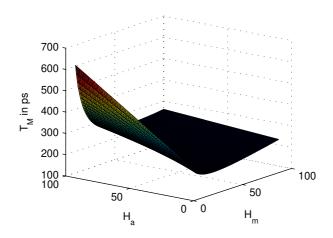

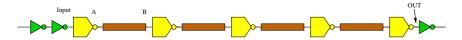

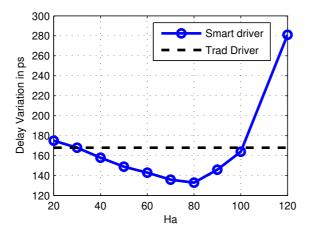

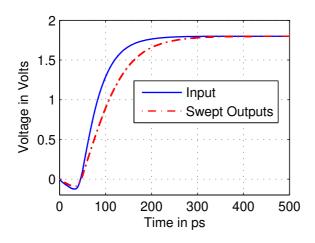

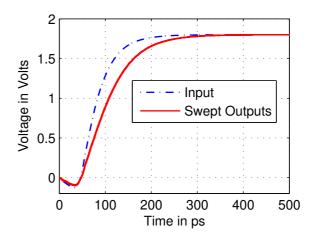

# 1.4.1 Smart Repeaters for Interconnections in Nanometer Technologies

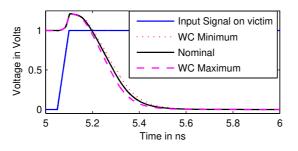

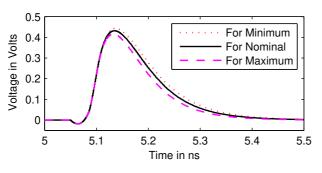

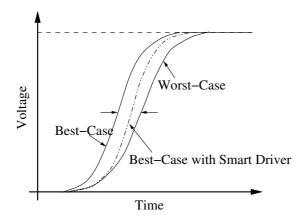

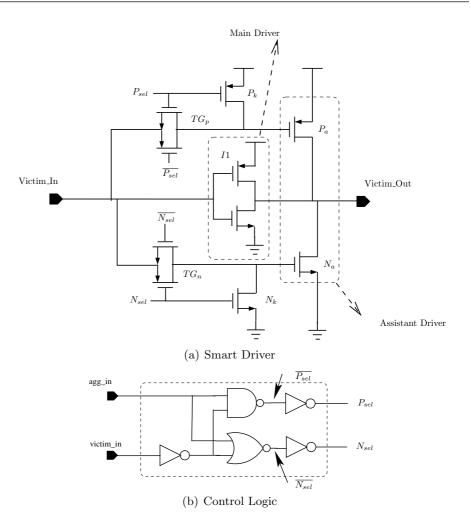

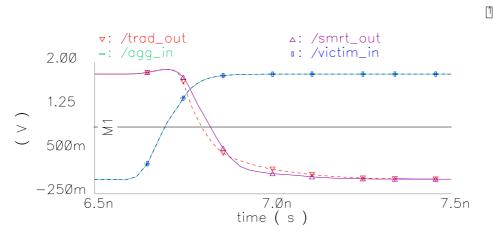

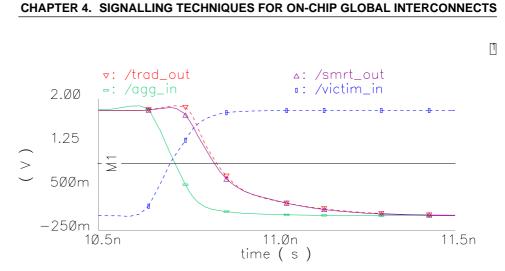

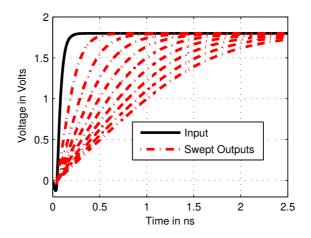

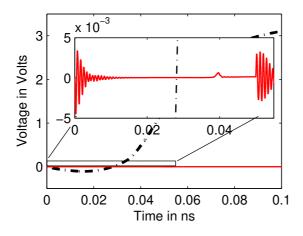

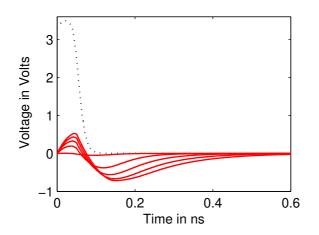

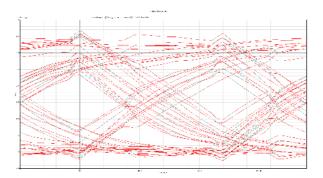

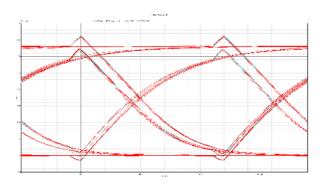

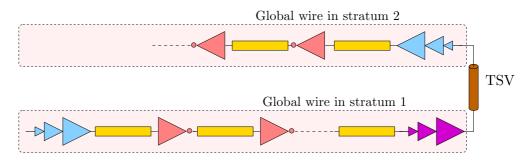

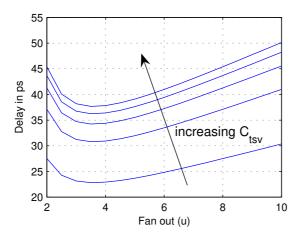

Summary: Smart repeaters exploit the fact that in a parallel wire structure, the effective capacitance of a given wire is dynamic; i.e. it is a function of not only the physical geometry, but also the relative switching pattern described by the bits on the wire in question (the victim) and the adjacent wires (aggressors). With a traditional repeater, since the drive strength is static, the result is a spread of the propagation delay, with the repeater strength being essentially too much for every bit pattern other than the worst-case pattern. In the proposed repeater, the drive strength is dynamically altered depending on the relative bit pattern, by partitioning it into a Main Driver and Assistant Driver. For a higher effective load capacitance both drivers switch, while for a lower effective capacitance the assistant driver is quiet. By disconnecting part of the repeater when it is not needed, the total load capacitance to the previous stage is reduced, resulting in reduced energy consumption for those instances. It is experimentally shown that for a UMC 0.18  $\mu m$  technology the potential energy saving is 10% over a traditional repeater for typical global wire lengths. Also, with the technology scaling the potential average saving in energy can be as much 20%-30% for typical global wire lengths in nanometre technologies.

<u>Author's Contribution:</u> The first author came up with the concept, carried out analytical work on dynamic energy saving and the timing model, designed the circuit, carried out the simulations, and wrote the manuscripts of all of the following publications.

Related Publications:

Roshan Weerasekera, Li-Rong Zheng, Dinesh Pamunuwa and Hannu Tenhunen, "Switching sensitive interconnect Driver to Combat Dynamic Delay in on-Chip Buses," in *Lecture Notes in Computer Science (Proceedings of PATMOS)*, vol. 3728, pp. 277-285, 2005.

Technical Contribution in the paper: This paper proposes a switching pattern dependent-driver and provides circuit-level proof of concept.

Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng and Hannu Tenhunen, "Minimum-Power, Delay-Balanced Drivers for interconnects in the Nanometer Regime," in *Proceedings of the international workshop on System-Level Interconnect Prediction*, German, March, 2006, pp. 113-120.

Technical Contribution in the paper: A methodology for design of the SMART repeater is proposed and a high-level analysis of the energy saving is presented.

3. Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng and Hannu Tenhunen, "Delay-Balanced Smart-Repeaters for on-chip Global Signaling", in PProceedings of the 20<sup>th</sup> International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems, 2007, pp. 308-313.

<u>Technical Contribution in the paper:</u> The circuit level implementation of the smart repeater, a first order delay model, power and delay comparison, crosstalk, and sizing of assistant and main driver for different coupling capacitances are presented.

Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng and Hannu Tenhunen, "Minimal-Power, Delay-Balanced Smart Repeaters for Global Interconnects in the Nanometer Regime", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 16, no. 5, pp. 589-593, May, 2008.

Technical Contribution in the paper: Energy and timing models, driver circuit design, and experimental verification of the models have been revisited.

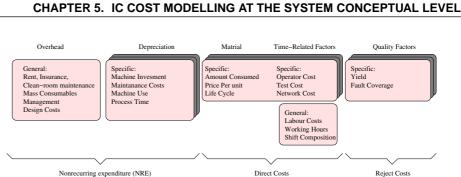

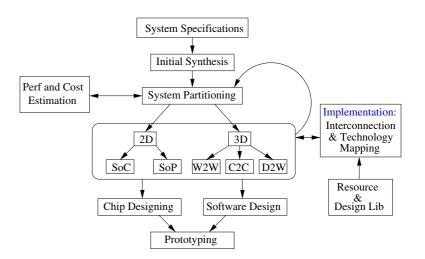

# 1.4.2 Cost and Performance Trade-offs for 2-D and 3-D Mixed-Signal ICs

Summary: Because of today's market demand for high-performance, high-density portable hand-held applications, electronic system design technology has shifted the focus from 2-D planar single-chip solutions to alternative options such as tiled silicon and single-level embedded modules as well as 3-D integration. Among the various choices, finding an optimal solution for system implementation deals usually with cost, performance and other technological trade-off analysis at the system conceptual level. It has been identified that decisions made within the first 20% of the total design cycle time will ultimately affect up to 80% of the final product cost. In this work, we discuss appropriate and realistic metrics for performance and cost trade-off analyses both at system conceptual level (up-front in the design phase) and at the implementation phase for verification in the 3-D integration. In order to validate the methodology, two ubiquitous electronic systems are analyzed under various implementation schemes and the pros and cons of each of them are discussed.

<u>Author's Contribution:</u> The author came up with the idea, derived all the models, carried out the analyses, and wrote the manuscripts of all the following publications.

Roshan Weerasekera, Li-Rong Zheng, Dinesh Pamunuwa and Hannu Tenhunen, Weerasekera, Roshan; Li-Rong Zheng,; Pamunuwa, Dinesh; Tenhunen, Hannu, "Early selection of system implementation choice among SoC, SoP and 3-D Integration," in *IEEE International System-on-Chip Conference*, September, 2007, pp.187-190.

Technical Contribution in the paper: A preliminary description on yield, cost, and performance models for SoC, SoP, and 3-D integration for trade-off analyses are presented in this paper.

#### 1.4. SCOPE OF THESIS AND AUTHOR'S CONTRIBUTION

Roshan Weerasekera, Li-Rong Zheng, Dinesh Pamunuwa and Hannu Tenhunen, "Extending Systems-on-Chip to the Third Dimension: Performance, Cost and Technological Tradeoffs," in *Proceedings of the IEEE/ACM international conference on Computer-aided design*, IEEE Press, November, 2007, pp. 212-219.

Technical Contribution in the paper: An extensive discussion on the yield, cost, thermal issues and performance of 2-D and 3-D integration options are carried out in this paper.

Roshan Weerasekera, Dinesh Pamunuwa, Li-Rong Zheng and Hannu Tenhunen, "2-D and 3-D Integration of Heterogeneous Electronic Systems under Cost, Performance and Technological Constraints," in *IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems*, September, 2008, Under Review.

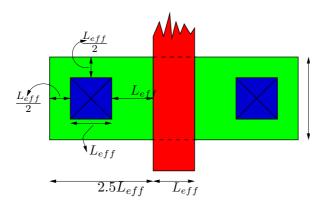

<u>Technical Contribution in the paper:</u> Yield, cost and performance models presented in first and second papers have been refined introducing the effects of thermal-via insertion to reduce excess heat generated in 3D-ICs and the testing cost.

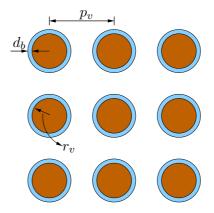

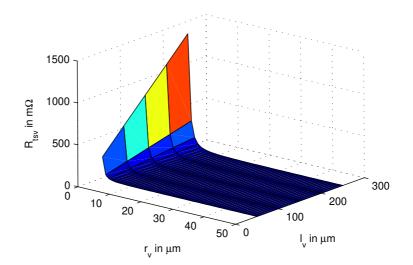

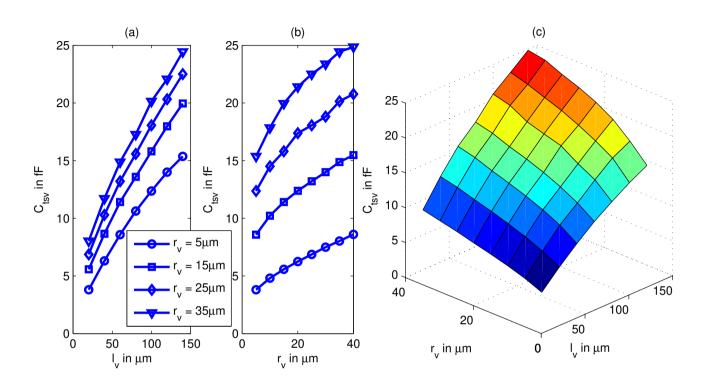

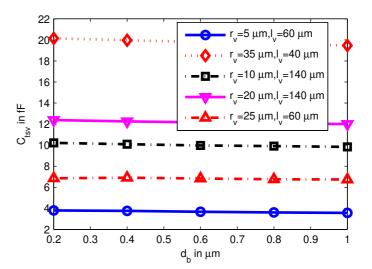

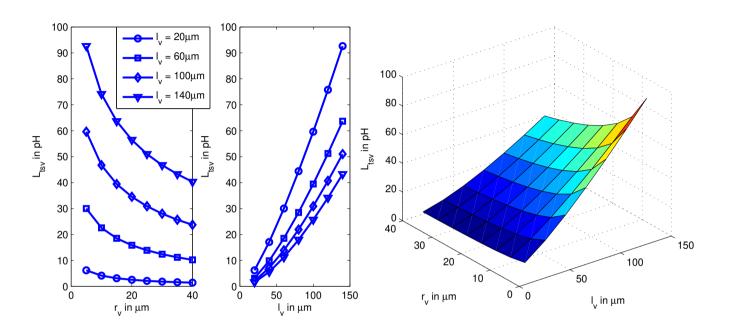

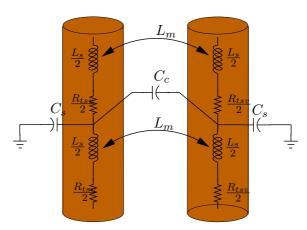

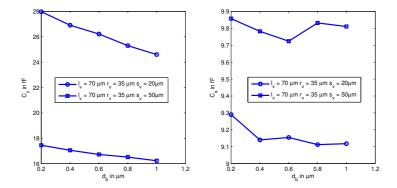

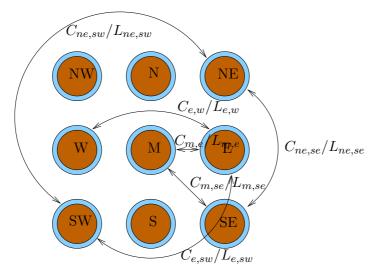

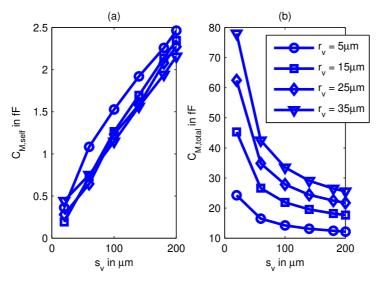

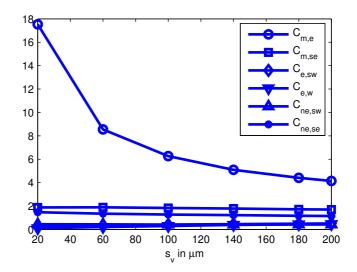

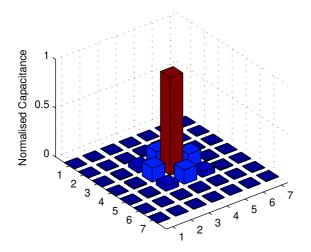

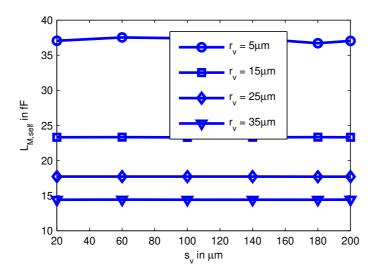

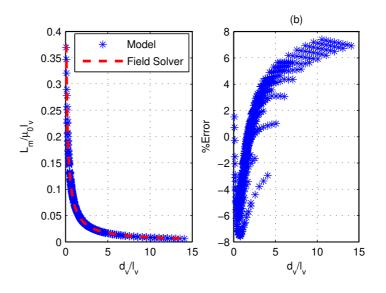

# 1.4.3 Electrical Modelling of Through-Silicon Vias in 3-D Integrated Circuits

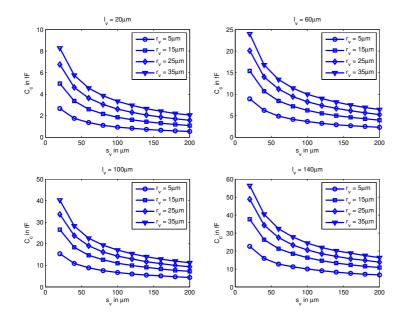

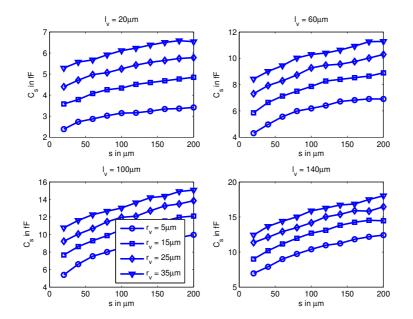

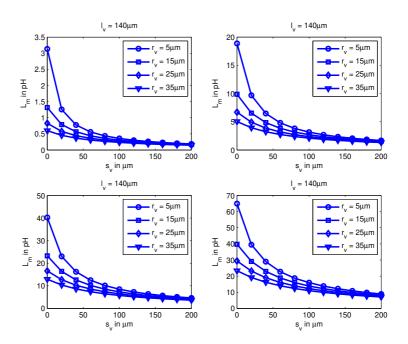

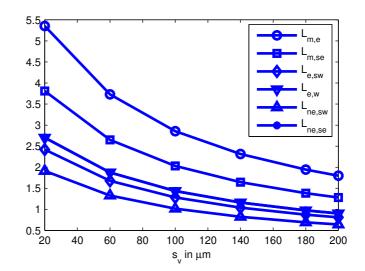

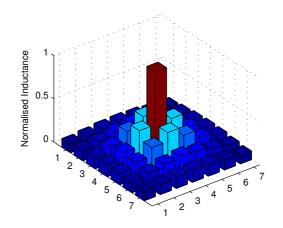

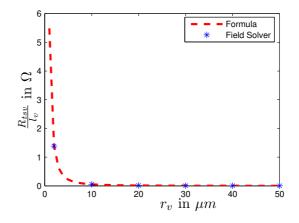

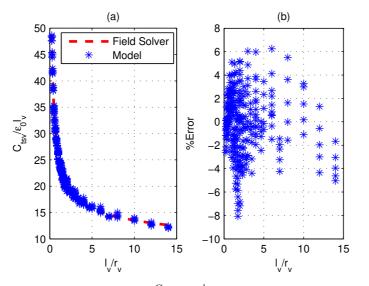

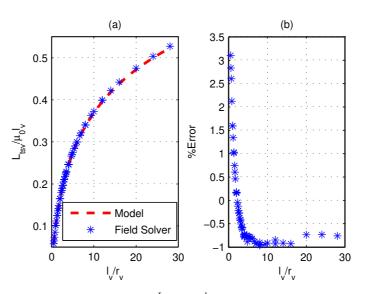

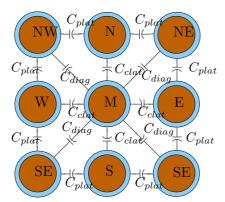

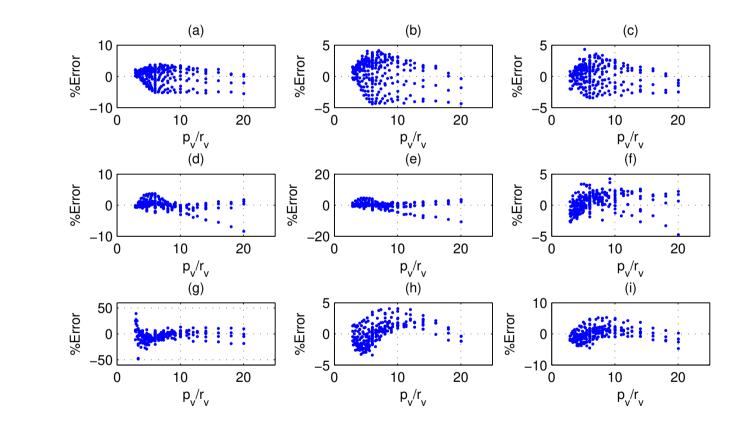

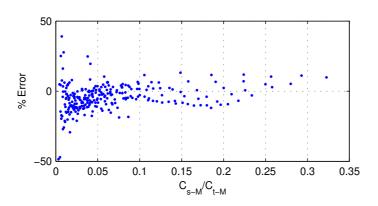

Summary: Parasitic parameter (resistance, capacitance, and inductance) extraction of TSV structures is a critical step towards a successful physical design of three-dimensional integrated circuits. Various TSV structures starting from a lone TSV and going up to a  $3 \times 3$  bundle have been simulated in a field solver with varying geometrical parameters, and its electrical parameters have been extracted. Then, a set of novel closed-form equations are proposed for TSV parasitics in terms of physical dimensions and material properties, allowing the electrical modelling of TSV bundles without the need for computationally expensive field-solvers. Finally, suitable equivalent circuits including capacitive and inductive coupling are derived, and comparisons with field solver provided values are used to show the accuracy of the proposed parasitic parameter models for the purpose of performance and SI analysis.

<u>Author's Contribution:</u> The author came up with the idea, built the test structures, analysis methodology, derived the empirical formulae, and wrote the manuscripts of the following publications.

1. Roshan Weerasekera, Dinesh Pamunuwa, Hannu Tenhunen, and Li-Rong Zheng, "Modelling Through-Silicon-Vias in 3D-ICs," *IET Electronic Letters*, September, 2008, Under Review.

Technical Contribution in the paper: This paper proposes novel compact closedform equations for TSV parasitics in terms of physical dimensions and material properties allowing electrical modelling of TSV bundles without the need for computationally expensive field-solvers.

2. Roshan Weerasekera, Dinesh Pamunuwa, Matt Grange, Hannu Tenhunen, and Li-Rong Zheng, "Parasitic Parameter Estimation and Electrical Modelling of Through-Silicon Vias in 3-D ICs," *IEEE International Symposium* on Circuits and Systems 2009, Under Review.

<u>Technical Contribution in the paper:</u> This is a detailed discussion of the compact closed-form equations proposed in paper 1 for TSV parasitics with delay and noise amplitude estimations using extracted and predicted parasitics.

Matt Grange, Roshan Weerasekera, Dinesh Pamunuwa and Hannu Tenhunen, "Exploration of Through Silicon Via Interconnect Parasitics for 3-Dimensional Integrated Circuits" *IEEE International Symposium on Circuits* and Systems 2009, Under Review.

Technical Contribution in the paper: Trends in TSV bundle parasitics, signal integrity issues and related metrics are discussed.

4. Roshan Weerasekera, Matt Grange, Dinesh Pamunuwa, Hannu Tenhunen, and Li-Rong Zheng "Modelling and Analysis of Through Silicon Via Interconnects in 3-Dimensional Integrated Circuits" In submission to IEEE transactions of VLSI.

Technical Contribution in the paper: Trends in TSV parasitics, their empirical models, and signal integrity issues are throughly discussed in this paper.

# 1.5 Thesis Organization

This thesis is organized into seven chapters. Chapter one is the introduction to the thesis where the historical evolution and trends in electronic system design, research overview and author's contribution are discussed. The second chapter provides basic theoretical background for interconnect modelling and analysis. Trends in TSV parasitics and novel compact closed-form equations for them are proposed in Chapter 3. In Chapter 4, signalling techniques suitable for on-chip global interconnects for 2-D and 3-D integrated circuits are presented. Based on the process and gate level data available, a system conceptual level chip/die parameter estimation methodology is discussed in Chapter 5. These models are not originally from the author's research work, but a comprehensive collection and some changes being made in compliance with the current needs. Using these system level parameters, yield and cost models for various packaging options are derived. Chapter 6 discusses the cost and performance trade-off analysis methodology for 2-D and 3-D integration are presented with two case studies. In Chapter 7, the conclusions and future work is elaborated. 2

# **Interconnect Modelling and Analysis**

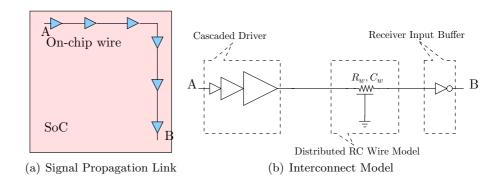

This chapter serves as a general introduction to the research issues discussed in this thesis. It starts by discussing non-idealities in wires, and carries out a comprehensive review on established parasitic estimation techniques and electrical modelling from low to high frequencies for wires. The chapter ends with a discussion of delay estimation models.

# 2.1 Introduction

$\mathbf{T}$  he significant difference between any two electronic system, for example a personal computer and a washing machine controller is the pattern of interconnections between various active and passive components. These interconnections or wires carry signals from one place to another and make up the different functionality that the user expects. Thus, realizing the interconnections between various devices and modules make up an electronic circuit or system.

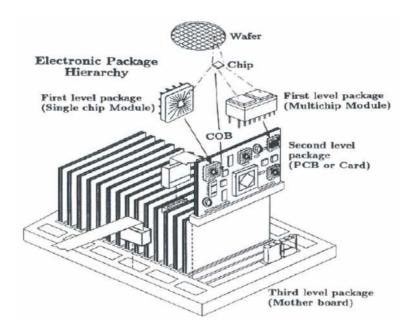

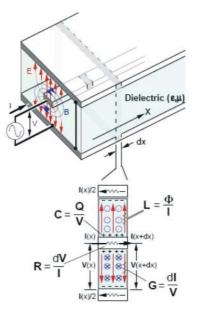

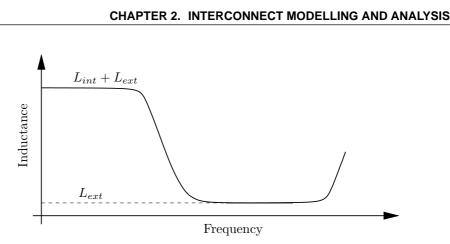

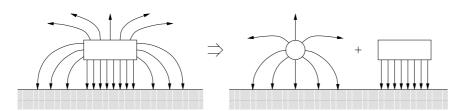

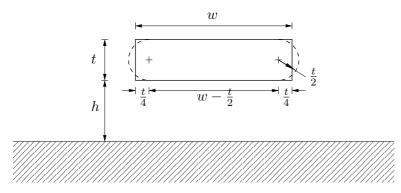

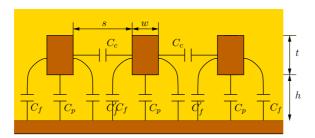

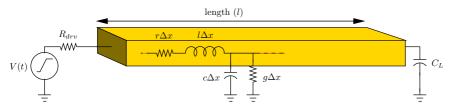

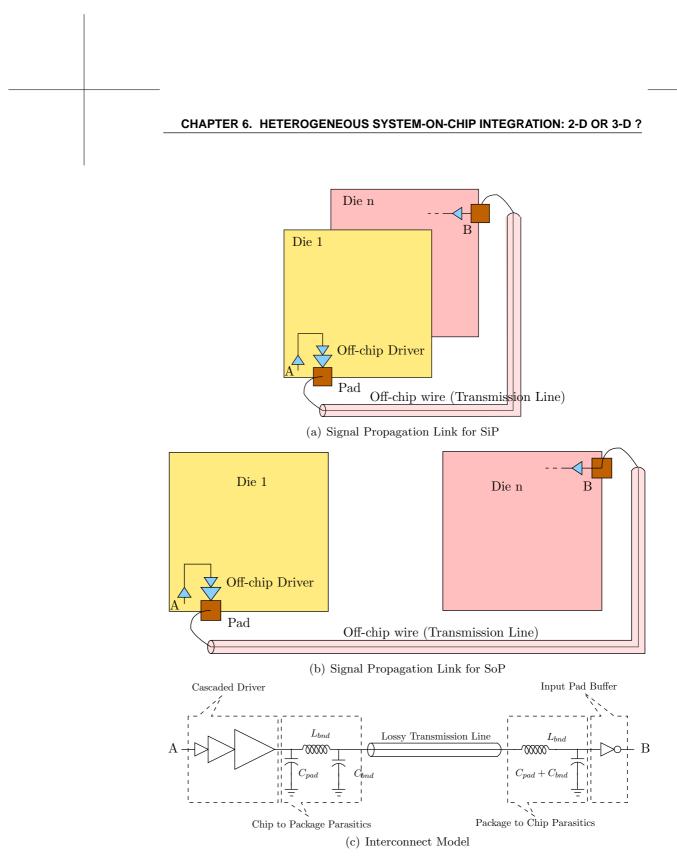

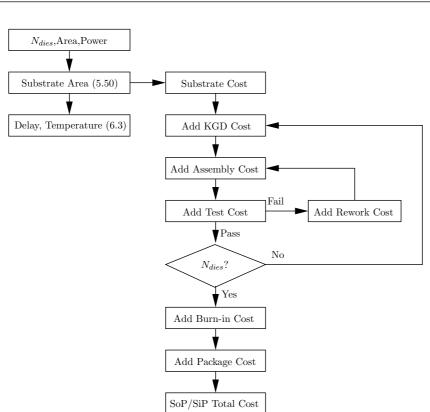

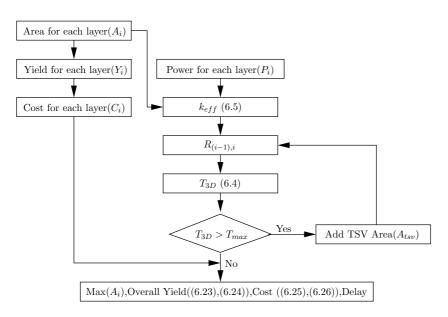

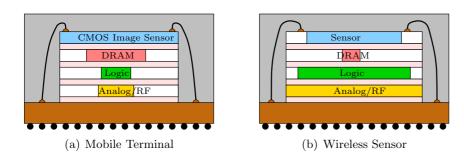

Electronic Systems are packaged in a hierarchy of chips, carriers, circuit boards, chassis and cabinets (Refer Figure 2.1). At each level of hierarchy, signals are transported on different kinds of interconnections. On-chip wires constitute the lowest level in a hierarchy that spans chip- to package-level connections (such as bond wires, package vias and solder balls, and package traces), circuit-board level connections (thick film wires), backplane-level wires (thick film metal layers or cables), chassis-level connections (more cables) and finally rack-level connections (such as bus bars made of solid metal straps or rods for power connections).