## SYSTEM-LEVEL METHODS FOR POWER AND ENERGY EFFICIENCY OF FPGA-BASED EMBEDDED SYSTEMS

PAWEŁ PIOTR CZAPSKI

School of Computer Engineering

A thesis submitted to the Nanyang Technological University in fulfillment of the requirement for the degree of Doctor of Philosophy

To My Parents

Acknowledgements

#### ACKNOWLEDGEMENTS

I would like to express my sincere appreciation to my supervisor Associate Professor Andrzej Śluzek for his continuous interest, infinite patience, guidance, and constant encouragement that was motivating me during this research work. His vision and broad knowledge play an important role in the realization of the whole work.

I acknowledge gratefully possibility to conduct this research at the Intelligent Systems Centre, the place with excellent working environment.

I would also like to acknowledge the financial support that I received from the Nanyang Technological University and the Intelligent Systems Centre during my studies in Singapore.

Finally, I would like to acknowledge my parents and my best friend Maciej for a constant help in these though moments.

Table of Contents

## **TABLE OF CONTENTS**

| Title Page        |                                                        | i    |

|-------------------|--------------------------------------------------------|------|

| Acknowledgements  |                                                        | iii  |

| Table of Contents |                                                        | iv   |

| List of Symbols   |                                                        | vii  |

| List of Abbre     | eviations                                              | X    |

| List of Figur     | es                                                     | xiii |

| List of Table     | S                                                      | XV   |

| Abstract          |                                                        | xvii |

| Chapter I         | Introduction                                           | 1    |

| 1.1.              | Introduction                                           | 1    |

| 1.2.              | Wireless sensor networks                               | 2    |

| 1.3.              | FPGA and MCU in WSN applications                       | 3    |

|                   | 1.3.1. Typical applications                            | 3    |

|                   | 1.3.2. Comparative analysis                            | 4    |

| 1.4.              | Scope, objectives, and thesis organization             | 5    |

|                   | 1.4.1. Scope                                           | 5    |

|                   | 1.4.2. Objectives                                      | 7    |

|                   | 1.4.3. Thesis organization                             | 9    |

| Chapter II        | Literature Overview                                    | 11   |

| 2.1.              | Power and energy issues in FPGA-based designs          | 11   |

|                   | 2.1.1. Power and energy issues in design               | 12   |

|                   | 2.1.2. Power consumption in FPGA                       | 13   |

|                   | 2.1.3. Power characteristics of FPGA                   | 15   |

|                   | 2.1.4. Power consumption estimation in FPGA            | 17   |

|                   | 2.1.5. Means of power consumption reduction in FPGA    | 18   |

|                   | 2.1.6. Advanced power reduction techniques in FPGA     | 19   |

| 2.2.              | Data processing in WSN applications                    | 24   |

|                   | 2.2.1. Sensing principles                              | 25   |

|                   | 2.2.2. Sensors selection for surveillance applications | 27   |

|                   | 2.2.3. Noise in typical sensing devices                | 29   |

|                   | 2.2.4. Data processing algorithms                      | 31   |

| 2.3.              | Data-reduction in WSN applications                     | 32   |

|             | 2.3.1. Introduction to data-reduction                       | 33 |

|-------------|-------------------------------------------------------------|----|

|             | 2.3.2. Typical WSN data-reduction algorithms                | 33 |

|             | 2.3.3. Data-reduction requirements in WSN's                 | 34 |

| 2.4.        | Algorithm partitioning of FPGA-based designs                | 35 |

| 2.5.        | Chapter summary                                             | 36 |

| Chapter III | Experimental Setup                                          | 38 |

| 3.1.        | Software tools and development platform                     | 38 |

|             | 3.1.1. Software                                             | 38 |

|             | 3.1.2. Hardware, and algorithms verification and validation | 39 |

| 3.2.        | Introduction to Handel-C                                    | 40 |

| 3.3.        | General assumptions and notions on results                  | 41 |

|             | 3.3.1. Hardware resources requirements                      | 42 |

|             | 3.3.2. Processing time requirements                         | 42 |

|             | 3.3.3. Power consumption estimates                          | 42 |

| 3.4.        | Chapter summary                                             | 44 |

| Chapter IV  | Power Estimates in System- and Low-Level Experiments        | 45 |

| 4.1.        | Introduction to conducted experiments and general           | 45 |

|             | assumptions                                                 |    |

| 4.2.        | Results of the experiments                                  | 47 |

| 4.3.        | Chapter summary                                             | 52 |

| Chapter V   | Relations Between Size of Design, Clock Domains, and        | 53 |

|             | Power Consumption                                           |    |

| 5.1.        | Introduction and general assumptions                        | 53 |

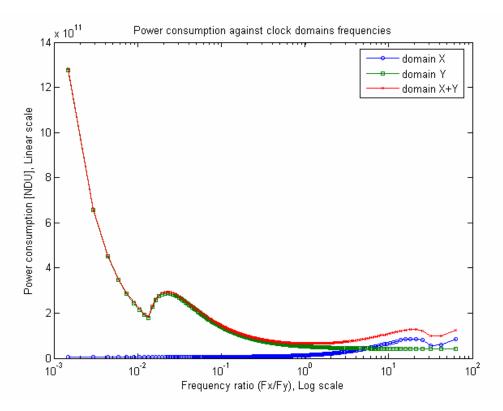

| 5.2.        | Experimental results                                        | 55 |

|             | 5.2.1. Power consumption and clock frequency                | 55 |

|             | 5.2.2. Multiple clock domains                               | 56 |

| 5.3.        | Chapter summary                                             | 63 |

| Chapter VI  | Parallel Partitioning of Algorithms                         | 64 |

| 6.1.        | Introduction and general assumptions                        | 64 |

| 6.2.        | Experiments                                                 | 65 |

|             | 6.2.1. Algorithm partitioning into parallel domains         | 65 |

|             | 6.2.2. Implementations details                              | 66 |

|             | 6.2.3. Results                                              | 72 |

| 6.3.        | Chapter summary                                             | 74 |

| Chapter VII     | Sequential Algorithm Partitioning                              | 76  |

|-----------------|----------------------------------------------------------------|-----|

| 7.1.            | Assumptions and methodology                                    | 77  |

|                 | 7.1.1. Algorithm partitioning                                  | 77  |

|                 | 7.1.2. Implementation details                                  | 79  |

| 7.2.            | Results                                                        | 79  |

|                 | 7.2.1. Selected algorithms and their partitioning              | 79  |

|                 | 7.2.2. Hardware requirements                                   | 80  |

|                 | 7.2.3. Processing time                                         | 81  |

|                 | 7.2.4. Device inactivity coefficient                           | 81  |

|                 | 7.2.5. Design inactivity coefficient from device inactivity    | 85  |

|                 | coefficient                                                    |     |

|                 | 7.2.6. Power and energy optimization                           | 88  |

| 7.3.            | Chapter summary and practical recommendations                  | 98  |

| Chapter VIII    | Data Processing and Transmission                               | 100 |

| 8.1.            | Introduction                                                   | 100 |

|                 | 8.1.1. Setup                                                   | 101 |

|                 | 8.1.2. Parameters of data processing algorithms and data       | 101 |

|                 | transmission                                                   |     |

|                 | 8.1.3. Power and energy estimates                              | 102 |

|                 | 8.1.4. Other general assumptions                               | 103 |

| 8.2.            | Results                                                        | 104 |

|                 | 8.2.1. System-level experiments                                | 105 |

|                 | 8.2.2. Hardware-level experiments                              | 107 |

| 8.3.            | Chapter summary                                                | 111 |

| Chapter IX      | Contributions and Future Works                                 | 113 |

| 9.1.            | Contributions                                                  | 113 |

|                 | 9.1.1. System-level power estimates                            | 113 |

|                 | 9.1.2. System-level design partitioning                        | 114 |

|                 | 9.1.3. Energy optimization in data processing and transmission | 115 |

| 9.2.            | Future works                                                   | 116 |

| List of Publica | tions                                                          | 118 |

| Lisi of Fublications | 110 |

|----------------------|-----|

| References           | 120 |

List of Symbols

## LIST OF SYMBOLS

## (The symbols are defined as below, unless specified in the context)

| a                            | a certain additive value                                   |

|------------------------------|------------------------------------------------------------|

| α                            | device inactivity coefficient (describing dynamic power    |

|                              | used in low switching activity period) of a certain device |

|                              | with a particular design implemented                       |

| $\alpha d$                   | design inactivity coefficient (describing dynamic power    |

|                              | used in low switching activity period) of a design (or a   |

|                              | clock domain)                                              |

| С                            | processing time (in clock cycles)                          |

| СС                           | amount of clock cycles required to process data            |

| <i>C</i> <sub><i>x</i></sub> | processing time (in clock cycles) of clock domain x        |

| <i>C</i> <sub>y</sub>        | processing time (in clock cycles) of clock domain y        |

| $C_i$                        | capacitance of resource i                                  |

| $\Delta f_x$                 | frequency change of clock domain <i>x</i>                  |

| $\Delta f_y$                 | frequency change of clock domain y                         |

| $\Delta t$                   | overall execution time change due to frequency changes     |

|                              | $\Delta f_x$ and $\Delta f_y$                              |

| $D_x$                        | denotes clock domain x                                     |

| $D_y$                        | denotes clock domain y                                     |

| Ε                            | total energy consumption                                   |

| $E_{bit}$                    | energy required to send 1 data bit                         |

| $E_{process}$                | processing energy                                          |

| $E_{send}$                   | sending energy                                             |

| $E_{total}$                  | total energy (spent on processing and sending data)        |

| f                            | clock frequency                                            |

| $f_i$                        | clock frequency of resource <i>i</i>                       |

| $f_x$                        | clock frequency of clock domain x                          |

| $f_y$                        | clock frequency of clock domain y                          |

List of Symbols

| hwa                | hardware area (or amount of the equivalent NAND gates)     |

|--------------------|------------------------------------------------------------|

| $h_{x}$            | hardware resources (system-level equivalent) used by clock |

|                    | domain <i>x</i>                                            |

| $h_{y}$            | hardware resources (system-level equivalent) used by clock |

|                    | domain y                                                   |

| $H_{_U}$           | hardware utilization coefficient                           |

| INDATAWIDTH        | input data bitwidth                                        |

| k                  | low-level-to-system-level dynamic power consumption        |

|                    | coefficient                                                |

| n                  | multiply factor                                            |

| OUTDATAWIDTH       | output data bitwidth                                       |

| OUTVOL             | amount of communicated data                                |

| $P_i$              | estimated dynamic power consumption for design with a      |

|                    | certain circuit replicated <i>i</i> times                  |

| Р                  | total dynamic power consumption                            |

| $P_{avg}$          | average dynamic power consumption                          |

| P <sub>total</sub> | total processing power (based on hwa and cc)               |

| $P_{DA}$           | dynamic power consumption of working design (in            |

|                    | simplified form)                                           |

| $P_{DU}$           | dynamic power consumption of inactive design (in           |

|                    | simplified form)                                           |

| SAMPLELENGTH       | total length of processed data sample                      |

| SAMPLELENGTH_LCL   | length of data processed locally                           |

| $S_{i}$            | switching activity of resource <i>i</i>                    |

| $S_{AD}$           | average switching activity of working design               |

| $S_{UD}$           | switching activity (averaged over the design area) during  |

|                    | inactivity period                                          |

| $S_{uncf}$         | switching activity averaged over the whole area of unused  |

|                    | part of FPGA                                               |

| t                  | total time of the whole algorithm execution or its part    |

| t <sub>exec</sub>  | data processing execution time                             |

|                    | execution time of algorithm part in clock domain x         |

| t <sub>x</sub>     | execution time of algorithm part in clock domain x         |

List of Symbols

| t <sub>y</sub> | execution time of algorithm part in clock domain y   |

|----------------|------------------------------------------------------|

| Т              | a certain execution time                             |

| $U_i$          | utilization of resource <i>i</i>                     |

| V              | voltage                                              |

| $V_{_{dd}}$    | power supply voltage                                 |

| $V_i$          | voltage swing of resource <i>i</i>                   |

| $V_{th}$       | threshold voltage                                    |

| x              | denotes clock domain x or its part                   |

| X              | denotes (also in figures) clock domain x or its part |

| У              | denotes clock domain y or its part                   |

| Y              | denotes (also in figures) clock domain y or its part |

List of Abbreviations

## LIST OF ABBREVIATIONS

(The abbreviations are defined as below, unless specified in the context)

| ADC    | Analog-to-Digital Converter                             |

|--------|---------------------------------------------------------|

| ASIC   | Application-Specific Integrated Circuit                 |

| ASP    | Application Specific Processor                          |

| ASSP   | Application-Specific Standard Product                   |

| BWT    | Burrow-Wheeler Transform                                |

| BZIP2  | Basic Zip with Modifications (data-reduction algorithm) |

| CAD    | Computer-Aided Design                                   |

| CFAR   | Constant False Alarm Rate (e.g. CFAR detector)          |

| CFDF   | Clock Frequency Division Factor                         |

| CLB    | Configurable Logic Block                                |

| DAC    | Digital-to-Analog Converter                             |

| Double | wire that travels two CLB's                             |

| DSP    | Digital Signal Processor                                |

| EDIF   | Electronic Design Interchange Format                    |

| EEPROM | Electrically Erasable Programmable Read-Only Memory     |

| EWMA   | Exponentially Weighted Moving Average (e.g. EWMA        |

|        | filter)                                                 |

| FF     | Flip-Flop                                               |

| FIR    | Finite Impulse Response (e.g. FIR filter)               |

| FLASH  | Type of EEPROM                                          |

| FPGA   | Field-Programmable Gate Array                           |

| GPP    | General Purpose Processor                               |

| HDL    | Hardware Description Language                           |

| Hex    | wire that travels six CLB's                             |

| HLL    | High-Level Language                                     |

| ID     | Identification Data                                     |

| IIR    | Infinite Impulse Response (e.g. IIR filter)             |

| IOB    | Input-Output Block                                      |

| IP     | Intellectual Property (e.g. IP core)                    |

| ISA    | Instruction Set Architecture                            |

| ISE    | Integrated Software Environment                         |

List of Abbreviations

| IXbar | Input Crossbar – switch connecting wire segment to CLB      |

|-------|-------------------------------------------------------------|

|       | input                                                       |

| Long  | wire that travels the length of FPGA chip (in vertical and  |

|       | horizontal dimensions)                                      |

| LUT   | Lookup Table                                                |

| LZO   | Lempel-Ziv-Oberhumer (data-reduction algorithm)             |

| LZW   | Lempel-Ziv-Welch (data-reduction algorithm)                 |

| MCU   | Microcontroller                                             |

| NAND  | logical operator that consists of logical AND followed by   |

|       | logical NOT returning false value only if both operands are |

|       | true (e.g. NAND gate - logic gate that simulates the        |

|       | function of the logical operator NAND)                      |

| NDU   | Non-Descriptive Unit (e.g. a certain NDU amount of power    |

|       | or energy)                                                  |

| NRE   | Non-Recurring Engineering (e.g. NRE cost)                   |

| OTP   | One-Time Programmable (e.g. OTP device)                     |

| OXbar | Output Crossbar - switch connecting wire segment to CLB     |

|       | output                                                      |

| par   | Handel-C keyword directing instructions to be executed in   |

|       | parallel                                                    |

| PCB   | Printed Circuit Board                                       |

| PIR   | Passive Infrared                                            |

| PPMd  | Prediction by Partial Matching with Modifications (data-    |

|       | reduction algorithm)                                        |

| RLE   | Run-Length Encoding (data-reduction algorithm)              |

| RTL   | Register Transfer Level                                     |

| SMA   | Simple Moving Average (e.g. SMA filter)                     |

| SOPC  | System-on-Programmable-Chip                                 |

| SPI   | Serial Peripheral Interface                                 |

| SRAM  | Static Random Access Memory                                 |

| SSR   | Small-Scale Reconfigurability                               |

| ST    | Structured Transpose                                        |

| TTM   | Time to Market                                              |

| UART  | Universal Asynchronous Receiver-Transmitter                 |

| WSN   | Wireless Sensor Network                                     |

List of Abbreviations

| WT  | Wavelet Transform              |

|-----|--------------------------------|

| ZRL | The Zurich Research Laboratory |

List of Figures

## LIST OF FIGURES

| Figure 1. Architecture of Virtex-II FPGA chip, [50].                               | 15 |

|------------------------------------------------------------------------------------|----|

| Figure 2. Typical dynamic power consumption distribution of Virtex-II FPGA         | 17 |

| chip, [50].                                                                        |    |

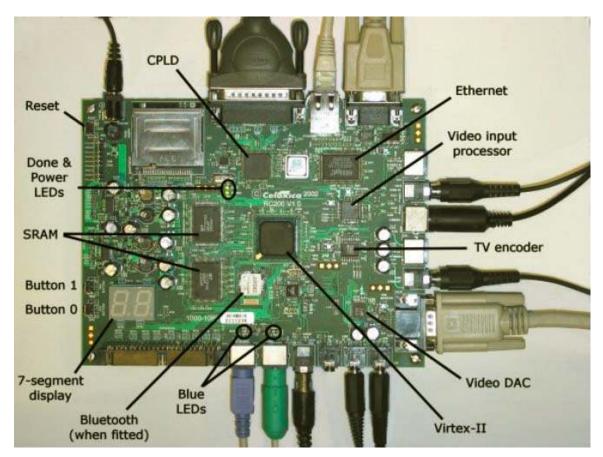

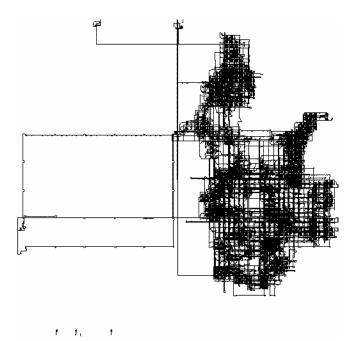

| Figure 3. Devices on exemplary RC200 (same as RC203, except FPGA chip)             | 39 |

| development board, [108].                                                          |    |

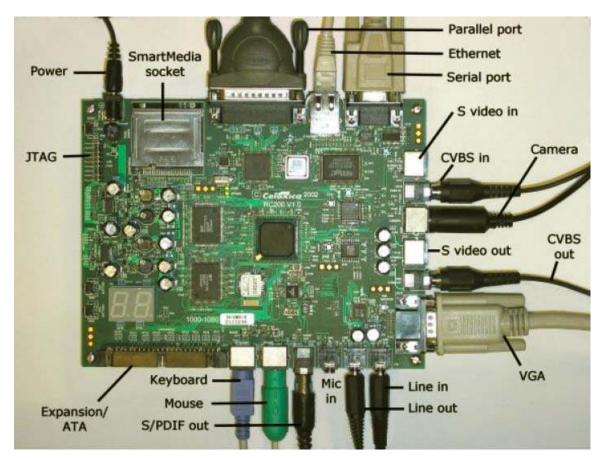

| Figure 4. Connectors on exemplary RC200 (same as RC203, except FPGA                | 40 |

| chip) development board, [108].                                                    |    |

| Figure 5. Compressor (15MHz; on the right) and decompressor (15MHz; on             | 47 |

| the left) in an exemplary Design A – Huffman coding.                               |    |

| Figure 6. Design B with only <i>compressor</i> (15MHz) – Huffman coding.           | 48 |

| Figure 7. Design B with only <i>decompressor</i> (15MHz) – <i>Huffman coding</i> . | 48 |

| Figure 8. Compressor (24MHz; on the right) and decompressor (6MHz; on the          | 49 |

| left) in an exemplary Design A-Huffman coding.                                     |    |

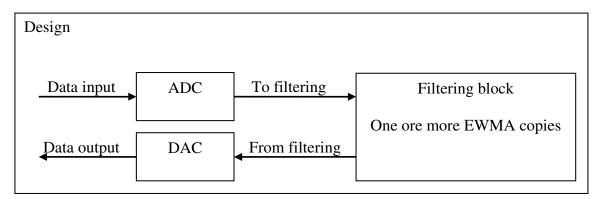

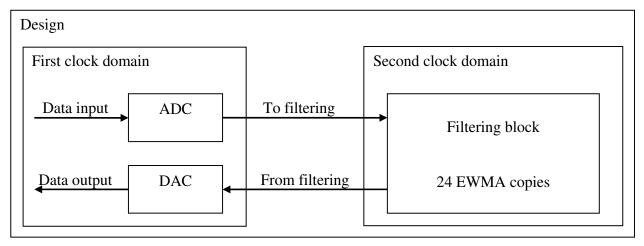

| Figure 9. Design implementation ("shell design") consisting of ADC, DAC,           | 54 |

| and a certain number of EWMA filter copies; an example of a single clock           |    |

| domain design.                                                                     |    |

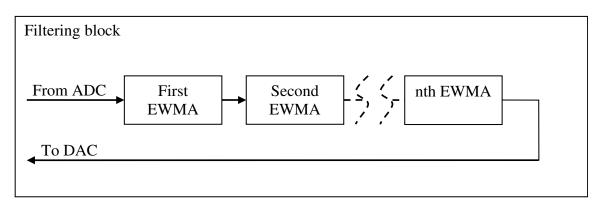

| Figure 10. Functional implementation of filtering block; an example of a single    | 54 |

| clock domain design.                                                               |    |

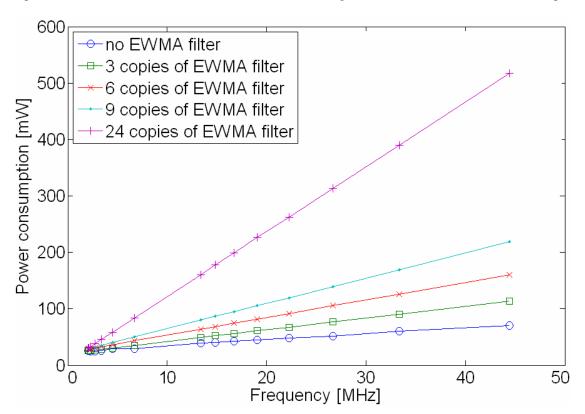

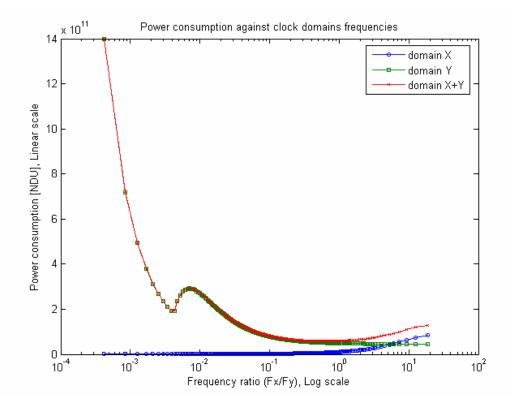

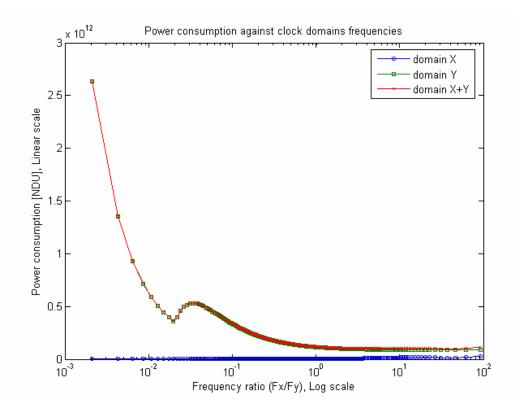

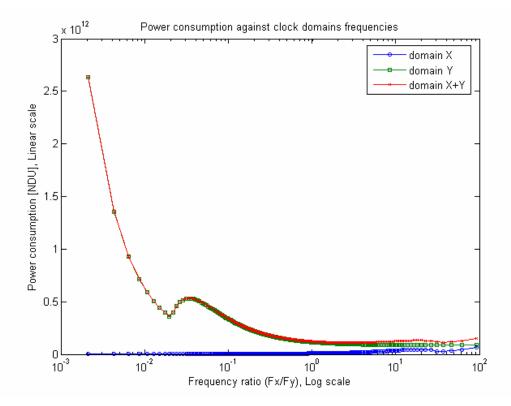

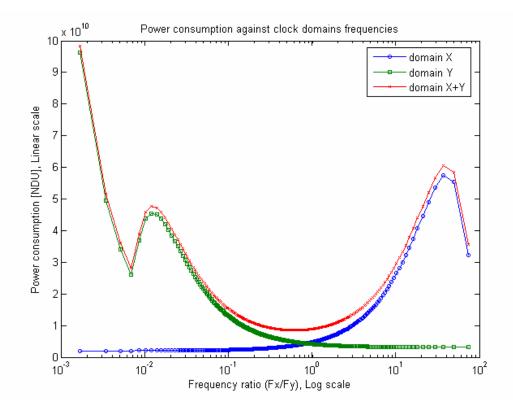

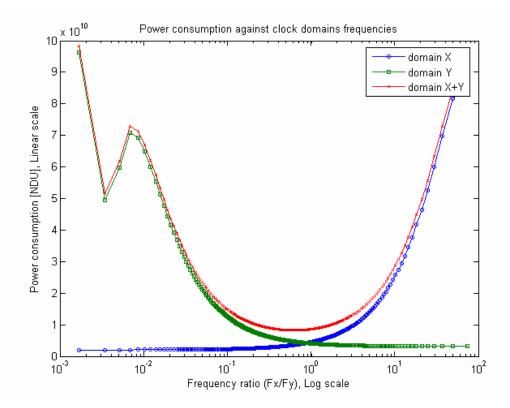

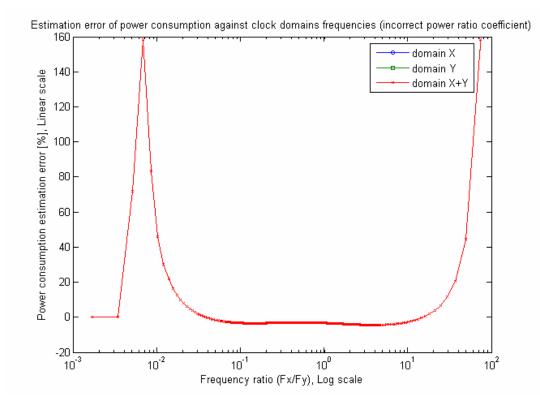

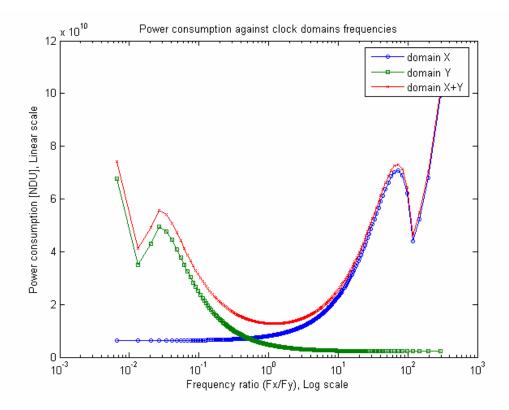

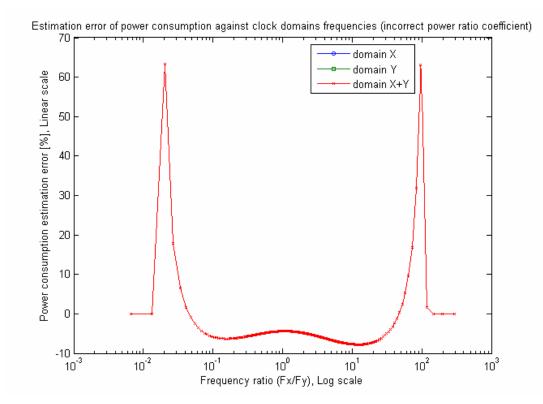

| Figure 11. Relations between dynamic power consumption versus clock                | 56 |

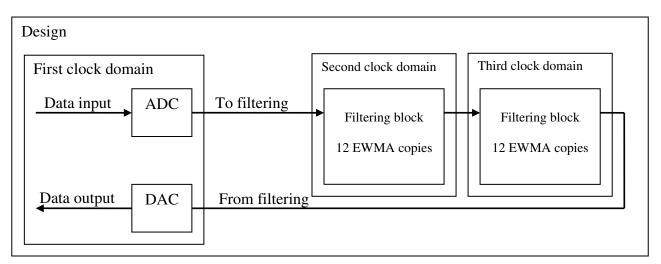

| frequency and design size.                                                         |    |

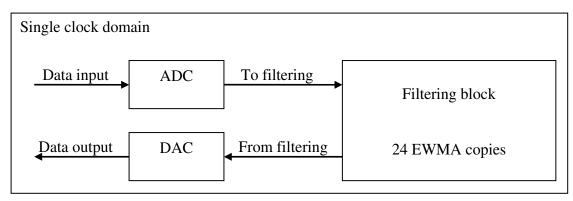

| Figure 12. An example of a single clock domain design.                             | 57 |

| Figure 13. An example of a two clock domains design.                               | 57 |

| Figure 14. An example of a three clock domains design (12 EWMA copies per          | 57 |

| domain).                                                                           |    |

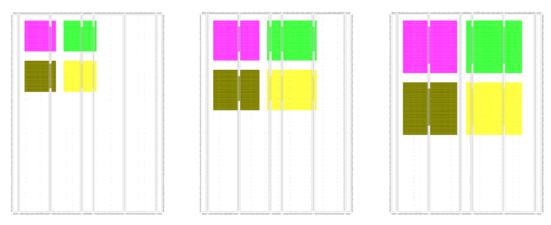

| Figure 15. Area constraints for clock domains with 3, 6, and 9 copies of           | 62 |

| EWMA filter per domain, respectively.                                              |    |

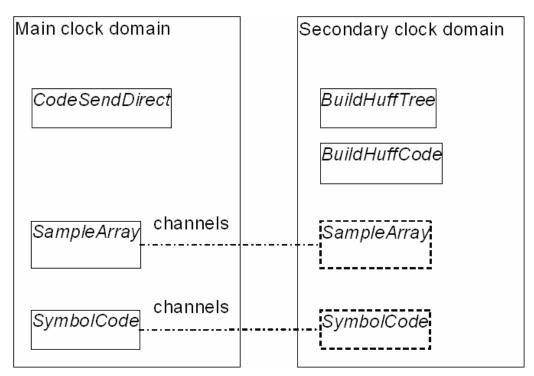

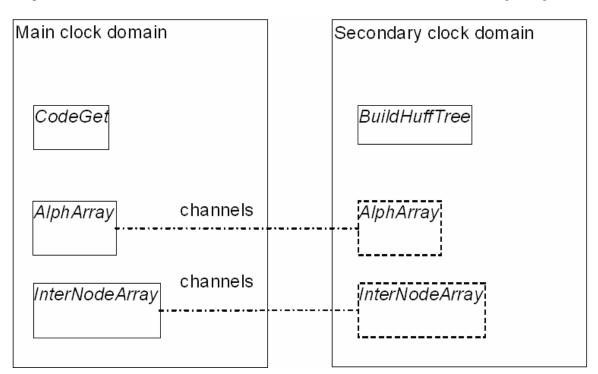

| Figure 16. Block diagram of Huffman coding compressor.                             | 68 |

| Figure 17. Block diagram of Huffman coding decompressor.                           | 69 |

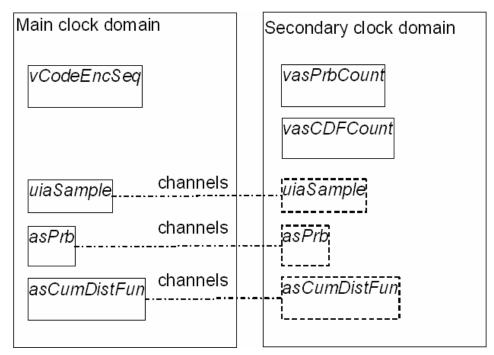

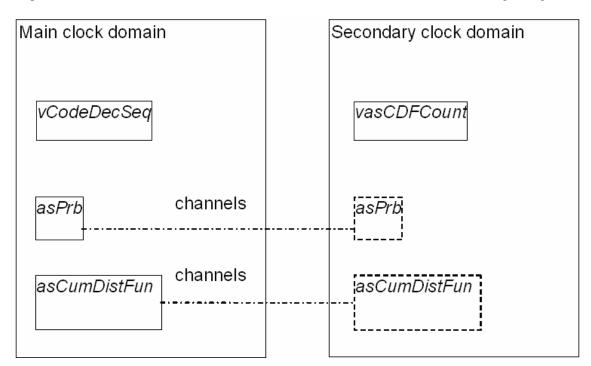

| Figure 18. Block diagram of Arithmetic coding compressor.                          | 70 |

| Figure 19. Block diagram of Arithmetic coding decompressor.                        | 71 |

| Figure 20. Average power consumption in <i>EngDetectorTS_simple</i> algorithm.     | 88 |

| Figure 21. Average power consumption in <i>EnergyEwmaR</i> algorithm.              | 89 |

## List of Figures

| Figure 22. Average power consumption in <i>EwmaDetectorDiffPrm</i> algorithm.         | 89  |

|---------------------------------------------------------------------------------------|-----|

| Figure 23. Average power consumption in <i>EwmaDetectorRatioPrm</i> algorithm.        | 90  |

| Figure 24. Average power consumption in SmaFilter algorithm.                          | 90  |

| Figure 25. Average power consumption in VarDef algorithm.                             | 91  |

| Figure 26. Average power consumption in <i>MoveVarE</i> algorithm.                    | 91  |

| Figure 27. Average power consumption in MoveVarD algorithm.                           | 92  |

| Figure 28. Average power consumption in <i>MeanDev</i> algorithm.                     | 92  |

| Figure 29. Average power consumption estimate of <i>SmaFilter</i> algorithm (using    | 94  |

| the hardware inactivity coefficient of SmaFilter_OptLngPth).                          |     |

| Figure 30. Estimation error of SmaFilter average power consumption                    | 94  |

| (difference between Figures 24 and 29).                                               |     |

| Figure 31. Average power consumption estimate of <i>MeanDev</i> algorithm (using      | 95  |

| the hardware inactivity coefficient of MeanDev_OptLngPth).                            |     |

| Figure 32. Estimation error of MeanDev average power consumption                      | 95  |

| (difference between Figures 28 and 31).                                               |     |

| Figure 33. Average power consumption in <i>EngDetectorTS_simple</i> algorithm         | 97  |

| for $\alpha = 0$ .                                                                    |     |

| Figure 34. Average power consumption in <i>SmaFilter</i> algorithm for $\alpha = 0$ . | 97  |

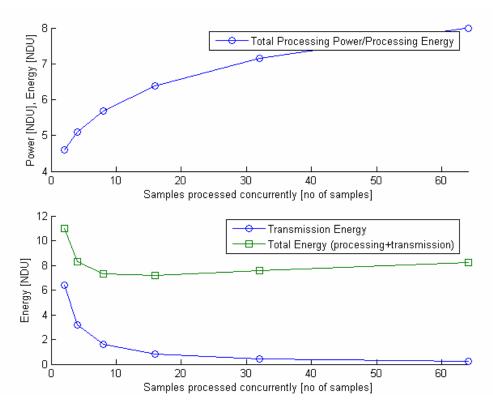

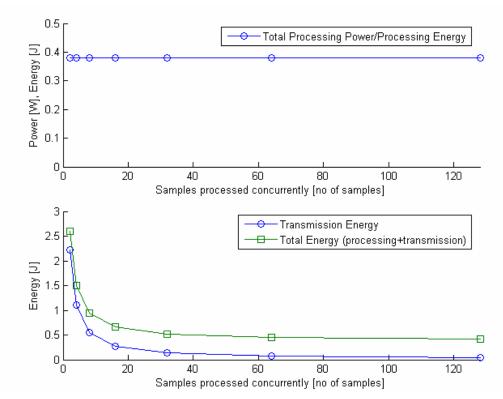

| Figure 35. <i>Mean</i> – top: processing power and energy, bottom: transmission and   | 106 |

| total energy.                                                                         |     |

| Figure 36. <i>VarDef</i> – top: processing power and energy, bottom: transmission     | 106 |

| and total energy.                                                                     |     |

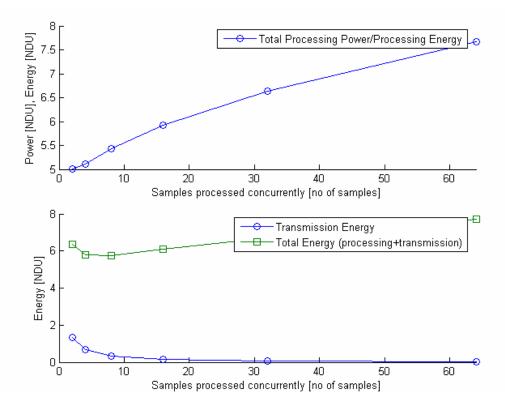

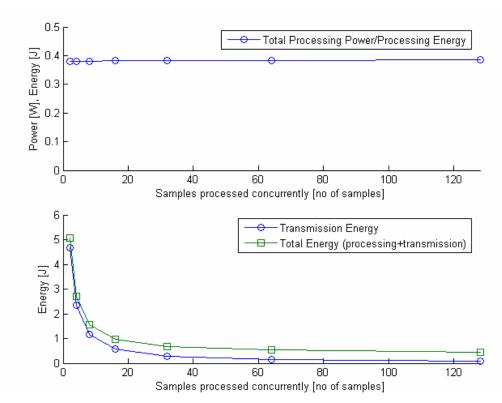

| Figure 37. <i>Mean</i> (scenario 1) – top: processing power and energy, bottom:       | 108 |

| transmission energy and total energy.                                                 |     |

| Figure 38. <i>VarDef</i> (scenario 1) – top: processing power and energy, bottom:     | 109 |

| transmission energy and total energy.                                                 |     |

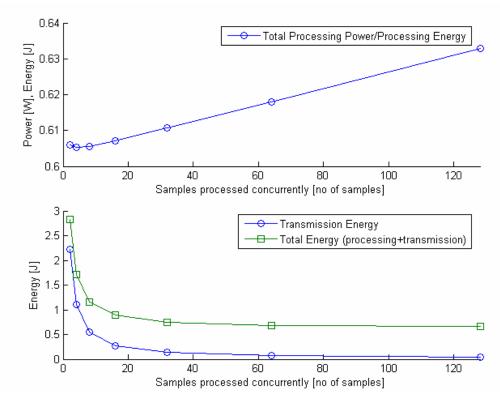

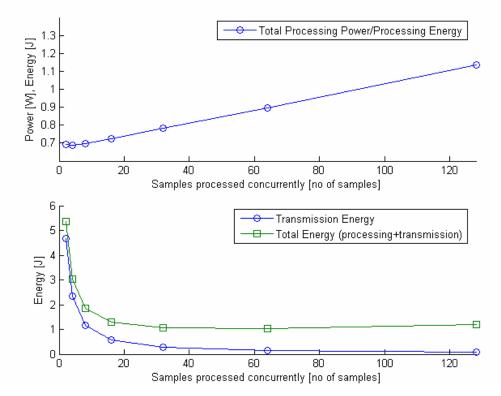

| Figure 39. Mean (scenario 2) – top: processing power and energy, bottom:              | 110 |

| transmission energy and total energy.                                                 |     |

| Figure 40. VarDef (scenario 2) – top: processing power and energy, bottom:            | 110 |

| transmission energy and total energy.                                                 |     |

List of Tables

## LIST OF TABLES

| Table 1. Tools (supporting C-like languages) for FPGA design.                     | 7  |

|-----------------------------------------------------------------------------------|----|

| Table 2. Effective capacitances of Virtex-II FPGA chip resources, [50].           | 16 |

| Table 3. Effective capacitances of Virtex-II FPGA chip resources, [53].           | 17 |

| Table 4. General properties of typical passive and active sensors used in         | 25 |

| surveillance WSN applications, [65].                                              |    |

| Table 5. Sensor selection metrics.                                                | 29 |

| Table 6. Comparison of Celoxica development boards, [109].                        | 40 |

| Table 7. System- and hardware-level complexities – <i>Huffman coding</i> (15MHz). | 46 |

| Table 8. Only <i>decompressor</i> – Design B.                                     | 49 |

| Table 9. Only <i>compressor</i> – Design B.                                       | 49 |

| Table 10. The overall power consumption (decompressor/compressor) –               | 49 |

| Design A.                                                                         |    |

| Table 11. The overall power consumption (decompressor/compressor) –               | 50 |

| Design A.                                                                         |    |

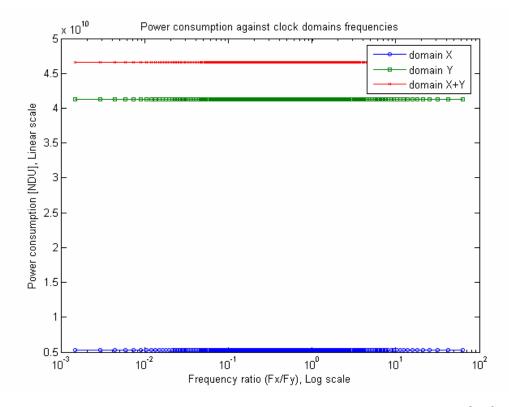

| Table 12. Design with 12 copies of EWMA filter; clock frequency 44.3MHz.          | 58 |

| Table 13. Design with 24 copies of EWMA filter; clock frequency 44.3MHz.          | 58 |

| Table 14. Design with 48 copies of EWMA filter; clock frequency 44.3MHz.          | 58 |

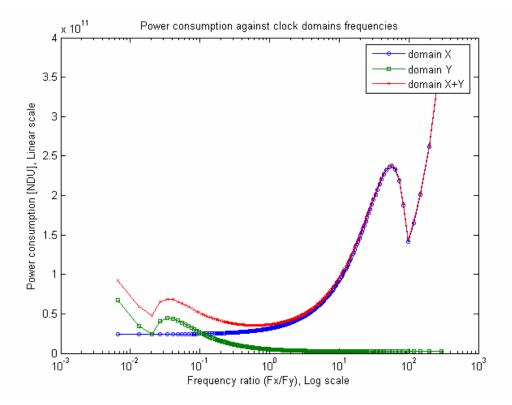

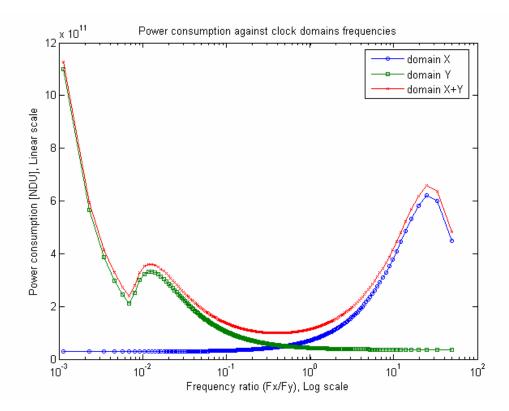

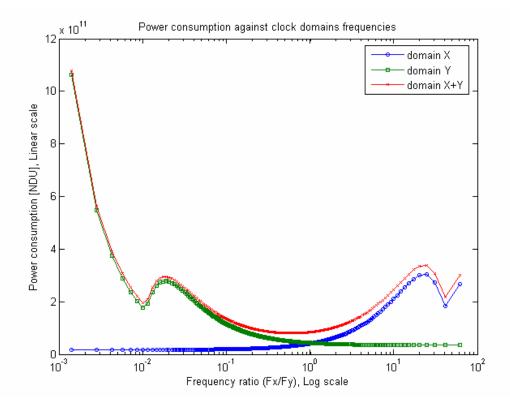

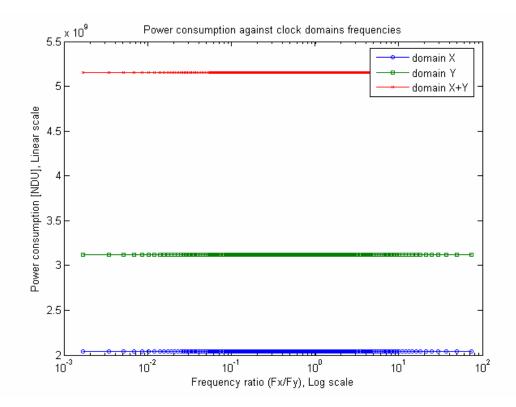

| Table 15. Design with 3 copies of EWMA filter per domain.                         | 60 |

| Table 16. Design with 6 copies of EWMA filter per domain.                         | 60 |

| Table 17. Design with 9 copies of EWMA filter per domain.                         | 61 |

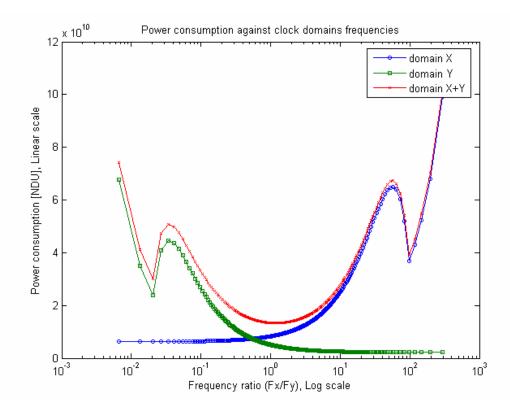

| Table 18. Design with 3 copies of EWMA filter per domain.                         | 62 |

| Table 19. Design with 6 copies of EWMA filter per domain.                         | 63 |

| Table 20. Design with 9 copies of EWMA filter per domain.                         | 63 |

| Table 21. Huffman coding (compressor) - hardware resources and processing         | 69 |

| time.                                                                             |    |

| Table 22. Huffman coding (decompressor) – hardware resources and                  | 69 |

| processing time.                                                                  |    |

| Table 23. Arithmetic coding (compressor) – hardware resources and processing      | 71 |

| time.                                                                             |    |

| Table 24. Arithmetic coding (decompressor) – hardware resources and               | 71 |

| processing time.                                                                  |    |

|                                                                                   |    |

| Table 25. Huffman coding – channel overheads.                                      | 72  |

|------------------------------------------------------------------------------------|-----|

| Table 26. Arithmetic coding – channel overheads.                                   | 72  |

| Table 27. Sequential algorithm partitioning (functional results).                  | 80  |

| Table 28. Hardware requirements for the selected algorithms (the system-level      | 80  |

| estimates).                                                                        |     |

| Table 29. Processing times, clock cycles, and basis clock frequencies.             | 81  |

| Table 30. Device inactivity coefficients for selected algorithms and selected      | 82  |

| clock frequencies.                                                                 |     |

| Table 31. Device inactivity coefficient – 1 copy of SmaFilter_OptLngPth            | 83  |

| algorithm.                                                                         |     |

| Table 32. Device inactivity coefficient – 8 copies of SmaFilter_OptLngPth          | 83  |

| algorithm.                                                                         |     |

| Table 33. Device inactivity coefficient – 16 copies of SmaFilter_OptLngPth         | 83  |

| algorithm.                                                                         |     |

| Table 34. Device inactivity coefficient – 1 copy of MeanDev_OptLngPth              | 83  |

| algorithm.                                                                         |     |

| Table 35. Device inactivity coefficient – 8 copies of MeanDev_OptLngPth            | 84  |

| algorithm.                                                                         |     |

| Table 36. Device e inactivity coefficient – 16 copies of MeanDev_OptLngPth         | 84  |

| algorithm.                                                                         |     |

| Table 37. Device inactivity coefficient changes for a hypothetical FPGA and a      | 85  |

| design of gradually increased size (assumed: $S_{AD} = 0.5$ , $S_{UD} = 0.1$ and   |     |

| $S_{uncf} = 0.01$ ).                                                               |     |

| Table 38. Design inactivity coefficient – SmaFilter_OptLngPth and                  | 86  |

| MeanDev_OptLngPth algorithms.                                                      |     |

| Table 39. $S_{uncf}$ (switching activity of the unused part of the FPGA) estimated | 87  |

| from <i>SmaFilter_OptLngPth</i> and <i>MeanDev_OptLngPth</i> algorithms.           |     |

| Table 40. Selected parameters of Chipcon CC1000, [115].                            | 103 |

| Table 41. System-level results of changing SAMPLELENGTH_LCL – Mean,                | 105 |

| MeanDev.                                                                           |     |

| Table 42. System-level results of changing SAMPLELENGTH_LCL –                      | 105 |

| VarEstim, VarDef.                                                                  |     |

|                                                                                    |     |

Abstract

#### Abstract

Field programmable gate array (FPGA) processing units present considerably higher programming flexibility than other fixed architectures (e.g. microcontrollers (MCU's), digital signal processors (DSP's)). Although performances of FPGA are often compared to application-specific integrated circuits (ASIC's), the price for such a flexibility of programmable devices is a significantly higher power consumption, compared to other fixed-architecture processors.

Power consumption of FPGA implementations can be reduced at the low-level of design. However, for designs of moderate and high complexity such low-level approaches are tedious to implement and time-consuming. High (system) levels of design (e.g. algorithmic languages such as Handel-C) allow building systems of significantly higher complexity. Unfortunately, high-level design techniques have a limited (or no at all) ability to control power/energy properties of a design. The objective of our work is, therefore, to investigate the system-level approaches to power (and energy) efficiency of FPGA-based devices.

FPGA's dissipate static and dynamic power. However, only the dynamic power consumption is design-dependent, while static power consumption is mainly technology-dependent. Thus, we generally ignore the issues of static power reduction in the presented results.

First, we show that power and energy properties of FPGA-based designs can be estimated with a reasonable precision at the high level of designing process. Moreover, we show that the system-level partitioning of designs into several clock domains (typically used to improve performance only) does not noticeably affect power consumption and hardware resources compared to the equivalent low-level partitioning. These two observations are the foundations of further experiments on system-level approaches to power and energy efficiency.

We separately analyze the system-level parallel and sequential algorithm partitioning (in both cases employing the concept of multi-clock domains). It is shown that parallel algorithm partitioning can be optimized (by exploiting system-level estimates of domain sizes and timing) to provide substantial power consumption savings. Sequential partitioning was found a less efficient tool for reducing power and energy consumption of designs. However, we found that in sequentially partitioned designs power consumption losses can be minimized by selecting proper clock frequencies of a particular domain, if for certain reasons the domains must be run at diversified frequencies (which generally dramatically increases the overall energy usage).

Finally, we analyze the total consumption of data-processing and datatransmission energies in FPGA-based designs (which is a typical problem for wireless sensor network (WSN) applications). In general, hardware requirements (i.e. power and energy) of data processing algorithms grow proportionally to the amount of data processed concurrently, while the energy required for transmission is proportional to the volume of transmitted data. We show that by combining system-level algorithms properties and characteristics of transmission modules, substantial savings of the overall energy are achievable.

We believe that the proposed solutions will lead to more advanced system-level approaches to power and energy efficiency, i.e. development of tools incorporating lowlevel power and energy characteristics into high-level design methodologies. Such tools would have the ability to control low-level characteristics (e.g. power and energy consumption) of FPGA-based designs from the highest levels of abstraction.

Introduction

## CHAPTER I INTRODUCTION

This chapter is a general introduction to our work on the system-level methods for power and energy efficiency of the programmable logic-based embedded systems. First, in Section 1.1, we define ubiquitous computing. Then, in Section 1.2, we introduce one of the most important (for this work) examples of ubiquitous computing, i.e. the wireless sensor network (WSN). In Section 1.3 field-programmable gate arrays (FPGA's) devices and microcontrollers (MCU's) are discussed from the WSN's perspective, i.e. their applications, advantages, and existing drawbacks. Finally, in Section 1.4, we present the scope, objectives and organization of the thesis.

## **1.1. Introduction**

The term ubiquitous computing appeared at the beginning of the 90's and was introduced by Mark Weiser (1952-1999; widely considered to be the father of ubiquitous computing), [1], [2]. In his most cited quotation [1] and [3] he stated that "*The most profound technologies are those that disappear*. *They weave themselves into the fabric of everyday life until they are indistinguishable from it*". Since then, there was a dramatic increase in the use of companion and embedded devices in the last decade. Computers are no longer stand-alone special-purpose machines operated by the experts only. Instead, they are present in networked environments ubiquitously.

In general, a ubiquitous environment is a collection of embedded, wearable, and handheld devices, wirelessly connected (possibly to a fixed network infrastructure, e.g. internet), [2], [4]. They have to be aware of their surroundings and be capable to provide services to and use services from other parties effectively, [5].

Although some scientists find ubiquitous and pervasive computing as separate terms, they agree that these words are almost synonyms, [1], [2]. If not, then pervasive computing refers to systems of small and mobile devices that are used for retrieving information anytime, anywhere, and on any device, [2], [6]. Moreover, the goal of ubiquitous computing is to hide computer architecture, while the pervasive computing is to create a technology that can invisibly assimilate into our everyday life, [2].

Requirements to ubiquitous computing are the effect of progress in distributed computing, [5]. Distributed computing requires remote communication, fault tolerance,

high availability, remote information access, and distributed security. Key issues in mobile computing are the cross product of the above issues with new ones, such as mobile networking, mobile information access, adaptive applications, energy awareness, and location sensitivity. Subsequently, key issues in ubiquitous computing are the cross product of the issues in mobile computing and new issues such as smart spaces, invisibility, localized scalability, and uneven conditioning of environments.

## **1.2.** Wireless sensor networks

Wireless sensor networks (WSN's) are an example of ubiquitous computing. Their development started from military applications (Smart Dust, Net), [7]. Initially, WSN's were defined as large-scale, wireless, ad-hoc, multi-hop, unpartitioned networks of homogenous, tiny, and immobile sensor nodes. However, development of WSN's in the area of civilian applications (environmental and species monitoring, agriculture, industry, healthcare, etc.) have shown that such a definition is inaccurate, [7]. WSN's can be heterogeneous, mobile, with different network topologies, and may use existing network infrastructures. More generally, WSN's can be defined as networks of nodes with communication, computation, sensing, and even actuation abilities, [8], [9].

A sensor node may consist of a power, a sensing, a processing, a communication, and even an actuation unit, [8], [9]. The power unit is often a rechargeable battery, usually non-replaceable in the field, equipped with a voltage converter. Power harvesting techniques can be alternatively used. However, their low efficiency limits applicability, [7], [8], [9]. The sensing unit provides the processing and/or communication units with relevant signal data (analog and digital signals can be encountered), [8]. The processing unit, usually a microcontroller (MCU) (e.g. Crossbow WSN development platforms) and seldom a field-programmable gate array (FPGA), processes and passes data to a network, and may also perform some networking tasks, [10], [11], [12], [13], [14], [15]. Depending on the node concept, data can be aggregated, passed, or routed, [9], [14]. The communication unit is responsible for transmitting and receiving data. Some of the networking tasks may be embedded in the communication unit, especially if data has to be only routed without any prior processing, [13].

Introduction

## **1.3. FPGA and MCU in WSN applications**

## **1.3.1.** Typical applications

To our knowledge, there are only few WSN (or related to WSN's) applications employing FPGA. Moreover, this programmable logic device is rather used as a supporting processing unit to the main processor, e.g. MCU.

Tyndal National Institute is developing a miniaturized modular platform for WSN's, [11]. This platform is build with an idea of stackable layers, each designed for a particular purpose, i.e. providing power to a device, sensing, processing, and communication. A layer equipped with FPGA is used for high-speed processing (computationally intensive signal processing, intelligent functionalities). Moreover, performing all tasks locally is possible by the relevant FPGA reconfiguration<sup>1</sup> that may also reduce wirelessly transmitted data. Employing FPGA was motivated by its computation capabilities and significant number of programmable inputs and outputs that may be used to control sensors and actuators, [10].

The Zurich Research Laboratory (ZRL) wireless sensor networking test bed consists of sensor units, a wireless network, a gateway connecting wireless sensors to the host environment, middleware supporting sensor data distribution to sensor applications, and sensor applications, [12]. Sensor units are equipped with FPGA that collects the sensors data, assembles the data into data frames, and sends the resulting data frames to the radio module.

In [13], the feasibility of networking functionality migration from a sensor unit to a radio unit is investigated. The radio unit is equipped with FPGA. However, the most computationally demanding tasks are performed by MCU located in the sensor unit.

Hybrid fine-grained integration of the fixed and reconfigurable logic is presented in [14]. The concept of small-scale reconfigurability (SSR) and optimum combination of such a hybrid logic system is investigated for power efficient adaptable WSN.

FPGA as a complete solution for a reconfigurable wireless communication system for small spacecraft is investigated in [16]. Such a programmable device is envisaged to incorporate all major communication and networking functionalities. Spacecraft wireless networks are not highly active. Therefore, it is envisaged that FPGA may replace other

<sup>&</sup>lt;sup>1</sup> Swapping between different algorithms while having small FPGA footprint (not enough to accommodate all algorithms) so reducing power consumption.

computation components such as general purpose processors (GPP's), digital signal processors (DSP's), application-specific standard products (ASSP's), and application-specific integrated circuits (ASIC's).

## **1.3.2.** Comparative analysis

## A) FPGA advantages

Undoubtedly, the most important advantage of FPGA is reconfigurability, [16]. The same processing unit may be used for different functionalities. Reconfigurability may also be used for adaptability of a particular device to changing environmental conditions and network topologies.

FPGA has a number of user programmable inputs and outputs that help when interconnecting a significant number of different devices, e.g. sensors, actuators, [11]. FPGA designs do not require complex fabrication process compared to ASIC-based, [16]. This allows for low production volumes. Moreover, FPGA architecture allows for post-production configuration of the final product and even changes leading to the next product generation. Therefore, programmable devices are often used for prototyping, evaluation, and development of fixed-logic designs, [17]. Although the performance of FPGA is close to ASIC, they are far away in the field of power and energy efficiency. FPGA devices are significantly inferior, mainly because of additional hardware resources (switching transistors and configuration memory) needed to maintain reconfigurability.

### **B) FPGA Disadvantages**

There are four general types of FPGA, i.e. static random access memory (SRAM)based FPGA, electrically erasable programmable read-only memory (EEPROM)-based FPGA, FLASH-based FPGA, and Antifuse-based FPGA (does not support reconfiguration) [18].

SRAM-based FPGA is manufactured in a deep submicron technology due to required logic density. Hence, its power demands are significant, [8], [11], [19]. Moreover, noticeable amount of power is wasted in a standby and due to current leakages (caused by SRAM memory cells and switch transistors increasing the number of active elements). SRAM-based FPGA contains the reprogrammable device and the boot ROM

holding the configuration data. However, loading a configuration data at the power up requires significant amount of time.

EEPROM-based FPGA does not need boot ROM, and FLASH-based devices have smaller configuration memory compared to first one.

Antifuse-based FPGA does not require switch transistors or configuration memory, hence, the only required power is for the logic array. Therefore, the standby current is reduced significantly. However, this type of FPGA is only a one-time programmable (OTP) device.

#### C) MCU advantages

MCU's used in WSN applications are often equipped with various types of memory such as volatile and non-volatile, interfaces such as serial peripheral interfaces (SPI's), universal asynchronous receiver-transmitters (UART's), analog-to-digital and digital-to-analog converters (ADC's), (DAC's), counters, and timers, [8].

MCU's are also equipped with advanced power management circuits (various low power modes) and allow for diversified voltage and clock speed of the core, [8], [11], [14], [17], [19], [20].

Their specific instruction set architecture (ISA) allows them to perform complex signal processing computations, [13]. Moreover, some microcontrollers support multi-tasking, so implementing a simple operation system such as TinyOS is possible, [9].

## D) MCU Disadvantages

MCU's are a type of application specific processor (ASP). They are designed with a specific ISA and data-path, that is, to perform efficiently relevant operations only. Moreover, they have considerably less inputs and outputs compared to FPGA's, [11].

### **1.4.** Scope, objectives, and thesis organization

## 1.4.1. Scope

WSN's are a considerably new field of science. However, growing application diversity and the corresponding requirements significantly increase the pace of WSN's

#### Introduction

development. Demands are also put on reducing non-recurring engineering (NRE) costs and time to market (TTM). Moreover, such devices are expected to be hardly visible and long lasting, which further complicates their development. Altogether, complexity of sensor nodes pushes their development from the low-(hardware) level to higher levels of abstraction.

Demands for flexibility, performance, longevity, and cost-related issues put on ubiquitous devices, suggest the usage of programmable logic devices, e.g. FPGA, as the processing unit. Technology advancements in the area of FPGA allow manufacturing of multimillion-gate devices, e.g. Altera FPGA chips, Xilinx FPGA chips. This fact additionally increases attention paid to reconfigurable architectures as the processing units, e.g. software-based processors (LatticeMico, Nios, MicroBlaze, PicoBlaze, XTensa), [21], [22], [23], [24]. Moreover, technology advancements are also observed in the area of high-level design techniques, e.g. compilers (Quartus, ISE), hardware description languages (Verilog, VHDL), and high-level hardware description languages such as Handel-C (named algorithmic HDL or algorithmic languages for clarity in the thesis), [21], [22], [25]. They allow for synthesis and prototyping of processing units in a relatively short time, skipping tedious low-level design techniques (with some additional power and hardware resources overheads, however), [21], [22], [25].

Undoubtedly, hardware description languages (HDL's) and the associated programming environments are already matured. Well established manufactures like Altera and Xilinx provide consumers with their programmable logic devices as well as with complete development environments, [21], [22]. Although the development processes using HDL's are considerably faster than transistor-level techniques, high-level HDL's (i.e. the system-level techniques) may shorten this process additionally. However, such languages, e.g. Handel-C, and the corresponding development environments, e.g. DK Celoxica, are still in their development stage.

Numerous academic groups and commercial vendors have attempted to create tools that convert a high-level language (HLL) into a HDL representation for register transfer level (RTL) synthesis (often referred to as 'C to HDL' or 'C to RTL' methodology) targeting either Verilog or VHDL HDL languages, [26]. Existing HLL's (allowing targeting FPGA at an algorithm level) are usually modifications of C or C++ programming languages, [26], [27], [28]. Since standard C lacks notations typical to hardware, such as parallelism or the passage of time, the concepts are introduced, either as extensions to the relevant language (or via 'pragmas') or are built into the tool and

#### Introduction

annotated by a programmer against the standard C description. In effect, these allow a designer to use such a C-like programming language as a HDL. However, the differences of these C-like languages compared to standard C/C++ prevent simulation of the code outside specialized simulators. The range of tools (and associated C-like languages) that allow programming FPGA's is surprising, see Table 1, just to name a few.

| Toolset         Vendor      |                                            |

|-----------------------------|--------------------------------------------|

| NISC toolset [29]           | University of California                   |

| Altium Designer [30]        | Altium                                     |

| Catapult [31]               | Mentor Graphics                            |

| Cynthesizer [32]            | Forte Design Systems                       |

| Agility Compiler [33]       | Celoxica                                   |

| DK Design Suite [34]        | Agility Design Solutions (former Celoxica) |

| DIMEtalk [35]               | Nallatech                                  |

| Impulse C [36]              | Impulse Accelerated Technologies           |

| FpgaC [37]                  | an open source initiative                  |

| SA-C [38]                   | Colorado State University                  |

| Cascade [39]                | CriticalBlue                               |

| Mitrion [40]                | Mitrionics                                 |

| C2R Compiler [41]           | CebaTech                                   |

| Mimosys Clarity [42]        | Mimosys                                    |

| HybridThreads Compiler [43] | University of Kansas                       |

Table 1. Tools (supporting C-like languages) for FPGA design.

However, these high-level HDL's and the accompanying tools are focused on parallelization approaches, rather than abstraction, and lack the relevant development board libraries. To our knowledge, Agility Design Solutions (former Celoxica) is the only vendor providing complete high-level HDL programming environment, proprietary Clike language (Handel-C), and a number of development boards with platform abstract layer libraries. That is, DK Design Suite and RC development boards are often used by academia.

## **1.4.2.** Objectives

We have observed that there is lack of system-level approaches to power and energy efficient development of programmable logic based designs. Although Handel-C (exemplar algorithmic HDL) allows for almost the same flexibility as C languages, it lacks the power and energy management schemes. Hence, the only way to achieve better power and energy efficiency of relevant designs is to deal with the design levels below the system level, that is, with the hardware levels. Therefore, we come up with several

#### Introduction

approaches that allow achieving, to some extent, power and energy efficiency at the system-level.

Dividing a particular design into multi-clock domains is a well established technique to achieve better performances in the programmable devices arena. Although this operation is rather hardware-level oriented, algorithmic HDL's, such as Handel-C, allow for implementing a particular algorithm into various clock domains. Power and energy characteristics of such a multi-clock domain design partitioned at the hardware-level are easily recognizable. That is, performing such an operation carefully should not change power and energy characteristics of a design (assuming a similar number of hardware resources are employed). However, dividing a design into a number of clock domains at the system level is challenging since algorithmic HDL synthesis is focused on parallelization rather than on implemented logic, that is, on performance rather than on power and energy efficiency. It is also unknown how such a design partitioned at the system-level will behave in terms of hardware resources and power consumption. In general, the research approaches in our work to the system-level power and energy efficiency are based on multi-clock domain designs. Thus, the first of the objectives of the thesis is to investigate:

# (i) Relations between domains, i.e. clock domains, size of a domain, size of a design, power consumption.

We investigate to what extent design partitioning at the system-level (using algorithmic language constructs) is as predictable as at the hardware-level in terms of hardware resources and power consumption. In other words, we verify whether dividing a design into multiple clock domains can be performed directly at the system-level.

Following the general thesis direction, i.e. the multi-clock domain approach, we subsequently investigate the ability of system-level algorithm partitionings to achieve power and energy efficiency. It is envisaged that some groups of (subject to partitioning) algorithms perform selected operations in parallel and/or sequentially (sometimes interchangeably). Therefore, the next research area of the thesis is:

## (ii) Issues of parallel and sequential algorithm partitioning.

Data communication (receiving as well as transmitting) is found the most power and energy consuming operation among other operations performed by an embedded device. Thus, another objective of the thesis is to investigate:

(iii) Energy efficiency of data communication from the perspective of data processing algorithms.

#### Introduction

The results presented in the thesis indicate that the proposed techniques give satisfactory results with acceptable power, energy, and hardware resources overheads. It is envisaged that with little effort our approaches can be integrated into lower levels of the design process, i.e. hardware description environments, allowing a further shortening of the development process.

## **1.4.3.** Thesis organization

The thesis is divided into several chapters, each corresponding to a major topic of our work. In the beginning of each chapter a brief overview of its content is given, and the chapters are summarized with general conclusions.

In Chapter 2 we survey the literature related to the scope and objectives of our work. First, in Section 2.1, we present power and energy issues in FPGA chips themselves and in FPGA-based designs. Next, in Section 2.2, we survey sources on data processing in WSN's. We discuss sensing principles, sensor selection for WSN applications, application requirements to sensing devices, and data processing algorithms. However, the latter is only a brief introduction to the algorithms further analyzed in other parts of the thesis. In general, we do not analyze algorithm structures and how they perform since this is out of the thesis scope. In Section 2.3, we survey data-reduction algorithms used in WSN's. Finally, in Section 2.4, existing approaches to algorithm partitioning in FPGA designs are discussed.

In Chapter 3 the experimental setup is described. We overview high- and lowlevel development tools (programming environment, hardware targeting, etc.) used for the conducted experiments, and give general assumptions regarding the experiments. In this chapter, we also give a brief introduction to the high-level hardware description language, i.e. Handel-C, used in our experiments for the implementations of the algorithms.

Chapter 4 discusses relations between system- and low-level results of the algorithms implementations. In other words, we investigate whether system-level results can, at least to some extent, represent similar experiments performed at the hardware-level. Using this approach, tedious low-level implementations can be avoided by performing qualitatively the same experiments at higher levels of the design process. The results of these experiments are the basis for further system-level experiments.

#### Introduction

In Chapter 5 we investigate relations between clock domains, size of a design, chip area constraints, and power consumption, i.e. what clock frequency is suitable for a particular design size in terms of power consumption, and how dividing designs into several clock domains influences power consumption. We also investigate dependencies between low-level design integration (a multi-clock domain design) and power consumption predictability at the system-level.

Chapter 6 presents experiments on a parallel algorithm partitioning. We base our investigations on selected data-reduction algorithms used in WSN applications. Parallel algorithm partitioning is discussed from the perspective of the power efficiency improvement.

In Chapter 7, a sequential algorithm partitioning, based on selected typical data processing algorithms used in WSN's, is investigated. We prove that selection of a clock frequency to such a sequentially partitioned algorithm (e.g. for a desired performance increase) must be performed extremely carefully. Otherwise, power and energy efficiency of a design may be strongly sacrificed. Although the chapter focuses on determining optimum domain clock frequencies in multi-clock domains designs rather than on improving power and energy efficiency, we show that the selection of clock frequencies influences power and energy properties of the design.

Chapter 8 approaches data processing and communicating issues in terms of energy consumption. The conducted experiments focus on the hardware resources required to implement the relevant data processing logic and the data volume to be communicated. In effect, significant energy efficiency improvement is approached.

In Chapter 9 we conclude our work and present feasible future works.

Literature Overview

## CHAPTER II LITERATURE OVERVIEW

This chapter is the survey of the literature related to the scope and objectives of our work. In Section 2.1 we present power and energy issues in programmable devices, i.e. FPGA chips themselves, and in FPGA-based designs. However, the problems are addressed from the system-level view point, i.e. power and energy issues are not deeply studied at the hardware-level (transistor-level). In the following sections we present issues related to WSN's, which we considered a leading example of embedded systems. We chose surveillance applications as the typical application of WSN's. First, in Section 2.2, we survey sources on data processing in WSN's. Although the main focus is on algorithms, it is envisaged that other issues related to sensing are important to understand the subject. Therefore, issues like sensing principles, sensor selection for WSN applications, noise issues in sensing devices, and finally data processing algorithms, are discussed. Data processing algorithms are only briefly presented since the detailed analysis can be found in other parts of the thesis. Nevertheless, algorithm structures and how they perform are not analyzed at all since this is out of the thesis scope. In Section 2.3 we survey data-reduction algorithms used in WSN applications. Finally, existing approaches to algorithm partitioning in FPGA designs are discussed in Section 2.4.

## 2.1. Power and energy issues in FPGA-based designs

Power and energy efficiency may be analyzed at each of the design levels, i.e. ranging from a transistor-level to a system-level, [44]. Designing at the device-level, covering power issues at the circuit- and transistor-levels, was found the most important issue in the past decade. The device-level experts (circuits and layout) were responsible for power and energy, while the system-level experts (architectures, compilers, and operating systems) were designing for speed and performance. In recent years, however, there has been a growing interest in power and energy issues analyzed at higher levels (i.e. system-levels), e.g. [44], [45], [46], [47].

The basic building block of the current processors is a CMOS circuit, [44], [47], [48]. Each technology advancement in circuits that shrinks the transistor feature size by a factor of n, reduces the capacitance by n, and lowers the supply voltage by  $n^2$ , should reduce the dissipated power by a factor of  $n^3$  assuming the same clock frequency.

However, new processor generations result in more complex and more performancedemanding designs. They use a higher clock frequency, a larger chip area, and more transistors, [44], [49]. In effect, there is a significant increase in the power dissipation and power density. Finally, power management policies aiming at the device-level become insufficient. Therefore, power issues of current processors become a key design constraint and propagate to higher levels of design, [44], [45], [46], [47].

## 2.1.1. Power and energy issues in design

The key to a proper design is to understand the conceptual difference between power-aware and low-power systems, [44]. The main goal in designing low-power systems is power minimization, while power-aware systems are designed to achieve particular power and energy properties.

## • Power-aware design *versus* power/energy minimization

Decreasing power and energy does not have to be the main concern in poweraware designs. Actually, power and/or energy may even be increased. An example is the issue of decreasing the peak power in a processor. Typically, this is achieved by using a scheme that intentionally delays execution of some instructions to smoothen their distribution, so decreasing the peak of consumed power. However, such an approach may increase the execution time, and thus increase the energy consumption. Hence, this scheme is generally not suited for low-power designs.

## • Average power and maximum power

Decreasing the average power does not have to reduce the maximum power. The average power dissipation, representing the power consumption distribution histogram, is computed over the entire execution time while the maximum power represents the peak value of such a histogram. Thus, decreasing the average power may sometimes increase the maximum power. Hence, these approaches are also not suitable to low-power designs.

## • Power efficiency and energy efficiency

The integral of the power consumption over the execution time represents energy. It is well known that an improved power efficiency of a design may be obtained by decreasing the clock frequency and/or by reducing the power supply voltage of the

#### Literature Overview

processor. However, this may degrade the performance of such a design, increasing the execution time, thus effectively increasing the energy consumption.

## • Power-constrained and energy-constrained design

An energy-constrained design is one that is running under the constraints of a finite source of energy such as a battery. On the contrary, a power-constrained design is running on the infinite source of energy such as a solar battery. However, such an energy source is constrained by its power efficiency. Hence, the energy budget and the available power are totally different designing metrics.

## • Energy-constrained design and energy minimization

Studies on batteries show that their properties are far from ideal capacitors, and the battery charge depends on other than capacity issues. Hence, the energy-constrained designs are focused on battery lifetime that does not correspond to energy-minimization.

## 2.1.2. Power consumption in FPGA

Devices fabricated in CMOS technology (e.g. FPGA) dissipate static and dynamic power, e.g. [44], [46], [47], [48], [50], [51].

## • Static power

The leakage current between power supply and ground is the main source of the static power and includes the reverse biased PN-junction current, the sub-threshold leakage, the gate induced drain leakage, the punch through, and the gate tunnelling, [44]. The sub-threshold leakage current (that depends on temperature and the threshold voltage  $V_{th}$ ) constitutes the majority of the leakage current.

In the past, a negligible level of the leakage current was the reason of not taking it into power consumption analysis. However, a significant static power increase can be expected due to the shrinking transistor size. Feature size decrease is generally accompanied by a reduction of the power supply voltage ( $V_{dd}$ ). Hence, the threshold voltage has to be reduced to maintain or increase the performance. Eventually, the static power increases significantly since the sub-threshold leakage current grows exponentially with the threshold voltage decrease. The static power is independent of the device

activity, but it depends on the device area and temperature. Thus, the static power is present whenever a power is supplied to the CMOS device.

In addition, the thermal characteristic is also affected by the design shrinking. Onchip temperature may vary across the whole chip area. Its maximum values depend on the chip area and the maximum power dissipation. Therefore, by reducing the total maximum power the maximum temperature may be decreased, so influencing the static power.

It is claimed by some researchers, [50], that the static power of a typical FPGA device, e.g. Virtex-II family (SRAM-based FPGA, 0.15µm technology), is in the range of 5 up to 20% of the overall dissipated power (depending on the temperature, the clock frequency, and the implemented logic).

## • Dynamic power

In a CMOS device, signal transitions at their transistors are the source of dynamic power dissipation, [44], [46], [47]. Frequencies of these transitions are obviously related to the clock frequency, i.e. the dynamic power consumption is generally modelled as:

$$P = \sum_{i} C_{i} \cdot V_{i}^{2} \cdot f_{i} \qquad (1)$$

where  $C_i$ ,  $V_i$ , and  $f_i$ , represent the capacitance, the voltage swing, and the clock frequency of the resource *i*, respectively, [44], [47], [50], [51]. The total dynamic power is the sum of the dynamic power of all resources.

FPGA programmability introduces additional design-dependent factors contributing to the dynamic power: the effective capacitance of resources, the resource utilization, and the switching activity of resources, [45], [50], [51].

The effective capacitance is the sum of original capacitance of the components and of parasitic effects caused by interconnection wires and transistors. The resource utilization represents the amount of resources that are not used after chip configuration. The average number of signal transitions in a clock cycle is represented by the switching activity. This generally depends on several factors, e.g. input signal patterns. Therefore, (1) can be expressed by:

$$P = V^2 \cdot f \cdot \sum_i C_i \cdot U_i \cdot S_i \qquad (2)$$

where V is the supply voltage, f is the clock frequency, and  $C_i$ ,  $U_i$ , and  $S_i$ , represent the effective capacitance, the resource utilization, and the switching activity of each resource, respectively, [50].

Literature Overview

## 2.1.3. Power characteristics of FPGA

A typical FPGA chip consists of (apart from its main array of slices and I/O blocks) a number of hard cores, i.e. memory blocks, digital clock managers, encryption circuits, custom multipliers, etc., [50].

An FPGA's power and performance are often compared to their ASIC counterparts, [50], [51]. However, the programmability of FPGA needs the interconnection structures with loading larger than for custom circuits, [52]. Moreover, the capacity load of signal nets over dedicated metal wires is additionally increased by signal buffers, pass transistors, and other programmable switching structures.

Such a flexibility of programmable devices compared to other processing units, with almost fixed architecture, leads to significant power consumption increase.

# A) FPGA architecture – programmable fabrics (Virtex-II FPGA family chip example)

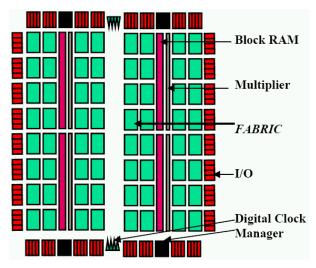

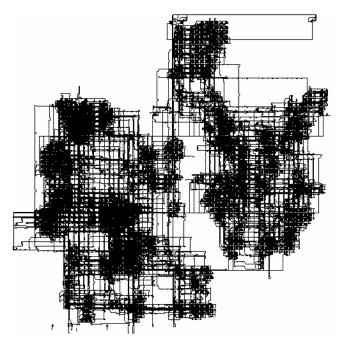

Virtex-II, which can be considered a typical FPGA chip (see Figure 1) consists of configurable logic blocks (CLB's) that are interconnected by a number of routing resources, [50]. Each CLB contains four slices, also referred as logic, where each slice consists of two 4-input lookup tables (LUT's), two flip-flops (FF's), and a diversity of dedicated circuits that accommodates more efficient implementations of some specific logic.

Figure 1. Architecture of Virtex-II FPGA chip, [50].

Virtex-II uses a segmented routing structure that minimizes the number of transistors and wires traversed by a signal reaching its destination. This routing architecture includes wires that travel along two CLB's (Double's), six CLB's (Hex'es), and the length of FPGA chip (Long's), in both the vertical and horizontal dimensions. There are also pass transistors and buffers associated with each set of wires. Moreover, there are two sets of switches that connect wire segments to inputs and outputs of each CLB, called input crossbars (IXbar's) and output crossbars (OXbar's), respectively. These interconnection resources add a significant power consumption to the power dissipated by other parts of the FPGA.

## B) FPGA power consumption distribution (Virtex-II FPGA family chip example)

The dynamic power consumption distribution of a particular FPGA is determined by the effective capacitance, and by the utilization and the switching activity of the relevant resources.

Various techniques are used to estimate the effective capacitance of the FPGA resources, but the results are not significantly different; Tables 2 and 3 ([50] and [53]). For example, compare capacitance values of Double, Hex, and Long in Table 2 to the same resources in Table 3. They are within 90% accuracy. Capacitances of long lines and the global clock tree change with the width and the height of a device, while capacitances of other resources are the same among members of a particular device family.

| Туре              | Resource      | Capacitance [pF] |

|-------------------|---------------|------------------|

| CLB interconnects | IXbar         | 9.44             |

|                   | OXbar         | 5.12             |

|                   | Double        | 13.20            |

|                   | Hex           | 18.40            |

|                   | Long          | 26.10            |

| CLB logic         | LUT inputs    | 26.40            |

|                   | FF inputs     | 2.88             |

|                   | Carry         | 2.68             |

| Clocking          | Global wiring | 300              |

|                   | Local         | 0.72             |

Table 2. Effective capacitances of Virtex-II FPGA chip resources, [50].

Literature Overview

| Resource             | Capacitance [pF] |

|----------------------|------------------|

| Embedded multiplier  | 1.196            |

| Block select RAM     | 880              |

| CLB                  | 26               |

| Long-line route      | 23               |

| Hex-line route       | 18               |

| Double-line route    | 13               |

| Direct-connect route | 5                |

Table 3. Effective capacitances of Virtex-II FPGA chip resources, [53].

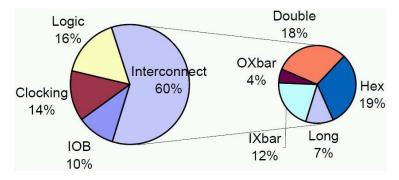

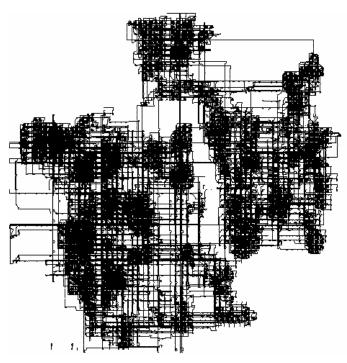

Although numerous factors influence the resources utilization and the switching activity (e.g. design dependences, input patterns, etc.), experimental results consistently indicate that most of the dynamic power in current FPGA's is consumed by interconnects, and may constitute up to 60% of the total dissipated power, see Figure 2, [45], [46], [50], [51], [52], [53].

Figure 2. Typical dynamic power consumption distribution of Virtex-II FPGA chip, [50].

Moreover, a large portion of power, especially in arithmetic circuits, is wasted by unproductive signal transitions (caused by glitches), [46], [50], [52]. This is caused by spurious signal transitions on interconnect lines due to unequal logic or interconnect delays.

## 2.1.4. Power consumption estimation in FPGA

To ensure a proper functionality of a particular system, power consumption of the FPGA chip has to be estimated in early design steps, [49]. This is essential to design the appropriate printed circuit board (PCB), to provide an adequate power supply, and to ensure conditions for heat dissipation.

Real measurements as well simulation-based estimations can be used to obtain details of FPGA power consumption, [45], [49], [50], [51], [54].

#### Literature Overview

Undoubtedly, the real measurements give the highest power measurement accuracy, however, the investigated device must be a representative one, [45]. Otherwise, measurements results may be distorted by some odd characteristics, e.g. during the manufacturing process.

The simulation-based power estimations are definitely much more convenient, [45]. However, they provide only approximate measurements.

Currently, power estimation approaches are mainly based on the switching capacitance and other corresponding factors, e.g. the average switching activity and the average resource utilization, [44], [45], [47], [48], [49], [50], [51], [53]. These power estimation approaches are found the most suitable for SRAM-based FPGA devices where the majority of designs are synchronous and driven by the system clock.

## 2.1.5. Means of power consumption reduction in FPGA