# System-Level Observation Framework for Non-Intrusive Runtime Monitoring of Embedded Systems

| Item Type     | text; Electronic Dissertation                                                                                                                                                                                                                                                                                         |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Authors       | Lee, Jong Chul                                                                                                                                                                                                                                                                                                        |  |  |  |

| Publisher     | The University of Arizona.                                                                                                                                                                                                                                                                                            |  |  |  |

| Rights        | Copyright © is held by the author. Digital access to this material<br>is made possible by the University Libraries, University of Arizona.<br>Further transmission, reproduction or presentation (such as<br>public display or performance) of protected items is prohibited<br>except with permission of the author. |  |  |  |

| Download date | 22/08/2022 20:47:53                                                                                                                                                                                                                                                                                                   |  |  |  |

| Link to Item  | http://hdl.handle.net/10150/338687                                                                                                                                                                                                                                                                                    |  |  |  |

## SYSTEM-LEVEL OBSERVATION FRAMEWORK FOR NON-INTRUSIVE RUNTIME MONITORING OF EMBEDDED SYSTEMS

by

Jong Chul Lee

Copyright © Jong Chul Lee 2014

# A Dissertation Submitted to the Faculty of the

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

In Partial Fulfillment of the Requirements For the Degree of

# DOCTOR OF PHILOSOPHY

In the Graduate College

## THE UNIVERSITY OF ARIZONA

2014

## THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE

As members of the Dissertation Committee, we certify that we have read the dissertation prepared by Jong Chul Lee entitled System-Level Observation Framework for Non-Intrusive Runtime Monitoring of Embedded Systems and recommend that it be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy.

|                   | Date: 10/23/14 |

|-------------------|----------------|

| Dr. Roman Lysecky |                |

|                   | Date: 10/23/14 |

| Dr. Ali Akoglu    |                |

|                   | Date: 10/23/14 |

| Dr. Meiling Wang  |                |

Final approval and acceptance of this dissertation is contingent upon the candidate's submission of the final copies of the dissertation to the Graduate College.

I hereby certify that I have read this dissertation prepared under my direction and recommend that it be accepted as fulfilling the dissertation requirement.

Date: 10/23/14

Dissertation Director: Dr. Roman Lysecky

## STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at the University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the copyright holder.

SIGNED: \_\_\_\_\_

Jong Chul Lee

#### ACKNOWLEDGEMENTS

I have many people to thank for this dissertation. First and foremost, I would like to give my tremendous thanks to my advisor, Professor Roman Lysecky, for all the advice, supports, encouragements, and trusts he has offered to me without any reservation. He guided me through the years and helped me to grow passion and become more and more mature in academic research. Because of his support and understanding, I had a pleasant and valuable experience during my Ph.D. study in the Electrical and Computer Engineering Department at the University of Arizona.

Special thanks go to Professor Ali Akoglu, Professor Meiling Wang, Professor Susan Lysecky and Professor Wei Hua Lin for the excellent courses they taught and for serving on my Ph.D. Written and Oral Comprehensive Exams as a committee member.

I would like to thank Tami Whelan for handling all the paper work necessary for the completion of my degree. I would like to express my appreciation to the supporting staff in the Department of Electrical and Computer Engineering for maintaining a friendly and stable learning environment.

I would also like to thank Doohwan Kim, a president of RTSync, and Chungman Seo, a senior research engineer at RTSync, for the excellent internship opportunity.

I would like to acknowledge my fellows and friends Hyun Jin Park, Sungjong Yoo, Junseok Kim, my labmates Karthik Shankar, Sachidanand Mahadevan, Vijay Gopinath, Jingqing Mu, Nathan Sandoval, Adrian Lizarraga and many other friends at University of Arizona, for their help and encouragement during my six years graduate student life here.

Last but not least, my family is to be thanked: Munam Lee, Booja Chung, Hoajin Lee, Bongjae Kim, Hyo Jin Lee, Chang Hwan Yoon, Jinchul Lee and Ko Eun Choi.

# DEDICATION

To my parents, Munam Lee and Booja Chung, without whose love and encouragement throughout the years this thesis would not have been possible.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                | 8  |

|----------------------------------------------------------------------------------------------------------------|----|

| LIST OF TABLES                                                                                                 | 10 |

| ABSTRACT                                                                                                       | 11 |

| CHAPTER 1 INTRODUCTION                                                                                         | 13 |

| CHAPTER 2 RELATED WORK AND BACKGROUND                                                                          | 17 |

| CHAPTER 3 HARDWARE OBSERVABILITY FRAMEWORK FOR<br>MINIMALLY INTRUSIVE ONLINE MONITORING OF EMBEDDED<br>SYSTEMS | 27 |

| 3.1 Overview                                                                                                   |    |

| 3.2 Hardware Observability Framework                                                                           | 27 |

| 3.2.1 Hardware Observability Interface (HWOI)                                                                  |    |

| 3.2.2 Hardware Observability Bus and Bridge                                                                    |    |

| 3.2.3 Hardware Observability Engine                                                                            |    |

| 3.3 Experimental Results                                                                                       |    |

| CHAPTER 4 EVENT-DRIVEN FRAMEWORK FOR CONFIGURABLE<br>RUNTIME SYSTEM OBSERVABILITY FOR SOC DESIGNS              |    |

| 4.1 Overview                                                                                                   | 40 |

| 4.2 System-level Observation Framework                                                                         | 41 |

| 4.3 Hardware Observability                                                                                     | 44 |

| 4.4 Software Observability                                                                                     | 47 |

| 4.5 System Observation Engine                                                                                  | 50 |

| 4.6 Cascading Event Probe                                                                                      | 51 |

| 4.7 Experimental Results                                                                                       | 53 |

| CHAPTER 5 SYSTEM OBSERVATION OF BLOCKING, NON-BLOCKING, AND CASCADING EVENTS FOR RUNTIME MONITORING OF REAL-   |    |

| TIME SYSTEMS                                                                                                   |    |

| 5.1 Overview                                                                                                   |    |

| 5.2 System-level Observation Framework                                                                         |    |

| 5.3 HWOI and SWOI Interface                                                                                    |    |

| 5.4 Blocking, Non-blocking, and Cascading Event Probes                                                         |    |

| 5.5 Software Event Probes                                                                                      | 63 |

| 5.6 Event Probe Configuration Stream                                                                                 | 65 |

|----------------------------------------------------------------------------------------------------------------------|----|

| 5.7 Pipelined, priority-based event stream controller                                                                | 67 |

| 5.8 In-order priority controller                                                                                     | 68 |

| 5.9 Experimental Results                                                                                             | 70 |

| 5.9.1 Monitoring Task Completion Time                                                                                | 72 |

| 5.9.2 Monitoring Task Scheduling Jitter                                                                              | 74 |

| 5.9.3 Area, Throughput, and Latency Results                                                                          | 76 |

| CHAPTER 6 AREA-EFFICIENT EVENT STREAM ORDERING FOR<br>RUNTIME OBSERVABILITY OF EMBEDDED SYSTEMS                      | 79 |

| 6.1 Overview                                                                                                         | 79 |

| 6.2 Overview of System-Level Observation                                                                             | 80 |

| 6.3 Round-Robin Priority-Based Event Stream Controller                                                               | 83 |

| 6.4 Online Event Stream Processing                                                                                   |    |

| 6.4.1 Immediate Sort/Output                                                                                          | 87 |

| 6.4.2 Delayed Sort/Output                                                                                            |    |

| 6.5 Experimental Results                                                                                             |    |

| 6.5.1 Area Results                                                                                                   | 90 |

| 6.5.2 Event Stream Latency Analysis                                                                                  | 90 |

| 6.5.3 Event Stream Throughput Analysis                                                                               | 93 |

| CHAPTER 7 PRIORITY-LEVEL BASED EVENT STREAM TECHNIQUE<br>FOR NON-INTRUSIVE RUNTIME MONITORING OF EMBEDDED<br>SYSTEMS | 95 |

| 7.1 Overview                                                                                                         |    |

| 7.2 Priority-Level Based Event Stream Controller                                                                     |    |

| 7.3 Experimental Results                                                                                             |    |

| 7.3.1 Area Results                                                                                                   |    |

| 7.3.2 Latency Analysis                                                                                               |    |

| 7.3.3 Throughput Analysis                                                                                            |    |

| 7.3.4 Event Stream Buffer Size Analysis                                                                              |    |

| CHAPTER 8 CONCLUSIONS                                                                                                |    |

| CHAPTER 9 FUTURE WORK                                                                                                |    |

| REFERENCES                                                                                                           |    |

## LIST OF FIGURES

| Figure 1: Nonintrusive hardware observability framework for a MicroBlaze processor system consisting of several hardware observability interfaces ( <i>HWOI</i> ), a dedicated hardware observability bus ( <i>HWOBus</i> ), a hardware observability bridge |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ( <i>HWOBridge</i> ), and a hardware observability engine ( <i>HWOEngine</i> ) to execute the                                                                                                                                                                |

| observation software                                                                                                                                                                                                                                         |

| Figure 2: Hardware observability interface consisting of up to 32 hardware event probes                                                                                                                                                                      |

| (HEPs), timestamp register (HWOI TS) providing relative cycle-level execution                                                                                                                                                                                |

| counts, and memory-mapped interface for both controlling the hardware                                                                                                                                                                                        |

| observability monitoring and accessing runtime information for each HEP                                                                                                                                                                                      |

| Figure 3: HWOI interrupt (HWOIntr) generation indicating the one or more unmasked                                                                                                                                                                            |

| hardware events have been observed                                                                                                                                                                                                                           |

| Figure 4: Hardware event probe (HEP) controller. 32                                                                                                                                                                                                          |

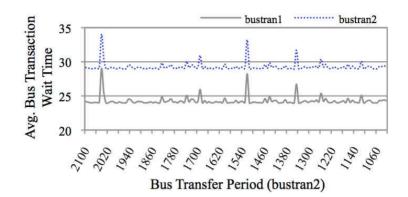

| Figure 5: Average bus transaction wait time for the configurable bus transaction cores,                                                                                                                                                                      |

| <i>bustran1</i> and <i>bustran2</i> , measured using the hardware observability framework 37                                                                                                                                                                 |

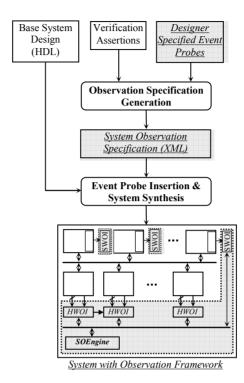

| Figure 6: Overview of system observability integration methodology utilizing pre-silicon                                                                                                                                                                     |

| verification specifications to automatically create a post-silicon, in-situ observation framework                                                                                                                                                            |

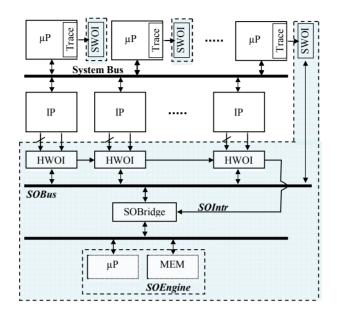

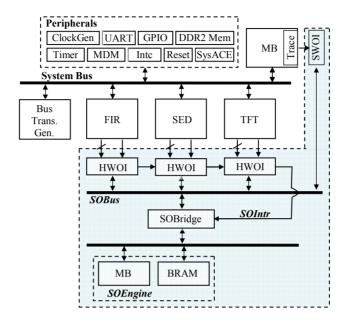

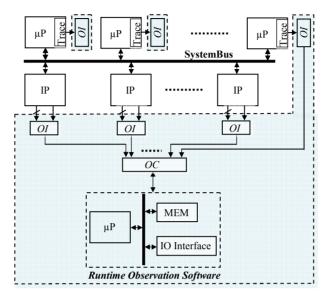

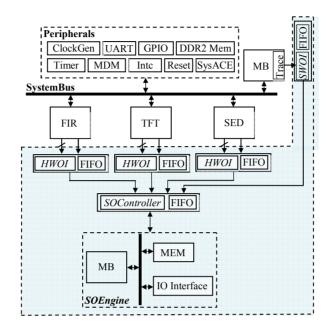

| Figure 7: Nonintrusive system-level observation framework consisting of several                                                                                                                                                                              |

| software observation interfaces (SWOIs), hardware observation interfaces (HWOIs),                                                                                                                                                                            |

| a dedicated system-level observation bus (SOBus), a system-level observation                                                                                                                                                                                 |

| bridge (SOBridge), and a system-level observation engine (SOEngine) to execute                                                                                                                                                                               |

| the observation software                                                                                                                                                                                                                                     |

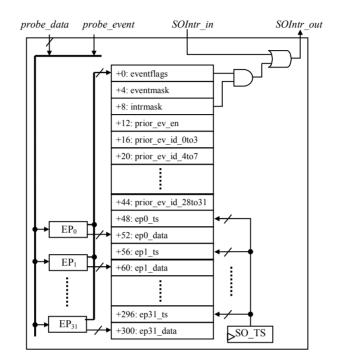

| Figure 8: Generalized structure of HWOI and SWOI consisting of up to 32 event probes                                                                                                                                                                         |

| (EPs), timestamp counter (SO_TS), and memory-mapped interface for managing                                                                                                                                                                                   |

| control registers and accessing the observation data in each EP                                                                                                                                                                                              |

| Figure 9: Event probe (EP) controller                                                                                                                                                                                                                        |

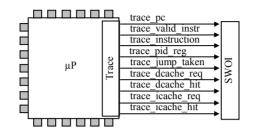

| Figure 10: Processor trace interface signals used in SWOI                                                                                                                                                                                                    |

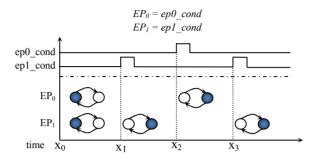

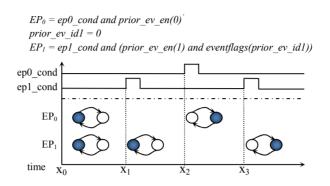

| Figure 11: Example system observation event behavior for two events $EP_0$ and $EP_1$                                                                                                                                                                        |

| without event cascading enabled. 51<br>Figure 12: Cascading event probe (CEP) controller. 52                                                                                                                                                                 |

| Figure 12: Cascading event probe (CEF) controller $52$<br>Figure 13: Example system observation event behavior for cascading events EP <sub>0</sub> and EP <sub>1</sub>                                                                                      |

| in which $EP_1$ is dependent on $EP_0$ having previously occurred                                                                                                                                                                                            |

| Figure 14: Overview of complete system design including three HWOIs and one SWOI.                                                                                                                                                                            |

|                                                                                                                                                                                                                                                              |

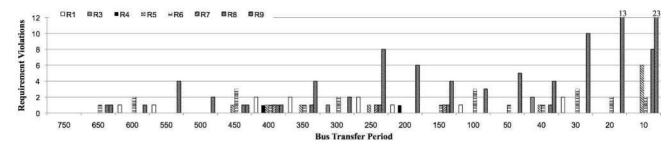

| Figure 15: Number of requirement violations within 30 minutes of system execution for                                                                                                                                                                        |

| decreasing idle periods between bus transactions                                                                                                                                                                                                             |

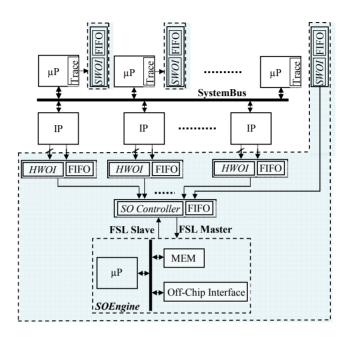

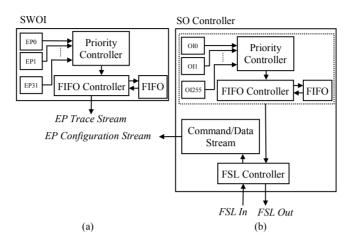

| Figure 16: System observation framework (SOF) consisting of several software                                                                                                                                                                                 |

| observation interfaces (SWOIs), hardware observation interfaces (HWOIs), a system                                                                                                                                                                            |

| observation controller (SOController), and a system observation engine (SOEngine)<br>executing the observation software                                                                                                                                      |

|                                                                                                                                                                                                                                                              |

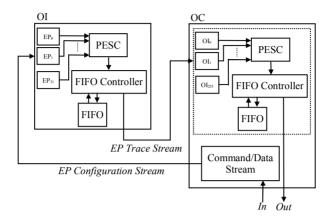

| Figure 17: Overview of priority-based event streaming hierarchy and configuration                    |

|------------------------------------------------------------------------------------------------------|

| stream interfaces for SOF                                                                            |

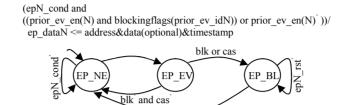

| Figure 18: Event probe (EP) controller for blocking, non-blocking, and cascading event               |

| probe                                                                                                |

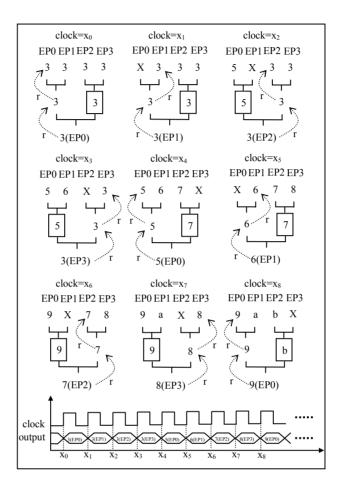

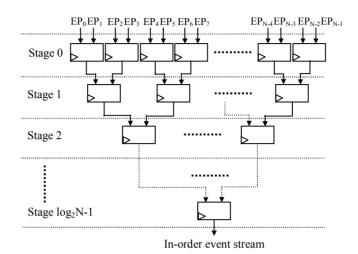

| Figure 19: Operation of in-order pipelined, priority-based event stream controller                   |

| highlighting the cycle by cycle operation for a system in which all EPs are triggered simultaneously |

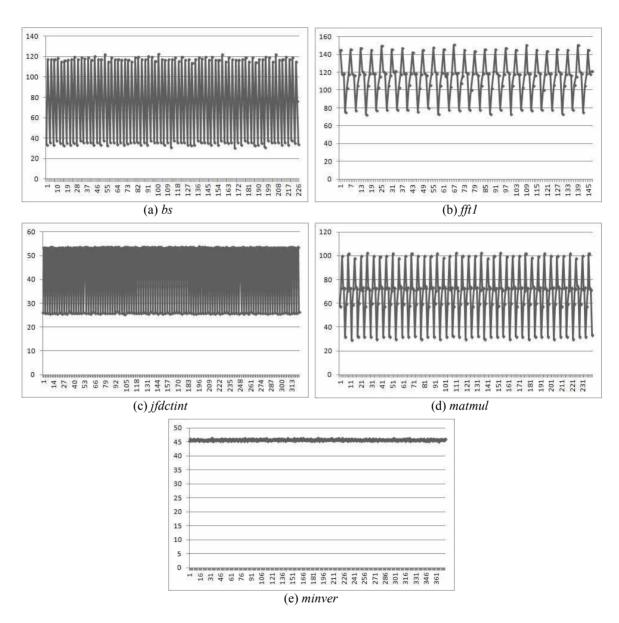

| Figure 20: Task completion time of application tasks (a) bs, (b) fft1, (c) jfdctint, (d)             |

| matmul, and (e) minver. The x-axis is the number of observed events and the y-axis                   |

| is time (ms) for 2 minute execution                                                                  |

| Figure 21: Scheduling jitter for application tasks (a) bs, (b) fft1, (c) jfdctint, (d) matmul,       |

| and (e) minver. The x-axis is the number of observed events and the y-axis is time                   |

| (ms) for 2 minute execution                                                                          |

| Figure 22: System observation methodology consisting of several observation interface                |

| (OIs) and in-situ observation software analyzing the event stream                                    |

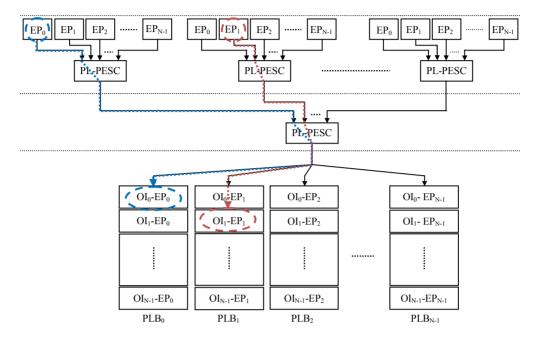

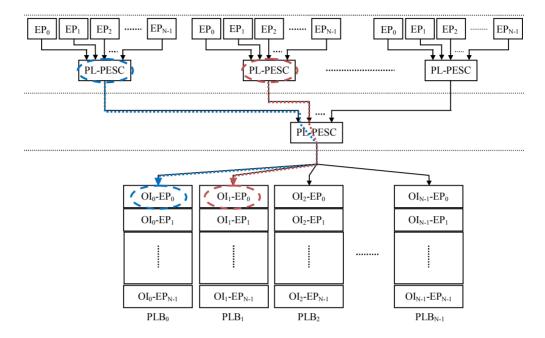

| Figure 23: Overview of priority-based event streaming hierarchy and configuration                    |

| stream interfaces for the system-level observation methodology                                       |

| Figure 24: Overview of pipelined event ordering hardware                                             |

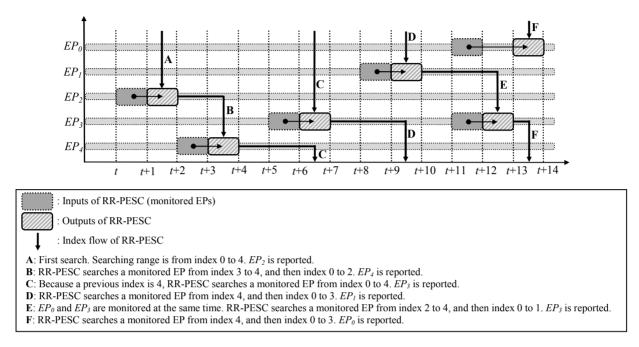

| Figure 25: Example operation of round-robin priority controller. The x-axis displays time            |

| (in clock cycles), and the y-axis displays EPs                                                       |

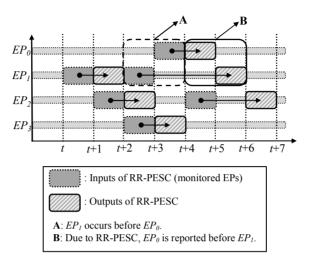

| Figure 26: An EP observed later can be output before an EP observed earlier. The x-axis              |

| displays time (in clock cycles), and the y-axis displays EPs                                         |

| Figure 27: Immediate Sort/Output Algorithm                                                           |

| Figure 28: Delayed Sort/Output Algorithm                                                             |

| Figure 29: Example operation of priority-level event stream controller using an $EP \rightarrow PL$  |

| priority assignment                                                                                  |

| Figure 30: Example operation of priority-level event stream controller using an OI $\rightarrow$ PL  |

| priority assignment                                                                                  |

| Figure 31: Overview of complete system design including three HWOIs and one SWOI.                    |

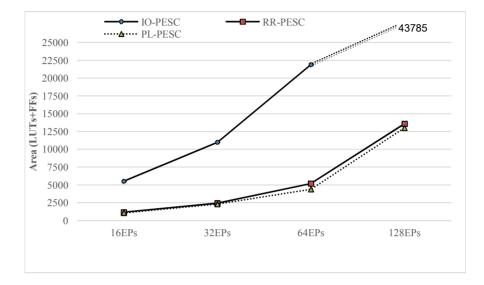

| Figure 32: Area requirements for the IO-PESC, RR-PESC and PL-PESC reported in                        |

| lookup tables (LUTs) and flip-flops (FFs)102                                                         |

# LIST OF TABLES

| Table 1: Summary of related work in dynamic trace and debug methods for hardware and software components of embedded systems.    18                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2: System and hardware observability area requirements reported in lookup tables                                                                                            |

| (LUTs) and flip-flops (FFs) for a Xilinx Virtex-5 FPGA (XC5VLX110T) for                                                                                                           |

| various components                                                                                                                                                                |

| Table 3: Description of processor trace interface signals.    48                                                                                                                  |

| Table 4: System latency requirements for target system.    54                                                                                                                     |

| Table 5: Area requirements for base system and SOF reported in lookup tables (LUTs)                                                                                               |

| flip-flops (FFs), and BRAMs                                                                                                                                                       |

| Table 6: Summary of periodic applications tasks based on applications within the SNU real-time benchmark suite                                                                    |

| Table 7: Area requirements for SOF components reported in lookup tables (LUTs), flip-                                                                                             |

| flops (FFs), and BRAMs                                                                                                                                                            |

| Table 8: Area requirements for the pipelined event ordering hardware and round-robir priority-based event stream controller reported in lookup tables (LUTs) and flip-flops (FFs) |

| Table 9: Latency (ms) for the pipelined event ordering hardware, the immediate sort/output and the delayed sort/output algorithms                                                 |

| Table 10: Throughput (events/second) for the pipelined event ordering hardware, the immediate sort/output and the delayed sort/output algorithms                                  |

| Table 11: Latency (ms) for the IO-PESC, RR-PESC with the immediate sort/output algorithm, and PL-PESC with the immediate sort/output algorithm                                    |

| Table 12: Throughput (events/second) for the IO-PESC, RR-PESC with the immediate sort/output algorithm, and PL-PESC with the immediate sort/output algorithm 106                  |

| Table 13: Event stream buffer size for the RR-PESC with the immediate sort/output algorithm and PL-PESC with the immediate sort/output algorithm                                  |

| Table 14: Summary of OI IDs, EP IDs, MFR, PL mapping (using an EP → PL priority assignment) for all EPs, and EBRs in the SLCS scenario                                            |

#### ABSTRACT

As system complexity continues to increase, the integration of software and hardware subsystems within system-on-a-chip (SOC) presents significant challenges in post-silicon validation, testing, and in-situ debugging across hardware and software layers. The deep integration of software and hardware components within SOCs often prevents the use of traditional analysis methods to observe and monitor the internal state of these components. This situation is further exacerbated for in-situ debugging and testing in which physical access to traditional debug and trace interfaces is unavailable, infeasible, or cost prohibitive.

In this dissertation, we present a system-level observation framework (SOF) that provides minimally intrusive methods for dynamically monitoring and analyzing deeply integrated hardware and software components within embedded systems. The SOF monitors hardware and software events by inserting additional logic within hardware cores and by listening to processor trace ports. The SOF provides visibility for monitoring complex execution behavior of software applications without affecting the system execution.

The SOF utilizes a dedicated event-streaming interface that allows efficient observation and analysis of rapidly occurring events at runtime. The event-streaming interface supports three alternatives: (1) an in-order priority-based event stream controller, (2) a round-robin priority-based event stream controller, and (3) a priority-level based event stream controller. The in-order priority-based event stream controller, which uses efficient pipelined hardware architecture, ensures that events are reported in-order based on the time of the event occurrence. While the in-order priority-based event stream controller provides high throughput for reporting events, significant area requirement can be incurred. The round-robin priority-based event stream controller is an area-efficient event stream ordering technique with acceptable tradeoffs in event stream throughput. To further reduce area requirement, the SOF supports a priority-level based event stream controller that provides an in-ordering method with smaller area requirements than the round-robin priority-based event stream controller.

Comprehensive experimental results using a complete prototype system implementation are presented to quantify the tradeoffs in area, throughput, and latency for the various event streaming interfaces considering several execution scenarios.

#### **CHAPTER 1**

#### **INTRODUCTION**

As system complexity continues to increase, the integration of software and hardware components within embedded systems presents key challenges in monitoring and analyzing complex hardware and software interactions. The deep integration of software and hardware components within embedded systems often prevents the use of traditional analysis methods to monitor and analyze the internal state of these components. This situation prevents the use of a logic analyzer to observe the interaction within embedded systems and may affect the system correctness during monitoring the erroneous behavior.

Existing debugging methods that require the system execution to be halted are intrusive, either requiring significant hardware resources or leading to system perturbations that can change the execution behavior, and pose considerable challenges for in-situ analysis. For example, JTAG [29] scan chains allow all registers within an SOC design to be monitored or controlled at runtime. However, in order to access those registers, the system execution must be halted. This perturbs the system execution such that observing the desired behavior may no longer be possible. Therefore, for in-situ analysis of monitored events, such intrusive methods are often infeasible, and when utilized may lead to system failure due to timing constraint violations—e.g. missed execution deadlines. Although many challenges exist for runtime in-situ system monitoring and testing, pre-silicon verification and testing methods provide a wealth of information that can potentially be utilized to efficiently monitor system execution at runtime. For example, important pre-silicon verification requirements can be effectively reused within post-silicon validation and testing procedures [5][6].

Intrusive debugging methods pose considerable challenges in real-time systems, for which hard execution constraints are critical to system correctness. If a task within the system does not complete its execution within the required time, the task can be considered to have failed. Whereas failure to meet hard execution deadlines may result in complete system failure, failure to meet soft execution deadlines lead to undesired system behavior that can incur system failure. Soft deadlines must still be met to meet the desired systems goals. Hence, new debugging and verification methods are needed to provide insitu analysis methods capable of monitoring software and hardware interactions without perturbing the system execution.

To overcome the challenges of traditional JTAG interfaces, numerous approaches have focused on trace-based methods for logging system events in both hardware and software components using dedicated trace and debug ports. For example, ARM's CoreSight [7] and Embedded Trace Microcell [8] can be synthesized within an SOC design to provide system-level trace capabilities using a dedicated trace port. However, these system-level trace methods are often limited in the amount of data that can be traced and stored in real-time or limited by the bandwidth of the trace port in reporting data to external test equipment.

In this dissertation, we present an event-driven system-level observation framework (SOF) providing low-overhead methods for observing and analyzing complex interactions across hardware and software boundaries at runtime. The SOF provides insitu support for controlling event probes within software and configuring hardware components using blocking, non-blocking, and cascading configurations. For serializing and reporting rapidly occurring event, the SOF provides three types of a priority-based event streaming interfaces. The contributions in this dissertation are: 1) a configurable, nonintrusive framework for monitoring designer-specified hardware and software events; 2) advanced observation methods for analyzing complex system events using blocking, non-blocking, and cascading event probe specifications; 3) a high-throughput pipelined, priority-based event streaming interface for serializing and analyzing monitored events at runtime; 4) area-efficient priority-based event streaming interfaces for efficiently reporting monitored events at runtime; and 5) a software sorting algorithm for efficiently sorting the event stream to provide a time ordered stream of observe events.

In Chapter 3, we present an initial framework for minimally intrusive hardware observability that provides designers with the ability to monitor complex application-specific hardware execution behavior at runtime with zero or minimal impact on system execution. In Chapter 4, we present an event-driven system-level observation framework that provides low-overhead methods for observing and analyzing designer specified hardware and software events at runtime. In Chapter 5, we present a system observation framework for monitoring and analyzing rapidly occurring software events. This system observation framework provides runtime support for defining and controlling software events with using blocking, non-blocking, and cascading event probes. In Chapter 6, we present an area-efficient event stream ordering technique that significantly reduces area requirements and two software sorting algorithms with acceptable tradeoffs in event

stream throughput. In Chapter 7, we present the priority-level based event streaming interface and a software sorting algorithm. In Chapter 8 and Chapter 9, we conclude and highlight future work.

#### **CHAPTER 2**

#### **RELATED WORK AND BACKGROUND**

In this section, we provide an extensive overview of related work on runtime trace and debug methods for hardware and software components. Table 1 provides a summary and classification of related work highlighting the collection method, target components, analysis method, storage, intrusiveness, and runtime configurability for each approach. The *collection method* defines how an approach collects data within the target system using trace based, scan based, or event driven alternatives. The target highlights the components within the SOC the approach seeks to monitor categorized as hardware or software. The analysis method indicates how and where the observed information is analyzed, including in-situ on-chip, in-situ off-chip, or offline. The storage defines where the collected information is stored within the system, including on-chip buffers, off-chip memory, none, or user-defined. The *intrusiveness* of an approach is defined as how the approach affects the execution of the system categorized as non-intrusive, minimally intrusive, and intrusive. A non-intrusive approach is one that in no way affects or perturbs the system execution. In contrast, an intrusive approach exhibits considerable impact on the system execution to the extent that it can affect both the correctness of the system execution and the validity of the information. A minimally intrusive approach is one that may impact the system, but the impact is either minor or can be controlled at runtime to minimize or eliminate the negative effects of the monitoring method. Lastly, the *runtime*

| Reference        | Collection<br>Method <sup>a</sup> | Target <sup>b</sup> | Analysis<br>Method <sup>c</sup> | Storage <sup>d</sup> | Intrusive-<br>ness <sup>e</sup> | Runtime<br>Config. <sup>f</sup> | Overheads and Note                                                                                                                                                                           |

|------------------|-----------------------------------|---------------------|---------------------------------|----------------------|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG [29]        | S                                 | H/S                 | OF                              | Ν                    | Ι                               | Ν                               | Requires systems to be halted to access internal signals.                                                                                                                                    |

| [2][3]           | T/E                               | Н                   | ION/IOC                         | В                    | N                               | С                               | Reconfigurable hardware resources for<br>implementing monitoring logic,<br>programmable through JTAG                                                                                         |

| [7][8]           | T/S                               | H/S                 | ION/IOC/OF                      | В                    | N/I                             | N                               | Limited by the number of signals that<br>can be traced and bandwidth of trace<br>port.                                                                                                       |

| [11][27][28][79] | Т                                 | S                   | ION/IOC                         | Ν                    | N/M                             | С                               | Utilizes the hidICE emulator to<br>observe multicore SOC designs. The<br>hidICE provides real-time trace with<br>minimal interference.                                                       |

| [18]             | Е                                 | Н                   | OF                              | N                    | Ι                               | N                               | Halts systems to report external debug events.                                                                                                                                               |

| [21][22]         | E                                 | H/S                 | IOC                             | 0                    | N/M                             | N                               | Requires host systems to analyze trace events.                                                                                                                                               |

| [24][25][75][76] | T/S                               | Н                   | IOC/OF                          | В                    | N/I                             | N                               | Limited by the number of signals and<br>duration that can be traced due to on-<br>chip memory and JTAG bandwidth<br>limitations.                                                             |

| [26][77][78]     | Е                                 | S                   | IOC                             | N                    | М                               | N                               | Lightweight software instrumentation utilized to monitor software events.                                                                                                                    |

| [31]-[40][60]    | E                                 | Н                   | OF                              | В                    | N/M                             | С                               | Utilizes efficient methods for<br>controlling when to trace and how to<br>store data within available trace buffer.<br>Limited by size of trace buffers and<br>bandwidth of off-chip access. |

| [41][42][43][74] | T/S                               | Н                   | OF                              | В                    | Ι                               | С                               | Option exists for implementing custom<br>analysis logic in hardware to filter<br>trace signals                                                                                               |

| [49]-[54]        | Е                                 | Н                   | OF                              | В                    | N/M                             | С                               | Method for custom creation of interconnection fabric for trace buffers.                                                                                                                      |

| [67]             | Е                                 | Н                   | IOC                             | N                    | М                               | N                               | Utilizes off-chip assertion checker<br>implemented within an FPGA.                                                                                                                           |

| [70][71]         | Е                                 | Н                   | IOC                             | 0                    | Ι                               | С                               | Profile of monitored events is transmitted over system bus.                                                                                                                                  |

| [72]             | S                                 | S                   | ION                             | Ν                    | М                               | N                               | To limit intrusion, an extension of<br>GDB enables a non-stop mode in<br>which only a single task is stopped<br>during debugging and all other tasks<br>can execute normally.                |

| [86]             | S                                 | Н                   | OF                              | Ν                    | Ι                               | Ν                               | Uses custom scan-chain for monitoring a subset of signals within system.                                                                                                                     |

| <u>SOF</u>       | <u>E</u>                          | <u>H/S</u>          | <u>10N</u>                      | <u>U</u>             | <u>N/M</u>                      | <u>C</u>                        | Event-driven in-situ observation<br>framework supporting configurable<br>method for observing, configuring,<br>analyzing, and reporting observations.                                        |

Table 1: Summary of related work in dynamic trace and debug methods for hardware and software components of embedded systems.

a. T=Trace, S=Scan-chain, E=Event-driven c. ION=In-situ on-chip, IOC=In-situ off-chip, OF=Offline e. N=Non-intrusive, M=Minimally intrusive, I=Intrusive

b. H=Hardware, S=Software

d. B=On-chip Buffer, O=Off-chip memory, N=None, U=User-define f. C=Configurable, N=Non-configurable

configurability indicates if an approach can be configured at runtime to select which

signals or events to monitor.

A software debugger allows an engineer to debug a software design by halting the execution of software at a particular point and examine the state of the software by observing the state of the processor's internal registers and system memory. A software breakpoint works by inserting a special instruction in the software design to be debugged. When the instruction is called, it invokes the debugger's exception handler. Similar tools exist for hardware designs [18][86], but it is difficult to pragmatically match the utility of a software debugger given the inherently parallel execution of hardware cores for two reasons. First, software is fundamentally linear. While high-level programming languages may obscure the fact, at the machine interface, software is a linear sequence of instructions. Second, the regularity of the load-store computer architecture means that intermediate results almost usually return to the memory system.

Furthermore, a debugger has a high utility only when testing a subsystem in isolation. As the number of subsystems that the debugger does not control increases, the utility of the debugger decreases dramatically. Halting one subsystem is of low value if the rest of the system—e.g. sensors, actuators, physical processes—continues to operate. Debugging within real-time systems presents additional challenges as proper operation is dependent on meeting tight timing constraints that can be easily perturbed during debugging.

*truss* [59] is an example of an indiscriminate trace tool that allows users to capture data regarding every system call that a program makes. This execution trace can be a powerful analysis tool because it isolates a very specific identifiable behavior, e.g. system calls, and makes a history available to the designer. If, however, a program's suboptimal

behavior is caused by the timing or frequency of making specific system calls, indiscriminately tracing with *truss* may slow the program down enough to cause it to leave the set of states we want to observe.

Solaris DTrace [19][59] and Linux SystemTap [68] are examples of dynamic software observability that are differentiated by several key attributes. Solaris DTrace implements several optimizations of dynamic tracing that are important to consider, as DTrace partially served as the inspiration for supporting hardware and system-level observability. First, disabled probes have no insertion penalty. In other words, a disabled probe incurs no execution overhead. Second, insertion of a probe does not require a design-time decision. Third, the code inserted for a probe point must be inserted in a manner consistent with the security and reliability requirements of the system. Unlimited insertion of arbitrary code would be likely to permit a user to circumvent security restrictions or insert unstable software.

In the context of real-time systems, previous work has focused on reducing the overhead of traditional software debuggers. When debugging a single task within a multitasked system, stopping all tasks during debugging is extremely intrusive, and can lead to incorrect behavior and even system failure. To minimize this intrusion, an extension of GDB enables a non-stop mode in which only a single task is stopped during debugging and all other tasks can execute normally [72]. This allows a user to control tasks explicitly in ways that are not possible in all-stop mode, meaning that all tasks of execution stop during debugging.

Leatherman and Stollen [41][42][43][74] present a debug methodology that incorporates distributed on-chip instrumentation (OCI) components allowing designers to configure how to trace—e.g. by defining the trace width and depth—and when to trace e.g. by defining triggers that start the trace process. The distributed OCI components can then be connected by a dedicated bus to an on-chip analyzer that can control and process the trace data before making that data accessible off-chip through a JTAG interface. The authors further propose a HyperJTAG interface that combines existing JTAG interfaces for processors within a multicore system with the distributed OCI components available through a single IP interface.

Similarly, Vermeulen and Goel [24][25][75][76] present a silicon debugging strategy for multiple clock domain systems using a JTAG port, in which an on-chip memory is utilized to trace specific internal signals that can later be accessed through the JTAG port. The proposed on-chip debug infrastructure and debugging software provide support for both real-time and time-intrusive monitoring. In order to support real-time, i.e. nonintrusive, monitoring, an on-chip memory is utilized to trace specific internal signals, which can then be accessed through the JTAG port. However, due to limitation in the availability on an on-chip memory, the duration and number of signals that can be monitored in real-time are limited.

Abramovici et al. [2][3] present a distributed reconfigurable fabric of multiplexers enabling designers to select a subset of signals to monitor. The selected signals are processed by a debug monitor that can directly forward the captured signals or perform basic processing on those signals—e.g. the debug monitor can directly process signals to only report anomalous ones. Each configurable multiplexer and debug monitor operates within a single clock domain. The outputs from the distributed debug monitors are collected together by a trace component that records the signals into an on-chip memory that can then be accessed by a JTAG port. The proposed distributed debug offers the advantage of being able to limit the amount of data that is traced, supporting multiple clock domains, and eliminating the need to route all probes to a single trace component, which can often lead to a unroutable design during the synthesis process.

Ko et al. [31]-[40][60] propose a system-level debug architecture targeted for postsilicon validation that utilizes configurable event triggers, a network of trace buffers, and a configurable communication framework for efficiently storing data samples within the available trace buffers. The event triggers enable designers to specify conditions that will start tracing of specific signals. The trigger conditions can be configured by designers through a set of configurable comparators. This approach enables designers to change event triggers at runtime. The proposed debug architecture includes a network of trace buffer for handling the simultaneous tracing of multiple data signals. The trace buffer architecture controls how traced signals are stored among available trace buffers according to designer specified priorities. While this debug methodology provides support for runtime configuration, the proposed approach is not focused on enabled runtime in-situ analysis of tracing events and data.

Liu and Xu [49]-[54] propose a methodology for creating an area efficient trace interconnection fabric. Given the set of signals that need to be traced, a custom interconnection fabric is created in which multiplexers are utilized to trace mutually

exclusive signals—i.e. signals that are unlikely to occur simultaneously—and a custom crossbar network is utilized to trace concurrently accessible signals. Using either designer specified identification of the types of signals to trace or analysis of the circuit structure, a customized interconnection fabric can be generated.

Rather than incorporate a scan-chain directly within an RTL design, Yang et al. [86] propose an alternative automated method for selecting and extracting a subset of internal signals to be monitored. The selected signals are monitored by a separate FPGA-based test platform that provides scan-chain access to these signals for use within a co-simulation environment. The propose methodology has the advantage of being able to utilize the original testbench developed for the RTL design, while relying on automated tools to extract the desired signals for post-silicon co-simulation and verification.

Watterson and Heffernan [26][77][78] propose an online software monitoring method with the specific focus on developing a minimally intrusive method so as not to affect the execution of the application. Within the proposed method, events from the processor can be generated by minimally intrusive software instrumentations that report an event to a dedicated on-chip monitoring core. The monitoring core can then process the events and report the required data to the external environment.

The Owl framework [70][71] is a distributed approach that incorporates monitoring modules within the specific parts of the system to be monitored. The distributed monitoring modules communicate the profile data to a specific location in main memory or to a separate memory dedicated for profiling. However, because the monitors will need to transmit this data via the system bus, the proposed approach can be intrusive due to

bus contention. As the intended target is a system realized within an FPGA, the monitoring modules themselves are reconfigurable. This allows a designer to change how the monitoring process is implemented at runtime. For example, a designer can reconfigure the monitoring modules to alter the frequency at which the profile data is written to memory to reduce the profiling traffic on the system bus.

The MAMon monitoring system [21][22] proposes a methodology for monitoring hardware and software based events within SOC designs by incorporating dedicated logic within hardware components to detect occurrences of specific events being monitored. A probe unit is utilized to capture and log all occurrences of these events within an external memory. Events within the MAMon system are defined as conditional expressions that are evaluated during each clock cycle. However, a host workstation is required to view and analyze the event log with capabilities for filtering and searching the monitored events.

Hardware assertions are typically used during the validation and verification stages of hardware developments. Assertions can be specified to formally define design requirements often utilized within simulations to verify correct behavior. If the requirements are violated, an error will be asserted such that designers can identify and correct the incorrect behavior. A common method for specifying design requirements using assertions is the Property Specification Language (PSL) [4][30].

Research efforts have also resulted in methods and tools for automatically generating hardware assertion checkers in the form of VHDL or Verilog code from assertion specified using PSL [1][14]-[17]. For example, the FoCs tool [1] was developed

to automate the verification process by generating hardware assertion checkers from a PSL specification that can be directly utilized within standard simulation environments. The FoCs tool significantly reduces development time and costs by eliminating the need for designers to manually create HDL for the assertions and eliminating the need to utilize specialized tools. Although the FoCs tool was initially targeted at design time simulation and verification, several efforts have explored the benefit of online assertion checkers [12][13][55]-[58][62]-[66]. Online assertion checking directly integrates the hardware assertion checkers within the prototype—or even final—hardware implementation. Such an approach offers several advantages over simulation, including the ability to verify the system within a deployed environment. In contrast to the proposed observability framework, online assertion checker only logs the occurrence of an assertion, and does not provide any mechanism for analyzing or responding to these assertions at runtime.

In [67], a debugging and verification environment is presented that is capable of monitoring multiple internal signals—or hardware probes—within a hardware design and provides real-time trace for a subset of those signals via a dedicated debug port. Given a large number of signals a designer may want to monitor, the debug port provides a reconfigurable data filter that can be rapidly reconfigured to select the subset of signals that are traced. This provides a balance between the inputs and outputs necessary for the debug port and the number of internal probes that can be supported. The trace data is transmitted to an assertion checker implemented by using an FPGA that can be utilized to

verify correct execution of the device—typically by verifying properties defined within an assertion language, such as PSL.

Backasch et al. [11] presented a runtime verification approach to observe multicore SOC designs and verify designer-specified system properties. The approach utilizes the hidICE (hidden ICE) emulator [27][28][79] that transfers trace data to external analysis tools. The behavior and the instructions carried out by the target SOC design can be precisely reconstructed and emulated by the hidICE emulator. The hidICE emulator enables observability of multicore SOC activities (e.g., bus control events, bus reads, interrupts, processors power state changes) to capture real-time, and concurrent trace of processors and hardware cores in shared bus multicore SOC. This framework utilizes a combination of on-chip analysis to extract the synchronization event needed between the target SOC and emulator, and off-chip analysis within the emulator and host device for analysis the system execution.

## **CHAPTER 3**

# HARDWARE OBSERVABILITY FRAMEWORK FOR MINIMALLY INTRUSIVE ONLINE MONITORING OF EMBEDDED SYSTEMS

#### 3.1 Overview

As the complexity of digital systems rapidly increases, designers are presented with significant challenges in monitoring, analyzing, and debugging the complex interactions of various software and hardware components. Existing hardware tests and debugging methods are often intrusive, either requiring significant hardware resources or requiring the execution of the system to be halted thus leading to system perturbations that can change the execution behavior to an extent that the erroneous behavior can no longer be observed—or lead to system failure due to missed execution deadlines.

In this chapter, we present an initial framework [44] for hardware observability that extends such dynamic observation capabilities to hardware and mixed hardware/software environments, thereby providing a runtime environment permitting system-wide observability. The hardware observability framework provides a flexible mechanism that can detect arbitrary designer-specified hardware events and allows users to observe those events through user-defined observation software.

## **3.2 Hardware Observability Framework**

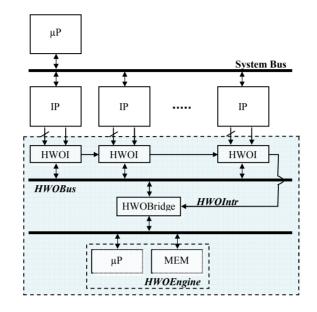

Figure 1 provides an overview of the proposed hardware observability framework for a system incorporating a Xilinx MicroBlaze processor [61][82] and several hardware cores.

Figure 1: Nonintrusive hardware observability framework for a MicroBlaze processor system consisting of several hardware observability interfaces (*HWOI*), a dedicated hardware observability bus (*HWOBus*), a hardware observability bridge (*HWOBridge*), and a hardware observability engine (*HWOEngine*) to execute the observation software.

We utilize a MicroBlaze processor-based system as an illustrative example throughout this article to closely match our experimental results in which the hardware observability framework was implemented and evaluated using a Xilinx FPGA. In contrast to existing methods for debugging, testing, and tracing of hardware designs, the hardware observability provides a nonintrusive framework for monitoring complex designerspecified hardware events. In response to those hardware events, designers can create customized observation software to analyze and monitor the hardware events for the specific testing, debugging, or monitoring tasks at hand.

The nonintrusive hardware observability framework for a MicroBlaze processor systems consists of one hardware observability interface (*HWOI*) for each hardware core,

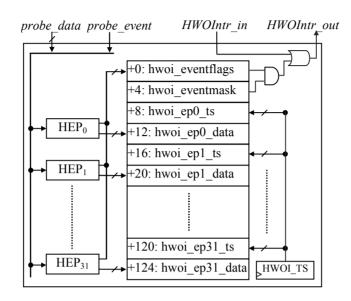

Figure 2: Hardware observability interface consisting of up to 32 hardware event probes (HEPs), timestamp register (HWOI\_TS) providing relative cycle-level execution counts, and memory-mapped interface for both controlling the hardware observability monitoring and accessing runtime information for each HEP.

a dedicated hardware observability bus (*HWOBus*), a hardware observability bridge (*HWOBridge*), and a small secondary microprocessor for the hardware observability engine (*HWOEngine*) to execute the observation software.

## 3.2.1 Hardware Observability Interface (HWOI)

The hardware observability interface (HWOI), presented in Figure 2, provides the fundamental framework for dynamically monitoring designer-specified elements within hardware circuits without intrusion or interruption to the circuit operation. The HWOI consists of one or more hardware event probes (HEPs), a timestamp register (HWOI\_TS), and a memory-mapped interface for controlling individual event probes and accessing the observation data for each probe.

Within the hardware observability approach, the basis element that can be observed is a hardware event. For each hardware IP core, the hardware events that need to be monitored at runtime area dependent on each specific hardware design. Hence, a designer must specify both the set of events to be observed and the set of probe signals from the IP cores that are needed to make these observations. While this approach requires additional effort on behalf of the designer, the core designer is the best source of knowledge for determining which event probes are needed to provide the highest level of observability for that hardware circuit. We note that although manual effort is currently required to incorporate additional hardware probes, our immediate future work focuses on developing automated tools for specifying hardware probes and automatically inserting the required logic within the hardware core. This event-driven observation approach provides significant flexibility in that complex execution behavior can be effectively observed at runtime and rapidly integrated within the observation framework.

The probes exported from the hardware cores can either consist of direct connections to internal signals or dedicated logics needed to detect an internal event. For example, consider a hardware event probe intended to monitor when access is granted to a shared bus for a burst transaction. To monitor this event, only the bus acknowledge signal needs to be exported to the HWOI. On the other hand, in order to observe a complex event such a specific execution order of states within a finite state machine, additional logic may be needed to track the sequence of events needed to trigger the event probe. Alternatively, the state register for the FSM can be exported to the HWOI, in which the logic required to detect the execution sequence can be incorporated.

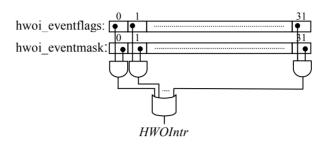

Figure 3: HWOI interrupt (*HWOIntr*) generation indicating the one or more *unmasked* hardware events have been observed.

The HWOI includes a timestamp counter (HWOI\_TS) that provides a simple mechanism for analyzing the relative timing behavior between individual events. The HWOI\_TS is a 32-bit free running counter that is incremented each hardware observability cycle. Considering a 100 MHz clock, the HWOI\_TS counter provides the ability to measure the timing of event occurrences up to 40 seconds apart, beyond which a user would be required to develop additional timing capabilities within the observation software. For systems with higher clock frequencies the size of the HWOI\_TS can be increased appropriately.

Each hardware event probe (HEP) defined by the designers will be associated with a one-bit event flag, a one bit event mask, a 32-bit timestamp register, a 32-bit data register, and HEP controller for the controlling the observation processes.

The events flags and event masks for all hardware event probes are accessible through two memory-mapped registers, *hwoi\_eventflags* and *hwoi\_eventmask*. Reading the *hwoi\_eventflags* register will return to the current state for all HEPs within HWOI, where a logical one indicates the hardware event has been observed, and a logical zero

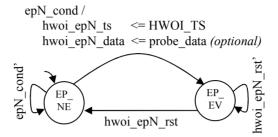

Figure 4: Hardware event probe (HEP) controller.

otherwise. Individual HEPs can be masked—or disabled—by configuring the *hwoi\_eventmask* register.

If any unmasked hardware event has been observed, the HWOI will assert an interrupt, *HWOIntr*, as shown in Figure 3. The *HWOIntr* is daisy-chained through all HWOIs within the system, providing a single interrupt to the hardware observability engine (HWOEngine) to indicate that one or more hardware events have been observed.

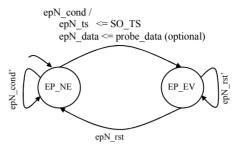

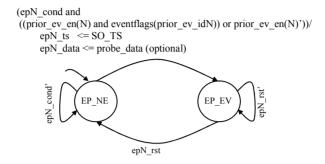

Each HEP contains an HEP controller implemented as a simple state machine consisting of two states, as shown in Figure 4. Initially, the HEP controller waits in the *no event* state, EP\_NE, until the desired event is observed, defined by the logical expression *epN\_cond*. When the hardware event is observed, the HEP controller will capture the current HWOI\_TS value and probe data into the HEP's timestamp, *hwoi\_epN\_ts*, and data, *hwoi\_epN\_data*, registers—both of which are optional and can be defined by the designer. The HEP controller will then transition to the *event* state, EP\_EV. In the EP\_EV state, the HEP controller waits until a reset signal, *hwoi\_epN\_rst*, is asserted for the probe. Writing a zero into the corresponding bit of the hwoi\_eventflags register generates the reset signal for an individual probe.

Minimally, to define an HEP, as designer must specify a Boolean condition corresponding to the target event and optionally define which data value should be captured on occurrence of this event. This specification can be directly incorporated within the state machine for the HEP controller. Alternatively, for monitoring complex sequential events, a designer can incorporate additional states within HEP controller to detect complex sequences for the target event.

We have currently designed the HWOI to support up to 32 HEPs, requiring a total of the 66 memory-mapped registers within the HWOI. The memory-mapped addresses for each register are illustrated in Figure 2. If a timestamp or event probe data is not needed for an HEP, the associated registers will be replaced with logical zeros in order to maintain a consistent memory mapped address space. Although currently supporting a maximum of 32 HEPs, the HWOI can be efficiently optimized if fewer HEPs are needed. Finally, we note that the proposed HWOI does not support logging multiple occurrences of a single HEP. Although this currently limits the frequency at which individual events can be monitored, future work specially focuses on providing low overhead methods to capture such occurrences for specific designer-specified event probes.

### 3.2.2 Hardware Observability Bus and Bridge

To avoid any contention over the system bus, a separate hardware observability bus (HWOBus) is utilized for communication with the HWOIs for the hardware IP cores. The HWOBus is a simple synchronous bus with unidirectional data input and output signals optimized for the small address space needed to support the HWOIs. A hardware observability bridge (HWOBridge) component is utilized to interface the HWOBus to the

processor local bus of the hardware observability engine. The HWOBridge implements the necessary address mapping and synchronization to interface between the two buses.

## 3.2.3 Hardware Observability Engine

The hardware observability engine (HWOEngine) is implemented as a set of user-defined software functions executing on a lightweight processor. The HWOEngine provides a set of APIs that can be utilized to hide the software interfacing details required to access the memory-mapped registers within each HWOI.

In response to the *HWOIntr* signal generated whenever any hardware event is observed, the HWOEngine first reads the *hwoi\_eventflags* register within all HWOIs. For each hardware event that has been observed, a user can associate an arbitrary software function into which the user provides the required observation capabilities. Once the observability software has completed, the HWOEngine must reset the HEP by writing a logical zero to the *hwoi\_eventflags* register within the HWOI. Importantly, care must be taken to only reset those HEPs that have been processed by the HWOEngine, as additional hardware events may have been observed within the HWOI during the execution of the hardware observation software. Furthermore, users are provided the option to either automatically reset the HEPs through the provided APIs or leave this control to the user-defined observation software.

This method for system observability offers several advantages. First, designers and end-users are provided great flexibility in controlling how and when to observe the various hardware components. Secondly, while the HEPs are fixed at design time, the user can update the observation software if observation needs change. Thirdly, the hardware observability framework can be readily integrated with existing methods for software observability, such as DTrace, thereby providing a single framework for system observability.

Given the goal of providing nonintrusive framework for hardware observability, the HWOEngine is implemented as a separate lightweight microprocessor system, as shown in Figure 1. The HWOEngine includes a dedicated processor (MicroBlaze), small memory (BRAM) for the observation software, interrupt controller, and communication device (UART) for controlling the observation software and providing minimal external reporting and tracing capabilities. Thus, the observation process is completely isolated from the main system, thereby eliminating any potential performance impacts on the main system execution. Furthermore, this implementation provides a secure method for ensuring that the user-defined observation software cannot corrupt and/or harm the system execution.

### **3.3 Experimental Results**

To evaluate the hardware observability framework, we consider a base system consisting of a 100 MHz MicroBlaze processor and three hardware IP cores connected to the PLB. The primary hardware core for this system is a 13-tap FIR filter that periodically processes data provided by the software application executing on the MicroBlaze microprocessor.

In addition, two configurable bus transaction cores, *bustran1* and *bustran2*, were developed. These cores are designed to model varying bus transfer patterns. In previous

efforts, we developed a complex streaming application utilizing the MicroBlaze processor and multiple dedicated hardware cores. During initial development efforts for this system, aperiodic delays in bus accesses and decreased throughput resulted in noticeable performance degradations. In determining the source of the execution delays, significant effort was required to directly incorporate additional logic within all hardware cores to monitor bus transactions, including bus requests, bus acknowledgments, and bus throughput. To create an analogous execution scenario, we utilize the configurable bus transaction hardware cores to generate similar—but controllable—bus access patterns.

We incorporated our hardware observability framework using the nonintrusive architecture presented in Figure 1. Three HEPs were defined for each hardware IP core. The FIR core implementation utilizes a mix of floating point inputs/outputs and fixedpoint internal computations. Thus, we incorporated three HEPs within the FIR core to detect and monitor various overflow conditions. Within each of the bus transaction cores, HEPs were defined to monitor the start of a bus request, bus access granted to the hardware core, and the bus transaction completion. The corresponding observability software executed on the HWOEngine reports any overflow conditions within the FIR core and computes various bus access statistics including average bus transaction wait time and data throughput.

The two bus transaction cores were configured to periodically transfer 4000 bytes of data using a burst transaction. *bustran1* periodically performs this transfer once every 1000 clock cycles. For the *bustran2* core, we varied the transfer period from once every 2000 cycles to once every 1000 cycles. Figure 5 presents the resulting average bus

Figure 5: Average bus transaction wait time for the configurable bus transaction cores, *bustran1* and *bustran2*, measured using the hardware observability framework.

transaction wait time for both *bustran1* and *bustran2*. The analysis demonstrates that for periodic bus transactions with differing transfer rates, overlapping periods of bus transaction can result in noticeable transfer delays of up to 13%. Furthermore, the bus priority assignment for these cores can have a significant effect on performance. Even with identical transfer periods, the *bustran1* components exhibits a 17% longer average wait time compared to *bustran2*.

We note that the proposed hardware observability framework is designed to be integrated within the final system implementation, such that system designers and endusers can utilize the hardware observability framework for testing, debugging, and monitoring the execution of a system both during testing and implementation phases as well as after system deployment.

The base system was synthesized using Xilinx Platform Studio (XPS) 11.5 [80] onto a Virtex-5 (XC5VLX110T) FPGA development board. Table 2 reports the area required by the base system in lookup tables (LUTs) and flips-flops (FFs). The base

|                   | LUTS  | FFS   | LUT+FF | %   |

|-------------------|-------|-------|--------|-----|

| BASE SYSTEM       | 10383 | 8751  | 19134  | 100 |

| System with HWO   | 13527 | 11676 | 25203  | 132 |

| HWO ENG. & BRIDGE | 2637  | 2214  | 4851   | 25  |

| HWO BRIDGE        | 354   | 320   | 674    | 4   |

| HEPs(1)           | 89    | 68    | 157    | 0.8 |

| HEPs (2)          | 136   | 104   | 240    | 1.3 |

| HEPs (4)          | 205   | 176   | 381    | 2   |

| HEPs (8)          | 273   | 320   | 593    | 3   |

| HEPs (16)         | 478   | 608   | 1086   | 6   |

| HEPs (32)         | 878   | 1184  | 2062   | 11  |

Table 2: System and hardware observability area requirements reported in lookup tables (LUTs) and flip-flops (FFs) for a Xilinx Virtex-5 FPGA (XC5VLX110T) for various components.