# System-Level Performance Evaluation of Three-Dimensional Integrated Circuits BARKER

by

## Arifur Rahman

B.S., Polytechnic University (1994) S.M., Massachusetts Institute of Technology (1996)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

January 2001

© Massachusetts Institute of Technology 2001. All rights reserved.

| Author                  |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Dep                     | partment of Electrical Engineering and Computer Science<br>January 12, 2001 |

|                         |                                                                             |

|                         |                                                                             |

| Certified by            |                                                                             |

|                         | Rafael Reif                                                                 |

| Associate Department He | ad and Professor of Electrical Engineering and Computer Science             |

|                         | Thesis Supervisor                                                           |

|                         |                                                                             |

|                         |                                                                             |

| Accepted by             | · · · · · · · · · · · · · · · · · · ·                                       |

|                         | Arthur C. Smith                                                             |

|                         | Professor of Electrical Engineering, Graduate Officer                       |

## System-Level Performance Evaluation of Three-Dimensional Integrated Circuits

by

#### Arifur Rahman

Submitted to the Department of Electrical Engineering and Computer Science on January 12, 2001, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

As the critical dimensions in VLSI design continue to shrink, system performance of integrated circuits (ICs) will be increasingly dominated by interconnect delay [1]. For the technology generations approaching 50 nm and beyond, innovative system architectures and interconnect technologies will be required to meet the projected system performance [2]. Interconnect material solutions such as copper and low-k inter-level dielectric (ILD) offer only a limited improvement in system performance. Significant and scalable solutions to the interconnect delay problem will require fundamental changes in system design, architecture, and fabrication technologies.

Three-dimensional (3-D) ICs can alleviate interconnect delay problems by offering flexibility in system design, placement and routing. They (3-D ICs) can be formed by vertical integration of multiple device layers using wafer bonding, recrystallization, or selective epitaxial growth. The flexibility to place devices along the vertical dimension allows higher device density and smaller form factor in 3-D ICs. The critical signal path that may limit system performance can also be shortened to achieve faster clock speed. By 3-D integration, device layers fabricated with different front-end process technologies can be stacked along the 3<sup>rd</sup> dimension to form systems-on-a-chip [3]. In this thesis work, opportunities and challenges for 3-D integration of logic networks, microprocessors, and programmable logic have been explored based on system-level modeling and analysis. A stochastic wire-length distribution model has been derived to predict interconnection complexity in 3-D ICs. As more device layers are integrated, the 3-D wire-length distribution becomes narrower compared to that of 2-D ICs, resulting in a significant reduction in the number and length of semi-global and global wires. In 3-D ICs with 2-4 device layers, 30% - 50% reduction in wire-length can be achieved. Besides performance modeling, thermal analysis has also been performed to assess power dissipation and heat removal issues in 3-D ICs. The total capacitance associated with signal interconnects and clock networks can be reduced by 3-D integration, leading to lower power dissipation for system performance comparable to that of 2-D ICs. However, for higher system performance in 3-D ICs, power dissipation increases significantly, and it is likely that innovative cooling techniques will be needed for reliable operation of devices and interconnects.

Thesis Supervisor: Rafael Reif

Title: Associate Department Head and Professor of Electrical Engineering and Computer

Science

### Acknowledgments

I would like to thank my advisor, Prof. Rafael Reif, for providing support for this research project and creating a lively and stimulating atmosphere. His mentorship has been an inspiration to me. The brainstorming sessions with Dr. James Chung during the early stages of this project were integral to defining my thesis. I would also like to thank Prof. Anantha Chandrakasan and Dimitri Antoniadis for participating in my thesis committee and providing feedback at various stages of this research project. I would also like to thank Prof. Jeffry A. Davis at the Georgia Institute of Technology for helping me understand his wire-length distribution models as well as Andy Fan for keeping me up to date about his 3-D technology development work.

I have benefited both academically and socially by interacting with many people within MIT. The photography related experiments and discussions with Gabor Csanyi and Indranath Neogy, the fishing trips with Dr. Ilya Lyubomirsky, and the workout routines with Dr. Dennis Okumu Ouma were essential for relieving stress and enriching my experience at MIT. I would like to thank my colleagues in Reifgoup, Ritwik Chatterjee, Kuan-Neng Chen, Shamik Das, Andy Fan, Simon Karecki, Wendy Mao, Laura Pruette, and Minghao Qi for their company and making a pleasant work environment. Syed Alam and Andy Fan read some of the chapters of this thesis and provided useful feedback. Mathew Varghese helped me get started with ANSYS for thermal analysis. I would also like to thank Ihsan Djomehri, James Fiorenza, Dr. Abraham Kim, Dr. Huey Le, Vikas Mehrotra, Hasan Nayfeh, Debroah Hodges-Pabon, Tae Park, Tamba Tugbawa, and Dr. Andy Wei for making my stay at MTL enjoyable.

I am indebted to the support and encouragement I have received over the years from my wife, Oni, our parents, and family members. It would have been a tough journey without their love and affection.

This research project was funded by MARCO Focused Research Center for Interconnects under Task V, Materials and Processing.

## Contents

| 1 | Int  | roduction                                                                    | 21 |

|---|------|------------------------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                                   | 21 |

|   | 1.2  | Issues Associated with Long Wires                                            | 23 |

|   | 1.3  | Opportunities for Three-Dimensional Integration                              | 27 |

|   |      | 1.3.1 Approaches to Three-Dimensional Integration                            | 28 |

|   | 1.4  | System-Level Performance Evaluation of Integrated Circuits and Contribu-     |    |

|   |      | tion of Thesis Work                                                          | 33 |

| 2 | Bac  | ekground: System-Level Modeling                                              | 35 |

|   | 2.1  | Methodology and the Modeling Framework                                       | 36 |

|   | 2.2  | Models for System-Level Simulation                                           | 38 |

|   |      | 2.2.1 Gate Delay                                                             | 38 |

|   |      | 2.2.2 Interconnect Delay                                                     | 41 |

|   |      | 2.2.3 Cycle Time                                                             | 47 |

|   |      | 2.2.4 Stochastic Wire-Length Distribution of 2-D Integrated Circuits         | 48 |

|   |      | 2.2.5 Models for Estimating Chip Area                                        | 56 |

|   | 2.3  | Examples: Chip Area and Clock Frequency Estimation                           | 61 |

|   | 2.4  | Extension of System-Level Modeling to 3-D ICs                                | 62 |

| 3 | Sys  | tem-Level Performance Modeling of Three-Dimensional (3-D) Inte-              |    |

|   | grat | ted Circuits (ICs)                                                           | 65 |

|   | 3.1  | Stochastic Wire-Length Distribution of Three-Dimensional Integrated Circuits | 66 |

|   |      | 3.1.1   | Approaches to Wire-Length Prediction in 3-D ICs                                  | 66           |

|---|------|---------|----------------------------------------------------------------------------------|--------------|

|   |      | 3.1.2   | Derivation                                                                       | 69           |

|   |      | 3.1.3   | ${\bf Intra-\ and\ Inter-Stratum\ Components\ of\ Wire-Length\ Distribution\ .}$ | 76           |

|   |      | 3.1.4   | Wiring Efficiency                                                                | 80           |

|   |      | 3.1.5   | Cost Function                                                                    | 80           |

|   | 3.2  | Exam    | ples: Chip Area and Clock Frequency Prediction                                   | 81           |

|   |      | 3.2.1   | Clock Frequency                                                                  | 81           |

|   |      | 3.2.2   | Chip Area                                                                        | 83           |

|   |      | 3.2.3   | Sandwich Interconnects                                                           | 84           |

|   | 3.3  | Summ    | nary                                                                             | 86           |

| 4 | Opp  | oortun  | ities for Three-Dimensional Implementation of Microprocessors                    | 89           |

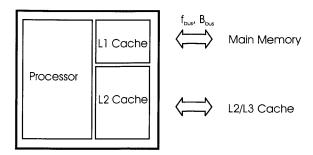

|   | 4.1  | Micro   | processor Model                                                                  | 91           |

|   |      | 4.1.1   | Cycles Per Instruction (CPI) and Throughput                                      | 91           |

|   |      | 4.1.2   | Logic-Memory Partitioning                                                        | 93           |

|   |      | 4.1.3   | Area Models                                                                      | 94           |

|   | 4.2  | Valida  | ation                                                                            | 95           |

|   | 4.3  | Chip    | Area and Interconnect Parameter Estimation of Microprocessors Im-                |              |

|   |      | pleme   | nted in Scaled Technologies                                                      | 96           |

|   | 4.4  | СРІ а   | nd Throughput Estimation                                                         | 102          |

|   | 4.5  | Summ    | nary                                                                             | 105          |

| 5 | Sto  | chastic | Routability Prediction and Three-Dimensional Integration o                       | $\mathbf{f}$ |

|   | Fiel | ld-Pro  | grammable Gate Arrays (FPGAs)                                                    | 107          |

|   | 5.1  | Introd  | luction                                                                          | 107          |

|   |      | 5.1.1   | Approaches to FPGA Design                                                        | 109          |

|   | 5.2  | SRAN    | M Based FPGA                                                                     | 110          |

|   | 5.3  | Stoch   | astic Models for Routability Prediction in FPGAs                                 | 114          |

|   |      | 5.3.1   | Calibration and Validation                                                       | 114          |

|   | 5.4  | Опро    | rtunities for 3-D Implementation of FPGAs                                        | 118          |

|   |      | 5.4.1          | Channel Density in 3-D FPGAs                              | 118 |

|---|------|----------------|-----------------------------------------------------------|-----|

|   |      | 5.4.2          | Logic Density                                             | 120 |

|   |      | 5.4.3          | Interconnect Delay                                        | 122 |

|   |      | 5.4.4          | Power Dissipation                                         | 125 |

|   | 5.5  | Summ           | ary                                                       | 129 |

| 6 | The  | ermal <i>i</i> | Analysis of Three-Dimensional Integrated Circuits         | 131 |

|   | 6.1  |                | uction                                                    | 131 |

|   | 6.2  |                | ation of Power Consumption in Microprocessors             | 133 |

|   | 0.2  | 6.2.1          |                                                           |     |

|   |      | 6.2.2          | Power Dissipation in Logic Gates                          | 135 |

|   |      |                | Power Dissipation in Clock Network                        | 136 |

|   |      | 6.2.3          | Power Dissipation in Interconnects                        | 139 |

|   |      | 6.2.4          | Power Dissipation in I/O Pads                             | 139 |

|   |      | 6.2.5          | Simulation Results: Estimation of Total Power Dissipation | 140 |

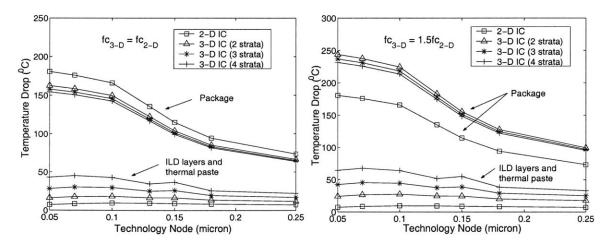

|   | 6.3  | Device         | e-Level Thermal Analysis                                  | 143 |

|   | 6.4  | Packag         | ge-Level Thermal Issues in 3-D IC                         | 147 |

|   |      | 6.4.1          | C4 Packaging Technology                                   | 148 |

|   |      | 6.4.2          | Estimation of Packaging Thermal Resistance                | 149 |

|   | 6.5  | Estima         | ation of Die Temperature                                  | 153 |

|   |      | 6.5.1          | Assumptions and Methodology                               | 154 |

|   |      | 6.5.2          | Simulation Results                                        | 154 |

|   | 6.6  | Summ           | ary                                                       | 156 |

| 7 | Con  | clusion        | n                                                         | 159 |

|   | 7.1  | Summ           | ary                                                       | 159 |

|   | 7.2  |                | • Work                                                    | 161 |

|   |      |                |                                                           | 101 |

| A | Fab  | ricatio        | n Process Flow of 3-D ICs Based on Wafer Bonding          | 163 |

| В | Stoc | chastic        | Net-Length Distribution of Global Interconnects in 3-D He | t-  |

|   | erog | geneous        | s System-on-a-Chip                                        | 167 |

| B.1 | Distrib | oution of Multi-Terminal Nets                |

|-----|---------|----------------------------------------------|

|     | B.1.1   | Heterogeneous Rent's Rule                    |

|     | B.1.2   | Multi-Terminal Nets                          |

|     | B.1.3   | Stochastic Placement and Routing Information |

| B.2 | Three-  | Dimensional Placement and Routing            |

## List of Figures

| 1-1 | (a) Three-dimensional IC with short and high-density vertical interconnec-          |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | tions between device layers. (b) Two-dimensional IC with high-speed on-chip         |    |

|     | optical buses for global signal distribution. (c) Clustered/tiled processing ar-    |    |

|     | chitecture with an array of processing elements (PEs)                               | 23 |

| 1-2 | Percentage of total number of wires and the corresponding contribution to           |    |

|     | total wire-length in a 2-D IC with ten million logic gates. Gate pitch is the       |    |

|     | unit for average separation between adjacent logic gates. Rent's constant           |    |

|     | and exponents are 4 and 2/3, respectively. Rent's Rule is given by $T=kN^p$ ,       |    |

|     | where N is the number of logic gates, k is Rent's constant, and p $(0 \le p \le 1)$ |    |

|     | is Rent's exponent                                                                  | 25 |

| 1-3 | The wire-length distribution in 2-D and 3-D implementation of logic circuits.       |    |

|     | Three-dimensional integration results in a narrower wire-length distribution        |    |

|     | with fewer and shorter semi-global and global wires and higher number of            |    |

|     | local wires.                                                                        | 27 |

| 1-4 | Illustration of various functional blocks in a future system-on-a-chip (SOC).       | 28 |

| 1-5 | Package-level 3-D integration by vertical stacking of multi-chip modules [28].      | 30 |

| 1-6 | Selective epitaxial growth of Si islands through seed windows for monolithic        |    |

|     | 3-D integration [44]                                                                | 30 |

| 1-7 | Cross section of a 3-D integrated circuit formed by face-to-back Cu-Cu wafer        |    |

|     | bonding                                                                             | 32 |

| 1-8 | Key definitions and terminologies for describing a generic 3-D IC                   | 33 |

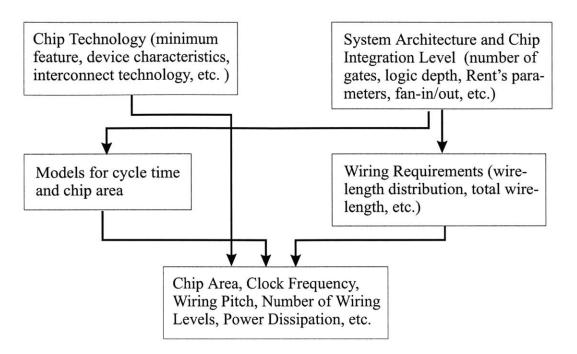

| 2-1  | A graphical illustration of the methodology which is the basis for system-level                                                              |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | simulation.                                                                                                                                  | 39 |

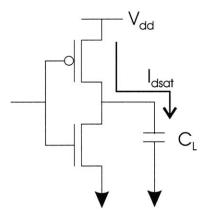

| 2-2  | Schematic of a CMOS inverter driving a capacitive load of capacitance, $C_L$                                                                 | 39 |

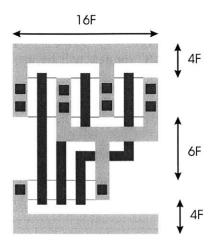

| 2-3  | Layout of a 3-input NAND gate gate. F is the minimum feature size                                                                            | 41 |

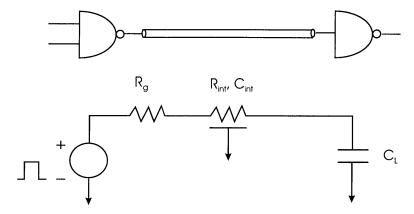

| 2-4  | RC circuit model of an interconnect driven by a logic gate. $R_g$ is the equiva-                                                             |    |

|      | lent gate capacitance, $R_{int}$ and $C_{int}$ are interconnect's resistance and capac-                                                      |    |

|      | itance, and $C_L$ is the load capacitance                                                                                                    | 42 |

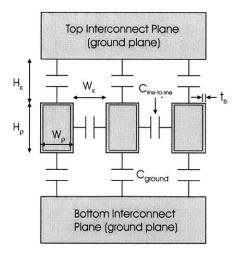

| 2-5  | Cross-section of interconnect lines and models for representing their equiva-                                                                |    |

|      | lent capacitance. $H_{\rho}$ and $W_{\rho}$ are the height and width of interconnect lines,                                                  |    |

|      | respectively; $H_{\epsilon}$ is the thickness of the ILD layer and $W_{\epsilon}$ is the spacing be-                                         |    |

|      | tween adjacent interconnect lines. $t_b$ is the thickness of the barrier material.                                                           | 43 |

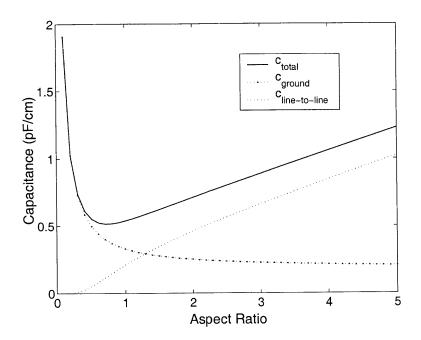

| 2-6  | Wiring capacitance as a function of interconnect's aspect ratio, $\gamma = H_{\rho}/W_{\rho}$ .                                              |    |

|      | It is assumed that $H_{\rho}=H_{\epsilon},W_{\rho}=W_{\epsilon},\mathrm{and}\epsilon=\epsilon_{o}\epsilon_{r}=\epsilon_{o}.$ When the aspect |    |

|      | ratio is more than one, total wiring capacitance increases linearly with aspect                                                              |    |

|      | ratio                                                                                                                                        | 45 |

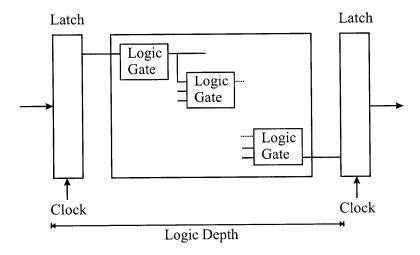

| 2-7  | The concept of logic depth in integrated circuits                                                                                            | 47 |

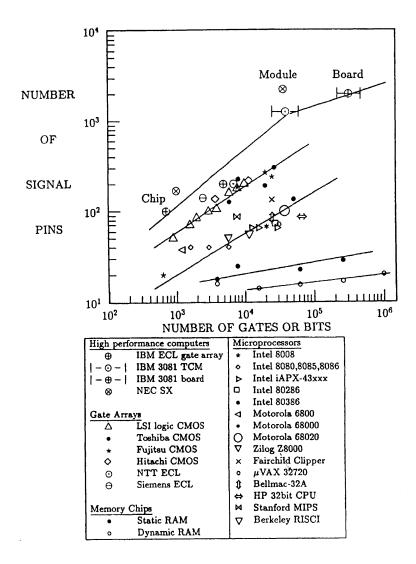

| 2-8  | Interconnection complexity in three circuits exhibiting Rent's exponent $p=0$                                                                |    |

|      | in (a), $0  in (b), and p = 1 in (c)$                                                                                                        | 50 |

| 2-9  | Correlation between the number of signal pins (I/O terminals) and the num-                                                                   |    |

|      | ber of logic gates for various digital systems [49]                                                                                          | 51 |

| 2-10 | The procedure for estimating the wire-length distribution in 2-D ICs                                                                         | 52 |

| 2-11 | A partial Manhattan circle partitioning strategy for estimating $N_a$ , $N_b$ , and                                                          |    |

|      | $N_c$ [17]                                                                                                                                   | 54 |

| 2-12 | Linear net model for converting point-to-point wire-length to net length                                                                     | 56 |

| 2-13 | Comparison of stochastic model and actual data of wire-length distribution                                                                   |    |

|      | for a microprocessor [17]                                                                                                                    | 56 |

| 2-14 | Illustration of reduction in wiring efficiency due to via blockage                                                                           | 58 |

| 2-15 | The average wiring efficiencies in global, semi-global, and local interconnect                                                               |    |

|      | tiers, represented by tier 3, 2, and 1 respectively                                                                                          | 59 |

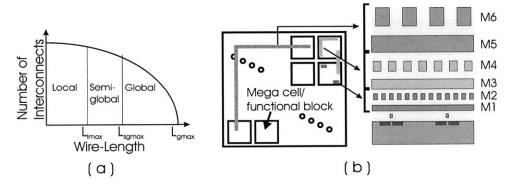

| 2-16 | (a) Partitioning of the wire-length distribution into local, semi-global, and                        |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | global regions. (b) Illustration of assigning interconnect levels based on wire                      |    |

|      | length                                                                                               | 60 |

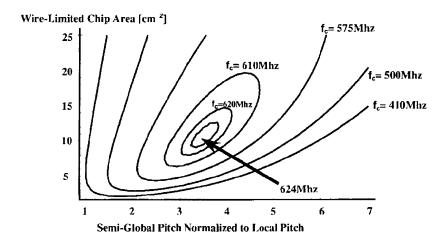

| 2-17 | Clock frequency, $f_c$ , versus chip area and semi-global wiring pitch of a wiring-                  |    |

|      | limited random logic network implemented in 0.18 $\mu m$ technology node [53].                       |    |

|      | Semi-global wiring pitch is varied to optimize the chip area or clock fre-                           |    |

|      | quency. The input parameters are consistent with device and interconnect                             |    |

|      | technologies listed in the SIA and ITRS roadmap [2, 7]                                               | 62 |

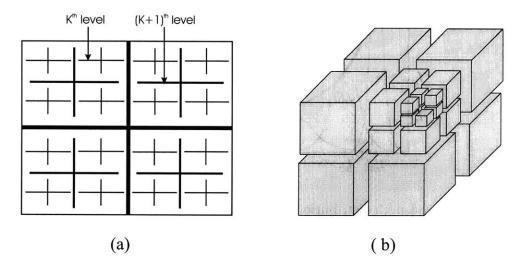

| 3-1  | Hierarchical partitioning on the placement locations for 2-D and 3-D ICs                             | 67 |

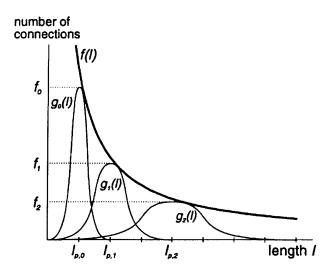

| 3-2  | The wire-length distribution based on hierarchical partitioning [70]. $g_0(l)$ ,                     |    |

|      | $g_1(l)$ , and $g_2(l)$ are the wire-length distribution of $0^{th}$ , $1^{st}$ , and $2^{nd}$ hier- |    |

|      | archical levels, respectively. The shorter wires generally belong to lower                           |    |

|      | hierarchical levels, whereas the longer wires belong to upper hierarchical levels.                   | 68 |

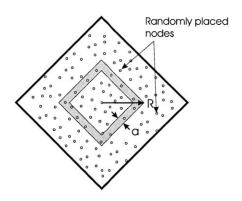

| 3-3  | The procedure for estimating wire-length distribution based on non-hierarchical $$                   |    |

|      | partitioning [77]. By applying Rent's rule, the number of interconnects be-                          |    |

|      | tween a node and a group on nodes within the band of radius $R$ and area                             |    |

|      | $\sim aR$ can be found. This process can be repeated for all possible values of                      |    |

|      | R to derive the complete wire-length distribution                                                    | 69 |

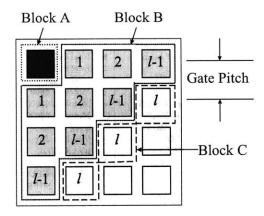

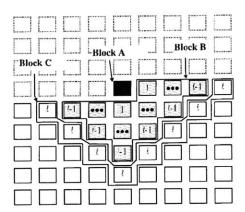

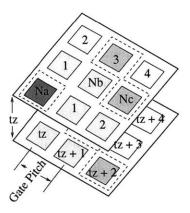

| 3-4  | The derivation of 3-D wire-length distribution: $N_a=1$ is the logic gate under                      |    |

|      | investigation, $N_c$ is the number of target logic gates at Manhattan distance                       |    |

|      | $l$ gate pitch, and $N_b$ is the number of logic gates in between $N_a$ and $N_c$                    | 70 |

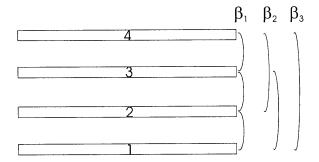

| 3-5  | Illustration of inter-stratum gate pair combinations for a 3-D IC with four                          |    |

|      | strata. For each combination there are two arrangements. As a result $\beta_1=6,$                    |    |

|      | $\beta_2 = 4$ , and $\beta_3 = 2$                                                                    | 71 |

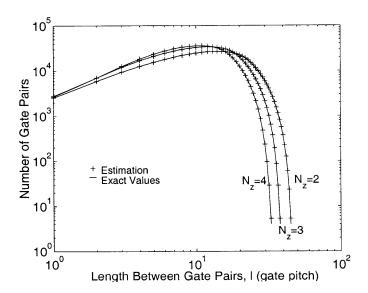

| 3-6  | Number of gate pairs, $M_{3D}(l,t_z)$ , vs. gate pair separation in 3-D ICs with                     |    |

|      | 1000 logic gates and 2, 3 and 4 strata. It is assumed that $t_z=1$                                   | 71 |

| 3-7  | Procedure for estimating the average values of $N_a,N_b,{\rm and}N_c$ in 3-D ICs                     | 72 |

| 3-8  | The wire-length distribution in 3-D ICs for negligible connectivity between                          |    |

|      | logic gates on different strata $(r_{upper} = r = 0)$                                                | 74 |

| 3-9  | The wire-length distribution of 3-D IC for $r_{upper} = N_z - 1$                                          | 74 |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 3-10 | The dotted region of the wire-length distribution of Fig. 3-9                                             | 75 |

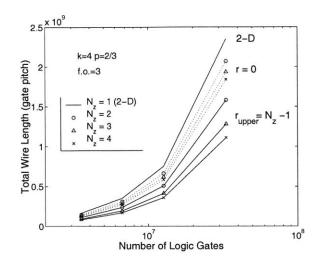

| 3-11 | The total wire-length in 2-D and 3-D ICs                                                                  | 76 |

| 3-12 | The average wire-length in 2-D and 3-D ICs                                                                | 76 |

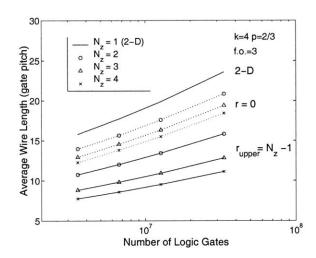

| 3-13 | The average wire-length in a 3-D integrated circuit with four device layers                               |    |

|      | for various upper bounds of $r$                                                                           | 77 |

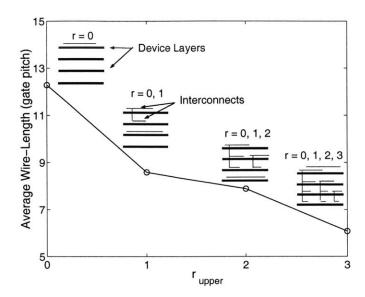

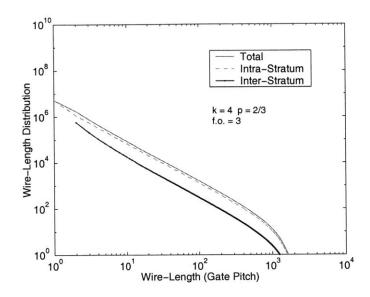

| 3-14 | The inter-, intra-stratum, and total wire-length distribution of a 3-D IC with                            |    |

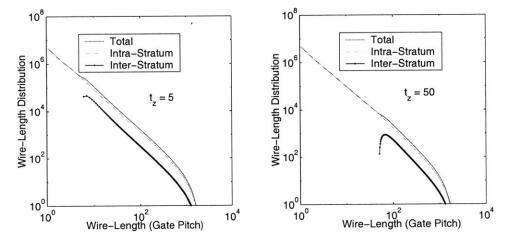

|      | 3.5 million logic gates. Number of strata $N_z=2$ and $t_z=1.$                                            | 78 |

| 3-15 | The inter-, intra-stratum, and total wire-length distribution of 3-D IC with                              |    |

|      | 3.5 million logic gates and two strata for $t_z = 5$ and $t_z = 50$ . Rent's param-                       |    |

|      | eters $k = 4$ , $p = 2/3$ and $\langle f.o. \rangle = 3$                                                  | 78 |

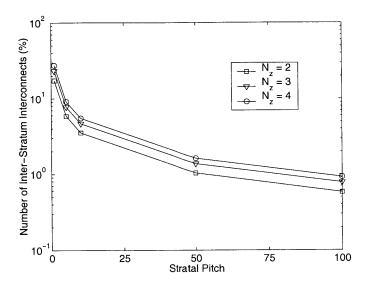

| 3-16 | The percentage of total number of interconnects due to inter-stratum compo-                               |    |

|      | nents vs. stratal pitch, $t_z$ . Rent's parameters $k = 4$ , $p = 2/3$ , and $\langle f.o. \rangle = 3$ . | 79 |

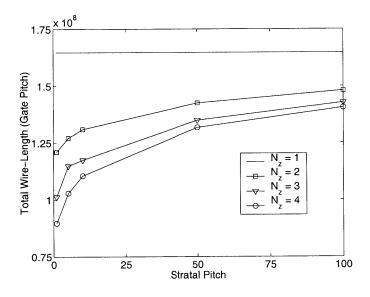

| 3-17 | The total wire-length of 2-D and 3-D ICs as a function of stratal pitch, $t_z$ .                          |    |

|      | Rent's parameters $k = 4$ , $p = 2/3$ and $\langle f.o. \rangle = 3$                                      | 79 |

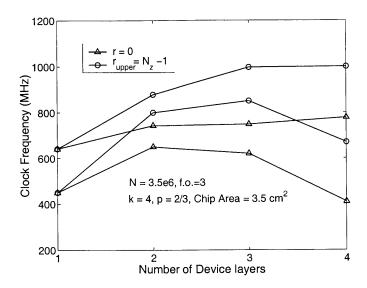

| 3-18 | The clock frequency of 2-D and 3-D ICs with 3.5 million logic gates and                                   |    |

|      | minimum feature size of 0.18 $\mu m$                                                                      | 83 |

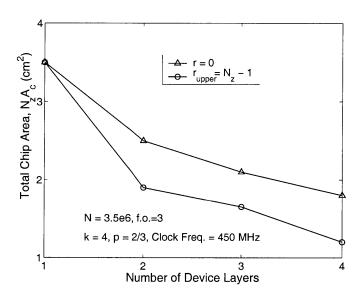

| 3-19 | The total Chip area, $N_z A_c$ , of 2-D and 3-D ICs for fixed clock frequency,                            |    |

|      | $f_c=450~MHz$ , and cost function, $c.f.\sim 6$ . The device-limited chip area is                         |    |

|      | .52 $cm^2$                                                                                                | 84 |

| 3-20 | Cross section of a hypothetical sandwich interconnect technology                                          | 85 |

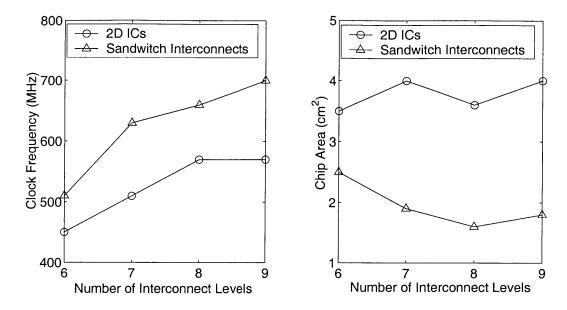

| 3-21 | The maximum clock frequency and the associated chip area of conventional                                  |    |

|      | and buried interconnect technologies                                                                      | 86 |

| 4-1  | A simplistic model of a conventional microprocessor                                                       | 90 |

| 4-2  | A H-tree clock distribution network                                                                       | 94 |

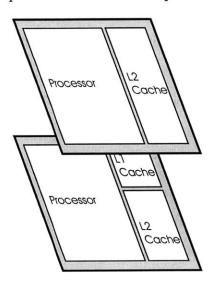

| 4-3  | A 3-D implementation of microprocessor                                                                    | 96 |

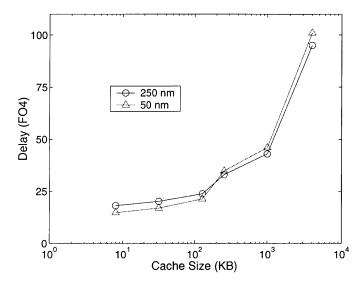

| 4-4  | Cache access time, in terms of FO4 inverted delay, as a function of cache size    |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | in two scaled technology nodes. For small cache size, access time increases       |     |

|      | as the $log$ of cache size [96]. For larger cache size, access time scales as the |     |

|      | cache size due to the dominance of interconnect delay [97]. It is assumed         |     |

|      | that global wiring pitch is 8F, where F is the minimum feature size               | 98  |

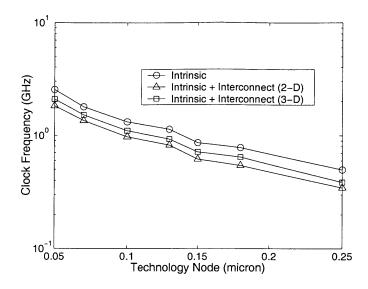

| 4-5  | The clock frequency in 2-D and 3-D implementation of microprocessors in           |     |

|      | scaled technology nodes. The critical path consists of 14 stages of 3-input       |     |

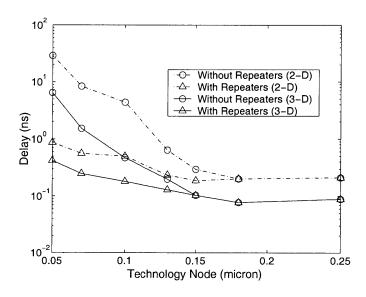

|      | NAND gates with fan-out of 3, and they are connected by average length wires.     | 100 |

| 4-6  | Interconnect delay of chip-edge length global wires with and without re-          |     |

|      | peaters in 2-D and 3-D implementation with 2 strata                               | 100 |

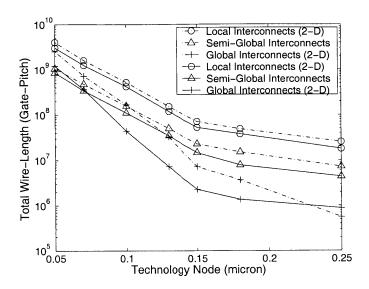

| 4-7  | Total wire-length of local, semi-global, and global interconnects in 2-D and      |     |

|      | 3-D implementation                                                                | 101 |

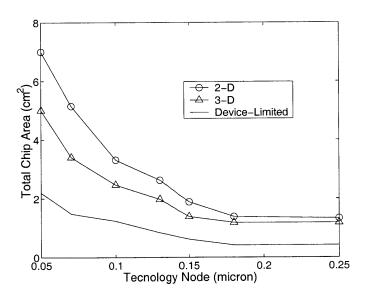

| 4-8  | Total chip area in 2-D and 3-D implementation. The device-limited chip area       |     |

|      | is estimated assuming minimum size transistors.                                   | 101 |

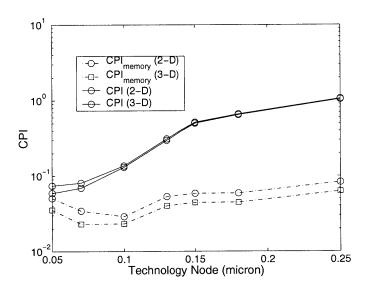

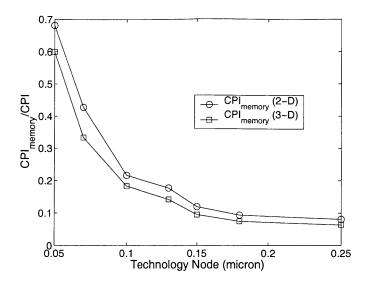

| 4-9  | $CPI$ and $CPI_{memory}$ in scaled technology nodes for 2-D and 3-D implemen-     |     |

|      | tation of microprocessors                                                         | 103 |

| 4-10 | The ratio of $CPI_{memory}$ and $CPI$ in scaled technology nodes                  | 104 |

| 4-11 | Throughput (BIPS) in 2-D and 3-D implementation of microprocessor                 | 104 |

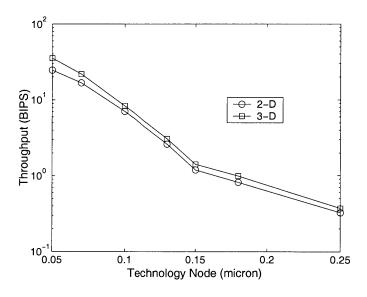

| 5-1  | Various approaches for implementing programmable interconnections in (a)          |     |

|      | SRAM-based (b) antifuse-based and (c) EPROM based FPGAs                           | 110 |

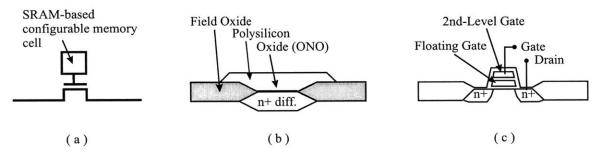

| 5-2  | A static memory-based FPGA                                                        | 110 |

| 5-3  | Programmable logic cells based on (a) look up tables and (b) configurable         |     |

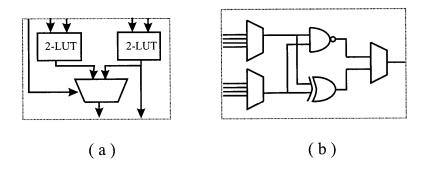

|      | logic gates in SRAM-based FPGA                                                    | 111 |

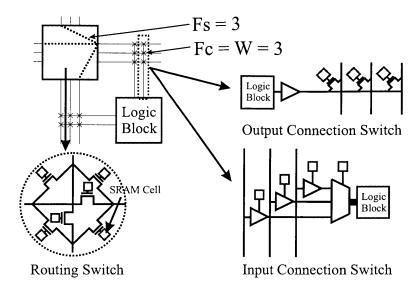

| 5-4  | Programmable routing and connection switches in SRAM-based FPGAs                  | 112 |

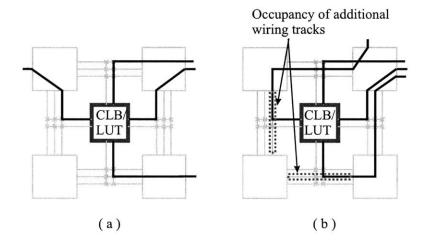

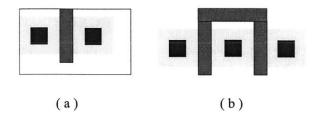

| 5-5  | (a) An ideal scenario where connections to input/output terminals of a LUT        |     |

|      | do not require additional wire-segments. (b) A non-ideal scenario that re-        |     |

|      | quires utilization of 2 additional wire segments for making input/output con-     |     |

|      | nections                                                                          | 115 |

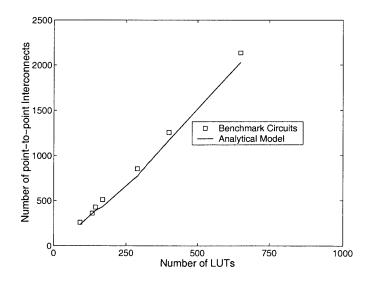

| 5-6  | LUT based FPGAs                                                                                                                                                                                                                                                                                                                              | 116 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

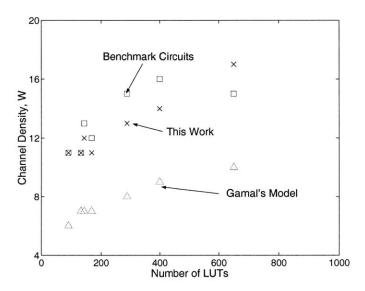

| 5-7  | Channel density for the benchmark circuits implemented in 4-input LUT                                                                                                                                                                                                                                                                        |     |

|      | based FPGAs                                                                                                                                                                                                                                                                                                                                  | 117 |

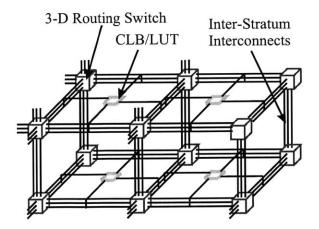

| 5-8  | A 3-D implementation of FPGAs with 3-D routing switches                                                                                                                                                                                                                                                                                      | 118 |

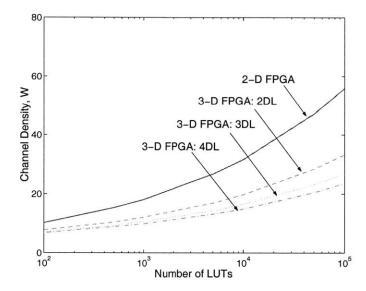

| 5-9  | Channel density in 2-D and 3-D 4-input LUT based FPGAs as a function of number of LUTs. The routing resource consists of one segment long wires. It has been assumed that Rent's parameters $k=5$ and $p=0.75$ , average fanout $=3.5$ , $\chi_{fpga}=0.95$ , and $e_t=0.4$ . In the figure, DL stands for number of device layers or strata | 119 |

| 5-10 | (a) A minimum-width transistor including the area needed to satisfy design rules. (b) A method to increase the drive strength of a transistor by folding                                                                                                                                                                                     | 101 |

|      | the polysilicon gate.                                                                                                                                                                                                                                                                                                                        | 121 |

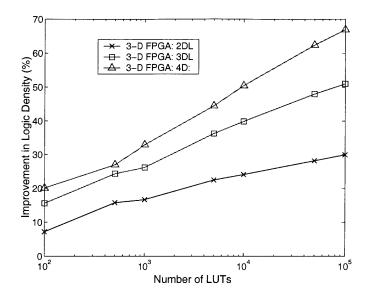

| 5-11 | Improvements in logic density as function of number of LUTs in 3-D FPGAs.                                                                                                                                                                                                                                                                    | 122 |

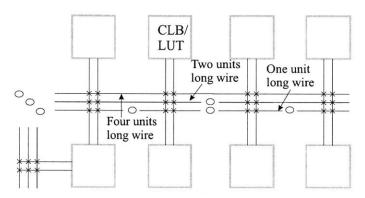

| 5-12 | Alternative routing choices using various length wire segments in SRAM-                                                                                                                                                                                                                                                                      |     |

|      | based FPGAs. Wire-length is measured in units of LUT pitch, the average separation between neighboring LUTs                                                                                                                                                                                                                                  | 123 |

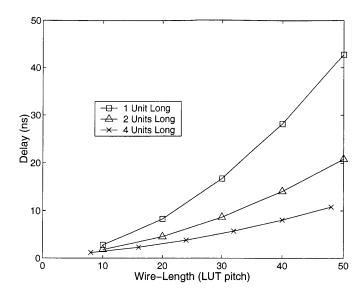

| 5-13 | Interconnect delay as a function of length for various wiring architecture implemented using 1, 2, and 4 unit long wire segments. The delay is roughly proportional to $n_{tr}^2$ , where $n_{tr}$ is the number of pass transistors in the interconnection path. LUT pitch is the separation between adjacent LUTs on the                   |     |

|      | same row or column                                                                                                                                                                                                                                                                                                                           | 124 |

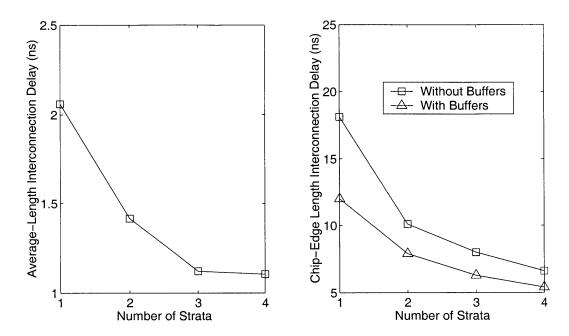

| 5-14 | Interconnect delay as a function of number of strata in 2-D and 3-D FPGAs.  The average-length wires are implemented by connecting one unit long wire segments, and the chip-edge length wires are implemented by connecting four 1/4 of chip-edge length wire segments                                                                      | 125 |

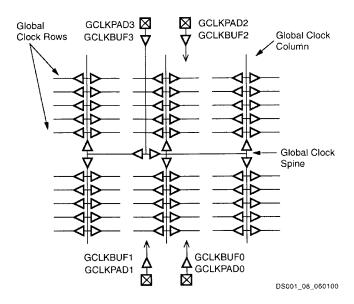

| 5-15 | A typical global clock distribution network in FPGAs [102]                                                                                                                                                                                                                                                                                   | 127 |

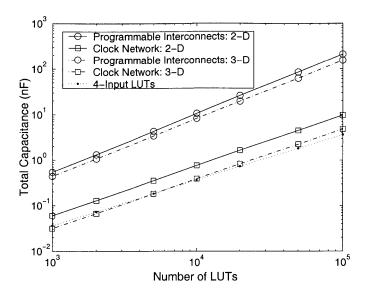

| 5-16 | Comparison of total capacitance associated with programmable intercon-             |     |

|------|------------------------------------------------------------------------------------|-----|

|      | nects, clock distribution network, and LUTs in 2-D and 3-D FPGAs with              |     |

|      | 2 strata and implemented in .25 $\mu m$ technology generation                      | 128 |

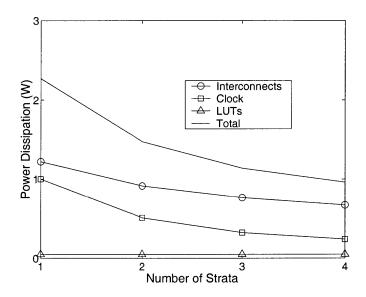

| 5-17 | Power dissipation in 2-D and 3-D FPGAs with 20K logic cells and imple-             |     |

|      | mented in .25 $\mu m$ technology node with 2.5 $V$ supply voltage and 100 $MHz$    |     |

|      | clock frequency                                                                    | 128 |

| 6-1  | Projected total power dissipation in microprocessors [7]                           | 133 |

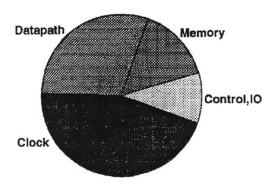

| 6-2  | Breakdown of power in a high-performance microprocessor [126]                      | 134 |

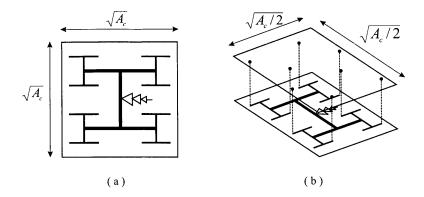

| 6-3  | H-tree clock network in (a) 2-D and (b) 3-D implementation of microproces-         |     |

|      | sors. The 3-D implementation consists of two strata and the clock network          |     |

|      | is located on the bottom stratum. Short inter-stratum vias are used to dis-        |     |

|      | tribute clock signals to the top stratum                                           | 137 |

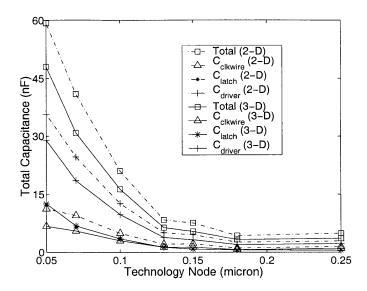

| 6-4  | The clock network capacitance in 2-D and 3-D implementation (with 2 strata)        |     |

|      | of microprocessors in scaled technology nodes                                      | 139 |

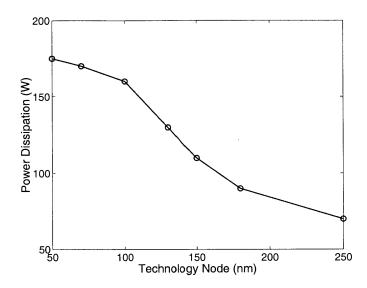

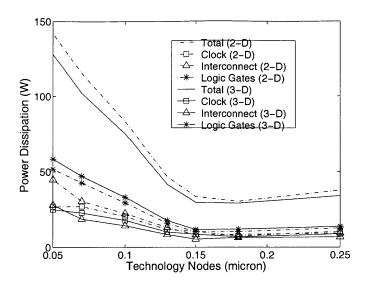

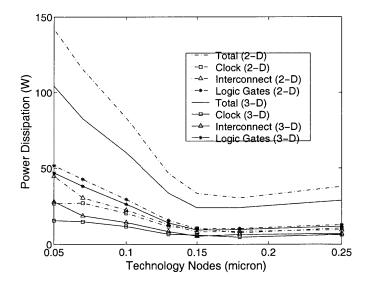

| 6-5  | The total power dissipation and various components of total power dissipa-         |     |

|      | tion in 2-D and 3-D implementation of microprocessors in scaled technology         |     |

|      | nodes                                                                              | 142 |

| 6-6  | The total power dissipation and various components of total power dissipa-         |     |

|      | tion in 2-D and 3-D implementation of microprocessors in scaled technology         |     |

|      | nodes. The 3-D integrated circuit is implemented using SOI technology. $$          | 142 |

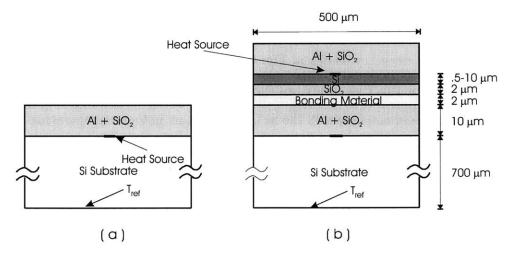

| 6-7  | Simplified cross section of (a) 2-D and (b) 3-D ICs with two strata for FEM        |     |

|      | based thermal analysis.                                                            | 143 |

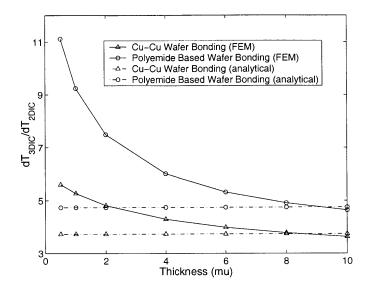

| 6-8  | Normalized temperature rise in top stratum for the geometry show in Fig. 6-        |     |

|      | 7 as a function of top stratum's Si thickness. $dT_{3DIC}$ and $dT_{2DIC}$ are the |     |

|      | maximum temperature rise in 2-D and 3-D ICs with respect to the reference          |     |

|      | temperature on the bottom most surface, $T_{ref}$ . The temperature rise based     |     |

|      | on analytical models is calculated by solving 1-D heat equation                    | 145 |

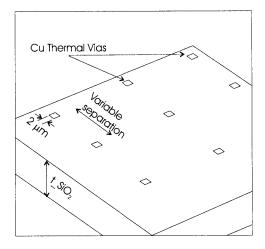

| 6-9  | A simplified geometry to assess the role of vias on heat removal                   | 145 |

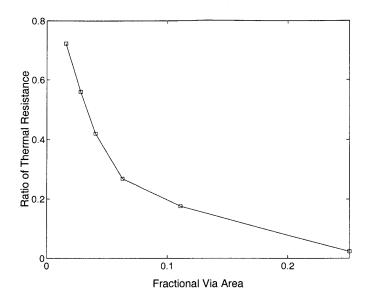

| 6-10 | The ratio of thermal resistance of a 10 $\mu m$ thick SiO <sub>2</sub> layer with and without          |      |

|------|--------------------------------------------------------------------------------------------------------|------|

|      | thermal vias as a function of fractional area occupied by thermal vias                                 | 146  |

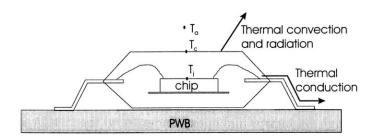

| 6-11 | A simplified heat transfer model of a packaged chip                                                    | 147  |

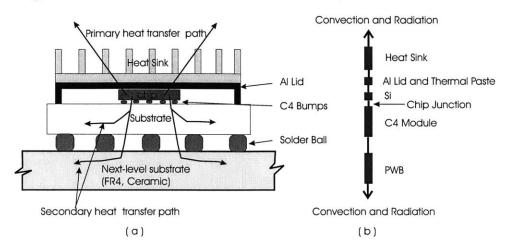

| 6-12 | (a) The cross section of a C4 package. (b) The thermal model of a C4 package                           | .149 |

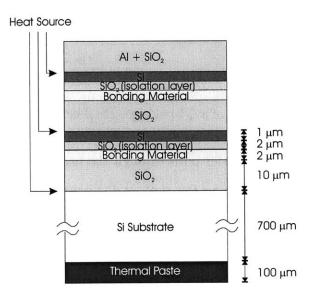

| 6-13 | Cross section of the geometry used for estimating $R_{jc}$ (not drawn to scale).                       | 150  |

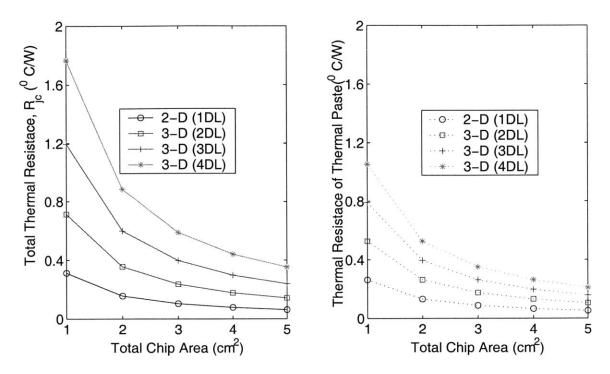

| 6-14 | Thermal resistance from junction to Al lid, $R_{jc}$ , and thermal resistance of the                   |      |

|      | thermal paste as a function of total chip area and number of strata (device                            |      |

|      | layers). DL stand for device layers.                                                                   | 151  |

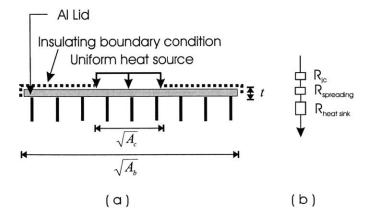

| 6-15 | (a) A simplified representation of Al lid and heat sink and (b) their thermal                          |      |

|      | models for estimating $R_{ca}$                                                                         | 151  |

| 6-16 | Spreading resistance, $R_{spreading}$ , of a typical heat sink for high-performance                    |      |

|      | systems such as microprocessors as a function of $\sqrt{\frac{A_c}{A_b}}$ and the thickness of         |      |

|      | the Al lid. The base area of the heat sink $A_b = 5 \times 5$ cm <sup>2</sup> , and $R_{heat\ sink} =$ |      |

|      | 1 ${}^{0}C/W$                                                                                          | 153  |

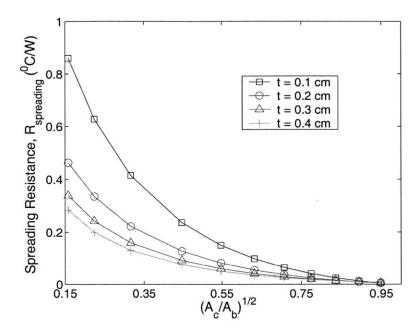

| 6-17 | The temperature drop with the ILD layers and thermal paste and the pack-                               |      |

|      | age in 2-D and 3-D implementation of ICs. $fc_{2-D}$ and $fc_{3-D}$ are the clock                      |      |

|      | frequency of 2-D and 3-D ICs. It has been assumed that the thermal resis-                              |      |

|      | tance of the heat sink is 1 ${}^{0}C/W$ , and Cu-based bonding technology has been                     |      |

|      | used                                                                                                   | 155  |

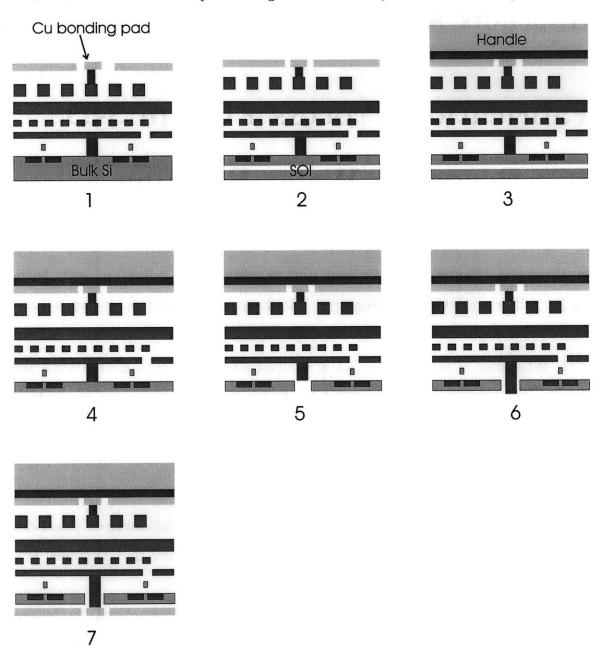

| A-1  | The process flow for fabricating 3-D ICs                                                               | 164  |

| A-2  | The process flow for fabricating 3-D ICs                                                               | 165  |

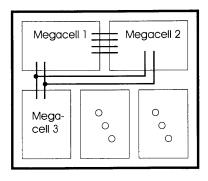

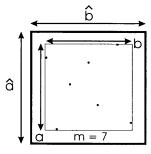

| B-1  | Multi-terminal nets in a SOC                                                                           | 168  |

| B-2  | The bounding are of terminals in a multi-terminal net                                                  | 169  |

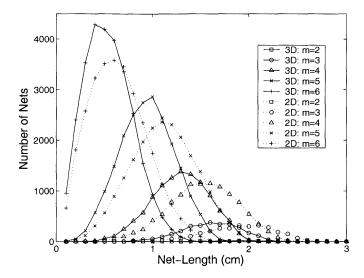

| B-3  | The stochastic wire-length distribution of $m$ -terminal nets in 2-D and 3-D                           |      |

|      | implementation of SOC                                                                                  | 171  |

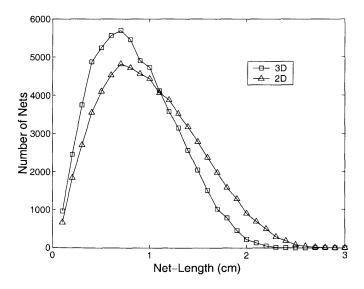

| B-4  | The stochastic global (inter-megacell) wire-length distribution in 2-D and                             |      |

|      | 3-D implementation of SOC                                                                              | 171  |

## List of Tables

| 1.1 | Projected system performance and interconnect parameters for scaled CMOS                      |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | technologies in high-performance microprocessors [2, 7]                                       | 24 |

| 1.2 | Comparison of device and interconnect delay in scaled technology nodes.                       |    |

|     | The parameters used to estimate delay are consistent with the projections                     |    |

|     | in semiconductor technology roadmap [2, 7]. The FO4 inverter delay (in                        |    |

|     | picosecond) is estimated using the heuristic, $\tau_{FO4} = 360 \cdot L_{drawn}$ , where      |    |

|     | $L_{drawn}$ is the drawn channel length in $\mu m$ [18]. $F$ is the minimum feature           |    |

|     | size. A clock cycle is approximated by 16FO4 delay [18]                                       | 25 |

| 2.1 | A complete list of equations used for estimating the key performance metrics                  |    |

|     | of CMOS microprocessor in SUSPENS [49]                                                        | 37 |

| 2.2 | Definition of variables for conservation of I/O terminals                                     | 53 |

| 3.1 | Simulation results of system-level modeling and analysis of 2-D random net-                   |    |

|     | works. $m_l$ , $m_{sg}$ , and $m_g$ are the number of local, semi-global, and global          |    |

|     | interconnect levels, respectively, and $p_l$ , $p_{sg}$ , and $p_g$ are their wiring pitches. |    |

|     | $\beta_g$ is the fractional delay of the chip-edge length wire compared to clock delay.       | 82 |

| 3.2 | Simulation results of system-level modeling and analysis of 3-D ICs for two                   |    |

|     | limiting cases of connectivity governed by the maximum value of range, $r$ .                  |    |

|     | $m_l, m_{sg}$ , and $m_g$ are the number of local, semi-global, and global interconnect       |    |

|     | levels, respectively, and $p_l$ , $p_{sg}$ , and $p_g$ are their wiring pitches               | 83 |

| 3.3 | Simulation results of interconnect parameters for system-level modeling and          |     |

|-----|--------------------------------------------------------------------------------------|-----|

|     | analysis of sandwich interconnect technology. $m_l, m_{sg}$ , and $m_g$ are the num- |     |

|     | ber of local, semi-global, and global interconnect levels, respectively, and $p_l$ , |     |

|     | $p_{sg}$ , and $p_g$ are their wiring pitches                                        | 86  |

| 4.1 | Extracted empirical parameters for projecting microprocessor's performance           |     |

|     | [50]                                                                                 | 92  |

| 4.2 | Comparison of published and projected system performance and interconnect            |     |

|     | parameters for Alpha 21164 (3.3 $V$ .5 $\mu m$ ) microprocessor [93]. It is assumed  |     |

|     | that $W/L$ ratio in the critical path is 30 and logic depth is 14, Rent's param-     |     |

|     | eters $k=4,p=.6,$ average fan-out is 3, and I/O pad area is $\sim 10\%$ of chip      |     |

|     | area                                                                                 | 95  |

| 4.3 | Comparison of published and projected system performance and interconnect            |     |

|     | parameters for Pentium $(3.3V~.35\mu m)$ microprocessor [94, 95]. It is assumed      |     |

|     | that $W/L$ ratio in the critical path is 30 and logic depth is 27, Rent's param-     |     |

|     | eters $k=4,p=.6,$ average fan-out is 3, and I/O pad area is $\sim 10\%$ of chip      |     |

|     | area                                                                                 | 96  |

| 4.4 | Metal resistivity, dielectric constant, and interconnect parameters in scaled        |     |

|     | technology nodes for microprocessors [7]                                             | 97  |

| 4.5 | The number of logic gates in the processor core and cache memory size for            |     |

|     | optimum system performance. In 250 nm and 180 nm technology nodes, L2                |     |

|     | cache is implemented off-chip and beyond 180 nm technology node, both L1             |     |

|     | and L2 cache are implemented on-chip. FO4 delay stands for fan-out of 4              |     |

|     | inverter delay, and for first order calculation, 16FO4 inverter delay can be         |     |

|     | used as a measure of cycle time [18]                                                 | 97  |

| 4.6 | Number of interconnect levels and wiring pitch for 2-D and 3-D implemen-             |     |

|     | tation of microprocessors.                                                           | 99  |

| 4.7 | Assumptions on memory access time, bus frequency, etc. based on empirical            |     |

|     | observation and projections from the SIA roadmap [7]                                 | 103 |

| 5.1 | Benchmark circuits for validating stochastic routing models                | 116 |

|-----|----------------------------------------------------------------------------|-----|

| 5.2 | Models for chip area dedicated to various components that make up SRAM-    |     |

|     | based FPGAs                                                                | 121 |

| 6.1 | The thermal conductivity of commonly used materials in ICs                 | 144 |

| 6.2 | Thermal conductivity of commonly used materials in micro electronic pack-  |     |

|     | aging                                                                      | 150 |

| 6.3 | Input parameters for estimating chip temperature [7, 140]                  | 155 |

| В.1 | The assumed Rent's parameters and the estimated chip area of the megacells |     |

|     | under consideration                                                        | 170 |

## Chapter 1

## Introduction

#### 1.1 Motivation

Over the last two decades, the historical progression of semiconductor industry can be attributed to cost per performance reduction due to transistor scaling and better manufacturing capabilities and the growing demand for integrated circuits (ICs) in consumer and industrial applications [4, 5]. High performance microprocessors, application specific integrated circuits (ASICs), and static or dynamic random access memories (SRAMs or DRAMs) continue to rely on transistor and interconnect scaling to meet density and performance targets. Though transistor scaling improves both speed and density, interconnect scaling improves density at the expense of degraded interconnect delay [1]. In older technology generations, interconnect delay represented a small fraction of the cycle time and did not have any significant impact on overall chip performance. However, in today's and future high-performance ICs, interconnect delay will have a significant impact on overall system performance [1].

To meet the wiring density requirement, interconnect's pitch is reduced and the number of interconnect levels is increased in successive technology generations. Interconnect's aspect ratio is often increased to reduce the wiring resistance. Though increasing the aspect ratio of interconnects leads to smaller resistance per unit length, it also results in higher coupling capacitance to neighboring interconnect lines on the same wiring level. In the current

technology generation, 60% - 80% of total wiring capacitance is due to lateral coupling capacitance. If the lateral coupling capacitance is too large, it may cause serious signal integrity problems [6]. In an ideal situation, if the wire-length is scaled down by the same factor as the wiring cross-section and pitch, the RC delay of a scaled interconnect would remain the same. However, this is not the case. With higher number of transistors per chip, the wiring complexity of an IC is expected to increase, leading to an increase in wire-length and chip area [2, 7]. In successive technology generations, it is also necessary to reduce interconnect delay so that overall system performance can be enhanced.

Al and  $SiO_2$  have been the materials of choice for multi-level metallization for many years. However, due to deteriorating performance of scaled interconnect lines in current and future technology generations, interconnect solutions based on low resistivity metal such as Cu and low-k inter-level dielectric (ILD) will be needed. Technology solutions based on Cu and low-k ILD are expected to extend interconnect scaling several technology generations. However, there is a limit to how low the dielectric constant of a realizable ILD material can be. In 35 nm technology node, it is expected that the effective dielectric constant of an ILD layer would be in the range of 1-1.5 [2]. Also, there is no alternative to Cu, as an interconnect metal layer, in sight yet. In the recent international technology roadmaps for semiconductors (ITRS) it has been suggested that beyond Cu and low-k, interconnect solutions based on innovative technology and/or system architecture will be required to meet the projected system performance requirements [2, 7]. Some of these potential solutions are [2, 7, 8, 9]:

- Three-dimensional integration

- On-chip or off-chip optical/RF interconnects

- System architectures exploiting communication locality

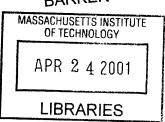

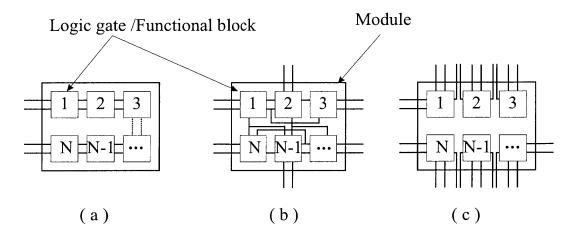

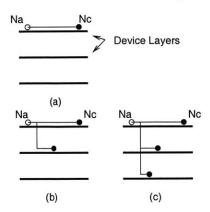

A graphical illustration of these technology- and system architecture-based solutions are provided in Fig. 1-1. Three-dimensional integration is expected to provide several key advantages such as higher packing density, high-speed operation, and integration of mixed technologies [10, 11]. Three-dimensional IC has the potential to alleviate future interconnect delay problems by offering flexibility in system design, placement, and routing.

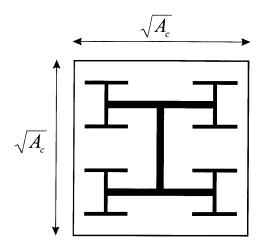

Figure 1-1: (a) Three-dimensional IC with short and high-density vertical interconnections between device layers. (b) Two-dimensional IC with high-speed on-chip optical buses for global signal distribution. (c) Clustered/tiled processing architecture with an array of processing elements (PEs).

Optical and RF interconnects are attractive for high-speed chip-to-chip communications [9, 12]. However, there is also interest in RF and optical interconnect technologies for on-chip clock and global signal distribution [9]. One of the benefits of optical interconnect is that it is essentially free from crosstalk, and power dissipation in global optical interconnect is much smaller compared to its electrical counterpart [9].

System architectures that exploit communication locality usually take advantage of tiled/clustered processing architecture [13]. Each cluster or processing element (PE) consists of an ALU and local registers. Computational tasks are mapped onto an array of distributed processing elements to minimize the need for frequent across-chip communication [13, 14]. When global communication is required, shared packet networks rather than dedicated wires can be used to make more efficient use of on-chip communication resource [13]. Though these competing solutions are quite different from each other, they are all targeted to minimize the impact of interconnect delay, cross-talk, etc. on overall system performance.

### 1.2 Issues Associated with Long Wires

Some of the commonly encountered interconnect related issues such as routability, delay, signal integrity, etc. are generally associated with semi-global and global wires [15, 16]. Though there are fewer long wires in an IC compared to short wires, they (long wires) take

| Technology Node (nm)                               | 180   | 150     | 130     | 100     | 70     | 50     | 35                     |

|----------------------------------------------------|-------|---------|---------|---------|--------|--------|------------------------|

| Microprocessor<br>Transistors/Chip<br>(Million)    | 23.8  | 47.6    | 95.2    | 190     | 539    | 1,523  | 4,308                  |

| Local clock frequency (MHz)                        | 1,250 | 1,767   | 2,100   | 3,500   | 6,000  | 10,000 | 13,500                 |

| Across-chip clock frequency (MHz)                  | 1,200 | 1,454   | 1,600   | 2,000   | 2,500  | 3,000  | 3,600                  |

| Number of Metal Levels                             | 6-7   | 7       | 7-8     | 8-9     | 9      | 9-10   | 10                     |

| Effective Resistivity (μΩ-cm) Cu Wiring            | 2.2   | 2.2     | 2.2     | 2.2     | 1.8    | <1.8   | <1.8                   |

| Inter Level Effective Dielectric<br>Constant       | 3.5-4 | 2.7-3.5 | 2.7-3.5 | 1.6-2.2 | 1.5    | <1.5   | <1.5                   |

| Maximum Interconnect Length (meters/chip) (SIA 97) | 1,480 | 2,160   | 2,840   | 5,140   | 10,000 | 24,000 | 60,000<br>(projection) |

(ITRS 99)

Solutions Being Pursued No Known Solution

Table 1.1: Projected system performance and interconnect parameters for scaled CMOS technologies in high-performance microprocessors [2, 7].

up a significant fraction of the wiring tracks or routable area. Design methodologies for signal integrity, repeater insertion, etc. are also dictated by the performance requirements of long wires.

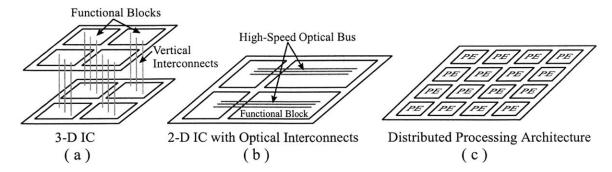

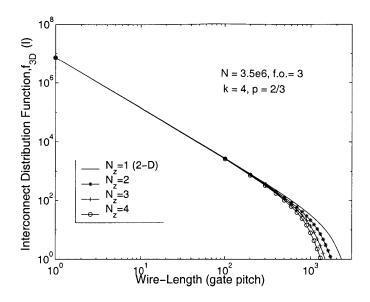

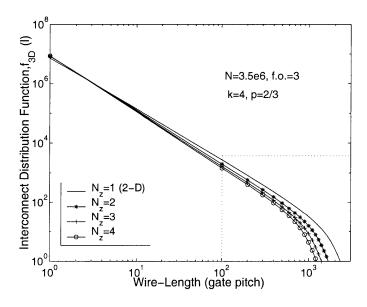

It is expected that total on-chip wire-length in microprocessors will increase from 820 m/chip in 250 nm technology node to 24000 m/chip in 50 nm technology node [2, 7] (see Table 1.2). This phenomenal increase in total wire-length is due to higher wiring requirements for a 1000× increase in the number of transistors per chip. Taking into account higher number of available interconnect levels in 50 nm technology node and the reduction in wiring pitch, complete wireability would require roughly a 4× increase in chip area. By examining the stochastic wire-length distribution of an IC, we find that typically the number of semi-global and global interconnects are much smaller than short or local interconnects [17]. However, the contribution of long wires to total wire-length is much higher than that of short wires. For example, as shown in Fig. 1-2, 20% of total number of wires contribute to 90% of total wiring need. Due to the significant contribution of long wires to total wire-length, the wiring-limited chip area, number of interconnect levels, etc. are

Figure 1-2: Percentage of total number of wires and the corresponding contribution to total wire-length in a 2-D IC with ten million logic gates. Gate pitch is the unit for average separation between adjacent logic gates. Rent's constant and exponents are 4 and 2/3, respectively. Rent's Rule is given by  $T = kN^p$ , where N is the number of logic gates, k is Rent's constant, and p (0  $\leq p \leq 1$ ) is Rent's exponent.

| Technology Node (nm)             | 500 | 180  | 100  | 70   | 50   | 35   |

|----------------------------------|-----|------|------|------|------|------|

| Chip-Edge Wire-Length (mm)       | 12  | 18.4 | 20.2 | 21.6 | 23.1 | 24.7 |

| Width: 4F Pitch: 8F              |     |      |      |      |      |      |

| Chip-Edge Length Wire Delay (ns) | .28 | 1.7  | 4.1  | 4.9  | 10.8 | 24.9 |

| FO4 Inverter Delay (ps)          | 180 | 64   | 36   | 25.2 | 18   | 12.6 |

| Chip-Edge Length Wire Delay      |     |      |      |      |      |      |

| (number of clock cycles)         | .1  | 1.7  | 7.2  | 12.2 | 37.6 | 123  |

Table 1.2: Comparison of device and interconnect delay in scaled technology nodes. The parameters used to estimate delay are consistent with the projections in semiconductor technology roadmap [2, 7]. The FO4 inverter delay (in picosecond) is estimated using the heuristic,  $\tau_{FO4} = 360 \cdot L_{drawn}$ , where  $L_{drawn}$  is the drawn channel length in  $\mu m$  [18]. F is the minimum feature size. A clock cycle is approximated by 16FO4 delay [18].

generally determined by the long wiring need of an IC. It is expected that total on-chip wire-length in a microprocessor will be 60 Km/chip in 35 nm technology node, creating a tremendous pressure on interconnect design, routability, and physical implementation (see Table 1.2).

Besides routability constraints for intermediate and long wires, their RC delay is also expected to increase in scaled technology nodes. Solutions based on reversed scaling of interconnects such that long wires have "fat" cross-sectional dimensions may enhance their performance but at the expense of lower wiring density and larger chip area. In Table 1.2, RC delay of chip-edge length global wires and intrinsic device delay for microprocessors, implemented in scaled technology nodes, are shown. For a first order calculation, 16-20 stages of FO4 (fan-out of 4) inverter delay can be used as a model for cycle time [18]. From Table 1.2, in scaled technology nodes, the number of clock cycles required to send signals across chip in non-repeated global lines will increase significantly which can have serious implications on overall system performance. To reduce long wire delay, repeaters have to be inserted every  $1 \ mm - 2 \ mm$  in high-performance circuits [13]. However, this measure leads to an increase in chip area and power dissipation. Due to insertion of repeaters on global wires, the increase in chip area can be as much as 20% for microprocessors beyond 100 nm technology nodes [19]. Even with repeater insertion, the number of clock cycles required to send signals across-chip will increase in scaled technology generations, and interconnect delay of long wires will have a significant impact on overall system performance.

Signal integrity issues in interconnect lines due to coupled noise from neighboring lines have a strong dependency on interconnect's length, and generally, semi-global and global wires are more susceptible to coupling noise [20]. To reduce the coupling noise, separation between adjacent interconnect lines on the same wiring plane have to be increased and/or repeaters have to be inserted. However, both of these measures increase the wiring-limited chip area.

Some of the design issues associated with long wires can be resolved at the expense of larger chip area, higher power dissipation or by increasing the number of interconnect levels. An alternative approach to resolve the long wire problems is by taking advantage of 3-D integration technology which will allow higher packing density and shorter interconnect length compared to conventional 2-D integration [11]. As a result, significant reduction in interconnect delay and chip area can be achieved in wiring-limited ICs.

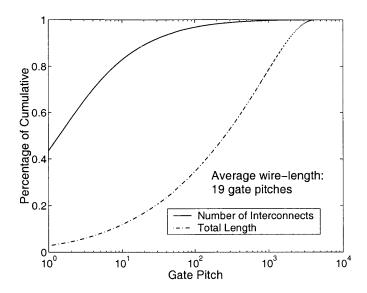

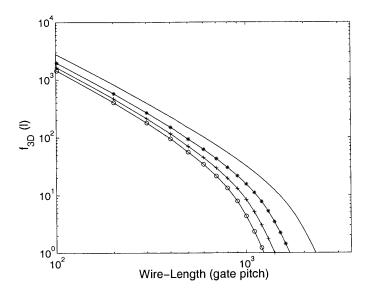

Figure 1-3: The wire-length distribution in 2-D and 3-D implementation of logic circuits. Three-dimensional integration results in a narrower wire-length distribution with fewer and shorter semi-global and global wires and higher number of local wires.

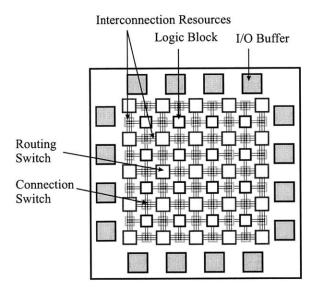

### 1.3 Opportunities for Three-Dimensional Integration

In the previous section, some of the commonly encountered design challenges associated with long wires have been discussed. Three-dimensional ICs are expected to reduce the semi-global and global wiring requirements significantly, therefore, allowing higher packing density in wiring-limited ICs and smaller interconnect delay [10, 11]. To illustrate the advantages of 3-D integration, in Fig. 1-3 the projected wire-length distribution of 2-D and 3-D logic circuits is shown. By mapping a 2-D IC in 3-D, the number and length of long wires can be reduced significantly at the expense of higher number of short wires. As a result of narrower wire-length distribution in 3-D integration, total and average wire-length will also become shorter, leading to smaller wiring-limited chip area and higher system performance. Three-dimensional integration can also result in a significant reduction in the number of repeaters for intermediate and long wires [21]. Based on system-level modeling and analysis work that will be presented in this thesis, we find that significant improvements in system performance and packing density are achievable by 3-D integration in applications such as high-performance logic, microprocessors, programmable devices, etc.

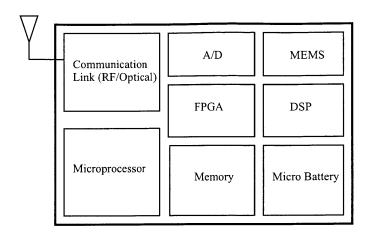

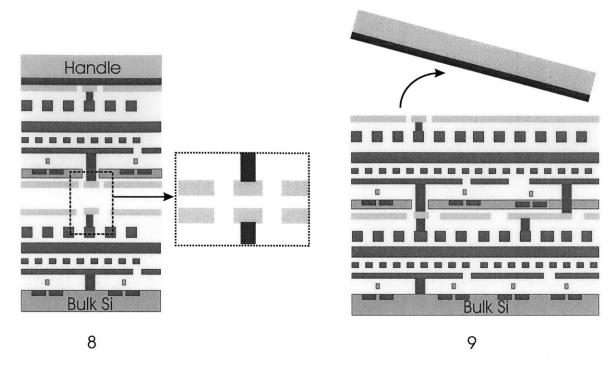

It is expected that future system-on-a-chip (SOC), as shown in Fig. 1-4, would require integration of digital, analog, and communication functionalities [22]. For portable applications, it will be desirable to have a small form factor for such systems. One of the challenges for implementing such SOC is the difficulty for monolithic integration of functional blocks

Figure 1-4: Illustration of various functional blocks in a future system-on-a-chip (SOC).

that would require different process technologies. For conventional (2-D) monolithic implementation, it would be difficult to optimize the CMOS process technology for all functional blocks. An alternative approach would be package-level integration of various components that are fabricated with optimized process technologies at the expense of higher cost and lower bandwidth (due to I/O limitation for off-chip communication) between functional blocks. Three-dimensional integration can alleviate these difficulties associated with both package-level and 2-D monolithic implementation of SOC. In 3-D integration a functional block or groups of functional blocks can be fabricated in different wafers using optimized process technologies and then integrated vertically to form SOC. To take advantage of the high bandwidth interconnection paths between device layers in 3-D integration, it may also be necessary to make innovative changes in the system architecture.

#### 1.3.1 Approaches to Three-Dimensional Integration

The concept of 3-D integration was demonstrated as early as in 1979 [23]. Though there have been significant research efforts in developing 3-D integration technologies in late 80's [10, 24, 25, 26, 27], commercialization of these technologies never materialized. Technology solutions by scaling the feature size to reduce cost per performance were simply too attractive compared available 3-D integration technologies. Also, the performance of ICs was device-limited, and there was no urgent need for technologies targeted towards reducing interconnect's RC delay. However, with the growing importance of interconnect

delay, it is now necessary to explore both near- and long-term interconnect solutions. It is speculated that beyond Cu and low-k, 3-D integration technologies can play a pivotal role in reducing interconnect delay and enabling monolithic integration of mixed technologies for SOC applications.

Approaches to 3-D integration can be classified by the following enabling technologies:

- Package-Level Integration

- Thin Film Technology (epitaxial growth, re-crystallization, etc.)

- Wafer Bonding

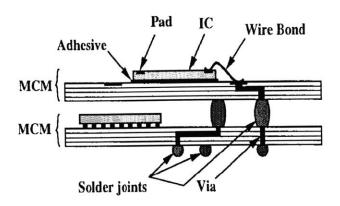

There are various package-level technologies for 3-D integration. In [28, 29] reviews of various packaging approaches to 3-D integration have been provided. In package-level 3-D integration, bare dies or packaged chips are stacked vertically, as shown in Fig. 1-5, and interconnections between them are formed at the chip periphery. Using package-level integration techniques, dense memory modules can be fabricated [30, 31, 32, 33]. Area interconnections formed by through-wafer vias or solder balls in the case of face-to-face bonding can also be used to provide vertical interconnections between stacked multi-chip modules (MCMs). Utilizing the area interconnection technology, vertical integration of ASICs and memory, signal processing circuits, and microprocessors have been implemented [34, 35, 36, 37, 38, 39]. The drawback in package-level 3-D integration technology is the lower density of vertical (inter-device layer) interconnects compared to monolithic 3-D integration. Some or the area interconnect technologies for wafer scale integration (WSI) also have very poor yield [35, 36].

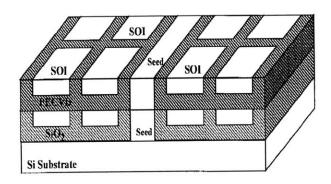

Presently, there are several fabrication process technologies, based on selective epitaxial growth (SEG) or re-crystallization, that can be used to grow single crystal or recrystallized poly-Si, separated by dielectric material, on top of an existing substrate [10, 26, 40, 41, 42, 43]. In selective epitaxial growth, as shown in Fig. 1-6, seed windows are opened on an oxidized Si substrate. Epitaxial growth is initiated through the seed window in the presence of dichlorosilane which supplies the silicon [44, 10, 42, 40, 41]. The quality of devices fabricated on epitaxially grown layer can be as good as those in bulk silicon. However, the high processing temperature  $(600\ ^{0}C - 1000\ ^{0}C)$  in SEG can cause significant degradation

Figure 1-5: Package-level 3-D integration by vertical stacking of multi-chip modules [28].

Figure 1-6: Selective epitaxial growth of Si islands through seed windows for monolithic 3-D integration [44].

in the quality of devices on lower device layers. Moreover, due to the low melting points of some interconnect metals and barrier layers, only poly-silicon interconnect levels are allowed in lower device layers. Another popular technique for fabricating second Si layer is to deposit polysilicon on a fully processed wafer, recrystallize the polysilicon film by intense laser beam or Ge-seeded lateral crystallization, and fabricate devices on the re-crystallized Si layer [10, 26, 43]. However, in these recrystallization techniques, it is difficult to control the grain size variations, and the quality of thin film transistors is not as good as bulk Si devices.

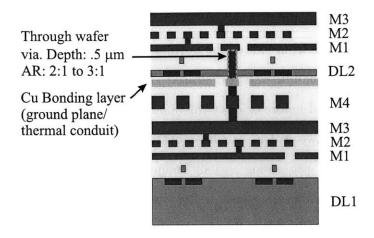

Low-temperature ( $< 450~^{\circ}C$ ) copper-copper or polyemide based wafer bonding can be used to bond two fully processed wafers for fabricating 3-D ICs [45, 46, 47]. In 3-D IC technology based on wafer bonding, after the fabrication of individual wafer, top wafer is

attached to a handle wafer, and it is thinned down from the back side. Then the backside of top wafer is bonded to the front side of the bottom wafer (i.e. back-to-front bonding); after the bonding process, the handle wafer is released. Through wafer vias for inter-device layer connections can be formed before or after the bonding step [46, 47]. Ideally, the processing steps required to bond two wafers can be repeated to bond as many wafers as desired. However, thermal issues, processing cost or complexity, etc. may dictate the number of wafers that can be profitably integrated. Using low-temperature wafer bonding technology, functional blocks that require different process technologies can be placed in different device layers to form 3-D SOC. A cross-sectional view of a 3-D IC formed by Cu-Cu wafer bonding is shown in Fig. 1-7. One of the limitations of wafer bonding technology is the lack of precision ( $\pm 3~\mu m$ ) in aligning Cu or metallic bumps using IR alignment to form interdevice layer interconnections. However, even with  $\pm 3~\mu m$  alignment tolerance, the number of available inter-device layer wiring tracks will be sufficient to meet the semi-global and global wiring need of a 3-D IC with a few device layers.

Compared to non-monolithic approaches to 3-D integration, the density of inter-device layer interconnections in monolithic approach is  $30 \times$  to  $50 \times$  higher. The relative cost for integrating various modules or components monolithically is generally smaller compared to packaging alternatives [48]. The potential improvements in form factor, power dissipation, or I/O bandwidth by monolithic 3-D integration may reduce the system cost compared to 2-D or 3-D package-level integration. Presently, Cu-Cu wafer bonding technique is being explored at MIT to demonstrate the feasibility of monolithic 3-D ICs. A detailed description of the process flow for fabricating 3-D ICs based on Cu-Cu wafer bonding is presented in Appendix A.

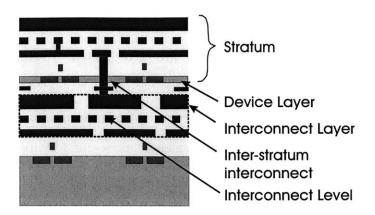

For clarity and to avoid confusion about the terminology for describing a 3-D IC, as shown in Fig. 1-8, following definitions will be used in this thesis work:

- Interconnect level: Combination of one metal layer of wires and one inter-level dielectric (ILD) with vias.

- Interconnect layer: A set of contiguous interconnect levels. E.g. multiple interconnect levels in a modern CMOS process.

DL = Device Layer M1-M4 = Interconnect Layers

Figure 1-7: Cross section of a 3-D integrated circuit formed by face-to-back Cu-Cu wafer bonding.

- Device layer: A planar layer of silicon in which transistors are fabricated. E.g. silicon wafer in bulk-Si CMOS IC or the thin silicon layer in a SOI-CMOS IC.

- Stacked device layer: Two or more device layer without intervening metal wires.

E.g. a system of silicon layers in which one of the layers is used as seed for crystalline growth by selective epitaxial growth (SEG) or by laser recrystallization.

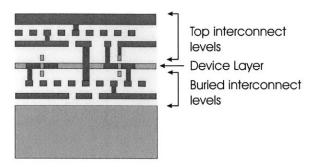

- Sandwich interconnect: Two or more interconnect layers sandwiching a thin device layers from top and bottom.

- Stratum: A combination of one device layer with a single interconnect layer, or sandwich interconnect.

- Multi-strata IC: Integrated circuits formed by stacking or bonding multiple strata and interconnecting them.

- Intra-stratum interconnect: Metal wires and vias which form electrical connection between two terminals within the same stratum.

- Inter-stratum interconnect: Metal wires and vias which form electrical connection between two terminals on different strata in multi-strata IC.

Figure 1-8: Key definitions and terminologies for describing a generic 3-D IC.

# 1.4 System-Level Performance Evaluation of Integrated Circuits and Contribution of Thesis Work

In system-level modeling and analysis, key performance metrics such as chip area, cycle time, interconnect parameters (number of interconnect levels, wiring pitch, etc.), etc. are estimated based on models representing system architecture, interconnection complexity, and device and interconnect technologies [49, 50, 51, 52]. Over the last several years, system-level modeling has been used quite successfully to assess the impact of scaling device and interconnect parameters and modifying system architecture on overall system performance [49, 50, 51, 52]. Circuit and system designers can use system-level modeling to estimate chip performance and wiring requirements at an early stage of a design cycle before routing and placement. Based on the feedback from system-level modeling, adjustments in chip design as well as wiring parameters can be made such that the final design can fit within the available Si area and required performance targets can be met.

Though some of the benefits of 3-D integration can be easily speculated, they have to be quantified so that key decisions for focusing future direction of research in this area can be made. It is also essential to examine the benefits and limitations in various approaches to 3-D integration so that cohesive research efforts can be directed to the most viable 3-D technology. In this thesis work, system-level modeling and analysis framework for 2-D ICs is extended to 3-D ICs to estimate key performance metrics and also to perform trade-off analysis for various approaches to 3-D integration. Based on system-level modeling, key

inter-stratum interconnect's density, etc. can also be estimated. To examine the interconnection complexity, a stochastic wire-length distribution model for 3-D ICs is derived and integrated in the system-level modeling framework. Various limiting cases of inter-stratum connectivity are also be examined. Key performance metrics for 3-D implementation of various VLSI circuits such as high-performance logic, microprocessors, reconfigurable circuits, etc. are estimated. For high performance logic circuits, it is found that significant reduction in critical path delay and chip area can be achieved by 3-D integration. Generally, system performance can be improved by increasing the number of strata. However, due to thermal issues, process complexity, yield, etc. it may not be profitable to integrate more than 4-5 strata.

Besides performance modeling, system-level analysis work is extended to examine thermal issues in 3-D ICs. Power dissipation in 3-D ICs is modeled by taking into account power dissipation due to driving device, interconnect, and clock wiring capacitance. Based on our analysis, due to the significant reduction in wiring capacitance in 3-D circuits, it will be feasible to reduce their total power dissipation compared to 2-D ICs for comparable system performance. However, due to the higher thermal resistance in 3-D ICs, for comparable amount of total power dissipation, junction temperature (in 3-D ICs) will be slightly higher than that of 2-D ICs. In this thesis work, detailed thermal analysis will be conducted to address both power dissipation and heat removal issues. Device- and package-level thermal analysis will be conducted based on numerical analysis and analytical models. Some recommendations will also be made to reduce the die temperature in 3-D ICs.

The thesis write-up is organized as follows: in Chapter 2, background on system-level modeling and analysis is provided. It is followed by the derivation of stochastic wire-length distribution of 3-D ICs and some case studies in Chapter 3. In Chapters 4 and 5, simulation results of system performance for various applications of 3-D ICs are presented. Thermal issues in 3-D ICs are discussed in Chapter 6, followed by Conclusions and Summary in Chapter 7.

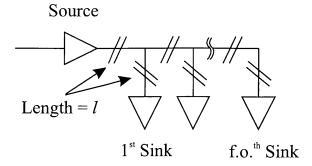

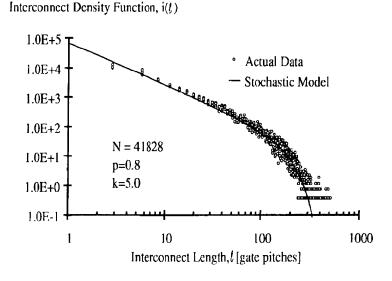

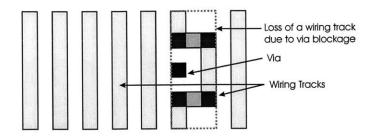

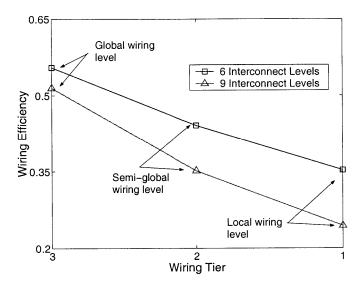

## Chapter 2