# System Scenario based Design of Dynamic Embedded Systems

- S. V. GHEORGHITA<sup>1</sup>, M. PALKOVIC<sup>2</sup>, J. HAMERS<sup>3</sup>, A. VANDECAPPELLE<sup>2</sup>,

- S. MAMAGKAKIS<sup>2</sup>, T. BASTEN<sup>1</sup>, L. EECKHOUT<sup>3</sup>, H. CORPORAAL<sup>1</sup>,

- F. CATTHOOR<sup>2,4</sup>, F. VANDEPUTTE<sup>3</sup> and K. De BOSSCHERE<sup>3</sup>

- <sup>1</sup> Eindhoven University of Technology, The Netherlands {s.v.gheorghita,a.a.basten,h.corporaal}@tue.nl

- <sup>2</sup> IMEC vzw, Leuven, Belgium

- {palkovic,vdcappel,mamagka,catthoor}@imec.be <sup>3</sup> Ghent University, Belgium

- {juan.hamers,lieven.eeckhout,frederik.vandeputte,koen.debosschere}@elis.ugent.be

- <sup>4</sup> Katholieke Universiteit Leuven, Belgium

http://www.es.ele.tue.nl/scenarios

In the past decade, real-time embedded systems have become much more complex due to the introduction of a lot of new functionality in one application, and due to running multiple applications concurrently. This increases the dynamic nature of today's applications and systems, and tightens the requirements for their constraints in terms of deadlines and energy consumption. State-of-theart design methodologies try to cope with these novel issues by identifying several most used cases and dealing with them separately, reducing the newly introduced complexity. This paper presents a generic and systematic design-time/run-time methodology for handling the dynamic nature of modern embedded systems, which can be utilized by existing design methodologies to increase their efficiency. It is based on the concept of system scenarios, which group system behaviors that are similar from a multi-dimensional cost perspective, such as resource requirements, delay, and energy consumption, in such a way that the system can be configured to exploit this cost similarity. At design-time, these scenarios are individually optimized. Mechanisms for predicting the current scenario at run-time and for switching between scenarios are also derived. This design trajectory is augmented with a run-time calibration mechanism, which allows the system to learn on-the-fly during its execution, and to adapt itself to the current input stimuli, by extending the scenario set, changing the scenario definitions, and both the prediction and switching mechanisms. To show the generality of our methodology, we show how it has been applied on four very different real-life design problems. In all presented case studies substantial energy reductions were obtained by exploiting scenarios.

Categories and Subject Descriptors: C.3.d [Computer Systems Organization]: Special-Purpose and Application-Based Systems—*Real-time and embedded systems*; D.2.10 [Software Engineer-ing]: Design—*Methodologies*

General Terms: Algorithms, Design, Performance

Additional Key Words and Phrases: Design methodology, dynamic nature, embedded systems, energy reduction, real-time systems, system scenarios

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee. © 2008 ACM 1084-4309/2008/0400-0001 \$5.00

# 1. INTRODUCTION

Embedded systems usually consist of processors that execute domain-specific applications. These systems are software intensive<sup>1</sup>, having much of their functionality implemented in software, which is running on one or multiple processors, leaving only the high performance functions implemented in hardware. Typical examples include TV sets, cellular phones, wireless access points, MP3 players and printers. Most of these systems are running multimedia and/or telecom applications and support multiple standards. Thus, these applications are full of dynamism, i.e., their execution costs (e.g., number of processor cycles, memory usage, energy) are environment dependent (e.g., input data, processor temperature).

Scenario-based design [Carroll 1995] has been used for some time in both hardware [Ionita 2005; Paul et al. 2006] and software design [Douglass 2004] of embedded systems. In both these cases, scenarios concretely describe, in an early phase of the development process, the use of a future system. They appear like narrative descriptions of envisioned usage episodes, or unified modeling language (UML) usecase diagrams [Fowler 2003] which enumerate, from a functional and timing point of view, all possible user actions and the system reactions that are required to meet a proposed system function. These scenarios are called *use-case scenarios*. They focus on the application functional and timing behaviors and on its interaction with the users and environment, and not on the resources required by a system to meet its constraints. These scenarios are used as an input for design approaches centered around the application context.

In this paper, we concentrate on a different and complementary type of scenarios, which we call system scenarios. These are derived from the combination of the behavior of the application and the application mapping on the system platform. These scenarios are used to reduce the system cost by exploiting information about what can happen at run-time to make better design decisions at design-time, and to exploit the time-varying behavior at run-time. While use-case scenarios classify the application's behavior based on the different ways the system can be used in its overall context, system scenarios classify the behavior based on the multi-dimensional cost tradeoff during the implementation trajectory. By optimizing the system per scenario and by making sure that the actual system scenario can be predicted at run-time, a system setting can be derived per scenario to optimally exploit the system scenario knowledge.

To motivate the system scenario usage in embedded system design, we start from the different *Run-Time Situations* (RTSs) in which a system may run on a given system platform. An RTS is a piece of system execution that is treated as an unit. Each RTS has an associated cost, which usually consists of one or several primary costs, like quality and resource usage (e.g., number of processor cycles, memory size). The system execution is a sequence of RTSs, and the current RTS is known only at the moment it occurs. However, at run-time, using various system parameters, so-called *RTS parameters*, it can be predicted in advance in which RTS the system will run next for a non-zero future time window. If the information

<sup>&</sup>lt;sup>1</sup>If the system's software contributes with essential elements to the design, construction, deployment, and evolution of the system as a whole, we talk about a software intensive system [IEEE 2000].

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, June 2008.

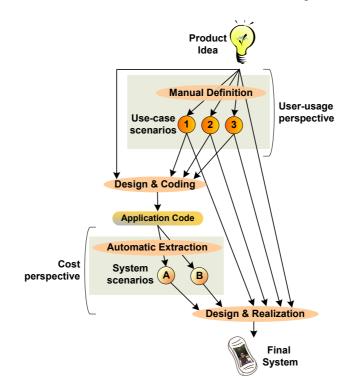

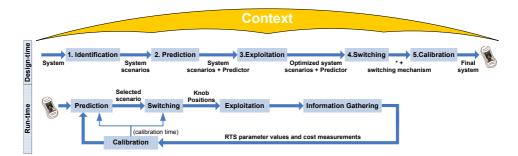

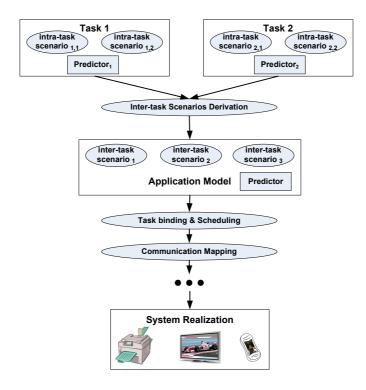

Fig. 1. A scenario based design flow for embedded systems.

about all possible RTSs in which a system may run is known at design-time, and the RTSs are considered in different steps of the embedded system design, a better optimized (e.g., faster or more energy efficient) system can be built because specific and aggressive design decisions can be made for each RTS. These intermediate per-RTS optimizations lead to a smaller, cheaper and more energy efficient system that can deliver the required quality. In general, any combination of N cost dimensions may be targeted. However, the number of cost dimensions and all possible values of the considered RTS parameters may lead to an exponential number of RTSs. This will degenerate to a long, and really complicated design process, that does not deliver the optimal system. Moreover, the run-time overhead of detecting all these different RTSs will be too high compared to the expected gain over their (quite) short time windows. To avoid this situation, in our work, the RTSs are classified and clustered from an N-dimensional cost perspective into system scenarios, such that the cost tradeoff combinations within a scenario are always fairly similar, the RTS parameter values allow an accurate prediction, and a system setting can be defined that allows to exploit the scenario knowledge and optimizations. This paper presents a systematic way of detecting and exploiting both at design-time and runtime the system scenarios of a given system. Generic solutions to the various steps in the methodology are provided whenever available. The method combines designtime analyses and optimizations with information collected at run-time about the environment in which the system is operating and the inputs being received.

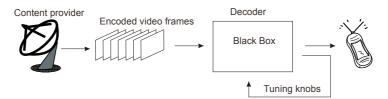

Fig. 2. Motivating example, no scenarios.

Figure 1 depicts a design trajectory using use-case and system scenarios. It starts from a product idea, for which the stakeholders<sup>2</sup> manually define the product's functionality as use-case scenarios. These scenarios characterize the system from a user perspective and are used as an input to the design of an embedded system that includes both software and hardware components. In order to optimize the design of the system, the detection and usage of system scenarios augments this trajectory (the bottom gray box from the figure). The run-time behavior of the system is classified using the methodology presented in this paper into several system scenarios, with similar cost tradeoffs within a scenario. For each individual scenario, more specific and aggressive design decisions can be made. The sets of usecase scenarios and system scenarios are not necessarily disjoint, and it is possible that one or more use-case scenarios correspond to one system scenario. But still, usually they are not overlapping and it is likely that a use-case scenario is split into several system scenarios, or even that several system scenarios intersect several use-case scenarios.

The paper is organized as follows. Section 2 gives a motivating example for our work, by showing how system scenario exploitation makes an H.264 video decoder more energy efficient. The system scenario methodology for embedded system design is detailed in section 3. It is accompanied in section 4 by case studies, that describe a diversity of applications that fit within this methodology, illustrating its broad application potential. Related work is presented in section 5, and the conclusions and our future plans are detailed in section 6.

# 2. MOTIVATING EXAMPLE

Figure 2 shows a typical system to which the system scenario design methodology is applicable. In this system, a content provider sends H.264 encoded sequences of video frames to a mobile device that decodes the content. The video decoder is often implemented as a main loop which is executed over and over again, reading encoded frames, decoding them and writing them to an output device (e.g., a screen). The application has to deliver a certain throughput (e.g., 30 frames per second), which imposes a time constraint on each loop iteration. Otherwise, the movie will stutter and the user's experience will degrade. When this kind of video decoder is implemented in a mobile device that is battery-operated and thus energyconstrained, the goal of using system scenarios when designing this system is to reduce the energy consumption, while retaining an acceptable frame rate.

$<sup>^{2}</sup>$ The stakeholders are persons, entities, or organizations who have a direct stake in the final system; they can be owners, regulators, developers, users or maintainers of the system.

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, June 2008.

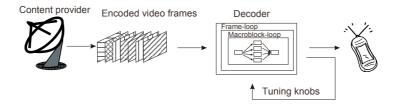

Fig. 3. Motivating example, system scenarios.

While every frame must be decoded within a fixed period of time, the actual time and energy needed to decode a frame on a processor with a given speed varies due to the dynamism exhibited by the video stream. Some frames require all the available decoding time while others demand only a fraction and leave the processor idle for the remaining time. On a small set of video sequences, we already noticed differences up to 450% in the required energy for decoding a single frame.

One well known technique for reducing energy consumption in this situation (fixed deadline, varying decode time) is Dynamic Voltage and Frequency Scaling (DVFS) [Jha 2001]. When scaling the voltage, the processor's frequency and therefore the execution time scales linearly ( $f_{CLK} \propto V_{DD}$ ), while the energy consumption scales approximately quadratically ( $E \propto V_{DD}^2$ ). As such, DVFS gives the system a *knob*, namely a choice to work at a certain frequency/voltage, that needs to be tuned at run-time. An important problem when applying DVFS in this situation is the need of knowing how many cycles (the *cycle budget*) are needed for decoding a frame, before actually decoding it. This is necessary to choose the appropriate scaling factor, i.e., to choose in which position to turn the DVFS system knob.

Existing DVFS systems work either fully dynamically based on run-time information, or fully statically based on design-time analysis. In the fully dynamic approach, no information about the decoder is considered except the notion of consecutive frames with different decode times that need to be decoded within a given deadline (figure 2). Without any information on how the internals of the decoder cause this variation in decode time, it is only possible to predict at run-time the required cycle budget of the current frame based upon the cycle budget needed for previously decoded frames [Hughes et al. 2001; Choi et al. 2002]. Another, fully static, approach considers complete information about the platform usage collected at design-time and uses static analysis to determine the remaining worst case cycle budget needed to complete execution at several points in the execution and fixes the DVFS system to the corresponding voltage and frequency [Shin and Kim 2005].

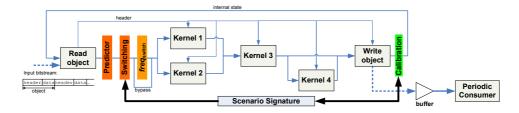

When using our proposed system scenarios (figure 3), we consider both information about the system at design-time, as well as the occurrence of certain types of input at run-time, which result in particular (groupings of) RTSs. Looking at the general structure of the H.264 decoder (figure 4), we see that each frame is subdivided into blocks of 16 by 16 pixels, called macroblocks. The main loop, which is the frame decoding loop, contains a second loop that iterates over the consecutive macroblocks. The read part of this loop takes an encoded macroblock object from the input stream and separates it into a *header* and the object's *data*. The write part places the decoded macroblock in the frame. The decoding part consists of several kernels. Each macroblock can be encoded using a different encoding scheme

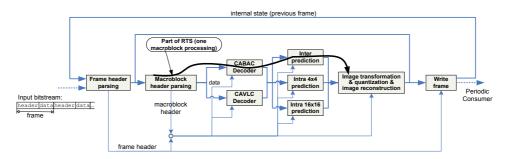

Fig. 4. Grey-box model of the H.264/AVC decoder processing a stream object.

that determines which kernels are used. Depending on the exact breakup of how many macroblocks of each frame belong to each scheme for a given iteration of the main frame loop, each of these kernels are executed for a certain number of times. This forms the *Run-Time Situation (RTS)* which can be characterized by the current *RTS parameters*, i.e., the macroblock breakup in this example. These parameters can be used to predict in advance the costs associated with the current RTS.

Considering each possible breakup of a frame for tuning the system at run-time would cause a too large overhead. When decoding CIF images (352 by 288 pixels), consisting of 396 macroblocks that may belong to 21 different encoding schemes, up to  $6.22 \cdot 10^{33}$  possible RTSs would need to be considered, and for each RTS the client has to store the optimal frequency/voltage. This is clearly impossible. Therefore, it is necessary to cluster frames with a similar breakup of macroblock types over the encoding schemes and mapping on the target platform. So frames that need similar cycle budgets are merged into the same system scenario. For each system scenario, we then determine the optimal knob setting of the mapping scheme and the platform. For example, we can determine the frequency/voltage setting of the DVFS scheme by using the cycle budget needed for a single (worst case) representative frame as the budget needed for all possible frames belonging to this scenario.

At run-time, whenever a client receives a movie from a content provider, it predicts for each frame the scenario it belongs to. Then, it scales the voltage and frequency according to the values determined at design-time, thereby reducing the energy consumption while still meeting the deadlines. Clearly, the more scenarios are considered, the higher the energy reduction that can be obtained, but also the more complex the prediction becomes. The prediction causes run-time overhead and it will add to the energy usage. The cost and gain of extra scenarios have to be traded off carefully to arrive at an optimal system. In the extreme, one can select a pure run-time controller approach. But then either the run-time decision overhead becomes too high, or the quality of the decision becomes very poor due to the too local view. The scenario approach avoids this bad tradeoff point.

Another interesting issue is to what extent scenario prediction can be made or needs to be made conservative. For complexity reasons, it may not be possible to consider all possible RTSs in the scenario definition. For the H.264 decoder, for

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, June 2008.

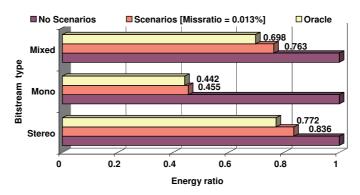

example, there are too many RTSs to take them all into account explicitly. When at run-time a frame arrives with a previously unseen macroblock breakup, it needs to be decided what to do. Hard guarantees on system performance can be given by predicting for these new breakups the *backup scenario*, which is the scenario that needs the overall worst case number of cycles to execute. However, this will often lead to less energy reduction than potentially possible. Since for video decoding a small percentage of missed frame deadlines is usually acceptable, one could aim for a more aggressive prediction, introducing the risk that a frame may get misspredicted as belonging to a scenario which has a lower cycle budget than the frame really needs, causing a missed deadline. This leads to a tradeoff between system quality in terms of missed deadlines and energy savings. In [Hamers et al. 2007], we managed to reduce energy consumption of the H.264 decoder by 46% with less than 0.1% of the deadlines missed, by using only 32 scenarios.

To exemplify the difference between use-case and system scenarios, let us consider a mobile device running an H.264 decoder that supports two different frame resolutions. From the user perspective, each resolution may be considered as a use-case scenario, because the resolution affects the perceived quality. Due to the different resolution, the two use-case scenarios contain a different number of macroblocks. Each of the two use-case scenarios can be divided automatically in more system scenarios based on the frame's macroblock mapping breakup, as presented above. This breakup is of no interest to the application designer or final product user, because it is a system-internal artefact of the video encoding, but it can be exploited to reduce energy consumption in the mapping. It may even be possible to integrate certain macroblock breakups of the two different resolutions into a single system scenario.

The following section details the systematic aspects of our methodology of identifying and exploiting system scenarios to create more efficient embedded systems, describing generic solution strategies for the various methodology steps whenever possible.

# 3. SYSTEM SCENARIO METHODOLOGY

Although the concept of system scenarios has been applied before on top of concrete design techniques both in an ad-hoc [Chung et al. 2002; Hansson et al. 2007; Murali et al. 2006b; Sasanka et al. 2002] as well as in a systematic way [Gheorghita et al. 2005; 2008b; Hamers et al. 2007; Mamagkakis et al. 2007; Palkovic et al. 2006; Yang et al. 2002], it is possible to generalize all those scenario approaches into a common systematic methodology. This section describes such a general and still near-optimal methodology, providing generic solutions whenever available. This generic methodology is the most important contribution of this paper. Parts of the solutions provided for the various steps, in particular those presented in sections 3.4 and 3.7, have not been published earlier. The methodology is applied to some specific contexts in section 4. The section is structured as follows. In section 3.1, the basic concepts behind the system scenario methodology are described. The methodology overview is given in section 3.2. The remaining subsections refine each of the steps of the general methodology. In the subsequent subsections, we always refer to system scenarios also when we use the abbreviated term *scenario*.

## 3.1 Basic Concepts

The goal of a scenario method is, given a system, to exploit at design-time its possible RTSs, without getting into an explosion of detail. If the environment, the inputs and the hardware architecture status would always be the same, then it would be possible to optimally tune the system to that particular situation. However, since a lot of parameters are changing all the time, the system must be designed for the worst case situation. Still, it is possible to tune the system at runtime (e.g., change the processor frequency/supply voltage), based on the actual RTS. If this has to happen entirely during run-time, the overhead is most likely too large. So, an optimal configuration of the system is selected up front, at designtime. However, if a different configuration would be stored for every possible RTS, a huge database is required. Therefore, the RTSs similar from the resource usage perspective are clustered together into a single scenario, for which we store a tuned configuration for the worst case of all RTSs included in it.

The system scenario methodology deals with two main problems. First, scenarios introduce various overheads due to switching between scenarios, storing code for a set of scenarios instead of a single application instance, predicting the RTS, etc. The decision of what constitutes a scenario has to take into account all these overheads, which leads to a complicated problem. Therefore, we divide the scenario approach into steps. Second, using a scenario method, the system requires extra functionality: deciding which scenario to switch to (or not to switch), using the scenario to change the system configuration, and updating the scenario set with new information gathered at run-time.

Many system parameters exist that can be tuned at run-time while the system operates, in order to optimize the application behavior on the platform which it is mapped on. We call these parameters system knobs. A huge variety of system knobs is available. Section 2 gives the example of DVFS; entirely different examples of other possible system knobs include the version of the code to run in case of an application that contains multiple versions of its source code, different compiler optimizations being applied to each of them [Palkovic et al. 2006], and the configuration of processing elements (e.g., number and type of function units) in a multi-processor system [Sasanka et al. 2002]. Anything that can be changed about the system during operation and that affects system cost (directly or indirectly) can be considered a system knob. Note that these changes do not have to occur at the hardware level; they can occur at the software level as well. A particular position or tuning of a system knob is called a *knob position*. If the knob positions are fully fixed at design-time, then the system will always have the same fixed, worst case cost. By configuring knobs while the system is operating, the system cost can be affected. In the DVFS example, the knob position is the choice of a particular operating voltage, and its change directly affects the processor speed and power, and indirectly the energy consumed to execute the application. However, tuning knob positions at run-time introduces overhead, which should be taken into account when the system cost is computed.

Instead of choosing a single knob position at design-time, it is possible, and highly desirable, to design for several knob positions. At different occurrences during runtime, one of these knob positions is chosen, depending on the actual RTS. When

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, June 2008.

the RTS starts, the appropriate knob position should be set. Moreover, the knob position is not changed during the RTS execution. Therefore, it is necessary to determine which RTS is about to start. This prediction is based on *RTS parameters*, which have to be observable and which are assumed to remain sufficiently constant during the RTS execution. These parameters together with their values in a given RTS form the RTS *snapshot*. In the H.264 example, the RTS corresponds to the decoding of a frame, and the RTS parameter is the frame breakup into the macroblock types.

The number of distinguishable RTSs from a system is exponential in the number of observable parameters. Therefore, to avoid the complexity of handling all of them at run-time, several RTSs are clustered into a single *system scenario*. A tradeoff is present here between optimisation quality and run-time overhead of the scenario exploitation. At run-time, the RTS parameters are used to detect the current scenario rather than the current RTS. In principle, the same knob position is used for all the RTSs in a scenario, so they all have the same cost value: the worst case of all the RTSs in the scenario. Therefore, it is best to cluster RTSs which have nearby cost values. Since at run-time any RTS may be encountered, it is necessary to design not one scenario but rather a *scenario set*. A scenario set is a partitioning of all possible RTSs, i.e., each RTS must belong to exactly one scenario.

The approach presented above is clear when the cost is one-dimensional, i.e., when one cost aspect dominates or when all the different cost aspects have been combined in a normalized weighted sum. The latter is not always easy in practice because "comparing apples and oranges" in a single dimension usually leads to inconsistencies and suboptimal results. Hence, N-dimensional Pareto sets can be used to specify the costs of a system scenario consisting of different RTSs instead of a weighted one-dimensional cost. Such Pareto sets [Pareto 1906; Geilen et al. 2007] allow to work with a Pareto boundary between all feasible and all non-feasible points in the N-dimensional cost space. The Pareto boundary (the Pareto points) for all the possible RTSs that have been clustered into a scenario (and that can potentially be encountered at run-time) characterizes the scenario. Unfortunately, it becomes less obvious to deal with statements like "nearby cost values of RTSs" or "taking the worst case of all the RTSs in the scenario". So, similarity between costs of different RTSs or in general sets of RTSs (scenarios) has to be substituted by a new element, e.g., by defining the normalized, potentially weighted distance between two N-dimensional Pareto sets as the size of an N-dimensional volume that is present in between these two sets. Based on this distance value, closeness of potential scenario options can be characterized, e.g., to decide whether or not to distinguish scenarios. An example of such an N-dimensional cost space and how to deal with it is provided in section 4.2. For more details, the reader is referred to [Okabe et al. 2003; Ykman-Couvreur et al. 2005; Ykman-Couvreur et al. 2006].

#### 3.2 Methodology Overview

Even though the system scenario concept is applicable to many contexts, we have devised a general methodology that can be instantiated in all of these contexts. This system scenario methodology and the presented generic solutions for some of its steps deal with issues that are common: choosing a good scenario set, deciding

Fig. 5. The system scenario methodology overview.

which scenario to switch to (or not to switch), using the scenario to change the system knobs, and updating the scenario set based on new information gathered at run-time. This leads to a five step methodology (figure 5), each of the steps having a design-time and a run-time phase. The first step, identification, is somewhat special in this respect, in the sense that its run-time phase is merged into the run-time phase of the final step, calibration.

- (1) *Identification* of the scenario set: In this step, the relevant RTS parameters are selected and the RTSs are clustered into scenarios. This clustering is based on the cost tradeoffs of the RTSs, or an estimate thereof. The identification step should take as much as possible into account the overhead costs introduced in the system by the following steps of the methodology. As this is not easy to achieve, an alternative solution is to refine the scenario identification (i.e., to further cluster RTSs) during these steps. Section 3.3 discusses the identification step in more detail.

- (2) Prediction of the scenario: At run-time, a scenario has to be selected from the scenario set based on the actual parameter values. This selection process is referred to as scenario prediction. In the general case, the parameter values may not be known before the RTS starts, so they may have to be estimated. Prediction is not a trivial task: both the number of parameters and the number of scenarios may be considerable, so a simple lookup in a list of scenarios may not be feasible. The prediction incurs a certain run-time overhead, which depends on the chosen scenario set. Therefore, the scenario set may be refined based on the prediction overhead. Section 3.4 details the two decisions made by this step at design-time: selection of the run-time prediction algorithm and refinement of the scenario set.

- (3) *Exploitation* of the scenario set: At design-time, the exploitation step is essentially based on some optimization that is applied when no scenario approach is applied. A scenario approach can simply be put on top of this optimization by applying the optimization to each scenario of the scenario set separately. Using the additional scenario information enables better optimization. At run-time, the exploitation is in fact the execution of the scenario. Section 3.5 details the common problems that should be handled during the exploitation step.

- (4) Switching from one scenario to another: Switching is the act of changing the system from one set of knob positions to another. This implies some overhead

(e.g., time and energy), which may be large (e.g., when migrating a task from one processor to another). Therefore, even when a certain scenario (different from the current one) is predicted, it is not always a good idea to switch to it, because the overhead may be larger than the gain. The switching step, detailed in section 3.6, selects at design-time an algorithm that is used at run-time to decide whether to switch or not. It also introduces into the application the way how to change the knob positions, i.e., how to implement the switch, and refines the scenario set by taking into account switching overhead.

(5) Calibration: The previous steps of our methodology make different choices (e.g., scenario set, prediction algorithm) at design-time that depend very much on the values that the RTS parameters typically have at run-time: it makes no sense to support a certain scenario if in practice it (almost) never occurs. To determine the typical values for the parameters, profiling augmented with static analysis can be used. However, our ability to predict the actual run-time environment, including the input data, is obviously limited. Therefore, we also foresee support for infrequent calibration at run-time, which complements all the methodology steps previously described. At design-time, information gathering mechanisms are designed and added to the application. At run-time they collect information about actual values of the parameters and the quality of the resulting system (e.g., number of deadline misses). Besides this, a calibration mechanism is introduced in the application. This is used to calibrate the cost estimates, the set of scenarios, the values of the parameters used for scenario prediction, and the knob positions. Calibration of the scenario set does not take place continuously during run-time, but only sporadically, at *calibration* time. Otherwise the overhead would obviously become too large. Also note that calibration is not meaningful when quality constraints are hard. It can only be applied if constraints are soft, or to optimize average-case behavior in the absence of constraints (e.g., when optimizing memory usage for energy reduction). Section 3.7 presents techniques for calibration.

In the following two paragraphs, we indicate intuitively why, in the design-time part of the methodology, the steps have been ordered as proposed. In particular, the reasoning behind this is based on a gradual pruning of the possible final scenario decisions. First, during identification, RTS parameters are limited to the ones that have a sufficient and observable cost impact on the final system. Then during clustering, we select the parameters that are easiest to be controlled as the actual system knobs and we cluster the corresponding RTSs based on similarity of cost (and knob settings, if applicable). In this way, we ensure that the cost distance between any two scenarios is maximized. This is needed because we have a clear tradeoff between the gains by introducing more scenarios and the cost it involves. This tradeoff leads to a further pruning of the search space for the most effective final scenario decisions. In the prediction step, we have to limit the potentially most usable scenarios to the ones that are also predictable at run-time with an affordable overhead. Also here a global tradeoff between gain and cost (run-time prediction overhead) is present. We cannot perform this second step of our method prior to the identification step because we cannot estimate the prediction cost before we at least have a good idea about the clustering of RTSs in scenarios. Note that the

opposite is not true: the information of the prediction step is not essential to decide on the clustering. This creates an asymmetrical relation which is the basis for the split between the two steps (see also the constrained orthogonalization approach in [Catthoor 2000]).

Only when we have decided how to perform the prediction, we can start the exploitation of the resulting scenarios in the particular application domain (step 3). Indeed, we could already start the exploitation after having the first clustering step, but that is not always efficient: the knowledge of the prediction cost will give us more potential for making good exploitation decisions. In contrast, the knowledge of the exploitation itself is not yet needed to make a good pruning choice on the prediction related selection. Finally, in the proposed design trajectory, we only decide on the scenario switching based on the actual overhead that is involved in the switching. The latter is only known after we have decided how to exploit the scenarios. The calibration step can be applied only when the rest of the steps are already done, as information about the scenario set, and the prediction and switching algorithms are needed to design the information gathering and calibration mechanism. So every step of our design-time methodology is positioned at a location where it has maximal impact but also where the required information to effectively decide on it is available as much as possible. The proposed split up in steps and order avoids phase coupling to a large extent. This avoids iteration on any of the individual steps after completion of a subsequent step in the methodology, which is a deliberate and important property of our generic design methodology.

The ordering of the steps at run-time follows the natural ordering of the various activities as they are needed at run-time. The ordering is in line with the designtime ordering with two exceptions. The first one was already mentioned. The identification and calibration steps are integrated, because part of the run-time calibration step may be to identify new scenarios, and no other means to identify new scenarios at run-time are available. Furthermore, the order of switching and exploitation is reversed when compared to the design-time order, as the run-time switching prepares the system for the given exploitation.

The next subsections detail the various steps of the methodology, outlining generic solutions whenever such solutions are available. The implementation of predictors presented in section 3.4 and the calibration mechanisms of section 3.7 have not been published earlier. All the presented solutions have been fully automated, and are applied in the various case studies presented in section 4.

#### 3.3 Identification

Before gaining the advantages that a scenario approach gives, it is necessary to identify the different scenarios that group all possible RTSs. This identification process happens in two phases, RTS parameter discovery and RTS clustering.

First, the interesting snapshot parameters are discovered. As mentioned before, a snapshot contains all parameters as well as their values that characterize a certain RTS. However, we are only interested in those parameters which have an impact on the system's behavior and execution cost. For example, interesting RTS parameters for an audio-video system are the size of the video frame, and whether the audio stream is mono or stereo.

The values of the selected parameters will be used to distinguish between the different RTSs, so two RTSs with the same snapshot are considered identical. However, they may still have different actual cost values, due to a choice of the parameters that does not precisely capture all the unique system behaviors. For example, two RTSs with a different data-dependent loop bound have a different execution time, but we consider them the same RTS if we are not observing that loop bound. When we are also observing that loop bound, each number of iterations corresponds to a different RTS. In the general case, a parameter selection that does not precisely capture all the individual behaviors of a system may lead to RTSs with a set of Pareto points in the multi-dimensional cost space as their actual (worst case) cost values. Such a parameter selection may be due to an imperfect analysis or for complexity reasons. However, it may also be deliberate, e.g., with the intention to handle certain minor dynamic variations or configuration options (i.e., a choice among different knob positions) entirely at run-time, or to create a hierarchy of scenarios, where the variation within one scenario at a certain hierarchical level is handled by another set of (sub-)scenarios.

Second, following the parameter discovery, all possible RTSs are clustered into system scenarios based upon a multi-objective cost function. The multi-objective cost function is dependent on the specific optimization and the system knobs we have in mind for the exploitation step. For the H.264 decoder presented in section 2, which targets a single-processor platform, we aim at reducing energy by applying DVFS and so we need accurate cycle-budget estimations for decoding the frames. The objective function in this case is one-dimensional and it is represented by the cycle budget needed for decoding each frame. (Note that the decoding of a frame was considered the RTS in this example.) For multi-media applications running on a multi-processor platform, the cost is typically multi-dimensional, including for example cycle budgets per processor, the derived frame decoding times and, when aiming at power optimization, derived power budgets. Whereas the knob for configuring a single-processor system for power optimization via DFVS is simply a single frequency setting, the knobs in a multi-processor system may potentially include configuration options of the various processors, the interconnect, the memory hierarchy, and other platform components. The RTS clustering into scenarios needs to take both cost and knob settings into account, to guarantee that only RTSs with compatible knob settings and similar costs are clustered into a single scenario.

The remaining part of this section details the two phases of the identification process.

3.3.1 *RTS Parameter Discovery.* In related work done so far, usually, parameter discovery is done in an ad-hoc manual manner by the system designer, by analyzing the application and profiting from domain knowledge. This is fine when all the important parameters are immediately obvious, such as the frame size in a video decoder. However, this process might prove tedious and incomplete for complex systems, as parameters that may have a large impact on the system behavior might go unnoticed. Developing a fully general tool that discovers the interesting parameters for all the design approaches where scenarios may be applied is hard, maybe even impossible, to realize due to the diversity of cost functions and optimization objectives. Therefore, we have developed a quite broadly applicable

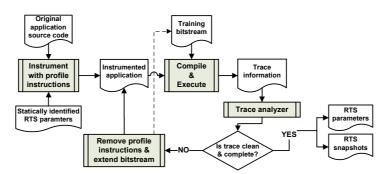

Fig. 6. RTS parameter identification approach.

domain-specific approach that is presented in the remaining part of this subsection.

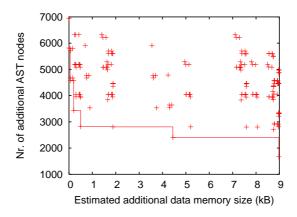

Our tool searches for control variables in the application source code that have a certain impact on the application resource requirements (e.g., number of cycles, memory utilization). These parameters fulfill the two requirements for selection: they are observable and they influence the application's behavior and cost (i.e., the resource needs). A first version of this tool [Gheorghita et al. 2005] statically analyzes the application source code to identify these variables. It is applicable for hard (real-time) constraints, due to the conservative analysis. In [Gheorghita et al. 2008b], a version applicable for soft real-time systems is presented. It profiles the application, and it uses the collected information for eliminating those control variables whose values do not have a real impact on system cost.

Our profiling based approach, detailed in figure 6, starts from the application source code which is then instrumented with profile instructions for all read and write operations on the statically identified variables. The instrumented code is then compiled and executed on (the initial part of) a training bitstream and the resulting program trace is collected and analyzed. The trace analyzer identifies the variables which do not have a large influence on the application behavior using different heuristics (e.g., it identifies the instructions that read and write to a large number of variables, which resembles an array-like access pattern; the accessed variables are considered to be data variables which have a small influence on the system behavior). In the next iteration, the instrumentation for these variables is removed and the application is executed on a larger part of the training sequence. This procedure is repeated until the entire sequence is processed and the trace analyzer does not dismiss any more variables. In each step of the design, and at each iteration, manual intervention is possible, but not necessary, to steer the decision process. The final result of this automated discovery is thus a list of relevant RTS parameters. During the profiling step it is of course possible to collect additional information such as the met RTSs identified by their snapshot, together with their cost. This information is then used in the RTS clustering step. However, finding a *representative* training bitstream that covers most of the behaviors that may appear during the system life-time, particularly including the most frequent ones, is in general a difficult problem. Hence, in contrast with analysis based identification that covers all possible RTSs, the profiling based identification is not conservative. It can happen that, at run-time, when the system runs, an RTS

that was not considered during identification is met. Therefore, a way of handling this situation should be added in the final implementation of the system. The calibration step in our method (see section 3.7) has been included for this reason, among others. Experiments show that the combination of profiling based parameter discovery and calibration is quite robust (see section 4.1), alleviating the problem of finding representative training sets and reducing the time needed for training.

3.3.2 RTS Clustering. Using the discovered RTS parameters, all identified RTSs are clustered into a set of system scenarios. For each RTS, in the most general case, we have a Pareto surface of potential exploitation points in the multi-dimensional exploration space. The clustering is done based upon a multi-objective cost function which is related to the specific optimization we want to apply to the system. Hence, the clustering searches for RTSs with similar Pareto surfaces. It starts from RTS snapshots and generates a set of scenarios, each of the scenarios being identified by a set of snapshots. The clustering takes into account the following information: (i) how often and for how long each RTS occurs at run-time, (ii) the cost deviation that occurs when clustering multiple RTSs into a single scenario, (iii) how many switches occur between each pair of scenarios, and (iv) the run-time scenario prediction, storage and switching overhead. It furthermore has to make sure that knob settings for the RTSs clustered in a single scenario are compatible. Having a multi-dimensional cost function means that both the inherent scenario costs and the switching cost becomes multi-dimensional also. Creating a good scenario set under these constraints can be formulated as an N-dimensional optimization problem. However, this optimization problem does not have a general practically executable solution, so heuristics need to be developed.

When clustering different RTSs into a scenario, we determine the cost of the scenario as the maximal cost of the RTSs that compose the scenario (which in a multi-dimensional cost space results in a Pareto surface). The clustering process is driven by two opposing forces. One force drives towards a large number of scenarios that contain a few RTSs, the extreme being each scenario to contain only one RTS, by only grouping RTSs with similar cost together, so that the estimated deviation between the cost value of an RTS and the cost of the scenario remains small. It uses the information from items (i) and (ii) of the list above. The other force takes into account the overheads (items (iii) and (iv) of the above list) introduced by the existence of a large number of scenarios, and it aims to decrease the number of scenarios by increasing their size in the number of contained RTSs.

Since the application does not remain in the same scenario forever, the switching overhead has to be taken into account. This overhead usually has effects on the cost function (e.g., scaling frequency and voltage of the processor costs both time and energy). So, depending on how large the switching overhead is, the aim is to reduce the number of scenario switches that appear at run-time. Taking this into account, the two forces identified above have to generate a tradeoff by clustering together into a scenario, not only RTSs with similar cost, but also the ones between which many switches appear at run-time.

The storage overhead of scenarios is strongly dependent on the kind of optimizations that are applied in the exploitation step. For example, in the H.264 decoder presented in section 2, a table has to be kept which maps the different scenarios

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, June 2008.

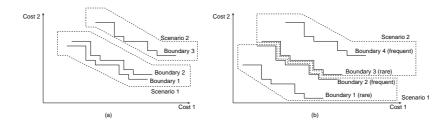

Fig. 7. Examples of RTS clustering.

to the optimal frequency-voltage pair. When the number of scenarios increases so does the size of this table, but the overhead per scenario will be small. On the other hand, in the case study presented in section 4.2, when optimized code is generated for each separate scenario, the overhead for storing this scenario-specific code is rather large.

Finally, since the scenarios need to be predicted at run-time, there is also the scenario predictor to consider. If the amount of scenarios increases, it will result in a larger and perhaps slower predictor. Also, the probability of a faulty prediction may increase with the number of possible scenarios.

Figure 7(a) depicts a clustering example with a two-dimensional cost function. Each RTS is represented by a (two-dimensional) Pareto boundary which represents different RTS knob configurations. Usually, the RTSs with similar Pareto boundaries are clustered to one scenario at design-time. Thus, the distance between two Pareto boundaries determines which ones to cluster. The cluster is then represented by its worst-case Pareto boundary. Based on this criterion, boundaries 1 and 2 are clustered in figure 7(a), forming the first scenario. Boundary 3 forms alone the second scenario. As already mentioned, apart from the distance also the frequency of occurrence is important. If a very frequent RTS is clustered with a very rare one, which has a worse Pareto boundary, this scenario and all RTSs in this scenario inherit the worse, rare Pareto boundary. In such a case, it is better to cluster the frequent Pareto boundaries with better rare Pareto boundaries so that the frequent Pareto boundary represents the created scenario. This is depicted in figure 7(b). This analysis and clustering is done at design-time. At run-time, the appropriate scenario with its Pareto boundary is identified and a concrete Pareto point is selected related to a specific knob configuration.

#### 3.4 Prediction

This step aims at deriving a predictor, which can determine at run-time the appropriate scenario in which the system executes. It starts from the information collected in the identification step. Just as this parameter identification step, scenario prediction can be solved in a rather generic way that is widely applicable. The resulting predictor mainly bases its decision on the values of the RTS parameters. Moreover, it has to be flexible (e.g., to have a structure that can be easily modified during the calibration phase) and to add a small decision overhead in the final system. We can define it as a prediction function:

$$f: \Omega_1 \times \Omega_2 \times \dots \times \Omega_n \to \{1, \dots, m\},\tag{1}$$

where n is the number of RTS parameters,  $\Omega_k$  is the set of all possible values of the parameter  $\xi_k$  (including ~ that represents undefined) and m is the number of scenarios in which the system was divided. The function f maps each RTS i, based on the parameter values  $\xi_k(i)$  associated with it, to the scenario to which the RTS belongs. If at run-time an RTS occurs that was not considered during the identification phase (e.g., because it was not met during profiling), it is mapped to the scenario that can deal even with the worst-case situation, the so-called *backup scenario*. If any optimization takes place, it is based on a worst-case analysis at design-time.

A predictor based only on the prediction function approach can be applied only after all the parameter values are known. If the identification was done in a conservative mode, which covers all possible RTSs that may appear at run-time, the prediction accuracy will be 100%, and we can speak about scenario detection. Waiting until all the parameter values are known at run-time may postpone the prediction moment unnecessarily long, and the scenario may be predicted too late to still profit maximally from the applied optimization. To handle this problem, multiple approaches may be considered (not necessarily in isolation), like (i) reducing or changing the set of considered parameters, and (ii) combining the prediction function with pure probabilistic prediction. In the first approach, we search for the set of parameters that can be used to identify the set of predictable scenarios that gives the highest gain, taking into the account the moment when they can be predicted at run-time. In the second case, the scenario prediction point may be moved to an earlier point in time by augmenting the prediction function with a mechanism that selects from the possible set of scenarios predicted by the function, the one with highest probability. For example, the mechanism may use advanced phase predictors [Vandeputte et al. 2005]. Using the probabilistic approach, the miss-prediction may increase. It is of two types: (i) over-prediction, when a scenario with a larger (multi-dimensional) cost is selected, and (ii) under-prediction, when a scenario with smaller (multi-dimensional) cost is selected. The first type does not produce critical effects, just leading to a less cost effective system; the second type often reduces the system quality, e.g., by increasing the number of deadline misses for the H.264 decoder.

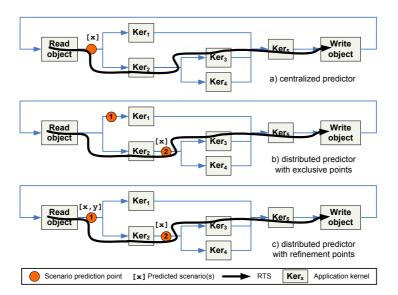

The place where the prediction function is introduced into the application, is called a *scenario prediction point*. From a structural point of view, considering the number of times and the places where the prediction function is introduced into the application, the predictors can be classified as follows:

- -*Centralized*: There is only one central point in the application where the current scenario is predicted. It is inserted in the application code in a common place that appears in all scenarios. For example, in the case of the application model presented in figure 8(a), it is introduced in the main loop, after the read part, when all the information necessary to predict the current scenario is known.

- *—Distributed*: There are multiple scenario prediction points, which may be:

- -Exclusive points: An identical (or tuned) prediction function is introduced multiple times into the application, in all the places where the RTS parameter values are known. At run-time, only one point from the set is executed in each RTS. This kind of predictor solves the problem that there may be no

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, June 2008.

Fig. 8. Types of scenario prediction.

common place in all scenarios, where a centralized predictor may be inserted. Figure 8(b) depicts a case where one of two prediction points is being executed for different RTSs.

Refinement points: Multiple points, which work as a hierarchy, are used to predict the current scenario in a loop iteration; the first that is met at runtime predicts a set of possible scenarios, and the following refine the set until only one scenario remains. This extension can improve the efficiency of optimizations as earlier switching between scenarios may be done, but it increases the number of switches. Hence, a tradeoff should be considered when using it, which depends on the problem at hand. This is actually a very similar problem tradeoff as the one for the RTS clustering substep. Hence, we believe that also here a similar set of heuristic algorithms can be reused. Usually, when switching between scenarios after a refinement predictor, the new scenario may be the scenario with the worst case cost from the remaining set of scenarios. However, the probabilistic approach presented above could also be used to select the scenario to which to switch. For the example depicted in figure 8(c), considering the scenario that executes kernels two, three and five, in the first scenario prediction point the set containing scenarios x and y is selected. Then, in the second scenario prediction point, the set is refined to only one scenario, x.

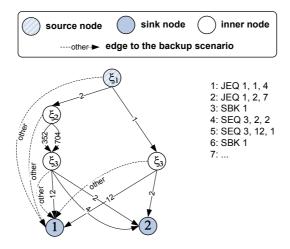

A generic implementation of a prediction function f, which incorporates requirements like flexibility and small overhead, is a *multi-valued decision diagram* [Wegener 2000], which consists of a directed acyclic graph G = (V, E) and a labeling of the nodes and edges. The sink nodes get labels from 1, ..., m and the inner (nonsink) nodes get labels from  $\xi_1, ..., \xi_n$ . Each inner node labeled with  $\xi_k$  has a number of outgoing edges equal to the number of the different values  $\xi_k(i)$  that appear for

Fig. 9. An example of a decision diagram and its implementation.

| OP  | VARIABLE-ID | VALUE       | DATA          | Description                                                                                                                                       |

|-----|-------------|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| JEQ | <var></var> | <val></val> | < address >   | Jump to <address> if <var> is equal to <val></val></var></address>                                                                                |

| JL  | <var></var> | < val >     | < address >   | Jump to $\langle address \rangle$ if $\langle var \rangle$ is less than $\langle val \rangle$                                                     |

| JMP | -           | -           | < address >   | Unconditional jump to <address></address>                                                                                                         |

| SEQ | <var></var> | <val></val> | <scenario $>$ | Predict <scenario> if <var> is equal to <val></val></var></scenario>                                                                              |

| SLE | < var >     | < val >     | <scenario $>$ | $\label{eq:predict} \mbox{Predict} < \mbox{scenario} > \mbox{if} < \mbox{var} > \mbox{is} \mbox{ less or equal to} < \mbox{val} > \label{eq:var}$ |

| SBK | -           | -           | <scenario $>$ | Predict <scenario> as a backup scenario</scenario>                                                                                                |

Table I. Instruction set used in predictor implementation.

RTS parameter  $\xi_k$  during the identification phase plus an edge labeled with other that leads directly to the backup scenario. Only one inner node without incoming edges exists in V, which is the source node of the diagram, and from which the diagram evaluation always starts. On each path from the source node to a sink node each RTS parameter  $\xi_k$  occurs at most once. A simplified example of a decision diagram for the motion compensation kernel from the H.264 video decoder is shown in figure 9. When a prediction function is used, it introduces two overheads: (i) code size and (ii) average run-time evaluation cost. Also this is similar to the RTS clustering substep. In the proposed solution, both depend on the decision diagram size (number of nodes and edges). Hence, reducing its size, the overheads decrease. However, the applied reduction rules may affect the prediction quality, especially for the RTSs that were not considered during the identification step (because for these RTSs, a different scenario may be predicted instead of the backup scenario). A few reduction rules are analyzed in [Gheorghita et al. 2008b]. Note that these reductions may render certain RTS parameters redundant, which happens if they do no longer occur in the final predictor. Also note that, conceptually, decision diagram transformations are scenario refinements, because a transformation affects the parameter value ranges characterizing a scenario.

We propose to implement decision diagrams as a program in a restricted programming language. The language is specified in table I and an example of its use is given in figure 9. The program implementing a decision diagram is represented by

PREDICTSCENARIO(HASHTABLE values, VECTOR dd) 1  $pc \leftarrow 1$ while TRUE 2 **do** value  $\leftarrow$  values[dd[pc].VARIABLE-ID] 3 4 if (dd[pc].OP = JEQ AND value = dd[pc].VALUE) OR (dd[pc].OP = JL AND value < dd[pc].VALUE) OR (dd[pc].OP = JMP)5then  $pc \leftarrow dd[pc]$ .DATA elseif (dd[pc].OP = SEQ AND value = dd[pc].VALUE) OR 6  $(dd[pc].OP = SLE AND value \leq dd[pc].VALUE) OR (dd[pc].OP = SBK)$ 7 then return dd[pc].DATA else pc + +8

Fig. 10. Decision diagram execution engine.

a data array in the application source code and it is executed by a simple execution engine, given in figure 10 and explained below. The proposed implementation has very little overhead and it allows an easy calibration of the decision diagram, by changing the values of appropriate array elements.

The language defined in table I allows to implement each edge of a decision diagram by one instruction, by using (i) a JEQ instruction if its destination node is labeled with a variable name, or (ii) a SEQ instruction if it is not labeled other and its destination node is labeled with a scenario name, or (iii) a SBK instruction if it is an other labeled edge. To reduce implementation costs, a group of adjacent edges that have a common destination can be implemented using only two instructions, using the JL and SLE instructions. The JMP instruction is used for calibration, as explained below.

The program that represents the decision diagram is executed by the execution engine presented in figure 10. This engine receives as input parameters a hash table (values) containing the pairs variable/value for the current RTS, and a vector (dd) containing the program that has to be executed. Each vector element represents an instruction. The position of the instruction to be executed is kept in the program counter pc, which is initialized to start with the first program instruction (line 1). The program execution ends only when an instruction that sets a scenario is executed and its condition, if present, evaluates to true (lines 6-7). If a jump instruction is met and its condition evaluates to true, the next instruction to be executed is determined by the data field of the current jump instruction (lines 4-5). Otherwise, if no condition evaluates to true, the program counter is set such that the next sequential instruction will be executed (line 8).

In conclusion, the above has detailed a generic form and implementation of scenario predictors, that is flexible and well suited for calibration, as explained in more detail in section 3.7. We end this section by mentioning several other aspects that may be addressed during the prediction step at design-time. The prediction step may cover the following actions: (i) a further clustering of scenarios considering the prediction overhead and the moment when the scenario may be predicted, (ii) possibly, a further pruning of the RTS parameters, (iii) clustering of previously unassigned RTSs (i.e., the ones that were not met during the identification process) into scenarios, and (iv) defining and placing the prediction mechanism into the application, by trading off prediction accuracy versus overhead, which influence the final system cost and quality.

Fig. 11. Scenario source code merging.

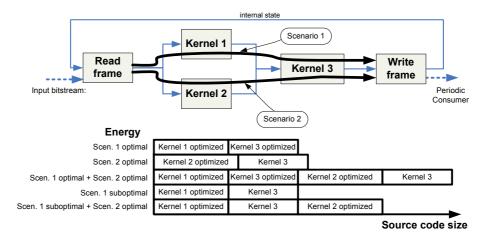

### 3.5 Exploitation

The exploitation step in the scenario methodology is very dependent on the context in which scenarios are applied. Nevertheless, some general aspects to be kept in mind can be mentioned. Exploitation in the context of the scenario methodology should be refined in two ways, to a large extent independently of the type of exploitation. First, optimizing each scenario in isolation might be inefficient. There is a strong correlation between the analysis and the optimization choices of the different scenarios, so the optimization of a scenario can be performed more efficiently by reusing information from other scenarios. Second, separate optimization for each scenario leads to separate systems. Simply putting all these next to each other could imply a huge overhead. Therefore, whatever is common between different scenarios should be merged together, e.g., by using code compaction techniques [Debray et al. 2002; De Sutter et al. 2006]. The remaining differences cause exploitation overhead, which should be taken into account to further refine the scenario set. Some optimizations that are suboptimal for an individual scenario, might be optimal from the system cost perspective when considering exploitation overhead. How difficult it is to simultaneously optimize scenarios depends on the context. As an example, figure 11 depicts an application with two scenarios: scenario 1 for the case where kernels 1 and 3 are executed, and scenario 2 for the case where kernels 2 and 3 are executed. To optimize the application for energy, a compiler may optimize each scenario separately to reduce the number of computation cycles. Assume that the energy-optimal exploitation of each scenario is, for scenario 1, to optimize both kernels 1 and 3, and, for scenario 2, to optimize only kernel 2, kernel 3 already being energy optimal for this scenario. Combining these two optimal scenario exploitations, the application source code contains code for kernel 3 twice (once optimized for scenario 1, and once untouched, as used in scenario 2). If the energy overhead introduced by storing the two versions of kernel 3 is large, the energy-optimal system might be obtained by using a suboptimal version of scenario 1, as presented in figure 11. This version uses the original implementation of kernel

3, so no code duplication for this kernel is needed in the final implementation of the application.

Both mentioned exploitation refinements for scenarios are specific to the type of optimization that is performed, so exploitation cannot really be fully generalized, illustrative examples being given in the literature overview of section 5 and the case studies of section 4.

#### 3.6 Switching

A system execution is a sequence of RTSs, and therefore a sequence of scenarios. At the border between two scenarios during execution, switching occurs. For executing this switch at run-time, at design-time a mechanism is derived and introduced into the system. The switching decision and process (changing the knob positions) may incur overhead, which is taken into account to further refine the scenario set. Moreover, it is also taken into account at run-time to decide whether or not to switch to a different scenario, together with other information (i.e., the sequence of previous and possible following RTSs). The expected gain times the expected time window where the scenario is applicable has to be compared to the exploitation cost, as already mentioned. The structure of this switching mechanism should be flexible enough to allow it to be calibrated.

Even if the switching overhead is exploitation dependent, our methodology treats this overhead in a general way. It uses the scenario cost versus overhead reports (e.g., energy, time) together with the information about how often a switch between two given scenarios appears at run-time, to avoid spending most of the system's running time on switching between scenarios, instead of on doing relevant work. For our H.264 example from section 2, the switching operation adjusts the supply voltage and processor frequency. Its overhead in time and energy depends on the implementation. Using the hardware circuit presented in [Burd et al. 2000] for switching, the overhead measured in time is up to  $70\mu s$  and in energy up to  $4\mu J$ . These overheads affect both the final system cost (e.g., more energy consumption) and its run-time properties (e.g., more deadline misses because of time overhead). It is important to compare the time overhead with the minimum time the system stays in a scenario, which is equal to the required period between two consecutive frames (or smaller due to late scenario prediction). For a throughput of 30 frames per second, a switch may be acceptable between each pair of consecutive frames, as the overhead represents up to 0.2% of the time (70µs out of 33ms). On the other hand, for an application with for example 2500 RTSs per second, the switch overhead per frame represents 20% of the time, so the switches should be quite rare. Another illustration of the very small overhead of the run-time controller is reported in [Yang and Catthoor 2003].

The way how the exploitation step encodes the scenarios into the system affects the switching cost. As we already mentioned, in the H.264 example, for each scenario a frequency-voltage pair is stored. However, for other exploitation examples, like the one presented in section 4.2, a copy of the source code for each scenario should be stored. These copies introduce large supplementary costs into the final system for each added scenario, and limit the total number of scenarios. The technique presented in section 4.2 can find a scenario set which achieves the best data memory optimization for the given instruction memory overhead. For a scenario

that is rarely activated, its source code may be kept in a compressed version to reduce the storage cost, but as a decompression is done when the scenario is enabled, this increases the switching overhead.

Thus, the overhead for switching between two scenarios depends on what the runtime switching implies, and the scenarios between which the application switches. The switching overhead affects both the final system cost (e.g., more energy consumption) and its run-time properties (e.g., more deadline misses because of time overhead). In the switching step at design-time, in parallel with deriving the switching mechanism, the set of scenarios, and consequently the predictor, may need to be adapted. This adaptation takes into account the cost of each scenario, how often the switch between each pair of scenarios appears at run-time and how expensive it is. Two scenarios that were considered separately so far but which have a relatively close cost, and between which the system switches very often at run-time might be merged in a scenario with the worst case cost among them.

The time overhead introduced by switching may cause undesired side-effects in a system, such as deadline misses in an H.264 decoder. Besides system and context dependent ways of handling such side-effects (e.g., an H.264 decoder may display the previous frame again if the deadline for the current frame is missed), we looked at a general way for minimizing the side-effects that are caused by the time overhead introduced by the switching mechanism. The most conservative way to handle this overhead is to reserve time in each scenario, considering that the scenario is always activated for only one RTS in a row and taking into account the largest switching time that may appear. This approach might be very expensive, in which case it is a viable solution only for systems that require hard guarantees. For systems where more freedom is acceptable, in each scenario, we may reserve time considering the switching time overhead averaged over the typical number of subsequent RTSs spent in a scenario, and the possible over-estimation in timing requirements that exist in the scenario. Such an over-estimation appears because for all RTSs clustered into a scenario, their worst case cost is considered always when the scenario appears. Moreover, buffers exist in almost all modern systems, such as an output buffer in a video decoding system, which potentially can be used to compensate for the overhead variations that appear at run-time.

#### 3.7 Calibration

The previous presented steps of our methodology make different design-time choices (e.g., scenario set, prediction algorithm) that depend very much on the possible values of RTS parameters, typically derived using profiling. This approach is obviously limited by our ability to predict the actual run-time environment, including the input data. It may lead to run-time problems, like encountering an RTS that was not considered in the design-time choices, or an RTS with a higher cost than the one of the scenario to which it is predicted to belong. The first case appears when an RTS occurs at run-time of which the snapshot was not met during the identification step. In the second case, its snapshot was considered during the identification step, but the worst case cost observed for that snapshot is smaller than the actual cost of this RTS. This is also related to a possibly imperfect choice of the parameters or simplification of the predictor. Therefore, calibration can be used at run-time to complement the methodology steps previously presented. And even if RTS pa-

rameters guarantee correct prediction and costs are conservative, calibration can be useful to exploit for example a situation in which low cost RTSs occur for long periods of time in a row.

At run-time, information is collected about actual values of the RTS parameters, the predicted scenario, the decisions taken by the switching mechanism, the measured cost for each scenario prediction and the quality of the resulting system (e.g., the number of deadline misses). Both the execution cycles of the collecting process and the amount of stored information should be small as the collection is executed for each RTS. To keep the overhead limited, the calibration mechanism therefore has access to only a limited amount of information. Moreover, it should be implemented as a low complexity algorithm.

Periodically, sporadically (e.g., when time slack is found into the system), or in critical situations (e.g., when the system quality is too low due to a certain number of missed deadlines), the calibration mechanism is enabled. Based on the collected information, it may (i) change the ranges of parameter values and knob positions that characterize each scenario, and (ii) adapt the scenario set by clustering existing scenarios or introducing new ones. In these cases, the prediction, and maybe the switching mechanism have to be adapted as well. However, during the calibration, no new parameters or knobs are added, because this leads to a complicated and expensive process, as to exploit the new parameters the predictor should be redesigned and for the new knobs the scenario exploitation step should be redone.

Depending on the optimization applied in the exploitation step, the most common operations in the two above mentioned categories that can be done efficiently considering the calibration's limited processing and storage budgets are:

- (1) To consider new RTSs that were not considered at design-time, and to map them to the scenario where they fit the best, based on the cost function, or to a new scenario. In this case, the predictor and the switching mechanism are also extended. As the complexity of the extension algorithm should be low, the resulting predictor will in general not be as efficient as if a new predictor were derived from scratch taking into account these new RTSs. Moreover, because an explosion in scenario storage has to be avoided, not for each RTS a new scenario can be created, but only for the ones which appear frequently enough to be promising for our final objective or problematic in terms of system quality.

- (2) To increase the actual cost of a scenario, based on its RTSs observed at runtime. This case may appear because the RTSs are defined using a limited set of parameters, and it is possible that there exist multiple equivalent RTSs with different cost and only the cheaper ones were considered at design time. The same problem may occur also when prediction quality is low, if many RTSs are incorrectly predicted to belong to a scenario with a cost that is too low (under-prediction).

- (3) To increase the cost of some or all scenarios, because the run-time overhead introduced by related scenario mechanisms (e.g., prediction) is higher than anticipated. The same problem appears when the run-time overhead variations are too high and the buffering in the system can not handle those variations. These cases are related to the fact that the input data and the environment in which the system runs is an extreme case (e.g., a lot of scenario switches), and

```

CALIBRATION(INT RTSCounter, ...)

INFORMATIONGATHERING()

1

2

SMALLADAPTATIONS()

3

for i \leftarrow 1 to noCriticalCalibrations

4

do if (RTSCounter - cCalib[i].LASTACTIVATION > cCalib[i].PERIOD)

5

then cCalib[i].FN(...)

cCalib[i].LASTÁCTIVATION \leftarrow RTSCounter

for i \leftarrow 1 to noNonCriticalCalibrations

6

7

8

do if (RTSCounter - nCalib[i].LASTACTIVATION > nCalib[i].PERIOD)

9

then if ENOUGHSLACK(nCalib[i].WCEC)

10

then nCalib[i].FN(...)

nCalib[i].LASTACTIVATION \leftarrow RTSCounter

11

```

Fig. 12. Calibration structure.

the system was dimensioned for the average case.

(4) To decrease the cost of a scenario, when only the RTSs with a low cost from that scenario actually appear at run-time. This improves our system cost (e.g., reducing energy), but potentially affects system quality negatively when RTSs with a higher cost occur. To maintain system quality, the cost may be increased again via the mechanism described in item two of this list, or by monitoring the scenario, the scenario cost may be reset to the value that it had before calibration when one or a few of its RTSs with a higher measured cost than the current scenario cost occur.

As an example of the introduction of a new scenario, consider the predictor decision diagram and its implementation given in figure 9. Assume a new scenario 3 is defined for the case that variable  $\xi_1$  has value 7. This can be incorporated in the implementation of the diagram by changing line 3 into a jmp x instruction to jump to some given line x corresponding to an empty entry in the array implementing the decision diagram. Line x is then set to seq 1, 7, 3 and line x+1 to SBK 1. In this way, every newly introduced scenario corresponds to two lines in the program implementing the decision diagram. This is not the most concise representation, but it is very simple to implement, very simple to revert, if necessary, and it allows to reserve space in the decision diagram implementation for a fixed number of new scenarios to be added at run-time.